Page 1

GENERAL DESCRIPTIONGENERAL DESCRIPTION

GENERAL DESCRIPTION

GENERAL DESCRIPTIONGENERAL DESCRIPTION

EM73P461A is an advanced single chip CMOS 4-bit one-time programming (OTP) micro-controller. It contains

4K/8K-byte ROM, 244-nibble RAM, 4-bit ALU, 13-level subroutine nesting, 22-stage time base, two 12-bit timer/

counters for the kernel function. EM73P461A also contains 6 interrupt sources, 1 input port, 2 bidirection ports,

LCD display (32x4), and one high speed timer/counter with melody output.

EM73P461A has plentiful operating modes (SLOW, IDLE, STOP) intended to reduce the power consumption.

FEATURESFEATURES

FEATURES

FEATURESFEATURES

• Operation voltage : 2.4V to 3.6V.

• Clock source : Dual clock system. Low-frequency oscillator is Crystal or RC oscillator (32K Hz,

• Instruction set : 109 powerful instructions for 4K ROM / 107 powerful instructoins for 8K ROM.

• Instruction cycle time : Up to 2us for 4 MHz (high speed clock).

• ROM capacity : 4096 X 8 bits / 8192 X 8 bits ROM are choosed by mask option.

• RAM capacity : 244 X 4 bits.

• Input port : 1 port (P0). P0(0..3) and IDLE releasing function are available by mask option.

• Bidirection port : 2 ports (P4, P8). P4.0 and SOUND is available by mask option. P4.1 is shared with

• 12-bit timer/counter : Two 12-bit timer/counters are programmable for timer, event counter and pulse width

• High speed timer/counter : One 8-bit high speed timer/counters is programmable for auto load timer, melody

• Built-in time base counter : 22 stages.

• Subroutine nesting : Up to 13 levels.

• Interrupt : External . . . . . 2 input interrupt sources.

• LCD driver : 32 X 4 dots, 1/4duty, 1/3duty, 1/2duty, static, 1/2 bias, 1/3 bias; 6 options selectable.

• Power saving function : SLOW, IDLE, STOP operation mode.

• Package type : Chip form 61 pins.

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

connect an external resistor) by mask option and high-frequency oscillator is RC

oscillator (connect an external resistor).

122 µs or 244µs by frequency double mask option for 32768 Hz (low speed clock).

HTC external input. P8(0..3) and IDLE releasing function are available by mask

option.

measurement.

output and pulse width measurement.

Internal . . . . . . 2 Timer overflow interrupts, 1 time base interrupt.

1 high speed timer overflow interrupt.

QFP 100 pins.

PDIP 42 pins.

APPLICATIONSAPPLICATIONS

APPLICATIONS

APPLICATIONSAPPLICATIONS

EM73P461A is suitable for application in family applicance, consumer products, hand held games and the toy

controller.

* This specification are subject to be changed without notice.

12.27.2001

1

Page 2

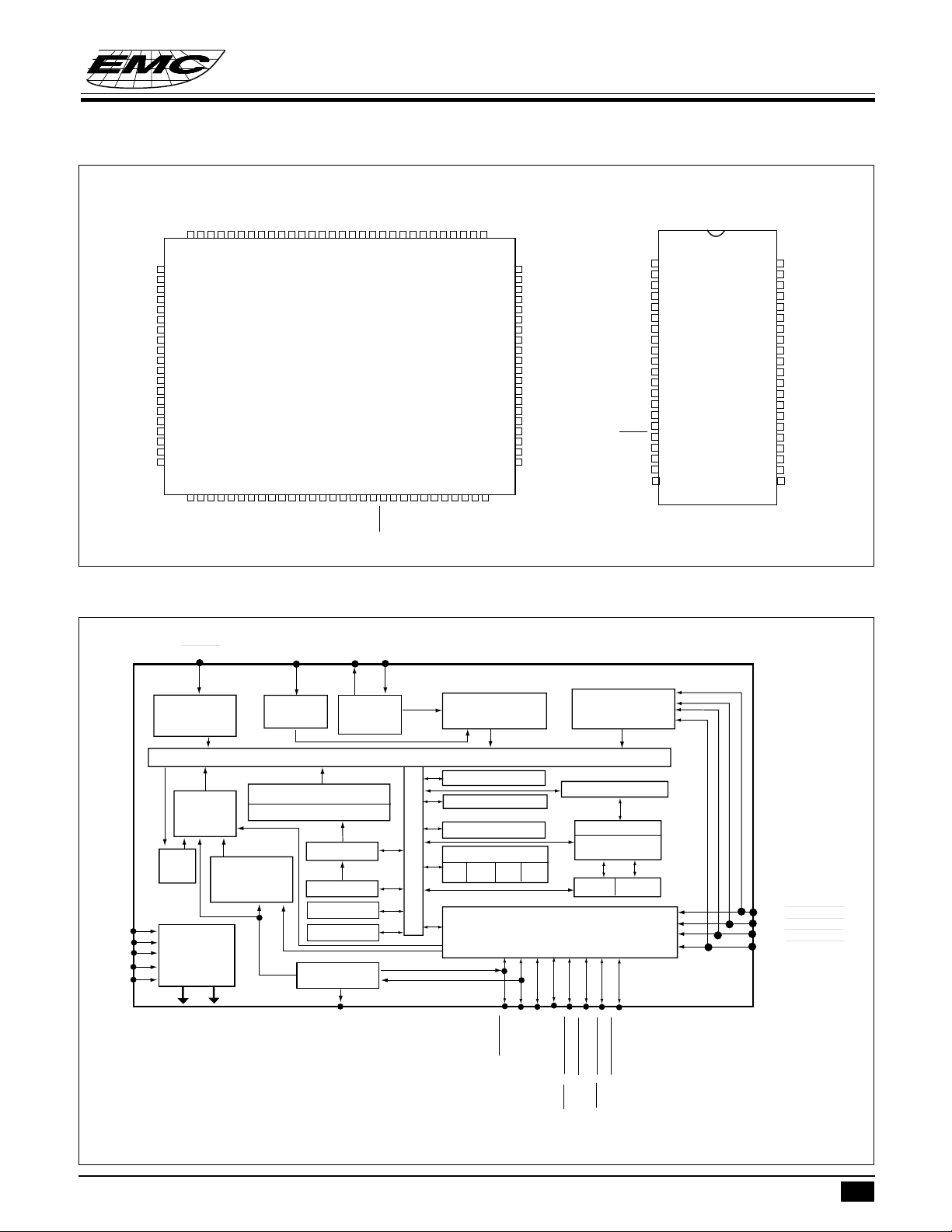

PIN ASSIGNMENTPIN ASSIGNMENT

PIN ASSIGNMENT

PIN ASSIGNMENTPIN ASSIGNMENT

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

NCNCNCNCNCNCNCNCNC

8079787776757473727170696867666564636261605958575655545352

81

NC

82

NC

83

SEG5

84

SEG4

85

SEG3

86

SEG2

87

SEG1

88

SEG0

89

COM3

90

COM2

91

COM1

92

COM0

93

VB

94

VA

95

V3

96

V2

97

V1

98

NC

99

NC

100

NC

123456789

NCNCNC

NC

VSS

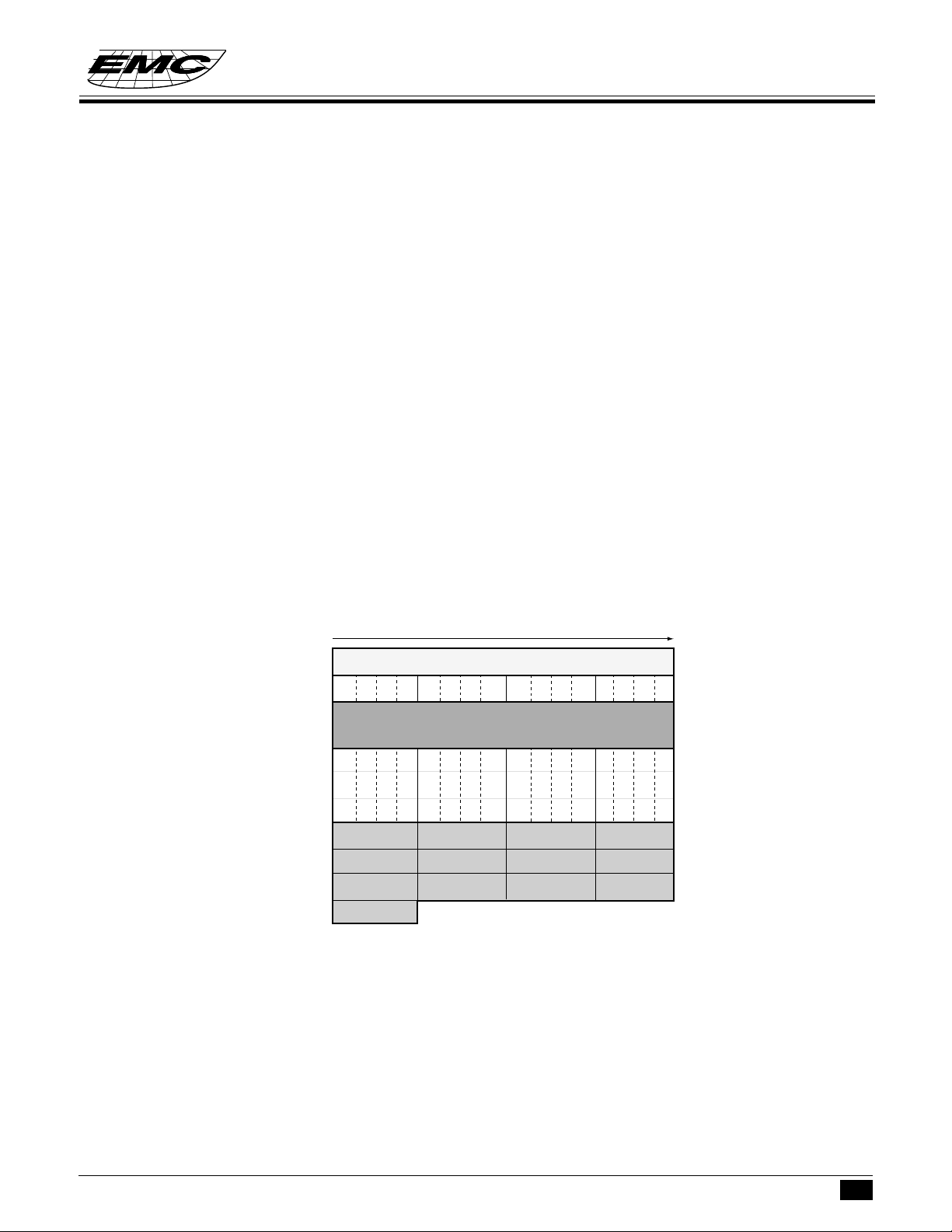

FUNCTION BLOCK DIAGRAMFUNCTION BLOCK DIAGRAM

FUNCTION BLOCK DIAGRAM

FUNCTION BLOCK DIAGRAMFUNCTION BLOCK DIAGRAM

RESET

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

EM73P461A

QFP 100

101112131415161718192021222324252627282930

NC

P4.3

P4.2

P4.1

VDD

CLK

P4.0

SOUND

LXOUT

CLK

LXIN

LXOUT

SEG12

SEG13

P8.3

SEG14

SEG15

SEG16

SEG17

NCNCNCNCNCNCNCNCNC

P8.2

P8.1

P8.0

RESET

LXIN

SEG18

SEG19

SEG20

SEG21NCNCNCNC

NC

51

50

NC

49

NC

48

NC

47

SEG22

46

SEG23

45

SEG24

44

SEG25

43

SEG26

42

SEG27

41

SEG28

40

SEG29

39

SEG30

38

SEG31

37

P0.0

36

P0.1

35

P0.2

34

P0.3

33

VPP

32

NC

31

NC

NC

LXOUT

VSS

CLK

LXIN

VDD

P4.3

P4.2

P4.1

P4.0

P8.3

P8.2

P8.1

P8.0

RESET

VPP

P0.3

P0.2

P0.1

1

V3

2

V2

3

V1

4

5

6

7

8

9

10

EM73P461A

11

PDIP42

12

13

14

15

16

17

18

19

20

21

VA

42

VB

41

COM0

40

COM1

39

COM2

38

COM3

37

SEG14

36

SEG15

35

SEG16

34

SEG17

33

SEG18

32

SEG19

31

SEG20

30

SEG21

29

SEG22

28

SEG23

27

SEG24

26

SEG25

25

SEG26

24

SEG27

23

P0.0

22

VA

VB

V1

V2

V3

Reset

Control

Interrupt

Control

Time

Base

LCD

COM0~COM3

Generator

Instruction Decoder

Instruction Register

Timer/Counter

(TA,TB)

SEG0~SEG31

Clock

ROM

PC

DP

SP

HTC

SOUND

Clock

Generator

(slow)

System Control

Data Bus

Timing

Generator

Data pointer

ACC

ALU

Flag

ZCS G

I/O Control

P4.2

P4.1TRGH

P4.0/SOUND

Sleep Mode

Control

Stack pointer

Stack

ROM

HR

LR

P4.3

P8.2(INT0)/WAKEUPC

P8.0(INT1)/WAKEUPA

P8.1(TRGB)/WAKEUPB

P8.3(TRGA)/WAKEUPD

P0.0/WAKEUP0

P0.1/WAKEUP1

P0.2/WAKEUP2

P0.3/WAKEUP3

* This specification are subject to be changed without notice.

12.27.2001

2

Page 3

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

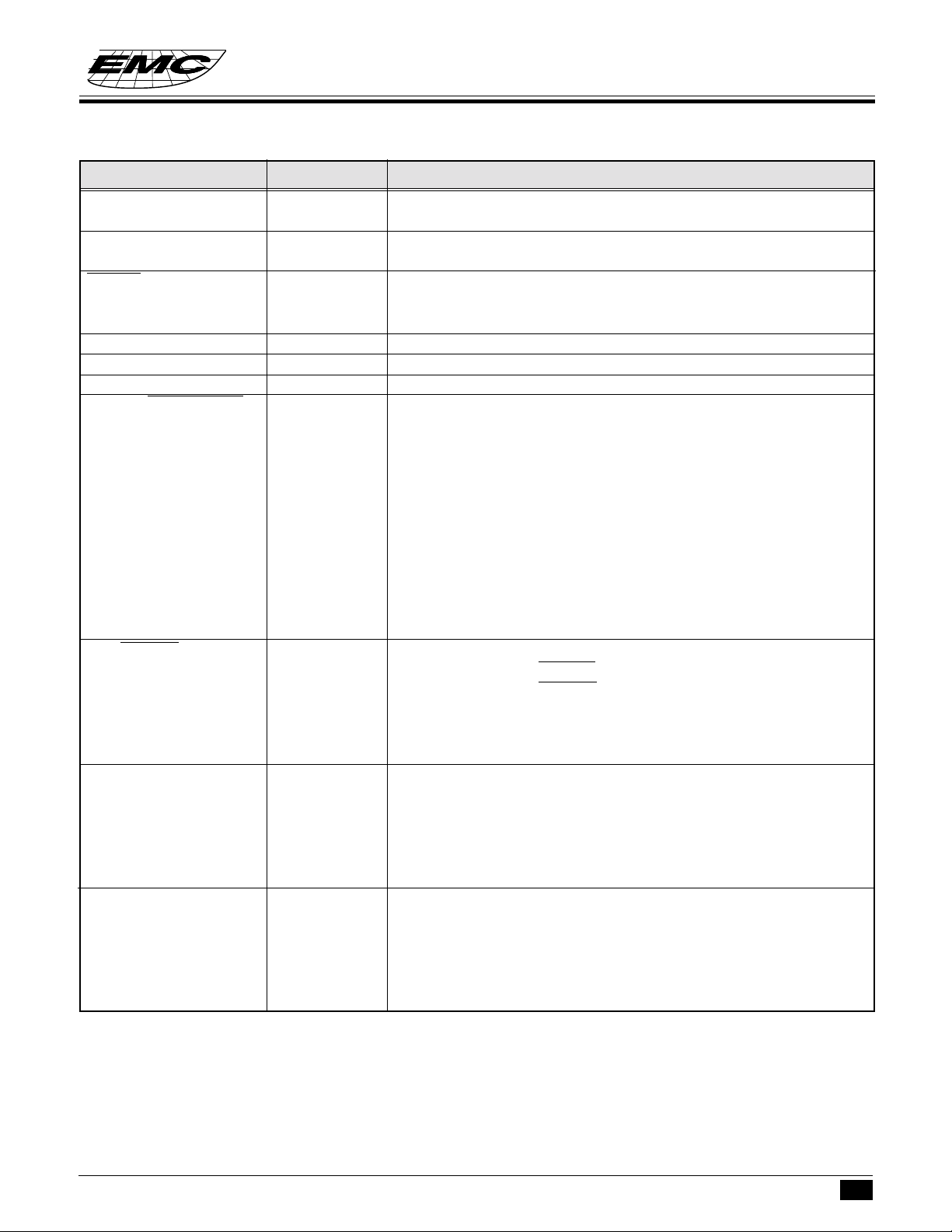

PIN DESCRIPTIONSPIN DESCRIPTIONS

PIN DESCRIPTIONS

PIN DESCRIPTIONSPIN DESCRIPTIONS

SymbolSymbol

Symbol

SymbolSymbol

V

DD

V

SS

RESET RESET-A System reset input signal, low active

CLK OSC-I RC clock source connecting pin

LXIN OSC-B/OSC-H1Crystal/RC connecting pin for low speed clock source

LXOUT OSC-B Crystal connecting pin for low speed clock source

P0(0..3)/WAKEUP0..3 INPUT-K 4-bit input port with IDLE releasing function

P4.0/SOUND I/O-R 1-bit bidirection I/O port or inverse sound effect output

P4.1/TRGH I/O-Q 1-bit bidirection I/O port with HTC external input

P4(2,3) I/O-Q 2-bit bidirection I/O port with high current source

Pin-typePin-type

Pin-type

Pin-typePin-type

PreliminaryPreliminary

FunctionFunction

Function

FunctionFunction

Power supply (+)

Power supply (+) for programming OTP

Power supply (-)

Power supply (-) for programming OTP

Reset input signal for programming OTP

Always internal pull-up

P0.0/ACLK : address counter clock for programming OTP

P0.1/PGMB : program data to OTP cells for programming OTP

P0.2/OEB : data output enable for programming OTP

P0.3/DCLK : data in/out clock signal for programming OTP

mask option : wakeup enable, negative edge release, pull-up

wakeup enable, negative edge release, none

wakeup enable, positive edge release, pull-down

wakeup enable, positive edge release, none

wakeup disable, pull-up

wakeup disable, pull-down

wakeup disable, none

mask option : SOUND enable, high current push-pull

SOUND disable, open-drain

SOUND disable, low current push-pull

SOUND disable, normal current push-pull

SOUND disable, high current push-pull

mask option : NMOS open-drain

PMOS open-drain

low current push-pull

normal current push-pull

high current push-pull

mask option : NMOS open-drain

PMOS open-drain

low current push-pull

normal current push-pull

high current push-pull

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

* This specification are subject to be changed without notice.

12.27.2001

3

Page 4

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

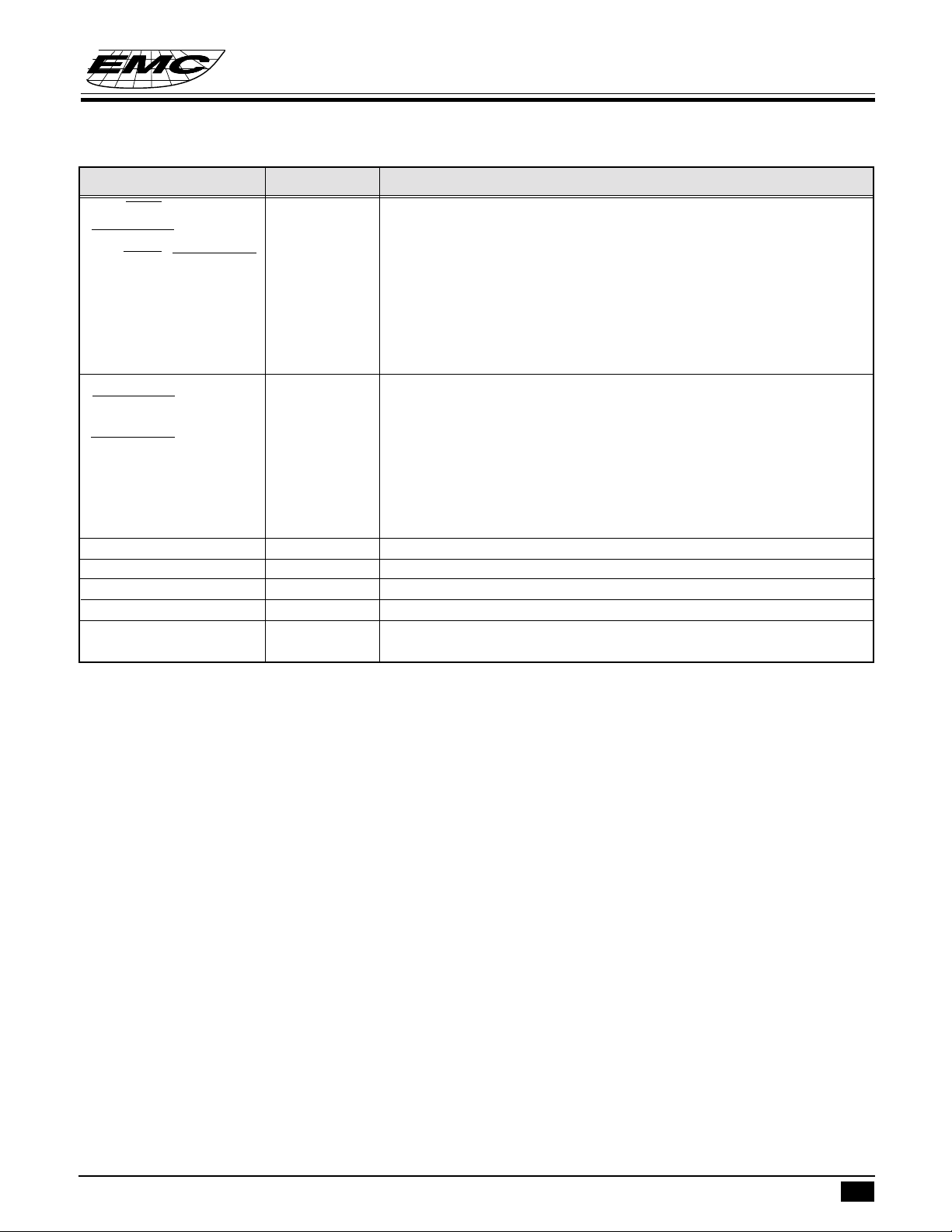

PIN DESCRIPTIONSPIN DESCRIPTIONS

PIN DESCRIPTIONS

PIN DESCRIPTIONSPIN DESCRIPTIONS

SymbolSymbol

Symbol

SymbolSymbol

P8.0(INT1) I/O-S 2-bit bidirection I/O port with external interrupt source input and IDLE

/WAKEUPA/DIN, releasing function

P8.2(INT0)/WAKEUPC P8.0/DIN : data input for programming OTP

P8.1(TRGB) I/O-S 2-bit bidirection I/O port with time/counter A,B external input and IDLE

/WAKEUPB/DOUT, releasing function

P8.3(TRGA) P8.1/DOUT : data output for programming OTP

/WAKEUPD mask option : wakeup enable, low current push-pull

SOUND Melody output

VA,VB, V1, V2, V3 Connect the capacitors for LCD bias voltage

COM0~COM3 LCD common output pins

SEG0~SEG31 LCD segment output pins

TEST/VPP Test pin must be floating

Pin-type Pin-type

Pin-type

Pin-type Pin-type

FunctionFunction

Function

FunctionFunction

mask option : wakeup enable, low current push-pull

wakeup enable, normal current push-pull

wakeup disable, open-drain

wakeup disable, low current push-pull

wakeup disable, normal current push-pull

wakeup enable, normal current push-pull

wakeup disable, open-drain

wakeup disable, low current push-pull

wakeup disable, normal current push-pull

VPP : high vlotage (12V) power source for programming OTP

FUNCTION DESCRIPTIONSFUNCTION DESCRIPTIONS

FUNCTION DESCRIPTIONS

FUNCTION DESCRIPTIONSFUNCTION DESCRIPTIONS

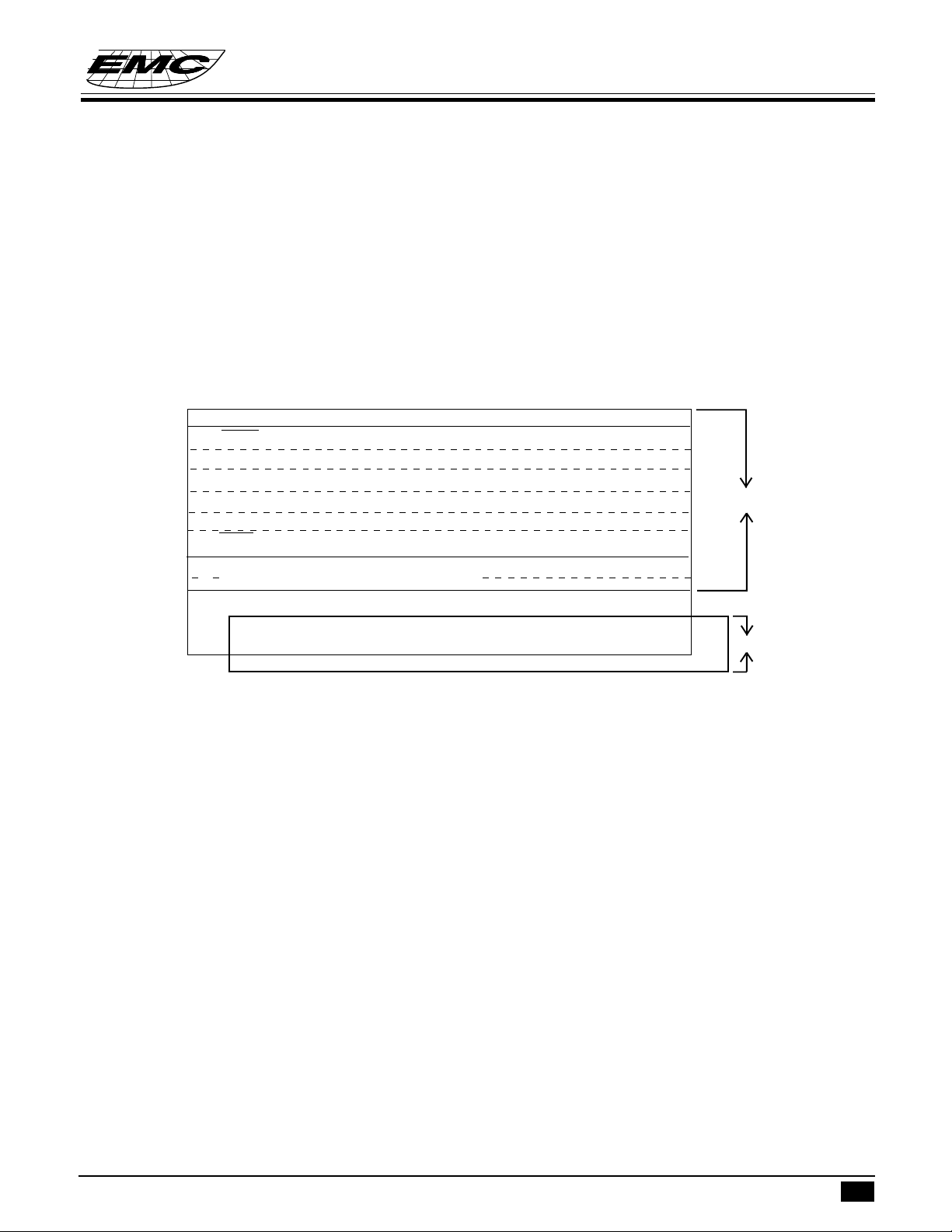

PROGRAM ROM (4K X 8 bits)PROGRAM ROM (4K X 8 bits)

PROGRAM ROM (4K X 8 bits)

PROGRAM ROM (4K X 8 bits)PROGRAM ROM (4K X 8 bits)

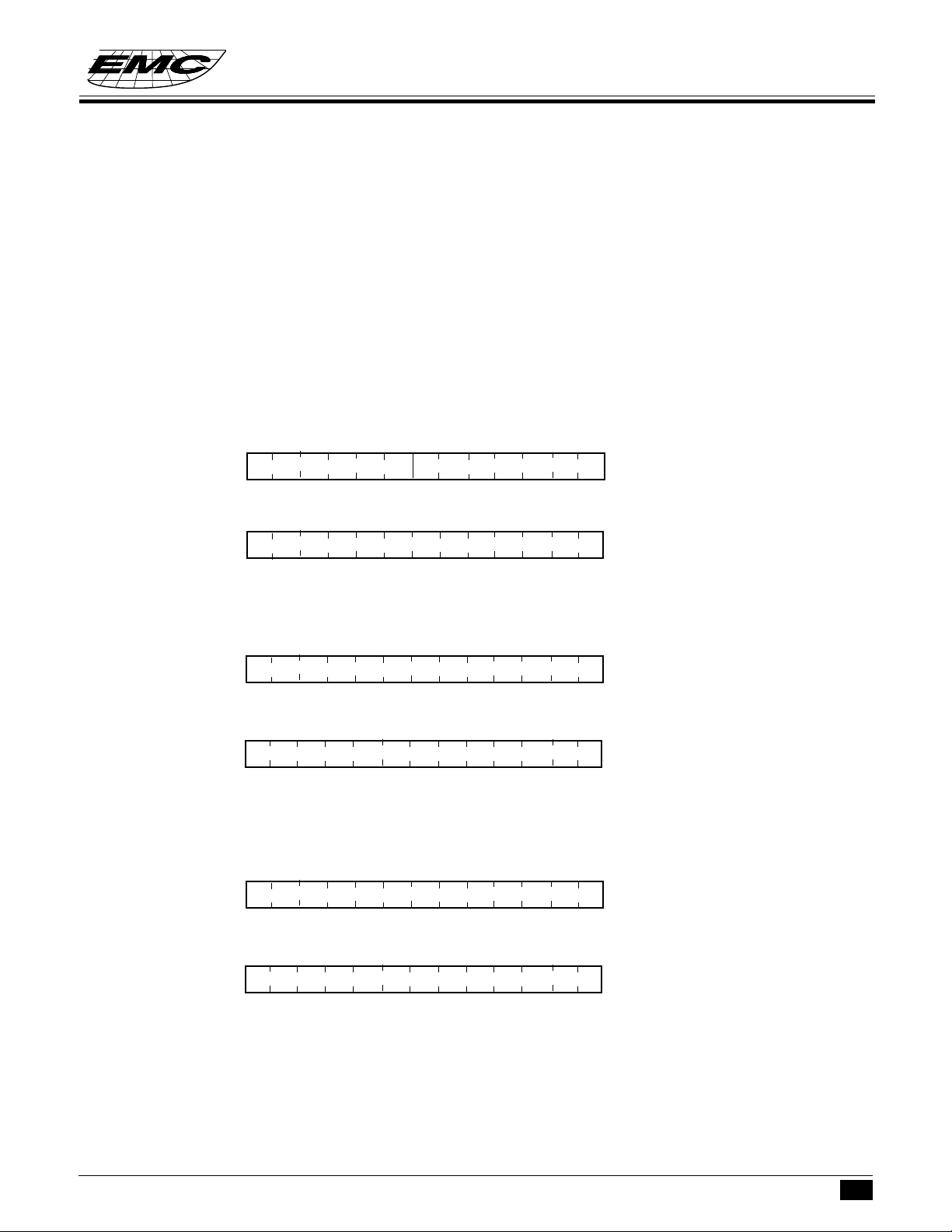

4 K x 8 bits program ROM contains user's program and some fixed data.

The basic structure of program ROM can be divided into 5 parts.

1. Address 000h: Reset start address.

2. Address 002h - 00Ch : 6 kinds of interrupt service routine entry addresses.

3. Address 00Eh-086h : SCALL subroutine entry address, only available at 00Eh,016h,01Eh,026h, 02Eh,

036h, 03Eh, 046h, 04Eh, 056h, 05Eh, 066h, 06Eh, 076h, 07Eh, 086h.

4. Address 000h - 7FFh : LCALL subroutine entry address.

5. Address 000h - FFFh : Except used as above function, the other region can be used as user's program region.

* This specification are subject to be changed without notice.

12.27.2001

4

Page 5

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

address 4096 x 8 bits

PreliminaryPreliminary

000h Reset start address

002h INT0; External interrupt service routine entry address

004h HTCI; High speed timer interrupt service entry address

006h TRGA; Timer/counterA interrupt service routine entry address

008h TRGB; Timer/counter B interrupt service routine entry address

00Ah TBI; Time base interrupt service routine entry address

00Ch INT1; External interrupt service routine entry address

00Eh

086h

.

.

.

SCALL, subroutine call entry address

.

.

.

FFFh

User's program and fixed data are stored in the program ROM. User's program is according the PC value

to send next executed instruction code. Fixed data can be read out by two ways.

(1) Table-look-up instruction :

Table -look-up instruction is depended on the Data Pointer (DP) to indicate to ROM address, then to get the

ROM code data.

LDAXLDAX

LDAX

LDAXLDAX

LDAXILDAXI

LDAXI

LDAXILDAXI

Acc Acc

Acc

Acc Acc

Acc Acc

Acc

Acc Acc

←←

ROM[DP] ROM[DP]

←

ROM[DP]

←←

ROM[DP] ROM[DP]

←←

ROM[DP] ROM[DP]

←

ROM[DP]

←←

ROM[DP] ROM[DP]

LL

L

LL

,DP+1,DP+1

,DP+1

,DP+1,DP+1

HH

H

HH

DP is a 12-bit data register which can store the program ROM address to be the pointer for the ROM code

data. First, user load ROM address into DP by instruction "STADPL, STADPM, STADPH", then user can

get the lower nibble of ROM code data by instruction "LDAX" and higher nibble by instruction "LDAXI".

PROGRAM EXAMPLE: Read out the ROM code of address 777h by table-look-up instruction.

LDIA #07h;

STADPL ; DP3-0 ← 07h

STADPM ; DP5-4 ← 07h

STADPH ; DP8-6 ← 07h, Load DP=0777h

:

LDL #00h;

LDH #03h;

LDAX ; ACC ← 6h

STAMI ; RAM[30] ← 6h

LDAXI ; ACC ← 5h

STAM ; RAM[31] ← 5h

:

ORG 0777h;

DATA 56h;

:

* This specification are subject to be changed without notice.

12.27.2001

5

Page 6

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PROGRAM ROM (8K X 8 bits)PROGRAM ROM (8K X 8 bits)

PROGRAM ROM (8K X 8 bits)

PROGRAM ROM (8K X 8 bits)PROGRAM ROM (8K X 8 bits)

PreliminaryPreliminary

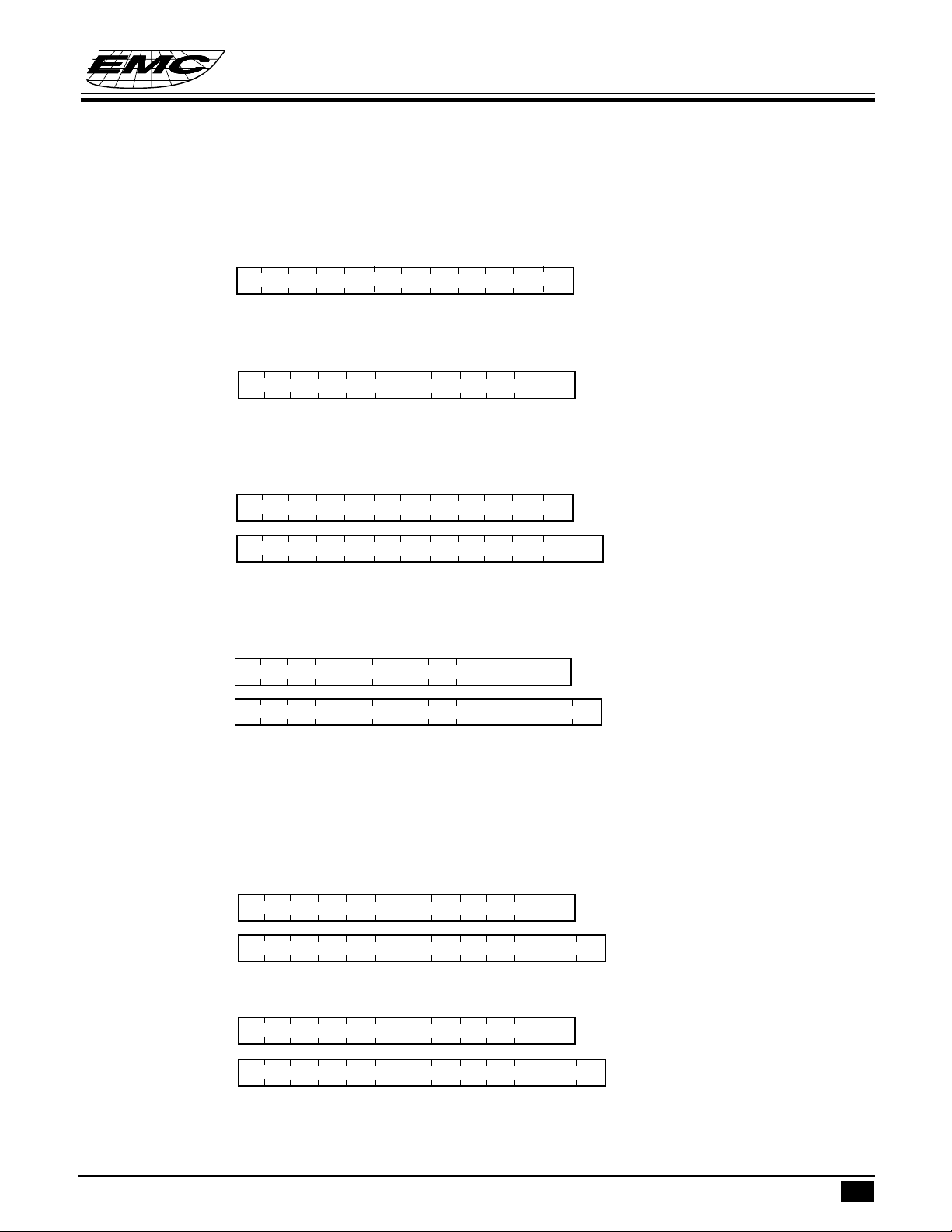

8 K x 8 bits program ROM contains user's program and some fixed data .

The basic structure of program ROM can be divided into 6 parts.

1. Address 0000h: Reset start address.

2. Address 0002h - 000Ch : 6 kinds of interrupt service routine entry addresses .

3. Address 000Eh - 0086h : SCALL subroutine entry address, only available at 000Eh, 0016h, 001Eh, 0026h, 002Eh,

0036h, 003Eh, 0046h, 004Eh, 0056h, 005Eh, 0066h, 006Eh, 0076h, 007Eh, 0086h.

4. Address 0000h - 07FFh : LCALL subroutine entry address.

5. Address 0000h - 1FFFh : Except used as above function, the other region can be used as user's program region.

6. Address 1000h - 1FFFh : Fixed data stortage area.

address 8192 x 8 bits

000h Reset start address

002h INT0; External interrupt service routine entry address

004h HTCI; High speed timer interrupt service entry address

006h TRGA; Timer/counterA interrupt service routine entry address

008h TRGB; Timer/counter B interrupt service routine entry address LCALL entry address

00Ah TBI; Time base interrupt service routine entry address

00Ch INT1; External interrupt service routine entry address

00Eh

086h

SCALL, subroutine call entry address

800h 1000h

::

FFFh Bank 1 fixed data area

1FFFh

User's program and fixed data are stored in the program ROM. User's program is according the PC value

to send next executed instruction code. Fixed data can be read out by table-look-up instruction.

Please note that fixed data only can be stored in 8K ROM Bank 1.

The program counter is a 13-bit binary counter. The PC can defined 8K ROM.

Table-look-up instruction :

Table -look-up instruction is depended on the Data Pointer (DP) to indicate to ROM address, then to get the

ROM code data.

LDAXLDAX

LDAX

LDAXLDAX

LDAXILDAXI

LDAXI

LDAXILDAXI

Acc Acc

Acc

Acc Acc

Acc Acc

Acc

Acc Acc

←←

ROM[DP] ROM[DP]

←

ROM[DP]

←←

ROM[DP] ROM[DP]

←←

ROM[DP] ROM[DP]

←

ROM[DP]

←←

ROM[DP] ROM[DP]

LL

L

LL

,DP+1,DP+1

,DP+1

,DP+1,DP+1

HH

H

HH

DP is a 13-bit data register which can store the program ROM address to be the pointer for the ROM code

data. First, user load ROM address into DP by instruction "STADPL, STADPM, STADPH", then user can

get the lower nibble of ROM code data by instruction "LDAX" and higher nibble by instruction "LDAXI".

* This specification are subject to be changed without notice.

12.27.2001

6

Page 7

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PROGRAM EXAMPLE: Read out the ROM code of address 1777h by table-look-up instruction for 8K ROM.

LDIA #07h;

STADPL ; DP3-0 ← 07h

STADPM ; DP5-4 ← 07h

STADPH ; DP8-6 ← 07h, Load DP=1777h

:

LDL #00h;

LDH #03h;

LDAX ; ACC ← 6h

STAMI ; RAM[30] ← 6h

LDAXI ; ACC ← 5h

STAM ; RAM[31] ← 5h

:

BANK 1

ORG 1777h

DATA 56h;

:

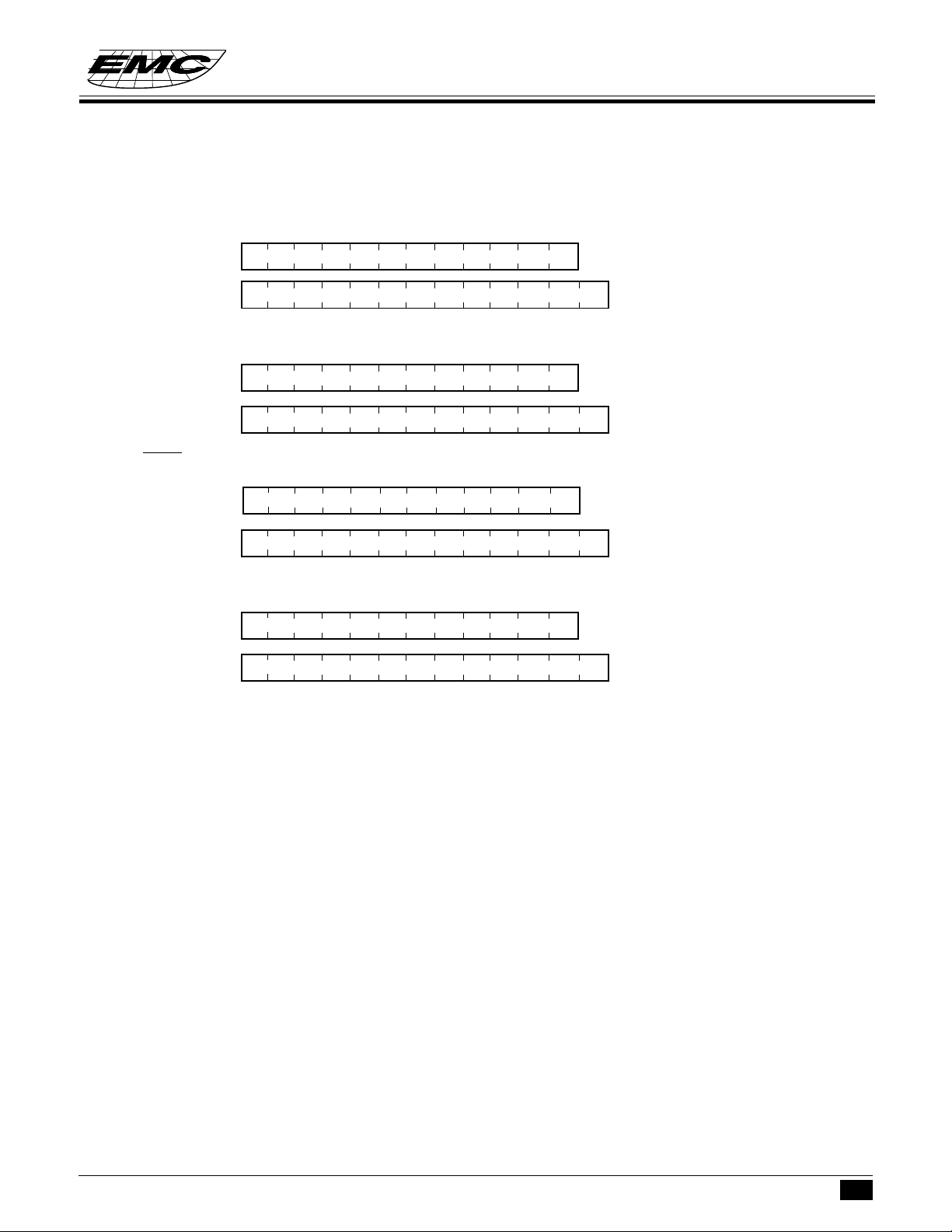

DATA RAM ( 244-nibble ) DATA RAM ( 244-nibble )

DATA RAM ( 244-nibble )

DATA RAM ( 244-nibble ) DATA RAM ( 244-nibble )

PreliminaryPreliminary

There is total 244 - nibble data RAM from address 00 to F3h

Data RAM includes 3 parts: zero page region, stacks and data area.

Increment

Address

00h~0Fh

zero page

10h~1Fh

20h~2Fh

30h~3Fh

LCD display RAM

40h~4Fh

:

B0h ~ BFh

C0h ~ CFh

D0h ~ DFh

E0h ~ EFh

F0h ~ F3h

level 0

level 4

level 8

level C

level 1

level 5

level 9

level 2

level 6

level A

level 3

level17

level B

* This specification are subject to be changed without notice.

12.27.2001

7

Page 8

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

LCD display RAM:

RAM address from 20h ~ 3Fh are the LCD display RAM area, the RAM data of this region can't be operated

by instruction LDHL xx and EXHL.

ZERO-PAGE:

From 00h to 0Fh is the location of zero-page. It is used as the pointer in zero-page addressing mode for the

instruction of "STD #k,y; ADD #k,y; CLR y,b; CMP k,y".

PROGRAM EXAMPLE: To wirte immediate data "07h" to address "03h" of RAM and to clear bit 2 of RAM.

STD #07h, 03h ; RAM[03] ← 07h

CLR 0Eh,2 ; RAM[0Eh]2 ← 0

STACK:

There are 13-level (maximum) stack for user using for subroutine (including interrupt and CALL). User can

assign any level be the starting stack by giving the level number to stack pointer (SP).

When user using any instruction of CALL or subroutine, before entry the subroutine, the previous PC address

will be saved into stack until return from those subroutines, the PC value will be restored by the data saved

in stack.

DATA AREA:

Except the special area used by user, the whole RAM can be used as data area for storing and loading general

data.

ADDRESSING MODE

(1) Indirect addressing mode:

Indirect addressing mode indicates the RAM address by specified HL register.

For example: LDAM ; Acc ← RAM[HL]

STAM ; RAM[HL] ← Acc

(2) Direct addressing mode:

Direct addressing mode indicates the RAM address by immediate data.

For example: LDA x ; Acc← RAM[x]

STA x ; RAM[x] ← Acc

(3) Zero-page addressing mode

For zero-page region, user can using direct addressing to write or do any arithematic, comparsion or bit

manupulated operation directly.

For example: STD #k,y ; RAM[y] ← #k

ADD #k,y; RAM[y] ← RAM[y] + #k

* This specification are subject to be changed without notice.

12.27.2001

8

Page 9

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

PROGRAM COUNTER (4K/8K ROM)PROGRAM COUNTER (4K/8K ROM)

PROGRAM COUNTER (4K/8K ROM)

PROGRAM COUNTER (4K/8K ROM)PROGRAM COUNTER (4K/8K ROM)

Program counter ( PC ) is composed by a 12-bit counter for 4K ROM/13-bit counter for 8K ROM which indicates

the next executed address for the instruction of program ROM.

For a 4K - byte size ROM, PC can indicate address form 000h - FFFh, for BRANCH and CALL instrcutions,

PC is changed by instruction indicating.

For a 8K - byte size ROM, PC can indicate address form 0000h - 1FFFh, for BRANCH and CALL instrcutions,

PC is changed by instruction indicating.

(1) Branch instruction:(1) Branch instruction:

(1) Branch instruction:

(1) Branch instruction:(1) Branch instruction:

SBR aSBR a

SBR a

SBR aSBR a

Object code: 00aa aaaa

Condition: SF=1; PC ← PC

PC Hold original PC value+1 aaaaaa (for 4K/8K ROM)

SF=0; PC ← PC +1( branch condition not satisified )

( branch condition satisified )

11-6.a

PC Original PC value + 1

LBR aLBR a

LBR a

LBR aLBR a

Object code: 1100 aaaa aaaa aaaa

Condition: SF=1; PC ← a ( branch condition satisified )

PC aaaaaaaaaaa a (for 4K/8K ROM)

SF=0 ; PC ← PC + 2 ( branch condition not satisified )

PC Original PC value + 2

SLBR aSLBR a

SLBR a

SLBR aSLBR a

Object code: 0101 0101 1100 aaaa aaaa aaaa (a : 1000 ~ 1FFFh)

0101 0111 1100 aaaa aaaa aaaa (a : 0000 ~ 0FFFh)

Condition: SF=1; PC ← a ( branch condition satisified )

PC aaaaaaaaaaa a (only for 8K ROM)

SF=0 ; PC ← PC + 2 ( branch condition not satisified )

PC Original PC value + 2

* This specification are subject to be changed without notice.

12.27.2001

9

Page 10

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

(2) Subroutine instruction:(2) Subroutine instruction:

(2) Subroutine instruction:

(2) Subroutine instruction:(2) Subroutine instruction:

SCALL aSCALL a

SCALL a

SCALL aSCALL a

Object code: 1110 nnnn

Condition : PC ← a ; a=8n+6 ; n=1..15 ; a=86h, n=0

PC0000aaaaaaaa

LCALL aLCALL a

LCALL a

LCALL aLCALL a

Object code: 0100 0 aaa aaaa aaaa

Condition: PC ← a

PC0aaaaaaaaaaa

RETRET

RET

RETRET

Object code: 0100 1111

Condition: PC ← STACK[SP]; SP + 1

P C The return address stored in stack (for 4K ROM)

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

P C The return address stored in stack (for 8K ROM)

RT IRT I

RT I

RT IRT I

Object code: 0100 1101

Condition : FLAG. PC ← STACK[SP]; EI ← 1; SP + 1

P C The return address stored in stack (for 4K ROM)

P C The return address stored in stack (for 8K ROM)

(3) Interrupt acceptance operation:(3) Interrupt acceptance operation:

(3) Interrupt acceptance operation:

(3) Interrupt acceptance operation:(3) Interrupt acceptance operation:

When an interrupt is accepted, the original PC is pushed into stack and interrupt vector will be loaded into

PC,The interrupt vectors are as following:

INT0INT0

INT0 (External interrupt from P8.2)

INT0INT0

PC000000000010 (for 4K ROM)

PC000000000001 0 (for 8K ROM)

TRGATRGA

TRGA (Timer A overflow interrupt)

TRGATRGA

PC000000000110 (for 4K ROM)

PC000000000011 0 (for 8K ROM)

* This specification are subject to be changed without notice.

12.27.2001

10

Page 11

TRGBTRGB

TRGB (Time B overflow interrupt)

TRGBTRGB

PC000000001000 (for 4K ROM)

PC000000000100 0 (for 8K ROM)

TBITBI

TBI (Time base interrupt)

TBITBI

PC000000001010 (for 4K ROM)

PC000000000101 0 (for 8K ROM)

INT1INT1

INT1 (External interrupt from P8.0)

INT1INT1

PC000000001100 (for 4K ROM)

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

PC000000000110 0 (for 8K ROM)

(4) Reset operation:(4) Reset operation:

(4) Reset operation:

(4) Reset operation:(4) Reset operation:

PC000000000000 (for 4K ROM)

PC000000000000 0 (for 8K ROM)

(5) Other operations:(5) Other operations:

(5) Other operations:

(5) Other operations:(5) Other operations:

For 1-byte instruction execution: PC + 1

For 2-byte instruction execution: PC + 2

ACCUMULATORACCUMULATOR

ACCUMULATOR

ACCUMULATORACCUMULATOR

Accumulator is a 4-bit data register for temporary data. For the arithematic, logic and comparative opertion

.., ACC plays a role which holds the source data and result.

FLAGSFLAGS

FLAGS

FLAGSFLAGS

There are four kinds of flag, CF ( Carry flag ), ZF ( Zero flag ), SF ( Status flag ) and GF ( General flag ),

these 4 1-bit flags are affected by the arithematic, logic and comparative .... operation.

All flags will be put into stack when an interrupt subroutine is served, and the flags will be restored after

RTI instruction executed.

* This specification are subject to be changed without notice.

12.27.2001

11

Page 12

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

(1) Carry Flag ( CF )

The carry flag is affected by following operation:

a. Addition : CF as a carry out indicator, when the addition operation has a carry-out, CF will be "1",

in another word, if the operation has no carry-out, CF will be "0".

b. Subtraction : CF as a borrow-in indicator, when the subtraction operation must has a borrow, in the CF

will be "0", in another word, if no borrow-in, CF will be "1".

c. Comparision: CF is as a borrow-in indicator for Comparision operation as the same as subtraction

operation.

d. Rotation: CF shifts into the empty bit of accumulator for the rotation and holds the shift out data after

rotation.

e. CF test instruction : For TFCFC instruction, the content of CF sends into SF then clear itself "0".

For TTSFC instruction, the content of CF sends into SF then set itself "1".

(2) Zero Flag ( ZF )

ZF is affected by the result of ALU, if the ALU operation generate a "0" result, the ZF will be "1",

otherwise, the ZF will be "0".

(3) Status Flag ( SF )

The SF is affected by instruction operation and system status.

a. SF is initiated to "1" for reset condition.

b. Branch instruction is decided by SF, when SF=1, branch condition will be satisified, otherwise,

branch condition will not be satisified by SF = 0.

@(4) General Flag ( GF )

GF is a one bit general purpose register which can be set, clear, test by instruction SGF, CGF and TGS.

PROGRAM EXAMPLE:

Check following arithematic operation for CF, ZF, SF

@ : just for 4K ROM.

* This specification are subject to be changed without notice.

12.27.2001

12

Page 13

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

CF ZF SF

LDIA #00h; - 1 1

LDIA #03h; - 0 1

ADDA #05h; - 0 1

ADDA #0Dh; - 0 0

ADDA #0Eh; - 0 0

ALUALU

ALU

ALUALU

The arithematic operation of 4 - bit data is performed in ALU unit. There are 2 flags can be affected by the

result of ALU operation, ZF and SF. The operation of ALU can be affected by CF only.

ALU STRUCTUREALU STRUCTURE

ALU STRUCTURE

ALU STRUCTUREALU STRUCTURE

ALU supported user arithematic operation function, including : addition, subtraction and rotaion.

DATA BUS

ALU

ZF CF SF GF

ALU FUNCTIONALU FUNCTION

ALU FUNCTION

ALU FUNCTIONALU FUNCTION

(1) Addition:

For instruction ADDAM, ADCAM, ADDM #k, ADD #k,y .... ALU supports addition function.

The addition operation can affect CF and ZF. For addition operation, if the result is "0", ZF will be "1",

otherwise, not equal "0", ZF will be "0". When the addition operation has a carry-out, CF will be "1",

otherwise, CF will be "0".

EXAMPLE:

Operation Carry Zero

3+4=7 0 0

7+F=6 1 0

0+0=0 0 1

8+8=0 1 1

(2) Subtraction:

For instruction SUBM #k, SUBA #k, SBCAM, DECM... ALU supports user subtraction function. The

subtraction operation can affect CF and ZF, For subtraction operation, if the result is negative, CF will

be "0", it means a borrow out, otherwise, if the result is positive, CF will be "1". For ZF, if the result of

subtraction operation is "0", the ZF will be "1", otherwise, ZF will be "1".

* This specification are subject to be changed without notice.

12.27.2001

13

Page 14

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

EXAMPLE:

Operation Carry Zero

8-4=4 1 0

7-F= -8(1000) 0 0

9-9=0 1 1

(3) Rotation:

There are two kinds of rotation operation, one is rotation left, the other is rotation right.

RLCA instruction rotates Acc value to left, shift the CF value into the LSB bit of Acc and the shift out data

will be hold in CF.

MSB LSB

ACC

CF

RRCA instruction operation rotates Acc value to right, shift the CF value into the MSB bit of Acc and the

shift out data will be hold in CF.

MSB LSB

ACC

CF

PROGRAM EXAMPLE: To rotate Acc right and shift a "1" into the MSB bit of Acc.

TTCFS; CF ← 1

RRCA; rotate Acc right and shift CF=1 into MSB.

HL REGISTERHL REGISTER

HL REGISTER

HL REGISTERHL REGISTER

HL register are two 4-bit registers, they are used as a pair of pointer for the address of RAM memory and also

2 independent temporary 4-bit data registers. For some instruction, L register can be a pointer to indicate the

pin number ( Port4 ).

HL REGISTER STRUCTUREHL REGISTER STRUCTURE

HL REGISTER STRUCTURE

HL REGISTER STRUCTUREHL REGISTER STRUCTURE

3 2 1 0

3 2 1 0

H REGISTER

HL REGISTER FUNCTIONHL REGISTER FUNCTION

HL REGISTER FUNCTION

HL REGISTER FUNCTIONHL REGISTER FUNCTION

* This specification are subject to be changed without notice.

L REGISTER

12.27.2001

14

Page 15

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

(1)For instruction : LDL #k, LDH #k, THA, THL, INCL, DECL, EXAL, EXAH, HL register used as a

temporary register.

PROGRAM EXAMPLE: Load immediate data "5h" into L register, "Dh" into H register.

LDL #05h;

LDH #0Dh;

(2) For instruction LDAM, STAM, STAMI .., HL register used as a pointer for the address of RAM memory.

PROGRAM EXAMPLE: Store immediate data #Ah into RAM of address 35h.

LDL #5h;

LDH #3h;

STDMI #0Ah; RAM[35] ← Ah

(3) For instruction : SELP, CLPL, TFPL, L regieter be a pointer to indicate the bit of I/O port.

When LR = 0 indicate P4.0

PROGRAM EXAMPLE: To set bit 0 of Port4 to "1"

LDL #00h;

SEPL ; P4.0 ← 1

STACK POINTER (SP)STACK POINTER (SP)

STACK POINTER (SP)

STACK POINTER (SP)STACK POINTER (SP)

Stack pointer is a 4-bit register which stores the present stack level number.

Before using stack, user must set the SP value first, CPU will not initiate the SP value after reset condition

. When a new subroutine is accepted, the SP will be decreased one automatically, in another word, if

returning from a subroutine, the SP will be increased one.

The data transfer between ACC and SP is by instruction of "LDASP" and "STASP".

DATA POINTER (DP)DATA POINTER (DP)

DATA POINTER (DP)

DATA POINTER (DP)DATA POINTER (DP)

Data pointer is a 12-bit register which stores the address of ROM can indicate the ROM code data

specified by user (refer to data ROM).

CLOCK AND TIMING GENERATORCLOCK AND TIMING GENERATOR

CLOCK AND TIMING GENERATOR

CLOCK AND TIMING GENERATORCLOCK AND TIMING GENERATOR

The clock generator is supported by a single clock system, the clock source comes from crystal (resonator)

or RC oscillation is decided by mask option, the working frequency range is 480 K Hz to 4 MHz depending

on the working voltage.

CLOCK GENERATOR STRUCTURECLOCK GENERATOR STRUCTURE

CLOCK GENERATOR STRUCTURE

CLOCK GENERATOR STRUCTURECLOCK GENERATOR STRUCTURE

There are two clock generator for system clock control. P14 is the status register for the CPU status. P16,

P19 and P22 are the system clock mode control ports.

* This specification are subject to be changed without notice.

12.27.2001

15

Page 16

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

CLK

LXIN

LXOUT

SYSTEM CLOCK MODE CONTROLSYSTEM CLOCK MODE CONTROL

SYSTEM CLOCK MODE CONTROL

SYSTEM CLOCK MODE CONTROLSYSTEM CLOCK MODE CONTROL

The system clock mode controller can start or stop the high-frequency and low-frequency clock oscillator

and switch between the basic clocks. EM73P461A has four operation modes (NORMAL, SLOW,IDLE

and STOP operation modes).

High-frequency

generator

Low-frequency

generator

Mask option for choose Crystal or RC oscillator

Crystal connection

operation

fc

fs

LXIN

LXOUT

STOP

mode

System clock

mode control

System control

RC connection

High osc : stopped

Low osc : stopped

P14

P16

P19

P22

LXIN

Command

(P16)

NORMAL

operation

mode

System ClockSystem Clock

System Clock

System ClockSystem Clock

High osc : oscillating

Low osc : oscillating

Command

(P22)

Reset

IDLE

(CPU

stops)

High osc : stopped

Low osc : oscillating

Command

(P22)

Command

Command

(P16)

SLOW

operation

(P19)

I/O or internal timer wakeup

Available functionAvailable function

Available function

Available functionAvailable function

mode

High osc : stopped

Low osc : oscillating

One instruction cycleOne instruction cycle

One instruction cycle

One instruction cycleOne instruction cycle

Operation ModeOperation Mode

Operation Mode

Operation ModeOperation Mode

RESET

operation

Reset

Reset

OscillatorOscillator

Oscillator

OscillatorOscillator

I/O wakeup

Reset

Reset release

NORMAL High, Low frequency High frequency clock LCD, High speed timer 8/fc

SLOW Low frequency Low frequency clock LCD, High speed timer 4/fs or 8/fs by mask option

IDLE Low frequency CPU stops LCD STOP None CPU stops All disable -

* This specification are subject to be changed without notice.

12.27.2001

16

Page 17

NORMAL OPERATION MODENORMAL OPERATION MODE

NORMAL OPERATION MODE

NORMAL OPERATION MODENORMAL OPERATION MODE

The 4-bit µc is in the NORMAL operation mode when the CPU is reseted. This mode is a dual clock system

(high-frequency(fc) and low-frequency(fs) clocks oscillating). It can be changed to SLOW or STOP

operation mode by the command register (P22 or P16).

The instruction cycle is 8/fc in NORMAL operation mode.

LCD display and high speed timer/counter with melody output are available for the NORMAL operation

mode.

SLOW OPERATION MODESLOW OPERATION MODE

SLOW OPERATION MODE

SLOW OPERATION MODESLOW OPERATION MODE

The SLOW operation mode is a single clock system (low-frequency(fs) clock oscillating). It can be changed

to the DUAL operation mode with the commoand register (P22), STOP operation mode with P16 and IDLE

operation mode with P19.

The instruction cycle is 4/fs or 8/fs by frequency double mask option in SLOW operation mode.

LCD display and high speed timer/counter with melody output are available for the SLOW operation mode.

32 1 0 Initial value : 0000

P22

* SOM * *

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

SOM Select operation mode

0 NORMAL operation mode

1 SLOW operation mode

P14 32 10 Initial value : *000

* WKS LFS CPUS

LFS Low-frequency status CPUS CPU status

0 LXIN source is not stable 0 NORMAL operation mode

1 LXIN source is stable 1 SLOW operation mode

WKS Wakeup status

0 Wakeup not by internal timer

1 Wakeup by internal timer

Port14 is the status register for CPU. P14.0 (CPU status) and P14.1 (Low-frequency status) are read-only

bits. p14.2 (wakeup status) will be set to "1" when CPU is wake-up by internal timer. P14.2 will be cleared

to "0" when user out data to P14.

IDLE OPERATION MODEIDLE OPERATION MODE

IDLE OPERATION MODE

IDLE OPERATION MODEIDLE OPERATION MODE

The IDLE operation mode suspends all SLOW operations except for the low-frequency clock and LCD

driver. It retains the internal status with low power consumption without stopping the clock function and

LCD display.

LCD display is available for the IDLE operation mode. Sound generator is disabled in this mode. The IDLE

operation mode will be wakeup and return to the SLOW operation mode by the internal timing generator or

I/O pins (P0(0..3)/WAKEUP 0..3 or P8(0..3)/WAKEUPA..D).

* This specification are subject to be changed without notice.

12.27.2001

17

Page 18

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

P19 32 10 Initial value : 0000

IDME SIDR

IDME Enable IDLE mode SIDR Select IDLE releasing condition

0 1 Enable IDLE mode 0 0 P0(0..3), P8(0..3) pin input

* * Reserved 0 1 P0(0..3), P8(0..3) pin input and 1 sec signal

1 0 P0(0..3), P8(0..3) pin input and 0.5 sec signal

1 1 P0(0..3), P8(0..3) pin input and 15.625 ms signal

STOP OPERATION MODESTOP OPERATION MODE

STOP OPERATION MODE

STOP OPERATION MODESTOP OPERATION MODE

The STOP operation mode suspends system operation and holds the internal status immediately before the

suspension with low power consumption. This mode will be released by reset or I/O pins (P0(0..3)/

WAKEUP 0..3 or P8(0..3)/WAKEUP A..D).

LCD display and high speed timer/counter with melody output are disabled in the mode.

P16 3210 Initial value : 0000

SPME SWWT

SPME Enable STOP mode SWWT Set wake-up warm-up time

0 1 Enable STOP mode 0 0 wait normal frequency ready (26/fc)

* * Reserved 0 1 wait slow frequency ready (2

14/

fs)

1 0 Reserved

1 1 Reserved

TIME BASE INTERRUPT ( TBI )TIME BASE INTERRUPT ( TBI )

TIME BASE INTERRUPT ( TBI )

TIME BASE INTERRUPT ( TBI )TIME BASE INTERRUPT ( TBI )

The time base can be used to generate a fixed frequency interrupt. There are 8 kinds of frequencies can be

selected by setting P25.

P25 3 2 1 0

initial value : 0000

P25 NORMAL operation mode SLOW operation mode

0 0 x x Interrupt disable Interrupt disable

0 1 0 0 Interrupt frequency LXIN / 2

3

Hz Reserved

0 1 0 1 Interrupt frequency LXIN / 24 Hz Reserved

0 1 1 0 Interrupt frequency LXIN / 25 Hz Reserved

0 1 1 1 Interrupt frequency LXIN / 2

14

Hz Interrupt frequency LXIN / 2

14

Hz

1 1 0 0 Interrupt frequency LXIN / 21 Hz Reserved

1 1 0 1 Interrupt frequency LXIN / 26 Hz Interrupt frequency LXIN / 26 Hz

1 1 1 0 Interrupt frequency LXIN / 28 Hz Interrupt frequency LXIN / 28 Hz

1 1 1 1 Interrupt frequency LXIN / 2

10

Hz Interrupt frequency LXIN / 2

10

Hz

1 0 x x Reserved Reserved

TIMER / COUNTER ( TIMERA, TIMERB )TIMER / COUNTER ( TIMERA, TIMERB )

TIMER / COUNTER ( TIMERA, TIMERB )

TIMER / COUNTER ( TIMERA, TIMERB )TIMER / COUNTER ( TIMERA, TIMERB )

Timer/counters can support user three special functions:

1. Even counter

2. Timer.

3. Pulse-width measurement.

* This specification are subject to be changed without notice.

12.27.2001

18

Page 19

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

These three functions can be executed by 2 timer/counter independently.

For timerA, the counter data is saved in timer register TAH, TAM, TAL, which user can set counter initial

value and read the counter value by instruction "LDATAH(M,L), STATAH(M,L)" and timer register is

TBH, TBM, TBL and W/R instruction "LDATBH (M,L), STATBH (M,L)".

The basic structure of timer/counter is composed by two same structure counter, these two counters can be

set initial value and send counter value to timer register, P28 and P29 are the command ports for timerA

and timer B, user can choose different operation mode and different internal clock rate by setting these two

ports. When timer/counter overflow, it will generate a TRGA(B) interrupt request to interrupt control unit.

INTERRUPT CONTROL

TRGA request

12 BIT COUNTER

P8.3/

TRGA

internal clock

TIMER/COUNTER CONTROLTIMER/COUNTER CONTROL

TIMER/COUNTER CONTROL

TIMER/COUNTER CONTROLTIMER/COUNTER CONTROL

EVENT COUNTER CONTROL

TIMER CONTROL

PULSE-WIDTH MEASUREMENT

P28

CONTROL

TMSA

DATA BUS

IPSA

P29

TRGB request

12 BIT COUNTER

EVENT COUNTER CONTROL

TIMER CONTROL

PULSE-WIDTH MEASUREMENT

CONTROL

TMSB IPSB

P8.1/

TRGB

MUX

internal clock

high speed timer/counter

P8.1/TRGB, P8.3/TRGA are the external timer inputs for timerB and timerA, they are used in event

counter and pulse-width measurement mode.

Timer/counter command port: P28 is the command port for timer/counterA and P29 is for the timer/

counterB.

Port 28

3 2 1 0

TMSA IPSA

Initial state: 0000

TIMER/COUNTER MODE SELECTION

TMSA (B) Function description

0 0 Stop

0 1 Event counter mode

Port 29

3 2 1 0

TMSB

Initial state: 0000

IPSB

1 0 Timer mode

1 1 Pulse width measurement mode

INTERNAL PULSE-RATE SELECTION INTERNAL PULSE-RATE SELECTION

IPSA NORMAL mode SLOW mode IPSB NORMAL mode SLOW mode

3

0 0 LXIN/2

Hz Reserved 0 0 Depend on high speed timer/counter

0 1 LXIN/27 Hz LXIN/27 Hz 0 1 LXIN/25 Hz LXIN/25 Hz

1 0 LXIN/211 Hz LXIN/211 Hz 1 0 LXIN/29 Hz LXIN/29 Hz

1 1 LXIN/215 Hz LXIN/215 Hz 1 1 LXIN/213 Hz LXIN/213 Hz

* This specification are subject to be changed without notice.

12.27.2001

19

Page 20

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

TIMER/COUNTER FUNCTIONTIMER/COUNTER FUNCTION

TIMER/COUNTER FUNCTION

TIMER/COUNTER FUNCTIONTIMER/COUNTER FUNCTION

Timer/counterA can be programmable for timer, event counter and pulse width measurement. Each timer/

counter can execute any one of these functions independly.

EVENT COUNTER MODE

For event counter mode, timer/counter increases one at any rising edge of P8.1/TRGB for timerB (P8.3/

TRGA for timer A). When timerB (timerA) counts overflow, it will give interrupt control an interrupt request

TRGB (TRGA).

P8.1/TRGB (P8.3/TRGA)

TimerB (TimerA) value n n+1 n+2 n+3 n+4 n+5 n+6

PROGRAM EXAMPLE: Enable timerA with P28

LDIA #0100B;

OUTA P28; Enable timerA with event counter mode

TIMER MODE

For timer mode, timer/counter increase one at any rising edge of internal pulse. User can choose 4 kinds

of internal pulse rate by setting IPSB for timerB (IPSA for timerA).

When timer/counter counts overflow, TRGB (TRGA) will be generated to interrupt control unit.

Internal pulse

TimerB (TimerA )value

n n+1 n+2 n+3 n+4 n+5 n+6

n+7

PROGRAM EXAMPLE:To generate TRGA interrupt request after 60 ms with system clock LXlN=32KHz

LDIA #0100B;

EXAE; enable mask 2

EICIL 110111B; interrupt latch ←0, enable EI

LDIA #0AH;

STATAL;

LDIA #00H;

STATAM;

LDIA #0FH;

STATAH;

LDIA #1000B;

OUTA P28; enable timerA with internal pulse rate: LXIN/23 Hz

NOTE: The preset value of timer/counter register is calculated as following procedure.

Internal pulse rate: LXIN/2

3

; LXIN = 32KHz

The time of timer counter count one = 23 /LXIN = 8/32768=0.244ms

The number of internal pulse to get timer overflow = 60 ms/ 0.244ms = 245.901= 0F6H

The preset value of timer/counter register = 1000H - 0F6H = 0F0AH

PULSE WIDTH MEASUREMENT MODE

* This specification are subject to be changed without notice.

12.27.2001

20

Page 21

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

For the pulse width measurement mode, the counter only incresed by the rising edge of internal pulse rate as

external timer/counter input (P8.1/TRGB, P8.3/TRGA ), interrupt request will be generated as soon as

timer/counter count overflow.

P8.1/TRGB(P8.3/TRGA)

Internal pulse

TimerB(TimerA) value

n n+1 n+2 n+3 n+4 n+5

PROGRAM EXAMPLE: Enable timerA by pulse width measurement mode.

LDIA #1100b;

OUTA P28; Enable timerA with pulse width measurement mode.

HIGH SPEED TIMER/COUNTERHIGH SPEED TIMER/COUNTER

HIGH SPEED TIMER/COUNTER

HIGH SPEED TIMER/COUNTERHIGH SPEED TIMER/COUNTER

EM73P461A has one 8-bit high speed timer/counter (HTC). It supports three special functions : auto load

timer, melody output and pulse width measurement modes. The HTC is available for the NORMAL and

SLOW operation mode.

The HTC can be set initial value and send counter value to counter registers (P11 and P10), P31 is the

command port for HTC, user can choose different operation mode and different internal clockrate by setting

the port. The timer/counter increase one at the rising edge of internal pulse. The HTC can generate an overflow

interrupt (HTCI) when it overflows. The HTCI cannot be generated when the HTC is in the melody mode

or disabled.

P4.0/SOUND

SOUND

P4.1/TRGH

Output data

mask option

F

HTC

P31(3,2)

XIN

P31(1,0)

Input data

÷2

8-bit binary counter

P11

P10

Overflow

Reload

Data bus

HTCI interrupt

Timer/counter B

P31 is the command register of the 8-bit high speed timer/counter.

P31 32 1 0 Initial value : 0000

HTMS HIPS

HTMS Mode selection HIPS Clock rate selection

0 0 Stop 0 0 LXIN/20 Hz LXIN/20 Hz

0 1 Auto load timer mode 0 1 LXIN/22 Hz LXIN/22 Hz

1 0 Melody mode 1 0 CLK/24 Hz Reserved

1 1 Pulse width measurement mode 1 1 CLK/26 Hz Reserved

P11 and P10 are the counter registers of the 8-bit high speed timer/counter. P10 is the lower nibble register

and P11 is the higher nibble register. (HT is the value of counter registers.)

32 1 0 P10 3210Initial value : 0000 0000 (HT)

P11

Higher nibble register Lower nibble register

* This specification are subject to be changed without notice.

NORMAL mode SLOW mode

12.27.2001

21

Page 22

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

** F

=[(XIN/2X)/(100H-HT)]/2, HT=0~255

HTC

** Example : LXIN=32K Hz, HIPS=01, HT=11110000B=0F0H.

⇒F

LDIA #1111B

OUTA P11

LDIA #0000B

OUTA P10

LDIA #1001B

OUTA P31

=[(32K Hz/22)/(100H-0f0H)]/2=256 Hz.

HTC

The value of 8-bit binary up counter can be presetted by P10 and P11. The value of registers can loaded into

the HTC when the counter starts counting or occurs overflow. If user write value to the registers before the

next overflow occurs, the preset value can be changed.

The preset value will be changed when users output the different data to P10 and P11.

The count value of HTC can be read from P10 and P11. The value is unstable when user read the value during

counting. Thus, user must disable the counter before reading the value.

The P4.0/SOUND and SOUND pins will output the squre wave in the melody mode. When the CPU is not

in the melody mode, the P4.0/SOUND is high and SOUND is low.

The P4.1/RGH pin will be the input pin in the pulse width measurement mode. User must output high to P4.1/

TRGH and then it can be the HTC external input pin. When the HTC is disabled, the P4.1 pin is a normal I/

O pin.

INTERRUPT FUNCTIONINTERRUPT FUNCTION

INTERRUPT FUNCTION

INTERRUPT FUNCTIONINTERRUPT FUNCTION

There are 6 interrupt sources, 2 external interrupt sources, 4 internal interrupt sources. Multiple

interrupts are admitted according the priority.

TypeType

Type

TypeType

External External interrupt(INT0) 1 IL 5 EI=1 002H

Internal High speed timer overflow interrupt (HTCI) 2 IL 4 EI=1, MASK3=1 004H

Internal TimerA overflow interrupt (TRGA) 3 IL 3 EI=1, MASK2=1 006H

Internal TimerB overflow interrupt (TRGB) 4 IL2 EI=1, MASK1=1 008H

Internal Time base interrupt(TBI) 5 IL 1 00AH

External External interrupt(INT1) 6 IL0 EI=1,MASK0=1 00CH

INTERRUPT STRUCTUREINTERRUPT STRUCTURE

INTERRUPT STRUCTURE

INTERRUPT STRUCTUREINTERRUPT STRUCTURE

Interrupt sourceInterrupt source

Interrupt source

Interrupt sourceInterrupt source

Reset by system reset and program

instruction

PriorityPriority

Priority

PriorityPriority

MASK0 MASK1 MASK1 MASK2 MASK3

INT1

r0

IL0

TBI

r1

IL1

InterruptInterrupt

Interrupt

InterruptInterrupt

TRGB

IL2r2IL3

LatchLatch

Latch

LatchLatch

TRGA

r3

InterruptInterrupt

Interrupt

InterruptInterrupt

Enable conditionEnable condition

Enable condition

Enable conditionEnable condition

HTCI

r4

IL4

INT0

r5

IL5

Program ROMProgram ROM

Program ROM

Program ROMProgram ROM

entry addressentry address

entry address

entry addressentry address

Reset by system reset and program

instruction

Set by program instruction

EI

Interrupt request Interrupt entry address

* This specification are subject to be changed without notice.

Priority checker

Entry address generator

12.27.2001

22

Page 23

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

Interrupt controller:

IL0-IL5 : Interrupt latch. Hold all interrupt requests from all interrupt sources. ILr can not be

set by program, but can be reset by program or system reset, so IL only can decide

which interrupt source can be accepted.

MASK0-MASK3 : Except INT0, MASK register can promit or inhibit all interrupt sources.

EI : Enable interrupt Flip-Flop can promit or inhibit all interrupt sources, when inter-

rupt happened, EI is cleared to "0" automatically, after RTI instruction happened,

EI will be set to "1" again.

Priority checker : Check interrupt priority when multiple interrupts happened.

INTERRUPT FUNCTIONINTERRUPT FUNCTION

INTERRUPT FUNCTION

INTERRUPT FUNCTIONINTERRUPT FUNCTION

The procedure of interrupt operation:

1. Push PC and all flags to stack.

2. Set interrupt entry address into PC.

3. Set SF= 1.

4. Clear EI to inhibit other interrupts happened.

5. Clear the IL for which interrupt source has already be accepted.

6. To excute interrupt subroutine from the interrupt entry address.

7. CPU accept RTI, restore PC and flags from stack. Set EI to accept other interrupt requests.

PreliminaryPreliminary

PROGRAM EXAMPLE: To enable interrupt of "INT0, TRGA"

LDIA #1100B;

EXAE; set mask register "1100B"

EICIL 111111B ; enable interrupt F.F.

LCD DRIVERLCD DRIVER

LCD DRIVER

LCD DRIVERLCD DRIVER

EM73P461A can directly drive the liquid crystal display (LCD) and has 32 segment, 4 common output pins (1/

2 bias, 1/3 bias). There are total 32x4 dots can be display. The V1, V2, V3, VA, VB, VDD and VSS pins are

the LCD bias generator.

CONTROL OF LCD DRIVERCONTROL OF LCD DRIVER

CONTROL OF LCD DRIVER

CONTROL OF LCD DRIVERCONTROL OF LCD DRIVER

The LCD driver control command register is P27. When LDC is 0, the LCD is disabled, the COM and SEG

pins are VSS. When LDC is 1, the LCD driver enables.

When the CPU is reseted or during the STOP operation mode, the LCD driver is disabled.

Port27

The LCD display data is stored in the display data area of the data memory (RAM).

The display data area begins with address 20H during reset. The LCD display data area ia as below :

2 1 0 Initial value : 0000

LDC DUTY

LDC LCD display control DUTY Driving method select

0 LCD display disable 0 0 0 1/4 duty (1/3 bias)

1 LCD display enable 0 0 1 1/4 duty (1/2 bias)

0 1 0 1/3 duty (1/3 bias)

0 1 1 1/3 duty (1/2 bias)

1 0 0 1/2 duty (1/2 bias)

1 0 1 Static

1 1 * Reserved

* This specification are subject to be changed without notice.

12.27.2001

23

Page 24

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

RAM COM3 COM2 COM1 COM0

address bit3 bit2 bit1 bit0

SEG0 20H

SEG1 21H

SEG2 22H

::

::

SEG30 3EH

SEG31 3FH

The relation between LCD display data and driving method

Driving method bit3 bit2 bit1 bit0

1/4 duty COM3 COM2 COM1 COM0

1/3 duty - COM2 COM1 COM0

1/2 duty - - COM1 COM0

Static - - - COM0

LCD frame frequency : According to the drive method to set the frame frequency.

Duty Frame frequency (Hz)

1/4 duty 64 x (4/4) = 64

1/3 duty 64 x (4/3) = 85

1/2 duty 64 x (4/2) = 128

Static 64

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

PROGRAM EXAMPLE :

LDIA #0001B ; 1/4 duty, 1/2 bias

OUTA P27

LDIA #1001B ; enable LCD

OUTA P27

LCD DRIVING METHODSLCD DRIVING METHODS

LCD DRIVING METHODS

LCD DRIVING METHODSLCD DRIVING METHODS

There are six kinds of driving methods can be selected by DUTY (P27.0~P27.2). The drivinf waveforms of

LCD driver are as below :

• •

VDD=3VVDD=3V

•

VDD=3V

• •

VDD=3VVDD=3V

(1) 1/4 duty (1/3 bias)

COM0

COM1

COM2

COM3

SEG0

SEG0-COM0

ON

SEG0-COM1

OFF

VA

VB

Frame

V

DD

3V

V3

2V

V2

1V

V1

V

SS

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

-V1

-V2

-V3

V3

V2

V1

Vss

-V1

-V2

-V3

(2 ) 1/3 duty (1/3 bias)

V

DD

3V

V3

2V

V2

VA

VB

Frame

1V

V1

V

SS

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

V3

V2

V1

Vss

-V1

-V2

-V3

V3

V2

V1

Vss

-V1

-V2

-V3

* This specification are subject to be changed without notice.

12.27.2001

24

Page 25

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

(3) 1/4 duty (1/2 bias)

V

DD

3V

V3

1.5V

V2

VA

V1

VB

V

SS

COM0

COM1

COM2

COM3

SEG0

SEG0-COM0

ON

SEG0-COM1

OFF

Frame

RESETTING FUNCTIONRESETTING FUNCTION

RESETTING FUNCTION

RESETTING FUNCTIONRESETTING FUNCTION

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

-V1

-V3

V3

V1

Vss

-V1

-V3

(4) 1/3 duty (1/2 bias)

V

DD

3V

V3

1.5V

V2

VA

V1

VB

V

SS

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

-V1

-V3

V3

V1

Vss

Frame

-V1

-V3

VA

Frame

VB

V

DD

3V

V3

1.5V

V2

V1

V

SS

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

V3

V1

Vss

-V1

-V3

V3

V1

Vss

-V1

-V3

(6) static(5) 1/2 duty (1/2 bias)

V

DD

3V

V3

1.5V

V2

VA

V1

VB

V

SS

V3

Vss

ON

OFF

V3

V1

Vss

V3

Vss

-V3

V3

Vss

-V3

Frame

When CPU in normal working condition and RESET pin holds in low level for three instruction cycles at least,

then CPU begins to initialize the whole internal states, and when RESET pin changes to high level, CPU begins

to work in normal condition.

The CPU internal state during reset condition is as following table :

Hardware condition in RESET state Initial value

Program counter 0000h

Status flag 01h

Interrupt enable flip-flop ( EI ) 00h

MASK0 ,1, 2, 3 00h

Interrupt latch ( IL ) 00h

P10, 11,14, 16, 19, 25, 27, 28, 29, 31 00h

P4, 8, 23, 24 0Fh

Both oscillator Start oscillation

The RESET pin is a hysteresis input pin and it has a pull-up resistor available by mask option.

The simplest RESET circuit is connect RESET pin with a capacitor to V

RESET

and a diode to VDD.

SS

* This specification are subject to be changed without notice.

12.27.2001

25

Page 26

EM73P461A I/O PORT DESCRIPTION :EM73P461A I/O PORT DESCRIPTION :

EM73P461A I/O PORT DESCRIPTION :

EM73P461A I/O PORT DESCRIPTION :EM73P461A I/O PORT DESCRIPTION :

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

PortPort

Port

PortPort

0 E Input port , wakeup function

1-- -2-- -3-- -4 E Input port E Output port, P4.0/SOUND

5-- -6-- -7-- -8 E Input port, wakeup function, E Output port

9-- -10 -- I High speed timer/counter low nibble

11 -- I High speed timer/counter high nibble

12 -- -13 -- -14 I CPU status I Clear P14.0 to 0

15 -- -16 I STOP mode control register

17 -18 -19 I IDLE mode control register

20 -21 -22 I Slow mode control register

23 -24 -25 I Timebase control register

26 -27 I LCD control register

28 I Timer/counter A control register

29 I Timer/counter B control register

30 -31 I HTC control register

Input functionInput function

Input function

Input functionInput function

Output functionOutput function

Output function

Output functionOutput function

NoteNote

Note

NoteNote

* This specification are subject to be changed without notice.

12.27.2001

26

Page 27

ABSOLUTE MAXIMUM RATINGSABSOLUTE MAXIMUM RATINGS

ABSOLUTE MAXIMUM RATINGS

ABSOLUTE MAXIMUM RATINGSABSOLUTE MAXIMUM RATINGS

ItemsItems

Items

ItemsItems

Sym.Sym.

Sym.

Sym.Sym.

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

RatingsRatings

Ratings

RatingsRatings

ConditionsConditions

Conditions

ConditionsConditions

Supply Voltage V

Input Voltage V

Output Voltage V

Power Dissipation P

Operating Temperature T

Storage Temperature T

RECOMMANDED OPERATING CONDITIONSRECOMMANDED OPERATING CONDITIONS

RECOMMANDED OPERATING CONDITIONS

RECOMMANDED OPERATING CONDITIONSRECOMMANDED OPERATING CONDITIONS

ItemsItems

Items

ItemsItems

Supply Voltage V

Sym.Sym.

Sym.

Sym.Sym.

DD

DD

IN

O

D

OPR

STG

RatingsRatings

Ratings

RatingsRatings

2.4V to 3.6V 500KHz<Fc<4MHz by RC osc

-0.5V to 6V

-0.5V to VDD+0.5V

-0.5V to VDD+0.5V

300mW T

0oC to 50oC

-55oC to 125oC

=50oC

OPR

ConditionCondition

Condition

ConditionCondition

Fs=32KHz by crystal osc

Input Voltage V

Operating Frequency F

IH

V

IL

C

0.90xVDD to V

0V to 0.10xV

DD

DD

4MHz CLK, VDD (RC osc), R=100KΩ

Fs 32KHz LXIN, LXOUT (crystal osc)

DC ELECTRICAL CHARACTERISTICSDC ELECTRICAL CHARACTERISTICS

DC ELECTRICAL CHARACTERISTICS (VDD=3±0.3V, VSS=0V, T

DC ELECTRICAL CHARACTERISTICSDC ELECTRICAL CHARACTERISTICS

Parameters Sym. Parameters Sym.

Parameters Sym.

Parameters Sym. Parameters Sym.

Supply current I

DD

Min.Min.

Min.

Min.Min.

Typ.Typ.

Typ.

Typ.Typ.

Max.Max.

Max.

Max.Max.

UnitUnit

Unit

UnitUnit

200 320 600 µA VDD=3.3V,no load,NORMAL mode,

OPR

=25oC)

ConditionsConditions

Conditions

ConditionsConditions

Fc=4MHz, Fs=32KHz

=3.3V,no load,SLOW mode, Fs=32KHz

DD

=3.3V,IDLE mode

DD

=3.3V, STOP mode

DD

DD

SS

Hysteresis voltage V

Input current I

V

HYS+

HYS-

IH

47 15µAV

25 10µAV

0 0.1 1 µA V

0.50VDD0.65VDD 0.75V

0.20VDD0.30V

0.40V

DD

V RESET, P0, P8

DD

V

DD

30 40 60 µA P0, Pull-down, VIH=V

-60 -40 -30 µA P0, Pull-up, VIH=V

0 0.1 1 µA P0, None

=3.3V, VIH=3.3/0V

DD

DD

=3.3V,VIL=0.4V

Output voltage V

0 ±0.1 ±1 µA RESET, V

I

IL

-100 -200 -500 µA Normal current Push-pull,VDD=3.3V,VIL=0.4V

-30 -50 -85 µA Low current push-pull, V

OH

2.4 2.6 2.7 V High current push-pull, SOUND

V

=2.7V, IOH=-2mA

DD

2.0 2.4 2.5 V Normal current push-pull,

V

=2.7V, IOH=-60µA

V

Leakage current I

LO

Input resistor R

LCD bias voltage V1

1

(

/2 bias) V2

V3

LCD bias voltage V1

1

(

/3 bias) V2

V3

IN

OL

0 0.1 0.3 V VDD=2.7V,IOL=1mA

0 0.1 1 µA Open-drain, VDD=3.3V, VO=3.3V

35 50 70 KΩ RESET

1

/2VDD-0.11/2V

1

/2VDD-0.11/2V

VDD-0.1 V

1

/3VDD-0.11/3V

2

/3VDD-0.12/3V

VDD+0.1 V

1

/2VDD+0.1 V I1=5µA

DD

1

/2VDD+0.1 V I2=5µA

DD

VDD+0.1 V I3=5µA

DD

1

/3VDD+0.1 V I1=5µA

DD

2

/3VDD+0.1 V I2=5µA

DD

VDD+0.1 V I3=5µA

DD

DD

Frequency stability 2 5 20 % Fc=4MHz, RC osc, [F(3V)-F(2.4V)]/F(3V)

Frequency variation 2 5 20 % Fc=4MHz, V

=3V, RC osc,

DD

[F(typical)-F(worse case)]/F(typical)

* This specification are subject to be changed without notice.

12.27.2001

27

Page 28

RESET PIN TYPERESET PIN TYPE

RESET PIN TYPE

RESET PIN TYPERESET PIN TYPE

TYPE RESET-A

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

RESET

OSCILLATION PIN TYPEOSCILLATION PIN TYPE

OSCILLATION PIN TYPE

OSCILLATION PIN TYPEOSCILLATION PIN TYPE

TYPE OSC-B TYPE OSC-H1

LXIN

LXOUT

TYPE OSC-I

100KΩ

CLK

mask option

Crystal

Osc.

RC Osc.

2 MΩ

LXIN

RC Osc.

INPUT PIN TYPEINPUT PIN TYPE

INPUT PIN TYPE

INPUT PIN TYPEINPUT PIN TYPE

TYPE INPUT-K

positive

edge

detector

negative

edge

detector

I/O PIN TYPEI/O PIN TYPE

I/O PIN TYPE

I/O PIN TYPEI/O PIN TYPE

input data

WAKEUP

mask option

: mask option

TYPE I/O-N TYPE I/O-Q

: mask option : mask option

* This specification are subject to be changed without notice.

12.27.2001

28

Page 29

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

TYPE I/O-RTYPE I/O-R

TYPE I/O-R

TYPE I/O-RTYPE I/O-R

TYPE I/O-Q

: mask option

path B

path A

Output

data

latch

Input

data

Output

data

Special function

output

TYPE I/O-STYPE I/O-S

TYPE I/O-S

TYPE I/O-STYPE I/O-S

TYPE I/O-N

WAKEUP function

mask option

path B

path A

SEL

Output

data

latch

Special function

control input

Input

data

Output

data

Path A : For set and clear bit of port instructions, data goes through path A from output data latch to CPU.

Path B : For input and test instructions, data from output pin go through path B to CPU and the output data latch

will be set to high.

* This specification are subject to be changed without notice.

12.27.2001

29

Page 30

PAD DIAGRAMPAD DIAGRAM

PAD DIAGRAM

PAD DIAGRAMPAD DIAGRAM

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

V1

VSS

CLK

LXOUT

LXIN

VDD

P4.3

P4.2

P4.1/TRGH

P4.0/SOUND

SOUND

P8.3

P8.2

P8.1/DOUT

P8.0/DIN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

EMC

16

V2

V3

60

61

17 18 19

59

VA

58

VB

57

COM0

56

COM1

55

EM73P461A

21

22 23

20

COM2

COM3

54

(0,0)

24

25

SEG0

5253

26

SEG1

51

27

SEG2

50

28

SEG3

49

29

SEG4

48

30

SEG5

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG31

SEG30

RESET

TEST/VPP

P0.2/OEB

P0.3/DCLK

P0.1/PGMB

P0.0/ACLK

SEG29

Unit : µm

Chip Size : 2070 x 2500 µm

Note : For PCB layout, IC substrate must be floated or connected to VSS.

* This specification are subject to be changed without notice.

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

12.27.2001

30

Page 31

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

Pad No.Pad No.

Pad No.

Pad No.Pad No.

1 V1 -905.0 1115.5

2 VSS -905.0 990.5

3 CLK -905.0 870.5

4 LXOUT -905.0 750.5

5 LXIN -905.0 630.5

6 VDD -905.0 510.5

7 P4.3 -905.0 380.5

8 P4.2 -904.0 214.8

9 P4.1/TRGH -904.0 94.8

10 P4.0/SOUND -904.0 -25.2

11 SOUND -904.0 -415.7

12 P8.3 -904.0 -535.7

13 P8.2 -904.0 -655.7

14 P8.1/DOUT -904.0 -775.7

15 P8.0/DIN -904.0 -895.7

16 RESET -848.2 -1119.4

17 TEST/VPP -728.2 -1120.0

18 P0.3/DCLK -608.2 -1119.9

19 P0.2/OEB -488.2 -1119.9

20 P0.1/PGMB -368.2 -1119.9

21 P0.0/ACLK -248.2 -1119.9

22 SEG31 -128.2 -1119.9

23 SEG30 -8.2 -1119.9

24 SEG29 111.8 -1119.9

25 SEG28 231.8 -1119.9

26 SEG27 351.8 -1119.9

27 SEG26 471.8 -1119.9

28 SEG25 591.9 -1119.9

29 SEG24 711.8 -1119.9

30 SEG23 841.8 -1119.9

31 SEG22 899.4 -999.9

32 SEG21 899.4 -874.9

33 SEG20 899.4 -750.0

34 SEG19 899.4 -625.0

35 SEG18 899.4 -500.0

36 SEG17 899.4 -375.0

37 SEG16 899.4 -250.0

38 SEG15 899.4 -125.0

39 SEG14 899.4 0.0

40 SEG13 899.4 145.5

SymbolSymbol

Symbol

SymbolSymbol

XX

X

XX

YY

Y

YY

* This specification are subject to be changed without notice.

12.27.2001

31

Page 32

EM73P461AEM73P461A

EM73P461A

EM73P461AEM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

PreliminaryPreliminary

Preliminary

PreliminaryPreliminary

Pad No.Pad No.

Pad No.

Pad No.Pad No.

41 SEG12 899.4 275.5

42 SEG11 899.4 395.5

43 SEG10 899.4 515.5

44 SEG9 899.4 635.5

45 SEG8 899.4 755.5

46 SEG7 899.4 875.5