Page 1

© 1999 Fairchild Semiconductor Corporation DS009612 www.fairchildsemi.com

June 1989

Revised November 1999

DM93L14 Quad Latch

DM93L14

Quad Latch

General Description

The DM93L14 is a mul tifunctional 4-bit latch designed for

general purpose s torage appl ications in high spe ed digital

systems. All outputs have active pull-up circuitry to provide

high capacitance drive and to provide low im pedance in

both logic states for good noise immunity.

Features

■ Can be used as single input D latches or set/reset

latches

■ Active low enable gate input

■ Overriding master reset

Ordering Code:

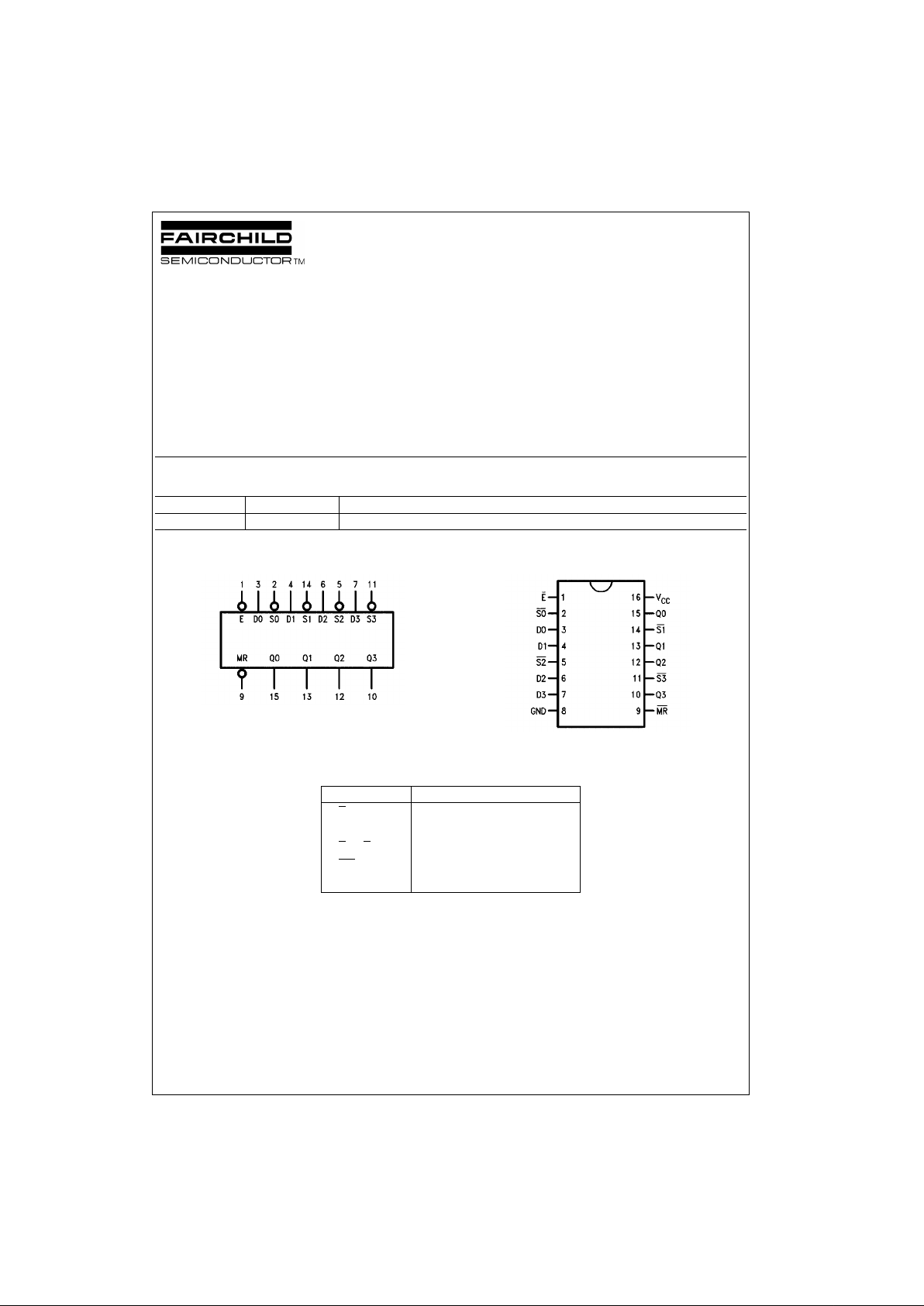

Logic Symbol

VCC = Pin 16

GND = Pin 8

Connection Diagram

Pin Descriptions

Order Number Package Number Package Description

DM93L14N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Pin Names Description

E

Enable Input (Active LOW)

D0 − D3 Data Inputs

S

0 − S3 Set Inputs (Active LOW)

MR

Master Reset Input (Active LOW)

Q0 − Q3 Latch Outputs

Page 2

www.fairchildsemi.com 2

DM93L14

Functional Description

The DM93L14 consists of four latches with a common

active LOW Enable input and active LOW Master Reset

input. When the E nable goes HIGH, data present i n the

latches is stored a nd the state of the latch is no longer

affected by the S

n

and Dn inputs. the Master Reset when

activated overrides all other input conditions forcing all

latch outputs LOW. Each of the four latches can be operated in one of two modes:

D-TYPE LATCH—For D-type operation the S

input of a

latch is held LOW. While the common Enable is active the

latch output follo ws the D input. Infor mation pr esent at th e

latch output is stored in the latch when the Enable go es

HIGH.

SET/RESET LATCH—During set/reset op eration when th e

common Enable is LOW a latch is reset by a LOW on the D

input, and can be set by a LOW on the S

input if the D input

is HIGH. If both S

and D inputs are LOW, the D input will

dominate and the latch will be reset. When the Enable

goes HIGH, the la tch rema ins in t he last st ate prior to disablement. The two modes of la tch operat ion are shown in

the Truth Table.

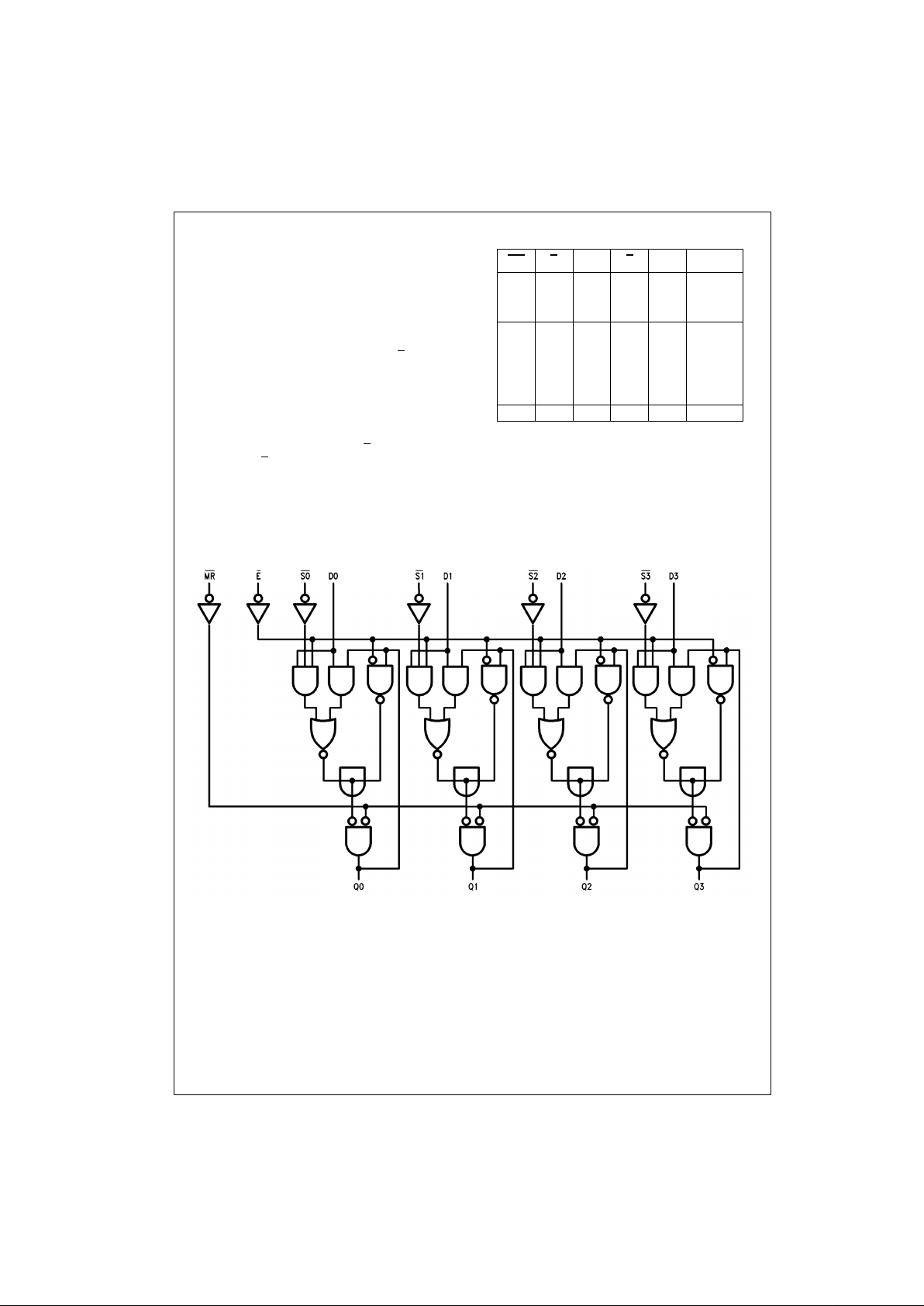

Tr uth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Q

n−1

= Previous Output St ate

Q

n

= Present Output State

Logic Diagram

MR E

D

S

Q

n

Operation

HLLLLD Mode

HLHLL

HHXXQ

n-1

HLLLLR/S Mode

HLHLH

HLLHL

HLHHQ

n-1

HHXXQ

n-1

L X X X L RESET

Page 3

3 www.fairchildsemi.com

DM93L14

Absolute Maximum Ratings(Note 1)

Note 1: The Absolute Maximum Ratings are those values beyond which

the safety of the dev ice cannot b e guaranteed . The device sh ould not be

operated at these limit s. The parametric values defi ned in the Electrical

Characteristics tab les are not guaranteed a t t he absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

Recommended Operating Conditions

Supply Voltage 7V

Input Voltage 5.5V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.5 5 5.5 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.7 V

I

OH

HIGH Level Output Voltage −400 µA

I

OL

LOW Level Output Current 4.8 mA

T

A

Free Air Operating Tempera ture −55 125 °C

tS (H) Setup Time HIGH or LOW 10

ns

tS (L)

Dn to E

20

tH (H) Hold Time HIGH or LOW 0

ns

tH (L) Dn to E 10

t

S

(H) Setup time HIGH, Dn to S

n

15 ns

t

H

(L) Hold time LOW, Dn to S

n

5ns

tW (L)

E Pulse Width LOW

30 ns

t

W

(L)

MR Pulse Width LOW

25 ns

t

REC

Recovery time, MR to E 5ns

Page 4

www.fairchildsemi.com 4

DM93L14

Electrical Characteristics

Over recommended operating free air temperature range (unless otherwise noted)

Note 2: All typicals are at VCC = 5V, TA = 25°C

Note 3: Not more than one output should be shorted at a t im e, and the duration should not exceed one second.

Note 4: I

CC

is measured with all out puts open and all inputs g rounded.

Switching Characteristics

VCC = +5.0V, TA = +25°C (See Waveforms and Load Configurations)

Symbol Parameter Conditions Min

Typ

Max Units

(Note 2)

V

I

Input Clamp Voltage VCC = Min, II = −10 mA −1.5 V

V

OH

HIGH Level Output Voltage VCC = Min, IOH = Max,

2.4 V

V

IL

= Max, VIH = Min

V

OL

LOW Level Output Voltage VCC = Min, IOL = Max,

0.3 V

V

IH

= Min, VIL = Max

I

I

Input Current @ Max VCC = Max, VI = 5.5V

1mA

Input Voltage

I

IH

HIGH Level Input Current VCC = Max, VI = 2.4V Inputs 20

µA

D

n

30

I

IL

LOW Level Input Current VCC = Max, VI = 0.3V Inputs −400

µA

D

n

−600

I

OS

Short Circuit VCC = Max

−2.5 −25 mA

Output Current (Note 3)

I

CC

Supply Current VCC = Max (Note 4) 16.5 mA

Symbol Parameter Min Max Units

t

PLH

Propagation Delay 45

ns

t

PHL

E to Q

n

36

t

PLH

Propagation Delay 30

ns

t

PHL

Dn to Q

n

30

t

PLH

Propagation Delay, MR to Q

n

30 ns

t

PHL

Propagation Delay, Sn to Q

n

33 ns

Page 5

5 www.fairchildsemi.com

DM93L14 Quad Latch

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described , no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are dev ic es or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provide d in the labe l ing, can be re asonably expected to result in a significant injury to the

user.

2. A critical compo nent in any com ponen t of a life s upp ort

device or system whose failure to perform can be reasonably expected to cause the failure of the l ife support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Loading...

Loading...