Datadelay PDU13F-0.5, PDU13F-0.5A2, PDU13F-0.5B2, PDU13F-0.5M, PDU13F-0.5MC3 Datasheet

...

|

|

|

PDU13F |

|

|

|

|

|

|

3-BIT PROGRAMMABLE |

data |

|

|

® |

|

3 |

|||

DELAY LINE |

delay |

|

||

(SERIES PDU13F) |

devices, inc. |

|||

|

|

|

|

|

FEATURES

∙Digitally programmable in 8 delay steps

∙Monotonic delay-versus-address variation

∙Two separate outputs: inverting & non-inverting

∙Precise and stable delays

∙Input & outputs fully TTL interfaced & buffered

∙10 T2L fan-out capability

∙Fits standard 14-pin DIP socket

∙Auto-insertable

PACKAGES

IN |

|

1 |

14 |

|

VCC |

IN |

|

1 |

16 |

|

|

VCC |

||

|

|

|

|

|

||||||||||

N/C |

|

2 |

13 |

|

N/C |

N/C |

|

|

15 |

|

|

N/C |

||

|

|

|

2 |

|

|

|||||||||

N/C |

|

3 |

12 |

|

N/C |

N/C |

|

3 |

14 |

|

|

N/C |

||

|

|

|

|

|

||||||||||

OUT |

|

4 |

11 |

|

N/C |

N/C |

|

4 |

13 |

|

|

N/C |

||

|

|

|

|

|

||||||||||

OUT/ |

|

5 |

10 |

|

A0 |

OUT |

|

5 |

12 |

|

|

N/C |

||

|

|

|

|

|

||||||||||

EN/ |

|

6 |

9 |

|

A1 |

OUT/ |

|

6 |

11 |

|

|

A0 |

||

|

|

|

|

|

||||||||||

GND |

|

7 |

8 |

|

A2 |

EN/ |

|

7 |

10 |

|

|

A1 |

||

|

|

|

|

|

||||||||||

|

|

|

|

|

|

GND |

|

|

8 |

9 |

|

|

A2 |

|

PDU13F-xx |

DIP |

|

|

|

|

|

||||||||

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

||||||

PDU13F-xxA2 Gull-Wing |

PDU13F-xxMC3 |

|

||||||||||||

PDU13F-xxB2 J-Lead |

|

|||||||||||||

Military Gull-Wing |

||||||||||||||

PDU13F-xxM |

Military DIP |

|||||||||||||

|

|

|

|

|

|

|

|

|||||||

FUNCTIONAL DESCRIPTION |

PIN DESCRIPTIONS |

|

The PDU13F-series device is a 3-bit digitally programmable delay line. |

IN |

Delay Line Input |

The delay, TDA, from the input pin (IN) to the output pins (OUT, OUT/) |

OUT |

Non-inverted Output |

depends on the address code (A2-A0) according to the following formula: |

OUT/ |

Inverted Output |

|

A2 |

Address Bit 2 |

TDA = TD0 + TINC * A |

A1 |

Address Bit 1 |

|

A0 |

Address Bit 0 |

where A is the address code, TINC is the incremental delay of the device, |

EN/ |

Output Enable |

and TD0 is the inherent delay of the device. The incremental delay is |

VCC |

+5 Volts |

specified by the dash number of the device and can range from 0.5ns |

GND |

Ground |

through 50ns, inclusively. The enable pin (EN/) is held LOW during

normal operation. When this signal is brought HIGH, OUT and OUT/ are forced into LOW and HIGH states, respectively. The address is not latched and must remain asserted during normal operation.

SERIES SPECIFICATIONS

∙Total programmed delay tolerance: 5% or 1ns,

whichever is greater

∙Inherent delay (TD0): 6ns typical (OUT)

5.5ns typical (OUT/)

∙Setup time and propagation delay: Address to input setup (TAIS): 6ns

Disable to output delay (TDISO): 6ns typ. (OUT)

∙Operating temperature: 0° to 70° C

∙Temperature coefficient: 100PPM/°C (excludes TD0)

∙Supply voltage VCC: 5VDC ± 5%

∙Supply current: ICCH = 45ma

ICCL = 20ma

∙Minimum pulse width: 20% of total delay

DASH NUMBER SPECIFICATIONS

Part |

Incremental Delay |

Total Delay |

||

Number |

Per Step (ns) |

Change (ns) |

||

PDU13F-.5 |

.5 ± .3 |

3.5 ± 1.0 |

||

PDU13F-1 |

1 |

± .4 |

7 ± 1.0 |

|

PDU13F-2 |

2 |

± .4 |

14 |

± 1.0 |

PDU13F-3 |

3 |

± .5 |

21 |

± 1.1 |

PDU13F-5 |

5 |

± .6 |

35 |

± 1.8 |

PDU13F-10 |

10 |

± 1.0 |

70 |

± 3.5 |

PDU13F-15 |

15 |

± 1.3 |

105 ± 5.3 |

|

PDU13F-20 |

20 |

± 1.5 |

140 ± 7.0 |

|

PDU13F-40 |

40 |

± 2.0 |

280 |

± 14.0 |

PDU13F-50 |

50 |

± 2.5 |

350 |

± 17.5 |

NOTE: Any dash number between .5 and 50 not shown is also available.

©1997 Data Delay Devices

Doc #97001 |

DATA DELAY DEVICES, INC. |

1 |

1/10/97 |

3 Mt. Prospect Ave. Clifton, NJ 07013 |

PDU13F

APPLICATION NOTES

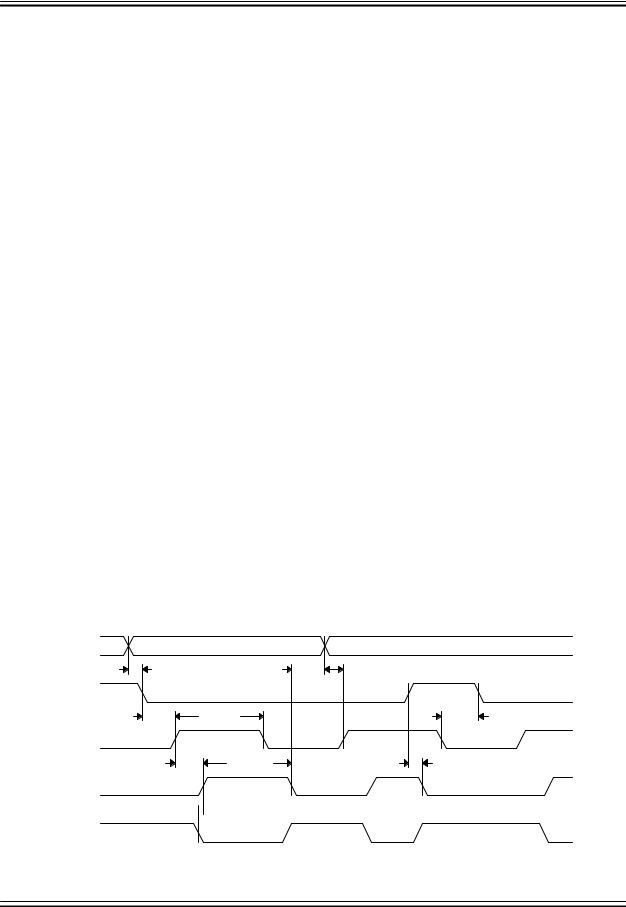

ADDRESS UPDATE |

possibility of spurious signals persists until the |

|

required TDISH has elapsed. |

The PDU13F is a memory device. As such, |

INPUT RESTRICTIONS |

special precautions must be taken when |

|

changing the delay address in order to prevent |

|

spurious output signals. The timing restrictions |

There are three types of restrictions on input |

are shown in Figure 1. |

pulse width and period listed in the AC |

After the last signal edge to be delayed has |

Characteristics table. The recommended |

conditions are those for which the delay |

|

appeared on the OUT pin, a minimum time, |

tolerance specifications and monotonicity are |

TOAX, is required before the address lines can |

guaranteed. The suggested conditions are |

change. This time is given by the following |

those for which signals will propagate through the |

relation: |

unit without significant distortion. The absolute |

TOAX = max { (Ai - A i-1) * TINC , 0 } |

conditions are those for which the unit will |

produce some type of output for a given input. |

|

where A i-1 and Ai are the old and new address |

When operating the unit between the |

codes, respectively. Violation of this constraint |

recommended and absolute conditions, the |

may, depending on the history of the input signal, |

delays may deviate from their values at low |

cause spurious signals to appear on the OUT |

frequency. However, these deviations will |

pin. The possibility of spurious signals persists |

remain constant from pulse to pulse if the input |

until the required TOAX has elapsed. |

pulse width and period remain fixed. In other |

A similar situation occurs when using the EN/ |

words, the delay of the unit exhibits frequency |

and pulse width dependence when operated |

|

signal to disable the output while IN is active. In |

beyond the recommended conditions. Please |

this case, the unit must be held in the disabled |

consult the technical staff at Data Delay Devices |

state until the device is able to “clear” itself. This |

if your application has specific high-frequency |

is achieved by holding the EN/ signal high and |

requirements. |

the IN signal low for a time given by: |

|

TDISH = Ai * TINC |

Please note that the increment tolerances listed |

represent a design goal. Although most delay |

|

Violation of this constraint may, depending on |

increments will fall within tolerance, they are not |

guaranteed throughout the address range of the |

|

the history of the input signal, cause spurious |

unit. Monotonicity is, however, guaranteed over |

signals to appear on the OUT pin. The |

all addresses. |

A2-A0 |

A i-1 |

|

Ai |

TAENS |

|

TOAX |

TAIS |

EN/ |

|

|

|

TENIS |

PWIN |

|

TDISH |

IN |

|

|

|

TDA |

PWOUT |

|

TDISO |

OUT

TSKEW

TSKEW

OUT/

Figure 1: Timing Diagram

Doc #97001 |

DATA DELAY DEVICES, INC. |

2 |

1/10/97 |

Tel: 973-773-2299 Fax: 973-773-9672 http://www.datadelay.com |

Loading...

Loading...