Page 1

A

B

C

D

E

MODEL NAME :

1 1

PCB NO :

BOM P/N :

LA-9331P

4619KL31L01

RANGER 17

Compal Confidential

2 2

RANGER 17

Schematic Document

Rev: X00

3 3

2012-06-22

@ : Nopop Component

4 4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Cover Sheet

Size Document Number Rev

Custom

LA-9331P

D

Date: Sheet of

E

1 61Friday, June 22, 2012

0.1

Page 2

A

B

C

D

E

eDP to LVDS

RTD2136

P.37

eDP deMux

PS8338

FFS

P.28

HDMI

Intel

Haswell

4-lane eDP

LNG3DMTR

P.46

Fan Control

EMC1412

P.51

CPU XDP

Conn.

P.7

P.30

LVDS Mux

PI3LVD1012

eDP MUX

PS8321

P.38

P.29

LVDS Conn.

eDP Conn.

1 1

P.39 P.39

P.30

LVDS Mux

PI3LVD1012

eDP MUX

PS8321

Processor

DP/HDMI

LVDS to DP SW

STDP4028

HDMI to LVDS SW

STDP6038

HDMI Redriver

HDMI 1.3 Input

HDMI 1.4a Output

2 2

Conn.

miniDP Conn.

Mini Card #1(Half)

WLAN/WiMax

BT4.0+LE/WiGig

DMC

P.32

DP Redriver

P.27

P.48

PS8330

HDMI Redriver

PS121

PS121

HDMI SW

TS3DV421

P.35

L

VDS Mux

PI3LVD1012

P.34

HDMI MUX

P.33 P.33

P.32

P.27

PS8271

HDMI MUX

.36

P

PS8271

P.31

P.36

Display MiniCard

P.48

3 3

RJ45 Conn.

USB3.0 Daughter Board

P.50

9 in 1 Conn.

Card Reader Board

LAN(GbE)

E2201 Killer

Card Reader

RTS5209

P.41

P.50

SPI ROM

RTC conn.

Power On/Off CKT.

4 4

DC/DC Interface CKT.

Power Circuit DC/DC

P.54, 55, 56, 57, 58, 59, 60, 61

P.52

53

P.

A

8MB

ENE KC3810

B

eDP

LVDS

HDMI

DP1.2

DP/HDMI

P.20

P.40

VPK MCU

VPK Daughter Board

MXM III

Conn.

P.26

USB2.0

PCI-E 2.0

USB2.0

PCI-E 2.0

PCI-E 2.0

PCI-E 2.0

Int.KBD

PEGx16

SPI

Gen 3

4

C 47W/57W

Scoket G3

rPGA-947

P.6, 7, 8, 9, 10, 11, 12

DMI x4

100MHz

5GT/s

Intel

Lynx Point

PCH

HM87

BGA 695 Balls

P.17, 18, 19, 20, 21, 22, 23, 24, 25

LPC Bus

ENE KB9012

ouch Pad

T

P.50

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

C

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

Memory Bus DDRIII

Dual Channel

1.35V DDRIII 1600 MHz

USB3.0

USB 2.0

USB3.0

USB 2.0

USB3.0

USB 2.0

USB3.0

USB 2.0

204pin DDRIII SO-DIMM x4

BANK 0, 1, 2, 3

USB3.0 Rediver

USB3.0 Rediver

USB3.0 Rediver

USB3.0 Rediver

P.49

PS8713

P.49

PS8713

PS8713

PS8713

USB3.0 Daughter Board

USB2.0

USB2.0

USB2.0

USB2.0

SATA 3.0

SATA 3.0

SATA 3.0

SATA Rediver

PS8520BT

SATA Rediver

PS8520BT

SATA Rediver

PS8520BT

P.46

P.47

P.47

HD Audio

P.40

Audio Codec

ALC3661

TI

TPA3113D2

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

D

P.13, 14, 15, 16

USB 3.0/USB 2.0 Conn.

( USB Charger Port )

USB 3.0/USB 2.0 Conn.

P.49

P.49

USB 3.0/USB 2.0 Conn.

USB 3.0/USB 2.0 Conn.

P.50

with eDP Panel

Digital Camera

Digital Camera

AlienFX/ELC

3D IR

HDD Conn. 1

HDD Conn. 2

HDD Conn. 3

In ODD Bay (In place of ODD)

ODD Conn.

Mini Card #3(Full)SATA 3.0

mSATA

Combo Jack

( iPhone & Nokia compatible)

Headphone Jack

Headphone Jack

P.42

P.43

Array Mics

Array Mics

Int. Speaker (2.5W*4)

Title

Size Document Number Rev

Custom

Date: Sheet of

P.30

54

P.

P.45,46

P.52

P.46

P.46

P.47

P.47

P.47

P.42

P.42

P.42

P.30

P.39

P.43

Block Diagram

LA-9331P

with LVDS Panel

Camera with eDP Panel

Camera with LVDS Panel

E

2 61Friday, June 22, 2012

0.1

Page 3

A

B

C

D

E

Compal Confidential

Project Code : VAS00

File Name : LA-9331P

1 1

LS-9335P

POWER BUTTON/B

on/off SW

Led x 2

L

S-9336P

INDICATOR/B

Led-HDD

2 2

3 3

Led-Wireless

Led-CapsLock

To M/B

Hot Bar

FFC

6 pin

Lid

Tron Light

FFC

20 pin

LS-9337P

CardReader /B

Card Slot

KSI/KSO

30 pin

VPK Keyboard

40 pin

Backlight / 8 Pressure-sense Analog Signals

To USB30/B

FFC

30 pin

22 pin

HDD2 conn.

LS-9338P

VPK Daughter/B

VPK MCU MAX7313

FFC

16 pin

Touch Pad

4 pin

FFC

FFC

60 pin

PWM

Key Pad

22 pin

HDD1 conn.

Wire

12pin

6 pin

10 pin

Hot Key

Hot Bar

LS-9334P

LOGO /B

Led x 2

6pin

Hot Bar Hot Bar

LS-9333P LS-9331P LS-9332P

Alien head badge/B Alien Slits-L Light/BAlien Slits-R Light/B

Led x 2Led x 2 Led x 2

L R

Wire

6pin

LS-933BP

Tron L/B

Led x 1

4 4

Wire

10pin

To M/B

Wire

6pin

LS-933CP

Tron R/B

Led x 1

50pin

B To B conn.

WireWireWire

6pin6pin

44 pin

Coaxial/Wire Combo

20 pin

LF-XXXXP

FPC

50pin

B To B conn.

LA-9331P M/B

Camera

LCD Panel

HDD3ODD

HDD in ODD Bay Cable

RJ45

USB3.0

USB3.0

LS-9339P

USB30 /B

A

LS-933DP

Tron FL/B

Led x 1

LS-933EP

Tron FR/B

Led x 1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

E

3 61Friday, June 22, 2012

0.1

Page 4

A

+1.35V

+1.05V

ON

OFF

OFF

Issued Date

USB 3.0 PORT

1

2

4

5

6

+5VS

+3VS

+1.5VS

+1.05VS

+0.675VS

+3VMXM

+5VMXM

+VCC_CORE

+1.35V_CPU_VDDQ

ONON

OFF

OFF

DESTINATION

D1

HD

HDD2

ODD

mSATA

MINI CARD-1 WLAN

MINI CARD-2 DMC

2012/06/22 2013/06/21

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

100K +/- 5%Ra

0

1

2

3

4

5

6

7 NC

Rb V min

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0 0 V

AD_BID

0.168 V

0.375 V 0.503 V

0.634 V

0.958 V

1.372 V

1.851 V

2.433 V

V typ

AD_BID

0 V 0.155 V

0.250 V

0.819 V

1.185 V

1.650 V

2.200 V

3.300 V

V

AD_BID

0.362 V

0.621 V

0.945 V

1.359 V

1.838 V

2.420 V

3.300 V

max

EC AD3

0x00-0x0C

0x0D-0x1C

0x1D-0x30

0x31-0x49

0x4A-0x69

0x6A-0x8E

0x8F-0xBB

0xBC-0xFF

POWER STATES

RUN

Signal

State

S0 (Full ON) / M0

S5 (SOFT OFF) / M-OFF

SLP

S3#

HIGH

LOW HIGH

LOW

SLP

SLP

S4#

HIGH ON

LOW LOW LOW LOW ON

S5#

HIGH

S4

STATE#

HIGHHIGH

HIGH LOW ONS3 (Suspend to RAM) / M-OFF

LOW

SLP

M#

HIGH

LOW ONLOW LOWS4 (Suspend to DISK) / M-OFF

ALWAYS

PLANE

SUS

PLANE

ON

OFF

Symbol Note :

: means Digital Ground

1 1

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLK

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

CLKOUT_PCIE6

CLKOUT_PCIE7

CLKOUT_PEG_A

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SML0CLK PCH

PCH_SML0DATA

PCH_SML1CL K

PCH_SML1DA TA

MEM_SMBCLK

MEM_SMBDAT A

KB9012

KB9012

PCH

PCH

DMC

WLAN BATT DIMM

V

: means Analog Ground

DESTINATIONDIFFERENTIAL

MINI CARD-1 WLAN

MINI CARD-2 DMC

10/100/1G LAN

CARD READER

None

None

None

one

N

MXM

V

V

FLEX CLOCKS DESTINATION

CLKOUTFLEX0

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

Thermal

4028

Sensor

V

V

2136

FFS MXM

V

V

PLANE

ON ON

OFFOFF OFF

CLKOUT

PCI0

PCI1

PCI2

PCI3

PCI4

VPK MCU

VV

CLOCKS

OFFOFFON

OFFOFF

PCH_LOOPBACK

EC

80port debug card

None

None

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PM TABLE

power

plane

State

S0 ON

S3

S5 S4/AC

S5 S4/AC don't exist

None

None

None

None

DESTINATION

XDP

Charger6038

TP mSATA

V

V

V

V V

PCB Revision

0.1 (SSI)

0.2 (PT)

0.3 (ST)

0.4 (QT)

1.0 (MP)

+5VALW

+3VALW

+3VLP

+3V_PCH

ON OFF

ON

OFF

SATAIII

SATA0

SATA1

SATA2

SATA3

SATA4/PCIE LANE1

SATA5/PCIE LANE2

Link

Security Classification

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

A

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

Connetion

JUSB1 (Left side)

JUSB2 (Left side)

NA3

NA

JUSB3 (Right side)

JUSB4 (Right side)

Compal Secret Data

Deciphered Date

USB2.0

PCI EXPRESS

Lane 1/USB3.0 Port 3

Lane 2/USB3.0 Port 4

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

USB PORT#0DESTINATION

JUSB1(USB3.0 P1)

JUSB2(USB3.0 P2)

1

JUSB3(USB3.0 P5)

2

JUSB4(USB3.0 P6)

3

JMINI1 (WLAN)

4

JMINI2 (DMC)

5

6

AlienFX/ELC

IR SENSOR

7

No

8

9

10

11

12

13

ne

None

None

e

DP CAMERA

LVDS CAMERA

PK K/B

V

DESTINATION

None

None

10/100/1G LAN

CARD READER

None

None

None

None

Compal Electronics, Inc.

Title

Notes List

Size Document Number Rev

Custom

LA-9331P

Date: Sheet of

4 61Friday, June 22, 2012

0.1

Page 5

5

SMBUS Address [TBD]

R10

PCH

D D

U11

U8

R7

MEM_SMBCLK

MEM_SMBDATA

SML0CLK

SML0DATA

N11K6

SML1CLK

SML1DATA

+3VS

SCL2

SDA2

QH9B

EC_SMB_CK2

EC_SMB_DA2

2.2K

+3VS

2.2K

79

80

EC_SMB_CK2

EC_SMB_DA2

0 Ω

0 Ω

QH9A

C C

KBC

B B

KB9012

2.2K

2.2K

77

SCL1

SDA1

A A

EC_SMB_CK1

78 EC_SMB_DA1

EC_SMB_CK2_R

EC_SMB_DA2_R

0 Ω

0 Ω

+3VALW_EC

4

2K

2.

2.2K

2.2K

2.2K

2.2K

2.2K

+3VS

+3V_MXM

+3V_PCH

+3V_PCH

+3V_PCH

QV2B

CSCL

CSDA

QV2A

22 Ω

22 Ω

VPK_SMB_CK2

VPK_SMB_DA2

QV8

QV6

100 Ω

100 Ω

+3VS

0 Ω

0 Ω

0 Ω

0 Ω

0 Ω0 Ω

CLK_SMB

DAT_SMB

QH9A

H9B

Q

4.7K

4.7K

CIICSCL

CIICSDA

EC_HDMI_DAT_R

EC_HDMI_CLK_R

EC_HDMI_CLK

EC_HDMI_DAT

4.7K

4.7K

VGA_SMB_CK1

VGA_SMB_DA1

MXM_CURI2C_CLK

MXM_CURI2C_DATA

+DVCC33

4.7K

4.7K

+3V_MXM

3

2.2K

2.2K

111

RTD2136S

112

+3VS

LVDS transfer DP

B14

STDP4028

C13

HDMI IN

72

STDP6038

71

VPK

43

MSP430F5508

42

Thermal sensor

8

ADM1032

7

Thermal sensor

8

ADM1032

7

70

MXM1 CONN

68

MXM Current Monitor

5

HPA00900

6

4

5

BATT CONN

+3VS

PCH_SMBCLK

PCH_SMBDATA

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [0FFFFh to 0FF80h]

MXM FAN CONTROL

SMBUS Address [100_1100]

SYSTEM FAN CONTROL

SMBUS Address [100_1100]

SMBUS Address []

SMBUS Address []

SMBUS Address []

2

0 Ω

0 Ω

DDR_XDP_SMBCLK_R1

DDR_XDP_SMBDAT_R1

0 Ω

MINI2_SMBCLK

MINI2_SMBDATA

0 Ω

202

200

202

200

202

200

202

200

4

6

30

32

30

32

15

16

DIMM1

DIMM2

DIMM3

DIMM4

53

51

G sensor

LNG3DM

Touch pad

XDP

mSATA

DMC

1

SMBUS Address [A2]

SMBUS Address [A6]

SMBUS Address [A0]

SMBUS Address [A4]

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

0 Ω

0 Ω

PU700

5

4

SMBUS Address [000_1001]

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

2012/06/22 2013/06/21

3

Compal Secret Data

Deciphered Date

Custom

2

Compal Electronics, Inc.

Title

SMBus block diagram

Size Document Number Rev

LA-9331P

Date: Sheet of

1

5 61Friday, June 22, 2012

0.1

Page 6

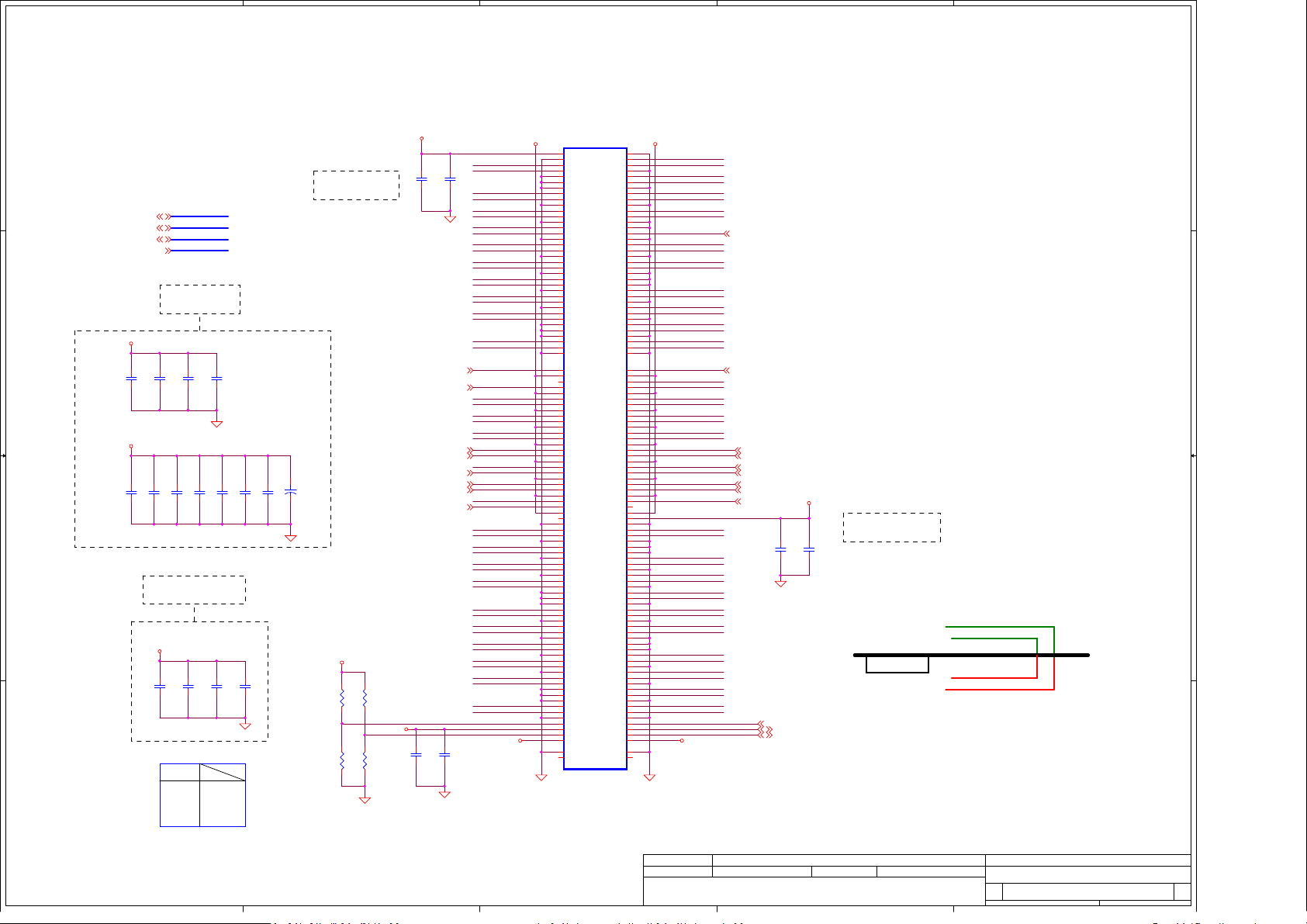

5

4

3

2

1

D D

Haswell rPGA EDS

JCPU1A

PEG_RCOMP

DMI_CRX_PTX_N0<17>

DMI_CRX_PTX_N1<17>

DMI_CRX_PTX_N2<17>

DMI_CRX_PTX_N3<17>

DMI_CRX_PTX_P0<17>

DMI_CRX_PTX_P1<17>

DMI_CRX_PTX_P2<17>

DMI_CRX_PTX_P3<17>

DMI_CTX_PRX_N0<17>

DMI_CTX_PRX_N1<17>

DMI_CTX_PRX_N2<17>

C C

FDI_CSYNC<17>

FDI_INT<17>

B B

DMI_CTX_PRX_N3<17>

DMI_CTX_PRX_P0<17>

DMI_CTX_PRX_P1<17>

DMI_CTX_PRX_P2<17>

DMI_CTX_PRX_P3<17>

RC3 0_0402_5%~D

RC87 0_0402_5%~D

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

12

12

FDI_CSYNC_R

FDI_INT_R

D21

DMI_RXN_0

C21

DMI_RXN_1

B21

DMI_RXN_2

A21

DMI_RXN_3

D20

DMI_RXP_0

C20

DMI_RXP_1

B20

DMI_RXP_2

A20

DMI_RXP_3

D18

DMI_TXN_0

C17

DMI_TXN_1

B17

DMI_TXN_2

A17

DMI_TXN_3

D17

DMI_TXP_0

C18

DMI_TXP_1

B18

DMI_TXP_2

A18

DMI_TXP_3

H29

FDI_CSYNC

J29

FDI_INT

IN

TEL_HASWELL_HAS WELL

CONN@

DMI FDI

1 OF 9

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

PEG_COMP

CAD Note:

Trace width=12 mils ,Spacing=15mil

Max length= 400 mils.

PEG_COMP

E23

PEG_GTX_C_HRX_N0

M29

PEG_GTX_C_HRX_N1

K28

PEG_GTX_C_HRX_N2

M31

PEG_GTX_C_HRX_N3

L30

PEG_GTX_C_HRX_N4

M33

PEG_GTX_C_HRX_N5

L32

PEG_GTX_C_HRX_N6

M35

PEG_GTX_C_HRX_N7

L34

PEG_GTX_C_HRX_N8

E29

PEG_GTX_C_HRX_N9

D28

PEG_GTX_C_HRX_N10

E31

PEG_GTX_C_HRX_N11

D30

PEG_GTX_C_HRX_N12

E35

PEG_GTX_C_HRX_N13

D34

PEG_GTX_C_HRX_N14

E33

PEG_GTX_C_HRX_N15

E32

PEG_GTX_C_HRX_P0

L29

PEG_GTX_C_HRX_P1

L28

PEG_GTX_C_HRX_P2

L31

PEG_GTX_C_HRX_P3

K30

PEG_GTX_C_HRX_P4

L33

PEG_GTX_C_HRX_P5

K32

PEG_GTX_C_HRX_P6

L35

PEG_GTX_C_HRX_P7

K34

PEG_GTX_C_HRX_P8

F29

PEG_GTX_C_HRX_P9

E28

PEG_GTX_C_HRX_P10

F31

PEG_GTX_C_HRX_P11

E30

PEG_GTX_C_HRX_P12

F35

PEG_GTX_C_HRX_P13

E34

PEG_GTX_C_HRX_P14

F33

PEG_GTX_C_HRX_P15

D32

PEG_HTX_GRX_N0

H35

PEG_HTX_GRX_N1

H34

PEG_HTX_GRX_N2

J33

PEG_HTX_GRX_N3

H32

PEG_HTX_GRX_N4

J31

PEG_HTX_GRX_N5

G30

PEG_HTX_GRX_N6

C33

PEG_HTX_GRX_N7

B32

PEG_HTX_GRX_N8

B31

PEG_HTX_GRX_N9

A30

PEG_HTX_GRX_N10

B29

PEG_HTX_GRX_N11

A28

PEG_HTX_GRX_N12

B27

PEG_HTX_GRX_N13

A26

PEG_HTX_GRX_N14

B25

PEG_HTX_GRX_N15

A24

PEG_HTX_GRX_P0

J35

PEG_HTX_GRX_P1

G34

PEG_HTX_GRX_P2

H33

PEG_HTX_GRX_P3

G32

PEG_HTX_GRX_P4

H31

PEG_HTX_GRX_P5

H30

PEG_HTX_GRX_P6

B33

PEG_HTX_GRX_P7

A32

PEG_HTX_GRX_P8

C31

PEG_HTX_GRX_P9

B30

PEG_HTX_GRX_P10

C29

PEG_HTX_GRX_P11

B28

PEG_HTX_GRX_P12

C27

PEG_HTX_GRX_P13

B26

PEG_HTX_GRX_P14

C25

PEG_HTX_GRX_P15

B24

Near MXM Connector

+VCOMP_OUT

12

RC224.9_0402_1%~D

CC1 0.22U_0402_16V7K~D

1 2

CC2 0.22U_0402_16V7K~D

1 2

CC3 0.22U_0402_16V7K~D

1 2

CC4 0.22U_0402_16V7K~D

1 2

CC5 0.22U_0402_16V7K~D

1 2

CC13 0.22U_0402_16V7K~D

1 2

CC6 0.22U_0402_16V7K~D

1 2

CC7 0.22U_0402_16V7K~D

1 2

CC8 0.22U_0402_16V7K~D

1 2

CC9 0.22U_0402_16V7K~D

1 2

CC10 0.22U_0402_16V7K~D

1 2

CC11 0.22U_0402_16V7K~D

1 2

CC12 0.22U_0402_16V7K~D

1 2

CC14 0.22U_0402_16V7K~D

1 2

CC15 0.22U_0402_16V7K~D

1 2

CC16 0.22U_0402_16V7K~D

1 2

CC17 0.22U_0402_16V7K~D

1 2

CC18 0.22U_0402_16V7K~D

1 2

CC19 0.22U_0402_16V7K~D

1 2

CC20 0.22U_0402_16V7K~D

1 2

CC21 0.22U_0402_16V7K~D

1 2

CC22 0.22U_0402_16V7K~D

1 2

CC23 0.22U_0402_16V7K~D

1 2

CC24 0.22U_0402_16V7K~D

1 2

CC25 0.22U_0402_16V7K~D

1 2

CC26 0.22U_0402_16V7K~D

1 2

CC27 0.22U_0402_16V7K~D

1 2

CC28 0.22U_0402_16V7K~D

1 2

CC29 0.22U_0402_16V7K~D

1 2

CC30 0.22U_0402_16V7K~D

1 2

CC31 0.22U_0402_16V7K~D

1 2

CC32 0.22U_0402_16V7K~D

1 2

CC33 0.22U_0402_16V7K~D

1 2

CC34 0.22U_0402_16V7K~D

1 2

CC35 0.22U_0402_16V7K~D

1 2

CC36 0.22U_0402_16V7K~D

1 2

CC37 0.22U_0402_16V7K~D

1 2

CC38 0.22U_0402_16V7K~D

1 2

CC39 0.22U_0402_16V7K~D

1 2

CC40 0.22U_0402_16V7K~D

1 2

CC41 0.22U_0402_16V7K~D

1 2

CC42 0.22U_0402_16V7K~D

1 2

CC43 0.22U_0402_16V7K~D

1 2

CC44 0.22U_0402_16V7K~D

1 2

CC45 0.22U_0402_16V7K~D

1 2

CC46 0.22U_0402_16V7K~D

1 2

CC47 0.22U_0402_16V7K~D

1 2

CC48 0.22U_0402_16V7K~D

1 2

CC49 0.22U_0402_16V7K~D

1 2

CC50 0.22U_0402_16V7K~D

1 2

CC51 0.22U_0402_16V7K~D

1 2

CC52 0.22U_0402_16V7K~D

1 2

CC53 0.22U_0402_16V7K~D

1 2

CC54 0.22U_0402_16V7K~D

1 2

CC55 0.22U_0402_16V7K~D

1 2

CC56 0.22U_0402_16V7K~D

1 2

CC57 0.22U_0402_16V7K~D

1 2

CC58 0.22U_0402_16V7K~D

1 2

CC59 0.22U_0402_16V7K~D

1 2

CC60 0.22U_0402_16V7K~D

1 2

CC61 0.22U_0402_16V7K~D

1 2

CC62 0.22U_0402_16V7K~D

1 2

CC63 0.22U_0402_16V7K~D

1 2

CC64 0.22U_0402_16V7K~D

1 2

PEG_GTX_HRX_N0

PEG_GTX_HRX_N1

PEG_GTX_HRX_N2

PEG_GTX_HRX_N3

PEG_GTX_HRX_N4

PEG_GTX_HRX_N5

PEG_GTX_HRX_N6

PEG_GTX_HRX_N7

PEG_GTX_HRX_N8

PEG_GTX_HRX_N9

PEG_GTX_HRX_N10

PEG_GTX_HRX_N11

PEG_GTX_HRX_N12

PEG_GTX_HRX_N13

PEG_GTX_HRX_N14

PEG_GTX_HRX_N15

PEG_GTX_HRX_P0

PEG_GTX_HRX_P1

PEG_GTX_HRX_P2

PEG_GTX_HRX_P3

PEG_GTX_HRX_P4

PEG_GTX_HRX_P5

PEG_GTX_HRX_P6

PEG_GTX_HRX_P7

PEG_GTX_HRX_P8

PEG_GTX_HRX_P9

PEG_GTX_HRX_P10

PEG_GTX_HRX_P11

PEG_GTX_HRX_P12

PEG_GTX_HRX_P13

PEG_GTX_HRX_P14

PEG_GTX_HRX_P15

PEG_HTX_C_GRX_N0

PEG_HTX_C_GRX_N1

PEG_HTX_C_GRX_N2

PEG_HTX_C_GRX_N3

PEG_HTX_C_GRX_N4

PEG_HTX_C_GRX_N5

PEG_HTX_C_GRX_N6

PEG_HTX_C_GRX_N7

PEG_HTX_C_GRX_N8

PEG_HTX_C_GRX_N9

PEG_HTX_C_GRX_N10

PEG_HTX_C_GRX_N11

PEG_HTX_C_GRX_N12

PEG_HTX_C_GRX_N13

PEG_HTX_C_GRX_N14

PEG_HTX_C_GRX_N15

PEG_HTX_C_GRX_P0

PEG_HTX_C_GRX_P1

PEG_HTX_C_GRX_P2

PEG_HTX_C_GRX_P3

PEG_HTX_C_GRX_P4

PEG_HTX_C_GRX_P5

PEG_HTX_C_GRX_P6

PEG_HTX_C_GRX_P7

PEG_HTX_C_GRX_P8

PEG_HTX_C_GRX_P9

PEG_HTX_C_GRX_P10

PEG_HTX_C_GRX_P11

PEG_HTX_C_GRX_P12

PEG_HTX_C_GRX_P13

PEG_HTX_C_GRX_P14

PEG_HTX_C_GRX_P15

PEG_GTX_HRX_P[0..15] <29>

PEG_GTX_HRX_N[0..15] <29>

PEG_HTX_C_GRX_P[0..15] <29>

PEG_HTX_C_GRX_N[0..15] <29>

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

CPU (1/7) DMI,PEG

ze Document Number Rev

Si

Custom

LA-9331P

2

Date: Sheet of

1

6 61Friday, June 22, 2012

0.1

Page 7

5

4

3

2

1

SM_DRAMPWROK with DDR Power Gating Topology

+3V_PCH

100K_0402_5%~D

+3V_PCH

CLK_CPU_SSC_DPLL#<18>

CLK_CPU_SSC_DPLL<18>

UC1

NC

A

GND3Y

12

H_THERMTRIP#

H_CATERR#

H_PROCHOT#

H_PROCHOT#<43,63>

H_THERMTRIP#<21>

H_PM_SYNC<17>

H_CPUPWRGD<21>

CLK_CPU_DPLL#<18>

CLK_CPU_DPLL<18>

CLK_CPU_DMI#<18>

CLK_CPU_DMI<18>

RC2010K_0402_5%~D @

RC2110K_0402_5%~D @

VCC

12

+VCCIO_OUT

+3VS

5

PCH_PLTRST#_BUF

4

@

RC89

RUN_ON_CPU1.5VS3#<10,56>

1

2

CC156

1 2

0.1U_0402_25V6K~D

5

1

P

B

4

O

2

A

G

UC2

74AHC1G09GW_TSSOP5~D

3

12

RC94 0_0402_5%~D

@

RC57 56_0402_5%~D

1 2

RC134 0_0402_5%~D

1 2

place RC134 near CPU

1 2

RC25 0_0402_5%~D

RC51 0_0402_5%~D

RC52 0_0402_5%~D

RC43 0_0402_5%~D

RC22 0_0402_5%~D

RC15 0_0402_5%~D

RC13 0_0402_5%~D

0.1U_0402_25V6K~D

+1.05VS

1K_0402_1%~D

12

CC140

20K_0402_5%~D

12

12

12

12

12

12

12

RC17

RC10 43_0402_5%~D

RC11

D D

SYS_PWROK<17>

PM_DRAM_PWRGD<17>

C C

B B

SSC CLOCK TERMINATION, IF NOT USED, stuff RC20,RC21

RC88 0_0402_5%~D

+3V_PCH

RC18 200_0402_1%~D

+VCCIO_OUT

1 2

RC136 56_0402_5%~D@

1 2

RC128 49.9_0402_1%~D@

1 2

RC44 62_0402_5%~D

CPU_SSC_DPLL

CPU_SSC_DPLL#

1 2

1 2

1 2

Buffered reset to CPU

1

PLT_RST#<17,43,44,51,53>

2

SN74LVC1G07DCKR_SC70-5~D

RUNPWROK_AND

2

H_PECI<21,43>

1 2

CPU_PLTRST#< 21>

+1.35V_CPU_VDDQ

39_0402_5%~D

@

RC64

SSM3K7002FU_SC70-3~D

1 2

13

D

@

QC1

G

S

H_CATERR#

H_PECI

T66PAD~D @

H_PROCHOT#_R

H_THERMTRIP#_R

H_PM_SYNC

VCCPWRGOOD_0_R

PM_DRAM_PWRGD_CPU

CPU_PLTRST#_R

CPU_DPLL#

CPU_DPLL

CPU_SSC_DPLL#

CPU_SSC_DPLL

CPU_DMI#

CPU_DMI

1.8K_0402_1%

12

RC16

12

RC28 0_0402_5%~D

3.3K_0402_1%~D

12

RC14

AP32

SKTOCC

AN32

CATERR

AR27

PECI

AK31

RSVD

AM30

PROCHOT

AM35

THERMTRIP

AT28

PM_SYNC

AL34

PWRGOO D

AC10

SM_DRAMPW ROK

AT26

PLTRSTIN

G28

DPLL_REF _CLKN

H28

DPLL_REF _CLKP

F27

SSC_DPLL _REF_CLKN

E27

SSC_DPLL _REF_CLKP

D26

BCLKN

E26

BCLKP

CONN@

RC54 0_0402_5%~D@

12

RC53 0_0402_5%~D

12

PM_DRAM_PWRGD_CPU

Haswell rPGA EDS

JCPU1B

MISC

THERMAL

PWR

INTEL_HASWELL_HASWELL

CPU_PLTRST#_R

SM_RCOMP_ 0

SM_RCOMP_ 1

SM_RCOMP_ 2

DDR3

SM_DRAMRST

PRDY

PREQ

TCK

TMS

TRST

JTAG

TDI

TDO

DBR

BPM_N_0

BPM_N_1

CLOCK

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

2 OF 9

CAD Note:

Avoid stub in the PWRGD path

while placing resistors RC25 & RC130

+3V_PCH

1 2

RC125 1K_0402_1%~D@

PBTN_OUT#<17,43>

CPU_PWR_DEBUG<10>

PCH_SMBDATA<12,13,14,15,19,49,50,51,53>

PCH_SMBCLK<12,13,14,15,19,49,50,51,53>

SM_RCOMP0

AP3

SM_RCOMP1

AR3

SM_RCOMP2

AP2

DDR3_DRAMRST#_CPU

AN3

XDP_PRDY#

AR29

XDP_PREQ#

AT29

XDP_TCLK

AM34

XDP_TMS

AN33

XDP_TRST#

AM33

XDP_TDI_R

AM31

XDP_TDO_R

AL33

XDP_DBRESET#_R

AP33

XDP_OBS0_R

AR30

XDP_OBS1_R

AN31

XDP_OBS2_R

AN29

XDP_OBS3_R

AP31

XDP_OBS4_R

AP30

XDP_OBS5_R

AN28

XDP_OBS6_R

AP29

XDP_OBS7_R

AP28

For ESD concern, please put near CPU

VCCPWRGOOD_0_R

+VCCIO_OUT

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

1

1

CC65

CC66

2

2

Place near JXDP1

SYS_PWROK_XDP

RC5 need to close to JCPU1

H_CPUPWRGD H_CPUPWRGD_XDP

RC5 1K_0402_1%~D

1 2

RC6 0_0402_5%~D

1 2

RC8 0_0402_5%~D

1 2

RC12 0_0402_5%~D

IMVP_PWRGD<17,43,62>

RC50 0_0402_5%~D

RC36 0_0402_5%~D

RC46 0_0402_5%~D

RC47 0_0402_5%~D

RC48 0_0402_5%~D

RC23 0_0402_5%~D

RC24 0_0402_5%~D

RC26 0_0402_5%~D

RC30 0_0402_5%~D

RC31 0_0402_5%~D

RC33 0_0402_5%~D

RC34 0_0402_5%~D

RC37 0_0402_5%~D

RC40 0_0402_5%~D

RC38 0_0402_5%~D

RC39 0_0402_5%~D

10K_0402_5%~D

12

RC135

1 2

RC126 0_0402_5%~D

1 2

RC127 0_0402_5%~D

1 2

DDR3_DRAMRST#_CPU <12>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CRB Rev 0.7 is depop

CFG0<9>

CFG1<9>

CFG2<9>

CFG3<9>

CFG4<9>

CFG5<9>

CFG6<9>

CFG7<9>

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCLK_R

XDP_TMS_R

XDP_TRST#_R

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_OBS0

XDP_OBS1

DDR3 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

+VCCIO_OUT +VCCIO_OUT

XDP_PREQ#_R

XDP_PRDY#_R

CFG0

CFG1

CFG2

CFG3

XDP_OBS0

XDP_OBS1

CFG4

CFG5

CFG6

CFG7

CFD_PWRBTN#_XDP

SYS_PWROK_XDP

DDR_XDP_SMBDAT_R1

DDR_XDP_SMBCLK_R1

XDP_TCLK_R

XDP_DBRESET# <17>

RC45 100_0402_1%~D

1 2

RC55 75_0402_1%~D

1 2

RC49 100_0402_1%~D

1 2

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A 0

11

OBSDATA_A 1

13

GND4

15

OBSDATA_A 2

17

OBSDATA_A 3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B 0

29

OBSDATA_B 1

31

GND10

33

OBSDATA_B 2

35

OBSDATA_B 3

37

GND12

39

PWRGOO D/HOOK0

41

HOOK1

43

VCC_OBS_ AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK 4

ITPCLK#/HO OK5

VCC_OBS_ CD

RESET#/HOO K6

DBR#/HOOK 7

GND15

TD0

TRST#

TDI

TMS

GND17

CONN@

CRB Rev 0.7 no pull up

2

CFG17

4

CFG16

6

8

CFG8

10

CFG9

12

14

CFG10

16

CFG11

18

20

CFG19

22

CFG18

24

26

CFG12

28

CFG13

30

32

CFG14

34

CFG15

36

38

CLK_XDP

40

CLK_XDP#

42

44

XDP_RST#_RCPU_PWR_DEBUG_R

46

XDP_DBRESET#

48

50

XDP_TDO

52

XDP_TRST#_R

54

XDP_TDI

56

XDP_TMS_R

58

60

PU/PD for JTAG signals

XDP_DBRESET#_R

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO_R

XDP_TCLK

XDP_TRST#

CFG17 <9>

CFG16 <9>

CFG8 <9>

CFG9 <9>

CFG10 <9>

CFG11 <9>

CFG19 <9>

CFG18 <9>

CFG12 <9>

CFG13 <9>

CFG14 <9>

CFG15 <9>

RC144 0_0402_5%~D

1 2

RC145 0_0402_5%~D

1 2

CPU_PLTRST#_R

12

RC9 1K_0402_1%~D

RC19 1K_0402_1%~D

12

RC27 51_0402_1%~D@

12

RC29 51_0402_1%~D

12

RC32 51_0402_1%~D@

12

RC35 51_0402_1%~D

12

RC42 51_0402_1%~D

12

RC41 51_0402_1%~D

12

+1.05VS

+3VS

CLK_CPU_ITP <18>

CLK_CPU_ITP# <18>

CAD Note:

PLACE PULL-UP RESISTOR WITHIN 2 INCH OF THE CPU

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

2

Compal Electronics, Inc.

Title

CPU (2/7) PM,XDP,CLK

ze Document Number Rev

Si

Custom

LA-9331P

Date: Sheet of

1

7 61Friday, June 22, 2012

0.1

Page 8

5

4

3

2

1

D D

C C

B B

A A

DDR_A_D[0..63]<12,14>

+V_SM_VREF

+DIMM0_1_VREF

+DIMM0_1_CA

+DIMM0_1_CA +DIMM0_1_VREF

1 2

1

CC137

0.022U_0402_25V7K~D

24.9_0402_1%

RC150

2

12

5

RC147

0_0402_5%

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+1.35V

1K_0402_1%~D

12

1K_0402_1%~D

12

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AM9

AN9

AM8

AN8

AR9

AT9

AR8

AT8

AJ9

AK9

AJ6

AK6

AJ10

AK10

AJ7

AK7

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

D12

B11

A11

E11

D11

B12

A12

AM3

F16

F13

RC96

+DIMM0_1_CA_CPU

RC82

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

CONN@

JCPU1C

3 OF 9

Haswell rPGA EDS

RSVD_AC7

SA_CK_N_0

SA_CK_P_0

SA_CKE_0

SA_CK_N_1

SA_CK_P_1

SA_CKE_1

SA_CK_N_2

SA_CK_P_2

SA_CKE_2

SA_CK_N_3

SA_CK_P_3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

RSVD_V10

SA_RAS

SA_WE

SA_CAS

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

TEL_HASWELL_HAS WELL

IN

CC138

0.022U_0402_25V7K~D

RC151

24.9_0402_1%

4

Haswell rPGA EDS

SB_CKN0

SB_CK0

SB_CKE_0

SB_CKN1

SB_CK1

SB_CKE_1

SB_CKN2

SB_CK2

SB_CKE_2

SB_CKN3

SB_CK3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

SB_RAS

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

TEL_HASWELL_HAS WELL

2

RSVD

RSVD

SB_WE

AG8

Y4

AA4

AF10

Y3

AA3

AG10

Y2

AA2

AG9

Y1

AA1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

R7

P8

AA9

R10

R6

P6

P7

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

4 OF 9

JCPU1D

I

N

0.022U_0402_25V7K~D

Issued Date

3

DDR_B_D[0..63]<13,15>

+V_SM_VREF

CC139

RC149

24.9_0402_1%

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

RC146

1 2

0_0402_5%

1

2

12

2012/06/22 2013/06/21

AR18

SB_DQ_0

AT18

SB_DQ_1

AM17

SB_DQ_2

AM18

SB_DQ_3

AR17

SB_DQ_4

AT17

SB_DQ_5

AN17

SB_DQ_6

AN18

SB_DQ_7

AT12

SB_DQ_8

AR12

SB_DQ_9

AN12

SB_DQ_10

AM11

SB_DQ_11

AT11

SB_DQ_12

AR11

SB_DQ_13

AM12

SB_DQ_14

AN11

SB_DQ_15

AR5

SB_DQ_16

AR6

SB_DQ_17

AM5

SB_DQ_18

AM6

SB_DQ_19

AT5

SB_DQ_20

AT6

SB_DQ_21

AN5

SB_DQ_22

AN6

SB_DQ_23

AJ4

SB_DQ_24

AK4

SB_DQ_25

AJ1

SB_DQ_26

AJ2

SB_DQ_27

AM1

SB_DQ_28

AN1

SB_DQ_29

AK2

SB_DQ_30

AK1

SB_DQ_31

L2

SB_DQ_32

M2

SB_DQ_33

L4

SB_DQ_34

M4

SB_DQ_35

L1

SB_DQ_36

M1

SB_DQ_37

L5

SB_DQ_38

M5

SB_DQ_39

G7

SB_DQ_40

J8

SB_DQ_41

G8

SB_DQ_42

G9

SB_DQ_43

J7

SB_DQ_44

J9

SB_DQ_45

G10

SB_DQ_46

J10

SB_DQ_47

A8

SB_DQ_48

B8

SB_DQ_49

A9

SB_DQ_50

B9

SB_DQ_51

D8

SB_DQ_52

E8

SB_DQ_53

D9

SB_DQ_54

E9

SB_DQ_55

E15

SB_DQ_56

D15

SB_DQ_57

A15

SB_DQ_58

B15

SB_DQ_59

E14

SB_DQ_60

D14

SB_DQ_61

A14

SB_DQ_62

B14

SB_DQ_63

CONN@

+1.35V

1K_0402_1%~D

12

RC86

+V_SM_VREF_CNT

1K_0402_1%~D

12

RC78

Compal Secret Data

Deciphered Date

+1.35V

12

12

T67 PAD~D@

M_CLK_DDR#0 <14>

M_CLK_DDR0 <14>

DDR_CKE0_DIMMA <14>

M_CLK_DDR#1 <14>

M_CLK_DDR1 <14>

DDR_CKE1_DIMMA <14>

M_CLK_DDR#4 <12>

M_CLK_DDR4 <12>

DDR_CKE4_DIMMC <12>

M_CLK_DDR#5 <12> DDR_CKE6_DIMMD <13>

M_CLK_DDR5 <12>

DDR_CKE5_DIMMC <12>

DDR_CS0_DIMMA# <14>

DDR_CS1_DIMMA# <14>

DDR_CS4_DIMMC# <12>

DDR_CS5_DIMMC# <12>

M_ODT0 <14>

M_ODT1 <14>

M_ODT4 <12>

M_ODT5 <12>

DDR_A_BS0 <12,14>

DDR_A_BS1 <12,14>

DDR_A_BS2 <12,14>

DDR_A_RAS# <12,14>

DDR_A_WE# <12,14>

DDR_A_CAS# <12,14>

DDR_A_MA[0..15] <12,14>

DDR_A_DQS#[0..7] <12,14>

DDR_A_DQS[0..7] <12,14>

1K_0402_1%~D

RC95

+DIMM0_1_VREF_CPU

1K_0402_1%~D

RC81

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

AC7

M_CLK_DDR#0

U4

M_CLK_DDR0

V4

DDR_CKE0_DIMMA

AD9

M_CLK_DDR#1

U3

M_CLK_DDR1

V3

DDR_CKE1_DIMMA

AC9

M_CLK_DDR#4

U2

M_CLK_DDR4

V2

DDR_CKE4_DIMMC

AD8

M_CLK_DDR#5 DDR_CKE6_DIMMD

U1

M_CLK_DDR5

V1

DDR_CKE5_DIMMC

AC8

DDR_CS0_DIMMA#

M7

DDR_CS1_DIMMA#

L9

DDR_CS4_DIMMC#

M9

DDR_CS5_DIMMC#

M10

M_ODT0

M8

M_ODT1

L7

M_ODT4

L8

M_ODT5

L10

DDR_A_BS0

V5

DDR_A_BS1

U5

DDR_A_BS2

AD1

V10

DDR_A_RAS#

U6

DDR_A_WE#

U7

DDR_A_CAS#

U8

DDR_A_MA0

V8

DDR_A_MA1

AC6

DDR_A_MA2

V9

DDR_A_MA3

U9

DDR_A_MA4

AC5

DDR_A_MA5

AC4

DDR_A_MA6

AD6

DDR_A_MA7

AC3

DDR_A_MA8

AD5

DDR_A_MA9

AC2

DDR_A_MA10

V6

DDR_A_MA11

AC1

DDR_A_MA12

AD4

DDR_A_MA13

V7

DDR_A_MA14

AD3

DDR_A_MA15

AD2

DDR_A_DQS#0

AP15

DDR_A_DQS#1

AP8

DDR_A_DQS#2

AJ8

DDR_A_DQS#3

AF3

DDR_A_DQS#4

J3

DDR_A_DQS#5

E2

DDR_A_DQS#6

C5

DDR_A_DQS#7

C11

DDR_A_DQS0

AP14

DDR_A_DQS1

AP9

DDR_A_DQS2

AK8

DDR_A_DQS3

AG3

DDR_A_DQS4

H3

DDR_A_DQS5

E3

DDR_A_DQS6

C6

DDR_A_DQS7

C12

RC148

1 2

0_0402_5%

1

2

12

M_CLK_DDR#2

M_CLK_DDR2

DDR_CKE2_DIMMB

M_CLK_DDR#3

M_CLK_DDR3

DDR_CKE3_DIMMB

M_CLK_DDR#6

M_CLK_DDR6

M_CLK_DDR#7

M_CLK_DDR7

DDR_CKE7_DIMMD

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

DDR_CS6_DIMMD#

DDR_CS7_DIMMD#

M_ODT2

M_ODT3

M_ODT6

M_ODT7

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

Title

Size Document Number Rev

Custom

Date: Sheet of

T76 PAD~D@

M_CLK_DDR#2 <15>

M_CLK_DDR2 <15>

DDR_CKE2_DIMMB <15>

M_CLK_DDR#3 <15>

M_CLK_DDR3 <15>

DDR_CKE3_DIMMB <15>

M_CLK_DDR#6 <13>

M_CLK_DDR6 <13>

M_CLK_DDR#7 <13>

M_CLK_DDR7 <13>

DDR_CKE7_DIMMD <13>

DDR_CS2_DIMMB# <15>

DDR_CS3_DIMMB# <15>

DDR_CS6_DIMMD# <13>

DDR_CS7_DIMMD# <13>

M_ODT2 <15>

M_ODT3 <15>

M_ODT6 <13>

M_ODT7 <13>

DDR_B_BS0 <13,15>

DDR_B_BS1 <13,15>

DDR_B_BS2 <13,15>

DDR_B_RAS# <13,15>

DDR_B_WE# <13,15>

DDR_B_CAS# <13,15>

DDR_B_MA[0..15] <13,15>

DDR_B_DQS#[0..7] <13,15>

DDR_B_DQS[0..7] <13,15>

Compal Electronics, Inc.

CPU (3/7) DDRIII

LA-9331P

1

8 61Friday, June 22, 2012

0.1

Page 9

5

4

3

2

1

COMPENSATION PU FOR eDP

+VCOMP_OUT

EDP_COMP

D D

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

12

RC124.9_0402_1%~D

Haswell rPGA EDS

CPU_HDMI_N0<36>

CPU_HDMI_P0<36>

CPU_HDMI_N1<36>

CPU_HDMI_P1<36>

HDMI

C C

DMC

B B

CPU_HDMI_N2<36>

CPU_HDMI_P2<36>

CPU_HDMI_N3<36>

CPU_HDMI_P3<36>

CPU_DPD_DMC_N0<39>

CPU_DPD_DMC_P0<39>

CPU_DPD_DMC_N1<39>

CPU_DPD_DMC_P1<39>

CPU_DPD_DMC_N2<39>

CPU_DPD_DMC_P2<39>

CPU_DPD_DMC_N3<39>

CPU_DPD_DMC_P3<39>

CPU_HDMI_N0

CPU_HDMI_P0

CPU_HDMI_N1

CPU_HDMI_P1

CPU_HDMI_N2

CPU_HDMI_P2

CPU_HDMI_N3

CPU_HDMI_P3

CPU_DPD_DMC_N0

CPU_DPD_DMC_P0

CPU_DPD_DMC_N1

CPU_DPD_DMC_P1

CPU_DPD_DMC_N2

CPU_DPD_DMC_P2

CPU_DPD_DMC_N3

CPU_DPD_DMC_P3

T28

DDIB_TXBN_0

U28

DDIB_TXBP_0

T30

DDIB_TXBN_1

U30

DDIB_TXBP_1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

INTEL_HASWELL_HAS WELL

CONN@

JCPU1H

eDP

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

RSVD

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

DDI

8 OF 9

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

CPU_EDP_AUX#

CPU_EDP_AUX

EDP_HPD

EDP_COMP

CPU_EDP_N0

CPU_EDP_P0

CPU_EDP_N1

CPU_EDP_P1

CPU_EDP_N2

CPU_EDP_P2

CPU_EDP_N3

CPU_EDP_P3

T77PAD~D @

CPU_EDP_N0 <31>

CPU_EDP_P0 <31>

CPU_EDP_N1 <31>

CPU_EDP_P1 <31>

CPU_EDP_N2 <31>

CPU_EDP_P2 <31>

CPU_EDP_N3 <31>

CPU_EDP_P3 <31>

CPU_EDP_AUX# <31>

CPU_EDP_AUX < 31>

HPD INVERSION FOR EDP

CPU_EDP_HPD#<31>

100K_0402_5%~D

12

RC75

+VCCIO_OUT

2

G

12

10K_0402_5%~D

RC65

EDP_HPD

BSS138_SOT23~D

13

D

QC10

S

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

CPU (4/7) FDI,eDP,DDI

ze Document Number Rev

Si

Custom

LA-9331P

2

Date: Sheet of

1

9 61Friday, June 22, 2012

0.1

Page 10

5

4

3

2

1

CFG STRAPS for CPU

CFG2

D D

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

CFG2

definition matches socket pin map definition

0:Lane Reversed

Haswell rPGA EDS

T103PAD~D@

T80 PAD~D@

T78 PAD~D@

T110PAD~D@

T81 PAD~D@

T79 PAD~D@

C C

B B

RC60 49.9_0402_1%~D

RC58 49.9_0402_1%~D

RC59 49.9_0402_1%~D

H_CPU_TESTLO

12

CFG_RCOMP

12

H_CPU_RSVD

12

T101PAD~D@

T83 PAD~D@

T108PAD~D@

+VCC_CORE

T82 PAD~D@

T94 PAD~D@

T85 PAD~D@

T84 PAD~D@

T86 PAD~D@

CFG0<6>

CFG1<6>

CFG2<6>

CFG3<6>

CFG4<6>

CFG5<6>

CFG6<6>

CFG7<6>

CFG8<6>

CFG9<6>

CFG10<6>

CFG11<6>

CFG12<6>

CFG13<6>

CFG14<6>

CFG15<6>

H_CPU_RSVD

H_CPU_TESTLO

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

AD10

W29

W28

W33

AL30

AL29

AL25

W30

W31

W34

AT20

AR20

AP20

AP22

AT22

AN22

AT25

AN23

AR24

AT23

AN20

AP24

AP26

AN25

AN26

AP25

AT1

RSVD_TP

AT2

RSVD_TP

RSVD

A34

RSVD_TP

A35

RSVD_TP

RSVD

RSVD

G26

RSVD

RSVD

RSVD

RSVD

F25

VCC

C35

RSVD_TP

B35

RSVD_TP

RSVD_TP

RSVD

RSVD

TESTLO

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CONN@

IN

TEL_HASWELL_HAS WELL

JCPU1I

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

9 OF 9

C23

B23

D24

D23

CFG_RCOMP

AT31

CFG16

AR21

CFG18

AR23

CFG17

AP21

CFG19

AP23

AR33

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

T99PAD~D @

T90PAD~D @

T87PAD~D @

T88PAD~D @

CFG16 <6>

CFG18 <6>

CFG17 <6>

CFG19 <6>

T91PAD~D @

T104PAD~D @

T92PAD~D @

T89PAD~D @

T93PAD~D @

T95PAD~D @

T111PAD~D @

T96PAD~D @

T98PAD~D @

T97PAD~D @

T100PAD~D @

T109PAD~D @

T102PAD~D @

T107PAD~D @

T105PAD~D @

T106PAD~D @

CFG4

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG4

Display Port Presence Strap

CFG6

CFG5

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

CFG[6:5]

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG7

1K_0402_1%~D

12

@

RC76

1K_0402_1%~D

12

RC77

1K_0402_1%~D

1K_0402_1%~D

12

12

@

RC90

@

RC92

1K_0402_1%~D

12

@

RC91

PEG DEFER TRAINING

1: (Default) PEG Train immediately

A A

CFG7

following xxRESETB de assertion

0: PEG Wait for BIOS for training

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

CPU (5/7) RSVD,CFG

ze Document Number Rev

Si

Custom

LA-9331P

2

Date: Sheet of

1

10 61Friday, June 22, 2012

0.1

Page 11

5

4

3

2

1

+VCC_CORE

AA26

VCC

AA28

VCC

AA34

VCC

AA30

VCC

AA32

VCC

AB26

VCC

AB29

VCC

AB25

VCC

AB27

VCC

AB28

VCC

AB30

VCC

AB31

VCC

AB33

VCC

AB34

VCC

AB32

VCC

AC26

VCC

AB35

VCC

AC28

VCC

AD25

VCC

AC30

VCC

AD28

VCC

AC32

VCC

AD31

VCC

AC34

VCC

AD34

VCC

AD26

VCC

AD27

VCC

AD29

VCC

AD30

VCC

AD32

VCC

AD33

VCC

AD35

VCC

AE26

VCC

AE32

VCC

AE28

VCC

AE30

VCC

AG28

VCC

AG34

VCC

AE34

VCC

AF25

VCC

AF26

VCC

AF27

VCC

AF28

VCC

AF29

VCC

AF30

VCC

AF31

VCC

AF32

VCC

AF33

VCC

AF34

VCC

AF35

VCC

AG26

VCC

AH26

VCC

AH29

VCC

AG30

VCC

AG32

VCC

AH32

VCC

AH35

VCC

AH25

VCC

AH27

VCC

AH28

VCC

AH30

VCC

AH31

VCC

AH33

VCC

AH34

VCC

AJ25

VCC

AJ26

VCC

AJ27

VCC

AJ28

VCC

AJ29

VCC

AJ30

VCC

AJ31

VCC

AJ32

VCC

AJ33

VCC

AJ34

VCC

AJ35

VCC

G25

VCC

H25

VCC

J25

VCC

K25

VCC

L25

VCC

M25

VCC

N25

VCC

P25

VCC

R25

VCC

T25

VCC

U25

VCC

U26

VCC

V25

VCC

V26

VCC

W26

VCC

W27

VCC

AB11

AE11

AH11

AL27

AK27

AL35

AN35

AL16

AL13

AM28

AM29

AL28

AP35

AP34

AT35

AR35

AR32

AL26

AT34

AL22

AT33

AM21

AM25

AM22

AM20

AM24

AL19

AM23

AT32

K27

L27

T27

V27

AB2

AB5

AB8

AE2

AE5

AE8

K11

N11

N8

T11

T2

T5

T8

W11

W2

W5

W8

N26

K26

E17

A23

F22

W32

J27

H27

Y25

Y26

Y27

Y28

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Haswell rPGA EDS

RSVD

RSVD

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

RSVD

VCC

RSVD

RSVD

VCC_SENS E

RSVD

VCCIO_OUT

VCCIO2PCH

VCCIOA_O UT

RSVD

RSVD

VSS

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VSS

PWR_DE BUG

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

TEL_HASWELL_HASWELL

IN

CONN@

JCPU1E

5 OF 9

D D

C C

B B

+1.35V_CPU_VDDQ Source

SUSP#<43,56,59,61>

CPU1.5V_S3_GATE<43>

SVID ALERT

VIDALERT_N<62>

SVID DATA

VIDSOUT<62>

VCC_SENSE

VCCSENSE<62>

VSSSENSE<62>

1 2

RC93 0_0402_5%~D@

1 2

RC79 0_0402_5%~D

+VCCIO_OUT

75_0402_1%~D

12

RC61

+VCCIO_OUT

110_0402_1%~D

12

RC63

+VCC_CORE

100_0402_1%~D

12

RC66

VCCSENSE

VSSSENSE

100_0402_1%~D

12

RC70

+3VALW

100K_0402_5%~D

12

RC74

RUN_ON_CPU1.5VS3#

61

QC4A

DMN66D0LDW-7_SOT363-6~D

2

CAD Note: Place the PU resistors close to CPU

RC60 close to CPU 300 - 1500mils

H_CPU_SVIDALRT#

12

RC6943_0402_5%~D

CAD Note: Place the PU resistors close to CPU

RC63 close to CPU 300 - 1500mils

VIDSOUT

CAD Note: RC67 SHOULD BE PLACED CLOSE TO CPU

VCCSENSE_R

12

RC670_0402_5%~D

CAD Note: RC68 SHOULD BE PLACED CLOSE TO CPU

VSSSENSE_R

12

RC680_0402_5%~D

VSSSENSE_R <11>

B+_BIAS

330K_0402_5%~D

12

RC72

RUN_ON_CPU1.5VS3RUN_ON_CPU1.5VS3

34

QC4B

DMN66D0LDW-7_SOT363-6~D

5

RUN_ON_CPU1.5VS3# <6,56>

+1.35V

QC3

AO4304L_SO8

8

7

6

5

4

0.022U_0402_25V7K~D

1M_0402_5%~D

12

RC143

1

2

+1.05VS

RC4 0_0603_5%~D@

RESISTOR STUFFING OPTIONS ARE

PROVIDED FOR TESTING PURPOSES

+1.35V_CPU_VDDQ

CC136

1

2

3

1

2

1

2

+1.35V_CPU_VDDQ

10U_0603_6.3V6M~D

12

CC135

1

2

12

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC180

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CC181

1

2

C_0805NEW

20K_0402_5%~D

@

RC73

+VCCIO_OUT

VDDQ DECOUPLING

10U_0603_6.3V6M~D

1

1

CC169

CC170

2

2

22U_0805_6.3V6M~D

CC183

CC182

1

1

2

2

C_0805NEW

T113 PAD~D@

T114 PAD~D@

T112 PAD~D@

T116 PAD~D@

+1.35V

CC151 0.1U_0402_10V7K~D

12

CC152 0.1U_0402_10V7K~D

12

T115 PAD~D@

+VCC_CORE

T151 PAD~D@

T152 PAD~D@

T153 PAD~D@

+VCCIO_OUT

T156 PAD~D@

+VCOMP_OUT

T160 PAD~D@

T159 PAD~D@

+1.05VS

10K_0402_5%~D

12

@

RC80

CPU_PWR_DEBUG

10K_0402_5%~D

12

@

RC71

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC168

2

22U_0805_6.3V6M~D

CC184

1

2

C_0805NEW

C_0805NEW

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

CC161

CC162

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CC186

CC185

1

1

2

2

C_0805NEW

C_0805NEW

10U_0603_6.3V6M~D

1

1

CC163

CC164

CC165

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CC189

CC187

CC188

1

1

2

2

C_0805NEW

C_0805NEW

T168 PAD~D@

T154 PAD~D@

VIDSCLK<62>

CPU_PWR_DEBUG<6>

T157 PAD~D@

T158 PAD~D@

T162 PAD~D@

T163 PAD~D@

10U_0603_6.3V6M~D

330U_D2_2VM_R6M~D

1

CC167

1

+

CC166

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CC190

CC191

1

1

2

2

C_0805NEW

C_0805NEW

+1.35V_CPU_VDDQ

VCCSENSE_R

H_CPU_SVIDALRT#

VIDSCLK

VIDSOUT

+VCC_CORE

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

2

Compal Electronics, Inc.

Title

CPU (6/7) PWR

ze Document Number Rev

Si

Custom

LA-9331P

Date: Sheet of

1

11 61Friday, June 22, 2012

0.1

Page 12

5

4

3

2

1

AA11

AA25

AA27

AA31

AA29

AB10

AA33

AA35

AC25

AC27

AC11

AD11

AC29

AC31

AC33

AC35

AE10

AE25

AE29

AE27

AE35

AF11

AG11

AG25

AE31

AG31

AE33

AH10

AG27

AG29

AG33

AG35

AJ11

AK11

AK25

AK26

AK28

AK29

AK30

AK32

A10

A13

A16

A19

A22

A25

A27

A29

A31

A33

AB1

AB3

AB4

AB6

AB7

AB9

AD7

AE1

AE3

AE4

AE6

AE7

AE9

AF6

AF8

AG6

AH1

AH2

AH3

AH4

AH5

AH6

AH7

AH8

AH9

AJ5

E19

A3

A4

A7

Haswell rPGA EDS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

IN

CONN@

JCPU1F

TEL_HASWELL_HAS WELL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

6 OF 9

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

AR10

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

D D

C C

B B

Haswell rPGA EDS

B34

VSS

B4

VSS

B7

VSS

C1

VSS

C10

VSS

C13

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C24

VSS

C26

VSS

C28

VSS

C30

VSS

C32

VSS

C34

VSS

C4

VSS

C7

VSS

D10

VSS

D13

VSS

D16

VSS

D19

VSS

D22

VSS

D25

VSS

D27

VSS

D29

VSS

D31

VSS

D33

VSS

D35

VSS

D4

VSS

D7

VSS

E1

VSS

E10

VSS

E13

VSS

E16

VSS

E4

VSS

E7

VSS

F10

VSS

F11

VSS

F12

VSS

F14

VSS

F15

VSS

F17

VSS

F18

VSS

F20

VSS

F21

VSS

F23

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

F32

VSS

F34

VSS

F4

VSS

F6

VSS

F7

VSS

F8

VSS

F9

VSS

G1

VSS

G11

VSS

G2

VSS

G27

VSS

G29

VSS

G3

VSS

G31

VSS

G33

VSS

G35

VSS

G4

VSS

G5

VSS

H10

VSS

H26

VSS

H6

VSS

H7

VSS

J11

VSS

J26

VSS

J28

RSVD

J30

VSS

J32

VSS

J34

VSS

J6

VSS

K1

VSS

TEL_HASWELL_HAS WELL

IN

CONN@

JCPU1G

RSVD

RSVD

RSVD

RSVD

VSS_SENSE

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

7 OF 9

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

VSSSENSE_R <10>

T120PAD~D @

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/22 2013/06/21

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

CPU (7/7) VSS

Size Document Number Rev

Custom

LA-9331P

2

Date: Sheet of

1

12 61Friday, June 22, 2012

0.1

Page 13

5

D D

DDR_A_DQS#[0..7]<7,14>

DDR_A_D[0..63]<7, 14>

DDR_A_DQS[0..7]<7,14>

DDR_A_MA[0..15]<7,14>

Layout Note:

Place near JDIMMA

C C

B B

A A

+1.35V

1U_0402_6.3V6K~D

1

1

CD3

2

2

+1.35V

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CD7

1

1

2

2

Layout Note:

Place near JDIMMA.203,204

+0.675VS

1

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CD4

CD8

1

2

1U_0402_6.3V6K~D

CD17

SA0

1

0

0

1U_0402_6.3V6K~D

1

1

CD5

CD6

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CD10

CD9

1

1

2

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

1

CD18

2

2

SA1

001

DIMM1A

1

DIMMB

DIMMC

1

DIMMD

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

330U_SX_2VY~D

@

1

CD13

CD11

CD74

1

1

2

1

CD19

2

+

2

2

1U_0402_6.3V6K~D

CD20

10K_0402_5%~D

10K_0402_5%~D

All VREF traces should

have 20 mil trace width

CD14

+3VS

RD38

1 2

RD21

@

1 2

4

RD39

@

10K_0402_5%~D

1 2

+3VS

RD22

10K_0402_5%~D

1 2