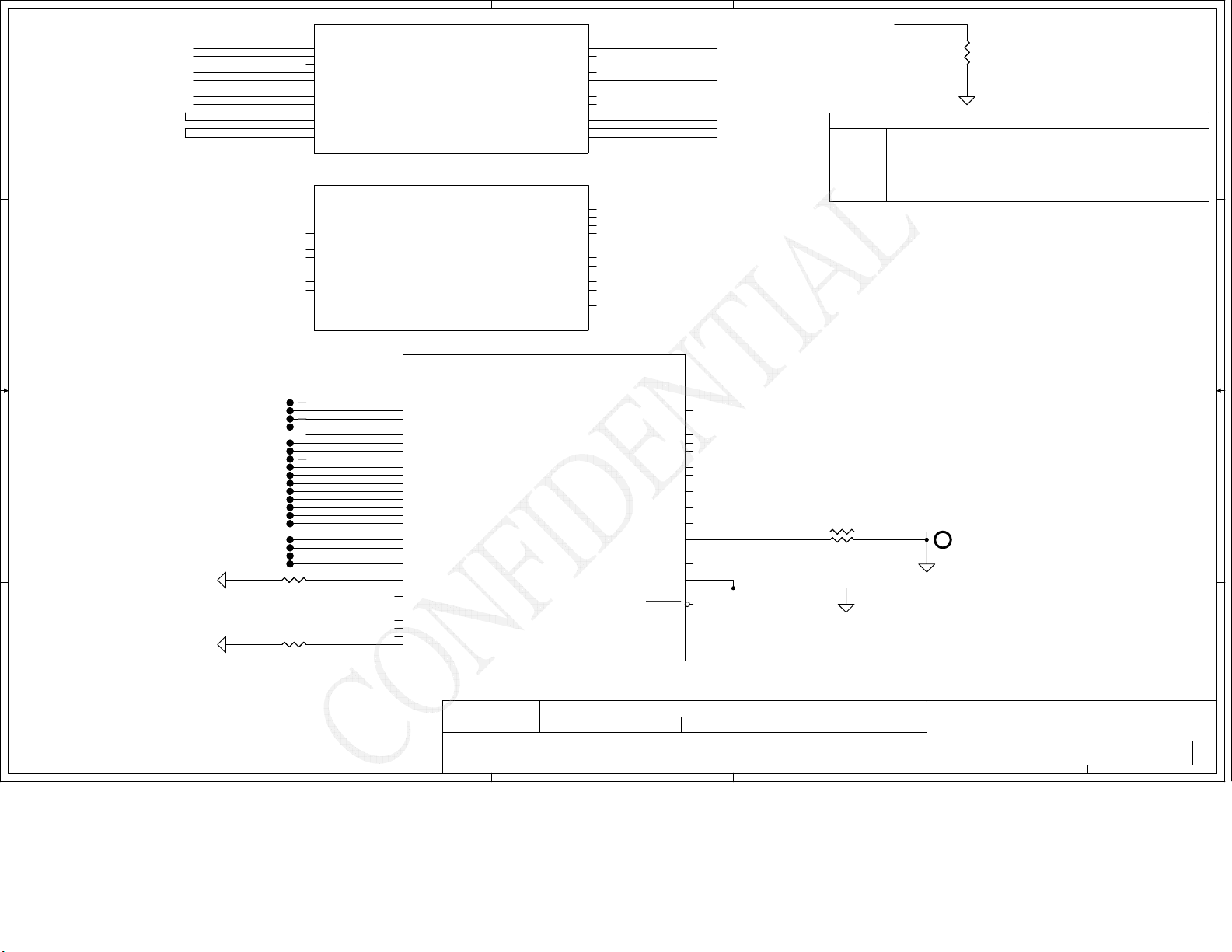

Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

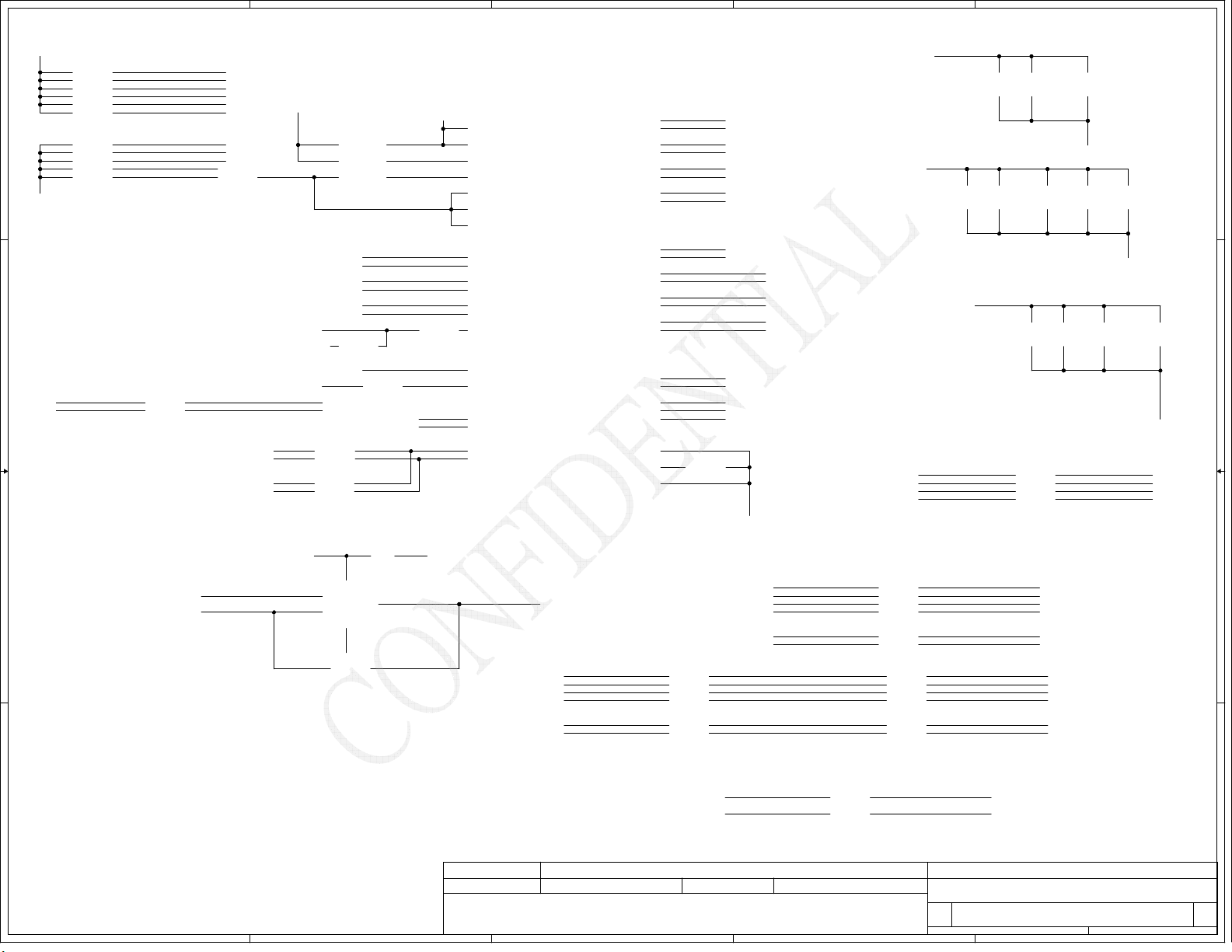

Hasswell M/B Schematics Document

Intel ULV Processor with LPDDR3/DDRIIIL

Date : 2013/06/26

3 3

Version 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

INS35596872

INS35596872

INS35596872

E

1.0

1.0

1.0

160Saturday, July 06, 2013

160Saturday, July 06, 2013

160Saturday, July 06, 2013

of

of

of

Page 2

A

www.vinafix.com

B

C

D

E

Compal Confidential

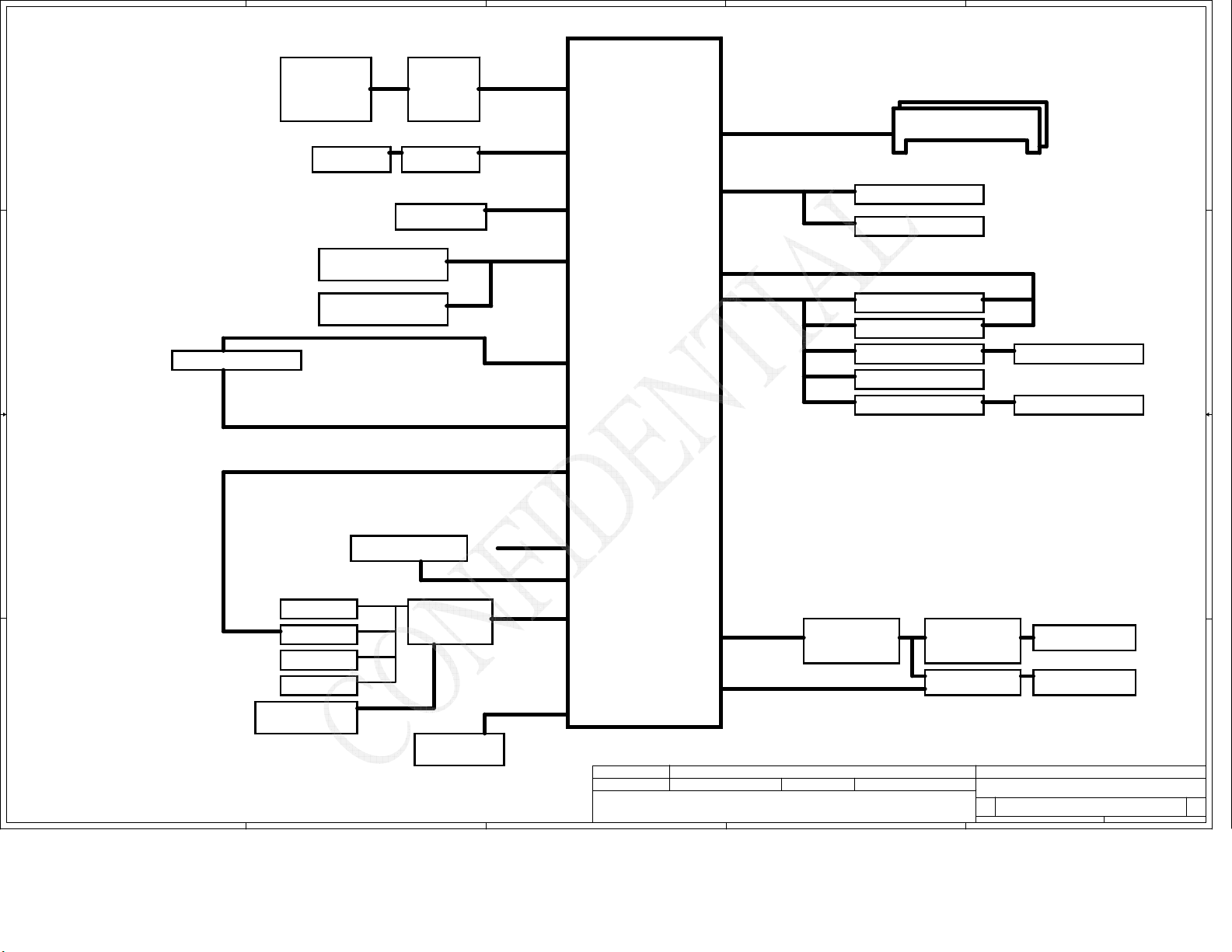

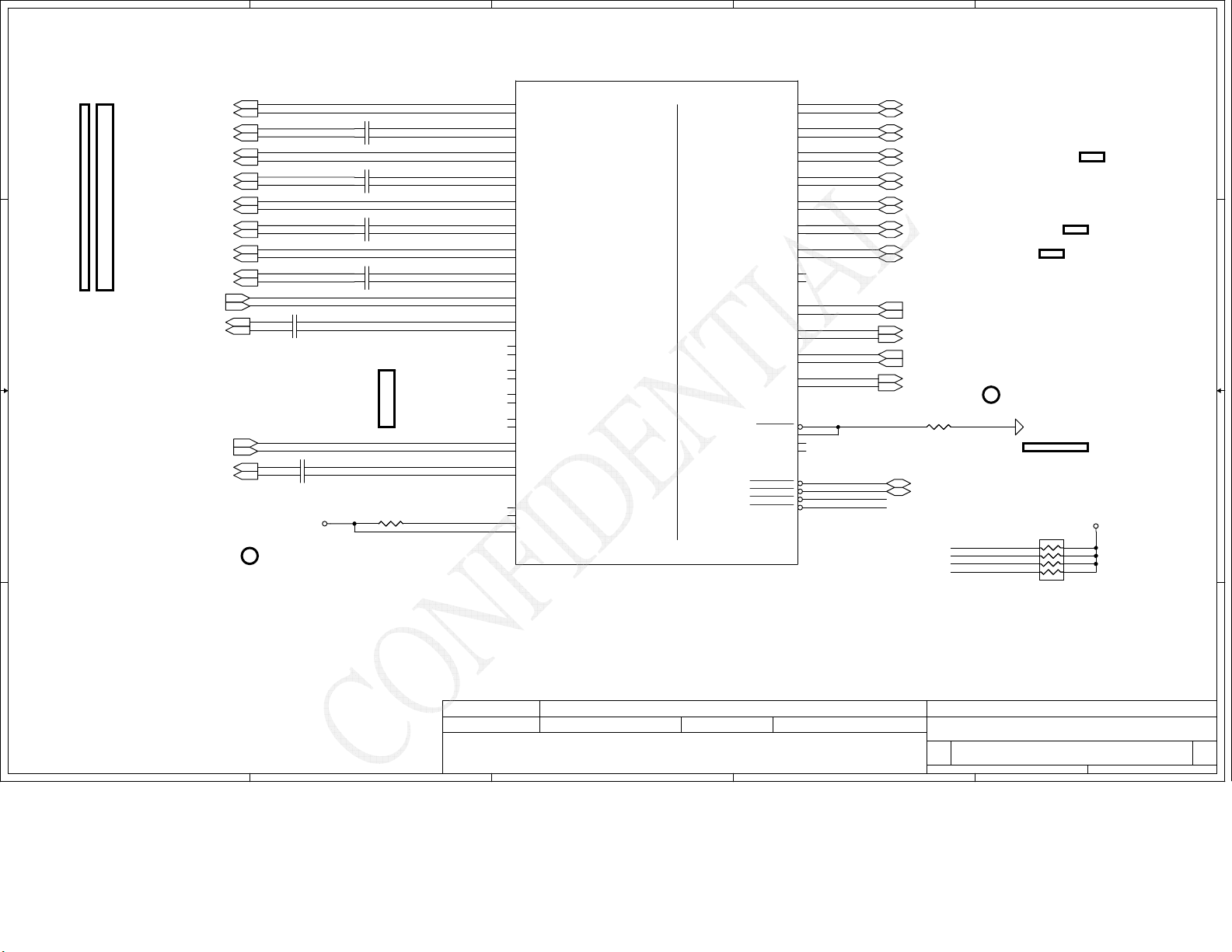

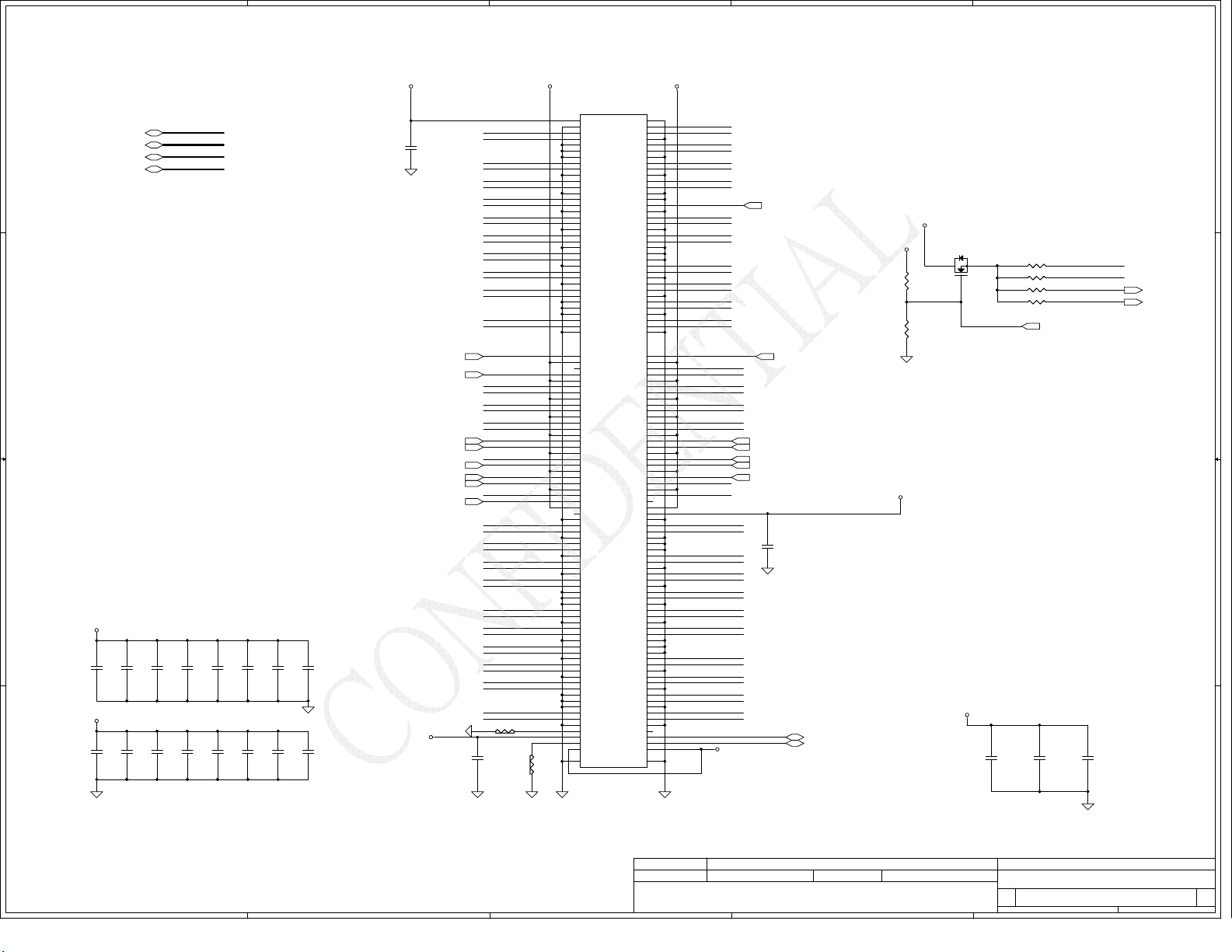

Model Name : Haswell

P18P20

P19

Lane 4

Lane 5

Lane 11

PCI-Ex4

Lane 7-Lane10

PCIe 2.0:5Gb/s

PCIe 3.0:8Gb/s

eDPx2

2.7Gb/s

HDMI

222.75MHz

PCI-E

PCIe 1.0:2.5Gb/s

PCIe 2.0:5Gb/s

PCIe 1.0:2.5Gb/s

PCIe 2.0:5Gb/s

PCI-E

USB2.0Port 3 (Reserved)

480Mb/s

Haswell

Ultra Light & Thin

1168P BGA

(USW ULT)

Dual Channel

DDR3L 1333MHz 1.35V

SATA 3.0

GEN1 1.5Gb/s

GEN2 3Gb/s

GEN3 6Gb/s

USB3.0

5Gb/s

USB2.0

480Mb/s

Port 2

2.5" SATA HDD

Port 3

SSD(MiniPCIe slot)

Port 0

USB2.0 port

Port 1

USB2.0 port

Port 2

Port 4

Camera

Port 6

WWAN(NGFF_B)

DDR3-SO-DIMM X 2

P15,16

P22

P22

Port 1

P26

Port 2

P26

P27

P20

P21

(nonCS)

USB2.0 portUSB charger

SIM conn

VRAM

File Name :

LA-9314PR10(NonCS)

1 1

P37~P40 P32~P36

Nvidia

N14-GV2

17W

RTD2136SLVDS panel

HDMI Conn

DDPB port

2 2

(nonCS)

WLAN(MiniPCIe slot)

Port 3

PCI-E Card reader

RTS5237

10/100/1G LAN

RTL8161G

P23

P25

P24

SMBUS

1MHz

3 3

(NonCS:USB)

Touch screen

P20

I2C_1

1MHz

USB2.0Port 5

480Mb/s

ENE KB9012Int.KBD

(NonCS)

Touch Pad

PS2

FAN

Lid switch

4 4

Accelerometer

HP3DC2

SMBUS

100KHz

P46

P42

LPC

33MHz

SPI

50MHz

HDA

SMBUS

1MHz

24MHz

HDA Aduio codec

92HD91

P28 P29

Audio Sub

HP Amp

P30

Sub conn

HP&MIC jack

(nonCS)

SPI ROM

8M

A

B

P7

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

INS35596872

INS35596872

INS35596872

E

260Saturday, July 06, 2013

260Saturday, July 06, 2013

260Saturday, July 06, 2013

of

of

of

0.1

0.1

0.1

Page 3

A

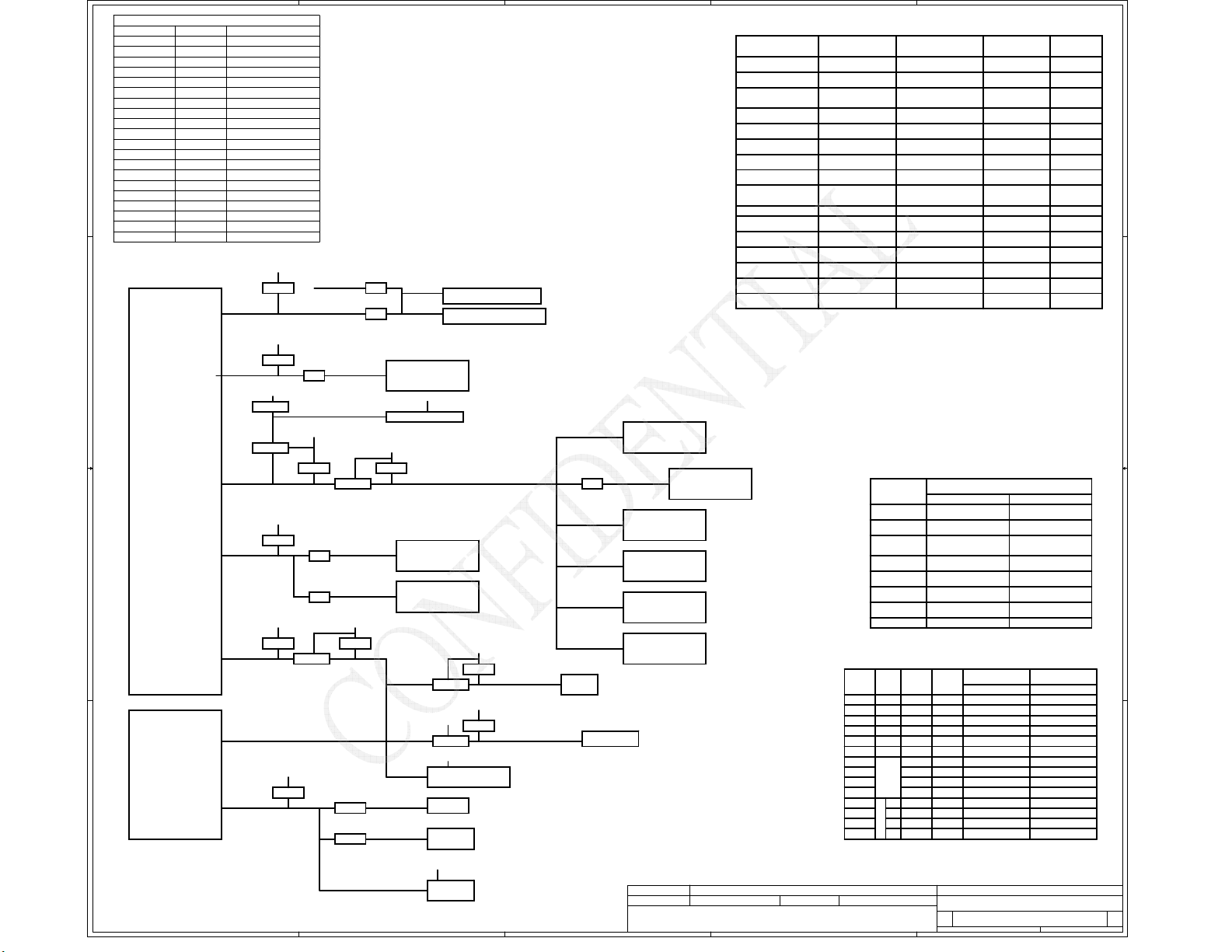

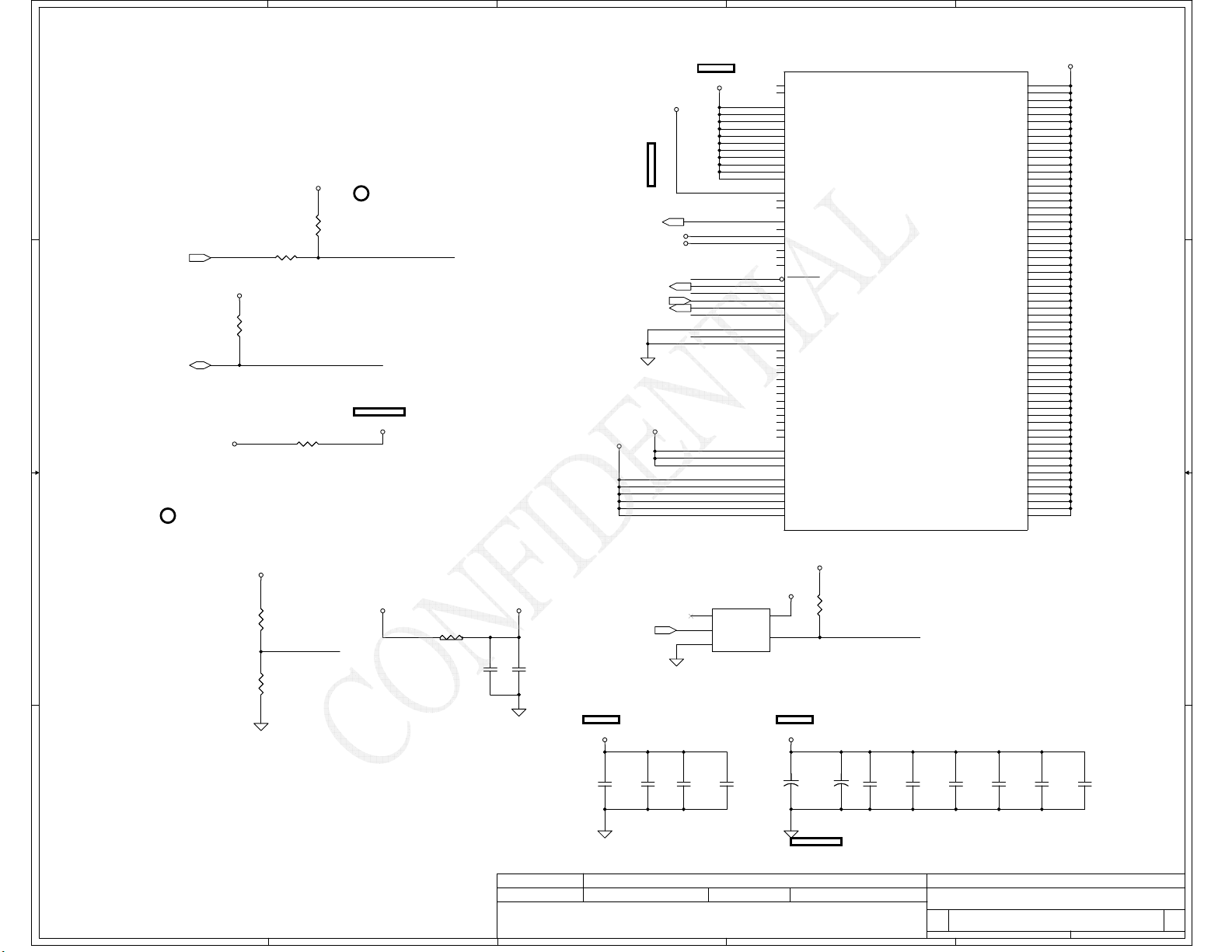

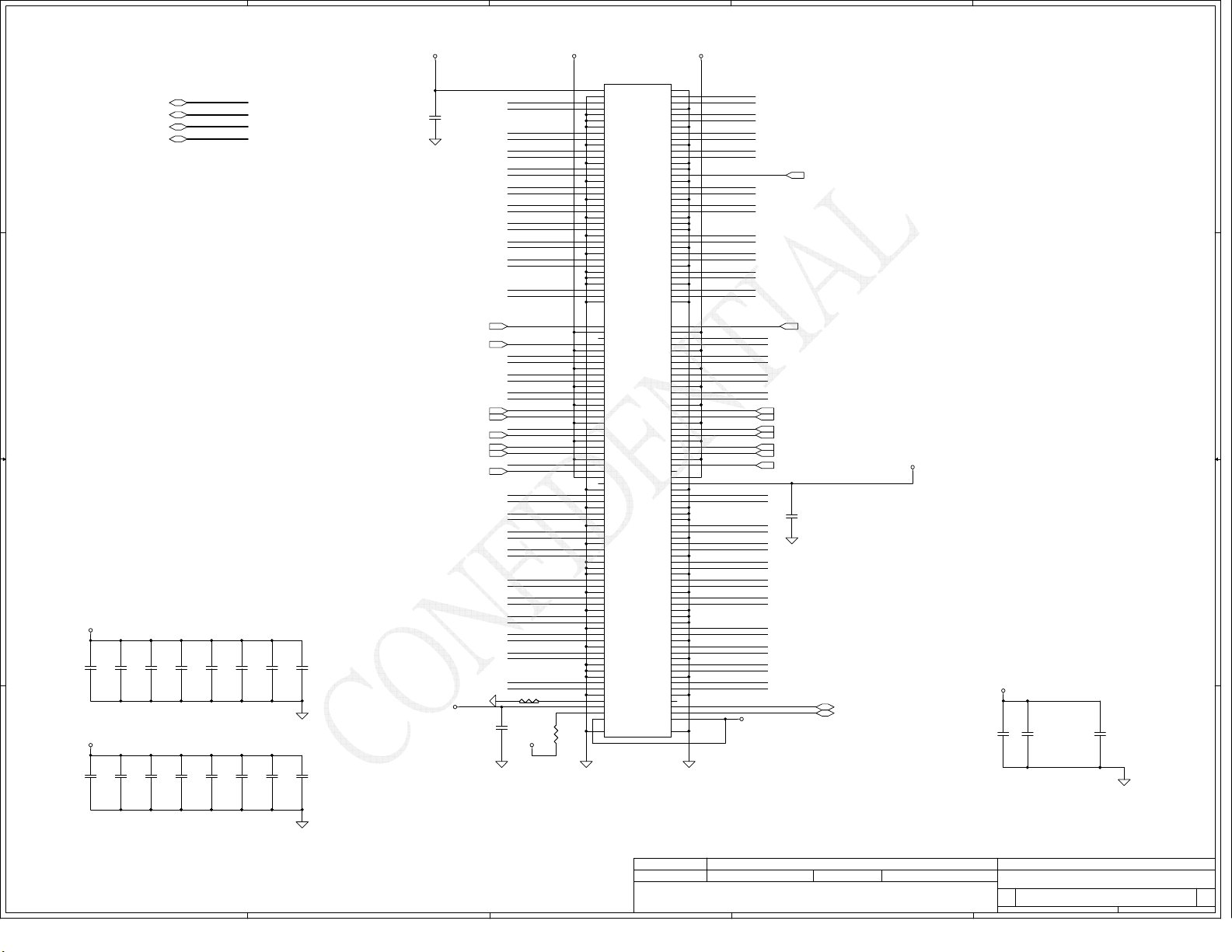

Power rail

+RTCVCC

VIN

BATT+

B+

+VL

+3VL

+5VALW

+3VALW

+3VALW_EC

+3V_PCH

1 1

+1.05V

+1.8V

+1.2V_1.35V

+5VS

+3VS

+1.8VS

+1.5VS

+1.05VS

+1.05VS_MODPHY

+0.6V_0.675VS

+VCC_CORE

Control (EC)

X

X

X

X

X

X

EC_ON

EC_ON

EC_ON

PCH_PWR_EN

SUSP#

SYSON

SYSON

SUSP#

SUSP#

SUSP#

SUSP#

SUSP#

X

X

X

UCPU1

Source (CPU)

X

X

X

X

X

X

X

X

X

X

PM_SLP_S5# / PM_SLP_S4#

PM_SLP_S5# / PM_SLP_S4#

PM_SLP_S3#

PM_SLP_S3#

PM_SLP_S3#

PM_SLP_S3#

PM_SLP_S3#

MPHY_PWREN

SM_PG_CTRL

VR12.5_VR_ON

F3

I2C_0_SCL

F2

I2C_0_SDA

R=1K

+3VS

@ is NO SMT part (empty)

short@ : short pad , don't pop.

@EMI@,@ESD@,@RF@ : Reserve , don't pop.

RF@ : RF team request, must add.

EMI@ : EMI team request, must add.

ESD@ : ESD team request, must add.

LVDS@ : Support LVDS panel.

eDP@ : Support eDP panel.

DIS@ : GPU BOM config.

WWAN@ : For WWAN function.

VGU00@,VGU11@ : Board ID config.

EC_SMB_CK2

EC_SMB_DA2

B

C

D

E

<Power gating GPIO,wake ,INT and RST>

Device

NGFF SSD

NGFF WWAN

NGFF WLAN/BT

WLAN (MiniPCIe)

USB3.0 CONN

USB3.0 CONN(Charger)

Card reader (PCI-E)

USB2.0 Camera

Touch Panel

Touch Pad -NonCS

Touch Pad -CS

WWAN

SATA HDD/SSD

mSATA

Audio DSP + codec

@

R=0

R=0

UA1,UA2:+1.8VS_AUDIO& +5VS_AUDIO

AUDIO CODEC

AUDIO subwoofer

(CS only)

(CS only)

Thermal (EC)

eDP*

LAN (PCI-E) GPIO12

Power gating GPIO

X(Not support)

X(Not support)

GPIO83

**

GPIO13

GPIO43

GPIO60

GPIO25

GPIO89

GPIO88

*

GPIO84

GPIO90

GPIO86

GPIO76

X(Not support)

V

Enable (ON)

ICCPU

H

H

LL

HH

HH

H

H

HH

LL

HH

H

H

HH

H

H

HL

HW part

Load switch

USB switch

USB charger

Load switch

Load switch

Load switch

PMOS

Load switch

Load switch

Load switch

Load switch

Load switch

Load switch

RST/IRQ

Wake/INT

GPIO34 GPIO54

GPIO93 GPIO94

GPIO52

GPIO50

GPIO55

GPIO38

X(Not support)

DEVSLP2#/GPIO39

X(Not support)

GPIO91 GPIO92

*

*

+3VS

2 2

F1

G4

CPU

AP2

AH1

AN1

AK1

3 3

AU3

AH3

UK1:+3VALW_EC

79

80

EC

77

4 4

78

I2C_1_SCL

I2C_1_SDA

+3VALW

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

0x96

EC_SMB_CK2

EC_SMB_DA2

EC_SMB_CK1

EC_SMB_DA1

R=1K

R=2.2K

2N7002

+3V_PCH

R=1K

+3V_PCH

R=2.2K

+3VALW

R=2.2K

@

R=0

+3V_PCH

R=2.2K

R=0

@

R=0

2N7002

I2C_1_SDA_PNL

I2C_1_SCL_PNL

I2C_1_SDA_PAD

I2C_1_SCL_PAD

2N7002

SML0CLK_NFC

SML0DATA_NFC

SML0CLK_NGFF

SML0DATA_NGFF

+3VS

R=2.2K

EC_SMB_CK2

EC_SMB_DA2

R=100

R=0

Touch Panel

+3VALW

Touch PAD

+3VS

R=10K

PCH_SMBCLK

PCH_SMBDATA

NFC

NGFF

Thermal Sensor

Charger

2N7002

DIS@

+3VS

2N7002

+3VS

BAT

(CS only)

(NonCS only)

(CS only)

(CS only)

+3VGS

DIS@

R=2.2K

+HP_5V

R=4.7K

I2CS_SCL

I2CS_SDA

DIS@

PCH_SMB_CK1_AMP

PCH_SMB_DA1_AMP

0x4D(1001 101b)

GPU

HP amp

PCH_SMBCLK_XDP

PCH_SMBDATA_XDP

R=0

UP1:+3VS

UP3:+3VS

0x9E

UA3:+5VS

UT1

eDP to LVDS

RTD2136

SO-DIMM A

SO-DIMM B

LPDDR3 EEPROM 1

LPDDR3 EEPROM 2

0x60(1100 000b)

XDP

(NonCS only)

(NonCS only)

(CS only)

(CS only)

<USB2.0 port>

USB2.0 port

0

1

2

3

4

5

6

7

DESTINATION

CS NonCS

USB 2.0(left side)

USB 2.0(left side)

USB 2.0(right side)

WLAN (NGFF) WLAN (MiniPCIe)

Camera

No contact

WWAN

Finger printer

<PCI-E,SATA,USB3.0>

PCI-E

Lane#

1

2

31

4

5

6

7

8

9

10

11

12

13

14

SATA

USB3.0

2

3

4

5

L3

3

L2

2

6

L1

1

L0

0

USB 2.0(left side)

USB 2.0(left side)

USB 2.0(right side)

Camera

Touch screen

WWAN

Finger printer

DESTINATION

CS

USB3.0

1

2

USB3.0 USB3.0

X(Not support)

3

Card reader(PCI-E)

4

10/100/1000 LAN 10/100/1000 LAN

SSD(mSATA)

2.5"HDD

NonCS

USB3.0

X(Not support)

Card reader(PCI-E)

GPU(DIS only)

GPU(DIS only)

GPU(DIS only)

GPU(DIS only)

WLAN (MiniPCIe)WLAN (NGFF)

X(Not used)X(Not used)

SSD(mSATA)

2.5"HDD

+3VALW

Security Classification

Security Classification

G-sensor

A

B

(0101 001b)

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Custom

Custom

Custom

Compal Electronics, Inc.

Notes List

Notes List

Notes List

INS35596872

INS35596872

INS35596872

360Saturday, July 06, 2013

360Saturday, July 06, 2013

360Saturday, July 06, 2013

E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

0.1

0.1

0.1

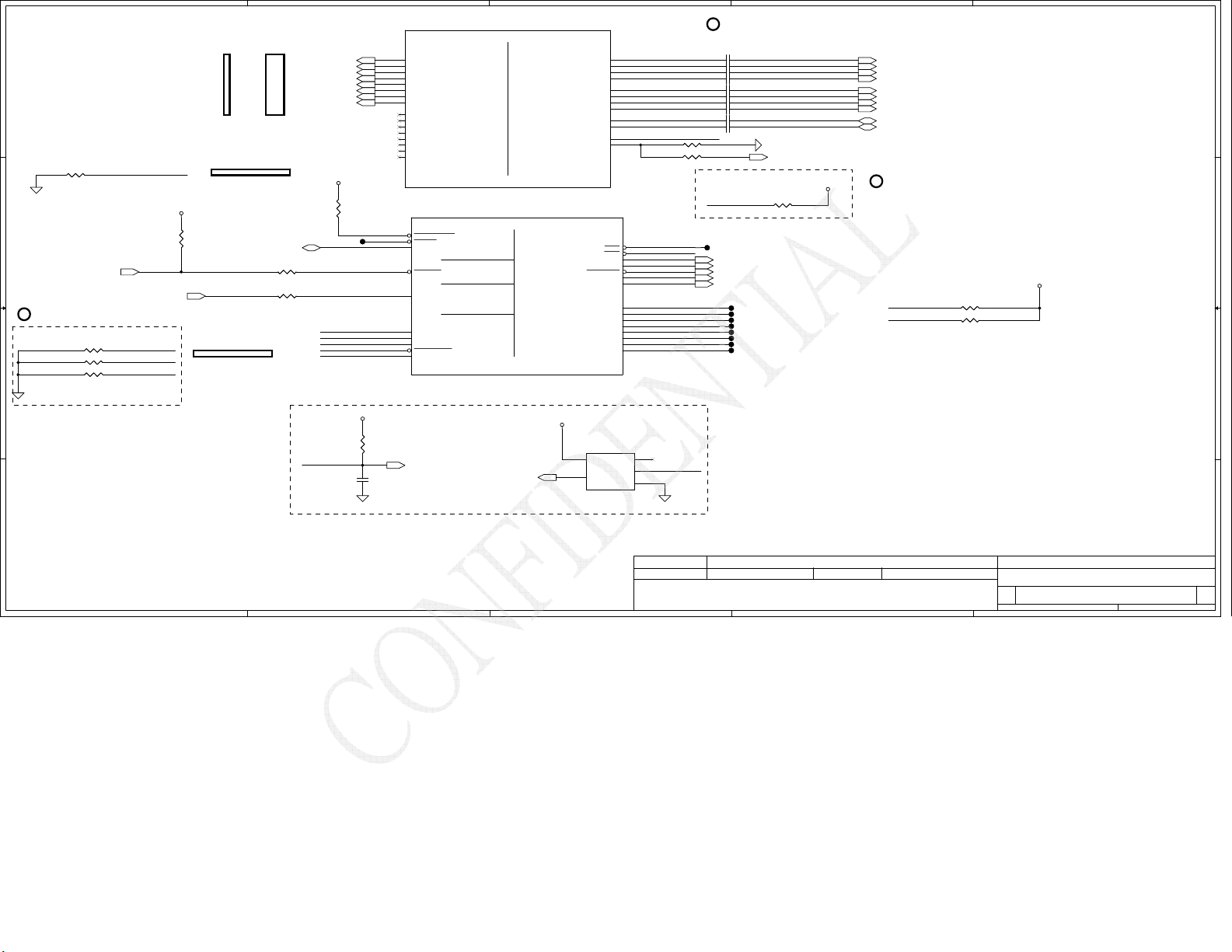

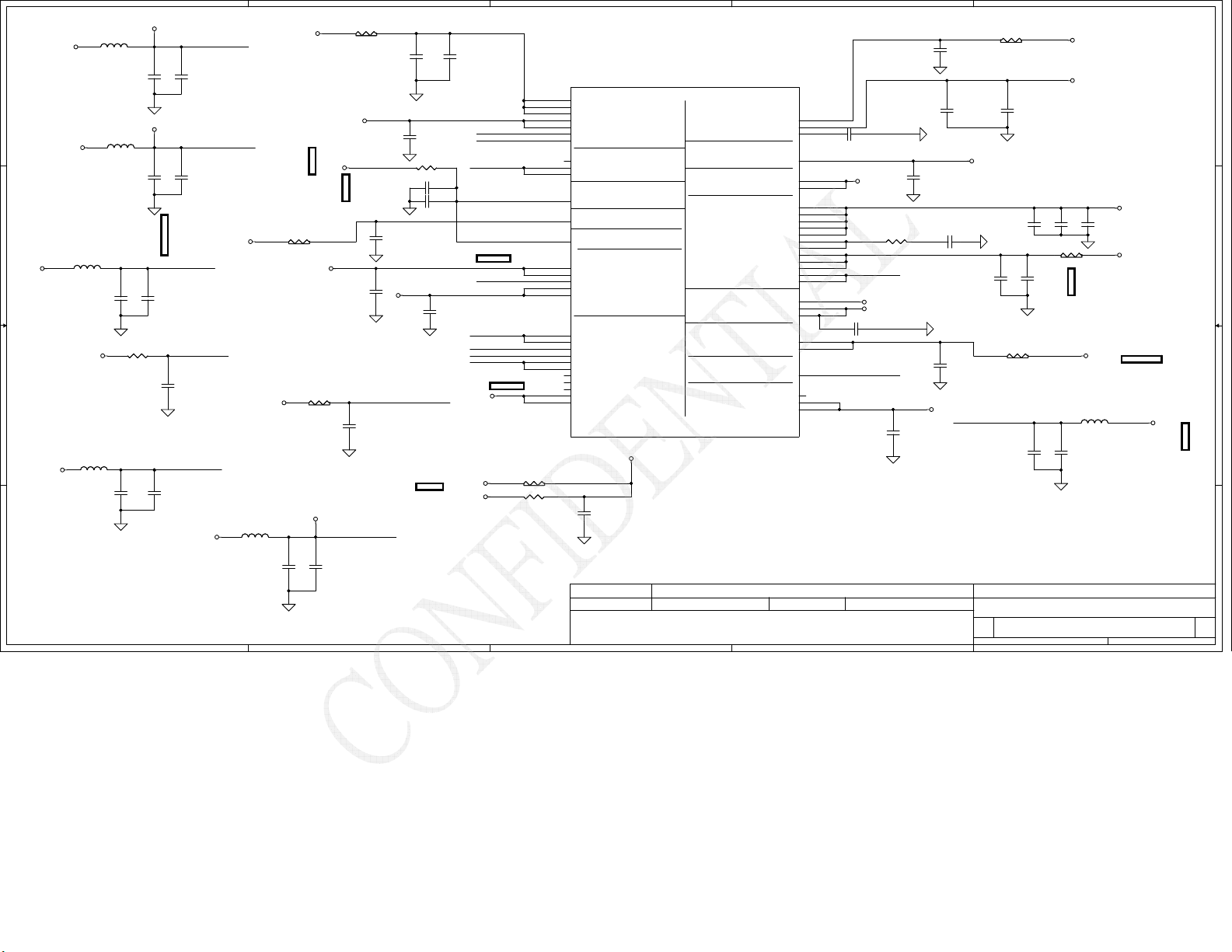

Page 4

5

<HDMI>

PCH_DPB_N2<19>

PCH_DPB_P2<19>

PCH_DPB_N1<19>

D D

<DB>UpdateHDMInetname

PCH_DPB_P1<19>

PCH_DPB_N0<19>

PCH_DPB_P0<19>

PCH_DPB_N3<19>

PCH_DPB_P3<19>

Swap,sameasolddesign

RC11 10K_0402_5%RC11 10K_0402_5%

C C

L

DDR3 COMPENSATION SIGNALS

B B

H_PROCHOT#<42>

DG V0.5 Trace width=12~15 mil

Max length=500mil

H_CPUPWRGD_R

12

+VCCIO_OUT

RC4

RC4

62_0402_5%

62_0402_5%

H_PROCHOT#

+1.05VS_PG<6>

SM_RCOMP0

RC18200_0402_1% RC18200_0402_1%

12

SM_RCOMP1

RC19\\TPERDFS1\CIS\CIS_SYMBOL_FOR_HW\RTL8111E-GR_QFN48_6X6.OLBRC19\\TPERDFS1\CIS\CIS_SYMBOL_FOR_HW\RTL8111E-GR_QFN48_6X6.OLB

12

SM_RCOMP2

RC20100_0402_1% RC20100_0402_1%

12

9/4removePROC_DETECT#offpagetoEC

12

H_PECI<42>

RC6 56_0402_5%RC6 56_0402_5%

1 2

@

@

RC7 1K_0402_1%

RC7 1K_0402_1%

1 2

<DB>IntelrequestRC19100‐‐>120

+3V_PCH

12

RC234

RC234

10K_0402_5%

10K_0402_5%

PROC_DETECT#

T51PAD @T51PAD @

H_PROCHOT#_R

H_CPUPWRGD_R

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR3_DRAMRST#

DDR_PG_CNTL

4

HASWELL_MCP_E

HASWELL_MCP_E

DDI EDP

DDI EDP

1 OF 19

1 OF 19

HASWELL_MCP_E

HASWELL_MCP_E

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3

DDR3

2 OF 19

2 OF 19

JTAG

JTAG

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AU60

AV60

AU61

AV15

AV61

D61

K61

N62

K63

C61

UCPU1A

UCPU1A

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

UCPU1B

UCPU1B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

3

CC97~CC102 must closed to connector not CPU

L

EDP_CPU_LANE_N0_C

C45

EDP_CPU_LANE_P0_C

B46

EDP_CPU_LANE_N1_C

A47

B47

EDP_CPU_LANE_N2_C

C47

EDP_CPU_LANE_P2_C

C46

EDP_CPU_LANE_N3_C

A49

B49

EDP_CPU_AUX#_C

A45

EDP_CPU_AUX_C EDP_CPU_AUX

B45

D20

RC1 0_0201_5%@RC1 0_0201_5%@

A43

RC2 0_0201_5%@RC2 0_0201_5%@

CC97 0.1U_0402_16V7KCC97 0.1U_0402_16V7K

1 2

CC98 0.1U_0402_16V7KCC98 0.1U_0402_16V7K

1 2

CC99 0.1U_0402_16V7KCC99 0.1U_0402_16V7K

1 2

CC100 0.1U_0402_16V7KCC100 0.1U_0402_16V7K

1 2

CC103 0.1U_0402_16V7KINS21744796CC103 0.1U_0402_16V7KINS21744796

1 2

CC104 0.1U_0402_16V7KINS21744796CC104 0.1U_0402_16V7KINS21744796

1 2

CC105 0.1U_0402_16V7KINS21744796CC105 0.1U_0402_16V7KINS21744796

1 2

CC106 0.1U_0402_16V7KINS21744796CC106 0.1U_0402_16V7KINS21744796

1 2

CC101 0.1U_0402_16V7KCC101 0.1U_0402_16V7K

1 2

CC102 0.1U_0402_16V7KCC102 0.1U_0402_16V7K

1 2

EDP_COMP

1 2

1 2

COMPENSATIONPUFOReDP

EDP_COMP

PRDY

PREQ

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS_CPU

XDP_TRST#_CPU

XDP_TDI_CPU

XDP_TDO_CPU

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

XDP_OBS4_R

XDP_OBS5_R

XDP_OBS6_R

XDP_OBS7_R

T58 PAD@T58 PAD@

XDP_TCK

XDP_TMS_CPU <6>

XDP_TRST#_CPU

XDP_TDI_CPU <6>

XDP_TDO_CPU <6>

T80 PAD@T80 PAD@

T79 PAD@T79 PAD@

T52 PAD@T52 PAD@

T53 PAD@T53 PAD@

T54 PAD@T54 PAD@

T55 PAD@T55 PAD@

T56 PAD@T56 PAD@

T57 PAD@T57 PAD@

EDP_CPU_LANE_N0

EDP_CPU_LANE_P0

EDP_CPU_LANE_N1

EDP_CPU_LANE_P1EDP_CPU_LANE_P1_C

EDP_CPU_LANE_N2

EDP_CPU_LANE_P2

EDP_CPU_LANE_N3

EDP_CPU_LANE_P3EDP_CPU_LANE_P3_C

EDP_CPU_AUX#

BKL_PWM_CPU INS19291009

+VCCIOA_OUT

12

RC324.9_0402_1% RC324.9_0402_1%

2

EDP_CPU_LANE_N0 <18>

EDP_CPU_LANE_P0 <18>

EDP_CPU_LANE_N1 <18>

EDP_CPU_LANE_P1 <18>

EDP_CPU_LANE_N2 <18>

EDP_CPU_LANE_P2 <18>

EDP_CPU_LANE_N3 <18>

EDP_CPU_LANE_P3 <18>

EDP_CPU_AUX# <18>

EDP_CPU_AUX <18>

DG V0.9 PEG_COMP

L

Trace width=20mil and spacing=25mil

Max length=100mil

XDP_TDI_CPU

XDP_PREQ#

RC12 51_0402_1%@ RC12 51_0402_1%@

RC13 51_0402_1%@ RC13 51_0402_1%@

<eDP>

<eDP>

12

12

1

+1.05VS_VCCST

+1.35V_VDDQ

12

RC308

RC308

470_0402_5%

470_0402_5%

DDR3_DRAMRST#

@

@

A A

5

1

CC88

CC88

0.1U_0402_16V7K

0.1U_0402_16V7K

2

4

DDR3_DRAMRST# <15,16>

+1.35V_VDDQ

SM_PG_CTRLINS19291222

NonCS

UC10

UC10

5

NC

VCC

4

A

Y

GND

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

3

1

DDR_PG_CNTL

2

3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

DDI,MSIC,XDP

DDI,MSIC,XDP

DDI,MSIC,XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-XXXXP

LA-XXXXP

LA-XXXXP

Date: Sheet

Date: Sheet

Date: Sheet

1

460Saturday, July 06, 2013

460Saturday, July 06, 2013

460Saturday, July 06, 2013

of

of

of

0.1

0.1

0.1

Compal Electronics, Inc.

LA-8661P

Page 5

5

4

3

2

1

DDR_A_D[0..63]<15>

HASWELL_MCP_E

UCPU1C

UCPU1C

DDR_A_D0

D D

C C

B B

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AW58

AW56

AW54

AW52

AM43

AM45

AM40

AM42

AM46

AM49

AM48

AM51

AH63

SA_DQ0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ10

AP62

SA_DQ11

AM61

SA_DQ12

AM60

SA_DQ13

AP61

SA_DQ14

AP60

SA_DQ15

AP58

SA_DQ16

AR58

SA_DQ17

AM57

SA_DQ18

AK57

SA_DQ19

AL58

SA_DQ20

AK58

SA_DQ21

AR57

SA_DQ22

AN57

SA_DQ23

AP55

SA_DQ24

AR55

SA_DQ25

AM54

SA_DQ26

AK54

SA_DQ27

AL55

SA_DQ28

AK55

SA_DQ29

AR54

SA_DQ30

AN54

SA_DQ31

AY58

SA_DQ32

SA_DQ33

AY56

SA_DQ34

SA_DQ35

AV58

SA_DQ36

AU58

SA_DQ37

AV56

SA_DQ38

AU56

SA_DQ39

AY54

SA_DQ40

SA_DQ41

AY52

SA_DQ42

SA_DQ43

AV54

SA_DQ44

AU54

SA_DQ45

AV52

SA_DQ46

AU52

SA_DQ47

AK40

SA_DQ48

AK42

SA_DQ49

SA_DQ50

SA_DQ51

AK45

SA_DQ52

AK43

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

AK46

SA_DQ57

SA_DQ58

AK49

SA_DQ59

SA_DQ60

AK48

SA_DQ61

SA_DQ62

AK51

SA_DQ63

HASWELL_MCP_E

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

DDR_A_DQS#0

AJ61

DDR_A_DQS#1

AN62

DDR_A_DQS#2

AM58

DDR_A_DQS#3

AM55

DDR_A_DQS#4

AV57

DDR_A_DQS#5

AV53

DDR_A_DQS#6

AL43

DDR_A_DQS#7

AL48

DDR_A_DQS0

AJ62

DDR_A_DQS1

AN61

DDR_A_DQS2

AN58

DDR_A_DQS3

AN55

DDR_A_DQS4

AW57

DDR_A_DQS5

AW53

DDR_A_DQS6

AL42

DDR_A_DQS7

AL49

+V_SM_VREF_CNT

AP49

+V_DDR_REFA_R

AR51

+V_DDR_REFB_R

AP51

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

<DDR3L>

+V_SM_VREF_CNT

M_CLK_DDR#0 <15>

M_CLK_DDR0 <15>

M_CLK_DDR#1 <15>

M_CLK_DDR1 <15>

DDR_CKE0_DIMMA <15>

DDR_CKE1_DIMMA <15>

DDR_CS0_DIMMA# <15>

DDR_CS1_DIMMA# <15>

DDR_A_RAS# <15>

DDR_A_WE# <15>

DDR_A_CAS# <15>

DDR_A_BS0

DDR_A_BS1 <15>

DDR_A_BS2

DDR_A_MA[0..15] <15>

DDR_A_DQS#[0..7] <15>

DDR_A_DQS[0..7] <15>

+V_DDR_REFA_R

+V_DDR_REFB_R

DDR_B_D[0..63]<16>

HASWELL_MCP_E

HASWELL_MCP_E

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

<DDR3L>

M_CLK_DDR#2 <16>

M_CLK_DDR2 <16>

M_CLK_DDR#3 <16>

M_CLK_DDR3 <16>

DDR_CKE0_DIMMB <16>

DDR_CKE1_DIMMB <16>

DDR_CS0_DIMMB# <16>

DDR_CS1_DIMMB# <16>

DDR_B_RAS# <16>

DDR_B_WE# <16>

DDR_B_CAS# <16>

DDR_B_BS0 <16>

DDR_B_BS1 <16>

DDR_B_BS2 <16>

DDR_B_MA[0..15] <16>

DDR_B_DQS#[0..7] <16>

DDR_B_DQS[0..7] <16>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AK20

AM20

AR18

AP18

UCPU1D

UCPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

AL28

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

AL25

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

AL21

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

AL18

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

DDRIII

DDRIII

DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-XXXXP

LA-XXXXP

LA-XXXXP

Date: Sheet

Date: Sheet

Date: Sheet

1

of

560Saturday, July 06, 2013

of

560Saturday, July 06, 2013

of

560Saturday, July 06, 2013

0.1

0.1

0.1

Compal Electronics, Inc.

Page 6

5

PCH_INTVRMEN

RC236330K_0402_5% RC236330K_0402_5%

1 2

RC32 20K_0402_5%RC32 20K_0402_5%

RC34 20K_0402_5%RC34 20K_0402_5%

D D

RC353

INS35596130RC353

HDA_SYNC_R HDA_SYNC

INS35596130

INS35596130

RC356 0_0201_5%

RC356 0_0201_5%

1 2

0_0402_5%

0_0402_5%

1 2

INS35596130

HDA_SDOUT

C C

B B

A A

12

M/B

M/B

12

M/B

M/B

12

RC301

100_0402_1%

100_0402_1%

RC283

RC41

@RC283

@

PCH_JTAG_TDO

@RC41

@

PCH_JTAG_TDI

@RC301

@

@

@

1 2

@

@

1 2

12

RC46

RC46

M/B

M/B

@

@

XDP_TCK_JTAGX

12

RC302

RC302

100_0402_1%

100_0402_1%

@

@

XDP_TRST#

PCH_JTAG_TMS

XDP_TMS

XDP_TDI_SWITCH

PCH_JTAG_TDO

XDP_TDI

PCH_JTAG_TDI

XDP_TDO

PCH_JTAG_TCK

XDP_TCK_JTAGX

XDP_TCK_JTAGX XDP_TDO

5

RC37 0_0201_5%@RC37 0_0201_5%@

1 2

RC196 0_0201_5%@RC196 0_0201_5%@

RC199 0_0201_5%@RC199 0_0201_5%@

RC307 0_0201_5%@RC307 0_0201_5%@

RC200 0_0201_5%

RC200 0_0201_5%

INS35596130

INS35596130

RC195 0_0201_5%

RC195 0_0201_5%

INS35596130

INS35596130

RC198 0_0201_5%@RC198 0_0201_5%@

RC194 0_0201_5%

RC194 0_0201_5%

INS35596130

INS35596130

RC197 0_0201_5%@RC197 0_0201_5%@

1 2

RC193 0_0201_5%

RC193 0_0201_5%

1 2

INS35596130

INS35596130

RC306 0_0201_5%@RC306 0_0201_5%@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CM28

CM28

HDA_BITCLK_AUDIO

22P_0402_50V8J

22P_0402_50V8J

CM29

CM29

HDA_RST_AUDIO#

22P_0402_50V8J

22P_0402_50V8J

PCH_JTAG_RST#

XDP_TMS_CPU

XDP_TDI

XDP_TCK

4

1

CC2

CC2

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1 2

1 2

1

CC5

CC5

1U_0402_6.3V6K

1U_0402_6.3V6K

2

INS35597247

INS35597247

RH2501 1M_0402_5%

RH2501 1M_0402_5%

1 2

RC367

EMI@ RC367

EMI@

33_0402_5%

33_0402_5%

12

RC45

M/B

M/B

12

RC303

100_0402_1%

100_0402_1%

XDP_TRST#_CPU

XDP_TDI_CPU

XDP_TDI_SWITCH

XDP_TDI_SWITCH

XDP_TDO_CPU

PCH_JTAG_TDO

4

12

JCMOS1

JCMOS1

SHORT PADS

SHORT PADS

PCH_RTCRST#

PCH_SRTCRST#

INS35597247

INS35597247

QH14

QH14

G

G

2

2N7002KW_SOT323-3

2N7002KW_SOT323-3

13

D

S

D

S

HDA_BIT_CLKHDA_BITCLK_AUDIO

12

RP1

RP1

1 8

HDA_SYNC_R

2 7

HDA_RST#HDA_RST_AUDIO#

3 6

HDA_SDOUT

4 5

{AF225CAE-0DE6-4A06-8E6D-EA2295109748}

{AF225CAE-0DE6-4A06-8E6D-EA2295109748}

@RC45

@

PCH_JTAG_TMS

@RC303

@

RC31 10M_0402_5%RC31 10M_0402_5%

1

CC3

CC3

18P_0402_50V8J

18P_0402_50V8J

2

RC35 1M_0402_5%RC35 1M_0402_5%

1 2

PCH_JTAG_RST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

T156PAD~D T156PAD~D

XDP_TCK_JTAGX

T157PAD~D T157PAD~D

PCH_JTAG_TCK

XDP_TRST#_CPU

RC16 51_0402_1%@RC16 51_0402_1%@

XDP_TDO_CPU

XDP_TCK

XDP_TDO

RC10 51_0402_1%RC10 51_0402_1%

RC14 51_0402_1%

RC14 51_0402_1%

RC15 51_0402_1%RC15 51_0402_1%

1 2

PCH_RTCX1

PCH_RTCX2

SM_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST#

PCH_RTCRST#

HDA_BIT_CLK

HDA_SYNC

HDA_RST#

HDA_SDIN0

HDA_SDOUT

1 2

12

12

@

@

12

12

3

PCH_RTCX1

PCH_RTCX2

1

CC4

CC4

18P_0402_50V8J

18P_0402_50V8J

2

EC_+1.05VS_PG

RC3851_0402_5% @ RC3851_0402_5% @

3

AW5

AY5

AU6

AV7

AV6

AU7

AW8

AV11

AU8

AY10

AU12

AU11

AW10

AV10

AY8

AU62

AE62

AD61

AE61

AD62

AL11

AC4

AE63

AV2

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TRST#_CPU

2

1K_0402_5%

1K_0402_5%

RC33

DC1

DC1

HASWELL_MCP_E

HASWELL_MCP_E

RTC

RTC

AUDIO

AUDIO

JTAG

JTAG

RC240

RC240

10K_0402_5%

10K_0402_5%

UC5

@UC5

@

2

1OE

3

1A

5

2OE

6

2A

12

3OE

11

3A

15

4OE

14

4A

8

GND

74CBTLV3126DS_SSOP16

74CBTLV3126DS_SSOP16

1

BAV70W 3P C/C_SOT-323

BAV70W 3P C/C_SOT-323

5 OF 19

5 OF 19

@

@

12

16

VCC

4

1B

7

2B

10

3B

13

4B

1

NC

9

NC

1

CC6

CC6

1U_0402_6.3V6K

1U_0402_6.3V6K

2

UCPU1E

UCPU1E

RTCX1

RTCX2

INTRUDER

INTVRMEN

SRTCRST

RTCRST

HDA_BCLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

HDA_RST/I2S_MCLK

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

DOCKEN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

TP5

TP6

JTAGX

RSVD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

RC33

2

3

XDP_TDO

XDP_TDI_SWITCH

XDP_TMS

XDP_TRST#

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

SATA

SATA

12

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

SATA_RCOMP

SATALED

CC86

@CC86

@

1 2

.1U_0402_16V7K

.1U_0402_16V7K

EC_+1.05VS_PG

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

TP7

K10

TP8

C12

U3

JRTC1

CONN@JRTC1

CONN@

1

1

2

2

3

GND

4

GND

ACES_50271-0020N-001

ACES_50271-0020N-001

PCIE_PTX_DRX_N6

PCIE_PTX_DRX_P6

DIRECT_ESATA_DETECT#

SATA_ODD_PRSNT_R_N

mSATA_DET#

3K_0402_1%

3K_0402_1%

SATA_COMP

1 2

SATA_LED#

DIRECT_ESATA_DETECT#

U16

U16

NC1VCC

2

A

Y

3

GND

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

mSATA_DET#

SATA_ODD_PRSNT_R_N

CC7 0.1U_0402_16V7KCC7 0.1U_0402_16V7K

1 2

CC8 0.1U_0402_16V7KCC8 0.1U_0402_16V7K

1 2

RC39

RC39

12

RC220

INS35596130RC220

INS35596130

0_0402_5%

0_0402_5%

12

5

4

1

RC217 100K_0402_5%RC217 100K_0402_5%

1 2

INS35597247

INS35597247

RC218 100K_0402_5%

RC218 100K_0402_5%

1 2

R511

R511

10K_0402_5%

10K_0402_5%

Title

Title

Title

INS16784064

INS16784064

INS16784064

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-XXXXP

LA-XXXXP

LA-XXXXP

Date: Sheet

Date: Sheet

Date: Sheet

1

660Saturday, July 06, 2013

660Saturday, July 06, 2013

660Saturday, July 06, 2013

0.1

0.1

0.1

of

of

of

Page 7

5

o

<MV>LAN_CLKREQ#changetoLAN_CLKREQ#_P

<MV>MINI1_CLKREQ#changetoMINI1_CLKREQ#_P

RC49 0_0201_5%INS35596130RC49 0_0201_5%INS35596130

PCIE LAN

D D

PCIE Card reader

<DB>Uppdate

WLAN <EC>

<DB>GPU New

GPU

+3VS

RPH11

RPH11

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

C C

B B

+3V_PCH

10K_0804_8P4R_5%

+3VS

RPH12

RPH12

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

PCH_SPI_CLK

INS35598727<42>

INS35598735<42>

INS35598743<42>

INS35598759<42>

1 2

RC85 3.3K_0402_5%RC85 3.3K_0402_5%

CLK_PCIE_LAN#<24>

CLK_PCIE_LAN<24>

CLK_PCIE_CR#<25>

CLK_PCIE_CR<25>

CR_CLKREQ#<25>

CLK_PCIE_MINI1#<23>

CLK_PCIE_MINI1<23>

INS16728031<32>

INS16727965<32>

1 2

RC369

EMI@ RC369

EMI@

+3V_PCH

RC80

@ RC80

@

3.3K_0402_5%

3.3K_0402_5%

1 2

EC_KBRST# <42>

INS34283878 <8>

RPH19

RPH19

INS34285098

INS34285098

INS37309103EMI@

INS37309103EMI@

RPH20

RPH20

INS34285098

INS34285098

1 2

PCH_SPI_CS0#_R

PCH_SPI_SO_R

PCH_SPI_WP#

INS37309103

INS37309103

18

27

36

45

PCH_SPI_CLK_R

18

27

36

45

MINI1_CLKREQ#_P

CR_CLKREQ#

LAN_CLKREQ#_P

PCIECLKREQ5#

GPU_CLKREQ#_P

PCIECLKREQ4#

PCH_SPI_CS0# PCH_SPI_CS0#_R

PCH_SPI_SO PCH_SPI_SO_R

PCH_SPI_HOLD# PCH_SPI_SIO3

RC368

RC368

SI#2012.10.30SupportquadIOfunction

9/10addThermalsensorforHPrequest

+3VS

CPU THERMAL SENSOR

1

CC14

CC14

@

@

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2200P_0402_50V7K

2200P_0402_50V7K

1 2

H_THERMDA

H_THERMDC

CPU_THERM#

CC15

CC15

A A

1 2

+3VS

RC96 33K_0402_5%RC96 33K_0402_5%

UC3

1

VDD

2

D+

3

D-

THERM#4GND

ADM1032ARMZ-2REEL_MSOP8

ADM1032ARMZ-2REEL_MSOP8

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

1 2

RC50 0_0201_5%INS35596130RC50 0_0201_5%INS35596130

1 2

RC310 0_0201_5%INS35596130RC310 0_0201_5%INS35596130

1 2

RC311 0_0201_5%INS35596130RC311 0_0201_5%INS35596130

1 2

RC55 0_0201_5%INS35596130RC55 0_0201_5%INS35596130

1 2

RC57 0_0201_5%INS35596130RC57 0_0201_5%INS35596130

1 2

RC312 0_0201_5%INS35596130RC312 0_0201_5%INS35596130

1 2

RC313 0_0201_5%INS35596130RC313 0_0201_5%INS35596130

1 2

LPC_FRAME#INS19291034

PCH_SPI_SI_RPCH_SPI_SI

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CS0#_R

PCH_SPI_WP#PCH_SPI_SIO2

RC56 0_0402_5%INS35596130RC56 0_0402_5%INS35596130

1 2

SPI ROM 8M

UC2

UC2

1

CS#

SO/SIO1

WP#

GND

PACDN042

PACDN042

SCLK

VCC

HOLD#

SCLK

SI/SIO0

8

7

6

5

2

3

4

INS44505121UC3

INS44505121

SDATA

ALERT#

LPC_AD0INS19291034

LPC_AD1INS19291034

LPC_AD2INS19291034

LPC_AD3INS19291034

SI#2012.11.1AddRC368,RC369to

IsolateSPIClockbyEMIrequest

EC_SMB_CK2

EC_SMB_DA2

THERMAL_ALERT#

9/13 change RC96 10K to 33K for EC

Thermal sensor SMBus address -->0111_100xb (0x78h)

5

4

HASWELL_MCP_E

UCPU1F

UCPU1F

PCIE_LAN#

PCIE_LAN

LAN_CLKREQ#_P

PCIE_CR#

PCIE_CR

CR_CLKREQ#

PCIE_MINI1#

PCIE_MINI1

MINI1_CLKREQ#_P

PCIE_GPU#

PCIE_GPU

GPU_CLKREQ#_P

PCIECLKREQ4#

PCIECLKREQ5#

LPC_AD0

LPC_AD2 SMBDATA

LPC_AD3

LPC_FRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_SIO2

PCH_SPI_SIO3

PCH_SPI_CLK_R

EON SA000046400 S IC FL 64M EN25Q64-104HIP SOP 8P

MXIC SA00006N100 S IC FL 64M MX25L6473EM2I-10G SOP 8P

WINBOND SA000039A30 S IC FL 64M W25Q64FVSSIQ SOIC 8P SPI ROM

Micron SA00005L100 S IC FL 64M N25Q064A13ESEC0F SO8W 8P

8

PCH_SPI_HOLD#

7

PCH_SPI_CLK_R

6

PCH_SPI_SI_R

5

4

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

UCPU1G

UCPU1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

RC84 3.3K_0402_5%RC84 3.3K_0402_5%

12

INS35598660 <42>

12

RC105 10K_0402_5%RC105 10K_0402_5%

LPC

LPC

SPI C-LINK

SPI C-LINK

+3VS

HASWELL_MCP_E

HASWELL_MCP_E

HASWELL_MCP_E

7 OF 19

7 OF 19

CLOCK

CLOCK

SIGNALS

SIGNALS

6 OF 19

6 OF 19

SMBUS

SMBUS

+3V_PCH

SMBALERT/GPIO11

SML0ALERT/GPIO60

SML1ALERT/PCHHOT/GPIO73

SML1CLK/GPIO75

SML1DATA/GPIO74

1

CC11

CC11

0.1U_0402_16V7K

0.1U_0402_16V7K

2

@

@

LAN_CLKREQ#_P LAN_CLKREQ#

MINI1_CLKREQ#_P

PCIECLKREQ5#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

XTAL24_IN

XTAL24_OUT

TP15

TP16

DIFFCLK_BIASREF

TP19

TP20

TP21

TP22

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

SMBCLK

SMBDATA

SML0CLK

SML0DATA

CL_CLK

CL_DATA

CL_RST

RC177

RC177

1 2

0_0402_5%

0_0402_5%

@RC187

@

1 2

0_0402_5%

0_0402_5%

3

2

CPU_XTAL24_IN

A25

CPU_XTAL24_OUT

B25

K21

M21

PCH_CLK_BIASREF

C26

TESTLOW1

C35

TESTLOW2

C34

TESTLOW3

AK8

TESTLOW4

AL8

AN15

CLK_PCI1 CLK_PCI_DEBUG

AP15

CLK_CPU_ITP#

B35

CLK_CPU_ITP

A35

RC61 22_0402_5%EMI@ RC61 22_0402_5%EMI@

RC63 22_0402_5%EMI@ RC63 22_0402_5%EMI@

RC52

RC52

3K_0402_1%

3K_0402_1%

1 2

4 5

3 6

2 7

1 8

1 2

1 2

+1.05VS_AXCK_LCPLL

PRH3

PRH3

10K_0804_8P4R_5%

10K_0804_8P4R_5%

T82 PAD@T82 PAD@

T81 PAD@T81 PAD@

9/17 add RF solution

SMBALERT#

AN2

SMBCLKLPC_AD1

AP2

AH1

USB_CR_PWREN

AL2

SML0CLK

AN1

SML0DATA

AK1

SML1ALERT#

AU4

SML1CLK

AU3

SML1DATA

AH3

AF2

AD2

AF4

RC183

@RC183

@

0_0402_5%

0_0402_5%

1 2

RC184

RC184

0_0402_5%

0_0402_5%

1 2

RC187

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

INS34283931 <9>

http://ISPDPRD/Windchill/servlet/WindchillAuthGW/wt.enterprise.URLProcessor/URLTemplateAction?u8&oid=VR%3Aext.compal.part.CompalPart%3A367112182&acti

INS34283939 <9>

<8>

<DB>No sensor hub

SMBCLK<43>

SMBDATA<43>

LAN_CLKREQ# <24>

MINI1_CLKREQ# <23>

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

CPU_XTAL24_IN

CPU_XTAL24_OUT

CC9

CC9

18P_0402_50V8J

<Page12>

CLK_PCI_LPCCLK_PCI0

<XDP CLK reserve TP> <DB>Add XDP CLK

INS35597295

INS35597295

CM30

CM30

CLK_PCI_LPC

1 2

22P_0402_50V8J

22P_0402_50V8J

INS35597295

INS35597295

CM31

CM31

CLK_PCI_DEBUG

1 2

22P_0402_50V8J

22P_0402_50V8J

INS35597295

INS35597295

CM33

CM33

PCH_SPI_CLK_R

1 2

22P_0402_50V8J

22P_0402_50V8J

QC2A 2N7002DWH_SOT363-6QC2A 2N7002DWH_SOT363-6

SMBCLK

6 1

QC2B

SMBDATA

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

SML1CLK

SML1DATA

GPU_CLKREQ#_P

PCIECLKREQ4#

QC2B

2

6 1

QC6A

QC6A

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

RC189

RC189

1 2

0_0402_5%

0_0402_5%

RC190

@RC190

@

1 2

0_0402_5%

0_0402_5%

18P_0402_50V8J

CLK_PCI_LPC <42>

CLK_PCI_DEBUG <22>

<LPC Debug>

SML0CLK

SML0DATA

SMBCLK

SMBDATA

SML1CLK

SML1DATA

+3VS +3VS

RC78

RC78

10K_0402_5%

2

3 4

10K_0402_5%

5

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

3 4

+3VS

5

QC6B

QC6B

GPU_CLKREQ#

Compal Electronics, Inc.

Title

Title

Title

INS23886333

INS23886333

INS23886333

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

LA-XXXXP

LA-XXXXP

LA-XXXXP

1

12

RC481M_0402_5% RC481M_0402_5%

3

1

2

3

IC.0160B.001

IC.0160B.001

GND

1

GND

2

4

YC2

YC2

<DB>CC9 CC10 6.8P-->18P

1 2

1 2

RP2 INS33034030RP2 INS33034030

1 8

2 7

3 6

4 5

RC79

RC79

10K_0402_5%

10K_0402_5%

1 2

1 2

PCH_SMBCLK <15,16,18>

PCH_SMBDATA <15,16,18>

EC_SMB_CK2 INS23375259

EC_SMB_DA2 INS23375259

P_R_0402 <32>

760Saturday, July 06, 2013

760Saturday, July 06, 2013

760Saturday, July 06, 2013

1

1

1

CC10

CC10

18P_0402_50V8J

18P_0402_50V8J

2

of

of

of

RC721K_0402_5% RC721K_0402_5%

RC731K_0402_5% RC731K_0402_5%

+3V_PCH

0.1

0.1

0.1

Page 8

5

V

Non Deep S3 RC91-->SMT

Deep S3 RC93-->SMT

INS34283947<9>

D D

Deep S3

SYS_PWROK<42>

PCH_PWROK<42>

PCH_RSMRST#<42>

PCH_SUSWARN#<42>

SUSWARN#_R

SUSACK#<42>

PBTN_OUT#<42>

ACIN<52,53>

@

@

RC91 0_0201_5%

RC91 0_0201_5%

1 2

RC93 0_0201_5%INS35596130RC93 0_0201_5%INS35596130

1 2

INS34283878<7>

RC99 0_0402_5%INS35596130RC99 0_0402_5%INS35596130

1 2

RC100 0_0402_5%INS35596130RC100 0_0402_5%INS35596130

1 2

RC104 0_0402_5%INS35596130RC104 0_0402_5%INS35596130

1 2

RC103 0_0402_5%INS35596130RC103 0_0402_5%INS35596130

1 2

CH751H-40PT_SOD323-2

CH751H-40PT_SOD323-2

DC2

DC2

21

<DB>RC112 10K-->100K

ENVDD_CPU

PCI_PIRQB#

PCI_PIRQC#

PCH_GPIO80

PCH_HP_DET

SYS_PWROK

RC114 0_0402_5%INS35596130RC114 0_0402_5%INS35596130

1 2

RC115 0_0402_5%INS35596130RC115 0_0402_5%INS35596130

1 2

RC116 0_0402_5%

RC116 0_0402_5%

1 2

INS35596130

INS35596130

EC_SMI#<9>

1 2

RC305 0_0402_5%

RC305 0_0402_5%

TP_INT#<43>

@

T146PAD~D@T146PAD~D

@

T154PAD~D@T154PAD~D

9/12 move HP_DET to GPIO53,

MIC_DET to GPIO51 (CS only)

@

@

RC112 100K_0402_5%RC112 100K_0402_5%

C C

12

PANEL_BKEN_CPU PD 100K on Page20

BKL_PWM_CPU<4>

ENBKL<42>

ENVDD_CPU

9/12 change connect to ACCEL_INT# on GPIO80

RC120 100K_0402_5%RC120 100K_0402_5%

B B

1 2

+3VS

RC125 10K_0402_5%RC125 10K_0402_5%

PRH8

PRH8

4 5

3 6

2 7

1 8

12

10K_0804_8P4R_5%

10K_0804_8P4R_5%

AOAC_PME#<42>

PCH_MC_WAKE#

4

PV#2013.01.07Addtestpoint

T83

T83

SUSACK#_R

SYS_RESET#

SYS_PWROK

PM_PWROK_R

APWROK_R

PLT_RST#_PCH

PCH_RSMRST#

SUSWARN#_R

PBTN_OUT#_R

ACIN_R

PM_BATLOW#

PM_SLP_S0#_R

PCH_SLP_WLAN#

BKL_PWM_CPU_R

ENBKL_CPU

ENVDD_CPU_RENVDD_CPU

EC_SMI#

PCI_PIRQB#

PCI_PIRQC#

PCH_GPIO80

AOAC_PME#_RAOAC_PME#

TP_INT#

TS_RST#

PCH_MC_WAKE#

PCH_MIC_DET

PCH_HP_DET

PLT_RST#INS46539173

AD4

B8

A9

C6

U6

P4

N4

N2

U7

R5

AW6

AM5

L1

L3

L4

RC268 0_0201_5%INS35596130RC268 0_0201_5%INS35596130

PAD~D

PAD~D

RC269 0_0201_5%

RC269 0_0201_5%

UCPU1H

UCPU1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

SLP_WLAN/GPIO29

UCPU1I

UCPU1I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

PLT_RST#

eDP SIDEBAND

eDP SIDEBAND

1 2

1 2

@

@

HASWELL_MCP_E

HASWELL_MCP_E

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

8 OF 19

8 OF 19

PCH_RSMRST#

PCH_DPWROK_R

GPIO

GPIO

1 2

RC300 0_0402_5%

RC300 0_0402_5%

4

INS35596130

INS35596130

HASWELL_MCP_E

HASWELL_MCP_E

9 OF 19

9 OF 19

@

@

+3VS

5

UC9

UC9

1

P

IN1

O

2

IN2

G

SN74AHC1G08DCKR_SC70-5

SN74AHC1G08DCKR_SC70-5

3

3

PM_SLP_S0#_R

PM_SLP_S3#

DSWVRMEN

DPWROK

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_SUS

SLP_LAN

CH751H-40PT_SOD323-2

CH751H-40PT_SOD323-2

DC3

DC3

21

RC316 0_0201_5%

RC316 0_0201_5%

1 2

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DISPLAY

DISPLAY

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

PLT_RST#_PCH

WAKE

SLP_A

<CPU>

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

T142

T142

PAD~D

PAD~D

PCH_DDPB_CLK

B9

PCH_DDPB_DAT

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

DSWODVREN

PCH_DPWROK_R

WAKE#

PM_CLKRUN#

SUS_STAT#

SUSCLK

1 2

INS35596130RC286

INS35596130

Non Deep S3 RC286-->@

T143

T143

Deep S3 RC286-->SMT

PAD~D

PAD~D

@

@

@

@

PCH_PWROK

PCH_DPWROK <42>

2

DSWODVREN - On Die DSW VR Enable

H:Enable

*

L:Disable

RC371 0_0402_5%

RC371 0_0402_5%

INS35596130

INS35596130

T62 PAD~DT62 PAD~D

SUSCLK <21>

PM_SLP_S5# <42>

PM_SLP_S3#

T145PAD~D@T145PAD~D@

0_0201_5%

0_0201_5%

RC286

PCH_DDPB_CLK <19>

PCH_DDPB_DAT <19>

1 2

WAKE# INS19291145

PM_CLKRUN# <42>

T144

T144

PAD~D

PAD~D

@

@

<7>

<HDMI>

AOAC_PME#

<DB>Add PM_CLKRUN#

PM_SLP_S4# <55>

PM_SLP_S3# <59>

PM_SLP_SUS# <42>

http://ISPDPRD/Windchill/servlet/WindchillAuthGW/wt.enterprise.URLProcessor/URLTemplateAction?u8&oid=

<DB>Reserved RC127

PCH_DDPB_HPD <19>

EDP_HPD <18>

<HDMI>

<eDP HPD>

<DB>Update net name EDP_HPD_R-->EDP_HPD

1

DSWODVREN

DSWODVREN

RC254 330K_0402_5%RC254 330K_0402_5%

RC255 330K_0402_5%

RC255 330K_0402_5%

12

12

@

@

PV#2013.02.07powerrailto+3V_DSW_P

WAKE#

RC98 1K_0402_5%RC98 1K_0402_5%

1 2

<DB>RC106 10K-->100K

<SI>RC106 100K-->10K

PCH_RSMRST#

SUSCLK

RC106 10K_0402_5%RC106 10K_0402_5%

RC107 1K_0402_5%@RC107 1K_0402_5%@

12

12

Deep S3:DSW power choose on page12

RPH15

PCH_SLP_WLAN#

USB_CR_PWREN

PM_BATLOW#

ACIN_R

PM_CLKRUN#

RPH15

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RC101 100K_0402_5%RC101 100K_0402_5%

1 2

RC110 8.2K_0402_5%RC110 8.2K_0402_5%

12

+RTCVCC

+3V_DSW_P

+3V_DSW_P

+3VS

A A

5

4

PD on KBC page

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PM,GPIO,DDI

PM,GPIO,DDI

PM,GPIO,DDI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-XXXXP

LA-XXXXP

LA-XXXXP

Date: Sheet

Date: Sheet

2

Date: Sheet

860Saturday, July 06, 2013

860Saturday, July 06, 2013

860Saturday, July 06, 2013

of

of

1

of

0.1

0.1

0.1

Page 9

5

9/12 reserve EC_FB_CLAMP_TGL_REQ# on GPIO16

9/12 reserve DGPU_GC6_EN on GPIO17

PCH_AUDIO_PWREN

1 2

1 2

T148PAD~D T148PAD~D

T149PAD~D T149PAD~D

@RC119

@

1 2

0_0201_5%

0_0201_5%

T150PAD~D T150PAD~D

NMI_DBG#_CPU

LAN_PWR_EN

EC_LID_OUT#

UART_WAKE#

BT_ON

HDDHALT_LED#

PCH_GPIO58

WL_OFF#

PCH_GPIO44

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

MPHY_PWREN

USB32_P0_PWREN_R#

PCH_GPIO14

USB_CAM_PWREN

LANCB_DET#_PCH

ACCEL_INT#

PCH_GPIO9

EC_SCI#

PCH_GPIO33

T158PAD~D T158PAD~D

DEVSLP1

DEVSLP2

HDA_SPKR

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

+3V_PCH

NMI_DBG#_CPU<42>

EC_LID_OUT#<42>

D D

9/12 reserve DGPU_HOLD_RST# on GPIO58

No sensor hub

No sensor hub

No sensor hub

INS16796023<32>

INS16800658<34>

EC_PME#<42>

HDDHALT_LED#<25>

DGPU_HOLD_RST#<32>

WL_OFF#<23>

10/23 [SI] change ACCEL_INT# to GPIO46

<DB>CS only PCH_HP_DET#

PCH_GPIO81(HDA_SPKR):NonCS only

C C

+3V_PCH

PRH4

PRH4

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

PRH5

PRH5

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

PRH6

PRH6

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RC213 100K_0402_5%RC213 100K_0402_5%

1 2

+3VS

B B

PRH7

PRH7

PRH10

PRH10

RPH13

RPH13

4 5

3 6

2 7

1 8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

SERIRQ

EC_SMI#

PCH_GPIO33

SATA_LED#

10K_0804_8P4R_5%

10K_0804_8P4R_5%

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RC122 0_0201_5%@RC122 0_0201_5%@

RC123 0_0201_5%@RC123 0_0201_5%@

EC_PME#

RC119

INS23375919<31>

ACCEL_INT#<46>

EC_SCI#<42>

DEVSLP1<22>

DEVSLP2<22>

HDA_SPKR

NMI_DBG#_CPU

EC_LID_OUT#

UART_WAKE#

BT_ON

HDDHALT_LED#

PCH_GPIO58

WL_OFF#

PCH_GPIO44

PCH_GPIO14

ACCEL_INT#

LANCB_DET#_PCH

PCH_GPIO9

USB32_P0_PWREN_R#

EC_SMI# <8>

SATA_LED# <6>

PCH_GPIO17

DEVSLP1

DEVSLP2

MPHY_PWREN

PCH_AUDIO_PWREN

LAN_PWR_EN

USB_CAM_PWREN

TOUCH_PANEL_PWREN

4

UCPU1J

UCPU1J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

PCH_GPIO16

PCH_GPIO17

Dummy

+3V_PCH +3VS +3VS

RPH14

RPH14

Y1

T3

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

U4

Y3

P3

Y2

AT3

AH4

AM4

AG5

AG3

AM3

AM2

P2

C4

L2

N5

V2

12

RC135

RC135

10K_0402_5%

10K_0402_5%

@

@

12

RC263

@RC263

@

10K_0402_5%

10K_0402_5%

4 5

3 6

2 7

1 8

GPIO15

GPIO16

GPIO17

GPIO24

GPIO27

GPIO28

GPIO26

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

GPIO48

GPIO49

GPIO50

HSIOPC/GPIO71

GPIO13

GPIO14

GPIO25

GPIO45

GPIO46

GPIO9

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

12

RC261

RC261

10K_0402_5%

10K_0402_5%

@

@

12

RC264

@RC264

@

10K_0402_5%

10K_0402_5%

SUSWARN#_R

10K_0804_8P4R_5%

10K_0804_8P4R_5%

GPIO

GPIO

12

RC262

RC262

10K_0402_5%

10K_0402_5%

12

SML1ALERT#

SMBALERT#

EC_SCI#

HASWELL_MCP_E

HASWELL_MCP_E

10 OF 19

10 OF 19

@

@

RC265

@RC265

@

10K_0402_5%

10K_0402_5%

CPU/

CPU/

MISC

MISC

LPIO

LPIO

INS34283947 <8>

INS34283939 <7>

INS34283931 <7>

3

THRMTRIP

RCIN/GPIO82

SERIRQ

OPI_COMP2

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

H_THERMTRIP#_C

D60

EC_KBRST#

V4

SERIRQ

T4

PCH_OPIRCOMP

AW15

AF20

AB21

NGFF_WIFI_3.3_PWREN

R6

WWAN_PWREN

L6

PCH_GPIO85

N6

MSATA_SSD_PWREN

L8

WWAN_OFF#

R7

TOUCH_PAD_PWREN#

L5

TOUCH_PANEL_PWREN

N7

SATA1_PWREN

K2

PCH_LAN_RST#

J1

PCH_LAN_WAKE#

K3

PCH_CR_RST#

J2

PCH_CR_WAKE#

G1

K4

G2

J3

J4

I2C_0_SDA

F2

I2C_0_SCL

F3

I2C_1_SDA

G4

I2C_1_SCL

F1

E3

F4

D3

E4

C3

E2

INS35596130RC129

INS35596130

0_0402_5%

0_0402_5%

1 2

49.9_0402_1%

49.9_0402_1%

RC108 0_0201_5%@RC108 0_0201_5%@

1 2

2

+1.05VS_VCCST

RC129

H_THEMTRIP#

EC_KBRST# <42>

SERIRQ <42>LAN_PWR_EN<31>

12

RC131

RC131

<DB>Add WWAN_PWREN

WWAN_OFF# <21>

TOUCH_PAD_PWREN# <43>

12

RC242

RC242

1K_0402_5%

1K_0402_5%

DG V0.9 PCH_OPIRCOMP

Width=12mil,spacing=12mil

L

Max length=500mil

DGPU_PWR_EN SE00000GC00M1

9/12 reserve DGPU_PWR_EN on GPIO85

Add WWAN_OFF# on GPIO87

NGFF_WIFI_3.3_PWREN

WWAN_PWREN

MSATA_SSD_PWREN

SATA1_PWREN

PCH_LAN_RST#

PCH_LAN_WAKE#

PCH_CR_RST#

PCH_CR_WAKE#

I2C_0_SCL

I2C_0_SDA

I2C_1_SDA

I2C_1_SCL

WWAN_OFF#

Boot BI O S Strap

*

10K_0804_8P4R_5%

10K_0804_8P4R_5%

10K_0804_8P4R_5%

10K_0804_8P4R_5%

0

1

4 5

3 6

2 7

1 8

INS35598061

INS35598061

1 2

Boot BIOS LocationPCH_GPIO86

SPI

4 5

3 6

2 7

1 8

@

@

@

@

18

27

36

45

PRH2

PRH2

RC36410K_0402_5% RC36410K_0402_5%

PRH9

PRH9

RPH18

RPH18

+3VS

+3VS

+3V_DSW_P

DSW power choose on page12

*

GPIO27

A A

RC277 10K_0402_5%RC277 10K_0402_5%

1 2

5

EC_PME#

PCH_GPIO27 (Have internal Pull-High)

High: VCCVRM VR Enable

Low: VCCVRM VR Disable

4

Security Classification

Security Classification

Security Classification

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/29 2011/06/29

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

GPIO,UART,I2C

GPIO,UART,I2C

GPIO,UART,I2C

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom