Page 1

A

1 1

B

C

D

E

2 2

Compal Confidential

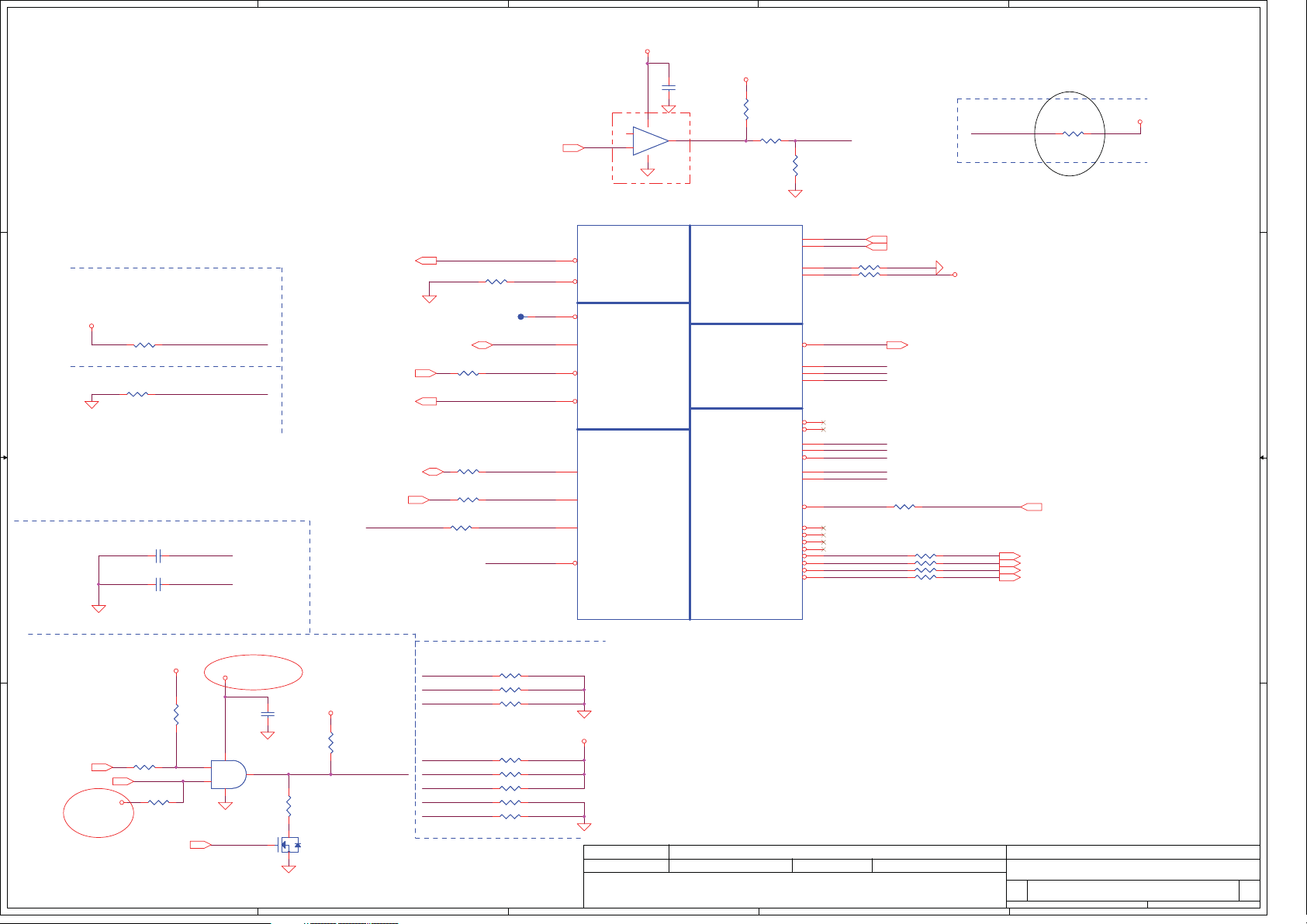

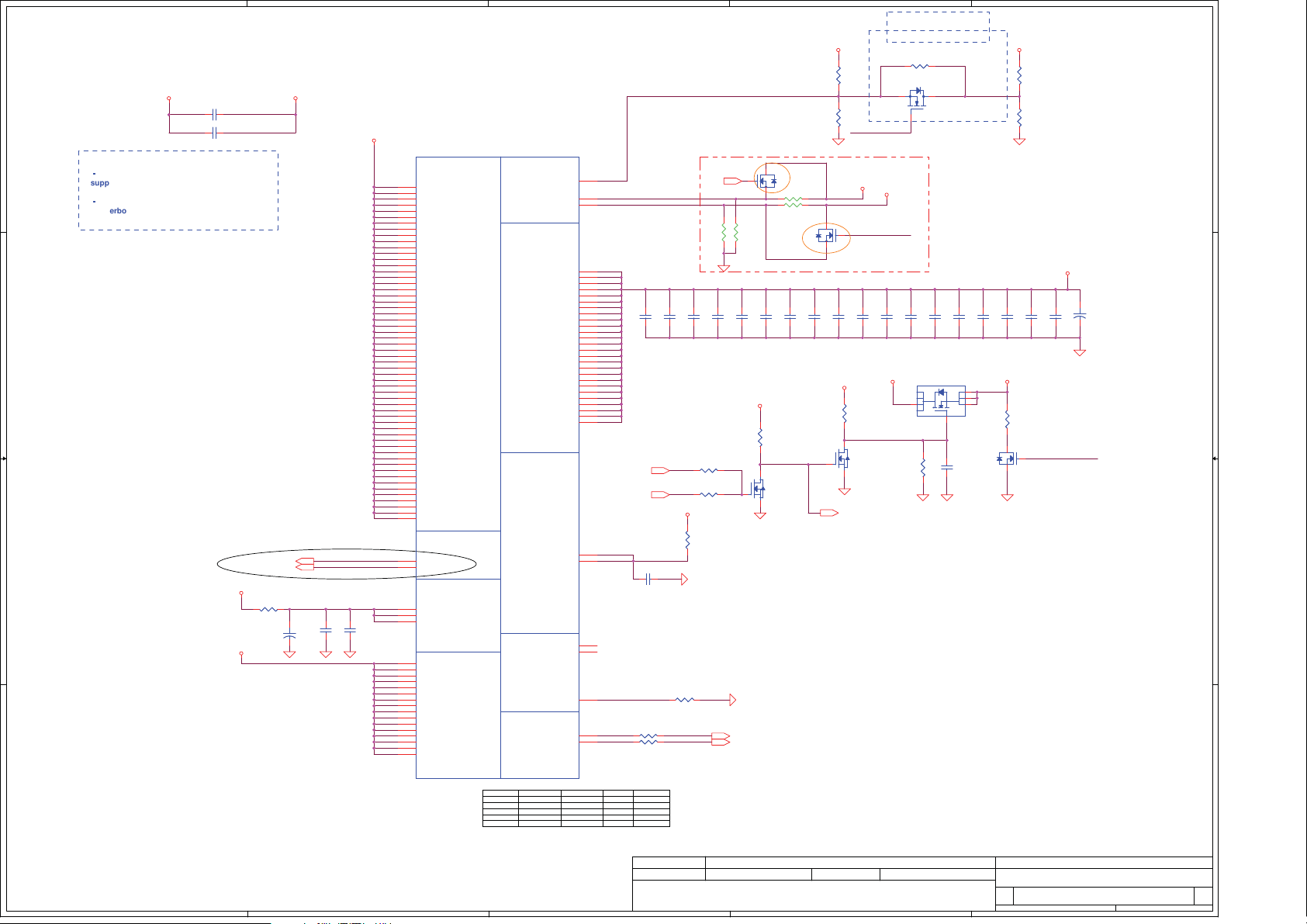

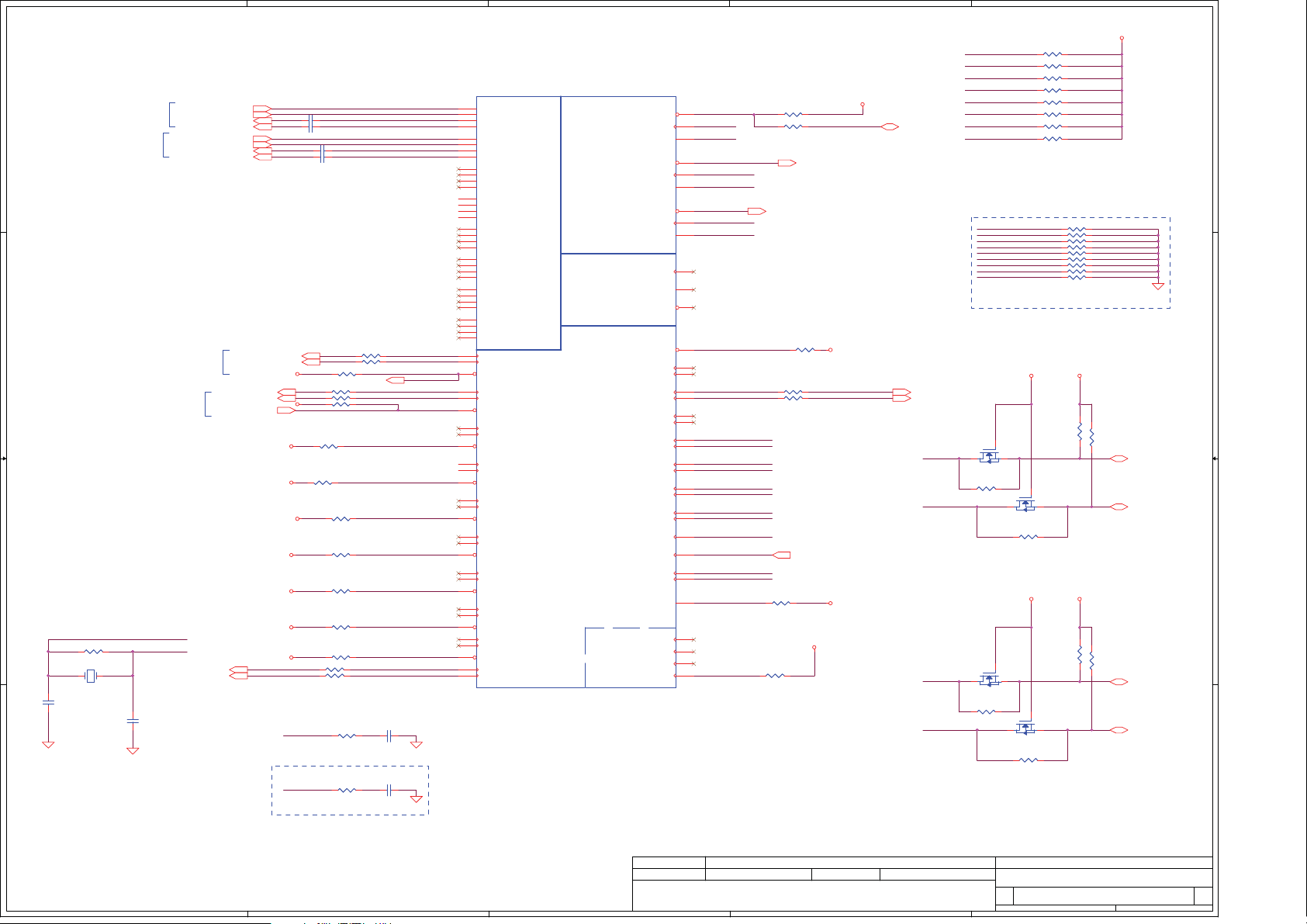

QAU20 M/B Schematics Document

Date : 2011/11/08

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/08/03

2010/08/03

2010/08/03

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

LA-8441P

LA-8441P

LA-8441P

146Monday, November 14, 2011

146Monday, November 14, 2011

146Monday, November 14, 2011

E

0.1

0.1

0.1

Page 2

A

B

C

D

E

Compal Confidential

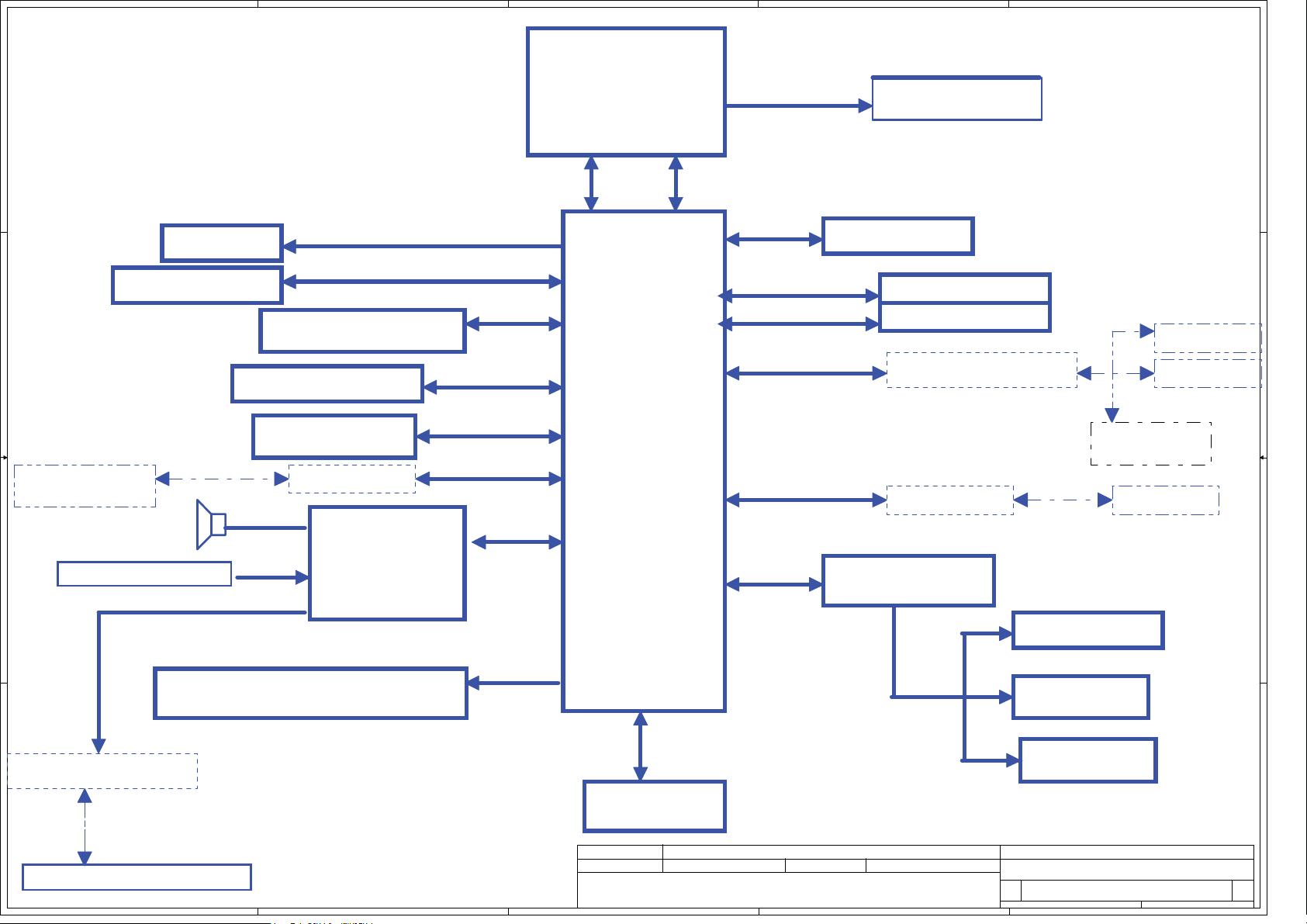

0RGHO1DPH4$8

)LOH1DPH/$3

1 1

,QWHO,Y\%ULGJH

^ϬϬϬϬϰZ:ϭϬ;ϭϯ',njͿ

8/93URFHVVRU

)&%*$

Page 4~10

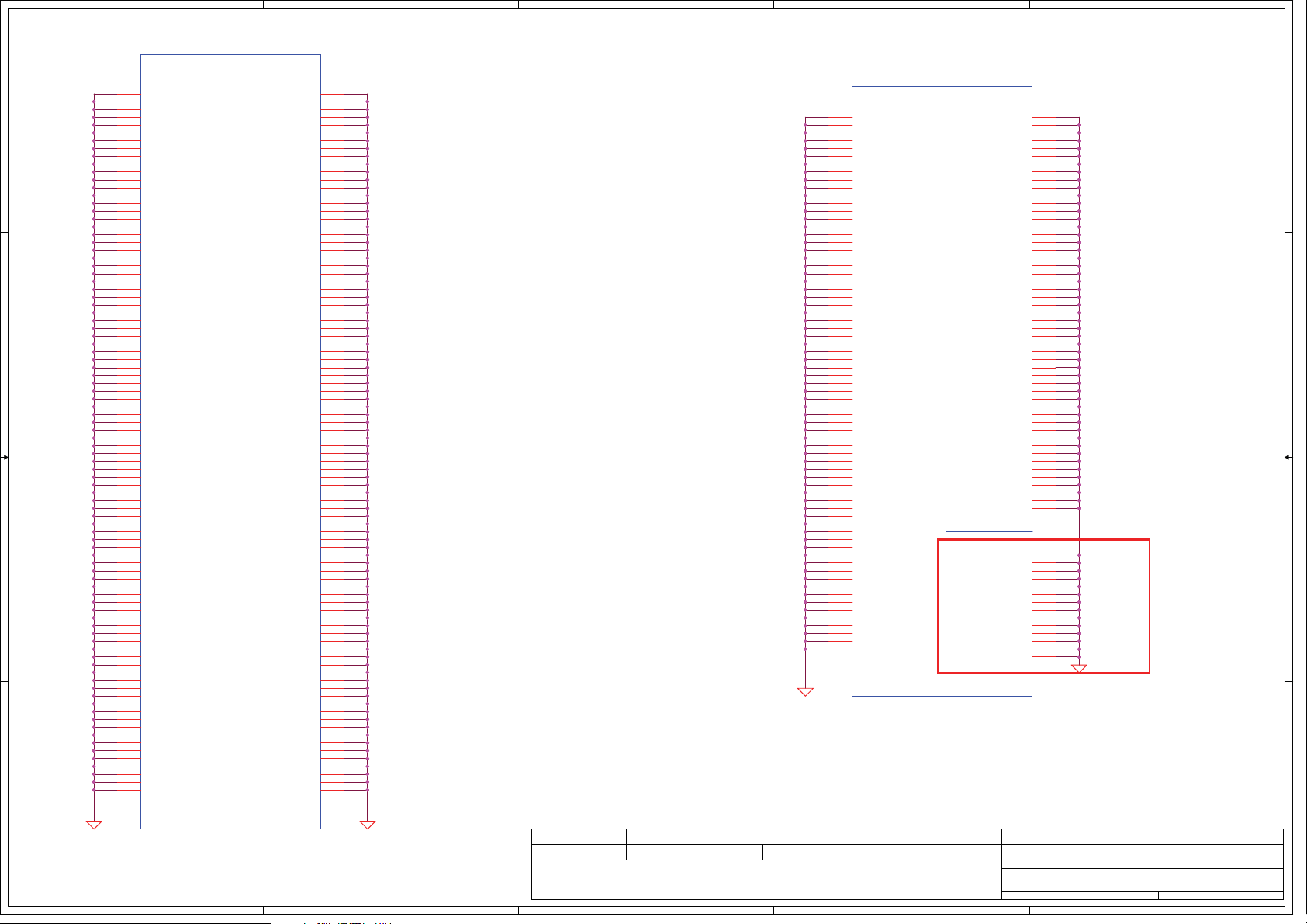

Memory BUS(DDRIII)

1.5V DDRIII 1066/1333/1600 for CR

1.5V DDRIII 1066/1333 for HR

Channel A

(256MX16) X4 chips

2GB/4GB chips

Page 11

DMI x4FDI x8

/9'6&RQQ

0LQL+'0,&RQQ

Page 23

Page 20

1)&

2 2

0XUDWD/;5:+)$$

LVDS

HDMI

SMBus

,QWHO

USB3.0

USB

USB

USB

PCIE2

SATA

SATA

HDA

3DQWKHU3RLQW3&+

6$14

SLQ%*$

USB

+''RQ'RFNLQJ

:RKP

:/$1%70LQL3&,(

6DQGLVNL66'

Port 0

Page 22

Page 24

'RFNLQJ&RQQ

86%&RQQ

Page 26

&DPHUD)URQW0

&DPHUD%DFN0

7R,2ERDUGFRQQ

'RFNLQJ&RQQ

Page 23

Page 25

**36

6,0&DUG

&DUG5HDGHU

576,2ERDUG

.H\ERDUG

$/&49&

3 3

$QDORJ0,&$UUD\

+'$&RGHF

Page 29

USB

670)5'<75

:/&6330&8

*6(1&203$66

/60'/+&75/*$3

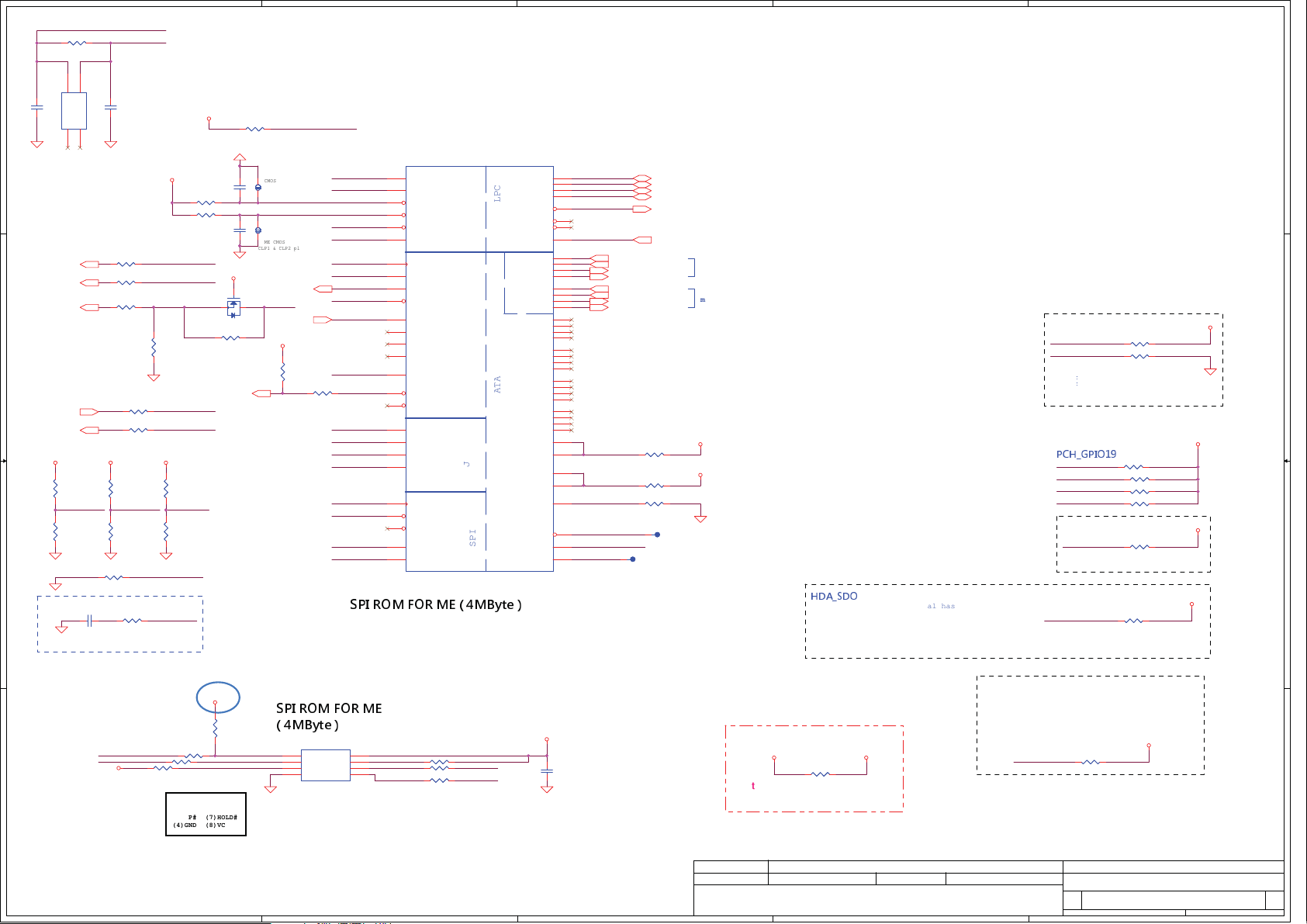

%,2663,520[0%0%

C

3DJHa

LPC

Page 27

Compal Secret Data

Compal Secret Data

2009/08/01 2011/10/18

2009/08/01 2011/10/18

2009/08/01 2011/10/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

/RFDWLRQ8+8+

7R,2ERDUGFRQQ

4 4

Page 25

Page 12

(1(.%

$

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

&RPER-DFNZ+30,&

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

*<526&23(

/*'75/*$3

6707$8775

8)')3136(1625

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

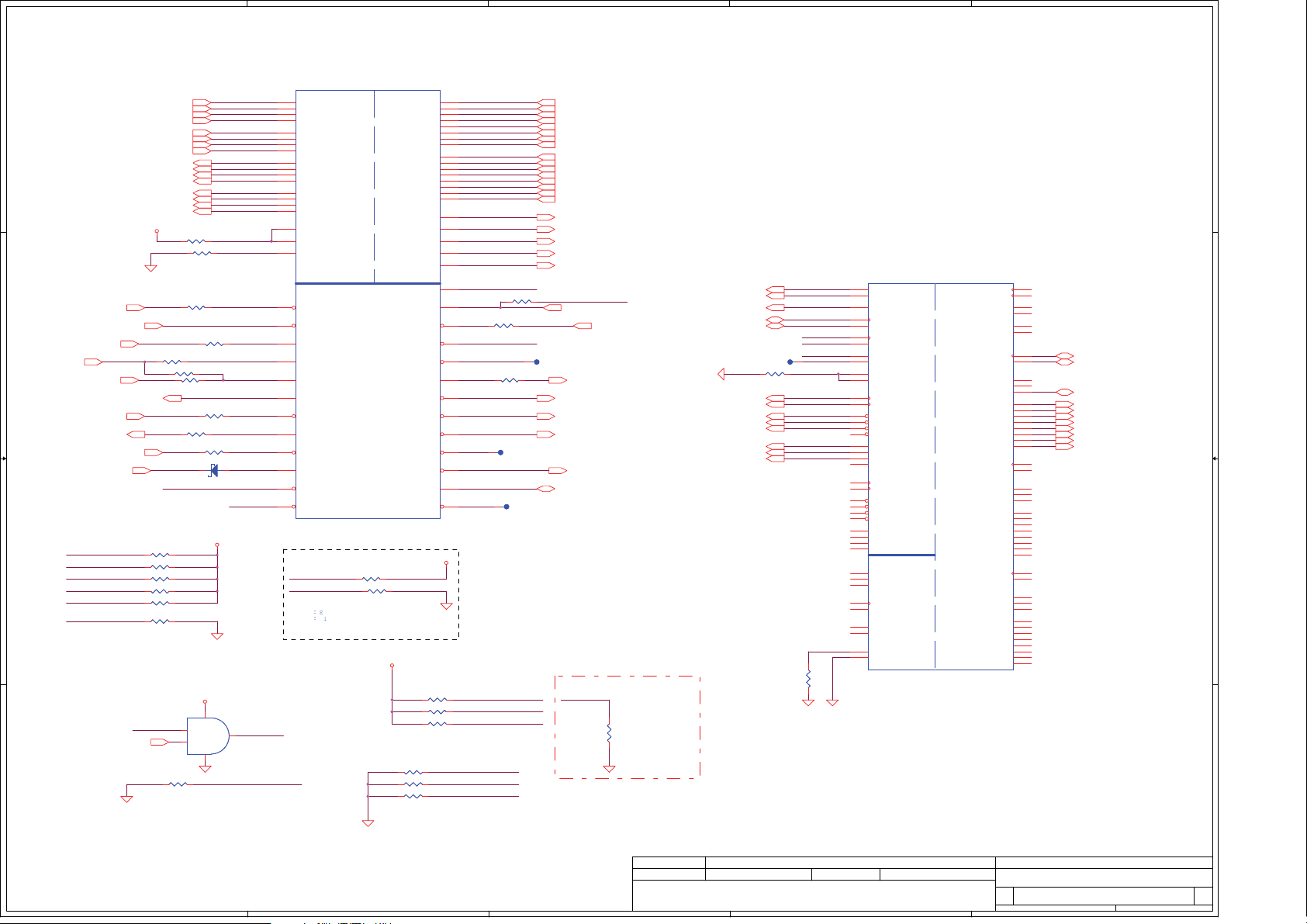

Block Diagrams

Block Diagrams

Block Diagrams

LA-8441P

LA-8441P

LA-8441P

E

246Monday, November 14, 2011

246Monday, November 14, 2011

246Monday, November 14, 2011

of

of

of

0.1

0.1

0.1

SPI

Page 3

A

B

C

D

E

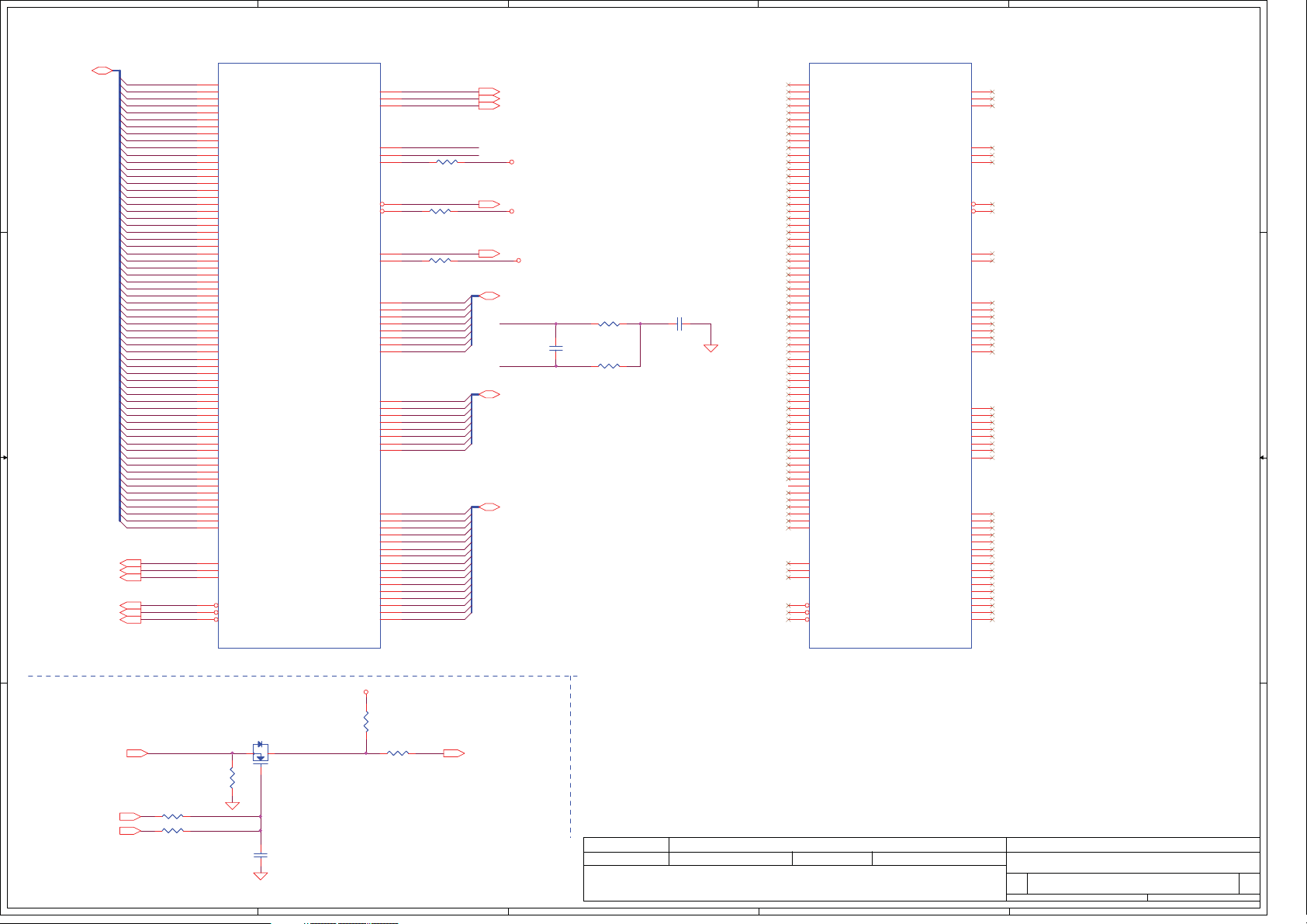

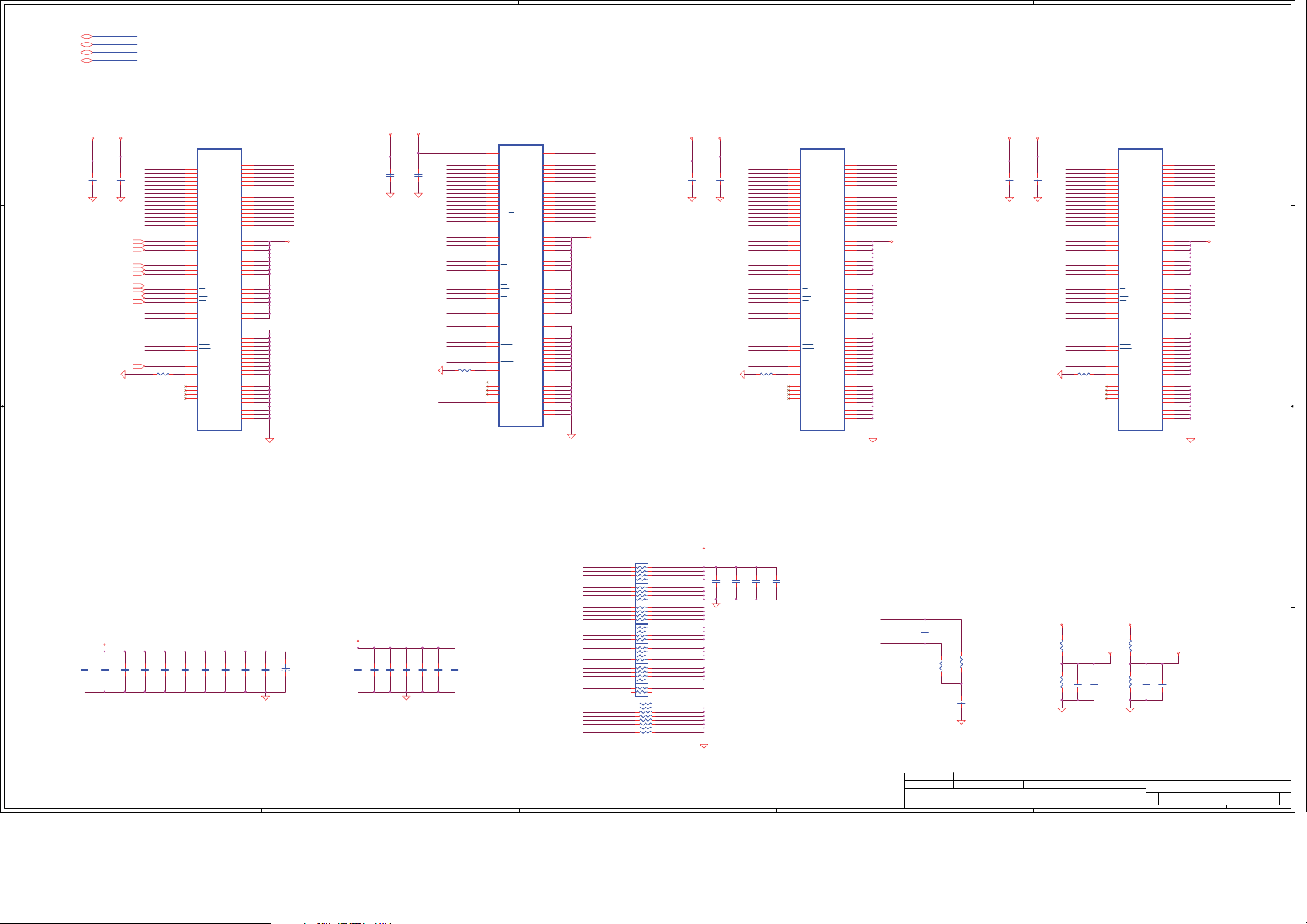

QAZ50 (LA-8101P Ver:0.1)

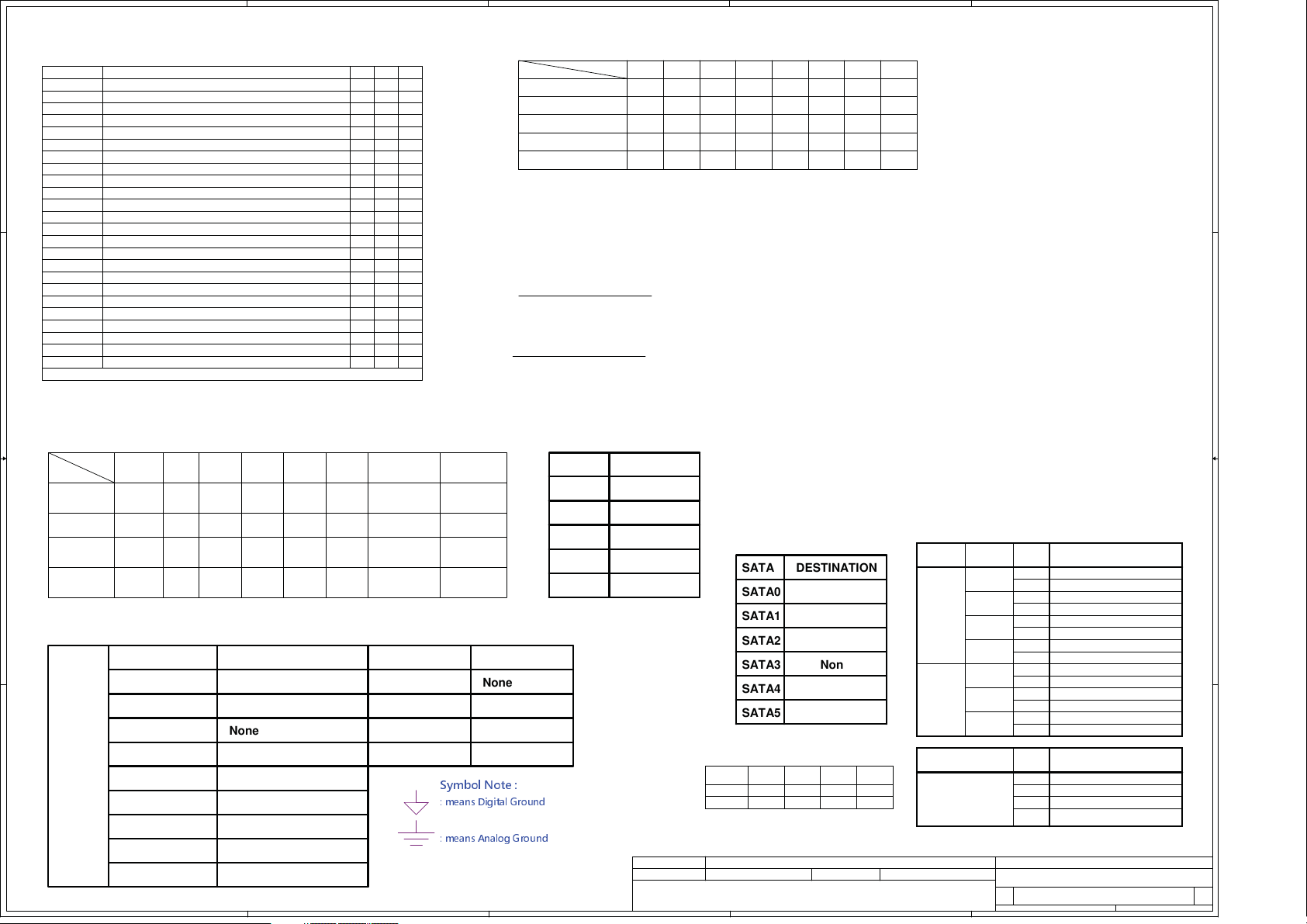

Voltage Rails

Power Plane Description

VIN

BATT+

B+

+CPU_CORE

1 1

+VCCSA ON

+VGFX_CORE Core voltage for UMA graphic

+0.75VS

+CHGRTC BATT+ or Vin to +CHGRTC always on power rail for sequence control

+RTCVCC

+VCCP

+1.5V

+1.5VS

+LG_OUT Voltage for LCD Panel Backlight LED Power

+1.8VS

+3VALW

+3VALW_EC

+LAN_IO

+3V_PCH

+3VS

+5VALW

+5V_PCH

+5VS

2 2

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

2011/08/19 Modify

S1

Adapter power supply (19V)

Battery power supply (7.2V)

AC or battery power rail for power circuit.

Core voltage for CPU

+0.75VP to +0.75VS switched power rail for DDR term inator

RTC power

+VCCP (1.05V ) power for PCH

+1.5VP to +1.5V power rail for DDRIII (1.35V OR 1.5V)

+1.5VS switched power rail

(+5VALW ) to 1.8V switched power rail to PCH & GPU

+3VALW always on power rail

+3VALW always to KBC

+3VALW to +LAN_IO power rail for LAN

+3VALW to +3V_PCH power rail for PCH (Short Jum per)

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

+5VALW to +5V_PCH power rail for PCH (Short resister )

+5VALW to +5VS switched power rail OFFONOFF

S3 S5

N/A N/A N/A

N/A N/A N/A

OFF

ON

OFF OFFVoltage for CPU SA RALL

ON

OFF OFF

ON

OFF OFF

ON ON*

ON

ON

ON

OFF OFF

ON ON

ON

OFF OFF

ON

OFF OFF

OFF

ON

ON

ON ON*

ON ON ON*

ON ON

ON ON

OFF

ON

ON ON*

ON

ON ON

N/AN/AN/A

OFF

ONON

OFF

OFF

ON*

ON*

OFF

ON*

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

EC SM Bus1 address

Device

Smart Battery

Address

0001 011X b

EC SM Bus2 address

Device

PCH ( Reserve)

Address

1010 0110b

SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

LOW

OFF

OFF

OFF

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA PCH

3 3

PCH_SMLCLK

PCH_SMLDATA

KB9012

KB9012

PCH

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLK

CLKOUT_PCIE3

CLKOUT_PCIE4

4 4

CLKOUT_PCIE5

CLKOUT_PCIE7 None

CLKOUT_PEG_B

A

2011/07/28 Modify

MINI2

MINI1

BATT

V

X

X

XX

(WLan1)

(mSATA)

X

X

XX

VV

X

DESTINATIONDIFFERENTIAL

10/100/1G LAN

MINI CARD WLAN

None

CARD READER

None

None

NoneCLKOUT_PCIE6

None

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA

XX

O

V

VO

X

FLEX CLOCKS DESTINATION

CLKOUTFLEX0

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

B

X

None

None

None

None

Symbol Note :

: means Digital Ground

: means Analog Ground

CLKOUT

PCI0

PCI1

PCI2

PCI3

PCI4

DESTINATION

PCH_LPBACK

PCI_LPC

None

None

None

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

DESTINATION

m-SATA,JSSD1

None

None

None

None

None

2011/08/19 Modify

CONN@@Option

X

CR UMA

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

X

Compal Secret Dat a

Compal Secret Dat a

2009/08/01 2011/10/18

2009/08/01 2011/10/18

2009/08/01 2011/10/18

Compal Secret Dat a

Deciphered D ate

Deciphered D ate

Deciphered D ate

D

USB Port Table

USB 2.0 USB 1.1 Port

UHCI0

EHCI1

EHCI2

USB 3.0 Port

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

USB/B ( External)

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

2011/07/12 Check

2 External

0

1

2

3

4

5

6

7

8

9

10

11

12

13

1

2

3

4

LA-8441P

LA-8441P

LA-8441P

USB Port

USB/B ( External)

USB/B ( External)

Mini Card(WLAN)

Camera

Test Point (RH274,RH310)

2 External

USB Port

USB/B ( External)

USB/B ( External)

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Notes List

Notes List

Notes List

E

0.1

0.1

346M onday, November 14, 2011

346M onday, November 14, 2011

346M onday, November 14, 2011

0.1

of

of

of

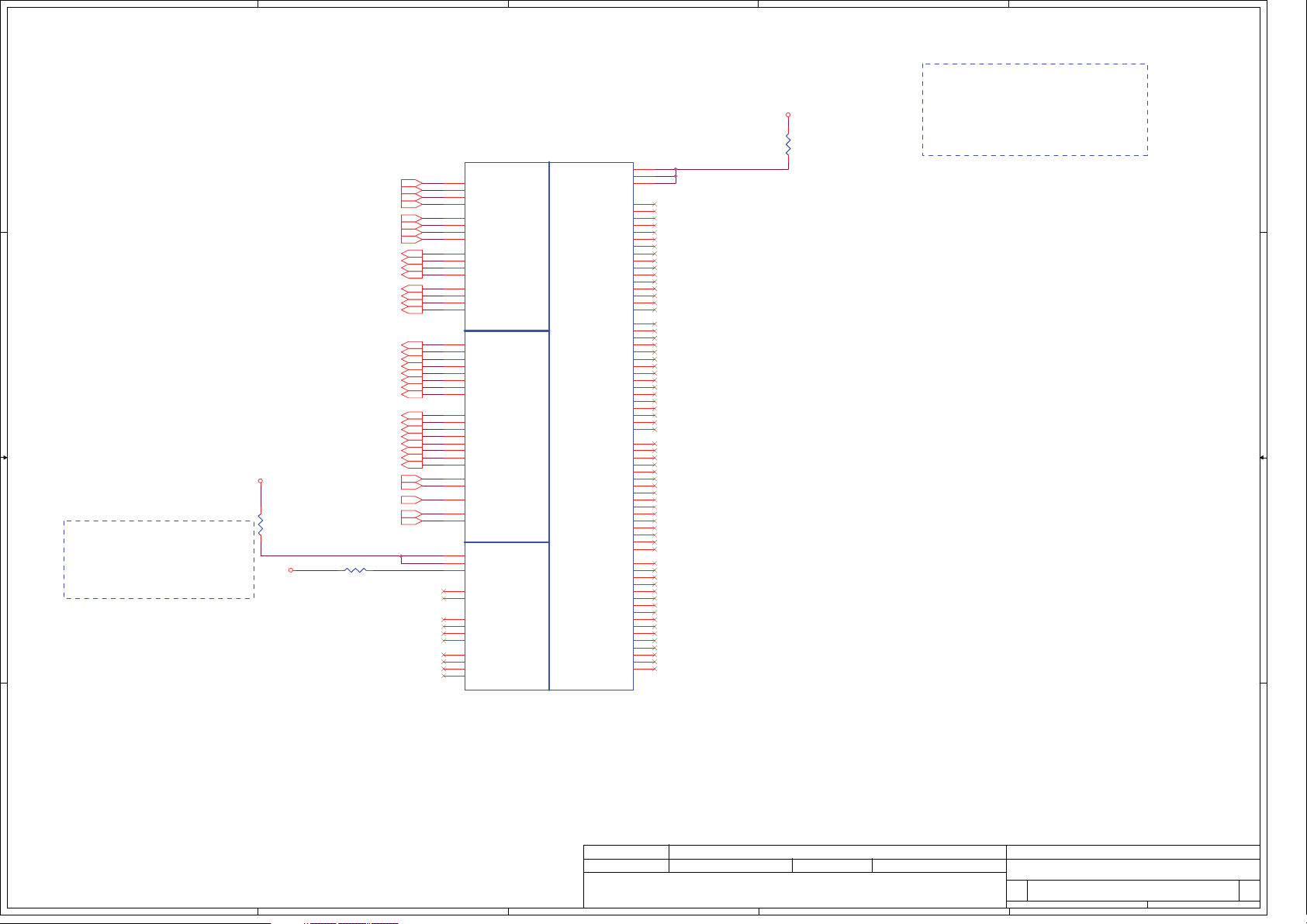

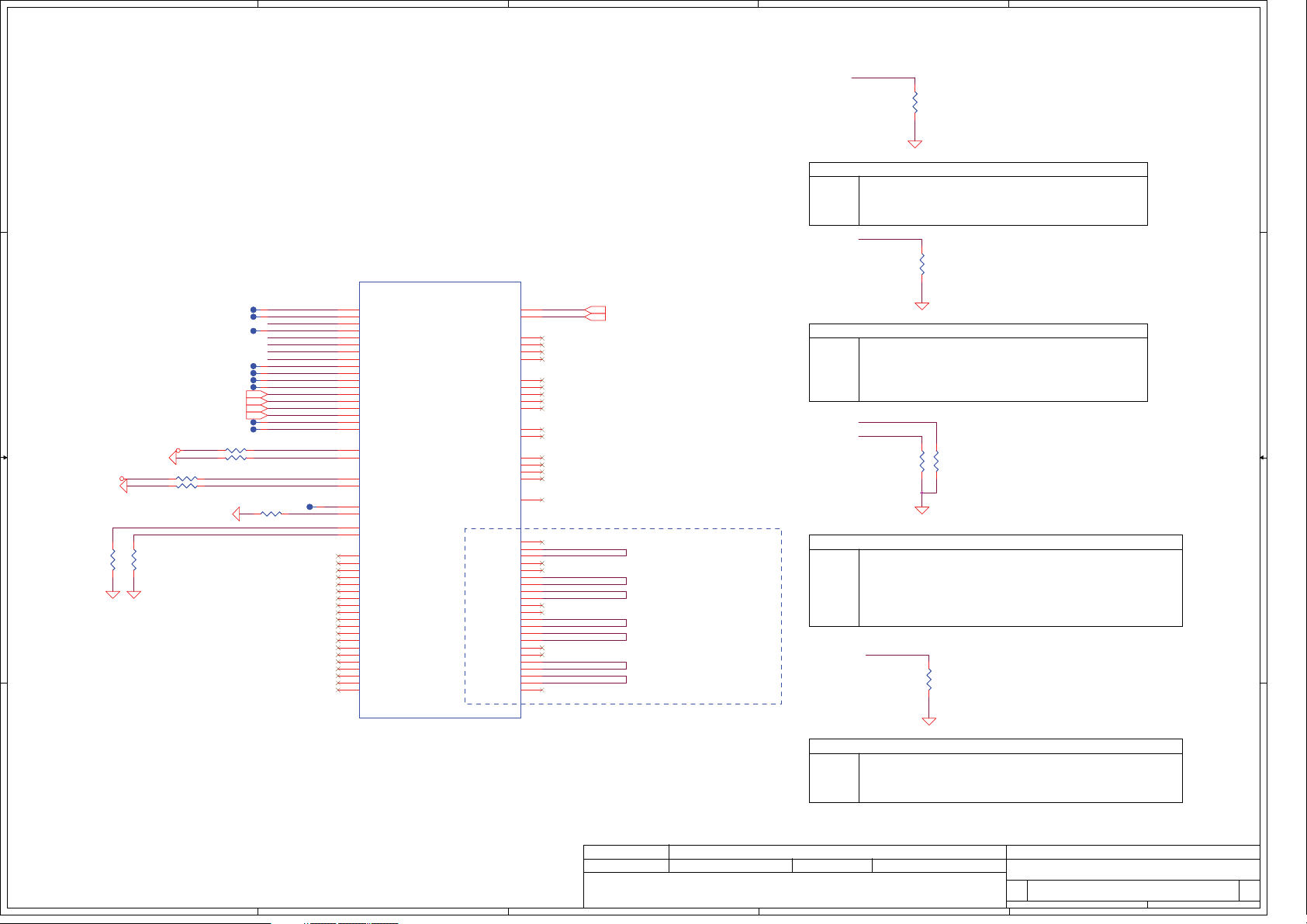

Page 4

5

D D

C C

+VCCP

12

RC2

RC2

24.9_0402_1%

24.9_0402_1%

eDP_COMPIO and ICOMPO signals

should be shorted near balls

B B

and routed with typical

impedance <25 mohms

+VCCP

RC86 10K_0402_5%@RC86 10K_0402_5%@

DMI_CRX_PTX_N0{14}

DMI_CRX_PTX_N1{14}

DMI_CRX_PTX_N2{14}

DMI_CRX_PTX_N3{14}

DMI_CRX_PTX_P0{14}

DMI_CRX_PTX_P1{14}

DMI_CRX_PTX_P2{14}

DMI_CRX_PTX_P3{14}

DMI_CTX_PRX_N0{14}

DMI_CTX_PRX_N1{14}

DMI_CTX_PRX_N2{14}

DMI_CTX_PRX_N3{14}

DMI_CTX_PRX_P0{14}

DMI_CTX_PRX_P1{14}

DMI_CTX_PRX_P2{14}

DMI_CTX_PRX_P3{14}

FDI_CTX_PRX_N0{14}

FDI_CTX_PRX_N1{14}

FDI_CTX_PRX_N2{14}

FDI_CTX_PRX_N3{14}

FDI_CTX_PRX_N4{14}

FDI_CTX_PRX_N5{14}

FDI_CTX_PRX_N6{14}

FDI_CTX_PRX_N7{14}

FDI_CTX_PRX_P0{14}

FDI_CTX_PRX_P1{14}

FDI_CTX_PRX_P2{14}

FDI_CTX_PRX_P3{14}

FDI_CTX_PRX_P4{14}

FDI_CTX_PRX_P5{14}

FDI_CTX_PRX_P6{14}

FDI_CTX_PRX_P7{14}

FDI_FSYNC0{14}

FDI_FSYNC1{14}

FDI_INT{14}

FDI_LSYNC0{14}

FDI_LSYNC1{14}

1 2

4

EDP_COMP

UCPU1A

UCPU1A

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COM PIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX [0]

AA4

eDP_TX [1]

AE10

eDP_TX [2]

AE6

eDP_TX [3]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

3

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

eDP

eDP

PEG_COMP

RC1

RC1

24.9_0402_1%

24.9_0402_1%

+VCCP

2

PEG_ICOMPI and RCOMPO signals should be

shorted and routed

with - max length = 500 mils - typi cal

impedance = 43 mohms

12

PEG_ICOMPO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/04/26 2011/10/18

2010/04/26 2011/10/18

2010/04/26 2011/10/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

LA-8101P

1

446Monday, November 14, 2011

446Monday, November 14, 2011

446Monday, November 14, 2011

of

of

of

0.1

0.1

0.1

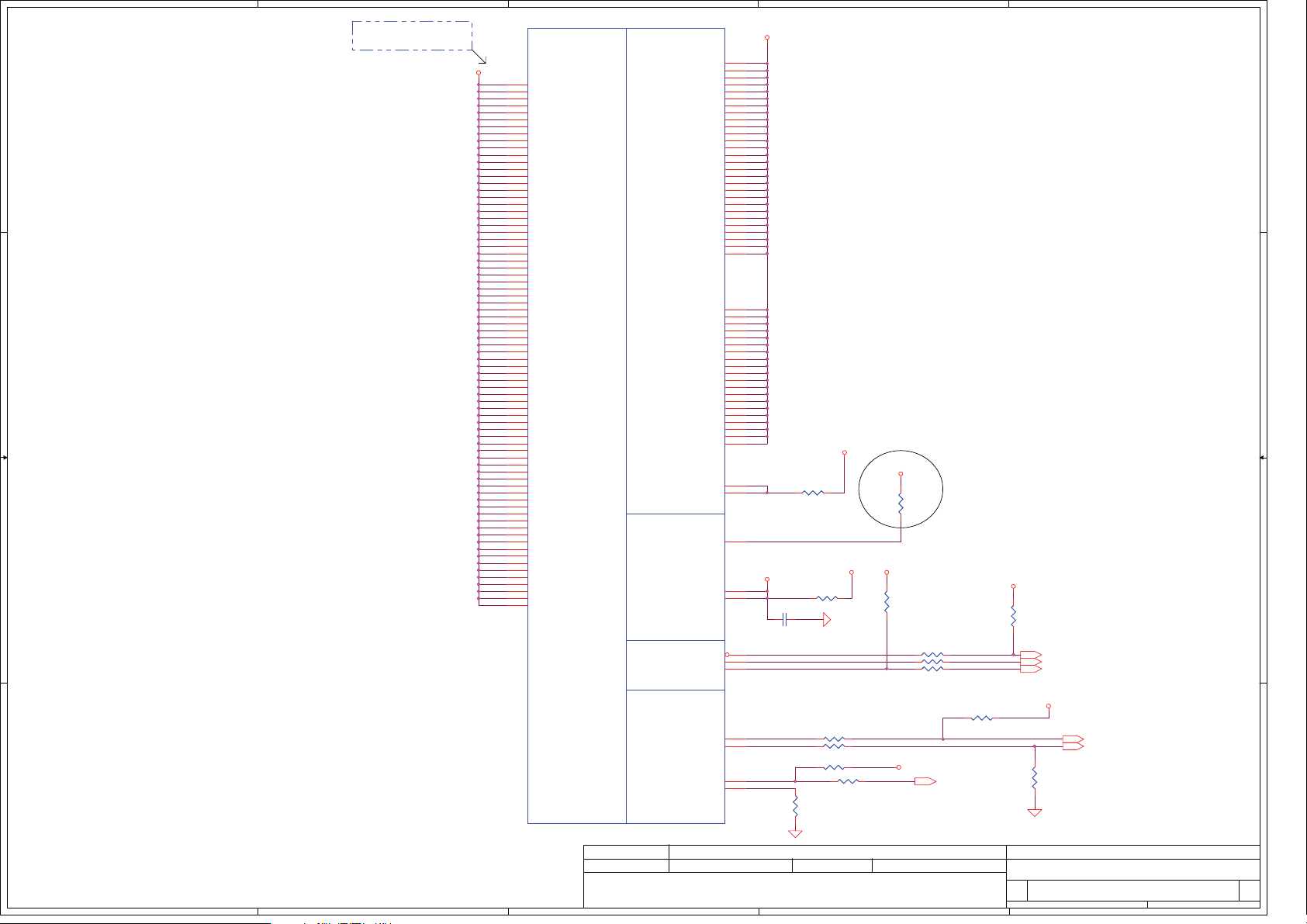

Page 5

5

4

3

Buffered reset to CPU

+3VS

2

1

1

CC1

CC1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

D D

UCPU1B

UCPU1B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

PLT_RST#

PLT_RST#{15,25,28}

This pin is for compability with future

platforms. A pull up resistor to VCCIO is

required if connected to the DF_TVS strap

on the PCH.

H_SNB_IVB#{16}

PROC_DETECT (Processor Detect): pulled to

ground on the processor package. There is no

connection to the processor silicon for this

signal. System board designers may use this

+VCCP

C C

Processor Pullups

RC8 62_0402_5%RC8 62_0402_5%

RC11 10K_0402_5%RC11 10K_0402_5%

12

12

H_PROCHOT#

H_CPUPWRGD_R

signal to determine if the processor is present

H_PROCHOT#{28}

H_THRMTRIP#{16}

H_PM_SYNC{14}

H_CPUPWRGD{16}

For EMI Request

H_CPUPWRGD

CC4

CC4

1 2

0.1U_0402_16V4Z

B B

0.1U_0402_16V4Z

XDP_DBRESET#

CC5

CC5

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CC5 near RC17

1 2

RC7 10K_0402_5%@RC7 10K_0402_5%@

T5PAD@T5PAD

@

H_PECI{16,28} H_DRAMRST# {6}

H_PROCHOT#_R

1 2

RC10 56_0402_5%RC10 56_0402_5%

H_THEMTRIP#

1 2

RC13 0_0402_5%RC13 0_0402_5%

1 2

RC16 0_0402_5%RC16 0_0402_5%

1 2

RC18 130_0402_5%RC18 130_0402_5%

H_PM_SYNC_R

H_CPUPWRGD_R

PM_DRAM_PWRGD_RPM_SYS_PWRGD_BUF

BUF_CPU_RST#

5

UC1

UC1

1

P

NC

Y

2

A

G

3

SN74LVC1G07DCKR_SC70-5

SN74LVC1G07DCKR_SC70-5

4

MISC THERMAL PWR MANAGEMENT

MISC THERMAL PWR MANAGEMENT

+VCCP

12

RC3

RC3

75_0402_5%

75_0402_5%

RC4

RC4

43_0402_1%

BUFO_CPU_RST# BUF_CPU_RST#

43_0402_1%

1 2

12

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

JTAG & BPM

JTAG & BPM

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

@

@

RC6

RC6

0_0402_5%

0_0402_5%

J3

H2

RC12 1K_0402_1%RC12 1K_0402_1%

AG3

RC35 1K_0402_1%RC35 1K_0402_1%

AG1

H_DRAMRST#

AT30

SM_RCOMP0

BF44

SM_RCOMP1

BE43

SM_RCOMP2

BG43

N53

N55

XDP_TCK

L56

XDP_TMS

L55

XDP_TRST#

J58

M60

L59

XDP_DBRESET#_R

K58

G58

E55

E59

G55

XDP_BPM#4_R

G59

XDP_BPM#5_R

H60

XDP_BPM#6_R

J59

XDP_BPM#7_R

J61

1 2

1 2

XDP_TDI

XDP_TDO

CLK_CPU_DMI {13}

CLK_CPU_DMI# {13}

RC17 0_0402_5%RC17 0_0402_5%

1 2

RC19 0_0402_5%@RC19 0_0402_5%@

1 2

RC20 0_0402_5%@RC20 0_0402_5%@

1 2

RC21 0_0402_5%@RC21 0_0402_5%@

1 2

RC22 0_0402_5%@RC22 0_0402_5%@

1 2

XDP_DBRESET#

+VCCP

XDP_DBRESET#

RC5 1K_0402_5%RC5 1K_0402_5%

circuit check 10k

XDP_DBRESET# {14}

CFG12 {7}

CFG13 {7}

CFG14 {7}

CFG15 {7}

12

+3VS

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

Issued Date

Issued Date

Issued Date

SA00004SX00

3

Compal Secret Data

Compal Secret Data

2010/4/26 2011/10/18

2010/4/26 2011/10/18

2010/4/26 2011/10/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

LA-8101P

546Monday, November 14, 2011

546Monday, November 14, 2011

546Monday, November 14, 2011

of

of

1

of

0.1

0.1

0.1

Follow PBL22 LA-7391 PR04

SYS_PWROK{14}

PM_DRAM_PWRGD{14}

A A

+3V_PCH

Modify

2011/10/03

RUN_ON_CPU1.5VS3#{9}

RC84

RC84

10K_0402_5%

10K_0402_5%

RC27

@ RC27

@

0_0402_5%

0_0402_5%

1 2

RC28

RC28

1 2

200_0402_5%

200_0402_5%

5

+3VS

12

1

2

Part Number = SA00003Y000

Part Number = SA00003Y000

Modify

+3V_PCH

2011/10/03

1

2

UC2

UC2

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

5

P

B

4

O

A

G

3

RUN_ON_CPU1.5VS3#

2

G

G

+1.5V_CPU_VDDQ

CC2

CC2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

12

@

@

RC29

RC29

39_0402_5%

39_0402_5%

13

D

D

@

@

QC1

QC1

2N7002_SOT23

2N7002_SOT23

S

S

12

RC25

RC25

200_0402_5%

200_0402_5%

PM_SYS_PWRGD_BUF

DDR3 Compensation Signals

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PU/PD for JTAG signals

XDP_TMS

RC30 51_0402_5%RC30 51_0402_5%

XDP_TDI

RC31 51_0402_5%RC31 51_0402_5%

XDP_TDO

RC32 51_0402_5%RC32 51_0402_5%

XDP_TCK

RC33 51_0402_5%RC33 51_0402_5%

XDP_TRST#

RC34 51_0402_5%RC34 51_0402_5%

4

RC23 140_0402_1%RC23 140_0402_1%

RC24 25.5_0402_1%

RC24 25.5_0402_1%

RC26 200_0402_1%RC26 200_0402_1%

SD00000X700

SD00000X700

12

12

12

12

12

12

12

12

+VCCP

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Page 6

5

UCPU1C

DDR_A_D[0..63]{11}

D D

C C

DDR_A_BS0{11}

B B

DDR_A_BS1{11}

DDR_A_BS2{11}

DDR_A_CAS#{11}

DDR_A_RAS#{11}

DDR_A_WE#{11}

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

UCPU1C

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

4

M_CLK_DDR0

AU36

M_CLK_DDR#0

AV36

DDR_CKE0_DIMMA

AY26

M_CLK_DDR1

AT40

M_CLK_DDR#1

AU40

1 2

BB26

RC81 36.5_0402_1%RC81 36.5_0402_1%

BB40

1 2

BC41

RC82 36.5_0402_1%RC82 36.5_0402_1%

AY40

1 2

BA41

RC83 36.5_0402_1%RC83 36.5_0402_1%

DDR_A_DQS#0

AL11

DDR_A_DQS#1

AR8

DDR_A_DQS#2

AV11

DDR_A_DQS#3

AT17

DDR_A_DQS#4

AV45

DDR_A_DQS#5

AY51

DDR_A_DQS#6

AT55

DDR_A_DQS#7

AK55

DDR_A_DQS0

AJ11

DDR_A_DQS1

AR10

DDR_A_DQS2

AY11

DDR_A_DQS3

AU17

DDR_A_DQS4

AW45

DDR_A_DQS5

AV51

DDR_A_DQS6

AT56

DDR_A_DQS7

AK54

DDR_A_MA0

BG35

DDR_A_MA1

BB34

DDR_A_MA2

BE35

DDR_A_MA3

BD35

DDR_A_MA4

AT34

DDR_A_MA5

AU34

DDR_A_MA6

BB32

DDR_A_MA7

AT32

DDR_A_MA8

AY32

DDR_A_MA9

AV32

DDR_A_MA10

BE37

DDR_A_MA11

BA30

DDR_A_MA12

BC30

DDR_A_MA13

AW41

DDR_A_MA14

AY28

DDR_A_MA15

AU26

M_CLK_DDR0 {11}

M_CLK_DDR#0 {11}

DDR_CKE0_DIMMA {11}

+0.75VS

DDR_CS0_DIMMA# {11}

+0.75VS

M_ODT0 {11}

+0.75VS

DDR_A_DQS#[0..7] {11}

M_CLK_DDR1

1

M_CLK_DDR#1

DDR_A_DQS[0..7] {11}

DDR_A_MA[0..15] {11}

2

30.1_0402_1%

30.1_0402_1%

RC87

RC87

CC10

CC10

2P_0402_50V8C

2P_0402_50V8C

RC88

RC88

30.1_0402_1%

30.1_0402_1%

3

12

12

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CC11

CC11

12

BD13

BF12

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BF8

AL4

AL1

UCPU1D

UCPU1D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

2

BA34

SB_CK[0]

AY34

SB_CK#[0]

AR22

SB_CKE[0]

BA36

SB_CK[1]

BB36

SB_CK#[1]

BF27

SB_CKE[1]

BE41

SB_CS#[0]

BE47

SB_CS#[1]

AT43

SB_ODT[0]

BG47

SB_ODT[1]

AL3

SB_DQS#[0]

AV3

SB_DQS#[1]

BG11

SB_DQS#[2]

BD17

SB_DQS#[3]

BG51

SB_DQS#[4]

BA59

SB_DQS#[5]

AT60

SB_DQS#[6]

AK59

SB_DQS#[7]

AM2

SB_DQS[0]

AV1

SB_DQS[1]

BE11

SB_DQS[2]

BD18

SB_DQS[3]

BE51

SB_DQS[4]

BA61

SB_DQS[5]

AR59

SB_DQS[6]

AK61

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

BF32

SB_MA[0]

BE33

SB_MA[1]

BD33

SB_MA[2]

AU30

SB_MA[3]

BD30

SB_MA[4]

AV30

SB_MA[5]

BG30

SB_MA[6]

BD29

SB_MA[7]

BE30

SB_MA[8]

BE28

SB_MA[9]

BD43

SB_MA[10]

AT28

SB_MA[11]

AV28

SB_MA[12]

BD46

SB_MA[13]

AT26

SB_MA[14]

AU22

SB_MA[15]

1

IVY-BRIDGE_BGA1 023

IVY-BRIDGE_BGA1 023

SA00004SX00

SA00004SX00

+1.5V

12

RC36

RC36

1K_0402_5%

1K_0402_5%

D

S

D

S

DDR3_DRAMRST#_RH_DRAMRST#

1 2

13

QC2

QC2

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

G

G

2

1

CC3

CC3

0.047U_0402_16V4Z

0.047U_0402_16V4Z

2

H_DRAMRST#{5}

RC38

RC38

4.99K_0402_1%

4.99K_0402_1%

A A

DRAMRST_CNTRL_PCH{9,13}

DRAMRST_CNTRL_EC{28}

5

RC39

RC39

0_0402_5%@

0_0402_5%@

1 2

RC53

RC53

1 2

0_0402_5%

0_0402_5%

DRAMRST_CNTRL

RC37

RC37

1K_0402_5%

1K_0402_5%

1 2

4

DDR3_DRAMRST# {11}

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/04/26 2011/10/18

2010/04/26 2011/10/18

2010/04/26 2011/10/18

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

LA-8101P

1

0.1

0.1

0.1

of

of

of

646Monday, November 14, 2011

646Monday, November 14, 2011

646Monday, November 14, 2011

Page 7

5

4

3

2

1

CFG Straps for Processor

CFG2

D D

12

RC40

RC40

1K_0402_1%

1K_0402_1%

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

UCPU1E

UCPU1E

CFG0

T9T9

CFG1

T6T6

CFG2

CFG3

T11T11

CFG4

C C

CFG12{5}

CFG13{5}

CFG14{5}

CFG15{5}

RC42 49.9_0402_1%RC42 49.9_0402_1%

+CPU_CORE

RC44 49.9_0402_1%RC44 49.9_0402_1%

+VGFX_CORE

12

RC46

RC46

1K_0402_1%

B B

1K_0402_1%

@

@

1 2

RC45 49.9_0402_1%RC45 49.9_0402_1%

CPU_RSVD6

CPU_RSVD7

12

RC47

RC47

1K_0402_1%

1K_0402_1%

@

@

1 2

RC43 49.9_0402_1%RC43 49.9_0402_1%

12

CFG5

CFG6

CFG7

CFG8

T8T8

CFG9

T14T14

CFG10

T15T15

CFG11

T16T16

CFG12

CFG13

CFG14

CFG15

CFG16

T17T17

CFG17

T18T18

12

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

1 2

RC9 0_0402_5%RC9 0_0402_5%

VCC_VAL_SENSE

VSS_VAL_SENSE

T25T25

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

BCLK_ITP

BCLK_ITP#

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

CLK_RES_ITP {13}

CLK_RES_ITP# {13}

DC_TEST_C4_D3

DC_TEST_A59_C59

DC_TEST_A61_C61

DC_TEST_BE59_BE61

DC_TEST_BG59_BG61

DC_TEST_BE3_BG3

DC_TEST_BE1_BG1

These pins are for solder joint

reliability and non-critical to

function. For BGA only.

Display Port Presence Strap

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

CFG4

*

1K_0402_1%

1K_0402_1%

11: (Default) x16 - Device 1 functions 1 and 2 disabled

*

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

12

RC41

RC41

1K_0402_1%

1K_0402_1%

@

@

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

CFG7

@RC48

@

RC48

12

12

12

@RC50

@

RC49

@RC49

@

1K_0402_1%

1K_0402_1%

RC50

1K_0402_1%

1K_0402_1%

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/04/26 2011/10/18

2010/04/26 2011/10/18

2010/04/26 2011/10/18

PEG DEFER TRAINING

CFG7

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1: (Default) PEG Train immediately following

*

xxRESETB de assertion

0: PEG Wait for BIOS for training

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

LA-8101P

0.1

0.1

746Monday, November 14, 2011

746Monday, November 14, 2011

1

746Monday, November 14, 2011

0.1

of

of

of

Page 8

5

D D

C C

B B

4

ULV type CPU

+CPU_CORE

28A

UCPU1F

UCPU1F

3

POWER

POWER

+VCCP

2

1

18A

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

CORE SUPPLY

CORE SUPPLY

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

+1.05VS_VCCPQ

AM25

AN22

PEG IO AND DDR IO

PEG IO AND DDR IO

RAILS

RAILS

RC51

RC51

1 2

0_0805_5%

0_0805_5%

VCCP_PWRCTRL_R

choose low or high

RC54

RC54

1 2

0_0805_5%

0_0805_5%

1 2

CC73 1U_0402_6.3V6KCC73 1U_0402_6.3V6K

+VCCP

+VCCP +VCCP

+VCCP

12

RC52

RC52

75_0402_5%@

75_0402_5%@

Voltage selection for VCCIO: For Huron

River platforms, this pin must be pulled high

on the motherboard.

12

RC55

RC55

130_0402_5%

130_0402_5%

+VCCP

12

RC56

RC56

75_0402_5%

75_0402_5%

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

3

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

SENSE LINES SVID QUIET

2010/04/26 2011/10/18

2010/04/26 2011/10/18

2010/04/26 2011/10/18

A A

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, IN C. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

H_CPU_SVIDCLK

B43

H_CPU_SVIDDAT

C44

VCCSENSE_R

F43

VSSSENSE_R

G43

VCCIO_SENSE_R

AN16

AN17

RC61 0_0402_5%RC61 0_0402_5%

1 2

RC62 0_0402_5%RC62 0_0402_5%

1 2

RC63

RC63

1 2

10_0402_1%

10_0402_1%

RC65 0_0402_5%RC65 0_0402_5%

1 2

12

10_0402_1%

10_0402_1%

RC66

RC66

SD034100A80

SD034100A80

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

H_CPU_SVIDALRT#

A44

RC57 43_0402_1%RC57 43_0402_1%

1 2

RC58 0_0402_5%RC58 0_0402_5%

1 2

RC59 0_0402_5%RC59 0_0402_5%

1 2

RC60 100_0402_1%RC60 100_0402_1%

+VCCP

VCCIO_SENSE {39}

2

VR_SVID_ALRT# {43}

VR_SVID_CLK {43}

VR_SVID_DATA {43}

+CPU_CORE

1 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Place the PU

resistors close to CPU

VCCSENSE {43}

12

VSSSENSE {43}

RC64

RC64

100_0402_1%

100_0402_1%

Place the PU

resistors close to VR

Compal Electronics, Inc.

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

LA-8101P

1

0.1

0.1

846Monday, November 14, 2011

846Monday, November 14, 2011

846Monday, November 14, 2011

0.1

of

of

of

Page 9

5

+1.5V_CPU_VDDQ +1.5V

CC74 0.1U_0402_10V7KCC74 0.1U_0402_10V7K

D D

Can connect to GND if motherboard only

ɄɄɄɄ

supports external graphics and if GFX VR is not

stuffed in a common motherboard design,

ɄɄɄɄ

VAXG can be left floating in a common

motherboard desig n (Gfx VR keeps VAXG from

floating) if the VR is stuffed

C C

B B

A A

12

CC75 0.1U_0402_10V7KCC75 0.1U_0402_10V7K

12

VCC_AXG_SENSE{43}

VSS_AXG_SENSE{43}

+1.8VS

0_0805_5%

0_0805_5%

1 2

+VCCSA

RC77

RC77

CC120

CC120

1

+

+

2

330U_D2_2VM_R6M

330U_D2_2VM_R6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

+VCCSA

+VGFX_CORE

+1.8VS_VCCPLL

CC121

CC121

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC122

CC122

4

26A

AA46

AB47

AB50

AB51

AB52

AB53

AB55

AB56

AB58

AB59

AC61

AD47

AD48

AD50

AD51

AD52

AD53

AD55

AD56

AD58

AD59

AE46

6A

UCPU1G

UCPU1G

VAXG[1]

VAXG[2]

VAXG[3]

VAXG[4]

VAXG[5]

VAXG[6]

VAXG[7]

VAXG[8]

VAXG[9]

VAXG[10]

VAXG[11]

VAXG[12]

VAXG[13]

VAXG[14]

VAXG[15]

VAXG[16]

VAXG[17]

VAXG[18]

VAXG[19]

VAXG[20]

VAXG[21]

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

3

POWER

POWER

AY43

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREF

VREF

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

SENSE LINES

VCCSA_VID[0]

VCCSA_VID[1]

VCCSA VID

lines

VCCSA VID

lines

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

VID[0] VID[1] 2011 2012

0 0 0.90 V Yes Yes

0 1 0.80 V Yes Yes

1 0 0.725 V No Yes

1 1 0.675 V No Yes

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

+V_DDR_REFA_R

BE7

+V_DDR_REFB_R

BG7

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

CPU1.5V_S3_GATE{28}

AM28

AN26

BC43

BA43

VCCSA_SENSE

U10

D48

D49

2

+V_SM_VREF should

+1.5V_CPU_VDDQ

12

+V_SM_VREF_CNT +V_SM_VREF

13

D

D

QC9

QC9

RC118

RC118

1U_0402_6.3V6K

1U_0402_6.3V6K

CC87

CC87

RC74

RC74

0_0402_5%

0_0402_5%

RC75

@RC75

@

12

12

1K_0402_1%

1K_0402_1%

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

CC88

CC88

1

2

VCCSA_VID0 {38}

VCCSA_VID1 {38}

2

G

G

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

S

S

RC117

RC117

@

@

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

1U_0402_6.3V6K

1U_0402_6.3V6K

CC89

CC89

CC90

CC90

1

1

2

2

+3VALW

12

RC72

RC72

100K_0402_5%

100K_0402_5%

RUN_ON_CPU1.5VS3#

61

2

QC5A

QC5A

SB00000AR10

SB00000AR10

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

DRAMRST_CNTRL_PCH{6,13}

CC85

CC85

1

2

SUSP#{28,31,39,40,41}

1U_0402_6.3V6K

1U_0402_6.3V6K

1 2

CC119

CC119

RC790_0402_5% RC790_0402_5%

1 2

1 2

RC80 0_0402_5%RC80 0_0402_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

RC78 0_0402_5%@ RC78 0_0402_5%@

1U_0402_6.3V6K

1U_0402_6.3V6K

CC86

CC86

1

2

+1.5V_CPU_VDDQ

12

1 2

VCCSA_VID0

VCCSA_VID1

1K_0402_1%

1K_0402_1%

1

2

1 2

0_0402_5%

0_0402_5%

1 2

RC76

RC76

0_0603_5%

0_0603_5%

12

+VREF0

RC1150_0402_5%~D @ RC1150_0402_5%~D @

12

RC1160_0402_5%~D @ RC1160_0402_5%~D @

12

13

D

D

QC10

QC10

2

G

G

S

S

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

CC91

CC91

CC92

CC92

1

1

2

2

+VSB

5

CC101

CC101

12

34

RUN_ON_CPU1.5VS3# {5}

have 20 mil trace width

RC67

RC67

0_0402_5%

0_0402_5%

12

@

RC85

RC85

1K_0402_1%

1K_0402_1%

RC89

RC89

1K_0402_1%

1K_0402_1%

RUN_ON_CPU1.5VS3

DRAMRST_CNTRL_PCH

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

+1.5V +1.5V_CPU_VDDQ

RC70

RC70

100K_0402_5%

100K_0402_5%

RUN_ON_CPU1.5VS3

SB00000AR10

SB00000AR10

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

QC5B

QC5B

@

3

2

QC3

@ QC3

@

AP2302GN-HF_SOT23-3

AP2302GN-HF_SOT23-3

1

+VREFB

5A

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC103

CC103

2

AON7212L_DFN8-5

AON7212L_DFN8-5

5

RC73

RC73

QC4

QC4

CC93

CC93

12

10U_0603_6.3V6M

1

CC94

CC94

2

4

1

CC118

CC118

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

10U_0603_6.3V6M

10U_0603_6.3V6M

CC102

CC102

1

2

+1.5V_CPU_VDDQ Source

330K_0402_5%

330K_0402_5%

1

2

Follow DG 0.71 page 6

10U_0603_6.3V6M

10U_0603_6.3V6M

CC95

CC95

1

2

3

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC96

CC96

2

D

D

S

S

+1.5V

12

RC68

RC68

1K_0402_1%

1K_0402_1%

@

@

12

RC69

RC69

1K_0402_1%

1K_0402_1%

@

@

+1.5V_CPU_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC98

CC98

CC97

CC97

2

2

RC71

RC71

470_0603_5%

470_0603_5%

1 2

QC6

QC6

13

RUN_ON_CPU1.5VS3#

2

G

G

SB570020110

SB570020110

2N7002E-T1-E3_SOT23-3

2N7002E-T1-E3_SOT23-3

1

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

+

+

CC100

CC100

CC99

CC99

330U_D2_2V_Y

330U_D2_2V_Y

2

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

3

2010/04/26 2011/10/18

2010/04/26 2011/10/18

2010/04/26 2011/10/18

Compal Secret Dat a

Compal Secret Dat a

Compal Secret Dat a

Deciphered D ate

Deciphered D ate

Deciphered D ate

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

LA-8101P

1

946M onday, November 14, 2011

946M onday, November 14, 2011

946M onday, November 14, 2011

of

of

of

0.1

0.1

0.1

Page 10

5

UCPU1H

UCPU1H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

A28

VSS[5]

A33

VSS[6]

A37

VSS[7]

A40

VSS[8]

A45

VSS[9]

A49

VSS[10]

A53

VSS[11]

A9

VSS[12]

VSS[13]

VSS[14]

VSS[15]

VSS[16]

VSS[17]

VSS[18]

VSS[19]

VSS[20]

VSS[21]

VSS[22]

VSS[23]

VSS[24]

VSS[25]

VSS[26]

VSS[27]

VSS[28]

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

VSS[35]

VSS[36]

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

VSS[44]

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

VSS[50]

VSS[51]

VSS[52]

VSS[53]

VSS[54]

VSS[55]

VSS[56]

VSS[57]

VSS[58]

VSS[59]

VSS[60]

VSS[61]

VSS[62]

VSS[63]

VSS[64]

VSS[65]

VSS[66]

VSS[67]

VSS[68]

VSS[69]

AJ7

VSS[70]

VSS[71]

VSS[72]

VSS[73]

VSS[74]

VSS[75]

VSS[76]

VSS[77]

VSS[78]

VSS[79]

VSS[80]

VSS[81]

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS

VSS

D D

C C

B B

A A

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

4

3

UCPU1I

UCPU1I

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D4

D40

D43

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

2

VSS[181]

VSS[182]

VSS[183]

VSS[184]

VSS[185]

VSS[186]

VSS[187]

VSS[188]

VSS[189]

VSS[190]

VSS[191]

VSS[192]

VSS[193]

VSS[194]

VSS[195]

VSS[196]

VSS[197]

VSS[198]

VSS[199]

VSS[200]

VSS[201]

VSS[202]

VSS[203]

VSS[204]

VSS[205]

VSS[206]

VSS[207]

VSS[208]

VSS[209]

VSS[210]

VSS[211]

VSS[212]

VSS[213]

VSS[214]

VSS[215]

VSS[216]

VSS[217]

VSS[218]

VSS[219]

VSS[220]

VSS[221]

VSS[222]

VSS[223]

VSS[224]

VSS[225]

VSS[226]

VSS[227]

VSS[228]

VSS[229]

VSS[230]

VSS[231]

VSS[232]

VSS[233]

VSS[234]

VSS[235]

VSS[236]

VSS[237]

VSS[238]

VSS[239]

VSS[240]

VSS[241]

VSS[242]

VSS[243]

VSS[244]

VSS[245]

VSS[246]

VSS[247]

VSS[248]

VSS[249]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

VSS

VSS

VSS[250]

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

NCTF

NCTF

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

1

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

SA00004SX00

SA00004SX00

5

Security Classification

Security Classification

Security Classification

2010/04/26 2011/10/18

2010/04/26 2011/10/18

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISIO N OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISIO N OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISIO N OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS