Page 1

CS485xx Family Data Sheet

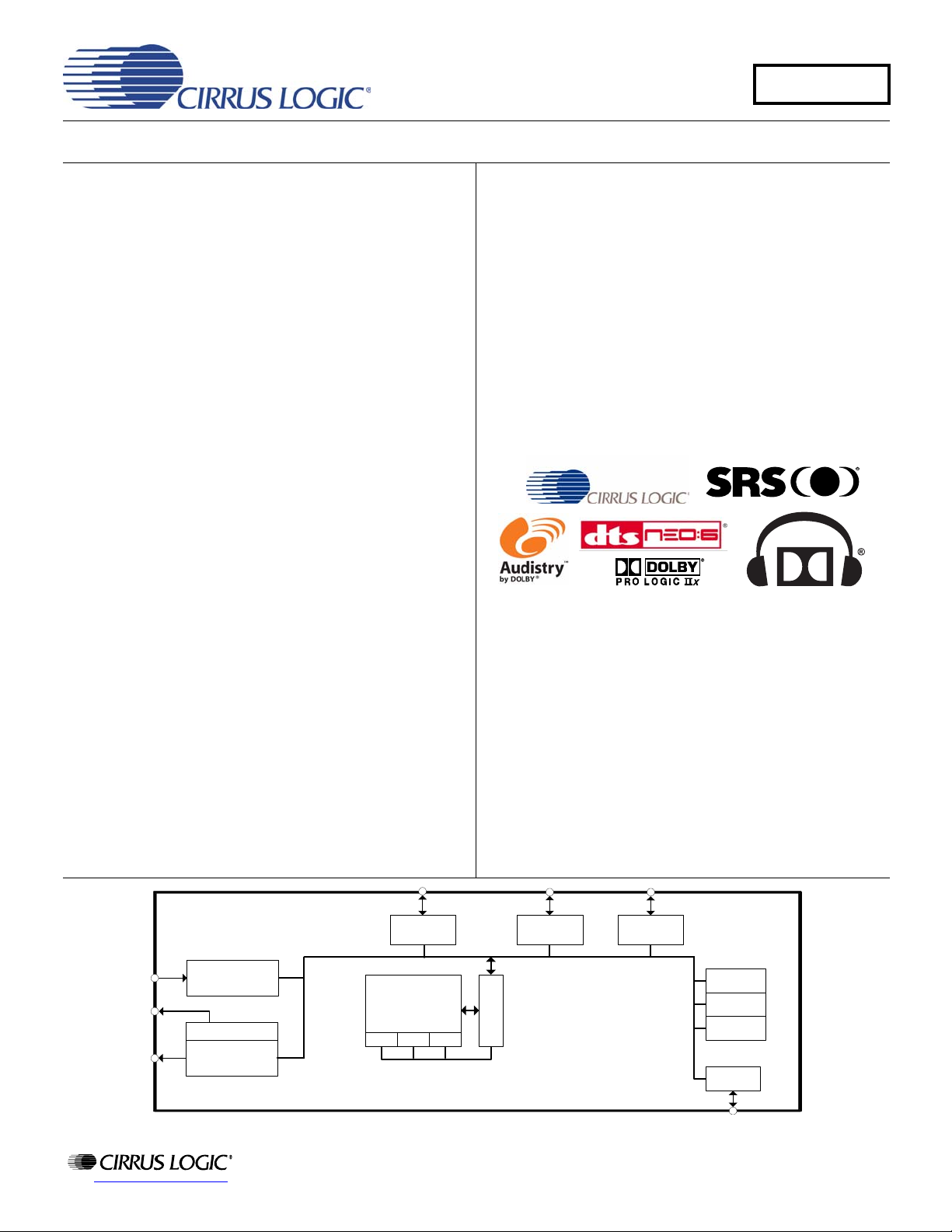

32-bit

DSP

D

M

A

P X Y

Serial

Control 1

12 Ch PCM

Audio Out

GPIO Debug

Watchdog

TMR1

TMR2

PLL

S/PDIF

12 Ch. Audio In /

6 Ch. SACD In

CS485xx

Features

Cost-effective, High-performance 32-bit DSP

300,000,000 MAC/S (multiply accumulates per second)

Dual MAC cycles per clock

72-bit accumulators are the most accurate in the industry

24k x 32 SRAM, 2k blocks - assignable to data or program

Internal ROM contains a variety of configurable sound

enhancement feature sets

8-channel internal DMA

Internal watch-dog DSP lock-up prevention

DSP Tool Set w/ Private Keys for Protecting Customer IP

Configurable Serial Audio Inputs/Output s

Configurable for all input/output types

Maximum 32-bit @ 192 kHz

Supports 32-bit audio sample I/O between DSP chips

TDM input modes (multiple channels on same line)

192 kHz SPDIF transmitter

Multi-channel DSD direct stream digital SACD input

Supports Two Different Input Fs Sample Rates

Output can be master or slave

Dual processing path capability

Input supports dual domain slave clocking

Hardware assist time sampling for sample rate conversion

Integrated Clock Manager/PLL

Can operate from external crystal, external oscillator

Input Fs Auto Detection

Host & Boot via Serial Interface

Configurable GPIOs and External Interrupt Input

1.8V Core and a 3.3V I/O that is tolerant to 5V input

Differentiating from the legacy Cirrus multi-standard, multi-channel

decoders, this new CS485xx family is still based on the same

high-performance 32-bit fixed point Digital Si gnal Processor core

but instead is equipped with much less memory, t ai lo ring it f or more

cost-effective applications associat ed with multi-channel and

virtual-channel sound enhancements. Target applications are:

Digital Televisions

Multimedia Peripherals

®

iPod

Docking Stations

Automotive Head Units

Automotive Outboard Amplifiers

HD-DVD

™

and Blu-ray Disc® DVD Receivers

PC Speakers

There are also a wide variety of licensable DSP codes available

today as seen by the following examples:

Cirrus also has developed, or is developing their own royalty-free

versions of popular features sets like Cirrus Bass Manager, Cirrus

Dynamic Volume Leveler, Cirrus Original Multichannel Surround,

Cirrus Virtual Speaker & Cirrus 3D-Audio.

The CS485xx family is programmed using the Cirrus proprietary

DSP Composer

designed using a drag-and-drop interface to place/utilize functional

macro audio DSP primitives. The end result is a software image that

is down-loaded to the DSP via serial host or serial boot modes.

See Section 6 for ordering information.

™

GUI development tool. Processing chains may be

Low-power Mode

“Energy Star

http://www.cirrus.com

®

Ready” in low-power mode, 268 µW in standby

CS485xx Block Diagram

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS734F5

OCT '11

Page 2

Contacting Cirrus Logic Support

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find the one nearest you, go to www.cirrus.com.

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information is subject to change

without notice and is pr ov i de d “A S I S” wi t hou t war r an ty of a ny k i nd ( ex p res s o r impl i ed ). Cus to mer s ar e adv ise d to obtain the lat est version of relevant information to verify,

before placing orders, that informatio n being relied on is current and complet e. All products are s old subject to the terms and conditions of s al e suppl i ed at the ti me of or de r

acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this in formation,

including use of this information as the b asis fo r manufacture or sale of any items, or for infring ement of patents or other rights of third parties. This document is the property

of Cirrus and by furnishi ng thi s i nformation, Cirrus grant s n o license, express or implied under any patents, mask work rights, copyrights, trademarks, t r a de se cre t s o r o t her

intellectual proper ty rig hts. Cirr us owns t he co pyri ght s ass ociat ed with the i nf ormati on c onta ine d here in a nd giv es c onse nt f or copies to be made of the information only for

use within your organiz ation with respect to Cirrus integrated circuits or other products of Cirrus. Th is consent does not ext end to other copying such as copying for general

distribution, advertising or promotional pu rp oses, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PR ODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATI ONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS

SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS.

INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK AND CIRRUS DISCLAIMS AND MAKES

NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR

PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PER MITS

THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATION S, CUSTOMER AGRE ES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS,

EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR

ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs, DSP Com poser, and Cirru s Framework ar e tradema rks of Cirrus Logic, Inc. All other brand and product names in this

document may be trademarks or service marks of their respective owners.

Dolby, Dolby Digitaol, Dolby Headphone, Virtual Speaker, and Pro Logic are registered trademarks of Dolby Laboratories, Inc. Supply of an implementation of Dolby

Technology does not convey a license no r imply a right under any pate nt, or any other industrial or Intelle ctual Property Right of Dolby Laboratories, to use the Implementation

in any finished end-user or ready-to-use final pro d uct. It is hereby no tified that a li cen s e for such u se is required from Dolby Laboratories.

DTS and DTS Neo:6 are regist ered trademarks of Dig i tal Theater Systems, Inc. It is hereby notified that a third-party license from DTS is necessary to distribute software of

DTS in any finished end-user or ready-to-use final pro du ct.

SRS, Circle Surround and Trusurround XT are registered trademarks of SRS Labs, Inc. Circl e Surround II is a trademark of SRS Labs, Inc. The Circle Surround technology

is incorporated under li cense from SRS Labs, Inc. The Circle Surround tec hnology rights incor porated in the CS485xx are owned by SRS Labs, a U.S. Cor poration and

licensed to Cirrus Logic, Inc. Purchaser of CS485xx must sign a license for use of the chip and display of the SRS Labs trademarks. Any products incorporating the CS485xx

must be sent to SRS Labs for review. The Circle Surround technology is protected under US and foreign patents issued and/or pending. Circle Surround, SRS and (O) symbol

are trademarks of SRS Labs, Inc. in the United States and selected foreign countrie s. Neither the purchase of the CS485xx, nor the corresponding sale of audio enhancement

equipment conveys the r ight to sell commerci alized recordings made wi th any SRS technology/sol ution. SRS Labs requires all set makers to comply with all rules and

regulations as outlined in the SRS Trademar k U sag e M a nual.

SPI is a trademark of Motorola, Inc.

I²C is a trademark of Philips Semiconductor.

iPod is a registered trademark of Apple Comput er, Inc.

HD DVD is a trademark of DVD Format/Logo Licensin g Corporation.

Blu-Ray Disc is a registered trademark of SONY KABUSHIKI KAISHA CORPORATION.

Energy Star is a registered trademark of the Environmental Protection Agency, a federal agency of the United States government.

DS734F5 2

Page 3

TABLE OF CONTENTS

1 Documentation Strategy ........................................................................................................................................... 1-5

2 Overview ..................................................................................................................................................................... 2-5

2.1 Licensing ............................................................................................................................................................ 2-5

3 Code Overlays ............................................................................................................................................................ 3-6

4 Hardware Functional Description ............................................................................................................................ 4-7

4.1 DSP Core ........................................................................................................................................................... 4-7

4.1.1 DSP Memory ............................................................................................................................................. 4-7

4.1.2 DMA Controller .......................................................................................................................................... 4-7

4.2 On-chip DSP Peripherals ................................................................................................................................... 4-7

4.2.1 Digital Audio Input Port (DAI) ............. ... ... ... ... .......................................... .... ............................................. 4-7

4.2.2 Digital Audio Output Port (DAO) ................................................................................................................ 4-8

4.2.3 Serial Control Port (I

4.2.4 GPIO ......................................................................................................................................................... 4-8

4.2.5 PLL-based Clock Generator ...................................................................................................................... 4-8

4.2.6 Hardware Watchdog Timer ....................................................................................................................... 4-8

4.3 DSP I/O Description ........................................................................................................................................... 4-8

4.3.1 Multiplexed Pins ........................................................................................................................................4-8

4.3.2 Termination Requirements ........................................................................................................................ 4-8

4.3.3 Pads .......................................................................................................................................................... 4-9

4.4 Application Code Security .................................................................................................................................. 4-9

5 Characteristics and Specifications .......................................................................................................................... 5-9

5.1 Absolute Maximum Ratings ................................................................................................................................ 5-9

5.2 Recommended Operations Conditions ..................................... ............. ............ ............. ............. .......................5-9

5.3 Digital DC Characteristics ................................................................................................................................... 5-9

5.4 Power Supply Characteristics ......................... ................ ................ ................ ................ .................................. 5-10

5.5 Thermal Data (48-pin LQFP) ............................................................................................................................ 5-10

5.6 Switching Characteristics—RESET .................................................................................................................. 5-11

5.7 Switching Characteristics—XTI ........................................................................................................................ 5-11

5.8 Switching Characteristics—Internal Clock ........................................................................................................5-11

5.9 Switching Characteristics—Serial Control Port–SPI Slave Mode ..................................................................... 5-12

5.10 Switching Characteristics—Serial Control Port–SPI Master Mode ................................................................. 5-13

5.11 Switching Characteristics—Serial Control Port–I

5.12 Switching Characteristics—Serial Control Port–I

5.13 Switching Characteristics—Digital Audio Slave Input Port .................................. ... ........................................ 5-15

5.14 Switching Characteristics—DSD Slave Input Port ..... ... .......................................... ........................................ 5-15

5.15 Switching Characteristics—Digital Audio Output (DAO) Port ....................... ... .... ... ........................................ 5-16

6 Ordering Information ............................................................................................................................................... 6-18

7 Environmental, Manufacturing, and Handling Information .................................................................................7-18

8 Device Pinout Diagrams .......................................................................................................................................... 8-19

8.1 CS48520, 48-pin LQFP Pinout Diagram .......................................................................................................... 8-19

8.2 CS48540, 48-pin LQFP Pinout Diagram .......................................................................................................... 8-20

8.3 CS48560, 48-pin LQFP Pinout Diagram .......................................................................................................... 8-21

9 Package Mechanical Drawings ............................................................................................................................... 9-22

9.1 48-pin LQFP Package Drawing ........................................................................................................................ 9-22

10 Revision History .............................. .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ................................................................... 10-23

2C™

or SPI™) ..................................... ............. ............. ............. ............ ............. ....... 4-8

2

C Slave Mode ................................................................... 5-13

2

C Master Mode ................................................................. 5-14

3 DS734F5

Page 4

LIST OF FIGURES

Figure 5-1. RESET Timing ...................................................................................................................................... 5-11

Figure 5-2. XTI Timing............................................................................................................................................. 5-11

Figure 5-3. Serial Control Port–SPI Slave Mode Timing .........................................................................................5-12

Figure 5-4. Serial Control Port–SPI Master Mode Timing .......................................................................................5-13

Figure 5-5. Serial Control Port–I

Figure 5-6. Serial Control Port–I

Figure 5-7. Digital Audio Input (DAI) Port Timing Diagram....... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .................................. 5-15

Figure 5-8. Direct Stream Digital–Serial Audio Input Timing........................................ ... ... ... .... ... ... ... ... .................. 5-15

Figure 5-9. Digital Audio Output Port Timing, Master Mode.................................................................................... 5-17

Figure 5-10. Digital Audio Output Timing, Slave Mode (Relationship LRCLK to SCLK)......................................... 5-17

Figure 8-1. CS48520, 48-pin LQFP Pinout.............................................................................................................. 8-19

Figure 8-2. CS48540, 48-pin LQFP Pinout.............................................................................................................. 8-20

Figure 8-3. CS48560, 48-pin LQFP......................................................................................................................... 8-21

Figure 9-1. 48-pin LQFP Package Drawing............................................................................................................. 8-22

2

C Slave Mode Timing.......................................................................................... 5-14

2

C Master Mode Timing........................................................................................ 5-15

LIST OF TABLES

Table 1-1. CS485xx Family Related Documentation....................................... ... ... ... .... ... .......................................... 1-5

Table 3-1. Device and Firmware Selection Guide................................. ... .... ... .......................................................... 3-6

Table 5-1. Master Mode (Output A1 Mode)............................................................................................................. 5-16

Table 5-2. Slave Mode (Output A0 Mode)............................................................................................................... 5-17

Table 6-1. Ordering Information .............................................................................................................................. 6-18

Table 7-1. Environmental, Manufacturing, and Handling Information .....................................................................7-18

4 DS734F5

Page 5

1 Documentation Strategy

1 Documentation Strategy

The CS485xx Family Data Sheet describes the CS485xx family of multichannel audio proce ssors. This document should

be used in conjunction with the following documents when evaluating or designing a system around the CS485xx family

of processors.

Table 1-1. CS485xx Family Related Documentation

Document Name Description

CS485xx Family Data Sheet This document

CS485xx Family Hardware User’s Manual Includes detailed system design information including Typical Connection Diagrams,

AN298–CS485xx Family Firmware User’s Manual Includes detailed firmware design information including signal processing flow

DSP Composer User’s Manual Includes detailed configuration and usage information for the GUI development tool.

The scope of the CS485xx Family Data Sheet is primarily the hardware specifications of the CS485xx family of devices.

This includes hardware functionality, characteristic data, pinout, and packaging information.

The intended audience for the CS485xx Family Data Sheet is the system PCB designer, MCU programmer, and the quality

control engineer.

Boot-Procedures, Pin Descriptions, etc.

diagrams and control API information

2 Overview

The CS485xx DSP Family is designed to provide high-performance post-processing and mixing of digital audio. The dual

clock domain provided on the PCM inputs allows for the mixing of audio streams with different sampling frequencies. The

low-power standby preserves battery life for applications which are always on, but not necessarily processing audio, such

as automotive audio systems.

There are three devices comprising the CS485xx family. The CS48520, CS485 40 and CS48560 are differentiated by the

number of inputs and outputs available. All DSPs support dual input clock domains and dual audio processing paths. All

DSPs are available in a 48-pin QFP package. Refer to Table3-1 for the input, output, firmware features of each device.

2.1 Licensing

Licenses are required for all of the third party audio processing algorithms listed in Section 3. Contact your local

Cirrus Logic Sales representative for more information.

5 DS734F5

Page 6

3 Code Overlays

3 Code Overlays

The suite of software available for the CS485xx family consists o f an operating system (OS) and a librar y of overlays. The

overlays have been divided into three main groups called Matrix-processors, Virtualizer-processors, and Post-processors.

All software components are defined below:

1. OS/Kernel—Encompasses all non-audio processing tasks, including loading data from external memory,

processing host messages, calling audio-processing subroutines, error concealment, etc.

2. Matrix-processor—Any Module that performs a matrix decode on PCM data to produce more output channels

than input channels (2n channels). Examples are Dolby ProLogic IIx and DTS Neo :6. Ge nerally speaking , these

modules increase the number of valid channe ls in the au dio I/O bu ffer.

3. Virtualizer-processor—Any module that encodes PCM data into fewer output channels than inpu t channels (n2

channels) with the effect of providing “phantom” speakers to represent the physical audio channels that were

eliminated. Examples are Dolby Headphone

reduce the number of valid channels in the audio I/O buffer.

4. Post-processors—Any module that processes audio I/O buffer PCM data in-place after the matrix- or

virtualizer-processors. Examples are bass management, audio manager, tone control, EQ, delay,

customer-specific effects, etc.

The bulk of each overlay is stored in ROM within the CS485xx, but a small imag e is required to configure the overlays and

boot the DSP. This small image can either be stored in an external serial FLASH/EEPROM, or downloaded via a host

controller through the SPI

™

/I2C™ serial port.

®

and Dolby Virtual Speaker®. Generally speaking, these modules

The overlay structure reduces the time required to reconfigure the DSP when a processing change is requested. Each

overlay can be reloaded independently without disturbing the other overlays. Fo r example, when a new matrix-processor

is selected, the OS, virtualizer-, and post-processors do not need to be reloaded — only the new matrix-processor (the

same is true for the other overlays).

Table 3-1 lists the firmware available based on device selection. Refer AN298, CS485xx Firmware User’s

Manual for the latest listing of application codes and Cirrus Framework

Table 3-1. Device and Firmware Selection Guide

Device Suggested Application Channel Count Input/Output Package

CS48520-CQZ Digital TV, portable audio docking station, portable DVD, DVD mini/

CS48540-CQZ

CS48540-DQZ

CS48560-CQZ

CS48560-DQZ

receiver, multimedia PC speakers

CS48520 features plus 8-channel car audio, DVD receiver Up to 8-channel in/8-channel out 48-pin QFP

CS48540 features plus 12-channel car audio, high-end digi tal TV , dual

source/dual zone SACD

™ modules available.

Up to 4-channel in/4-channel out 48-pin QFP

Up to 12-channel in/12-channel out 48-pin QFP

6 DS734F5

Page 7

4 Hardware Functional Description

4 Hardware Functional Description

4.1 DSP Core

The CS485xx family DSPs are single-core DSP with separate X and Y data and P code memory spaces. The DSP core

is a high-performance, 32-bit, user-programmable, fixed-point DSP that is capable of performing two

multiply-and-accumulate (MAC) operations per clock cycle. The DSP core has eight 72-bit accumulators, four X- and four

Y-data registers, and 12 index registers.

The DSP core is coupled to a flexible DMA engine. The DMA engine can move data between peripherals such as the serial

control port (SCP), digital audio input (DAI) and digital audio output (DAO), or any DSP core memory, all without the

intervention of the DSP. The DMA engine off loads data move instructions from the DSP core, leaving more MIPS available

for signal processing instructions.

CS485xx family functionality is controlled by application codes that are stored in on-board ROM or downloaded to the

CS485xx from a host controller or external serial FLASH/EEPROM.

Users can develop their applications using DSP Composer to crea te the processing chain and then compile the image into

a series of commands that are sent to the CS485xx through the SCP. The processing application can either load modules

(matrix-processors, virtualizers, post-processors) from the DSPs on-board ROM, or custom firmware can be downloaded

through the SCP.

The CS485xx is suitable for a variety of audio post-processing applications such as automotive hea d-ends, automotive

amplifiers, and boom boxes.

4.1.1 DSP Memory

The DSP core has its own on-chip data and program RAM and ROM and does not require external memory for

post-processing applications.

The Y-RAM and P-RAM share a single block of memory that can be configured to make Y and P equal in size, or more

memory can be allocated for Y-RAM in 2kword blocks.

4.1.2 DMA Controller

The powerful 8-channel DMA controller can move data between 8 on-chip resources. Each resource has its own arbiter:

X, Y, and P RAMs/ROMs and the peripheral bus. Modulo and linear addressing modes are supported, with flexible start

address and increment controls. The service intervals for each DMA channel, as well as up to 6 interrupt events, are

programmable.

4.2 On-chip DSP Peripherals

4.2.1 Digital Audio Input Port (DAI)

Each version of the CS485xx supports a different number of input channels. Refer to Table 3-1 for more details.

The DAI port supports a wide variety of data input formats at sa mple rates (Fs) as hig h as 192 kHz. The por t is capable of

accepting PCM or DSD formats. Up to 32-bit word lengths are supported. DSD is supported and internally converted to

PCM before processing. The DAI also supports a time division multiplexed (TDM) one-line data mode, that packs PCM

audio on a single data line (the total number possible depe nds on the ratio of SCLK to LRCLK and the ver sion of chip. For

example on the CS48520 only 4 ch of PCM are supported in one line mode and on the CS48560 up to 8 channels are

supported.).

The port has two independent slave-only clock domains. Each data input can be independently assigned to a clock

domain. The sample rate of the input clock domains can be determined au tomatically by the DSP, off- loading the task of

monitoring the SPDIF receiver from the host. A time-stamping feature allows the input data to be sample-rate converted

via software.

7 DS734F5

Page 8

4.3 DSP I/O Description

4.2.2 Digital Audio Output Port (DAO)

Each version of the CS485xx supports a different number of output channels. Refer to Table 3-1 for more details.

DAO port supports PCM resolutions of up to 32-bits. The port supports sample rates (Fs) as high as 192 kHz. The port

can be configured as an independent clock domain mastere d by the DSP, or as a clock slave if an external MCLK or SCLK/

LRCLK source is available. One of the serial audio pins can be re-configured as a S/PDIF transmitter th at drives a biphase

encoded S/PDIF signal (data with embedded clock on a single line).

The DAO also supports a time division multiplexed (TDM) o ne-line data mode, th at packs multiple channels of PCM audio

on a single data line.

4.2.3 Serial Control Port (I2C™ or SPI™)

2

The on-chip serial control port is capable of operating as master or slave in either SPI™ or I

™

C

modes. Master/

Slave operation is chosen by mode select pins when the CS485xx comes out of Reset. The serial clock pin can

support frequencies as high as 25 MHz in SPI mode (SPI clock speed must always be ≤ (F

serial control port also includes a pin for flow control of the communications inte rface (SCP_BSY

indicate when the DSP has a message for the host (SCP_IRQ

).

/2)). The CS485xx

dclk

) and a pin to

4.2.4 GPIO

Many of the CS485xx peripheral pins are multiplexe d with GPIO. Each GPIO ca n be configure d as an output, an input, or

an input with interrupt. Each input-pin interrupt can be configured as rising edge, falling edge, active-low, or active-high.

4.2.5 PLL-based Clock Generator

The low-jitter PLL generates integer or fractional multiples of a reference frequency which are used to clock the DSP core

and peripherals. Through a second PLL divider chain, a dependent clock domain ca n be output on the DAO port for driving

audio converters. The CS485xx defaults to running fro m the external reference freq uency and is switched to use th e PLL

output after overlays have been loaded and configured, either through master boot from an external FLASH or through

host control. A built-in crystal oscillator circuit with a buffered output is provided. The buffered output frequency ratio is

selectable between 1:1 (default) or 2:1.

4.2.6 Hardware Watchdog Timer

The CS485xx has an integrated watchdog timer that acts as a “health” monitor for the DSP. The watchdog timer must be

reset by the DSP before the counter expires, or the entire chip is reset. This peripheral ensures that the CS485xx will reset

itself in the event of a temporary system failure. In stand-alone mode (that is, no host MCU), the DSP will reboot from

external FLASH. In slave mode (that is, host MCU present) a GPIO will be used to signal the host that the watchdog has

expired and the DSP should be rebooted and re-configured.

4.3 DSP I/O Description

4.3.1 Multiplexed Pins

Many of the CS485xx family pins are multi-functional. For details on pin functionality, refer to the CS485xx Hardware

User’s Manual.

4.3.2 Termination Requirements

Open-drain pins on the CS485xx must be pulled high for proper opera tion. Refer to the CS485xx Hardware User’s Manual

to identify which pins are open-drain and what value of pull-up resistor is required fo r proper operation.

Mode select pins in the CS485xx family are used to select the boot mode upon the rising edge from reset. A detailed

explanation of termination requirements for each communication mode select pin ca n be found in the CS485xx Hardware

User’s Manual.

8 DS734F5

Page 9

4.4 Application Code Security

4.3.3 Pads

The CS485xx I/Os operate from the 3.3 V supply and are 5 V tolerant.

4.4 Application Code Security

The external program code may be encrypted by the programmer to protect any intellectual property it may contain. A

secret, customer-specific key is used to encrypt the program code that is to be stor ed external to the device. Contact your

local Cirrus representative for details.

5 Characteristics and Specifications

Note: All data sheet minimum and maximum timing parameters are guaranteed over the rated voltage and temperature.

All data sheet typical parameters are measured under the following conditions: T = 25° C, C

VDD = VDDA = 1.8 V, VDDIO = 3.3 V, GNDD = GNDIO = GNDA = 0 V.

5.1 Absolute Maximum Ratings

(GNDD = GNDIO = GNDA = 0 V; all voltages with respect to 0 V)

Parameter Symbol Min Max Unit

DC power supplies: Core supply VDD –0.3 2.0 V

PLL supply VDDA –0.3 3.6 V

I/O supply VDDIO –0.3 3.6 V

|VDDA–VDDIO| — — 0.3 V

Input pin current, any pin except supplies I

Input voltage on PLL_REF_RES V

Input voltage on I/O pins V

Storage temperature T

in

filt

inio

stg

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not

guaranteed at these extremes.

—±10mA

–0.3 3.6 V

–0.3 5.0 V

–65 150 °C

= 20 pF,

L

5.2 Recommended Operations Conditions

(GNDD = GNDIO = GNDA = 0 V; all voltages with respect to 0 V)

Parameter Symbol Min Typ Max Unit

DC power supplies: Core supply VDD 1.71 1.8 1.89 V

PLL supply VDDA 3.13 3.3 3.46 V

I/O supply VDDIO 3.13 3.3 3.46 V

|VDDA–VDDIO| — — 0 — V

Ambient operating temperature T

–CQZ — 0 — +70 —

–DQZ — –40 — +85 —

A

——— °C

Note: It is recommended that the 3.3 V IO supply come up ahead of or simultaneously with the 1.8 V core supply.

5.3 Digital DC Characteristics

(Measurements performed under static conditions.)

9 DS734F5

Page 10

5.4 Power Supply Characteristics

Parameter Symbol Min Typ Max Unit

High-level input voltage V

Low-level input voltage, except XTI V

Low-level input voltage, XTI V

Input hysteresis V

High-level output voltage (I

Low-level output voltage (I

= –2 mA), except XTI V

O

= 2 mA), except XTI V

O

Input leakage XTI I

Input leakage current (all digital pins wit h internal pull-up resistors enabled) I

LEAK

IH

IL

ILXTI

hys

OH

OL

LXTI

2.0 — — V

——0.8V

——0.6V

—0.4— V

VDDIO*0.9 — — V

——VDDIO*0.1V

—— 5 µA

——70µA

5.4 Power Supply Characteristics

(Measurements performed under operating conditions)

Parameter Min Typ Max Unit

Operational Power Supply Current:

VDD: Core and I/O operating

VDDA: PLL operating —8—mA

VDDIO: With most ports operating —27—mA

Total Operational Power Dissipation: — 480 — mW

1

— 203 — mA

Standby Power Supply Current:

VDD: Core and I/O not clocked — 100 — µA

VDDA: PLL halted —1—µA

VDDIO: All connected I/O pins 3-stated by other ICs in system — 50 — µA

Total Standby Power Dissipation — 348 — µW

1.Dependent on application firmware and DSP clock speed.

5.5 Thermal Data (48-pin LQFP)

Parameter Symbol Min Typ Max Unit

Junction Temperature T

j

Thermal Resistance (Junction to Ambient)

Two-layer board

Four-layer board

1

2

θ

ja

Thermal Resistance (Junction to Top of Package)

Two-layer board

Four-layer board

1.Two-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1 oz. copper covering 20% of the top and bottom layers.

2.Four-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1 oz. copper covering 20% of the top and bottom layers and 0.5

oz. copper covering 90 % of the internal power plane and ground plane layers.

3.To calculate the die temperature for a given power dissipation

T

= Ambient Temperature + [(Power Dissipation in Watts)*θja]

j

4.To calculate the case temperature for a given power dissipation

T

= T

– [(Power Dissipation in Watts)*ψjt]

c

j

3

4

ψ

jt

——125 °C

— 63.5 — °C/Watt

—54 —

— 0.70 — °C/Watt

—0.64—

10 DS734F5

Page 11

RESET#

T

rst2z

T

rstl

T

rstsu

T

rsthld

HS[3:0]

All Bidirectional

Pins

t

clkih

t

clkil

T

clki

XTI

5.6 Switching Characteristics—RESET

5.6 Switching Characteristics—RESET

Parameter Symbol Min Max Unit

RESET# minimum pulse width low T

All bidirectional pins high-Z after RESET# low T

Configuration pins setup before RESET# high T

Configuration pins hold after RESET# high T

rstl

rst2z

rstsu

rsthld

1—ms

— 100 ns

50 — ns

20 — ns

Figure 5-1. RESET Timing

5.7 Switching Characteristics—XTI

Parameter Symbol Min Max Unit

External Crystal operating frequency

XTI period T

XTI high time T

XTI low time T

External Crystal Load Capacitance (parallel resonant)

External Crystal Equivalent Series Resistance ESR — 50

1.Part characterized with the following crystal frequency values: 11.2896, 12.288, 18.432, 24.576, & 27 MH.z

2.CL refers to the total load capacitance as specified by the crystal manufacturer. Crystals that require a CL outside this range should be avoided. The

crystal oscillator circuit design should follow the crystal manufacturer’s recommendation for load capacitor selection.

1

2

F

xtal

clki

clkih

clkil

C

11.2896 27 MHz

33.3 100 ns

13.3 — ns

13.3 — ns

L

10 18 pF

Ω

Figure 5-2. XTI Timing

5.8 Switching Characteristics—Internal Clock

Parameter Symbol Min Max Unit

Internal DCLK frequency

11 DS734F5

1

CS4852x-CQZ

CS4854x-CQZ

CS4856x-CQZ

CS4854x-DQZ

CS4856x-DQZ

F

dclk

——MHz

F

xtal

F

xtal

F

xtal

F

xtal

F

xtal

150

150

150

150

150

Page 12

SCP_BSY#

SCP_CS#

SCP_CLK

SCP_MOSI

SCP_MISO

SCP_IRQ#

0

12670

56

7

t

spicss

t

spickl

t

spickh

t

spidsu

t

spidh

t

spidov

A6 A5 A0 R/W MSB LSB

MSB

LSB

t

spicsh

t

spibsyl

t

spiirql

t

spiirqh

f

spisck

t

spicsdz

5.9 Switching Characteristics—Serial Control Port–SPI Slave Mode

Parameter Symbol Min Max Unit

Internal DCLK period

1.After initial power-on reset, F

reset.

1

CS4852x-CQZ

CS4854x-CQZ

CS4856x-CQZ

CS4854x-DQZ

CS4856x-DQZ

= F

dclk

. After initial kick-start commands, the PLL is locked to max F

xtal

DCLKP — — ns

6.7

6.7

6.7

6.7

6.7

and remains locked until the next power-on

dclk

1/F

1/F

1/F

1/F

1/F

xtal

xtal

xtal

xtal

xtal

5.9 Switching Characteristics—Serial Control Port–SPI Slave Mode

Parameter Symbol Min Typical Max Units

SCP_CLK frequency

SCP_CS# falling to SCP_CLK rising t

SCP_CLK low time t

SCP_CLK high time t

Setup time SCP_MOSI input t

Hold time SCP_MOSI input t

SCP_CLK low to SCP_MISO output valid t

SCP_CLK falling to SCP_IRQ# rising t

SCP_CS# rising to SCP_IRQ# falling t

SCP_CLK low to SCP_CS# rising t

SCP_CS# rising to SCP_MISO output high-Z t

SCP_CLK rising to SCP_BSY# falling t

1.The specification f

communication port may be limited by the firmware application. Flow control using the SCP_BSY# pin should be implemented to prevent overflow of

the input data buffer. At boot the maximum speed is F

1

indicates the maximum speed of the hardware. The system designer should be aware that the act ual maximum speed of the

spisck

xtal

/3.

f

spisck

spicss

spickl

spickh

spidsu

spidh

spidov

spiirqh

spiirql

spicsh

spicsdz

spicbsyl

——25MHz

24 — — ns

20 — — ns

20 — — ns

5——ns

5——ns

——11ns

— — 20 ns

0——ns

24 — — ns

—20—ns

—3*DCLKP+20— ns

12 DS734F5

Figure 5-3. Serial Control Port–SPI Slave Mode Timing

Page 13

EE_CS#

SCP_CLK

SCP_MISO

SCP_MOSI

0

12670

56

7

t

spicss

t

spickl

t

spickh

t

spidsu

t

spidh

t

spidov

A6 A5 A0 R/W MSB LSB

MSB

LSB

t

spicsh

t

spicsx

f

spisck

t

spidz

t

spicsl

5.10 Switching Characteristics—Serial Control Port–SPI Master Mode

5.10 Switching Characteristics—Serial Control Port–SPI Master Mode

Parameter Symbol Min Typical Max Units

SCP_CLK frequency

SCP_CS# falling to SCP_CLK rising

SCP_CLK low time t

SCP_CLK high time t

Setup time SCP_MISO input t

Hold time SCP_MISO input t

SCP_CLK low to SCP_MOSI output valid t

SCP_CLK low to SCP_CS# falli ng t

SCP_CLK low to SCP_CS# rising t

Bus free time between active SCP_CS# t

SCP_CLK falling to SCP_MOSI output high-Z t

1.The specification f

communication port may be limited by the firmware application.

2.See Section 5.7.

3.SCP_CLK PERIOD refers to the period of SCP_CLK as being used in a given application. It does not refer to a tested parameter.

1

3

indicates the maximum speed of the hardware. The system designer should be aware that the act ual maximum speed of the

spisck

f

spisck

t

spicss

spickl

spickh

spidsu

spidh

spidov

spicsl

spicsh

spicsx

spidz

——F

— 11*DCLKP + (SCP_CLK PERIOD)/2 — ns

20 — — ns

20 — — ns

13 — — ns

5— —ns

—— 8ns

7— —ns

— 11*DCLKP + (SCP_CLK PERIOD)/2 — ns

— 3*DCLKP — ns

— — 20 ns

xtal

2

/2

MHz

5.11 Switching Characteristics—Serial Control Port–I2C Slave Mode

SCP_CLK frequency

SCP_CLK low time t

SCP_CLK high time t

SCP_SCK rising to SCP_SDA rising or falling for START or STOP condition t

START condition to SCP_CLK falling t

SCP_CLK falling to STOP condition t

Bus free time between STOP and START conditions t

Setup time SCP_SDA input valid to SCP_CLK rising t

Hold time SCP_SDA input after SCP_CLK falling t

13 DS734F5

Figure 5-4. Serial Control Port–SPI Master Mode Timing

Parameter Symbol Min Typical Max Units

1

f

iicck

iicckl

iicckh

iicckcmd

iicstscl

iicstp

iicbft

iicsu

iich

—— 400kHz

1.25 — — µs

1.25 — — µs

1.25 — — µs

1.25 — — µs

2.5 — — µs

3— —µs

100 — — ns

20 — — ns

Page 14

SCP_BSY#

SCP_CLK

SCP_SDA

SCP_IRQ#

01 67801 7

t

iicckl

t

iicckh

t

iicsutiich

A6 A0 R/W ACK

LSB

t

iicirqh

t

iicirql

8

ACK

MSB

t

iicstp

6

t

iiccbsyl

t

iicdov

t

iicbft

t

iicstscl

t

iicckcmd

f

iicck

t

iicckcmd

t

iicf

t

iicr

5.12 Switching Characteristics—Serial Control Port–I2C Master Mode

Parameter Symbol Min Typical Max Units

SCP_CLK low to SCP_SDA out valid t

SCP_CLK falling to SCP_IRQ# rising t

NAK condition to SCP_IRQ# low t

SCP_CLK rising to SCB_BSY# low t

1.The specification f

communication port may be limited by the firmware application. Flow control using the SCP_BSY# pin should be implemented to prevent overflow of

the input data buffer.

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the

iicck

iicdov

iicirqh

iicirql

iicbsyl

— — 18 ns

— — 3*DCLKP + 40 ns

— 3*DCLKP + 20 — ns

— 3*DCLKP + 20 — ns

5.12 Switching Characteristics—Serial Control Port–I2C Master Mode

SCP_CLK frequency

SCP_CLK low time t

SCP_CLK high time t

SCP_SCK rising to SCP_SDA rising or falling for START or STOP condition t

START condition to SCP_CLK falling t

SCP_CLK falling to STOP condition t

Bus free time between STOP and START conditions t

Setup time SCP_SDA input valid to SCP_CLK rising t

Hold time SCP_SDA input after SCP_CLK falling t

SCP_CLK low to SCP_SDA out valid t

1.The specification f

communication port may be limited by the firmware application.

Figure 5-5. Serial Control Port–I2C Slave Mode Timing

Parameter Symbol Min Max Units

1

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the

iicck

f

iicck

iicckl

iicckh

iicckcmd

iicstscl

iicstp

iicbft

iicsu

iicdov

iich

—400kHz

1.25 — µs

1.25 — µs

1.25 — µs

1.25 — µs

2.5 — µs

3— µs

100 — ns

20 — ns

—18 ns

14 DS734F5

Page 15

SCP_CLK

SCP_SDA

01 67801 7

t

iicckl

t

iicckh

t

iicsutiich

A6 A0 R/W ACK

LSB

8

ACK

MSB

t

iicstp

6

t

iicdov

t

iicbft

t

iicstscl

t

iicckcmd

f

iicck

t

iicckcmd

t

iicf

t

iicr

DAI_SCLK

DAI_DATAn

t

daidh

t

daidsu

5.13 Switching Characteristics—Digital Audio Slave Input Port

Figure 5-6. Serial Control Port–I2C Master Mode Timing

5.13 Switching Characteristics—Digital Audio Slave Input Port

Parameter Symbol Min Max Unit

DAI_SCLK period T

DAI_SCLK duty cycle — 45 55 %

Setup time DAI_DATAn t

Hold time DAI_DATAn t

daiclkp

daidsu

daidh

40 — ns

10 — ns

5—ns

5.14 Switching Characteristics—DSD Slave Input Port

DSD_SCLK Pulse Width Low t

DSD_SCLK Pulse Width High t

DSD_SCLK Frequency (64x Oversampled) — 1.024 — 3.2 MHz

DSD_A/B valid to DSD_SCLK rising setup time t

DSD_SCLK rising to DSD_A or DSD_B hold time t

15 DS734F5

Figure 5-7. Digital Audio Input (DAI) Port Timing Diagram

Parameter Symbol Min Typ Max Unit

sclkl

sclkh

sdlrs

sdh

Figure 5-8. Direct Stream Digital–Serial Audio Input Timing

78 — — ns

78 — — ns

20 — — ns

20 — — ns

Page 16

DAO_MCLK

DAO_SCLK

DAO_LRCLK

DAOn_DATAn

t

daomclk

t

daomsck

t

daomstlr

Note: In these diagrams, Falling edge is the inactive edge of DAO_SCLK.

5.15 Switching Characteristics—Digital Audio Output (DAO) Port

5.15 Switching Characteristics—Digital Audio Output (DAO) Port

Parameter Symbol Min Max Unit

DAO_MCLK period T

daomclk

DAO_MCLK duty cycle — 45 55 %

DAO_SCLK period for Master or Slave mode

DAO_SCLK duty cycle for Master or Slave mode

1.Master mode timing specifications are characterized, not production tested.

1

1

T

daosclk

—4060%

40 — ns

40 — ns

Table 5-1. Master Mode (Output A1 Mode)1,

2

Parameter Symbol Min Max Unit

DAO_SCLK delay from DAO_MCLK rising edge, DAO_MCLK as an input t

DAO_LRCLK delay from DAO_SCLK transition, respectively

DAO_SCLK delay from DAO_LRCLK transition, respectively

DAO1_DATA[3:0], DAO2_DATA[1:0] delay from DAO_SCLK transition

1.Master mode timing specifications are characterized, not production tested.

2.Master mode is defined as the CS48xx driving both DAO_SCLK, DAO_LRCLK. When MCLK is an input, it is divided to produce DAO_SCLK, DAO_

LRCLK.

3.This timing parameter is defined from the non-active edge of DAO_SCLK. The active edge of DAO_SCLK is the point at which the data is valid.

3

3

3

daomsck

t

daomstlr

t

daomlrts

t

daomdv

—19ns

—8ns

—8ns

—10ns

16 DS734F5

Figure 5-9. Digital Audio Output Port Timing, Master Mode

Page 17

DAO_SCLK

DAO_LRCLK

DAOn_DATAn

t

daosstlr

t

daosclk

DAO_SCLK

DAO_LRCLK

t

daoslrts

t

daosdv

t

daosclk

Note: In these diagrams, Falling edge is the inactive edge of DAO_SCLK.

5.15 Switching Characteristics—Digital Audio Output (DAO) Port

Table 5-2. Slave Mode (Output A0 Mode)

Parameter Symbol Min Max Unit

DAO_SCLK active edge to DAO_LRCLK transition t

DAO_LRCLK transition to DAO_SCLK active edge t

DAO_Dx delay from DAO_SCLK inactive edge t

1.Slave mode is defined as DAO_SCLK, DAO_LRCLK driven by an external source.

1

Figure 5-10. Digital Audio Output Timing, Slave Mode (Relationship LRCLK to SCLK)

daosstlr

daoslrts

daosdv

10 — ns

10 — ns

—11ns

17 DS734F5

Page 18

6 Ordering Information

The CS485xx family part number is CS485NI-XYZR where:

• N–Product Number Variant

• I–ROM ID Number

• X–Product Grade

• Y–Package Type

• Z–Lead (Pb) Free

• R–Tape and Reel Packaging

Table 6-1. Ordering Information

Part No. Grade Temp. Range Package

CS48520-CQZ Commercial 0 to +70° C 48-pin LQFP

CS48540-CQZ Commercial 0 to +70° C

CS48540-DQZ Automotive –40 to +85° C

CS48560-CQZ Commercial 0 to +70° C

CS48560-DQZ Automotive –40 to +85° C

Note: Contact the factory for availability of the automotive grade package.

6 Ordering Information

7 Environmental, Manufacturing, and Handling Information

Table 7-1. Environmental, Manufacturing, and Handling Information

Model Number Peak Reflow Temp

CS48520-CQZ 260° C 3 7 days

CS48540-CQZ

CS48540-DQZ

CS48560-CQZ

CS48560-DQZ

1.MSL (Moisture Sensitivity Level) as specified by IPC/JEDEC J-STD-020.

MSL Rating

1

Max Floor Life

18 DS734F5

Page 19

8 Device Pinout Diagrams

XTO

XTI

GNDA

PLL_REF_RES

VDDA (3.3V)

GPIO1

GPIO2

GPIO16, DAI1_DATA0

GPIO0

38

40

41

42

43

45

46

GPIO13, SCP_BSY#, EE_CS#

GPOI12, SCP_IRQ#

GPIO10, SCP__MISO / SDA

GPIO9, SCP_MOSI

GPIO11, SCP_CLK

35

33

31

30

28

26

25

GND4

GNDIO4

VDD3

GND3

VDDIO3

GNDIO3

23

22

21

19

17

15

1

GPIO5, XMTA

GPIO3, HS1

DAO1_DATA0, HS0

DAO_LRCLK

DAI1_LRCLK

GPIO18, DAO_MCLK

DAI1_SCLK

VDD1

GND1

DAO_SCLK

GPIO4, HS2

RESET#

VDDIO1

GNDIO1

GPIO6, DAO2 _DATA0, HS3

GPIO7, HS4

VDD2

GND2

VDDIO2

GNDIO2

2

3

4

5

6

7

9

10

11

12

GPIO8, SCP_CS#

TEST

DBDA

DBCK

XTAL_OUT GPIO15, DAI2_SCLK

GPIO14, DAI2_LRCLK

GPIO17, DAI2_DATA0

CS48520

48-Pin LQFP

8

13

14

16

18

20

24

27

29

32

34

36

37

39

44

47

48

8.1 CS48520, 48-pin LQFP Pinout Diagram

8 Device Pinout Diagrams

Figure 8-1. CS48520, 48-pin LQFP Pinout

19 DS734F5

Page 20

8.2 CS48540, 48-pin LQFP Pinout Diagram

XTO

XTI

GNDA

PLL_REF_RES

VDDA (3.3V)

GPIO1, DAI1_DATA2

GPIO2

GPIO16, DAI1_DATA0

GPIO0, DAI1_DATA1

38

40

41

42

43

45

46

GPIO13, SCP_BSY#, EE_CS#

GPOI12, SCP_IRQ#

GPIO10, SCP__MISO / SDA

GPIO9, SCP_MOSI

GPIO11, SCP_CLK

35

33

31

30

28

26

25

GND4

GNDIO4

VDD3

GND3

VDDIO3

GNDIO3

23

22

21

19

17

15

1

GPIO5, XMTA

GPIO3, DAO1_ DATA1, HS1

DAO1_DATA0, HS0

DAO_LRCLK

DAI1_LRCLK

GPIO18, DAO_MCLK

DAI1_SCLK

VDD1

GND1

DAO_SCLK

GPIO4, DAO1_ DATA2, HS2

RESET#

VDDIO1

GNDIO1

GPIO6, DAO2_DATA0, HS3

GPIO7, HS4

VDD2GND2

VDDIO2

GNDIO2

2

3

4

5

6

7

9

10

11

12

GPIO8, SCP_CS#

TEST

DBDA

DBCK

XTAL_OUT GPIO15, DAI2_SCLK

GPIO14, DAI2_LRCLK

GPIO17,

D

AI2_DATA0

CS48540

48-Pin LQFP

8

13

14

16

18

20

24

27

29

32

34

36

37

39

44

47

48

8.2 CS48540, 48-pin LQFP Pinout Diagram

Figure 8-2. CS48540, 48-pin LQFP Pinout

20 DS734F5

Page 21

8.3 CS48560, 48-pin LQFP Pinout Diagram

XTO

XTI

GNDA

PLL_REF_RES

VDDA (3.3V)

GPIO1, DAI1_DATA2, TM2, DSD2

GPIO2, DAI1_DATA3, TM3, DSD3

GPIO16, DAI1_DATA0, TM0, DSD0

GPIO0, DAI1_DATA1, TM1, DSD1

38

40

41

42

43

45

46

GPIO13, SCP_BSY#, EE_CS#

GPOI12, SCP_IRQ#

GPIO10, SCP__MISO / SDA

GPIO9, SCP_MOSI

GPIO11, SCP_CLK

35

33

31

30

28

26

25

GND4

GNDIO4

VDD3

GND3

VDDIO3

GNDIO3

23

22

21

19

17

15

1

GPIO5, DAO1_DATA3, X MTA

GPIO3, DAO1_ DATA1, HS1

DAO1_DATA0, HS0

DAO_LRCLK

DAI1_LRCLK, DAI1_DATA4, DSD5

GPIO18, DAO_MCLK

DAI1_SCLK, DSD-CLK

VDD1

GND1

DAO_SCLK

GPIO4, DAO1_ DATA2, HS2

RESET#

VDDIO1

GNDIO1

GPIO6, DAO2 _DATA0, HS3

GPIO7, DAO2_D ATA1, HS4

VDD2GND2

VDDIO2

GNDIO2

2

3

4

5

6

7

9

10

11

12

GPIO8, SCP_CS#

TEST

DBDA

DBCK

XTAL_OUT GPIO15, DAI2_SCLK

GPIO14, DAI2_LRCLK

GPIO17, DAI2_DATA0, DSD4

CS48560

48-Pin LQFP

8

13

14

16

18

20

24

27

29

32

34

36

37

39

44

47

48

8.3 CS48560, 48-pin LQFP Pinout Diagram

Figure 8-3. CS48560, 48-pin LQFP

21 DS734F5

Page 22

9 Package Mechanical Drawings

48 LD LQFP (7 x 7 x 1.4 mm body)

Number of Leads

48

MIN NOM MAX

A1.60

A1 0.05 0.15

A2 1.35 1.40 1.45

b 0.17 0.22 0.27

D9.00BSC

D1 7.00 BSC

e0.50BSC

E9.00BSC

E1 7.00 BSC

theta 0 7

L 0.45 0.60 0.75

L1 1.00 REF

NOTES:

1) Reference document: JEDEC MS-026

2) All dimensions are in millimeters and controlling dimension is in millimeters.

3) D1 and E1 do not include mold flash which is 0.25 mm max. per side.A1

4) Dimension b does not include a total allowable dambar protrusion of 0.08 mm max.

9.1 48-pin LQFP Package Drawing

9 Package Mechanical Drawings

22 DS734F5

Figure 9-1. 48-pin LQFP Package Drawing

Page 23

10 Revision History

10Revision History

Revision Date Changes

A1 July, 2006 Advance release.

A2 July, 2006 Updated pinout definition for pins 26 and 27. Updated typical power numbers.

A3 December 5, 2006 Updated sections 2.0, 4.21, 5.8, Table 3, Table 4, to show new device numbering scheme. Updated

PP1 March 12, 2007 Preliminary Release

PP2 December 18, 2007 Changed title of data sheet from CS48500 Da ta Sheet to CS485xx Family Data Sheet to cover all CS48 5xx

F1 April 21, 2007 Removed DSD Phase Modulation Mode from Section 5.14. Removed reference to MCLK in Section 5.14.

F2 July 14, 2008 Added reference to support for time division multiplexed (TDM) one-line data mode for DAO port in

F3 February 16, 2009 Updated Section5.5, adding Junction Temperature specification.

F4 June 29, 2011 Updated Section 5.10; changed T

F5 October, 2011 Updated Section 5.15 DAO output slave mode specifications.

sections 8.1, 8.2, 8.3.

family products. Updated Standby Power specif ica ti on in Section5.4. Updated DAO timing specifications

and timing diagrams in Section 5.15.

Redefined Master mode clock speed for SCP_CLK in Section 5.10. Redefined DC leakage

characterization data in Section 5.3. Added typical crystal frequency values in Table Footnote 1 under

Section 5.7. Modified Footnote 1 under Section 5.9. Modified power supply characteristics in Section 5.4,

Section 4.2.2.

value to 13 ns.

spidsu

23 DS734F5

Loading...

Loading...