Page 1

CS470xx Data Sheet

CS470xx

Features

Cost-effective, High-performance 32-bit DSP

300,000,000 MAC/S (multiply accumulates per second)

Dual MAC cycles per clock

72-bit accumulators are the highest precision in the

industry

32K x 32-bit SRAM with three 2K blocks assignable to

either Y data or program memory

Integrated DAC and ADC Functionality

†

8

Channels of 24-bit DAC output: 108dB DR, –98 dB

THD+N

†

4

Channels of 24-bit ADC input: 105dB DR, –98 dB

THD+N

Integrated 5:1 analog mux feeds one stereo ADC

Configurable Serial Audio Inputs and Outputs

Integrated 192 kHz S/PDIF Rx

Integrated 192 kHz S/PDIF Tx

Supports 32-bit serial data @ 192 kHz

Supports 32-bit audio sample I/O between DSP chips

TDM I/O modes

Supports Different Sample Rates (Fs)

Three integrated hardware SRC blocks

Output can be master or slave

Supports dual-domain Fs on S/PDIF vs. I²S inputs

DSP Tool Set with Private Keys Protect Customer IP

Integrated Clock Manager/PLL

Flexibility to operate from internal PLL, external crystal,

external oscillator

Input Fs Auto Detection w/ µC Acknowledgement

The CS470xx family is a new generation of audio

system-on-a-chip (ASOC) processors targeted at high

fidelity, cost sensitive designs. Derived from the highly

successful CS48500 32-bit fixed-point audio enhancement

processor family, the CS470xx further simplifies system

design and reduces total system cost by integrating the S/

PDIF Rx, S/PDIF Tx, analog inputs, analog outputs, and

SRCs. For example, a hardware SRC can down-sample a

192 kHz S/PDIF stream to a lower Fs to reduce memory

and MIPS requirements for processing. This integration

effectively reduces the chip count from 3 to 1, which allows

smaller, less expensive board designs.

Target applications include:

Automotive head units and outboard amplifiers

Automotive processors and automotive integration hubs

Digital TV

MP3 docking stations

AVR and DVD RX

DSP controlled speakers (subwoofers, sound bars)

The CS470xx is programmed using the simple yet powerful

Cirrus proprietary DSP Composer™ GUI development and

pre-production tuning tool. Processing chains can be

designed using a drag-and-drop interface to place/utilize

functional macro audio DSP primitives and custom audio

filtering blocks. The end result is a software image that is

downloaded to the DSP via serial control port.

The Cirrus Framework™ programming environment offers

Assembly and C language compilers and other software

development tools for porting existing code to the CS470xx

family platform.

The CS470xx is available in a 100-pin LQFP package with

exposed pad for better thermal characteristics. Both

Commercial (0°C to +70°C) and Automotive (–40°C to

+85°C) temperature grades.

Host Control and Boot via I²C™ or SPI™ Serial Interface

Configurable GPIOs and External Interrupt Input

1.8V Core and a 3.3V I/O that is tolerant to 5V input

Low-power Mode

†”

“

features differ on CS47024, CS47028, or CS47048.

See Table 3-1.

Copyright Cirrus Logic, Inc. 2012

http://www.cirrus.com

(All Rights Reserved)

Ordering Information:

See Section 6 for ordering information.

DS787PP9

JUL '12

Page 2

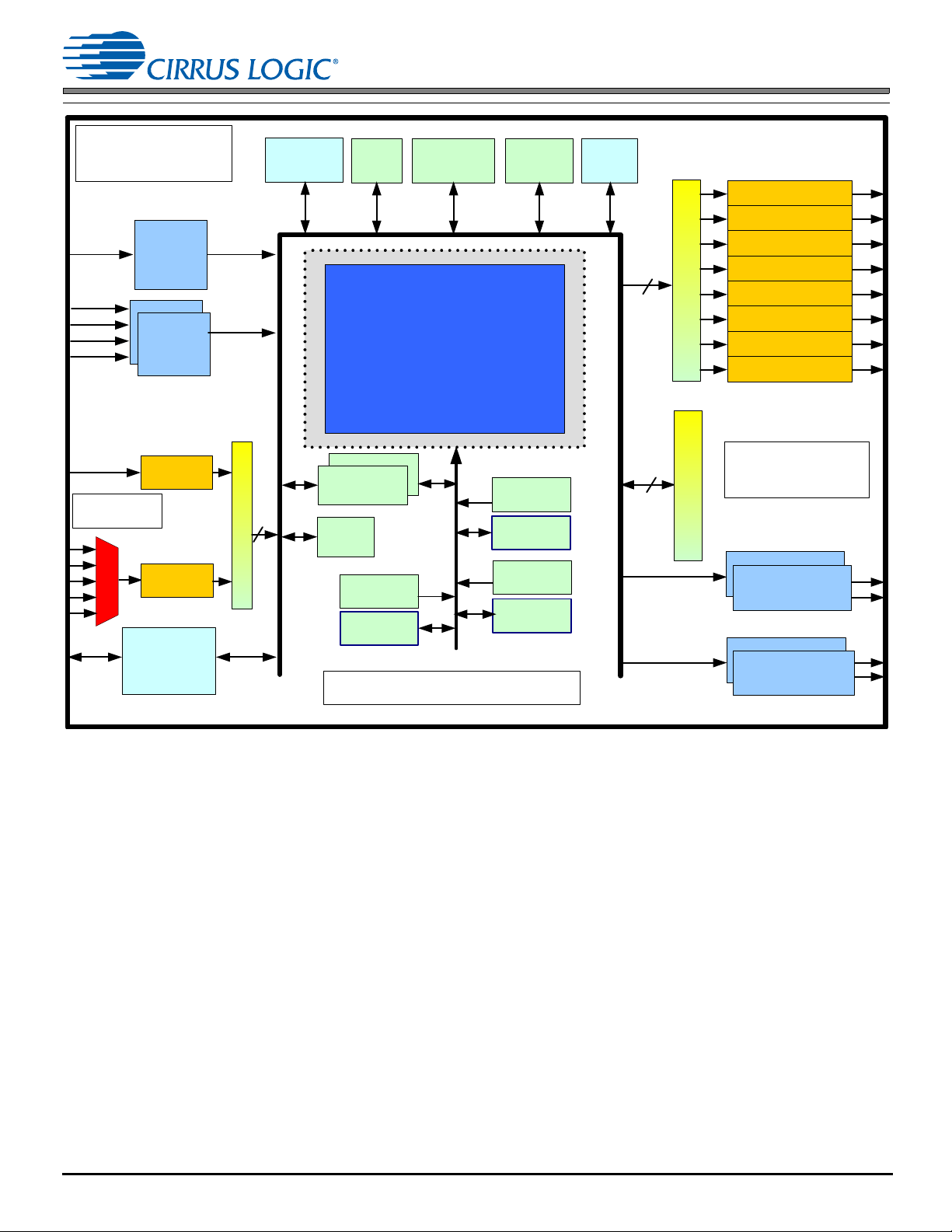

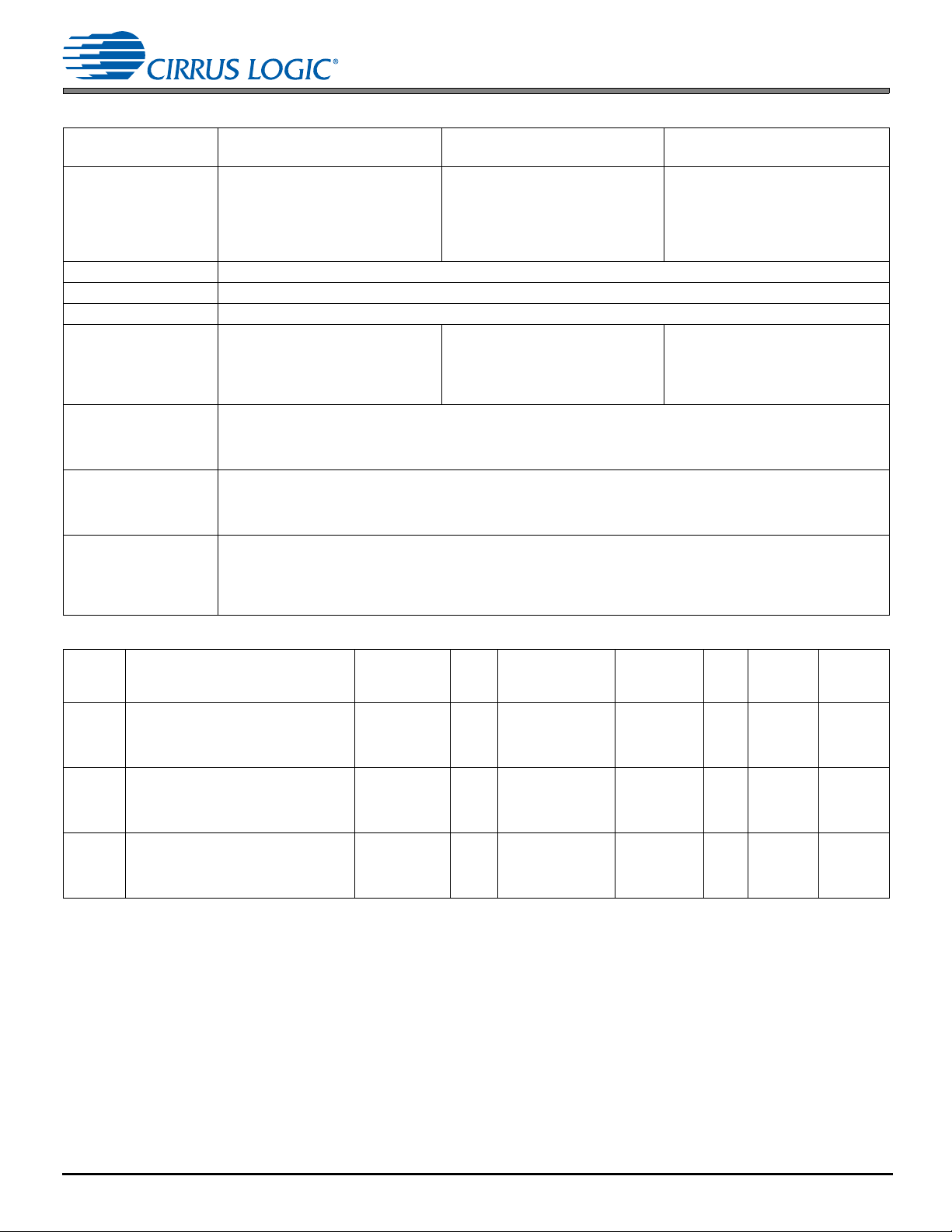

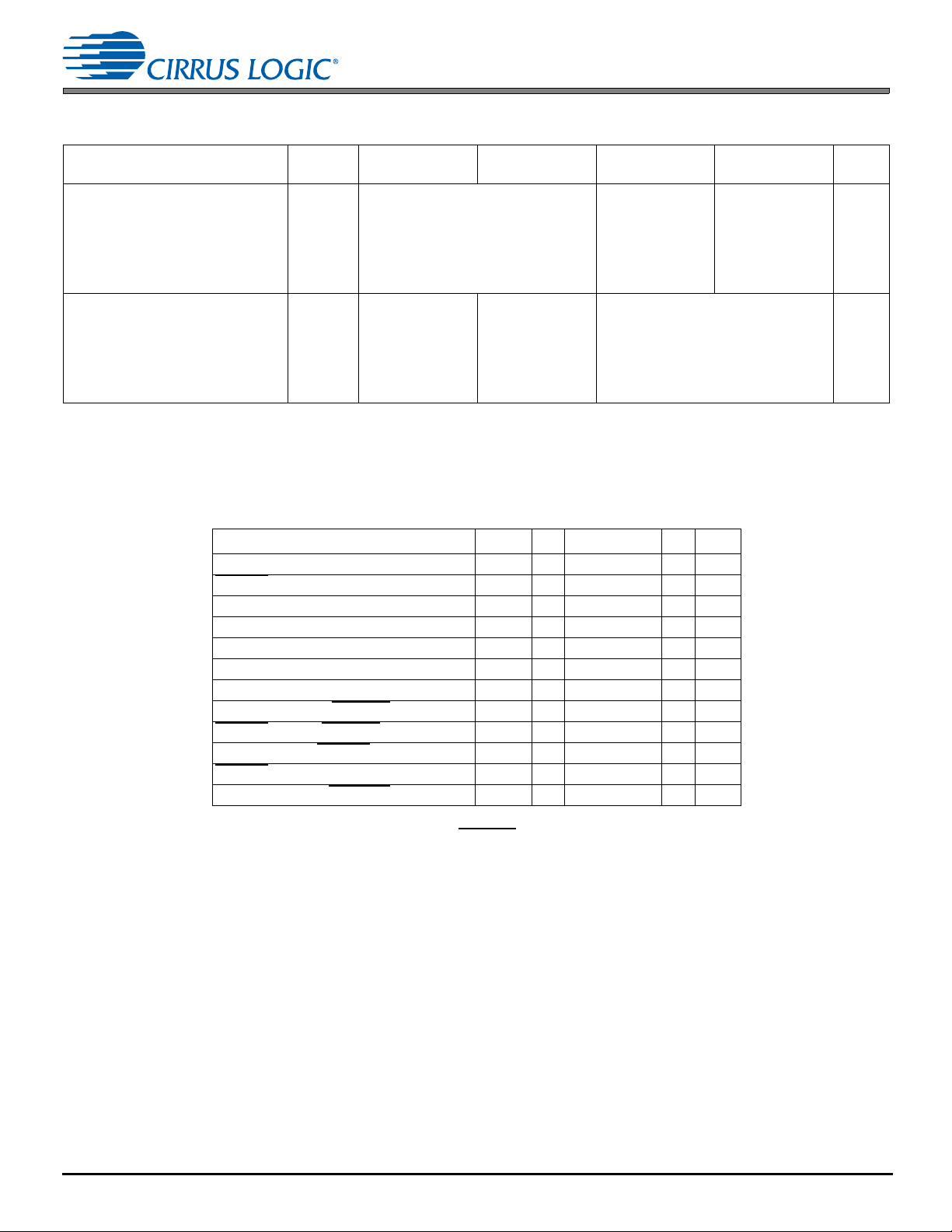

x8

x4

x2

x2

DAC0

text

Coyote 32-bit Core

in the CS47048 DSP

DMA

SPI / I2C

Control

I2S

ADC0/1

I2S

I2S / S/PDIF

PLL

ROM

S

R

C

2

Peripheral Bus

Clock

Manager

Timers

RAM

X

GPIO

DAC1

DAC2

DAC3

DAC4

DAC5

DAC6

DAC7

MUX

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-bit SRAM with three 2K blocks

Assignable to Program or Y Data memory

Memory Bus

I2S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/3

DBC

(I2C Slave)

PIC

ADC’s & DAC’s operate

in Single ended or

Differential mode

S

R

C

3

8ch

8ch

SRC3 has 8

independent Channels

for In or Out

4ch

DS787PP9 2

CS47048 Block Diagram

Page 3

Contacting Cirrus Logic Support

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find the one nearest you, go to www.cirrus.com.

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information is subject to change

without notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify,

before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order

acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information,

including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property

of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other

intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for

use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general

distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS

SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS.

INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK AND CIRRUS DISCLAIMS AND MAKES

NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR

PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS

THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS,

EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR

ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, Framerwork, and DSP Composer are trademarks of Cirrus Logic, Inc. All other brand and product names in this document

may be trademarks or service marks of their respective owners.

SPI is a trademark of Motorola, Inc.

I²C is a trademark of Philips Semiconductor.

Dolby, Pro Logic, Dolby Headphone, Virtual Speaker and the double-D symbol are registered trademarks of Dolby Laboratories, Inc. Supply of an implementation of Dolby

Technology does not convey a license nor imply a right under any patent, or any other industrial or Intellectual Property Right of Dolby Laboratories, to use the Implementation

in any finished end-user or ready-to-use final product. It is hereby notified that a license for such use is required from Dolby Laboratories.

SRS CircleSurround II technology is incorporated under license from SRS Labs, Inc. The SRS Circle Surround II technology/solution rights incorporated in the Cirrus Logic

CS470xx products are owned by SRS Labs, a U.S. Corporation and licensed to Cirrus Logic, Inc. Purchaser of the Cirrus Logic CS470xx products must sign a license for use

of the chip and display of the SRS Labs trademarks. Any products incorporating the Cirrus Logic CS470xx products must be sent to SRS Labs for review. SRS CircleSurround

II is protected under US and foreign patents issued and/or pending. SRS Circle Surround II, SRS and (O) symbol are trademarks of SRS Labs, Inc. in the United States and

selected foreign countries. Neither the purchase of the Cirrus Logic CS470xx products, nor the corresponding sale of audio enhancement equipment conveys the right to sell

commercialized recordings made with any SRS technology/solution. SRS Labs requires all set makers to comply with all rules and regulations as outlined in the SRS

Trademark Usage Manual.

3 DS787PP9

Page 4

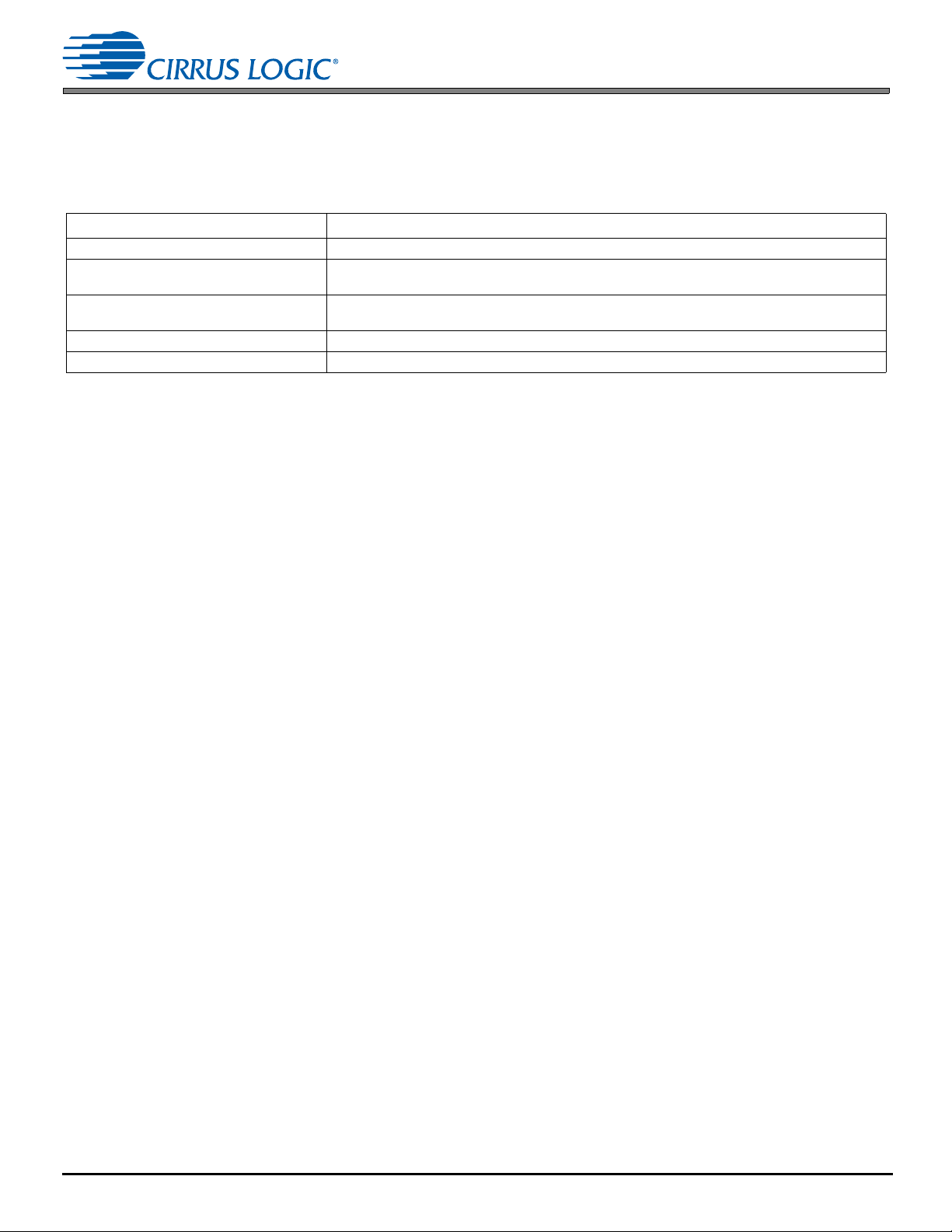

1 Documentation Strategy

1 Documentation Strategy

The CS470xx Data Sheet describes the CS47048, CS47028, and CS47024 audio processors. This document should be

used in conjunction with the following documents when evaluating or designing a system around the CS470xx processors.

Table 1-1. CS470xx Related Documentation

Document Name Description

CS470xx Data Sheet This document

CS470xx Hardware User’s Manual Guide Includes detailed system design information such as typical connection diagrams, boot-proce-

AN333 - CS470xx Firmware User’s Manual Includes a list of firmware modules available on the CS470xx family platform and detailed firm-

DSP Composer User’s Manual Includes detailed configuration and usage information for the GUI development tool

CDB470xx User’s Manual Includes detailed instructions on the use of the CDB470xx development board

dures, and pin descriptions

ware design information including signal processing flow diagrams and control API information

The scope of the CS470xx Data Sheet is primarily the hardware specifications of the CS470xx family of devices. This

includes hardware functionality, characteristic data, pinout, and packaging information.

The intended audience for the CS470xx Data Sheet is the system PCB designer, MCU programmer, and the quality control

engineer.

2 Overview

The CS470xx DSP is designed to provide high-performance post-processing and mixing of analog and digital audio. Dual

clock domains are supported when the DAI and SPDIF RX inputs are used together. Integrated sample rate converters

(SRCs) allow audio streams with different sample rates to be mixed. The low-power standby preserves battery life for

applications that are always on, but not necessarily processing audio, such as automotive audio systems.

The CS470xx uses voltage-out DACs and is capable of supporting dual input clock domains through the use of the internal

SRCs. The CS470xx is available in a 100-pin LQFP package. Refer to Table 3-1 and Table 3-2 for the input, output, and

firmware configurations for the CS470xx DSP.

2.1 Licensing

Licenses are required for any third-party audio processing algorithms provided for the CS470xx. Contact your local Cirrus

Logic Sales representative for more information.

DS787PP9 4

Page 5

3 Code Overlays

3 Code Overlays

The suite of software available for the CS470xx family consists of an operating system (OS) and a library of overlays. The

software components for the CS470xx family include:

1. OS/Kernel—Encompasses all non-audio processing tasks, including loading data from external serial memory,

processing host messages, calling audio-processing subroutines, error concealment, etc.

2. Decoder—Any module that performs a compressed audio decode on IEC61937-packed data delivered via S/PDIF

Rx or I²S input, such as Dolby Digital (AC3).

3. Matrix-processor—Any Module that performs a matrix decode on PCM data to produce more output channels than

input channels (2Æn channels). Examples are Dolby

speaking, these modules increase the number of valid channels in the audio I/O buffer.

4. Virtualizer-processor—Any module that encodes PCM data into fewer output channels than input channels (nÆ2

channels) with the effect of providing “phantom” speakers to represent the physical audio channels that were

eliminated. Examples are Dolby Headphone

modules reduce the number of valid channels in the audio I/O buffer.

5. Post-processors—Any module that processes audio I/O buffer PCM data. Examples are bass management, audio

manager, tone control, EQ, delay, customer-specific effects, and any post-processing algorithms available for the

CS470xx DSP.

The bulk of standard overlays are stored in ROM within the CS470xx, but a small image is required to configure the

overlays and boot the DSP. This small image can either be stored in an external serial flash/EEPROM, or downloaded via

a host controller through the SPI/I²C serial port.

®

2 and Dolby® Virtual Speaker® 2. Generally speaking, these

®

Pro Logic® IIx and SRS Circle Surround II®. Generally

The overlay structure reduces the time required to reconfigure the DSP when a processing change is requested. Each

overlay can be reloaded independently without disturbing the other overlays. For example, when a different post-processor

is selected, the OS, does not need to be reloaded—only the new post-processor.

Table 3-1 lists the different configuration options available. Refer to the CS470xx Firmware User’s Manual for the latest

listing of application codes and Cirrus Framework™ modules available. See Table 3-2, which provides a summary of the

available channels for each type of input and output communication mode for members of the CS470xx family of DSPs.

5 DS787PP9

Page 6

Table 3-1. CS470xx Device Selection Guide

3 Code Overlays

Features

Primary Applications • 4-In/8-Out Car Audio

Package 100-pin LQFP with Exposed Pad

DSP Core Cirrus Logic 32-bit Core

SRAM 32K x 32-bit SRAM with three 2K blocks x 32-bit SRAM, assignable to either Y data or program memory

Integrated DAC and ADC • 2 Channels of ADC input: with inte-

Configurable Serial Audio

Inputs/Outputs

Supports Different Fs

Sample Rates

Other Features • Integrated Clock Manager/PLL with flexibility to operate from internal PLL, external crystal, external oscillator

• High-end Digital TV

• Dual Source/Dual Zone

• 2 additional channels of ADC in-

• 8 channels of DAC output

• Integrated 192 kHz S/PDIF Rx, 2 Integrated 192 kHz S/PDIF Tx

• I2S support for 32-bit Samples @ 192 kHz

• TDM Input modes (Up to 8 channels)

• TDM Output modes (Up to 8 channels)

• Integrated hardware SRC blocks for all ADC and DAC channels

• Additional 8-channel hardware SRC block

• Dual-domain Fs on inputs (I2S and S/PDIF Rx)

• Output can be master or slave

• Host Control and Boot via SPI/I²C Serial Interface

• DSP Tool Set w/ Private Keys Protect Customer IP

• Configurable GPIOs and External Interrupts

• Hardware Watchdog Timer

CS47048-CQZ

CS47048-DQZ

• 2-In/8-Out Car Audio

• Sound Bar

•DVD Receiver

• 2 channels of ADC input: with inte-

grated 5:1 analog mux

• 8 channels of DAC output

put: without mux

CS47028-CQZ

CS47028-DQZ

grated 5:1 analog mux

CS47024-CQZ

CS47024-DQZ

• 2-In/4-Out Car Audio

• Digital TV

• Portable Audio Docking Station

• Portable DVD

• DVD Mini / Receiver

• Multimedia PC Speakers

• 2 channels of ADC input: with integrated 5:1 analog mux

• 4 channels of DAC output

T able 3-2. CS470xx Channel Count

Product

CS47048 • Up to 5 I2S lines, 2 channels per

line or

• 1 TDM line, up to 8 channels per

line.

CS47028 • Up to 5 I2S lines, 2 channels per

line or

• 1 TDM line, up to 8 channels per

line.

CS47024 • Up to 5 I2S lines, 2 channels per

line or

• 1 TDM line, up to 8 channels per

line.

1. Contact your Cirrus Logic representative to determine the TDM modes that are supported. The CS470xx can support up to 8 channels per line, but

the DSP software provided for the IC can restrict this capability.

PCM/TDM In

1

TDM Out

Up to 8 channels

Up to 8 channels

Up to 8 channels

PCM

1

Out

ADC with 5:1

Input Mux

82 2812

82 0812

82 0412

ADC with-

out Mux

DAC

Out

S/PDIF In

(Stereo

Pairs)

S/PDIF

Out (Ste-

reo Pairs)

DS787PP9 6

Page 7

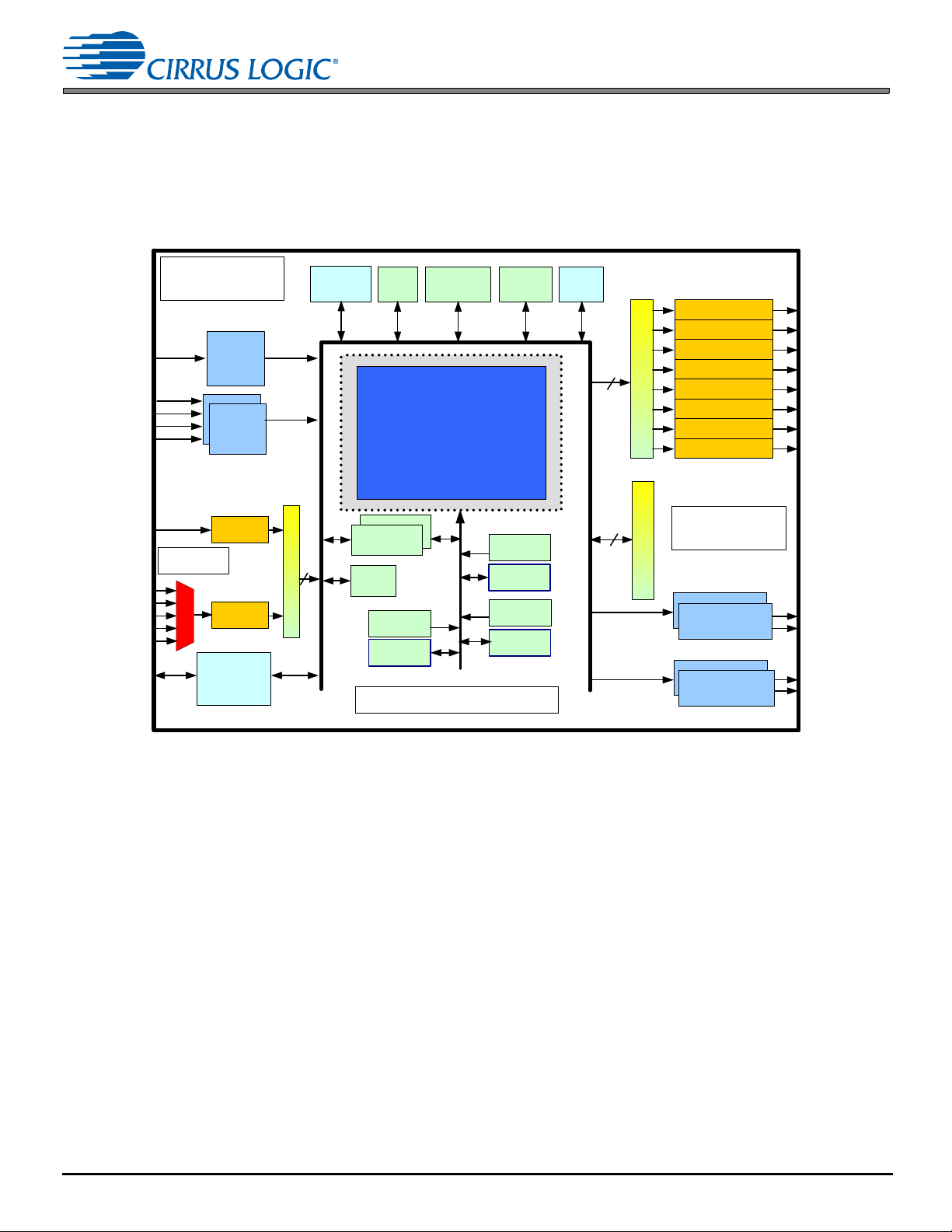

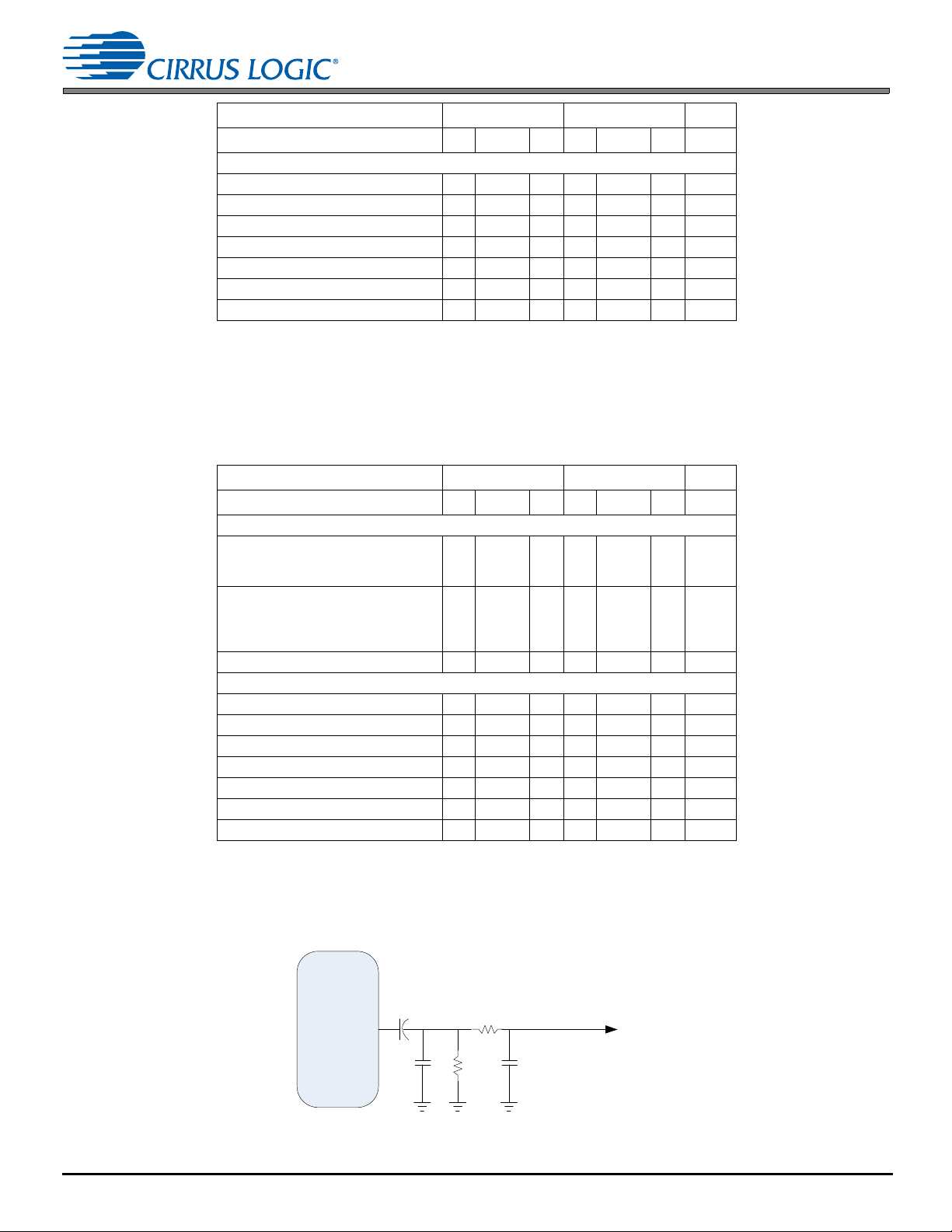

x8

x4

x2

x2

DAC0

text

32-bit Core

in the CS47048 DSP

DMA

SPI / I2C

Control

I2S

ADC0 /1

I2S

I2S / S/PDIF

PLL

ROM

S

R

C

2

Periphe r al Bus

Clock

Manager

Timers

RAM

X

GPIO

DAC1

DAC2

DAC3

DAC4

DAC5

DAC6

DAC7

MUX

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-b i t S RA M wi th thr ee 2K blo cks

Assignable to Program or Y Data memory

Memory Bus

I2S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/ 3

DBC

(I2C Slave )

PIC

ADC’s & DA C’s ope r at e

in Single ended or

Di fferen ti al mo d e

S

R

C

3

8ch

8ch

SRC3 h as 8

independent Channels

for In or Out

4ch

4 Hardware Functional Description

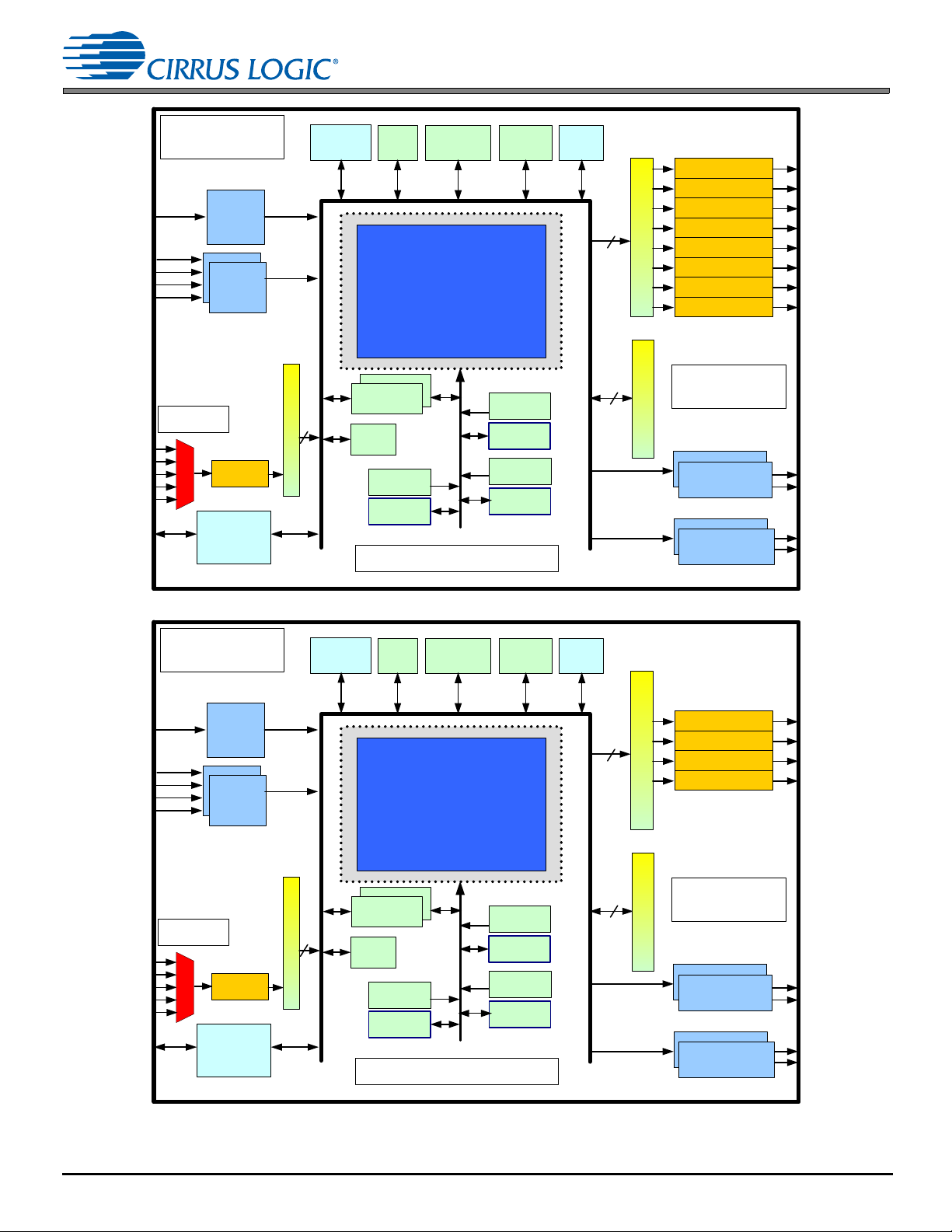

4 Hardware Functional Description

The CS470xx family, which includes the CS47048, CS47028, and CS47024 DSPs, is a true system-on-a-chip that

combines a powerful 32-bit DSP engine with analog/digital audio inputs and analog/digital audio outputs. It can be

integrated into a complex multi-DSP processing system, or stand alone in an audio product that requires analog-in and

analog-out. A top level block diagram for the CS47048, CS47028, and CS47024 products are shown in Fig. 4-1, Fig. 4-2,

and Fig. 4-3 respectively.

7 DS787PP9

Figure 4-1. CS47048 Top-level Block Diagram

Page 8

x8

x4

x2

x2

DAC0

text

32-bit Core

in the CS47028 DSP

DMA

SPI / I2C

Control

I2S

I2S

I2S / S/PDIF

PLL

ROM

S

R

C

2

Peripheral Bus

Clock

Manager

Timers

RAM

X

GPIO

DAC1

DAC2

DAC3

DAC4

DAC5

DAC6

DAC7

MUX

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-b i t S RA M wi th thr ee 2K blo cks

Assignable to Program or Y Data memory

Memory Bus

I2S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/ 3

DBC

(I2C Slave )

PIC

ADC’s & DA C’s ope r at e

in Single ended or

Di fferen ti al mo d e

S

R

C

3

8ch

8ch

SRC3 h as 8

independent Channels

for In or Out

4ch

x8

x4

x2

x2

text

32-bit Core

in the CS47024 DSP

DMA

SPI / I2C

Control

I2S

I2S

I2S / S/PDIF

PLL

ROM

S

R

C

2

Peripheral Bus

Clock

Manager

Timers

RAM

X

GPIO

DAC0

DAC1

DAC2

DAC3

MUX

S

R

C

1

ROM

RAM

ROM

RAM

P

Y

32K x 32-b i t S RA M wi th thr ee 2K blo cks

Assignable to Program or Y Data memory

Memory Bus

I2S /

S/PDIF

Stereo Inputs

On Analog in

ADC2/ 3

DBC

(I2C Slave )

PIC

ADC’s & DA C’s ope r at e

in Single ended or

Di fferen ti al mo d e

S

R

C

3

8ch

8ch

SRC3 h as 8

independent Channels

for In or Out

4ch

4 Hardware Functional Description

DS787PP9 8

Figure 4-2. CS47028 Top-level Block Diagram

Figure 4-3. CS47024 Top-level Block Diagram

Page 9

4.1 Cirrus Logic 32-bit DSP Core

4.1 Cirrus Logic 32-bit DSP Core

The CS470xx comes with a Cirrus Logic 32-bit core with separate X and Y data and P code memory spaces. The DSP

core is a high-performance, 32-bit, user-programmable, fixed-point DSP that is capable of performing two

multiply-and-accumulate (MAC) operations per clock cycle. The DSP core has eight 72-bit accumulators, four X-data and

four Y-data registers, and 12 index registers.

The DSP core is coupled to a flexible 8-channel DMA engine. The DMA engine can move data between peripherals such

as the serial control port (SCP), digital audio input (DAI) and digital audio output (DAO), sample rate converters (SRC),

analog-to-digital converters (ADC), digital-to-analog converters (DAC), or any DSP core memory, all without the

intervention of the DSP. The DMA engine off-loads data move instructions from the DSP core, leaving more MIPS

available for signal processing instructions.

CS470xx functionality is controlled by application codes that are stored in on-chip ROM or downloaded to the CS470xx

from a host controller or external serial flash/EEPROM.

Users can develop applications using the DSP Composer™ tool to create the processing chain and then compile the

image into a series of commands that are sent to the CS470xx through the SCP. The processing application can either

load modules (post-processors) from the DSPs on-chip ROM, or custom firmware can be downloaded through the SCP.

The CS470xx is suitable for a variety of audio post-processing applications where sound quality via sound enhancement

and speaker/cabinet tuning is required to achieve the sound quality consumers expect. Examples of such applications

include automotive head-ends, automotive amplifiers, docking stations, sound bars, subwoofers, and boom boxes.

4.2 DSP Memory

The DSP core has its own on-chip data and program RAM and ROM and does not require external memory for

post-processing applications.

The Y-RAM and P-RAM share a single block of memory that includes three 2K word blocks (32 bits/word) that are

assignable to either Y-RAM or P-RAM as shown in Table 4.

Table 4-1. Memory Configurations for the C470xx

P-RAM X-RAM Y-RAM

14K words 10K words 8K words

12K words 10K words 10K words

10K words 10K words 12K words

8K words 10K words 14K words

4.2.1 DMA Controller

The powerful 8-channel DMA controller can move data between 8 on-chip resources. Each resource has its own arbiter:

X, Y, and P RAMs/ROMs and the peripheral bus. Modulo and linear addressing modes are supported, with flexible start

address and increment controls. The service intervals for each DMA channel, as well as up to 6 interrupt events, are

programmable.

4.3 On-chip DSP Peripherals

4.3.1 Analog to Digital Converter Port (ADC)

The ADCs in the CS470xx devices feature dynamic range performance in excess of 100 dB. See Section 5.16 for more

details on CS470xx ADC performance. The CS47024 and CS47028 devices support up to 2 simultaneous channels of

analog-to-digital conversion with the input source selectable using an integrated 5:1 stereo analog mux (analog inputs

AIN_2A/B through AIN_6A/B). The CS47048 device adds a second pair of ADCs that are directly connected to input pins

AIN_1A/B providing a total of 4 simultaneous channels of analog-to-digital conversion. This feature gives the CS47048 the

ability to select from a total of six stereo pairs of analog input. A single programmable bit selects single-ended or differential

mode signals for all inputs. The conversions are performed with Fs=96 kHz.

9 DS787PP9

Page 10

4.3 On-chip DSP Peripherals

4.3.2 Digital to Analog Converter Port (DAC)

The DACs in the CS470xx devices feature dynamic range performance in excess of 100 dB. See Section 5.17 for more

details on CS470xx DAC performance. The CS47024 device supports four simultaneous channels of digital-to-analog

conversion. The CS47028 and CS47048 devices provide eight simultaneous channels of digital-to-analog conversion. The

DACs have voltage mode outputs that can be connected either as single-ended or differential signals. The conversions

are performed with Fs=96 kHz.

4.3.3 Digital Audio Input Port (DAI)

The input capabilities for each version of the CS470xx are summarized in Table 3-1 and Table 3-2.

Up to five DAI ports are available. Two of the DAI ports can be programmed to implement other functions. If the SPI mode

is used, the DAI_DATA4 pin becomes the SCP_CS input. The integrated S/PDIF receiver can be used to take over the

DAI_DATA3 pin.

The DAI port PCM inputs have a single slave-only clock domain. The S/PDIF receiver, if used, is a separate clock domain.

The output of the S/PDIF Rx can then be converted through one of the internal SRC blocks to synchronize with the PCM

input. The sample rate of the input clock domains can be determined automatically by the DSP, off-loading the task of

monitoring the S/PDIF Rx from the host. A time-stamping feature provides the ability to also sample-rate convert the input

data via software.The DAI port supports PCM format with word lengths up to 32 bits and sample rates as high as 192 kHz.

The DAI also supports a time division multiplexed (TDM) mode that packs up to 10 PCM audio channels on a single data

line.

4.3.4 S/PDIF RX Input Port (DAI)

One of the PCM pins of the DAI can also be used as a DC-coupled, TTL-level S/PDIF Rx input capable of receiving and

demodulating bi-phase encoded S/PDIF signals with Fs <

192 kHz.

4.3.5 Digital Audio Output Port (DAO)

DAO port supports PCM resolutions of up to 32-bits. The port supports sample rates (Fs) as high as 192 kHz. The port

can be configured as an independent clock domain mastered by the DSP, or as a clock slave if an external MCLK or SCLK/

LRCLK source is available.

The DAO also supports a time division multiplexed (TDM) mode, that packs up to 8 channels of PCM audio on a single

data line.

4.3.6 S/PDIF TX Output Port (DAO)

Two of the serial audio pins can be re-configured as S/PDIF TX pins that drive a bi-phase encoded S/PDIF signal (data

with embedded clock on a single line).

4.3.7 Sample Rate Converters (SRC)

All CS470xx devices have at least two internal hardware SRC modules. One is directly associated with the ADCs and

normally serves to convert data from the 96 kHz sampling rate of the ADCs to another Fs appropriate for mixing with other

audio in the system.

The other SRC module is directly associated with the DACs and normally serves to convert data from the DSP into the 96

kHz sample rate needed by the DACs.

The CS47024, CS47028, and CS47048 devices have an additional stand-alone 8-channel SRC module. This SRC module

can be used to make independent input clock domains synchronous (different Fs on PCM input and S/PDIF Rx).

DS787PP9 10

Page 11

4.4 DSP I/O Description

4.3.8 Serial Control Port (I2C or SPI)

The on-chip serial control port is capable of operating as master or slave in either SPI or I2C modes. Master/Slave

operation is chosen by mode select pins when the CS470xx comes out of reset. The serial clock pin can support

frequencies as high as 25 MHz in SPI mode (SPI clock speed must always be <

serial control port also includes a pin for flow control of the communications interface (SCP_BSY) and a pin to indicate

when the DSP has a message for the host (SCP_IRQ).

(DSP Core Frequency/2)). The CS470xx

4.3.9 GPIO

Many of the CS470xx peripheral pins are multiplexed with GPIO. Each GPIO can be configured as an output, an input, or

an input with interrupt. Each input-pin interrupt can be configured as rising edge, falling edge, active-low, or active-high.

4.3.10 PLL-based Clock Generator

The low-jitter PLL generates integer or fractional multiples of a reference frequency, which is used to clock the DSP core

and peripherals. Through a second PLL divider chain, a dependent clock domain can be output on the DAO port for driving

audio converters. The CS470xx defaults to running from the external reference frequency and is switched to use the PLL

output after overlays have been loaded and configured, either through master boot from an external flash or through host

control. A built-in crystal oscillator circuit with a buffered output is provided. The buffered output frequency ratio is

selectable between 1:1 (default) or 2:1.

4.3.11 Hardware Watchdog Timer

The CS470xx has an integrated watchdog timer that acts as a “health” monitor for the DSP. The watchdog timer must be

reset by the DSP before the counter expires, or the entire chip is reset. This peripheral ensures that the CS470xx resets

itself in the event of a temporary system failure. In stand-alone mode (where there is no host MCU), the DSP reboots from

external flash. In slave mode (where the host MCU is present), a GPIO is used to signal the host that the watchdog has

expired and the DSP should be rebooted and re-configured.

4.4 DSP I/O Description

4.4.1 Multiplexed Pins

Many of the CS470xx pins are multifunctional. For details on pin functionality, see Section 10.5, “Pin Assignments”, in the

CS470xx Hardware User’s Manual.

4.4.2 Termination Requirements

Open-drain pins on the CS470xx must be pulled high for proper operation. See the CS470xx Hardware User’s Manual to

identify which pins are open-drain and what value of pull-up resistor is required for proper operation.

Mode select pins on CS470xx are used to select the boot mode on the rising edge from reset. A detailed explanation of

termination requirements for each communication mode select pin can be found in the CS470xx Hardware User’s Manual.

4.4.3 Pads

The CS470xx Digital I/Os operate from the 3.3 V supply and are 5 V tolerant.

4.5 Application Code Security

The external program code can be encrypted by the programmer to protect any intellectual property it contains. A secret,

customer-specific key is used to encrypt the program code that is to be stored external to the device. Contact your local

Cirrus representative for details.

11 DS787PP9

Page 12

5 Characteristics and Specification s

5 Characteristics and Specifications

Note: All data sheet minimum and maximum timing parameters are guaranteed over the rated voltage and temperature.

All data sheet typical parameters are measured under the following conditions: T = 25°C, VDD = 1.8 V, VDDIO =

VDDA = 3.3 V, GND = GNDIO = GNDA = 0 V.

5.1 Absolute Maximum Ratings

(GND = GNDIO = GNDA = 0V; all voltages with respect to 0V)

Parameter Symbol Min Max Unit

DC power supplies:

Core supply

Analog supply

I/O supply

|VDDA–VDDIO|

Input pin current, any pin except supplies I

Input voltage on PLL_REF_RES V

Input voltage on digital I/O pins V

Analog Input Voltage V

Storage temperature T

WARNING: Operation at or beyond these limits can result in permanent damage to the device. Normal operation is not

guaranteed at these extremes.

VDD

VDDA

VDDIO

in

filt

inio

in

stg

–0.3

–0.3

–0.3

—

— ±10 mA

–0.3 3.6 V

–0.3 5.0 V

AGND–0.7 VA+0.7 V

–65 150 °C

2.0

3.6

3.6

0.3

V

V

V

V

5.2 Recommended Operating Conditions

(GND = GNDIO = GNDA = 0V; all voltages with respect to 0V)

Parameter Symbol Min Typ Max Unit

DC power supplies:

Core supply

Analog supply

I/O supply

|VDDA – VDDIO|

Ambient operating temperature

Commercial—CQZ (147 MHz)

Automotive—DQZ (131 MHz)

Automotive—DQZ (113 MHz)

VDD

VDDA

VDDIO

T

A

1.71

3.13

3.13

0

–40

–40

1.8

1.89

3.3

3.46

3.3

3.46

0

—+70

+85

+105

V

V

V

V

°C

Note: It is recommended that the 3.3 V IO supply come up ahead of or simultaneously with the 1.8 V core supply.

5.3 Digital DC Characteristics

(Measurements performed under static conditions.)

Parameter Symbol Min Typ Max Unit

High-level input voltage V

Low-level input voltage, except XTI V

Low-level input voltage, XTI V

Input Hysteresis V

High-level output voltage (I

Low-level output voltage (I

Input leakage XTI I

Input leakage current (all digital pins with internal

pull-up resistors enabled)

= –2mA), except XTO V

O

= 2mA), except XTO V

O

I

IH

IL

ILKXTI

hys

OH

OL

LXTI

LEAK

2.0 — — V

——0.8V

——0.6V

—0.4— V

VDDIO*0.9 — — V

— — VDDIO*0.1 V

—— 5 μA

——70μA

DS787PP9 12

Page 13

5.4 Power Supply Characteristics

Note: Measurements performed under operating conditions

Parameter Min Typ Max Unit

Operational Power Supply Current:

VDD: Core and I/O operating

VDDA: PLL operating current

VDDA: DAC operating current (all 8 channels enabled)

VDDA: ADC operating current (all 4 channels enabled)

VDDIO: With most ports operating

1

5.4 Power Supply Characteristics

—

325

—

—

—

—

—

16

56

34

27

—

—

—

—

mA

mA

mA

mA

mA

Total Operational Power Dissipation:

Standby Power Supply Current:

VDD: Core and I/O not clocked

VDDA: PLLs halted

VDDA: DAC disabled

VDDA: ADC disabled

VDDIO: All connected I/O pins 3-stated by other ICs in system

Total Standby Power Dissipation:

1. Dependent on application firmware and DSP clock speed.

5.5 Thermal Data (100-pin LQFP with Exposed Pad)

Parameter Symbol Min Typ Max Unit

Thermal Resistance (Junction to Ambient)

Two-layer Board

Four-layer Board

Thermal Resistance (Junction to Top of Package)

Two-layer Board

Four-layer Board

1

2

1

2

1. To calculate the die temperature for a given power dissipation:

= Ambient temperature + [ (Power Dissipation in Watts) * ja ]

j

2. To calculate the case temperature for a given power dissipation:

= j - [ (Power Dissipation in Watts) * jt ]

c

ja

jt

1025

—

410

—

26

—

40

—

24

—

215

1745

——3418—

——0.54

—

.28——

—

—

—

—

—

mW

μA

μA

μA

μA

μA

μW

°C/Watt

°C/Watt

Note: Two-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1-oz. copper covering 20%

of the top and bottom layers.

Four-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1-oz. copper covering 20% of the

top and bottom layers and 0.5-oz. copper covering 90% of the internal power plane and ground plane layers.

5.6 Digital Switching Characteristics–RESET

Parameter Symbol Min Max Unit

RESET minimum pulse width low

All bidirectional pins high-Z after RESET

Configuration pins setup before RESET

Configuration pins hold after RESET

1. The rising edge of RESET must not occur before the power supplies are stable at the recommended operating values as described in Section 5.2. In

addition, for the configuration pins to be read correctly, the RESET

T

13 DS787PP9

1

high T

high T

requirement must be met.

rstl

low T

T

rstl

rst2z

rstsu

rsthld

1—s

— 200 ns

50 — ns

20 — ns

Page 14

T

rstl

T

rstsu

T

rsthld

HS[3:0]

All supplies at

recommended

operating values.

VDD

1

1

Refers to all power supplies.

RESET

RESET

T

rst2z

T

rstl

T

rstsu

T

rsthld

HS[3:0]

All Bidirectional

Pins

t

clkih

t

clkil

T

clki

XTI

5.7 Digital Switching Characteristics–XTI

Figure 5-1. RESET Timing at Power-on

Figure 5-2. RESET

Timing after Power is Stable

5.7 Digital Switching Characteristics–XTI

Parameter Symbol Min Max Unit

External Crystal operating frequency

XTI period T

XTI high time T

XTI low time T

External Crystal Load Capacitance (parallel resonant)

External Crystal Equivalent Series Resistance ESR — 50

1. Part characterized with the following crystal frequency values: 12.288 and 24.576 MHz.

2. C

refers to the total load capacitance as specified by the crystal manufacturer. Crystals that require a CL outside this range should be avoided. The

L

crystal oscillator circuit design should follow the crystal manufacturer’s recommendation for load capacitor selection.

1

Figure 5-3. XTI Timing

F

12.288 24.576 MHz

xtal

clki

clkih

clkil

2

C

41 81 ns

13.3 — ns

13.3 — ns

10 18 pF

L

DS787PP9 14

Page 15

5.8 Digital Switching Characteristics–Internal Clock

5.8 Digital Switching Characteristics–Internal Clock

Parameter Symbol

Internal DSP_CLK frequency

1

CS47048-CQZ

CS47048-DQZ

CS47028-CQZ

CS47028-DQZ

CS47024-CQZ

CS47024-DQZ

Internal DSP_CLK period

1

CS47048-CQZ

CS47048-DQZ

CS47028-CQZ

CS47028-DQZ

CS47024-CQZ

CS47024-DQZ

1. After initial power-on reset, F

reset.

2. See Section 5.7. for all references to F

dclk

= F

xtal

Min (2-

layer Boards)

F

dclk

(See Footnote 2)

F

F

F

F

F

F

DCLKP

6.8

7.6

6.8

7.6

6.8

7.6

. After initial kick-start commands, the PLL is locked to max F

.

xtal

Min (4-

layer Boards)

xtal

xtal

xtal

xtal

xtal

xtal

6.8

6.8

6.8

6.8

6.8

6.8

Max (2-

layer Boards)

147

131

147

131

147

131

1/F

1/F

1/F

1/F

1/F

1/F

and remains locked until the next power-on

dclk

Max (4-

layer Boards)

147

147

147

147

147

147

xtal

xtal

xtal

xtal

xtal

xtal

5.9 Digital Switching Characteristics–Serial Control Port–SPI Slave Mode

Parameter Symbol Min Typical Max Unit

xtal

/3.

1

rising t

rising t

falling t

f

spisck

spicss

spickl

spickh

spidsu

spidh

spidov

spiirqh

spiirql

spicsh

spicsdz

spicbsyl

——25MHz

24 — — ns

20 — — ns

20 — — ns

5——ns

5——ns

——11ns

— — 27 ns

0——ns

24 — — ns

—20—ns

— 3*DCLKP+20 — ns

pin should be implemented to prevent overflow of the input data

SCP_CLK frequency

SCP_CS

falling to SCP_CLK rising t

SCP_CLK low time t

SCP_CLK high time t

Setup time SCP_MOSI input t

Hold time SCP_MOSI input t

SCP_CLK low to SCP_MISO output valid t

SCP_CLK falling to SCP_IRQ

SCP_CS

rising to SCP_IRQ falling t

SCP_CLK low to SCP_CS

SCP_CS

rising to SCP_MISO output high-Z t

SCP_CLK rising to SCP_BSY

1. f

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication

spisck

port can be limited by the firmware application. Flow control using the SCP_BSY

buffer. At boot the maximum speed is F

Unit

MHz

ns

15 DS787PP9

Page 16

SCP_BSY

SCP_CS

SCP_CLK

SCP_MOSI

SCP_MISO

SCP_IRQ

0

12670

56

7

t

spicss

t

spickl

t

spickh

t

spidsu

t

spidh

t

spidov

A6 A5 A0 R/W MSB LSB

MSB

LSB

t

spicsh

t

spibsyl

t

spiirql

t

spiirqh

f

spisck

t

spicsdz

1/

5.10 Digital Switching Characteristics–Serial Control Port–SPI Master

5.10 Digital Switching Characteristics–Serial Control Port–SPI Master Mode

1. f

port can be limited by the firmware application.

2. See Section 5.7.

3. SCP_CLK PERIOD refers to the period of SCP_CLK as being used in a given application. It does not refer to a tested parameter.

Figure 5-4. Serial Control Port–SPI Slave Mode Timing

Parameter Symbol Min Typical Max Units

SCP_CLK frequency

EE_CS

falling to SCP_CLK rising

SCP_CLK low time t

SCP_CLK high time t

Setup time SCP_MISO input t

Hold time SCP_MISO input t

SCP_CLK low to SCP_MOSI output valid t

SCP_CLK low to EE_CS

SCP_CLK low to EE_CS

Bus free time between active EE_CS

SCP_CLK falling to SCP_MOSI output high-Z t

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication

spisck

1,2

3

falling t

rising t

f

spisck

t

spicss

spickl

spickh

spidsu

spidh

spidov

spicsl

spicsh

t

spicsx

spidz

——F

— 11*DCLKP+(SCP_CLK PERIOD)/2 — ns

18 — — ns

18 — — ns

9— —ns

5— —ns

—— 8ns

7— —ns

— 11*DCLKP+(SCP_CLK PERIOD)/2 — ns

— 3*DCLKP — ns

— — 20 ns

/2 MHz

xtal

DS787PP9 16

Page 17

EE_CS

SCP_CLK

SCP_MISO

SCP_MOSI

0

12670

56

7

t

spicss

t

spickl

t

spickh

t

spidsu

t

spidh

t

spidov

A6 A5 A0 R/W MSB LSB

MSB

LSB

t

spicsh

t

spicsx

f

spisck

t

spidz

t

spicsl

1/

5.11 Digital Switching Characteristics–Serial Control Port I2C Slave Mode

Figure 5-5. Serial Control Port–SPI Master Mode Timing

5.11 Digital Switching Characteristics–Serial Control Port I2C Slave Mode

Parameter Symbol Min Typical Max Units

SCP_CLK frequency

SCP_CLK rise time t

SCP_CLK fall time t

SCP_CLK low time t

SCP_CLK high time t

SCP_CLK rising to SCP_SDA rising or falling for START or STOP condition t

START condition to SCP_CLK falling t

SCP_CLK falling to STOP condition t

Bus free time between STOP and START conditions t

Setup time SCP_SDA input valid to SCP_CLK rising t

Hold time SCP_SDA input after SCP_CLK falling t

SCP_CLK low to SCP_SDA out valid t

SCP_CLK falling to SCP_IRQ

NAK condition to SCP_IRQ

SCP_CLK rising to SCB_BSY

1. f

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication

iicck

port can be limited by the firmware application. Flow control using the SCP_BSY

buffer.

I2C Slave Address = 0x82

1

rising t

low t

low t

f

iicck

iicckl

iicckh

iicckcmd

iicstscl

iicstp

iicbft

iicsu

iicdov

iicirqh

iicirql

iicbsyl

pin should be implemented to prevent overflow of the input data

—— 400kHz

—— 150ns

iicr

—— 150ns

iicf

1.25 — — µs

1.25 — — µs

1.25 — — µs

1.25 — — µs

2.5 — — µs

3— —µs

110 — — ns

100 — — ns

iich

—— 18 ns

— — 3*DCLKP+40 ns

—3*DCLKP+20 — ns

—3*DCLKP+20 — ns

17 DS787PP9

Page 18

SCP_BSY

SCP_CLK

SCP_SDA

SCP_IRQ

01 67801 7

t

iicckl

t

iicckh

t

iicsutiich

A6 A0 R/W ACK

LSB

t

iicirqh

t

iicirql

8

ACK

MSB

t

iicstp

6

t

iiccbsyl

t

iicdov

t

iicbft

t

iicstscl

t

iicckcmd

f

iicck

t

iicckcmd

t

iicf

t

iicr

Start Condition

1/

Stop Condition

SCP_CLK

SCP_SDA

01 67801 7

t

iicckl

t

iicckh

t

iicsutiich

A6 A0 R/W ACK

LSB

8

ACK

MSB

t

iicstp

6

t

iicdov

t

iicbft

t

iicstscl

t

iicckcmd

f

iicck

t

iicckcmd

t

iicf

t

iicr

1/

5.12 Digital Switching Characteristics–Serial Control Port–I2C Master

Figure 5-6. Serial Control Port–I2C Slave Mode Timing

5.12 Digital Switching Characteristics–Serial Control Port–I2C Master Mode

1. f

iicck

port can be limited by the firmware application.

Parameter Symbol Min Max Units

1

f

iicck

iicr

iicf

iicckl

iicckh

iicckcmd

iicstscl

iicstp

iicbft

iicsu

iich

iicdov

—400kHz

— 150 ns

— 150 ns

1.25 — µs

1.25 — µs

1.25 — µs

1.25 — µs

2.5 — µs

3—µs

110 — ns

100 — ns

—36 ns

SCP_CLK frequency

SCP_CLK rise time t

SCP_CLK fall time t

SCP_CLK low time t

SCP_CLK high time t

SCP_CLK rising to SCP_SDA rising or falling for START or STOP condition t

START condition to SCP_CLK falling t

SCP_CLK falling to STOP condition t

Bus free time between STOP and START conditions t

Setup time SCP_SDA input valid to SCP_CLK rising t

Hold time SCP_SDA input after SCP_CLK falling t

SCP_CLK low to SCP_SDA out valid t

indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication

DS787PP9 18

Figure 5-7. Serial Control Port–I2C Master Mode Timing

Page 19

DAI_SCLK

DAI_DATAn

t

daidh

t

daidsu

DAO_MCLK

DAO_SCLK

DAO_LRCLK

DAO_DATAn

t

daomsck

t

daomlrts

t

daomdv

t

daomclk

5.13 Digital Switching Characteristics–Digital Audio Slave Input Port

5.13 Digital Switching Characteristics–Digital Audio Slave Input Port

Parameter Symbol Min Max Unit

DAI_SCLK period T

daiclkp

20 — ns

DAI_SCLK duty cycle — 45 55 %

Setup time DAI_DATAn t

Hold time DAI_DATAn t

daidsu

daidh

8—ns

5—ns

Figure 5-8. Digital Audio Input (DAI) Port Timing Diagram

5.14 Digital Switching Characteristics–Digital Audio Output Port

Parameter Symbol Min Max Unit

DAO_MCLK period T

daomclk

DAO_MCLK duty cycle — 45 55 %

DAO_SCLK period for Master or Slave mode

DAO_SCLK duty cycle for Master or Slave mode

Master Mode (Output A1 Mode)

1,2

DAO_SCLK delay from DAO_MCLK rising edge, DAO MCLK as an input t

DAO_LRCLK to DAO_SCLK inactive edge

DAO_SCLK inactive edge

3

to DAO_LRCLK. See Fig. 5-10.t

DAO_DATA[3:0] delay from DAO_SCLK inactive edge

Slave Mode (Output A0 Mode)

4

DAO_SCLK active edge to DAO_LRCLK transition. See Fig. 5-11.t

DAO_LRCLK transition to DAO_SCLK active edge. See Fig. 5-12.t

DAO_Dx delay from DAO_SCLK inactive edge t

1. Master mode timing specifications are characterized, not production tested.

2. Master mode is defined as the CS47048 driving both DAO_SCLK, DAO_LRCLK. When MCLK is an input, it is divided to produce DAO_SCLK, DAO_

LRCLK.

3. The DAO_LRCLK transition can occur on either side of the edge of DAO_SCLK. The active edge of DAO_SCLK is the point at which the data is

valid.

4. Slave mode is defined as DAO_SCLK, DAO_LRCLK driven by an external source.

1

1

3

. See Fig. 5-9.t

3

T

daosclk

—4060%

daomsck

daomlrts

daomstlr

t

daomdy

daosstlr

daoslrts

daosdv

20 — ns

20 — ns

—19ns

—8 ns

—8 ns

—8 ns

10 — ns

10 — ns

—11ns

19 DS787PP9

Figure 5-9. DAO_LRCLK Transition before DAO_SCLK Inactive Edge

Page 20

DAO_MCLK

DAO_SCLK

DAO_LRCLK

DAO_DATAn

t

daomclk

t

daomstlr

t

daomdv

t

daomsck

DAO_SCLK

DAO_LRCLK

DAO_Dx

t

daoslrts

t

daosclk

DAO_SCLK

DAO_LRCLK

t

daosstlr

t

daosdv

t

daosclk

DAO_Dx

5.14 Digital Switching Characteristics–Digital Audio Output Port

Figure 5-10. DAO_LRCLK Transition after DAO_SCLK Inactive Edge

Figure 5-11. DAO_LRCLK Transition before DAO_SCLK Inactive Edge

Figure 5-12. DAO_LRCLK Transition after DAO_SCLK Inactive Edge

DS787PP9 20

Page 21

5.15 Digital Switching Characteristics–S/PDIF RX Port

5.15 Digital Switching Characteristics–S/PDIF RX Port

(Inputs: Logic 0 = VIL, Logic 1 = VIH, CL = 20 pF)

Parameter Symbol Min Typ Max Units

PLL Clock Recovery Sample Rate Range — 30 — 200 kHz

5.16 ADC Characteristics

5.16.1 Analog Input Characteristics (Commercial)

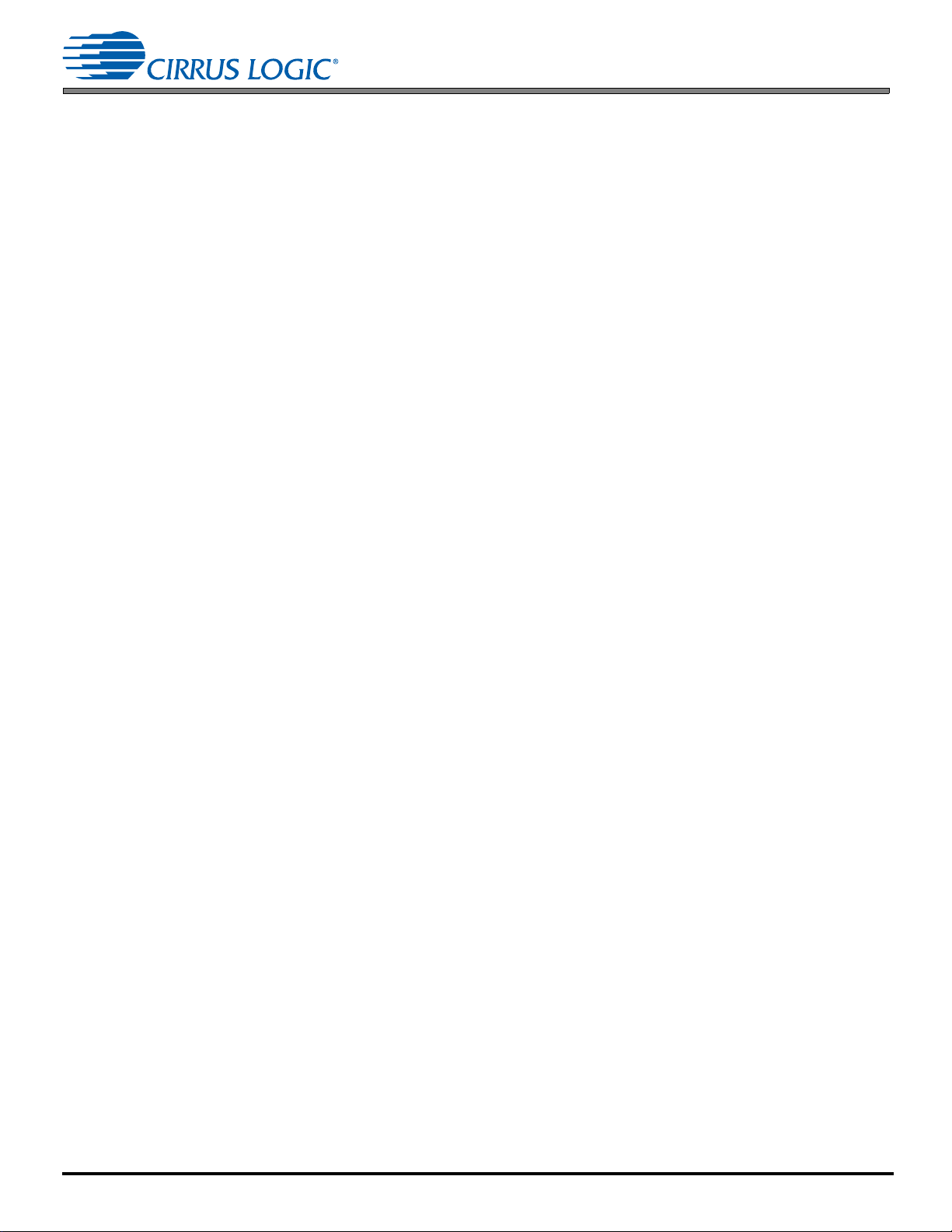

Test Conditions (unless otherwise specified): TA = 0–+70°C; VDD = 1.8V±5%, VDDA (VA) = 3.3V±5%, 1kHz sine wave

driven through the passive input filter (R

Bandwidth is 10–20kHz.

Fs = 96 kHz

Dynamic Range

A-weighted

Unweighted

40 kHz bandwidth unweighted

Total Harmonic Distortion + Noise

–1 dB

–20 dB

–60 dB

40 kHz bandwidth –1 dB

AIN_1A/B Interchannel Isolation

AID_[2.6]A/B MUX Interchannel Isolation — 95 — — 95 — dB

DC Accuracy

Interchannel Gain Mismatch — 0.1 — — 0.1 — dB

Gain Drift —

Analog Input

Full-scale Input Voltage

Differential Input Impedance

Single-ended Input Impedance

Common Mode Rejection Ratio (CMRR)8—60 —— — — dB

Parasitic Load Capacitance (C

1. dB units referred to the typical full-scale voltage.

2. These full-scale values were measured with R

3. The full-scale voltage can be changed by scaling R

Differential Full-Scale (Vpp) = 3.7*VDDA*(Ri+200)/(10k+200)

Single-Ended Full-Scale (Vpp) = 1.85*VDDA*(Ri+200)/(10k+200)

4. Measured between AIN_xx+ and AN_xx–.

5. Measured between AIN_xx+ and AGND.

6. Decreasing full-scale voltage by reducing R

7. Common mode input current should be kept to less than ±160uA to avoid performance degradation: |(I

=10 k in the differential case.

for R

i

8. This number was measured using perfectly matched external resistors (R

(|

R

|/Ri + 0.001).

i

represents the parasitic load capacitance between Ri on the input circuit and the input pin of the CS47048 package.

9. C

L

10. This measurement is not applicable to the CS47028 and CS47024 devices.

= 10 k) in Fig. 5-13 or Fig. 5-14; DSP running test application; Measurement

i

Differential Single-ended

Parameter Min Typ Max Min Typ Max Unit

1,6,7

99

105

—

96

96

102

102

—

—

99

6,7

—

–98

—

–82

—

–42

—

–90

10

—95 —— 95 — dB

—

–92

—

—

—

93

—

—

—

—

—

–95

–79

–39

–90

99

96

—

—

—

–89

—

—

—

dB

dB

dB

dB

dB

dB

dB

±120 —— ±120 — ppm/°C

2,3

4

5

9

)

L

=10k for both the single-ended and differential mode input circuits.

i

.

i

causes the noise floor to increase.

i

3.3 3.7•VA 3.9 1.65 1.85•VA 1.95 V

PP

— 400 — — — —

— — — — 200 —

— — 20 — — 20 pF

)/2| < 160uA. This corresponds to ±1.6V

ip+Iin

). Mismatch in the external resistors typically reduces CMRR by 20 log

i

21 DS787PP9

Page 22

10µF

C

L

R

i

AIN

100K

AIN_xA+

AIN_xB+

or

+

5.16 ADC Characteristics

5.16.2 Analog Input Characteristics (Automotive)

Test Conditions (unless otherwise specified): TA = –40–85°C; VDD = 1.8V±5%, VDDA (VA) = 3.3V±5%; kHz sine wave

driven through the passive input filter (R

Bandwidth is 10 Hz–20 kHz.

Fs = 96 kHz

Dynamic Range

A-weighted

Unweighted

40 kHz bandwidth unweighted

Total Harmonic Distortion + Noise

–1 dB

–20 dB

–60 dB

40 kHz bandwidth –1 dB

AIN_1A/B Interchannel Isolation

AID_[2.6]A/B MUX Interchannel Isolation — 95 — — 95 — dB

DC Accuracy

Interchannel Gain Mismatch — 0.1 — — 0.1 — dB

Gain Drift — ±120 — —

Analog Input

Full-scale Input Voltage

Differential Input Impedance

Single-ended Input Impedance

Common Mode Rejection Ratio (CMRR)8—60 —— — — dB

Parasitic Load Capacitance (C

1. dB units referred to the typical full-scale voltage.

2. These full-scale values were measured with R

3. The full-scale voltage can be changed by scaling R

Differential Full-Scale (Vpp) = 3.7*VDDA*(Ri+200)/(10k+200)

Single-Ended Full-Scale (Vpp) = 1.85*VDDA*(Ri+200)/(10k+200)

4. Measured between AIN_xx+ and AN_xx–.

5. Measured between AIN_xx+ and AGND.

6. Decreasing full-scale voltage by reducing R

7. Common mode input current should be kept to less than ±160uA to avoid performance degradation: |(I

=10 k in the differential case.

for R

i

8. This number was measured using perfectly matched external resistors (R

(|

R

|/Ri + 0.001).

i

represents the parasitic load capacitance between Ri on the input circuit and the input pin of the CS47048 package.

9. C

L

10. This measurement is not applicable to the CS47028 and CS47024 devices.

= 10 k) in Fig. 5-13 or Fig. 5-14; DSP running test application; Measurement

i

Differential Single-ended

Parameter Min Typ Max Min Typ Max Unit

1,6,7

97

105

—

94

94

102

102

—

—

99

6,7

—

–98

—

–82

—

–42

—

–90

10

—95 —— 95 — dB

—

–90

—

—

—

91

—

—

—

—

—

–95

–79

–39

–90

99

96

—

—

—

–87

—

—

—

dB

dB

dB

dB

dB

dB

dB

±120 — ppm/°C

2,3

4

5

9

)

L

=10k for both the single-ended and differential mode input circuits.

i

.

i

causes the noise floor to increase.

i

3.3 3.7•VA 3.9 1.65 1.85•VA 1.95 V

PP

— 400 — — — —

— — — — 200 —

— — 20 — — 20 pF

)/2| < 160uA. This corresponds to ±1.6V

ip+Iin

). Mismatch in the external resistors typically reduces CMRR by 20 log

i

Figure 5-13. ADC Single-ended Input Test Circuit

DS787PP9 22

Page 23

Figure 5-14. ADC Differential Input Test Circuit

10µF

C

L

R

i

AIN+

100K

10µF

C

L

R

i

AIN-

100K

AIN_xA-

AIN_xB-

or

AIN_xA+

AIN_xB+

or

+

+

5.16.3 ADC Digital Filter Characteristics

5.17 DAC Characteristics

Parameter

1,2

Min Typ Max Unit

Fs = 96 kHz

Passband (Frequency Response) to –0.1 dB corner 0 — 0.4896 Fs

Passband Ripple — — 0.08 dB

Stopband 0.5688 — — Fs

Stopband Attenuation 70 — — dB

Total Group Delay — 12/Fs — s

High-pass Filter Characteristics

Frequency Response:

–3.0 dB

–0.13 dB

—

—

20

1

——Hz

Hz

Phase Deviation @ 20 Hz — 10 — Deg

Passband Ripple — — 0 dB

Filter Settling Time — 10

1. Filter response is guaranteed by design.

2. Response is clock-dependent and scales with Fs.

5

/Fs 0 s

5.17 DAC Characteristics

5.17.1 Analog Output Characteristics (Commercial)

Test Conditions (unless otherwise specified): TA = 0–+70°C; VDD = 1.8V±5%, VDDA(VA) = 3.3V±5%; 1 kHz sine wave

driven through a filter shown in Fig. 5-15 or Fig. 5-16; DSP running test application; Measurement Bandwidth is 20 Hz–20

kHz.

Differential Single-ended

Parameter Min Typ Max Min Typ Max Unit

23 DS787PP9

Fs = 96 kHz

Dynamic Range

A-weighted

Unweighted

Total Harmonic Distortion + Noise

0 dB

–20 dB

–60 dB

Interchannel Isolation (1 kHz) — 95 — — 95 — dB

10299108

105——9996

—

–98

—

–88

—

–48

–90

—

—

105

102——dBdB

—

–95

—

–85

—

–45

–87

—

—

dB

dB

dB

Page 24

AOUT_x+

3.3 µF

C

L

R

L

AOUT

2200 pF

560

10 k

+

5.17 DAC Characteristics

Differential Single-ended

Parameter Min Typ Max Min Typ Max Unit

Analog Input

Full-scale Output 1.20 1.40

Interchannel Gain Mismatch — 0.1 — — 0.1 — dB

Gain Drift —

Output Impedance — 100 — — 100 —

DC Current Draw from an AOUT Pin1——10——10A

AC-load Resistance (R

Load Capacitance (CL)

2

)

L

2

3——3——k

— — 100 — — 100 pF

•VA 1.60 0.60 0.70•VA 0.80 V

PP

±120 — — ±120 — ppm/°C

5.17.2 Analog Output Characteristics (Automotive)

Test Conditions (unless otherwise specified): TA= –40 to +85C; VDD = 1.8V±5%, VDDA(VA) = 3.3V±5%; 1 kHz sine

wave driven through a filter shown in Fig. 5-15 or Fig. 5-16; DSP running test application; Measurement Bandwidth is

20 Hz–20 kHz.

Differential Single-ended

Parameter Min Typ Max Min Typ Max Unit

Fs = 96 kHz

Dynamic Range

A-weighted

Unweighted

Total Harmonic Distortion + Noise

0 dB

–20 dB

–60 dB

Interchannel Isolation (1 kHz) — 95 — — 95 — dB

Analog Input

Full-scale Output 1.20 1.40

Interchannel Gain Mismatch — 0.1 — — 0.1 — dB

Gain Drift —

Output Impedance — 100 — — 100 —

DC Current Draw from an AOUT Pin1——10——10A

AC-load Resistance (R

Load Capacitance (CL)

1. Guaranteed by design. The DC current draw represents the allowed current draw from the AOUT pin due to typical leakage through the electrolytic

DC-blocking capacitors.

2. Guaranteed by design. R

stability and signal integrity. In this circuit topology, C

parasitic), and effectively moves the dominant pole of the two-pole amp in the output stage. Increasing this value beyond the recommended 100 pF

can cause the internal op-amp to become unstable.

and CL reflect the recommended minimum resistance and maximum capacitance required for the internal op-amp’s

L

2

)

L

2

represents any capacitive loading that appears before the 560 series resistor (typically

L

10097108

105——9794

—

–98

—

–88

—

–48

–90

—

—

105

102——dBdB

—

–95

—

–85

—

–45

–87

—

—

•VA 1.60 0.60 0.70•VA 0.80 V

±120 — — ±120 — ppm/°C

3——3——k

— — 100 — — 100 pF

dB

dB

dB

PP

DS787PP9 24

Figure 5-15. DAC Single-ended Output Test Circuit

Page 25

N output: RL = 4.87k + ( [2F*1800pF]

-1

|| ((2.43k + [2F*470pF]-1 ) || 4.87k ))

AOUT

AOUT_x+

AOUT_x-

1.96 k

C

L

4700 pF 1200 pF

1.96k

22 µF

+

953

4.87 k 2.43 k

-

+

560

+

1800 pF

470 pF

4.87 k

22 µF

P output: R

L

= 1.96k + ( [2F*4700pF]

-1

|| (1.96k + [2F*22µF- ]-1 ) || (953 + [2F*1200pF ]-1 ))

C

L

10 k

100

50

75

25

2.5

51015

Safe Operating

Region

Capacitive Load -- C (pF)

L

Resistive Load -- R (k)

L

125

3

20

Figure 5-16. DAC Differential Output Test Circuit

5.17 DAC Characteristics

Figure 5-17. Maximum Loading

5.17.3 Combined DAC Interpolation and On-chip Analog Filter Response

Passband (Frequency Response)

25 DS787PP9

to 0.22 dB corner

to –3 dB corner

Frequency Response 10 Hz–20 kHz –0.02 — +0.02 dB

StopBand 0.5465 — — Fs

StopBand Attenuation 100 — — dB

Group Delay — 10/Fs — s

Parameter Min Typ Max Unit

0

0

——0.4125

0.4979FsFs

Page 26

6 Ordering Information

The CS470xx DSP part numbers are described as follows:

Example:

CS47048I-XYZR

where

I–ROM ID Letter

X–Product Grade

Y–Package Type

Z–Lead (Pb) Free

R–Tape and Reel Packaging

Table 6-1. Ordering Information

Part No. Grade Temp. Range Package

CS47048C-CQZ Commercial 0–+70°C 100-pin LQFP

CS47048C-DQZ Automotive –40–+85°C

CS47048C-EQZ Extended Automotive –40–+105°C

CS47028C-CQZ Commercial 0–+70°C

CS47028C-DQZ Automotive –40–+85°C

CS47028C-EQZ Extended Automotive –40–+105°C

CS47024C-CQZ Commercial 0–+70°C

CS47024C-DQZ Automotive –40–+85°C

CS47024C-EQZ Extended Automotive –40–+105°C

Note: Contact the factory for availability of the –D (automotive grade) package.

6 Ordering Information

7 Environmental, Manufacturing, and Handling Information

Table 7-1. Environmental, Manufacturing, and Handling Information

Model Number Peak Reflow Temp.

CS47048C-CQZ 260° C 3 7 days

CS47048C-DQZ

CS47048C-EQZ

CS47028C-CQZ 260° C 3 7 days

CS47028C-DQZ

CS47028C-EQZ

CS47024C-CQZ 260° C 3 7 days

CS47024C-DQZ

CS47024C-EQZ

1. Moisture Sensitivity Level as specified by IPC/JEDEC J-STD-020.

MSL

1

Rating

Max Floor Life

26 DS787PP9

Page 27

8 Device Pinout Diagrams

VDD1

GND2

VDDIO1

GNDIO1

VDD2

GND1

GPIO1, DAI_DATA2, TM2

GPIO2, DAI_DATA3, TM3, SPDIF RX

GPIO16, DAI_DATA0, TM0

GPIO0, DAI_DATA1, TM1

10

15

20

25

GPIO5, DAO_DATA3, HS3, S/PDIF TXa

GPIO3, DAO_DATA1, HS1

GPIO6, DAO_DATA0, HS0

GPIO7, DAO_LRCLK

GPIO15, DAI_LRCLK

GPIO18, DAO_MCLK, HS4

GPIO17, DAI_SCLK

GPIO14, DAO_SCLK

GPIO4, DAO_DATA2, HS2, S/PDIF TXb

VDDIO2

GNDIO2

DBDA

DBCK

CS47048

100-Pin LQFP

(Thermal Pad Package )

5

1

GPIO10, SCP_MISO, SCP_SDA

GPIO9, SCP_MOSI

GPIO8, SCP_CS, DAI_DATA4

GPIO12, SCP_IRQ

GPIO13, SCP_BSY, EE_CS

GNDIO3

GND_SUB

XTAL_OUT, TEST

GND3

XTI

XTO

GNDA_PLL

PLL_REF_RES

AIN_6B-

AIN_6B+

AIN_5B-

AIN_5B+

26

GPIO11, SCP_CLK

30

VDDIO3

35VDD3

40

VDDA_PLL

45

AIN_4B-

AIN_4B+

AIN_3B-

AIN_3B+

AIN_2B-

50AIN_2B+

70

65

60

55

51

75

AIN_1B-

AIN_5A-

VQ

BIASREF_DAC

AIN_5A+

VDDA3

AIN_1A-

AIN_1B+

GNDA3

AIN_1A+

AIN_4A-

AIN_3A-

AIN_3A+

BIASREF_ADC

VDD_ADC_MON

AIN_2A-

REXT

VDDA2

AIN_4A+

AIN_2A+

GNDA2

GND_DAC

VDD_DAC

AIN_6A-

AIN_6A+

95

90

85

100

80

76

AOUT_1+

AOUT_1-

VDDA7

AOUT_2+

AOUT_2-

AOUT_3+

AOUT_3-

GNDA 6

AOUT_4+

AOUT_4-

AOUT_5+

VDDA5

GNDA 5

AOUT_6+

AOUT_6-

RESET

GNDA 7

VDDA6

AOUT_5-

AOUT_7+

AOUT_7-

VDDA4

GNDA 4

AOUT_8+

AOUT_8-

8.1 CS47048, 100-pin LQFP Pinout Diagram

8 Device Pinout Diagrams

27 DS787PP9

Figure 8-1. CS47048 Pinout Diagram

Page 28

8.2 CS47028, 100-pin LQFP Pinout Diagram

VDD1

GND2

VDDIO1

GNDIO1

VDD2

GND1

GPIO1, DAI_DATA2, TM2

GPIO2, DAI_DATA3, TM3, SPDIF RX

GPIO16, DAI_DATA0, TM0

GPIO0, DAI_DATA1, TM1

10

15

20

25

GPIO5, DAO_DATA3, HS3, S/PDIF TXa

GPIO3, DAO_DATA1, HS1

GPIO6, DAO_DATA0, HS0

GPIO7, DAO_LRCLK

GPIO15, DAI_LRCLK

GPIO18, DAO_MCLK, HS4

GPIO17, DAI_SCLK

GPIO14, DAO_SCLK

GPIO4, DAO_DATA2, HS2, S/PDIF TXb

VDDIO2

GNDIO2

DBDA

DBCK

CS47028

100-Pin LQFP

(Thermal Pad Package )

5

1

GPIO10, SCP_MISO, SCP_SDA

GPIO9, SCP_MOSI

GPIO8, SCP_CS, DAI_DATA4

GPIO12, SCP_IRQ

GPIO13, SCP_BSY, EE_CS

GNDIO3

GND_SUB

XTAL_OUT, TEST

GND3

XTI

XTO

GNDA_PLL

PLL_REF_RES

AIN_6B-

AIN_6B+

AIN_5B-

AIN_5B+

26

GPIO11, SCP_CLK

30

VDDIO3

35VDD3

40

VDDA_PLL

45

AIN_4B-

AIN_4B+

AIN_3B-

AIN_3B+

AIN_2B-

50AIN_2B+

70

65

60

55

51

75

NC

AIN_5A-

VQ

BIASREF_DAC

AIN_5A+

VDDA3

NC

NC

GNDA3

NC

AIN_4A-

AIN_3A-

AIN_3A+

BIASREF_ADC

VDD_ADC_MON

AIN_2A-

REXT

VDDA2

AIN_4A+

AIN_2A+

GNDA2

GND_DAC

VDD_DAC

AIN_6A-

AIN_6A+

95

90

85

100

80

76

AOUT_1+

AOUT_1-

VDDA7

AOUT_2+

AOUT_2-

AOUT_3+

AOUT_3-

GNDA 6

AOUT_4+

AOUT_4-

AOUT_5+

VDDA5

GNDA 5

AOUT_6+

AOUT_6-

RESET

GNDA 7

VDDA6

AOUT_5-

AOUT_7+

AOUT_7-

VDDA4

GNDA 4

AOUT_8+

AOUT_8-

8.2 CS47028, 100-pin LQFP Pinout Diagram

28 DS787PP9

Figure 8-2. CS47028 Pinout Diagram

Page 29

8.3 CS47024, 100-pin LQFP Pinout Diagram

VDD1

GND2

VDDIO1

GNDIO1

VDD2

GND1

GPIO1, DAI_DATA2, TM2

GPIO2, DAI_DATA3, TM3, SPDIF RX

GPIO16, DAI_DATA0, TM0

GPIO0, DAI_DATA1, TM1

10

15

20

25

GPIO5, DAO_DATA3, HS3, S/PDIF TXa

GPIO3, DAO_DATA1, HS1

GPIO6, DAO_DATA0, HS0

GPIO7, DAO_LRCLK

GPIO15, DAI_LRCLK

GPIO18, DAO_MCLK, HS4

GPIO17, DAI_SCLK

GPIO14, DAO_SCLK

GPIO4, DAO_DATA2, HS2, S/PDIF TXb

VDDIO2

GNDIO2

DBDA

DBCK

CS47024

100-Pin LQFP

(Thermal Pad Package )

5

1

GPIO10, SCP_MISO, SCP_SDA

GPIO9, SCP_MOSI

GPIO8, SCP_CS, DAI_DATA4

GPIO12, SCP_IRQ

GPIO13, SCP_BSY, EE_CS

GNDIO3

GND_SUB

XTAL_OUT, TEST

GND3

XTI

XTO

GNDA_PLL

PLL_REF_RES

AIN_6B-

AIN_6B+

AIN_5B-

AIN_5B+

26

GPIO11, SCP_CLK

30

VDDIO3

35VDD3

40

VDDA_PLL

45

AIN_4B-

AIN_4B+

AIN_3B-

AIN_3B+

AIN_2B-

50AIN_2B+

70

65

60

55

51

75

NC

AIN_5A-

VQ

BIASREF_DAC

AIN_5A+

VDDA3

NC

NC

GNDA3

NC

AIN_4A-

AIN_3A-

AIN_3A+

BIASREF_ADC

VDD_ADC_MON

AIN_2A-

REXT

VDDA2

AIN_4A+

AIN_2A+

GNDA2

GND_DAC

VDD_DAC

AIN_6A-

AIN_6A+

95

90

85

100

80

76

AOUT_1+

AOUT_1-

VDDA7

AOUT_2+

AOUT_2-

AOUT_3+

AOUT_3-

GNDA 6

AOUT_4+

AOUT_4-

NC

VDDA5

GNDA 5

NC

NC

RESET

GNDA 7

VDDA6

NC

NCNCVDDA4

GNDA 4

NC

NC

8.3 CS47024, 100-pin LQFP Pinout Diagram

29 DS787PP9

Figure 8-3. CS47024 Pinout Diagram

Page 30

DS787PP9 30

9 100-pin LQFP with Exposed Pad Package Drawing

Fig. 9-1 shows the 100-pin LQFP package with exposed pad for the CS47048, CS47028, and CS47024.

Figure 9-1. 100-pin LQFP Package Drawing

Page 31

10 Parameter Definitions

10Parameter Definitions

10.1 Dynamic Range

The ratio of the RMS value of the signal to the RMS sum of all other spectral components over the specified bandwidth.

Dynamic Range is a signal-to-noise ratio measurement over the specified bandwidth made with a -60 dBFS signal. 60 dB

is added to resulting measurement to refer the measurement to full-scale. This technique ensures that the distortion

components are below the noise level and do not affect the measurement. This measurement technique has been

accepted by the Audio Engineering Society, AES17-1991, and the Electronic Industries Association of Japan, EIAJ

CP-307. Expressed in decibels.

10.2 Total Harmonic Distortion + Noise

The ratio of the RMS value of the signal to the RMS sum of all other spectral components over the specified bandwidth

(typically 10 Hz–20 kHz), including distortion components. Expressed in decibels. Measured at –1 and –20 dBFS as

suggested in AES17-1991 Annex A.

10.3 Frequency Response

A measure of the amplitude response variation from 10 Hz–20 kHz relative to the amplitude response at 1 kHz. Units in

decibels.

10.4 Interchannel Isolation

A measure of crosstalk between the left and right channels. Measured for each channel at the converter’s output with no

signal to the input under test and a full-scale signal applied to the other channel. Units in decibels.

10.5 Interchannel Gain Mismatch

The gain difference between left and right channels. Units in decibels.

10.6 Gain Error

The deviation from the nominal full-scale analog output for a full-scale digital input.

10.7 Gain Drift

The change in gain value with temperature. Units in ppm/°C.

31 DS787PP9

Page 32

11 Revision History

11Revision History

Revision Date Changes

PP1 August, 2009 Updated Characterization data in Section 5.4, Section 5.7, Section 5.9, Section 5.11, Section 5.12,

PP2 January, 2010 Updated TDM Feature description on page 1. Modified note at the bottom of the feature list on page 1.

PP3 June, 2010 Ta b le 3 -1 : Straddled all three columns in the “Supports Different Fs Sample Rates” row to indicate that

PP4 February, 2011 Added “Decoder” information to Section 3. Changed the name of the core to “Cirrus Logic 32-bit core”.

PP5 February, 2011 Added “SPDIF RX” to Fig. 5-17.

PP6 June, 2011 In Section 4.3.1 and Section 4.3.7, removed mention of 192 kHz sampling frequency. Updated temperature

PP7 April, 2012 Corrected peak reflow temperature in Ta bl e 7- 1 .

PP8 June, 2012 Added number of bits to Integrated DAC and ADC Functionality on the cover page.

PP9 July, 2012 Updated frequencies in Section 5.2. Added extended automotive grade information to Section 6 and

Section 5.16.1, Section 5.16.2, Section 5.16.3, Section 5.17.1, and Section 5.17.2. Modified Footnote 3 in

both Section 5.16.1 and Section 5.16.2. Added Footnote 5 to Section 5.14. Updated Section 2.1. Modified

Section 4.3.6 and Section 4.3.8. Modified references to TDM in various sections of the data sheet.

Updated table in Section 5.8, specifying performance data for 2- and 4-layer boards. Updated Tab l e 3 -1 and

Ta bl e 3 - 2 Updated block diagrams in Fig. 4-1, Fig. 4-2, and Fig. 4-3.

CS47024 devices have the same features as the CS47048 and CS47028.

Added “The CS47024 has the 8-channel SRC block” to Section 4.3.7.

Added text in the following places to indicate that the CS47024 implements the S/PDIF Rx functionality:

• Removed dagger from the S/PDIF Rx bullet on p. 1.

• Updated bullet in “Configurable Serial Audio Inputs/Outputs” row in Table 2 Integrated 192 kHz S/PDIF

Rx, 2 Integrated 192 kHz S/PDIF Tx.

• Changed entry in “S/PDIF In (Stereo Pairs)” column in Tab l e 3 -2 .

• Updated I2S block in Table 3-2.

• Removed text “On the CS47048 and CS47028...” from Section 4.3.4.

• Removed “(Not available on CS47024)” from the heading to Section 5.15.

• Described additional support for TDM 8-channel output mode on CS47024.

• Removed dagger from the TDM I/O bullet on p. 1.

• Straddled “Configurable Serial Audio Inputs/Outputs” row in Tab le 3- 1 .

• Changed cell in “TDM Out” column in Table 3-2.

• Removed text “On the CS47048 and CS47028...” from Section 4.3.5.

operating conditions in Section 5.2. Updated pin 33 to XTAL_OUT, TEST in Fig. 8-1, Fig. 8-2, and Fig. 8-3.

Section 7.

DS787PP9 32

Loading...

Loading...