Page 1

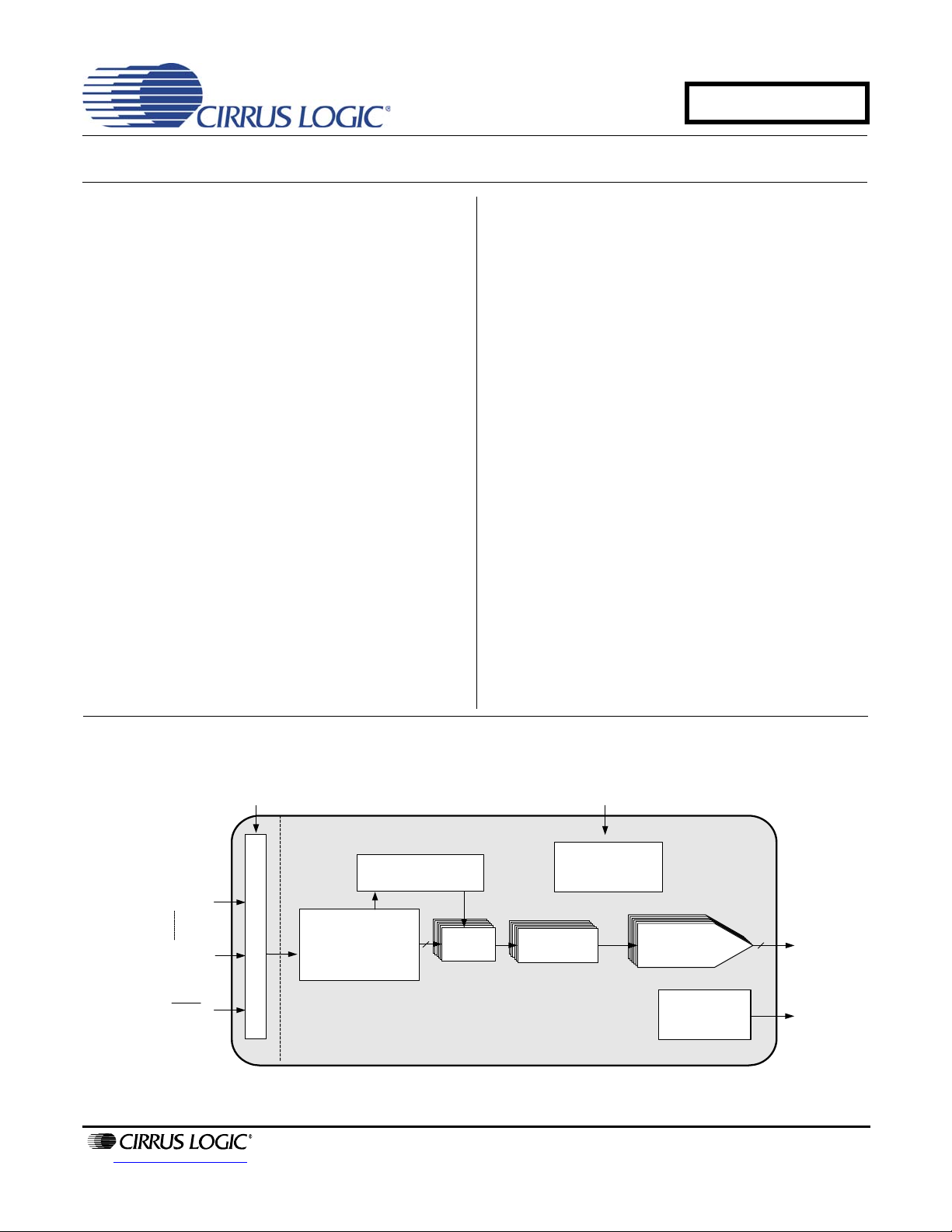

Internal Voltage

Reference

Auto-Speed

Detecting PCM

Serial Interface

Level Translator

Mode Control

Analog & Digital Core

Supply (5 V)

Single-Ended

Outputs

(Six Channels

6

PCM Serial

Audio Input

Digital

Filters

Switch-Cap

DAC and

Analog Filters

Multi-bit

Modulators

External Mu te

Control

Mute Control

Serial Audio Port & Control

Supply (1.8 V to 5 V)

6

Digital

De-emphasis

Confidential Draft

9/30/11

CS4361

20-Pin, 24-Bit, 192 kHz, 6-Channel D/A Converter

Features

Multi-Bit Delta-Sigma Modulator

24-Bit Conversion

Automatically Detects Sample Rates Up To

192 kHz

103 dB Dynamic Range

-94 dB THD+N

Low Clock-Jitter Sensitivity

+5 V Core Power

+1.8 V to +5 V Interface Power

Filtered Line-Level Outputs

On-Chip Digital De-emphasis

Popguard

Mute Output Control

Small 20-pin TSSOP Package

®

Technology

Description

The CS4361 is a complete 6-channel digital-to-analog

output system including interpolation, multi-bit D/A conversion, and output analog filtering in a small 20-pin

package. The CS4361 supports all major audio data interface formats.

The CS4361 is based on a fourth-order, multi-bit, deltasigma modulator with a linear analog low-pass filter.

This device also includes auto-speed mode detection

using both sample rate and master clock ratio as a

method of auto-selecting sampling rates between 2 kHz

and 216 kHz.

The CS4361 contains on-chip digital de-emphasis, operates from a single +5 V power supply with separate

built-in level shifter for the digital interface, and requires

minimal support circuitry. These features are ideal for

DVD players and recorders, digital televisions, home

theater and set-top box products, and automotive audio

systems.

The CS4361 is available in a 20-pin TSSOP Commercial grade package (-40 to 85° C). The CDB4361 is also

available for device evaluation and implementation su ggestions. Please refer to “Ordering Information” on

page 23 for complete ordering information.

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

SEPT '11

DS672F2

Page 2

Confidential Draft

TABLE OF CONTENTS

1. PIN DESCRIPTIONS .............................................................................................................................. 4

2. CHARACTERISTICS AND SPECIFICATIONS ...................................................................................... 5

RECOMMENDED OPERATING CONDITIONS .................................................................................... 5

ABSOLUTE MAXIMUM RATINGS ........................................................................................................ 5

DAC ANALOG CHARACTERISTICS - COMMERCIAL (-CZZ) ............................................................. 6

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ........................................ 7

DIGITAL INPUT CHARACTERISTICS ....................................... ... ... ... ... .... ... ... ... .... ... ... ........................8

POWER & THERMAL CHARACTERISTICS ......................................................................................... 8

SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE ...................................................... 9

3. TYPICAL CONNECTION DIAGRAM ................................................................................................... 11

4. APPLICATIONS ................................................................................................................................... 12

4.1 Master Clock .................................................................................................................................. 12

4.2 Serial Clock .................................................................................................................................... 12

4.2.1 External Serial Clock Mode ................................................................................................... 12

4.2.2 Internal Serial Clock Mode ................. ...................................................................................12

4.3 De-Emphasis ................................................................................................................................. 14

4.4 Mode Select ................................................................................................................................... 14

4.5 Initialization and Power-Down ........................................................................................................ 15

4.6 Output Transient Control ................................................................................................................ 16

4.6.1 Power-Up ................................................................. .... ...................................... ... ................ 16

4.6.2 Power-Down ................................ ... .... ... ... ....................................... ... ... .... ... ......................... 16

4.7 Grounding and Power Supply Decoupling ..................................................................................... 16

4.8 Analog Output and Filtering ........................................................................................................... 16

4.9 Mute Control .................................................................................................................................. 17

5. PERFORMANCE PLOTS ..................................................................................................................... 18

6. PARAMETER DEFINITIONS ................................................................................................................ 21

7. PACKAGE INFORMATION .................................................................................................................. 22

8. ORDERING INFORMATION ................................................................................................................ 23

9. REVISION HISTORY ............................................................................................................................ 24

9/30/11

CS4361

2

Page 3

Confidential Draft

LIST OF FIGURES

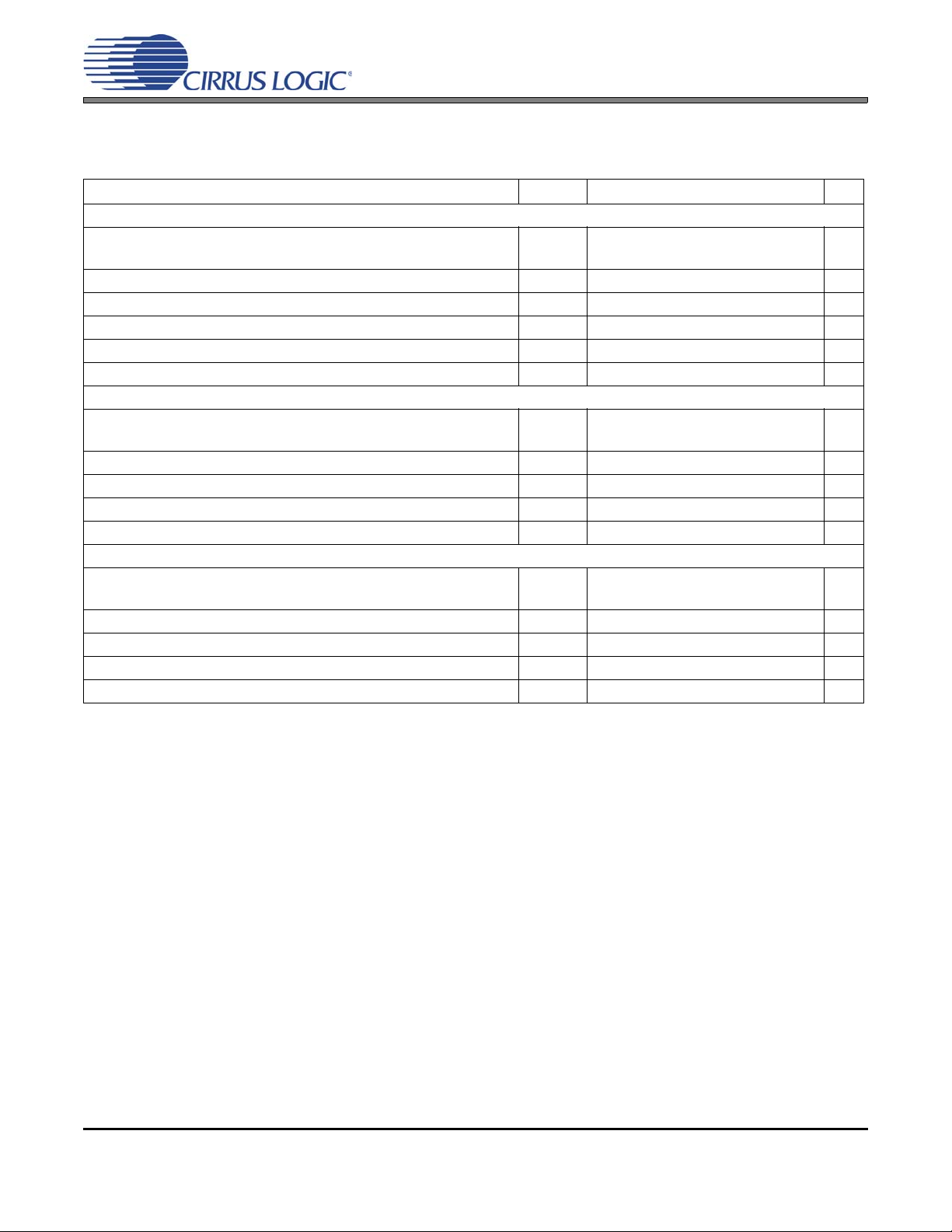

Figure 1.Equivalent Output Test Load ................................... ... .......................................... ... ... .................. 8

Figure 2.Maximum Loading .......................... ... ... .... ... ... ... .... ...................................... .... ... ... ... ..................... 8

Figure 3.External Serial Mode Input Timing .............................................................................................. 10

Figure 4.Internal Serial Mode Input Timing ............................................................................................... 10

Figure 5. Internal Serial Clock Generation ...... .......................................................................................... 10

Figure 6.Recommended Connection Diagram .......................................................................................... 11

Figure 7.CS4361 Data Format (I²S) ... .... ... ... ... ... .... ... ... .......................................... ... ................................ 13

Figure 8.CS4361 Data Format (Left-Justified) .......................................................................................... 13

Figure 9.CS4361 Data Format (Right-Justified 24) ................................... ... .... ... ... ... .... ... ... ... ... .... ... ... ...... 13

Figure 10.CS4361 Data Format (Right-Justified 16) ................................................................................. 14

Figure 11.De-Emphasis Curve (Fs = 44.1kHz) ......................................................................................... 14

Figure 12.CS4361 Initialization and Power-Down Sequence ................................................................... 15

Figure 13.Suggested Active-Low Mute Circuit .......................................................................................... 17

Figure 14.Single-Speed Stopband Rejection ............................................................................................ 18

Figure 15.Single-Speed Transition Band .................................................................................................. 18

Figure 16.Single-Speed Transition Band .................................................................................................. 18

Figure 17.Single-Speed Passband Ripple ...................... .... ... ... ... .... ... ... ... ... .... ... ... ................................... 18

Figure 18.Double-Speed Stopband Rejection .............................. .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ......... 19

Figure 19.Double-Speed Transition Band ................................................................................................. 19

Figure 20.Double-Speed Transition Band ................................................................................................. 19

Figure 21.Double-Speed Passband Ripple .................................. .......................................... ................... 19

Figure 22.Quad-Speed Stopband Rejection ............................................................................................. 20

Figure 23.Quad-Speed Transition Band ...................................... .... ... ... ... ... .... ... ... ... .... ... ... ... ................... 20

Figure 24.Quad-Speed Transition Band ...................................... .... ... ... ... ... .... ... ... ... .... ... ... ... ................... 20

Figure 25.Quad-Speed Passband Ripple ................................................................................................. 20

9/30/11

CS4361

LIST OF TABLES

Table 1. Common Clock Frequencies ....................................................................................................... 12

Table 2. Mode Pin Settings ....................................................................................................................... 14

3

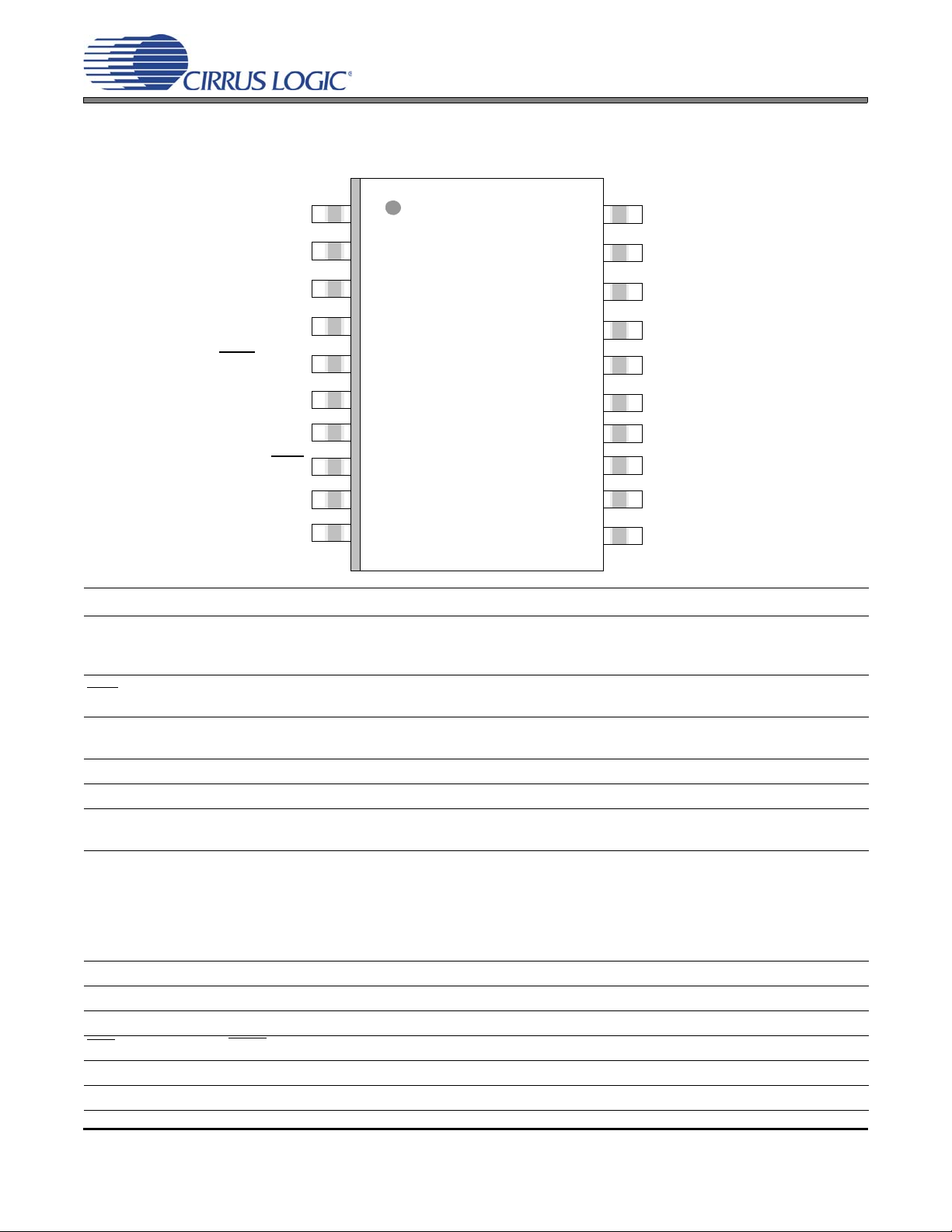

Page 4

Confidential Draft

1

2

3

4

5

16

6

7

8

15

14

13

12

11

9

10

17

18

19

20

MUTEC

VL

AOUT1

SDIN1

AOUT2

SDIN2

AOUT3

SDIN3

AOUT4

DEM

/SCLK

VA

LRCK

GND

MCLK

AOUT5

RST

AOUT6

MODE

VQ

FILT+

1. PIN DESCRIPTIONS

9/30/11

CS4361

Pin Name # Pin Description

SDIN1

SDIN2

SDIN3

DEM

/SCLK 5

LRCK 6

MCLK 7 Master Clock (Input) - Clock source for the delta-sigma modulator and digital filters.

VQ 11 Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.

FILT+ 10

AOUT1

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

GND 14 Ground (Input) - ground reference.

VA 15 Analog Power (Input) - Positive power for the analog and core digital sections.

VL 1 Interface Power (Input) - Positive power for the digital interface level shifters.

RST

MUTEC 20 Mute Control (Output) - Control signal for optional external muting circuitry.

MODE 9 Mode Control (Input) - Selects operational modes (see Table 2).

4

2

34Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

De-emphasis/External Serial Clock Input (Input) - used for de-emphasis filter control or external serial

clock input.

Left Right Clock (Input) - Determines which channel, Left or Right, is currently active on the serial

audio data line.

Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling

circuits.

19

18

17

16

13

12

Analog Output (Output) - The full scale analog output level is specified in the Analog Characteristics

specification table.

8 Reset (Input) - Applies reset to the internal circuitry when low.

Page 5

Confidential Draft

9/30/11

CS4361

2. CHARACTERISTICS AND SPECIFICATIONS

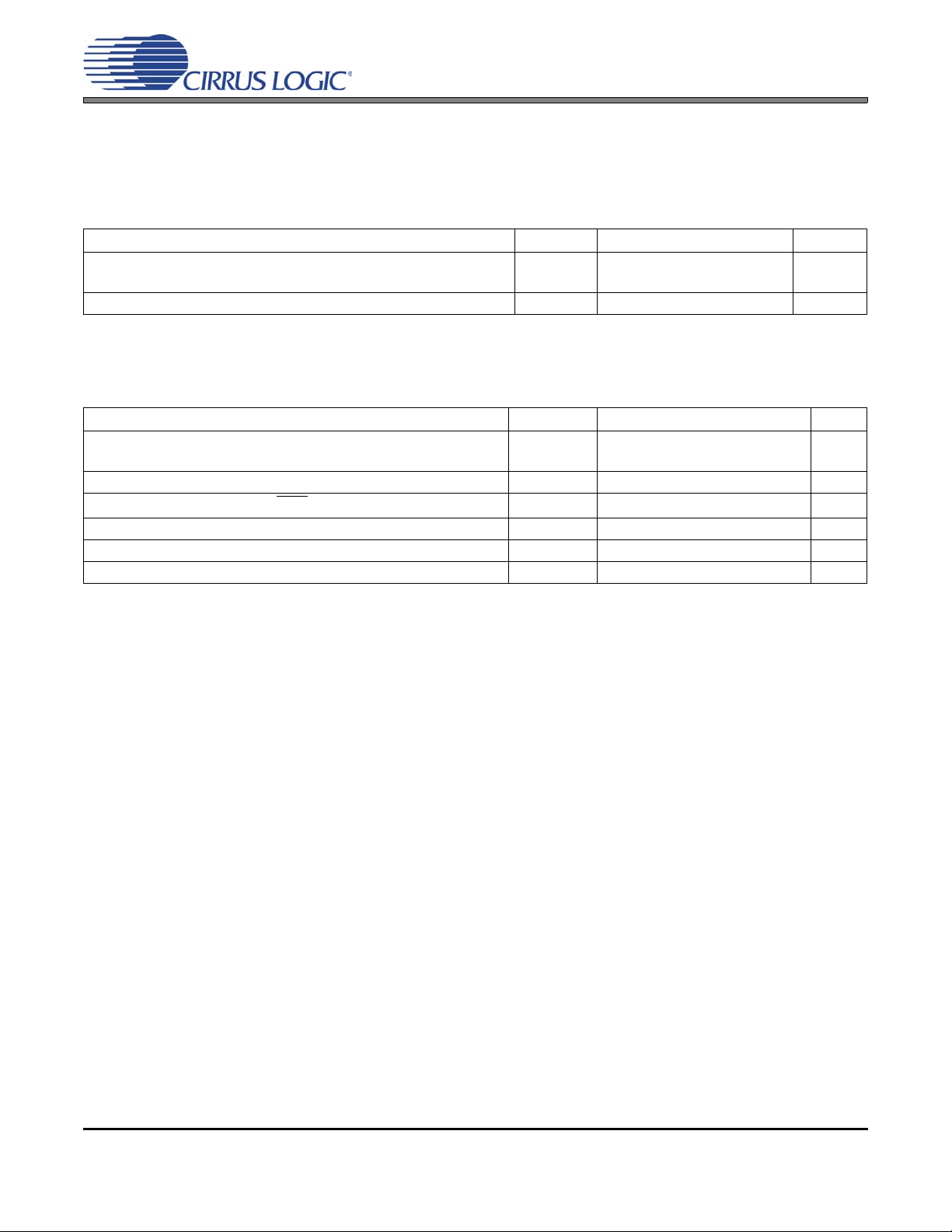

RECOMMENDED OPERATING CONDITIONS

AGND = 0 V; all voltages with respect to ground.

Parameters Symbol Min Nom Max Units

DC Power Supply

Specified Temperature Range Commercial T

VA

VL

A

4.75

1.7

-40 - +85 C

5.0

3.3

5.25

5.25

V

V

ABSOLUTE MAXIMUM RATINGS

AGND = 0 V; all voltages with respect to ground.

Parameters Symbol Min Max Units

DC Power Supply

Input Current, Any Pin Except Supplies I

Digital Input V oltage (pin 8, RST

Digital Input V oltage (all other digital pins) V

Ambient Operating Temperature (power applied) T

Storag e Temperature T

WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

)V

VA

VL

in

IND

IND

op

stg

-0.3

-0.3

-±10mA

-0.3 VA+0.4 V

-0.3 VL+0.4 V

-55 125 °C

-65 150 °C

6.0

VA

V

V

5

Page 6

Confidential Draft

9/30/11

CS4361

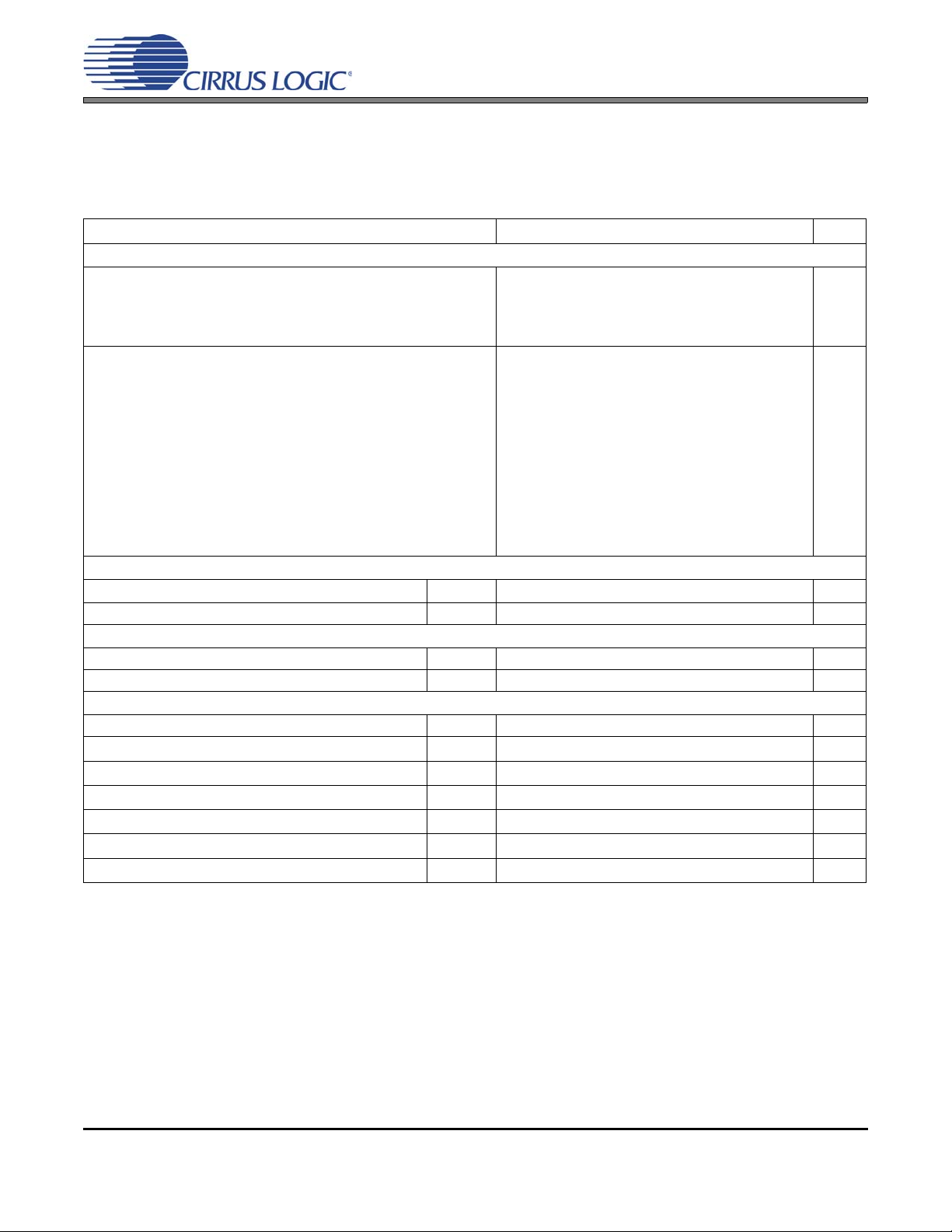

DAC ANALOG CHARACTERISTICS - COMMERCIAL

Test Conditions (unless otherwise specified). VA = 5.0 V, VL = 3.3 V, and TA = 25° C. Full-scale input sine wave.

Measurement Bandwidth is 10 Hz to 20 kHz. See (Note 1). Specifications apply to all channels unless otherwise

indicated.

Parameter Min Typ Max Unit

Dynamic Performance

Dynamic Range 18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

99

96

90

87

103

100

96

93

-

-

-

-

Total Harmonic Distortion + Noise

18 to 24-Bit Ch. 1-2, 0 dB

Ch. 3-4, 0 dB

Ch. 5-6, 0 dB

-20 dB

-60 dB

16-Bit Ch. 1-2, 0 dB

Ch. 3-4, 0 dB

Ch. 5-6, 0 dB

-20 dB

-60 dB

-

-

-

-

-

-

-

-

-

-

-93

-90

-94

-80

-40

-92

-89

-93

-73

-33

-86

-83

-87

-76

-36

-85

-82

-86

-67

-27

DAC Analog Characteristics - All Modes

Parameter Symbol Min Typ Max

Interchannel Isolation (1 kHz) - 100 - dB

DC Accuracy

Interchannel Gain Mismatch - 0.1 0.25 dB

Gain Drift - 100 - ppm/°C

Analog Output

Full Scale Output Voltage 0.60•VA 0.65•VA 0.70•VA Vpp

Quiescent Voltage V

Max DC Current draw from an AOUT pin I

Max Current draw from VQ I

Min AC-Load Resistance (see Figure 2)R

Max Load Capacitance (see Figure 2)C

Output Impedance Z

Q

OUTmax

Qmax

L

L

OUT

-0.5•VA-VDC

-10-A

- 100 - A

-3-k

- 100 - pF

- 100 -

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Notes:

6

1. One LSB of triangular PDF dither added to data.

Page 7

Confidential Draft

9/30/11

CS4361

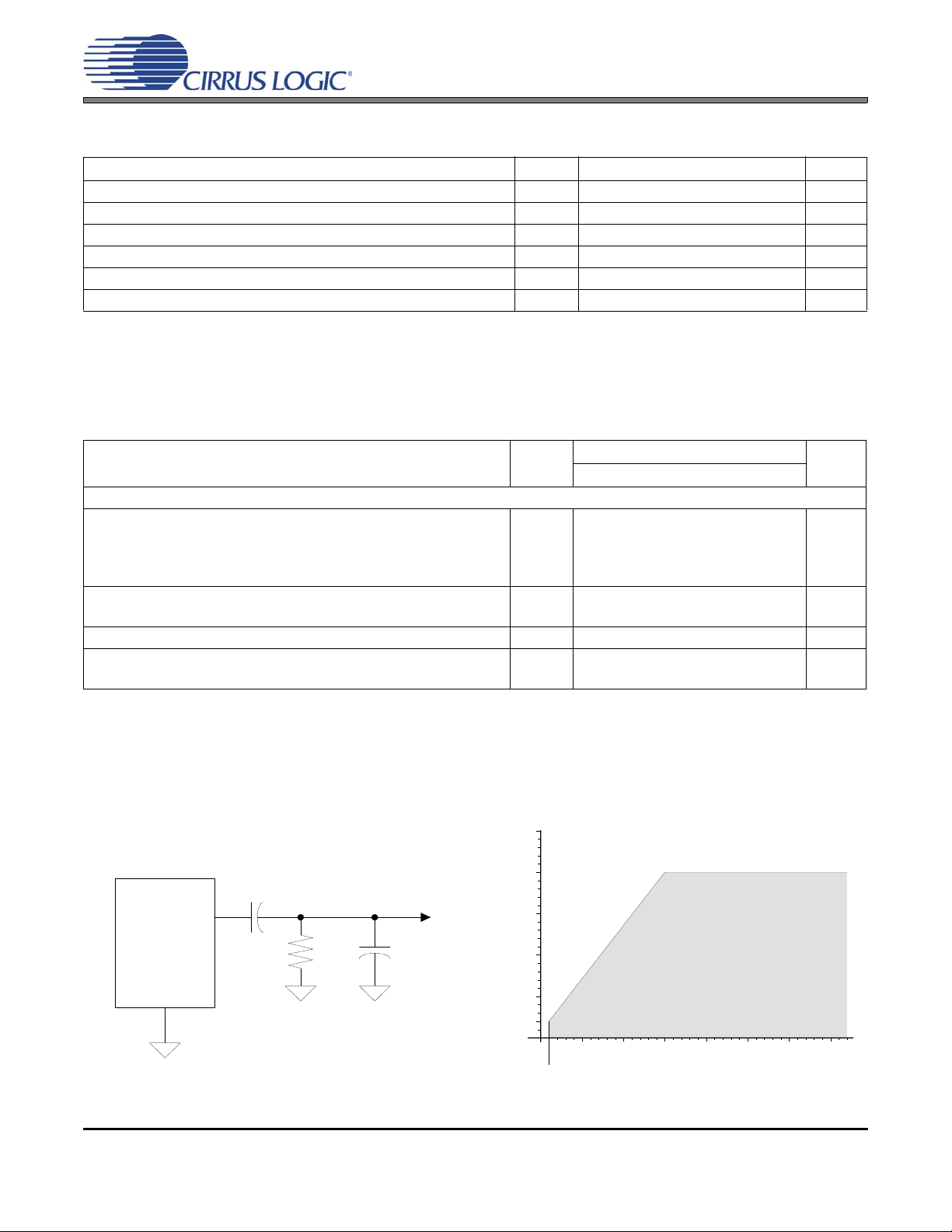

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

The filter characteristics have been norma lized to th e sample rate (Fs) and can be referenced to the desired sample rate by multiplying the given characteristic by Fs. (See Note 5)

Parameter Symbol Min Typ Max Unit

Single-Speed Mode

Passband (Note 2) to -0.05 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -.01 - +.08 dB

StopBand .5465 - - Fs

StopBand Attenuation (Note 3) 50 - - dB

Group Delay tgd - 1 0/Fs - s

De-emphasis Error (Note 4) Fs = 44.1 kHz - - +.05/-.25 dB

Double-Speed Mode

Passband (Note 2) to -0.1 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -.05 - +.2 dB

StopBand .5770 - - Fs

StopBand Attenuation (Note 3) 55 - - dB

Group Delay tgd - 5 /F s - s

Quad-Speed Mode

Passband (Note 2) to -0.1 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz 0 - +0.00004 dB

StopBand 0.7 - - Fs

StopBand Attenuation (Note 3) 51 - - dB

Group Delay tgd - 2.5/Fs - s

0

0

0

0

0

0

-

-

-

-

-

-

.4780

.4996

.4650

.4982

0.397

0.476

Fs

Fs

Fs

Fs

Fs

Fs

2. Response is clock-dependent and will scale with Fs.

3. For Single-Speed Mode, the measurement bandwidth is 0.5465 Fs to 3 Fs.

For Double-Speed Mode, the measurement bandwidth is 0.577 Fs to 1.4 Fs.

For Quad-Speed Mode, the measurement bandwidth is 0.7 Fs to 1 Fs.

4. De-emphasis is available only in Single-Speed Mode.

5. Amplitude vs. Frequency plots of this data are available in “Performance Plots” on page 18.

7

Page 8

Confidential Draft

AOUTx

AGND

3.3 µF

V

out

R

L

C

L

Figure 1. Equivalent Output Test Load Figure 2. Maximum Loading

100

50

75

25

2.5

51015

Safe Operating

Region

Capacitive Load -- C (pF)

L

Resistive Load -- R (k)

L

125

3

20

9/30/11

CS4361

DIGITAL INPUT CHARACTERISTICS

Parameters Symbol Min Typ Max Units

High-Level Input Voltage -all input Pins except RST (% of VL) V

Low-Level Input Voltage -all input Pins except RST (% of VL) V

High-Level Input Voltage -RST pin (Note 6) (% of VL) V

Low-Level Input Voltage -RST pin (% of VL) V

Input Leakage Current (Note 7) I

IH

IL

IH

IL

in

70% - - V

- - 30% V

90% - - V

- - 10% V

--±10A

Input Capacitance - 8 - pF

6. RST pin has an input threshold relative to VL, but is VA tolerant.

7. I

for LRCK is ±20 A max.

in

POWER & THERMAL CHARACTERISTICS

Parameters Symbol

Power Supplies

Power Supply Current normal operation

(Note 8)

power-down state (Note 9)

Power Dissipation normal operation

power-down state (Note 9)

Package Thermal Resistance

Power Supply Rejection Ratio (Note 10) (1 kHz)

(60 Hz)

8. Current consumption increases with increasing FS and increasing MCLK. Typ and Max values are

based on highest FS and highest MCLK. Current variance betwee n speed modes is small.

9. Power-Down Mode is defined when all clock and data lines are held static.

10. Valid with the recommended capacitor values on VQ and FILT+

agram in Section 4.

Min Typ Max

I

A

I

L

I

A

I

L

JA

PSRR -

-

-

-

-

-

-

-72-°C/Watt

-

as shown in the typical connection di-

5V Nom

66

0.1

300

26

331

1.63

60

40

90

1

-

-

455

-

-

-

Units

mW

mW

mA

mA

A

A

dB

dB

8

Page 9

Confidential Draft

10

9

SCLK

----------------

tsclkw

2

----------------- -

10

9

512Fs

--------------------- -10+

10

9

512Fs

--------------------- -15+

10

9

384Fs

--------------------- -15+

9/30/11

CS4361

SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE

Parameters Symbol Min Typ Max Units

MCLK Frequency 0.512 - 50 MHz

MCLK Duty Cycle 45 - 55 %

Input Sample Rate All MCLK/LRCK ratios combined

(Note 11) 256x, 384x, 1024x

256x, 384x

512x, 768x

1152x

128x, 192x

64x, 96x

128x, 192x

Fs 2

2

84

42

30

50

100

168

216

54

134

67

34

108

216

216

External SCLK Mode

LRCK Duty Cycle (External SCLK only) 45 50 55 %

SCLK Pulse Width Low t

SCLK Pulse Width High t

sclkl

sclkh

20 - - ns

20 - - ns

SCLK Duty Cycle 45 50 55 %

SCLK rising to LRCK edge delay t

SCLK rising to LRCK edge setup time t

SDIN valid to SCLK rising setup time t

SCLK rising to SDIN hold time t

slrd

slrs

sdlrs

sdh

20 - - ns

20 - - ns

20 - - ns

20 - - ns

Internal SCLK Mode

LRCK Duty Cycle (Internal SCLK only) (Note 12) -50-%

SCLK Period (Note 13)

t

sclkw

--ns

kHz

kHz

kHz

kHz

kHz

kHz

kHz

kHz

SCLK rising to LRCK edge

SDIN valid to SCLK rising setup time

SCLK rising to SDIN hold time

MCLK / LRCK =1152, 1024, 512, 256, 128, or 64

SCLK rising to SDIN hold time

MCLK / LRCK = 768, 384, 192, or 96

11. Not all sample rates are supported for all clock ratios. See table “Common Clock Frequencies” on

page 12 for supported ratios and frequencies.

12. In Internal SCLK Mode, the duty cycle must be 50%

13. The SCLK / LRCK ratio may be either 32, 48, 64, or 72. This ratio depends on data format and

MCLK/LRCK ratio. (See Figures 7-10)

t

sclkr

t

sdlrs

t

sdh

t

sdh

--s

--ns

--ns

--ns

±1/2 MCLK period.

9

Page 10

Confidential Draft

sclkh

t

slrs

t

slrd

t

sdlrs

t

sdh

t

sclkl

t

SDATA

SCLK

LRCK

Figure 3. External Serial Mode Input Timing

SDATA

*INTERNAL SCLK

LRCK

sclkw

t

sdlrstsdh

t

sclkr

t

Figure 4. Internal Serial Mode Input Timing

* The SCLK pulses shown are internal to the CS4361.

SDATA

LRCK

MCLK

*INTERNAL SCLK

1

N

2

N

Figure 5. Internal Serial Clock Generation

* The SCLK pulses shown are internal to the CS4361.

N equals MCLK divided by SCLK

9/30/11

CS4361

10

Page 11

Confidential Draft

DEM/SCLK

14

Audio

Data

Processor

External Clock

MCLK

GND

CS4361

SDIN1

LRCK

VL

AOUT1

6

2

5

7

1

0.1 µF

+

1µF

19

Audio Output

+5 V

3.3 µF

10 k

C

470

+

R +470

C=

4Fs(R 470)

R

ext

ext

ext

+

0.1 µF

33+µF

10

VQ

FILT+

11

Note*

Note* = This circuitry is intended for applications where the CS4361 connects

directly to an unbalanced output of the design. For internal routing

applications please see the DAC analog output characteristics for loading

limitations.

For best 20 kHz response

SDIN2

3

SDIN3

4

20

MUTEC

AOUT2

18

AOUT3

17

AOUT4

16

AOUT5

13

AOUT6

12

Optional

Muting

Circuit

RST

8

Controler

MODE

9

+1.8 V to + 5 V

VA

15

VL

GND

LRCK

LJ

RJ16

RJ24

I

2

S

MCLK

µF*3.3

µF*10

*Popguard ramp can be adjusted by selecting

this capacitor value to be 3.3 µF to give 250 ms

ramp time or 10 µF to give a 420 ms ramp time.

or

Figure 6. Recommended Connection Diagram

3. TYPICAL CONNECTION DIAGRAM

9/30/11

CS4361

11

Page 12

Confidential Draft

9/30/11

CS4361

4. APPLICATIONS

The CS4361 accepts data at standa rd audio sample rates including 48, 44.1 and 32 kHz in SSM, 96, 88.2 and

64 kHz in DSM, and 192, 176.4 and 128 kHz in QSM. Audio data is input via the serial data input pin (SDIN). The

Left/Right Clock (LRCK) determines which channel is currently being input on SDIN, and the optional Serial Clock

(SCLK) clocks audio data into the input data buffer.

4.1 Master Clock

MCLK/LRCK must be an integer ratio as shown in Table 1. The LRCK frequency is equal to Fs, the frequency at which words for each channel are input to the device. The MCLK-to-LRCK frequency ratio and speed

mode is detected automatically during the initialization sequence by counting the number of MCLK transitions during a single LRCK per iod and by de tecting the absolute speed of MCLK. Internal dividers are set

to generate the proper clocks. Table 1 illustrates several standard audio sample rates and the required

MCLK and LRCK frequencies . Pleas e no te the re is no required phase relationship, but MCLK, LRCK, and

SCLK must be synchronous.

MCLK (MHz)

LRCK

(kHz)

32

44.1

48

64

88.2

96

128

176.4

192

Mode

64x 96x 128x 192x 256x 384x 512x 768x 1024x 1152x

- ---8.1920 12.2880 - - 32.7680 36.8640

- ---11.2896 16.9344 22.5792 33.8680 45.1580 -

- ---12.2880 18.4320 24.5760 36.8640 49.1520 -

- - 8.1920 12.2880 - - 32.7680 49.1520 - -

- - 11.2896 16.9344 22.5792 33.8680 - - - -

- - 12.2880 18.4320 24.5760 36.8640 - - - -

8.1920 12.2880 - - 32.7680 49.1520 - - - -

1 1 .2896 16.9344 22.5792 33.8680 - - - - - -

12.2880 18.4320 24.5760 36.8640 - - - - - -

QSM DSM SSM

Table 1. Common Clock Frequencies

4.2 Serial Clock

The serial clock controls the shifting of data into the input data buffers. The CS4361 supports both external

and internal serial clock generation modes. Refer to Figures 7-10 for data formats.

4.2.1 External Serial Clock Mode

The CS4361 will enter the External Serial Clock Mode when 16 low-to-high transitions are detected on

the DEM

Clock Mode and de-emphasis filter cannot be accessed. The CS4361 will switch to Internal Serial Clock

Mode if no low-to-high transitions are detected on the DEM

LRCK. Refer to Figure 12.

/SCLK pin during any phase of the LRCK period. When this mode is enabled, the Internal Serial

4.2.2 Internal Serial Clock Mode

In the Internal Serial Clock Mo de, the serial clock is intern ally derived an d synchronou s with MCLK and

LRCK. The SCLK/LRCK frequency ratio is either 32, 48, 64, or 72 depending upon d ata format. Operation

in this mode is identical to operation with an external serial clock synchronized with LRCK. This mode allows access to the digital de-emphasis function. Refer to Figures 7 - 12 for details.

12

/SCLK pin for two consecutive frames of

Page 13

Confidential Draft

LRCK

SCLK

Left Channel

Right Channel

SDATA +3 +2 +1

LSB

+5 +4

MSB

-1 -2 -3 -4 -5

+3 +2 +1

LSB

+5 +4

MSB

-1 -2 -3 -4

Internal SCLK Mode External SCLK Mode

I²S, 16-Bit data and INT SCLK = 32 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

I²S, Up to 24-Bit data and INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

I²S, Up to 24-Bit data and INT SCLK = 72 Fs if

MCLK/LRCK = 1152

I²S, up to 24-Bit Data

Data Valid on Rising Edge of SCLK

Figure 7. CS4361 Data Format (I²S)

LRCK

SCLK

Left Channel

Right Channel

SDATA +3 +2 +1

LSB

+5 +4

MSB

-1 -2 -3 -4 -5

+3 +2 +1

LSB

+5 +4

MSB

-1 -2 -3 -4

Internal SCLK Mode External SCLK Mode

Left-Justified, up to 24-Bit Data

INT SCLK = 64 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Left-Justified, up to 24-Bit Data

Data Valid on Rising Edge of SCLK

Figure 8. CS4361 Data Format (Left-Justified)

LRCK

SCLK

Left Channel

SDATA

65432107

23 22 21 20 19 18

65432107

23 22 21 20 19 18

32 clocks

0

Right Channel

Internal SCLK Mode External SCLK Mode

Right-Justified, 24-Bit Data

INT SCLK = 64 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Right-Justified, 24-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 48 Cycles per LRCK Period

Figure 9. CS4361 Data Format (Right-Justified 24)

9/30/11

CS4361

13

Page 14

Confidential Draft

LRCK

SCLK

Left Channel

Right Channel

SDATA

6543210987

15 14 13 12 11 10

6543210987

15 14 13 12 11 10

32 clocks

Internal SCLK Mode External SCLK Mode

Right-Justified, 16-Bit Data

INT SCLK = 32 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Right-Justified, 16-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 32 Cycles per LRCK Period

Figure 10. CS4361 Data Format (Right-Justified 16)

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1 F2

3.183 kHz 10.61 kHz

Figure 11. De-Emphasis Curve (Fs = 44.1kHz)

4.3 De-Emphasis

The CS4361 includes on-chip digital de-empha sis. Figure 11 shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve will scale proportionally with changes in sample rate, Fs. The de-emphasis filter is active (inactive) if the DEM

falling edges of LRCK. This function is available only in the internal Serial Clock Mode when LRCK < 50 kHz.

9/30/11

CS4361

/SCLK pin is low (high) for five consecutive

4.4 Mode Select

Mode selection is determined by the Mode Select pin. The value of this pin is locked 1024 LRCK cycles after

RST

is released. This pin requires a specific connection to supply, ground, MCLK, or LRCK as outlined in

Table 2.

Mode pin is: Mode Figure

Tied to VL I²S 7

Tied to GND Left-Justified 8

Tied to LRCK Right-Justified - 24 bit 9

Tied to MCLK Right-Justified - 16bit 10

14

Table 2. Mode Pin Settings

Page 15

Confidential Draft

USER: Apply Power

Wait State

USER: Apply LRCK and MCLK

MCLK/LRCK Ratio Detection

USER: Applied SCLK

USER: Remove

LRCK

USER: change

MCLK/LRCK ratio

SCLK mode = internal

SCLK mode = external

Normal Operation

De-emphasis

available

Analog Output

is Generated

Normal Operation

De-emphasis

not available

Analog Output

is Generated

USER: change

MCLK/LRCK ratio

USER: Apply RST

or remove MCLK

USER: Remove

LRCK

USER: Apply RST

or remove MCLK

USER: Apply MCLK, release RST

Power-Down State

VQ and outputs low

VQ and outputs

ramp down

VQ and outputs

ramp down

VQ and outputs ramp up

USER: No SCLK

Figure 12. CS4361 Initialization and Power-Down Sequence

4.5 Initialization and Power-Down

The initialization and power-down sequence flow chart is shown i n Figure 12. The CS4361 enters the pow-

er-down state upon initial power-up. The interpo lation filter s an d delta- sigma m odu lators are r eset, and the

internal voltage reference, multi-bit digital-to-analog co nverters, and switched-capacitor low-pass filters are

powered down. The device will remain in the Power-Down Mode until RST

are present. Once MCLK and LRCK are detected, MCLK occurrences are counted over one LRCK period

to determine the MCLK/LRCK frequency ratio. Power is then applied to the internal voltage reference. Finally, power is applied to the D/A converters and switched-capacitor filters, and the analog outputs will ramp to

the quiescent voltage, VQ.

9/30/11

CS4361

is released and MCLK and LRCK

15

Page 16

Confidential Draft

4.6 Output Transient Control

The CS4361 uses Popguard technology to minimize the effects of output transients during power-up and

power-down. When implemented with external DC-blocking capacitors connected in series with the audio

outputs, this feature eliminates the audio tr ansients commonly produced by single-ended, single-supply

converters. To make the best use of this feature, it is necessary to understand its operation.

4.6.1 Power-Up

When the device is initially powered up, the audio outputs, AOUT1-6, are clamped to VQ, which is initially

low. After RST

quiescent voltage. This ramp takes approximately 200 ms to complete. The gradual voltage ramping allows time for the external DC-blocking capacitors to charge to VQ, effectively blocking the quiescent DC

voltage. Audio output begins approximately 2000 sample periods after va lid LRCK and SDIN are supplied

(and SCLK, if used).

is released and MCLK is applied, the outputs begin to ramp with VQ towards the nominal

4.6.2 Power-Down

To prevent audio transients at power-down, the DC-blocking capacitors must fully discharge before turning off the power. In order to do this, either stop MCLK o r hold RST

removing power. During this time, voltage on VQ and the audio outputs discharge gradually to GND. If

power is removed before this 250 ms time period has pas sed, a tr ansient will occur when the VA supply

drops below that of VQ. There is no minimum time for a power cycle; power may be reapplied at any time.

9/30/11

CS4361

low for a period of about 250 ms before

When changing clock ratio or sample rate, it is recommended that zero d ata (or near zero data) be present

on SDIN for at least 10 LRCK samples before the change is made. During the clocking change, the DAC

outputs will always be in a zero data state. If non-zero audio is present at the time of switching, a slight

click or pop may be heard as the DAC output automatically goes to its zero data state.

4.7 Grounding and Power Supply Decoupling

As with any high-resolution converter, the CS4361 requir es careful attention to power supply and grounding

arrangements to optimize performance. Figure 6 shows the recommended power arra ngement, with VA

connected to a clean +5 V supply. For best performance, decoupling and filter capacitors should be located

as close to the device package as possible, with the smallest capacitors placed closest.

4.8 Analog Output and Filtering

The analog filter present in the CS4361 is a switched-capacitor filter followed by a continuous-time, lowpass filter. Its response, combined with that of the digital interpolator, is given in Figures 14 - 21. The rec-

ommended external analog circuitry is shown in the “Typical Connection Diagram” on page 11.

The analog outputs are named AOUT1-6. The SDIN1 feeds AOUT1 as the ‘Left’ marked data and AOUT2

as the ‘Right’ marked data. The SDIN2 feeds AOUT3 as the ‘Left’ marked data and AOUT4 as the ‘Right’

marked data. The SDIN3 feeds AOUT5 as the ‘Left’ marked data and AOUT6 as the ‘Right’ marked data.

16

Page 17

Confidential Draft

470

Audio

Out

2 k

10 k

-V

+V

A

MMUN2111LT1

AOUT

MUTEC

CS4361

AC

Couple

47 k10 k

Filter

Cap

MMUN2211LT1

(if available)

6

6

(Low Ron)

Figure 13. Suggested Active-Low Mute Circuit

4.9 Mute Control

The MUTEC pin is intended to be used as control for an external mute circuit in order to add off-chip mute

capability.

This pin becomes active under the following conditions:

1. During power-up initialization

2. Upon reset

3. If the MCLK to LRCK ratio is incorrect

4. Upon receipt of 512 consecutive samples of zero

5. During power-down

The MUTEC pin will only go active on static zero data only if all 6 channels satisfy the 512 sample require-

ment. If any channel receives non-zero data, the mute pin will return low (inactive).

Use of the mute control function is not mandatory but is recommended for designs requiring the absolute

minimum in extraneous clicks and pops. Also, use of the mute control function can enable the system designer to achieve idle channel noise and signal-t o-noise ratios tha t are on ly limited by the external m ute circuit. The MUTEC pin is an active-high CMOS driver. See Figure 13 below for a suggested active-high mute

circuit.

9/30/11

CS4361

17

Page 18

Confidential Draft

Figure 14. Single-Speed Stopband Rejection Figure 15. Single-Speed Transition Band

Figure 16. Single-Speed Transition Band Figure 17. Single-Speed Passband Ripple

5. PERFORMANCE PLOTS

9/30/11

CS4361

18

Page 19

Confidential Draft

Figure 18. Double-Speed Stopband Rejection Figure 19. Double-Speed Transition Band

Figure 20. Double-Speed Transition Band Figure 21. Double-Speed Passband Ripple

9/30/11

CS4361

19

Page 20

Confidential Draft

Figure 22. Quad-Speed Stopband Rejection Figure 23. Quad-Speed Transition Band

Figure 24. Quad-Speed Transition Band Figure 25. Quad-Speed Passband Ripple

0

-10

-20

-30

-40

-50

Amplitude (dB)

-60

-70

-80

-90

-100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

Frequency(normalized to Fs)

9/30/11

0

-10

-20

-30

Amplitude (dB)

-40

-50

-60

CS4361

0.35 0.4 0.45 0.5 0.55 0.6 0.65 0.7 0.75

Frequency(normalized to Fs)

0

-5

-10

-15

-20

-25

Amplitude (dB)

-30

-35

-40

-45

-50

0.4 0.45 0.5 0.55 0.6 0.65 0.7

Frequency(normalized to Fs)

0.2

0.15

0.1

0.05

0

Amplitude (dB)

-0.05

-0.1

-0.15

-0.2

0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45

Frequency(normalized to Fs)

20

Page 21

Confidential Draft

6. PARAMETER DEFINITIONS

Total Harmonic Distortion + Noise (THD+N)

The ratio of the rms value of the signal t o the rms su m of all other spectral components over the specified

bandwidth (typically 10 Hz to 20 kHz), including distortion components. Expressed in decibels.

Dynamic Range

The ratio of the full-scale rms value of the signal to the rms sum of all other spectral components over the

specified bandwidth. Dynamic range is a signal-to-noise measurement over the specified bandwidth made

with a -60 dBFS signal. 60 dB is then added to the resulting measurement to refer the measurement to full

scale. This technique ensures that the distortion components are be low the noise level and do not effect the

measurement. This measurement technique has been accepted by the Audio Engineering Society, AES171991, and the Electronic Industries Association of Japan, EIAJ CP-307.

Interchannel Isolation

A measure of crosstalk between the left and right channels. Measured for each channel at the converter's

output with all zeros to the input under test and a full-scale signa l applied to the other channel. Units in d ecibels.

Interchannel Gain Mismatch

The gain difference between left and right channels. Units in decibels.

9/30/11

CS4361

Gain Error

The deviation from the nominal full scale analog output for a full scale digital input.

Gain Drift

The change in gain value with temperature. Units in ppm/°C.

21

Page 22

Confidential Draft

20L TSSOP (4.4 mm BODY) PACKAGE DRAWING

E

N

1

23

e

b

2

A1

A2

A

D

SEATING

PLANE

E1

1

L

SIDE VIEW

END VIEW

TOP VIEW

9/30/11

7. PACKAGE INFORMATION

INCHES MILLIMETERS NOTE

DIM MIN NOM MAX MIN NOM MAX

A -- -- 0.043 -- -- 1.10

A1 0.002 0.004 0.006 0.05 -- 0.15

A2 0.03346 0.0354 0.037 0.85 0.90 0.95

b 0.00748 0.0096 0.012 0.19 0.245 0.30

D 0.252 0.256 0.259 6.40 6.50 6.60 2,3

E 0.248 0.2519 0.256 6.30 6.40 6.50 1

E1 0.169 0.1732 0.177 4.30 4.40 4.50

e -- -- 0.026 -- -- 0.65 1

L 0.020 0.024 0.028 0.50 0.60 0.70

µ0°4°8°0°4°8°

CS4361

Notes:

22

JEDEC #: MO-153

Controlling Dimension is Millimeters.

1. “D” and “E1” are reference datums and do not included mold flash or protrusions, but do include mold

mismatch and are measured at the parting line, mold flash or protru sions shall not exceed 0 .20 mm per

side.

2. Dimension “b” does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be

0.13 mm total in excess of “b” dimension at maximum material condition. Dambar intrusion shall not reduce dimension “b” by more than 0.07 mm at least material condition.

3. These dimensions apply to the flat section of the lead between 0.10 and 0.25 mm from lead tips.

Page 23

Confidential Draft

9/30/11

CS4361

8. ORDERING INFORMATION

Product Description Package Pb-Free Grade Temp Range Container Order #

20-pin, 24-bit,

CS4361

CDB4361 CS4361 Evaluation Board - - - - CDB4361

192 kHz, 6-channel

D/A Converter

20-Plastic

TSSOP

Yes Commercial -40 to 85° C

Tube CS4361-CZZ

Tape and Reel CS4361-CZZR

23

Page 24

Confidential Draft

Contacting Cirrus Logic Support

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find the one nearest you, go to www.cirrus.com.

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without noti ce and is p rovided “AS IS” wit hout warran ty of any k ind (expr ess or i mplied). Customers are advis ed to ob tain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of thir d

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other inte llectual property rig hts. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent

does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARR ANTED FOR USE

IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOM ER’S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MER CHANTABILITY AND

FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY

INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OT HER AGE NTS FRO M ANY AND AL L LI ABI L IT Y, I NCL UDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic l ogo de s i gns, an d Po pg ua rd ar e t r a demar ks of Ci r ru s Logi c , I n c. Al l ot her br an d a nd pr oduct names in this document may be

trademarks or service marks of their respective owners.

9/30/11

9. REVISION HISTORY

Release Changes

A1 Initial Release.

A2 Correction to PDF file size.

F1 Removed VA = 3.3 V operation.

Updated Typ and Max THD+N and Dynamic Range specs in “DAC Analog Characteristics - Commercial”

on page 6.

Corrected “Output Transient Control” on page 16 and “CS4361 Initialization and Power-Down Sequence”

on page 15 to show ramp down when MCLK is removed.

Corrected MUTEC description “512 LRCK cycles” in “Mute Control” on page 17.

Removed -DZZ ordering option.

F2 Changed from footnote to “DAC Analog Characteristics - Commercial” on page 6 to read “One LSB of tri-

angular PDF dither added to data,” instead of “One-half LSB...”

Added -CZZR ordering option and removed references to -CZZ from the specifications..

CS4361

24

Loading...

Loading...