Page 1

`

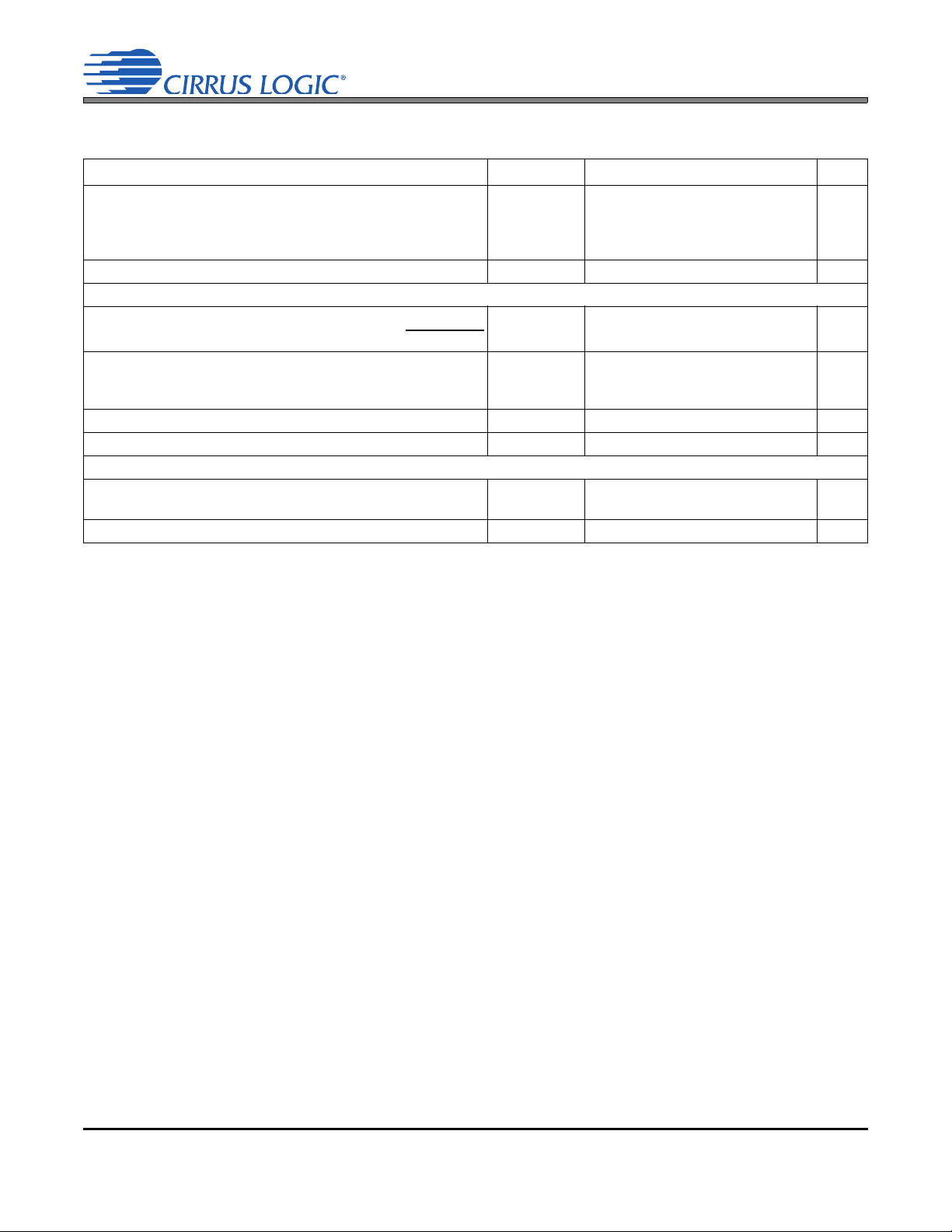

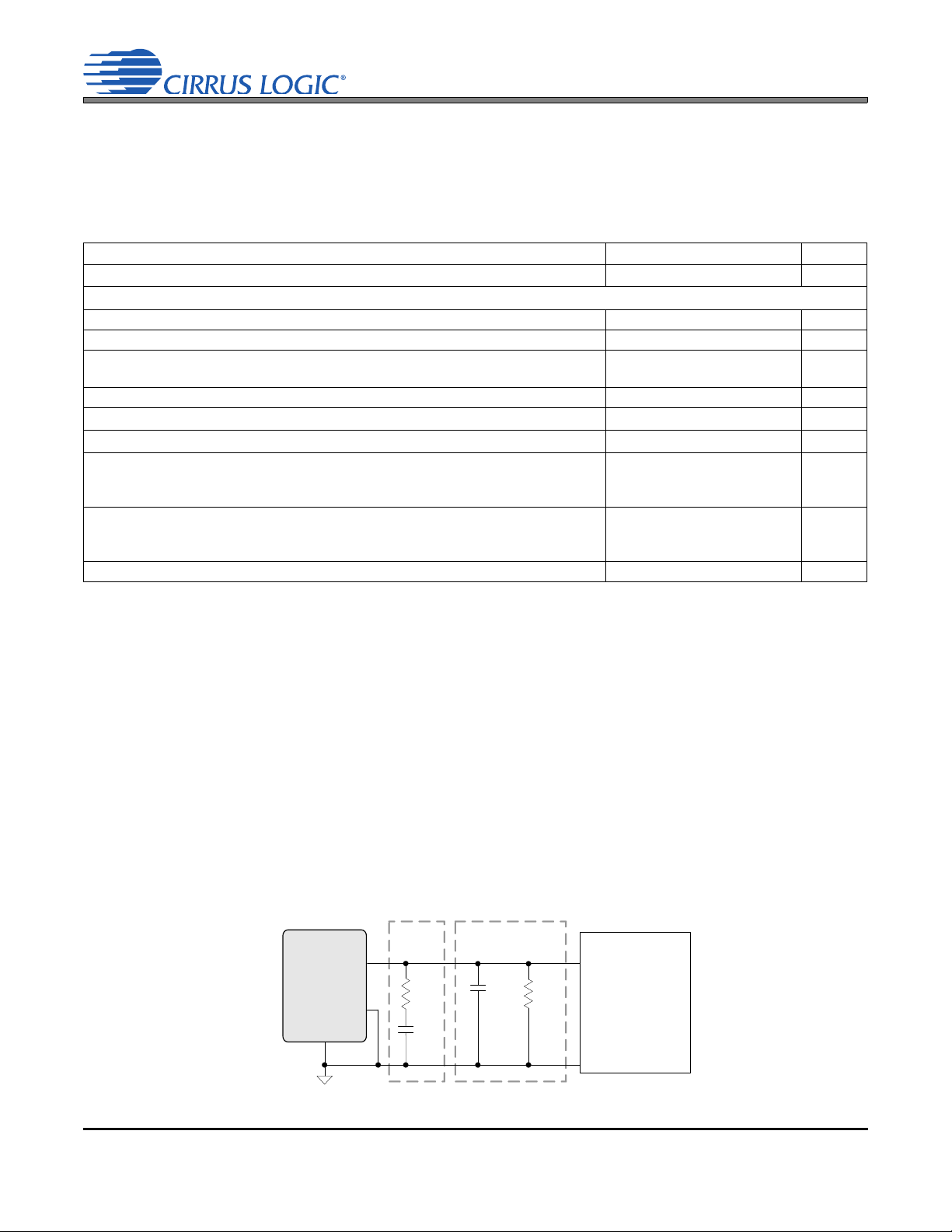

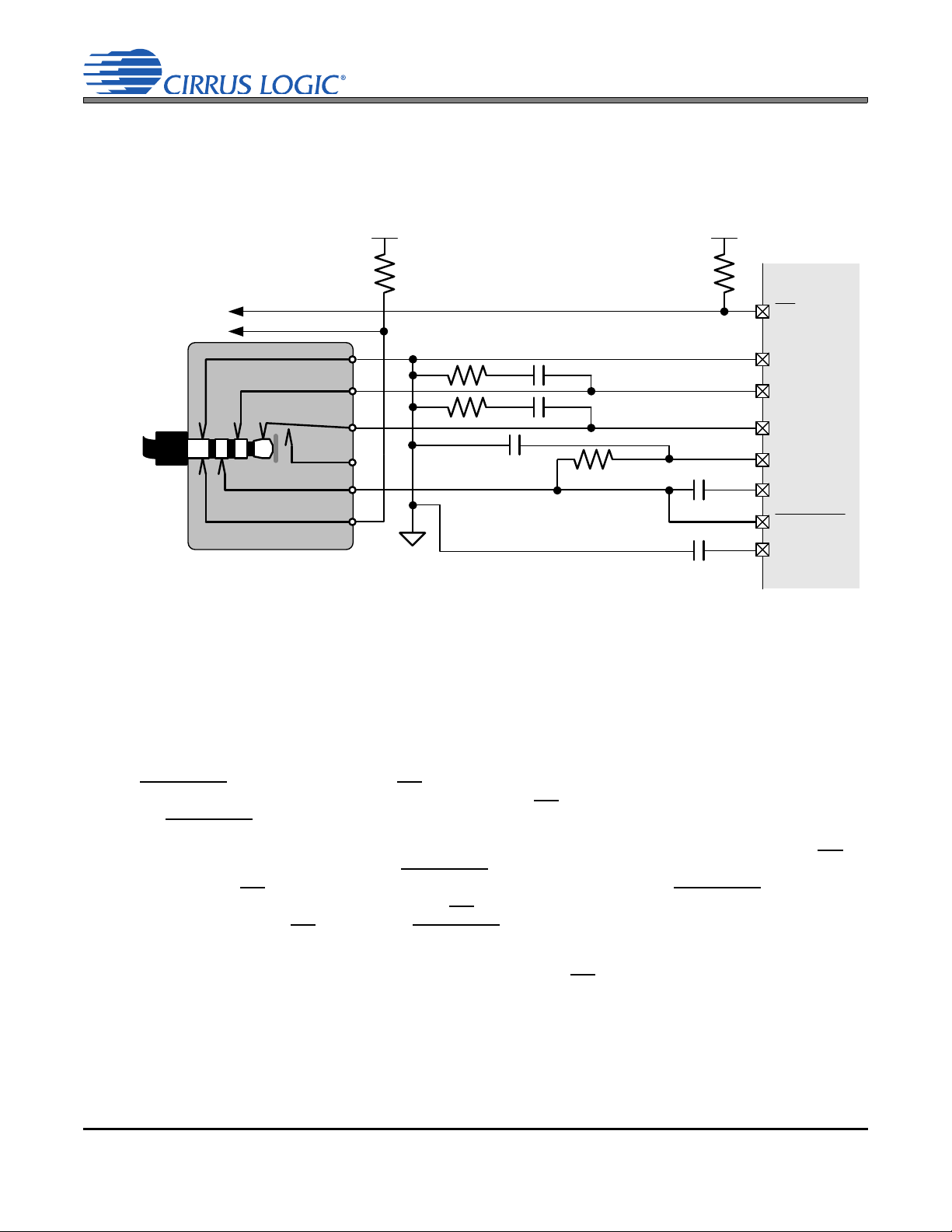

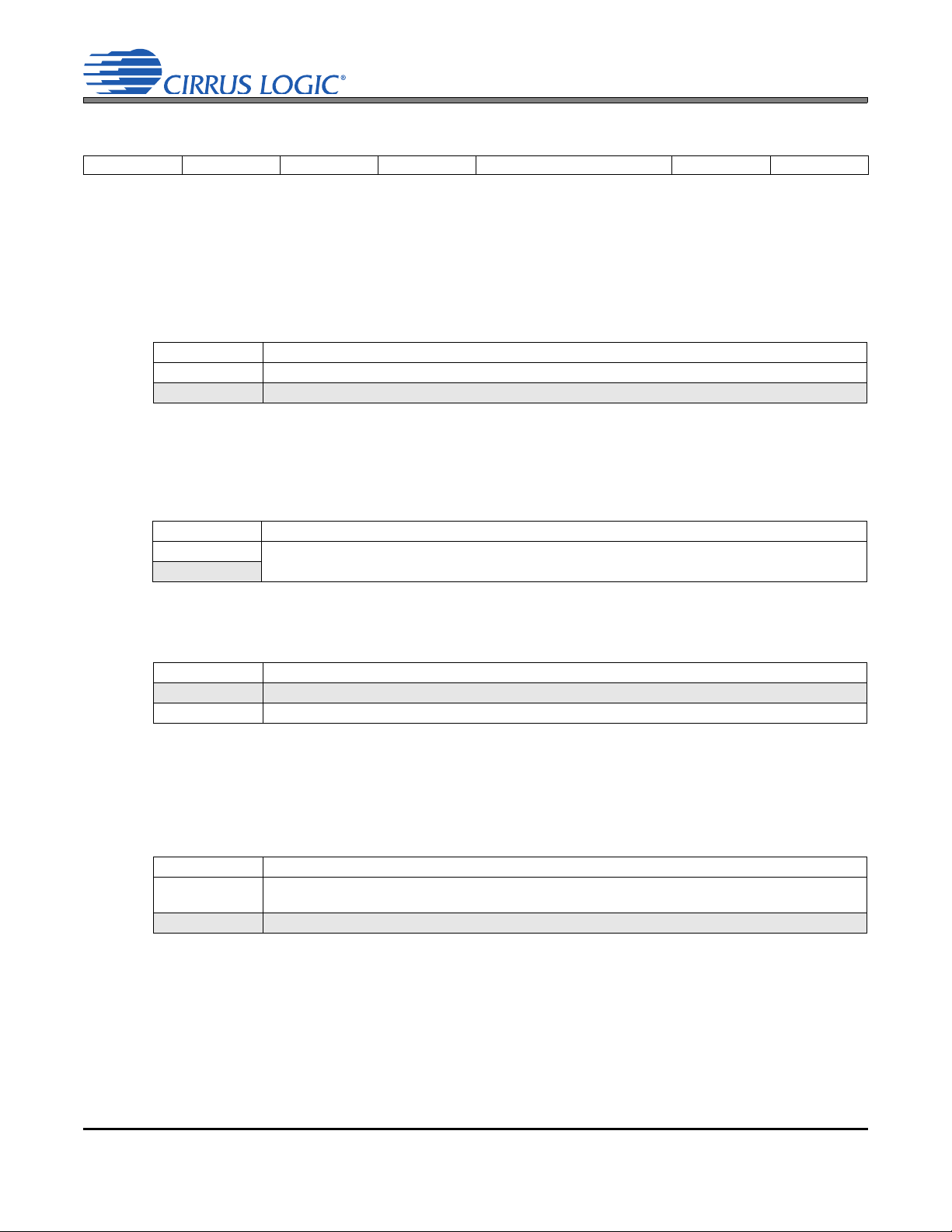

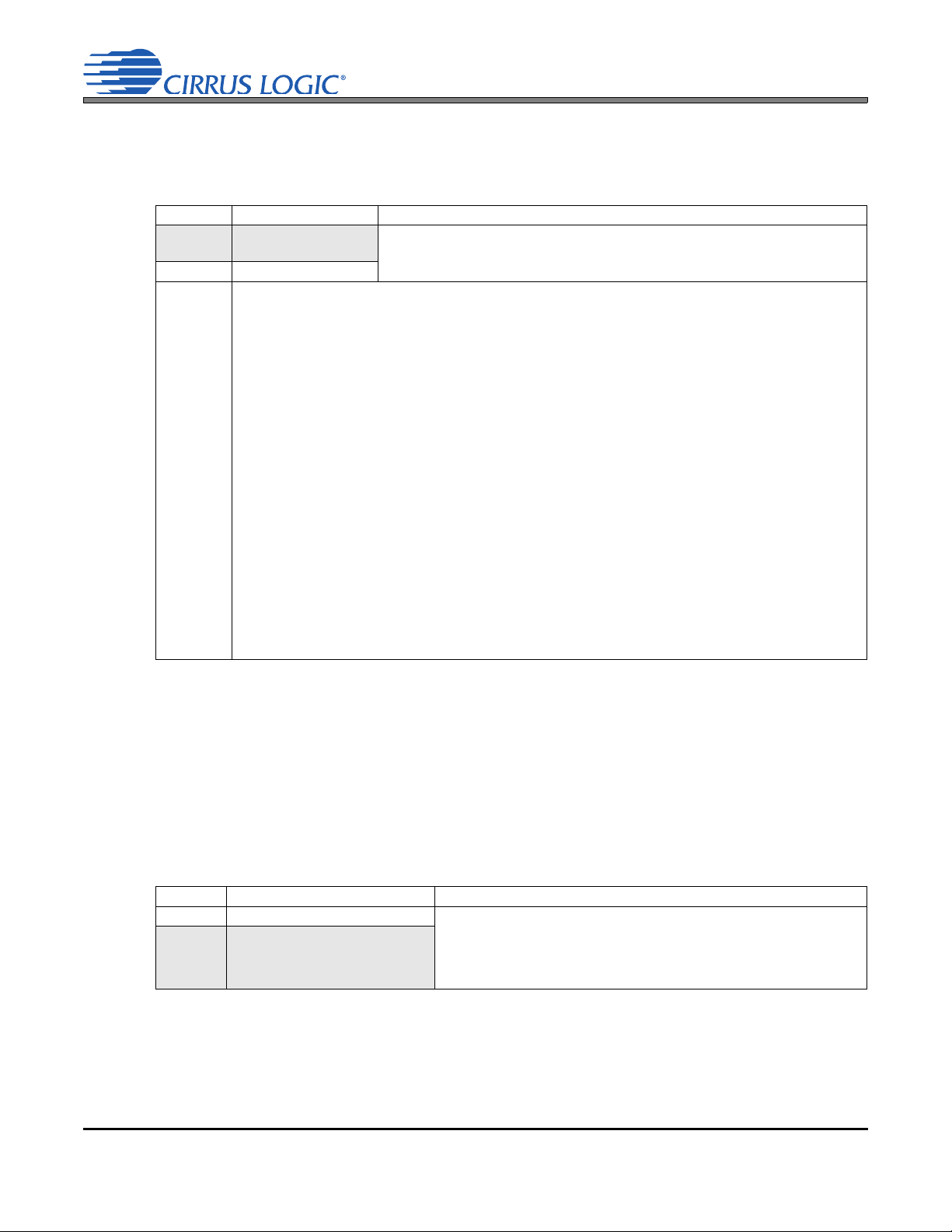

Line Outputs

Pseudo Diff. Input

-

+

+VCP_FILT

-VCP_FILT

Digital Processing

Level Shifters

CS42L73

Decimator,

HPF,

Noise

Gate,

ALC,

Volume,

Mute,

Swap/Mono

Volume, Mute, Limiter

MCLK

Stereo

Multi-bit

DAC

MCLK

Stereo

Multi-bit

DAC

LDO

VD_FILT

Headphone Outputs

Pseudo Diff. Input

-

+

+VCP_FILT

-VCP_FILT

Ear Speaker Output

VA

-

+

B

Speakerphone Line

Output (Right)

-

+

VP

B

VP

Speakerphone Output

(Left)

-

+

VP

A

VA

VA

Digital MIC Interface

Digital MIC Interface

VL

MCLK

Stereo

Multi-bit

ADC

-6 to +12 dB,

0.5 dB steps

-

+

MIC 2

MIC 1

Pseudo Diff. Input

Pseudo Diff. Input

Line Input (Left)

Line Input (Right)

Pseudo Diff. Input

+10 or

+20 dB

-

+

+10 or

+20 dB

-

+

MIC 1 Bias

MIC 2 Bias

MIC Bias Short DetectMIC Bias

Audio Serial Port

Voice Serial Port

Auxiliary Serial Port

Audio

Serial Port

SDOUT

SDIN

ASRC

ASRC

Voice

Serial Port

SDOUT

ASRC

Auxiliary

Serial Port

SDIN

ASRC

SDOUT

ASRC

SDIN

ASRC

-VCP_FILT

Inverting

Step-Down

VCP +VCP_FILT

+VCP_FILT

-VCP_FILT

MCLK

MCLK1

MCLK2

Control Port

Control Port

VP

VD_FILT

Digital Mixer

Volume, Mute, Limiter

MIC2_SDET

+

Audio Serial Port

Voice Serial Port

Auxiliary Serial Port

MIC/Line Input Path

CS42L73

Ultralow Power Mobile Audio and Telephony CODEC

Product Overview

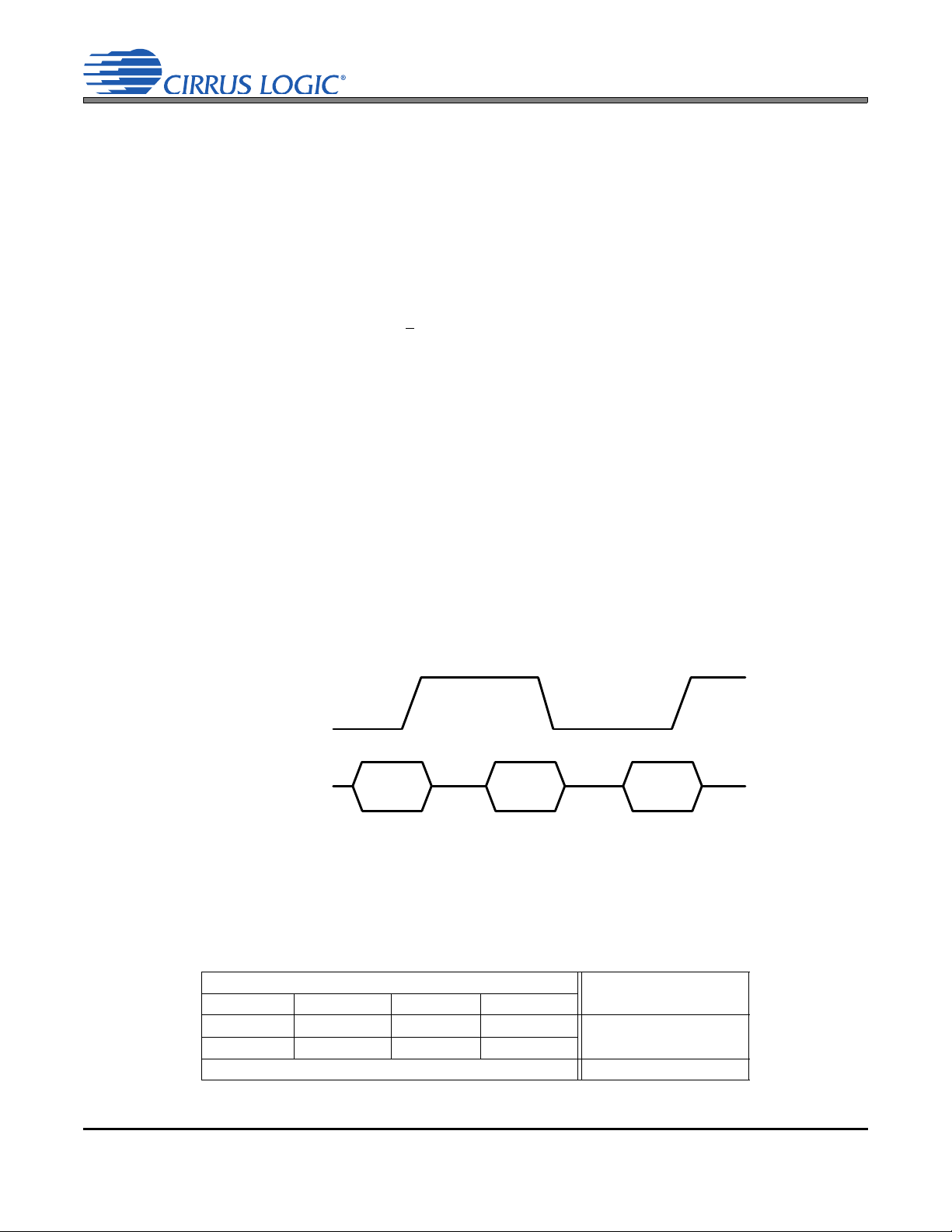

Stereo analog-to-digital converter (ADC)

Dual analog or digital mic support

Dual mic bias generators

Four digital-to-analog converters (DACs)

coupled to five outputs

– Ground-centered stereo headphone amp.

– Ground-centered stereo line output

– Mono ear speaker amplifier

– Mono 1-W speakerphone amplifier

– Mono speakerphone line output for stereo

speakerphone expansion

Three serial ports with asynchronous sample

rate converters

Digital audio mixing and routing

Ultralow Power Consumption

3.8-mW quiescent headphone playback

Applications

Smart phones, ultramobile PCs, and mobile

Internet devices

System Features

Native (no PLL required) support for 6/12/

24 MHz, 13/26 MHz, and 19.2/38.4 MHz

master clock rates and typical audio clock rates

Integrated high-efficiency power management

reduces power consumption

– Internal LDO regulator to reduce internal

digital operating voltage to VL/2 V

– Step-down charge pump provides low

headphone/line out supply voltage

– Inverting charge pump accommodates low

system voltage by providing negative rail for

HP and line amplifier

Flexible speakerphone amplifier powering

– 3.00–5.25 V range

– Independent cycling

Power-down management

– Individual controls for ADCs, digital mic

interface, mic bias generators, serial ports,

and output amplifiers and associated DACs

Programmable thermal overload notification

High-speed I²C™ control port (400 kHz)

(Features continued on page 2)

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2013

(All Rights Reserved)

JULY '13

DS882F1

Page 2

CS42L73

Stereo Analog-to-Digital Features

91-db dynamic range (A-weighted)

-85 dB THD+N

Independent ADC channel control

2:1 stereo analog input MUX

Stereo line input: Shared pseudodifferential

reference input

Dual analog mic inputs

– Pseudodifferential or single-ended

– Two, independent, programmable, low-noise

mic bias outputs

– Mic short detect to support headset button

Analog programmable gain amplifier (PGA)

(+12 to -6 dB in 0.5 dB steps)

+10 dB or +20 dB analog mic boost in addition

to PGA gain settings

Programmable automatic level control (ALC)

– Noise gate for noise suppression

– Programmable threshold and attack/release

rates

Dual Digital Microphone Interface

Programmable clock rate: Integer divide by 2 or

4 of internal MCLK

Stereo DAC to Headphone Amplifier

94-dB dynamic range (A-weighted)

-81 dB THD+N into 32

Integrated step-down/inverting charge pump

Class H amplifier, automatic supply adjustment

– High efficiency

–Low EMI

Pseudodifferential ground-centered outputs

High HP power output at -70/-81 dB THD+N

– 2 x 16/8.1 mW into 16/32 @ 1.8 V

Pop and click suppression

Analog volume control (+12 to -50 dB in 1 dB

steps; to -76 dB in 2 dB steps) with zero-cross

transitions

Digital volume control (+12 to -102 dB in 0.5 dB

steps) with soft-ramp transitions

Programmable peak-detect and limiter

Stereo DAC to Line Outputs

97 dB dynamic range (A-weighted)

-86 dB THD+N

Class-H amplifier

Pseudodifferential ground-centered outputs

1-V

Pop and click suppression

Analog volume control (+12 to -50 dB in 1 dB

line output @ 1.8 V

RMS

steps; to -76 dB in 2 dB steps) with zero-cross

transitions

Digital volume control (+12 to -102 dB in 0.5 dB

steps) with soft-ramp transitions

Programmable peak-detect and limiter

Mono DAC to Ear Speaker Amplifier

High-power output at -70 dB (0.032%) THD+N:

45 mW into 16 @ 1.8 V

Pop and click suppression

Digital volume control (+12 to -102 dB in 0.5 dB

steps) with soft-ramp transitions

Programmable peak-detect and limiter

Mono DAC to Speakerphone Amplifier

High output power at 1% THD+N: 1.06/0.76/

0.59 W into 8 @ 5.0/4.2/3.7 V

Direct battery-powered operation

Pop and click suppression

Digital volume control (+12 to -102 dB in 0.5 dB

steps) with soft-ramp transitions

Programmable peak-detect and limiter

Mono DAC-to-Speakerphone Line

Output

84 dB dynamic range (A-weighted)

-65 dB THD+N

High voltage (2 V

@ VA = 1.8 V, VP =

RMS

3.7 V) line output to ensure maximum output

from a wide variety of external amplifiers

Pop and click suppression

Digital volume control (+12 to -102 dB in 0.5 dB

steps) with soft-ramp transitions

Programmable peak-detect and limiter

Serial Ports

Three independent serial ports: auxiliary serial

port (XSP), audio serial port (ASP), and voice

serial port (VSP)

8.00, 11.025, 12.00, 16.00, 22.05, 24.00,

32.00, 44.10, and 48.00 kHz sample rates

All ports support master or slave operation with

I²S interface

XSP and VSP support slave operation with

PCM interface

XSP and ASP are stereo-input/stereo-output

to/from digital mixer

VSP is mono-input/stereo-output to/from digital

mixer

Integrated asynchronous sample rate

converters

2 DS882F1

Page 3

CS42L73

General Description

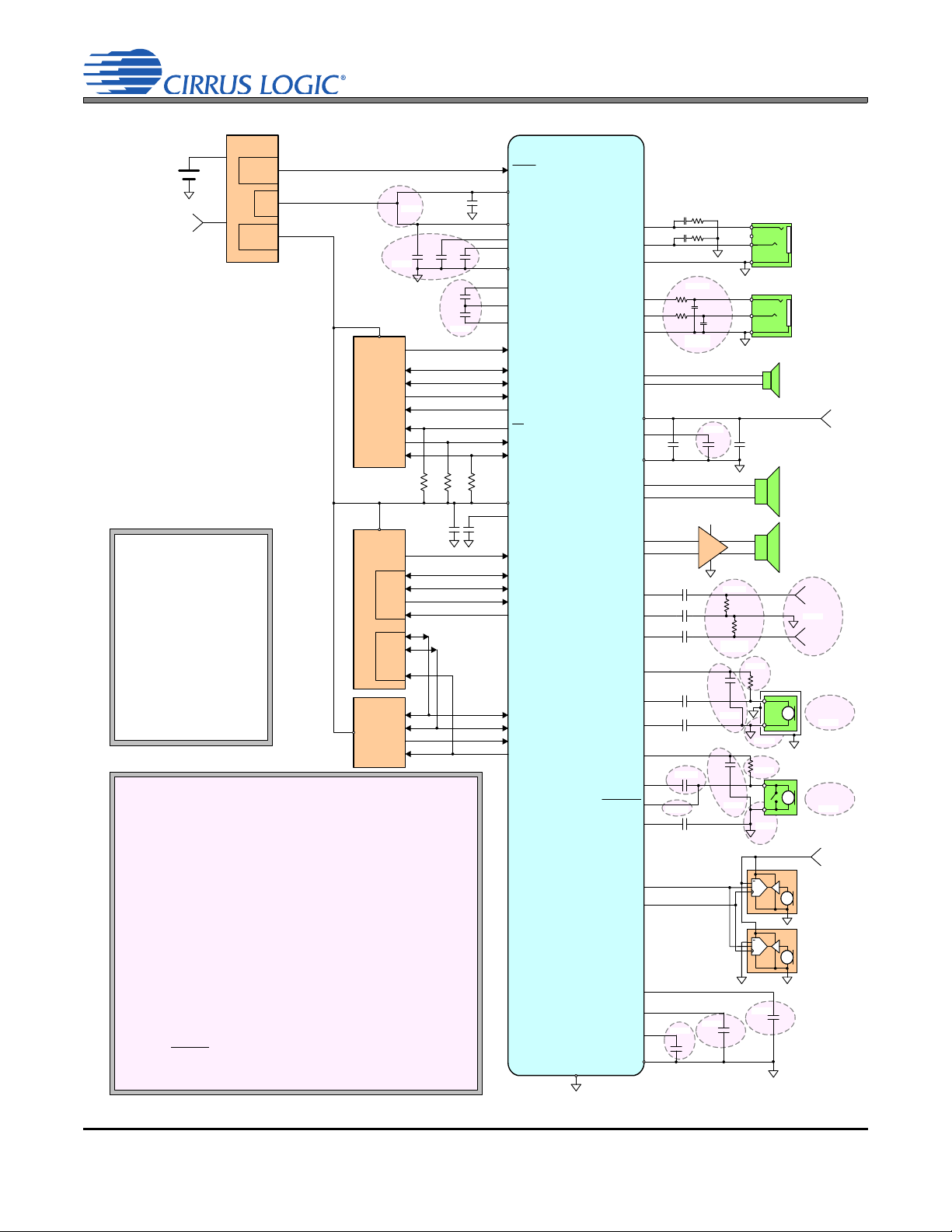

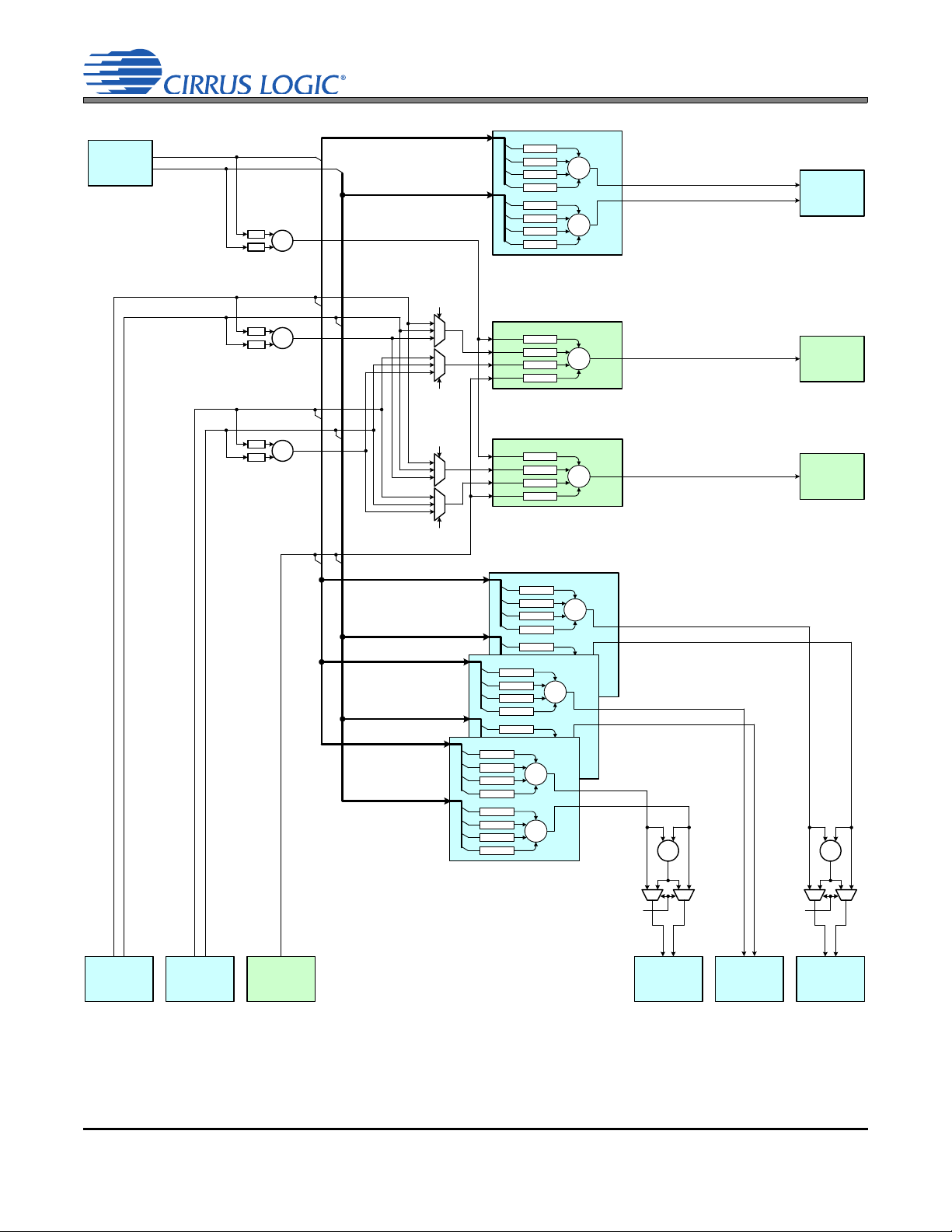

The CS42L73 is a highly integrated, low-power, audio and telephony CODEC for portable applications such as

smartphones and ultramobile personal computers.

The CS42L73 features a flexible clocking architecture, allowing the device to use reference clock frequencies of

6, 12, 24, 13, 26, 19.2, or 38.4 MHz, or any standard audio master clock. As many as two reference/master clock

sources may be connected; either one can be selected to drive the internal clocks and processing rate of the

CS42L73. Thus, multiple master clock sources within a system can be dynamically activated and deactivated to

minimize system-level power consumption.

Three asynchronous bidirectional serial ports (auxiliary, audio, and voice serial ports (XSP, ASP, and VSP,

respectively) support multiple clock domains of various digital audio sources or destinations. Three low-latency,

fast-locking, integrated high-performance asynchronous sample rate converters synchronize and convert the

audio samples to the internal processing rate of the CS42L73.

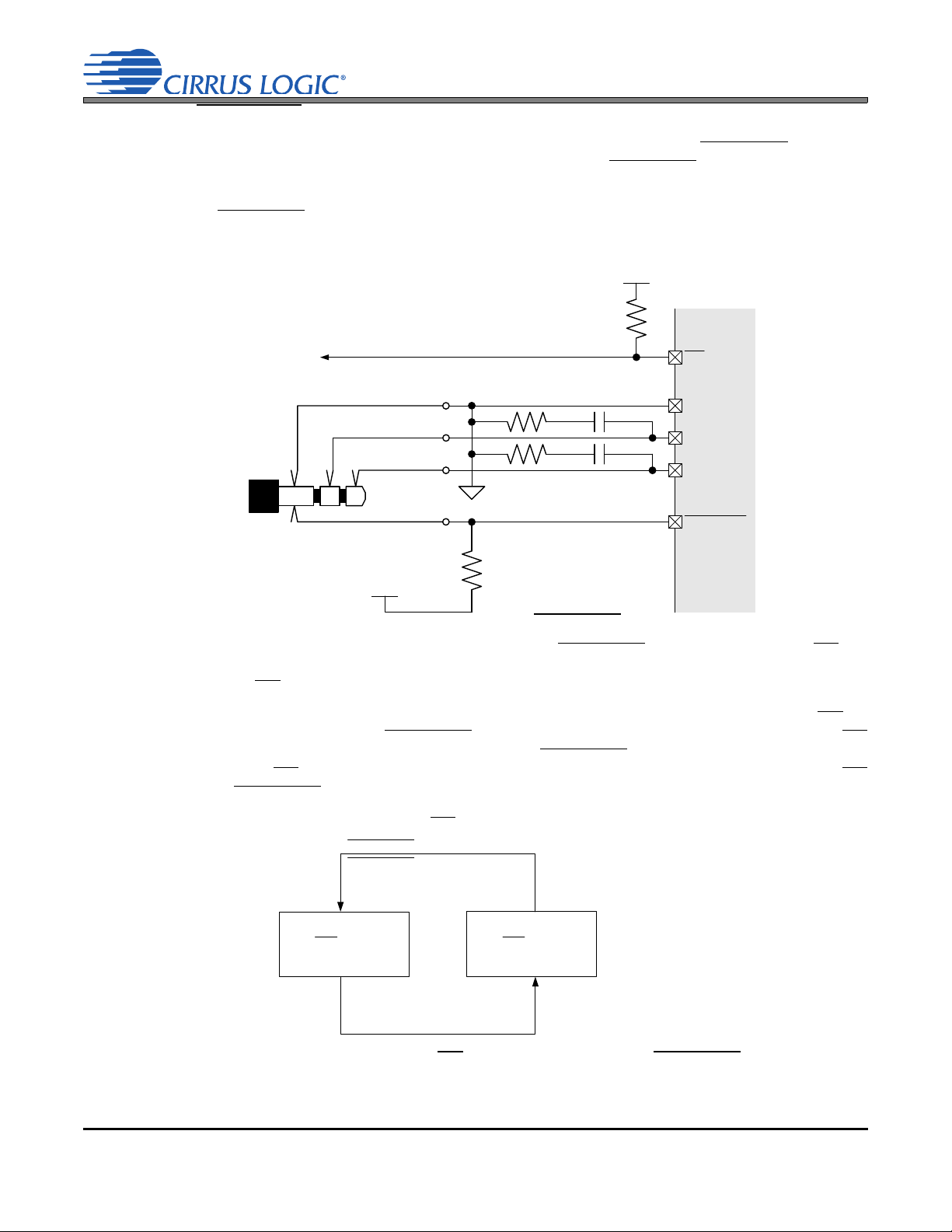

A stereo line input or two mono (one stereo) mic inputs are routed to a stereo ADC. The mic inputs may be

selectively preamplified by +10 or +20 dB. Two independent, low-noise mic bias voltage supplies are also provided.

A PGA is applied to the inputs before they reach the ADC.

The stereo input path that follows the stereo ADC begins with a multiplexer to selectively choose data from a

digital mic interface. Following the multiplexer, the data is decimated, selectively DC high-pass filtered,

channel-swapped or mono-to-stereo routed (fanned-out), and volume adjusted or muted. The volume levels can be

automatically adjusted via a programmable ALC and noise gate.

A digital mixer is used to mix and route the CS42L73’s inputs (analog inputs to ADC, digital mic, or serial ports) to

outputs (DAC-fed amplifiers or serial ports). There is independent attenuation on each mixer input for each output.

The processing along the output paths from the digital mixer to the two stereo DACs includes volume adjustment

and mute control. A peak-detector can be used to automatically adjust the volume levels via a programmable limiter.

The first stereo DAC feeds the stereo headphone and line output amplifiers, which are powered from a dedicated

positive supply. An integrated charge pump provides a negative supply. This allows a ground-centered analog

output with a wide signal swing, and eliminates external DC-blocking capacitors while reducing pops and clicks.

Tri-level Class H amplification is used to reduce power consumption under low-signal-level conditions. Analog

volume controls are provided on the stereo headphone and line outputs.

The second stereo DAC feeds several mono outputs. The left channel of the DAC sources a mono,

differential-drive, speakerphone amplifier for driving the handset speakerphone. The right channel sources a

mono, differential-drive, earphone amplifier for driving the handset earphone. The right channel is also routed to

a mono, differential-drive, speakerphone line output, which may be connected to an external amplifier to

implement a stereo speakerphone configuration when it is used in conjunction with the integrated speakerphone

amplifier.

The CS42L73 implements robust power management to achieve ultralow power consumption. High granularity in

power-down controls allows individual functional blocks to be powered down when unused. The internal low-dropout

regulator (LDO) saves power by running the internal digital circuits at half the logic interface supply voltage (VL/2).

A high-speed I

The CS42L73 is available in space-saving 64-ball WLCSP and 65-ball FBGA packages for the commercial (-40° to

+85° C) grade.

2

C control port interface capable of up to 400 kHz operation facilitates register programming.

DS882F1 3

Page 4

TABLE OF CONTENTS

1. PACKAGE PIN/BALL ASSIGNMENTS AND CONFIGURATIONS ..................................................... 12

1.1 64-Ball Wafer-Level Chip Scale Package (WLCSP) ...................................................................... 12

1.2 65-Ball Fine-Pitch Ball Grid Array (FBGA) Package ...................................................................... 13

1.3 Pin/Ball Descriptions ...................................................................................................................... 14

1.4 Digital Pin/Ball I/O Configurations .................................................................................................. 16

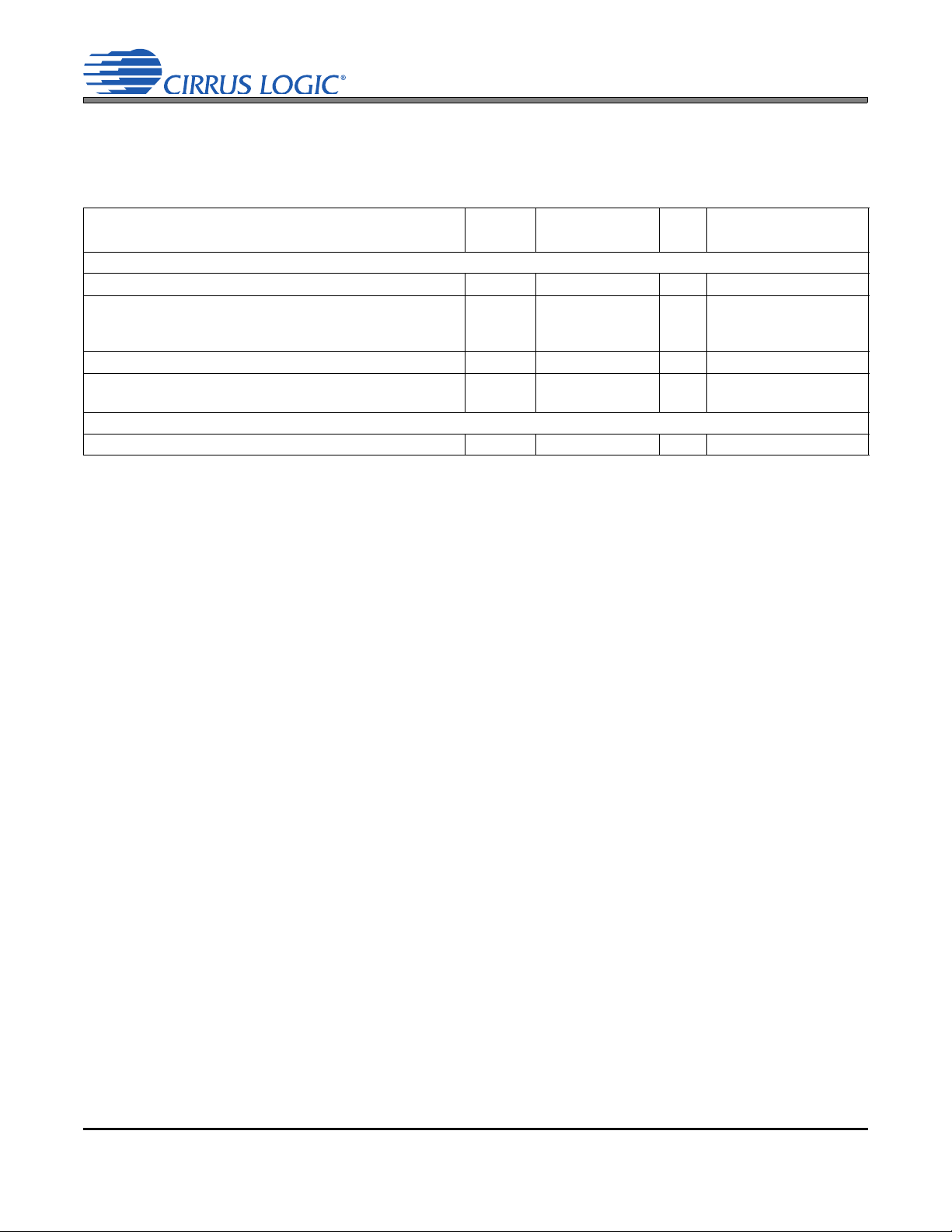

2. TYPICAL CONNECTION DIAGRAM ................................................................................................... 17

2.1 Low-Profile Charge-Pump Capacitors ........................................................................................... 18

2.2 Ceramic Capacitor Derating ........................................................................................................... 18

3. CHARACTERISTIC AND SPECIFICATIONS ...................................................................................... 19

4. APPLICATIONS ................................................................................................................................... 41

4.1 Overview ........................................................................................................................................ 41

4.1.1 Basic Architecture ................................................................................................................. 41

4.1.2 Line and Microphone Inputs .................................................................................................. 41

4.1.3 Line and Headphone Outputs (Class H, Ground-Centered Amplifiers) ................................. 41

4.1.4 Digital Mixer ........................................................................................................................... 41

4.1.5 Power Management .............................................................................................................. 41

4.2 Internal Master Clock Generation .................................................................................................. 42

4.3 Thermal Overload Notification ....................................................................................................... 42

4.4 Pseudodifferential Outputs ............................................................................................................. 43

4.5 Class H Amplifier .......................................................................................................................... 44

4.5.1 Power Control Options .......................................................................................................... 44

4.5.1.1 Standard Class AB Operation (Mode 001, 010, and 011) ......................................... 45

4.5.1.2 Adapt-to-Volume Settings (Mode 000) ...................................................................... 45

4.5.1.3 Adapt-to-Output Signal (Mode 111) ........................................................................... 46

4.5.2 Power Supply Transitions ...................................................................................................... 46

4.5.3 Efficiency ............................................................................................................................... 49

4.6 DAC Limiter .................................................................................................................................... 49

4.7 Analog Output Current Limiter ....................................................................................................... 51

4.8 Serial Ports .................................................................................................................................... 51

4.8.1 Power Management .............................................................................................................. 51

4.8.2 I/O .......................................................................................................................................... 51

4.8.3 High-impedance Mode .......................................................................................................... 52

4.8.4 Master and Slave Timing ....................................................................................................... 52

4.8.4.1 SCLK = MCLK Modes ............................................................................................... 53

4.8.5 Serial Port Sample Rates and Master Mode Settings ........................................................... 53

4.8.6 Formats ................................................................................................................................. 54

4.8.6.1 I²S Format .................................................................................................................. 55

4.8.6.2 PCM Format .............................................................................................................. 55

4.8.7 Mono/Stereo .......................................................................................................................... 57

4.8.8 Data Bit Depths ..................................................................................................................... 57

4.8.8.1 I²S Format Bit Depths ................................................................................................ 57

4.8.8.2 PCM Format Bit Depths ............................................................................................. 58

4.9 Asynchronous Sample Rate Converters (ASRCs) ......................................................................... 59

4.10 Input Paths ................................................................................................................................... 59

4.10.1 Input Path Source Selection and Powering ......................................................................... 59

4.10.2 Digital Microphone (DMIC) Interface ................................................................................... 60

4.10.2.1 DMIC Interface Description ...................................................................................... 60

4.10.2.2 DMIC Interface Signaling ......................................................................................... 60

4.10.2.3 DMIC Interface Powering ......................................................................................... 60

4.10.2.4 DMIC Interface Clock Generation ............................................................................ 61

4.11 Digital Mixer ................................................................................................................................. 61

4.11.1 Mono and Stereo Paths ....................................................................................................... 63

CS42L73

4 DS882F1

Page 5

CS42L73

4.11.2 Mixer Input Attenuation Adjustment .................................................................................... 63

4.11.3 Powered-Down Mixer Inputs ...............................................................................................64

4.11.4 Avoiding Mixer Clipping ....................................................................................................... 64

4.11.5 Mixer Attenuation Values .................................................................................................... 65

4.12 Recommended Operating Procedures ........................................................................................ 65

4.12.1 Initial Power-Up Sequence .................................................................................................. 65

4.12.2 Power-Up Sequence (xSP to HP/LO) ................................................................................. 66

4.12.3 Power-Down Sequence (xSP to HP/LO) ............................................................................. 67

4.12.4 Recommended Sequence for Modification of the MCLK Signal ......................................... 67

4.12.5 Microphone Enabling/Switching Sequence ......................................................................... 68

4.12.6 Final Power-Down Sequence .............................................................................................. 68

4.13 Using MIC2_SDET as Headphone Plug Detect ........................................................................... 69

4.14 Headphone Plug Detect and Mic Short Detect ............................................................................ 70

4.15 Interrupts ...................................................................................................................................... 70

4.16 Control Port Operation ................................................................................................................. 71

4.16.1 I²C Control ........................................................................................................................... 71

4.17 Fast Start Mode ........................................................................................................................... 73

4.18 Headphone High-Impedance Mode .............................................................................................75

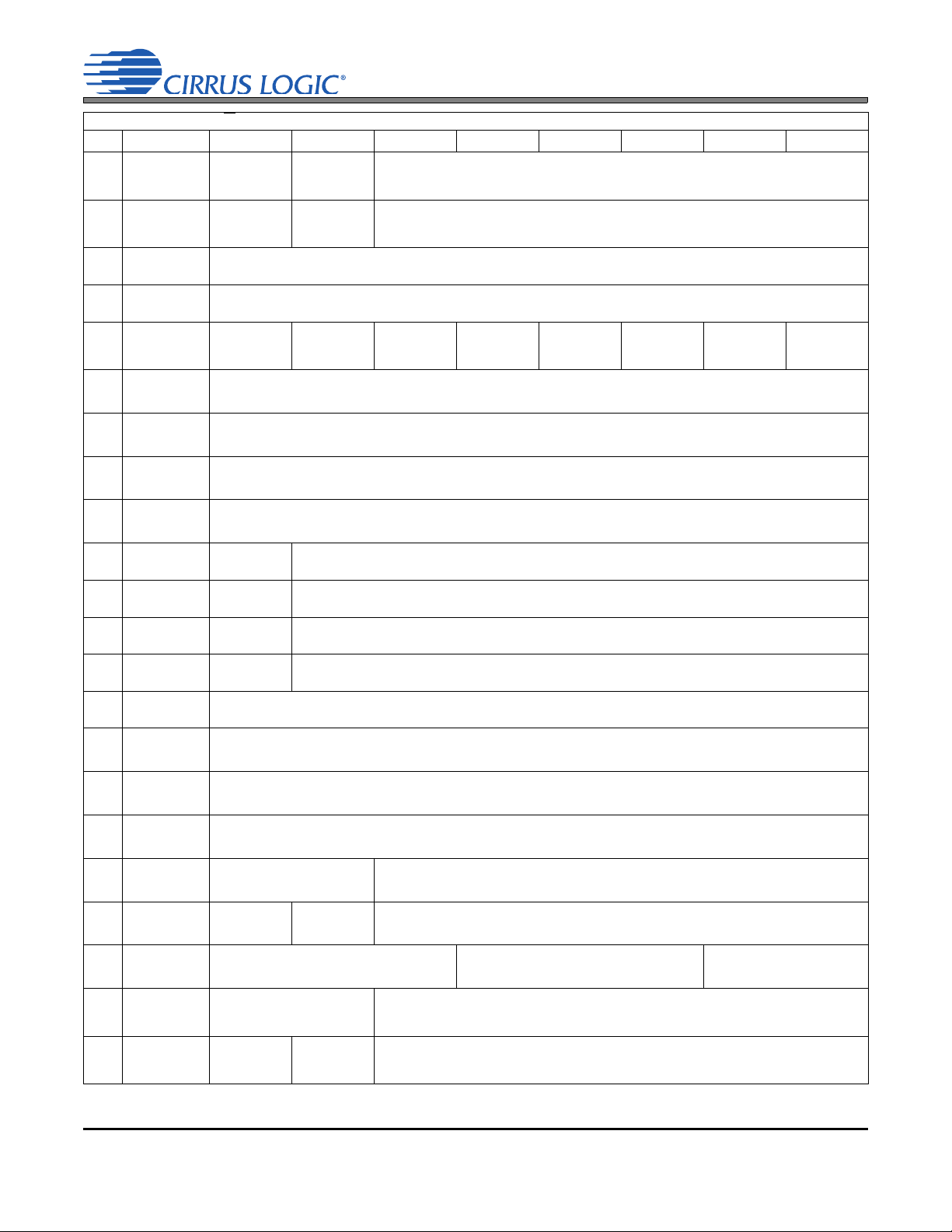

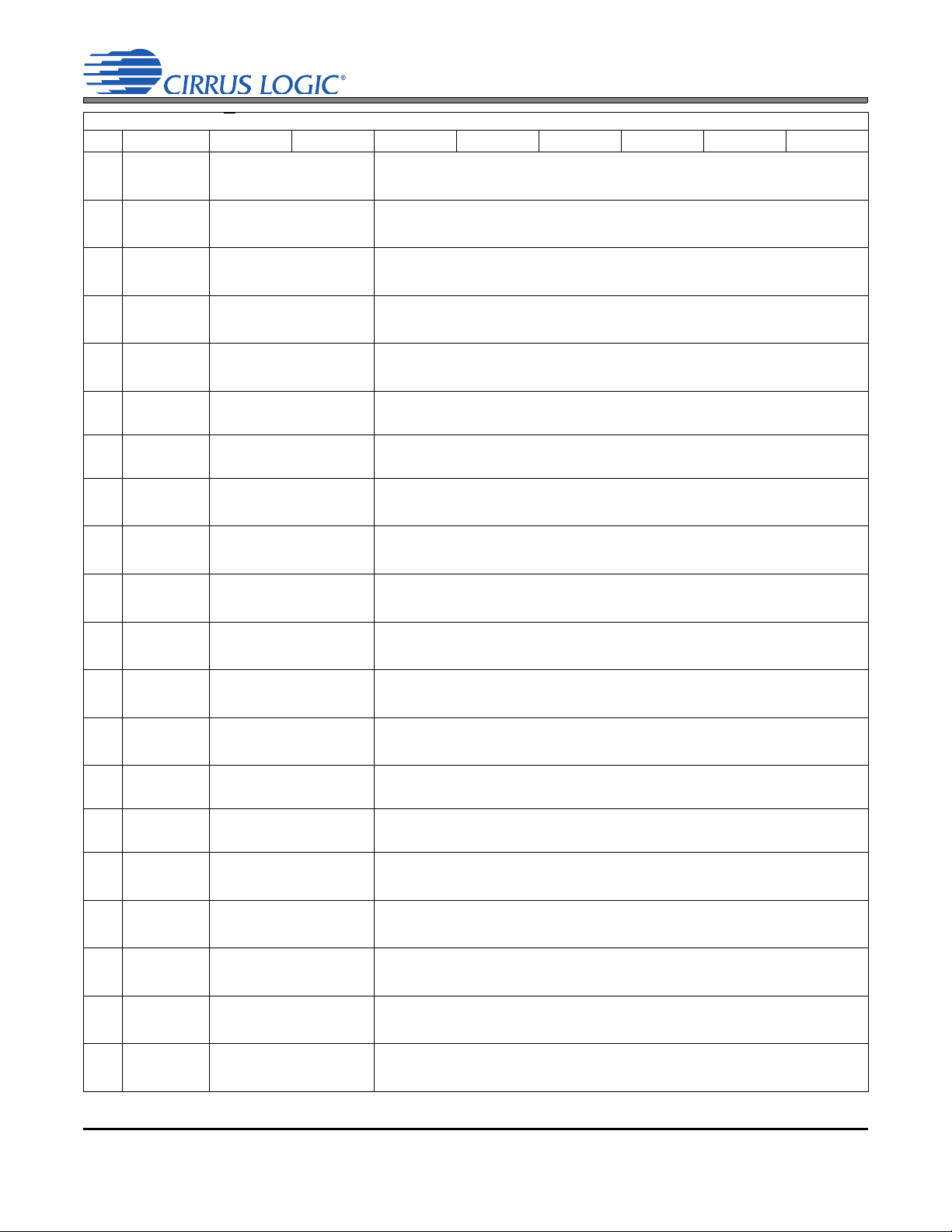

5. REGISTER QUICK REFERENCE ........................................................................................................ 76

6. REGISTER DESCRIPTION .................................................................................................................. 81

6.1 Fast Mode Enable (Address 00h) .................................................................................................. 81

6.1.1 Test Bits ................................................................................................................................ 81

6.2 Device ID A and B (Address 01h), C and D (Address 02h), and E (Address 03h) (Read Only) . 81

6.2.1 Device I.D. (Read Only) ........................................................................................................ 81

6.3 Revision ID (Address 05h) (Read Only) ......................................................................................... 81

6.3.1 Alpha Revision (Read Only) .................................................................................................. 81

6.3.2 Metal Revision (Read Only) .................................................................................................. 81

6.4 Power Control 1 (Address 06h) ...................................................................................................... 82

6.4.1 Power Down ADC x ............................................................................................................... 82

6.4.2 Power Down Digital Mic x ...................................................................................................... 82

6.4.3 Discharge Filt+ Capacitor ...................................................................................................... 82

6.4.4 Power Down Device .............................................................................................................. 82

6.5 Power Control 2 (Address 07h) ...................................................................................................... 83

6.5.1 Power Down MICx Bias ......................................................................................................... 83

6.5.2 Power Down VSP .................................................................................................................. 83

6.5.3 Power Down ASP SDOUT Path ............................................................................................ 83

6.5.4 Power Down ASP SDIN Path ................................................................................................ 83

6.5.5 Power Down XSP SDOUT Path ............................................................................................ 83

6.5.6 Power Down XSP SDIN Path ................................................................................................

6.6 Power Control 3 and Thermal Overload Threshold Control (Address 08h) ................................... 84

6.6.1 Thermal Overload Threshold Settings ................................................................................... 84

6.6.2 Power Down Thermal Sense .................................................................................................84

6.6.3 Power Down Speakerphone Line Output .............................................................................. 84

6.6.4 Power Down Ear Speaker ..................................................................................................... 84

6.6.5 Power Down Speakerphone ..................................................................................................84

6.6.6 Power Down Line Output ...................................................................................................... 85

6.6.7 Power Down Headphone ...................................................................................................... 85

6.7 Charge Pump Frequency and Class H Configuration (Address 09h) ............................................ 85

6.7.1 Charge Pump Frequency ...................................................................................................... 85

6.7.2 Adaptive Power Adjustment .................................................................................................. 85

6.8 Output Load, Mic Bias, and MIC2 Short Detect Configuration (Address 0Ah) ............................... 86

6.8.1 VP Supply Minimum Voltage Setting ..................................................................................... 86

6.8.2 Speakerphone Light Load Mode Enable ............................................................................... 86

6.8.3 Mic Bias Output Control ........................................................................................................ 86

83

DS882F1 5

Page 6

CS42L73

6.8.4 Short Detect Automatic Mute Control .................................................................................... 86

6.9 Digital Mic and Master Clock Control (Address 0Bh) ..................................................................... 87

6.9.1 Digital Mic Shift Clock Divide Ratio ....................................................................................... 87

6.9.2 Master Clock Source Selection ............................................................................................. 87

6.9.3 Master Clock Divide Ratio ..................................................................................................... 87

6.9.4 Master Clock Disable ............................................................................................................ 87

6.10 XSP Control (Address 0Ch) ......................................................................................................... 88

6.10.1 Tristate XSP Interface ......................................................................................................... 88

6.10.2 XSP Digital Interface Format ............................................................................................... 88

6.10.3 XSP PCM Interface Mode ................................................................................................... 88

6.10.4 XSP PCM Format Bit Order ................................................................................................88

6.10.5 XSP SCLK Source Equals MCLK ....................................................................................... 88

6.11 XSP Master Mode Clocking Control (Address 0Dh) .................................................................... 89

6.11.1 XSP Master/Slave Mode ..................................................................................................... 89

6.11.2 XSP Master Mode Clock Control Dividers ........................................................................... 89

6.12 ASP Control (Address 0Eh) ......................................................................................................... 89

6.12.1 Tristate ASP Interface ......................................................................................................... 89

6.12.2 ASP Sample Rate ............................................................................................................... 90

6.12.3 ASP SCLK Source Equals MCLK ....................................................................................... 90

6.13 ASP Master Mode Clocking Control (Address 0Fh) ..................................................................... 90

6.13.1 ASP Master/Slave Mode ..................................................................................................... 90

6.13.2 ASP Master Mode Clock Control Dividers ........................................................................... 90

6.14 VSP Control (Address 10h) .......................................................................................................... 91

6.14.1 Tristate VSP Interface .................................................................................................

6.14.2 VSP Digital Interface Format ............................................................................................... 91

6.14.3 VSP PCM Interface Mode ................................................................................................... 91

6.14.4 VSP PCM Format Bit Order ................................................................................................91

6.14.5 VSP SDIN Location ............................................................................................................. 92

6.14.6 VSP SCLK Source Equals MCLK ....................................................................................... 92

6.15 VSP Master Mode Clocking Control (Address 11h) ..................................................................... 92

6.15.1 VSP Master/Slave Mode ..................................................................................................... 92

6.15.2 VSP Master Mode Clock Control Dividers ........................................................................... 92

6.16 VSP and XSP Sample Rate (Address 12h) ................................................................................. 93

6.16.1 VSP Sample Rate ............................................................................................................... 93

6.16.2 XSP Sample Rate ............................................................................................................... 93

6.17 Miscellaneous Input and Output Path Control (Address 13h) ...................................................... 94

6.17.1 Digital Swap/Mono .............................................................................................................. 94

6.17.2 Input Path Channel B=A ...................................................................................................... 94

6.17.3 PREAMP and PGA Channel B=A ....................................................................................... 94

6.17.4 PGA Soft-Ramp ................................................................................................................... 95

6.17.5 Analog Zero Cross .............................................................................................................. 95

6.17.6 Digital Soft-Ramp ................................................................................................................ 96

6.17.7 Analog Output Soft Ramp ................................................................................................... 96

6.18 ADC/Input Path Control (Address 14h) ........................................................................................ 97

6.18.1 PGA x Input Select .............................................................................................................. 97

6.18.2 Boost x ................................................................................................................................ 97

6.18.3 Invert ADCx Signal Polarity ................................................................................................. 97

6.18.4 Input Path x Digital Mute ..................................................................................................... 97

6.19 Mic PreAmp and PGA Volume Control: Channel A (Mic 1, Address 15h) and Channel B

(Mic 2, Address 16h) .......................................................................................................................... 98

6.19.1 Mic PREAMP x Volume ....................................................................................................... 98

6.19.2 PGAx Volume ...................................................................................................................... 98

6.20 Input Path x Digital Volume Control: Channel A (Address 17h) and B (Address 18h) ................. 99

6.20.1 Input Path x Digital Volume Control .................................................................................... 99

........ 91

6 DS882F1

Page 7

CS42L73

6.21 Playback Digital Control (Address 19h) ..................................................................................... 100

6.21.1 Speakerphone [A], Ear Speaker/Speakerphone Line Output [B] (SES) Playback

Channels B=A ............................................................................................................................ 100

6.21.2 Headphone/Line Output (HL) Playback Channels B=A .................................................... 100

6.21.3 Limiter Soft-Ramp Disable ................................................................................................ 100

6.21.4 Ear Speaker/Speakerphone Line Output Digital Mute ...................................................... 100

6.21.5 Speakerphone Digital Mute ...............................................................................................101

6.21.6 Headphone/Line Output (HL) x Digital Mute ..................................................................... 101

6.22 Headphone/Line Output (HL) x Digital Volume Control: Channel A (Address 1Ah) and B

(Address 1Bh) .................................................................................................................................. 101

6.22.1 Headphone/Line Output (HL) x Digital Volume Control ..................................................... 101

6.23 Speakerphone Out [A] Digital Volume Control (Address 1Ch) .................................................. 102

6.23.1 Speakerphone Out [A] Digital Volume Control .................................................................. 102

6.24 Ear Speaker/Speakerphone Line Output (ESL) [B] Digital Volume Control (Address 1Dh) ...... 102

6.24.1 Ear Speaker/Speakerphone Line Output (ESL) [B] Digital Volume Control ...................... 102

6.25 Headphone Analog Volume Control: Channel A (Address 1Eh) and B (Address 1Fh) ............. 103

6.25.1 Headphone x Analog Mute ................................................................................................ 103

6.25.2 Headphone x Analog Volume Control ............................................................................... 103

6.26 Line Output Analog Volume Control: Channel A (Address 20h) and B (Address 21h) .............. 104

6.26.1 Line Output x Analog Mute ................................................................................................ 104

6.26.2 Line Output x Analog Volume Control ............................................................................... 104

6.27 Stereo Input Path Advisory Volume (Address 22h) ................................................................... 105

6.27.1 Stereo Input Path Advisory Volume .................................................................................. 105

6.28 XSP Input Advisory Volume (Address 23h) ............................................................................... 105

6.28.1 XSP Input Advisory Volume .............................................................................................. 105

6.29 ASP Input Advisory Volume (Address 24h) ............................................................................... 106

6.29.1 ASP Input Advisory Volume .............................................................................................. 106

6.30 VSP Input Advisory Volume (Address 25h) ............................................................................... 106

6.30.1 VSP Input Advisory Volume .............................................................................................. 106

6.31 Limiter Attack Rate Headphone/Line Output (HL) (Address 26h) .............................................. 107

6.31.1 Limiter Attack Rate HL ...................................................................................................... 107

6.32 Limiter Control, Release Rate Headphone/Line Output (HL) (Address 27h) ............................. 107

6.32.1 Peak Detect and Limiter HL ..............................................................................................107

6.32.2 Peak Signal Limit All Channels HL .................................................................................... 107

6.32.3 Limiter Release Rate HL ................................................................................................... 107

6.33 Limiter Min/Max Thresholds Headphone/Line Output (HL) (Address 28h) ................................ 108

6.33.1 Limiter Maximum Threshold HL ........................................................................................ 108

6.33.2 Limiter Cushion Threshold HL ........................................................................................... 108

6.34 Limiter Attack Rate Speakerphone [A] (Address 29h) ............................................................... 108

6.34.1 Limiter Attack Rate Speakerphone [A] .............................................................................. 108

6.35 Limiter Control, Release Rate Speakerphone [A] (Address 2Ah) .............................................. 109

6.35.1 Peak Detect and Limiter Speakerphone [A] ...................................................................... 109

6.35.2 Peak Signal Limit All Channels Speakerphone ................................................................. 109

6.35.3 Limiter Release Rate Speakerphone [A] ........................................................................... 109

6.36 Limiter Min/Max Thresholds Speakerphone [A] (Address 2Bh) ................................................. 110

6.36.1 Limiter Maximum Threshold Speakerphone [A] ................................................................ 110

6.36.2 Limiter Cushion Threshold Speakerphone [A] ................................................................... 110

6.37 Limiter Attack Rate Ear Speaker/Speakerphone Line Output (ESL) [B] .................................... 111

6.37.1 Limiter Attack Rate ESL [B] ............................................................................................... 111

6.38 Limiter Control, Release Rate Ear Speaker/Speakerphone Line Output (ESL) [B]

(Address 2Dh) .................................................................................................................................. 111

6.38.1 Peak Detect and Limiter ESL [B] ....................................................................................... 111

6.38.2 Limiter Release Rate ESL [B] ............................................................................................111

6.39 Limiter Min/Max Thresholds Ear Speaker/Speakerphone Line Output (ESL) [B] ...................... 112

DS882F1 7

Page 8

CS42L73

6.39.1 Limiter Maximum Threshold ESL [B] ................................................................................. 112

6.39.2 Limiter Cushion Threshold ESL [B] ................................................................................... 112

6.40 ALC Enable and Attack Rate AB (Address 2Fh) ........................................................................ 113

6.40.1 ALC for Channels A and B (ALCx) .................................................................................... 113

6.40.2 ALC Attack Rate for Channels A and B ............................................................................. 113

6.41 ALC Release Rate AB (Address 30h) ........................................................................................ 113

6.41.1 ALC Release Rate for Channels A and B ......................................................................... 113

6.42 ALC Threshold AB (Address 31h) .............................................................................................. 114

6.42.1 ALC Maximum Threshold for Channels A and B ............................................................... 114

6.42.2 ALC Minimum Threshold for Channels A and B ................................................................ 114

6.43 Noise Gate Control AB (Address 32h) .......................................................................................115

6.43.1 Noise Gate Enable for Channels A and B (NGx) .............................................................. 115

6.43.2 Noise gate Threshold and Boost for Channels A and B .................................................... 115

6.43.3 Noise Gate Delay Timing for Channels A and B ............................................................... 115

6.44 ALC and Noise Gate Misc Control (Address 33h) ..................................................................... 116

6.44.1 ALC Ganging of Channels A and B ................................................................................... 116

6.44.2 Noise Gate Ganging of Channels A and B ........................................................................ 116

6.44.3 ALCx Soft-Ramp Disable ..................................................................................................116

6.44.4 ALCx Zero Cross Disable .................................................................................................. 116

6.45 Mixer Control (Address 34h) ..................................................................................................... 117

6.45.1 VSP Mixer Output Stereo .................................................................................................. 117

6.45.2 XSP Mixer Output Stereo .................................................................................................. 117

6.45.3 Mixer Soft-Ramp Enable ................................................................................................... 117

6.45.4 Mixer Soft-Ramp Step Size/Period .................................................................................... 117

6.46 Stereo Mixer Input Attenuation (Addresses 35h through 54h) ................................................... 118

6.46.1 Stereo Mixer Input Attenuation ..........................................................................................119

6.47 Mono Mixer Controls (Address 55h) .......................................................................................... 120

6.47.1 Speakerphone (SPK) Mixer, ASP Select .......................................................................... 120

6.47.2 Speakerphone (SPK) Mixer, XSP Select .......................................................................... 120

6.47.3 Ear Speaker/Speakerphone Line Output (ESL) Mixer, ASP Select .................................. 120

6.47.4 ESL Mixer, Auxiliary Serial Port (XSP) Select ................................................................... 120

6.48 Mono Mixer Input Attenuation (Addresses 56h through 5Dh) .................................................... 121

6.48.1 Mono Mixer Input Attenuation ........................................................................................... 121

6.49 Interrupt Mask Register 1 (Address 5Eh) ...................................................................................122

6.50 Interrupt Mask Register 2 (Address 5Fh) ...................................................................................122

6.51 Interrupt Status Register 1 (Address 60h) .................................................................................122

6.51.1 MIC2 Short Detect ............................................................................................................. 122

6.51.2 Thermal Overload Detect .................................................................................................. 122

6.51.3 Digital Mixer Overflow ....................................................................................................... 123

6.51.4 Input Path x Overflow ........................................................................................................ 123

6.52 Interrupt Status Register 2 (Address 61h) .................................................................................123

6.52.1 Voice ASRC Data Out Lock .............................................................................................. 123

6.52.2 Voice ASRC Data In Lock .................................................................................................123

6.52.3 Audio ASRC Data Out Lock .............................................................................................. 124

6.52.4 Audio ASRC Data In Lock .................................................................................................124

6.52.5 Auxiliary ASRC Data Out Lock .......................................................................................... 124

6.52.6 Auxiliary ASRC Data In Lock .............................................................................................124

6.53 Fast Mode 1 (Address 7Eh) ....................................................................................................... 125

6.53.1 Fast Mode Bits 15:8 .......................................................................................................... 125

6.54 Fast Mode 2 (Address 7Fh) ....................................................................................................... 125

6.54.1 Fast Mode Bits 7:0 ............................................................................................................ 125

7. PCB LAYOUT CONSIDERATIONS ...................................................................................................125

7.1 Power Supply ............................................................................................................................... 125

7.2 Grounding .................................................................................................................................... 125

8 DS882F1

Page 9

CS42L73

7.3 Layout With Fine-Pitch, Ball-Grid Packages ................................................................................ 125

8. PERFORMANCE DATA ..................................................................................................................... 126

8.1 Analog Input Path Attributes ........................................................................................................ 126

8.1.1 PGA Analog Volume Nonlinearity (DNL and INL) ............................................................... 126

8.2 Analog Mic/Line ADC and Digital Mic Input Path Attributes ......................................................... 127

8.2.1 Input Path Digital LPF Response ........................................................................................ 127

8.2.2 Input Path Digital HPF Response ........................................................................................ 128

8.3 Core Circuitry Attributes ............................................................................................................... 129

8.3.1 ASRC Attributes .................................................................................................................. 129

8.3.1.1 Response ................................................................................................................. 129

8.3.1.2 Group Delay ............................................................................................................. 130

8.3.1.3 Lock Time ................................................................................................................ 130

8.4 Analog Output Paths Attributes .................................................................................................... 131

8.4.1 DAC Digital LPF Response .................................................................................................131

8.4.2 DAC HPF Response ........................................................................................................... 132

8.4.3 Output Analog Volume Nonlinearity (DNL and INL) ............................................................ 132

8.4.4 Startup Times ...................................................................................................................... 133

9. PARAMETER DEFINITIONS .............................................................................................................. 134

10. PACKAGE DIMENSIONS ................................................................................................................ 135

10.1 WLCSP Package ....................................................................................................................... 135

10.2 FBGA Package .......................................................................................................................... 136

11. THERMAL CHARACTERISTICS ..................................................................................................... 137

12. ORDERING INFORMATION ............................................................................................................ 137

13. REFERENCES .................................................................................................................................. 137

14. REVISION HISTORY ........................................................................................................................ 138

LIST OF FIGURES

Figure 1.Typical Connection Diagram ....................................................................................................... 17

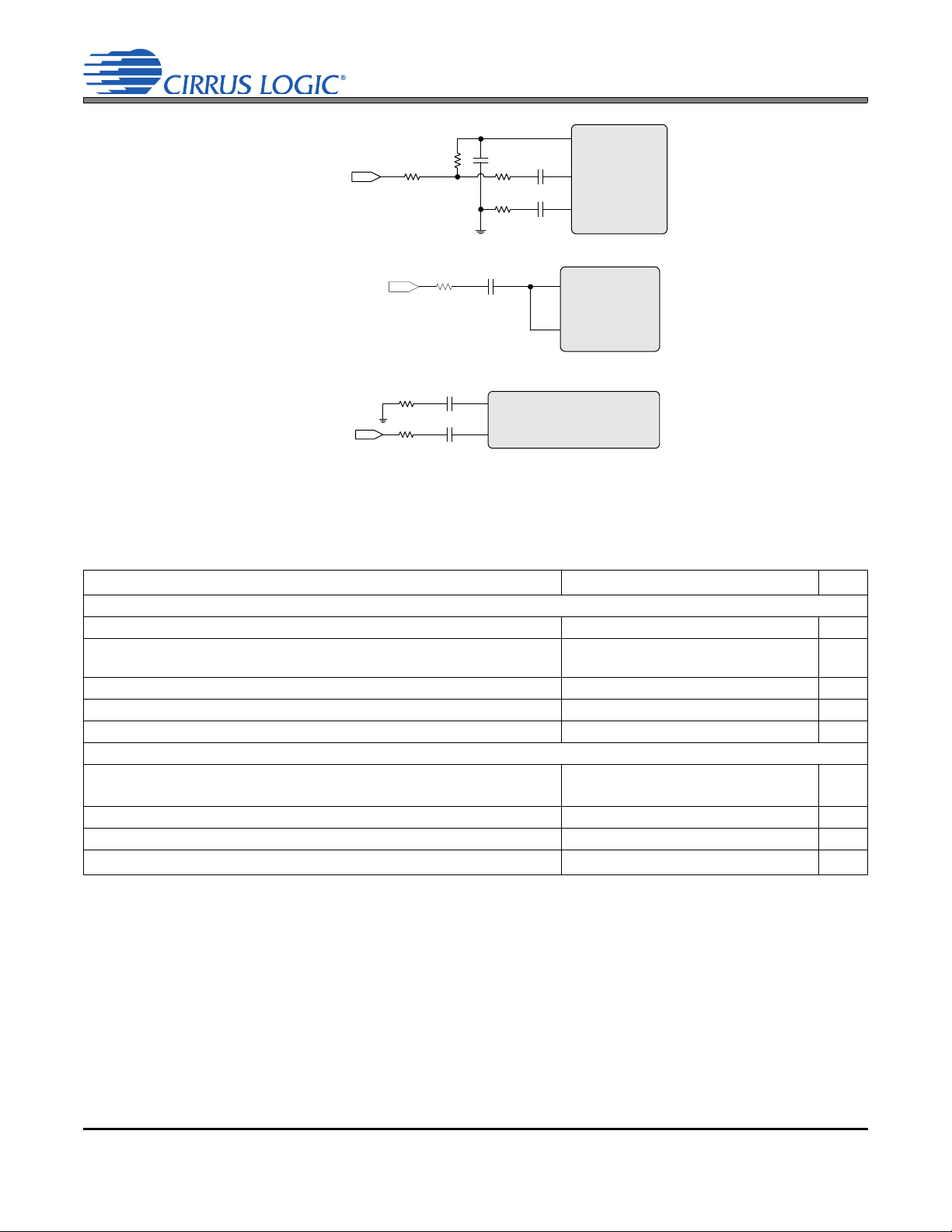

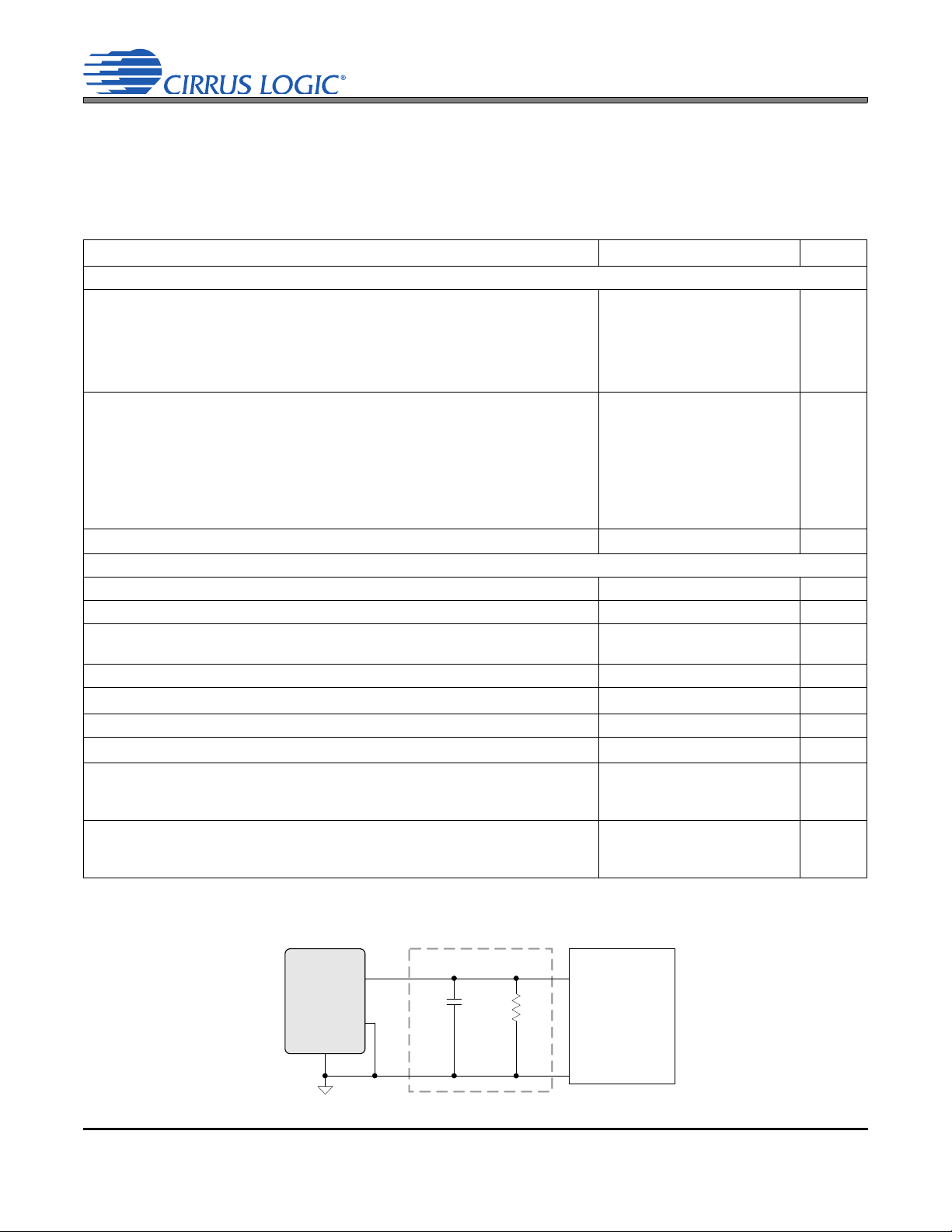

Figure 2.MICx Dynamic Range Test Configuration ................................................................................... 24

Figure 3.Analog Input CMRR Test Setup .................................................................................................. 24

Figure 4.LINEIN_REF/MICx_REF Input Voltage Test Setup .................................................................... 24

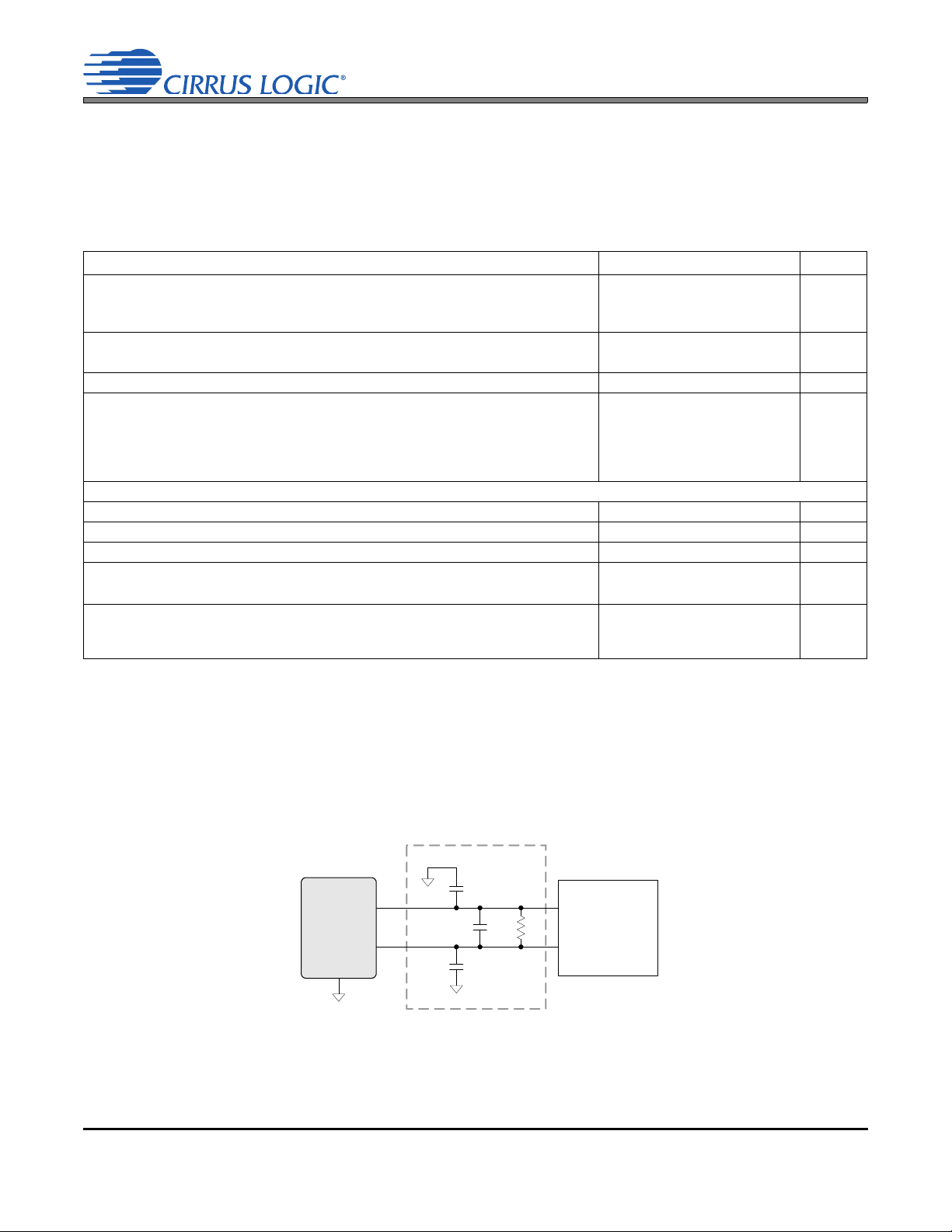

Figure 5.Headphone Output Test Configuration ....................................................................................... 28

Figure 6.Line Output Test Configuration ................................................................................................... 29

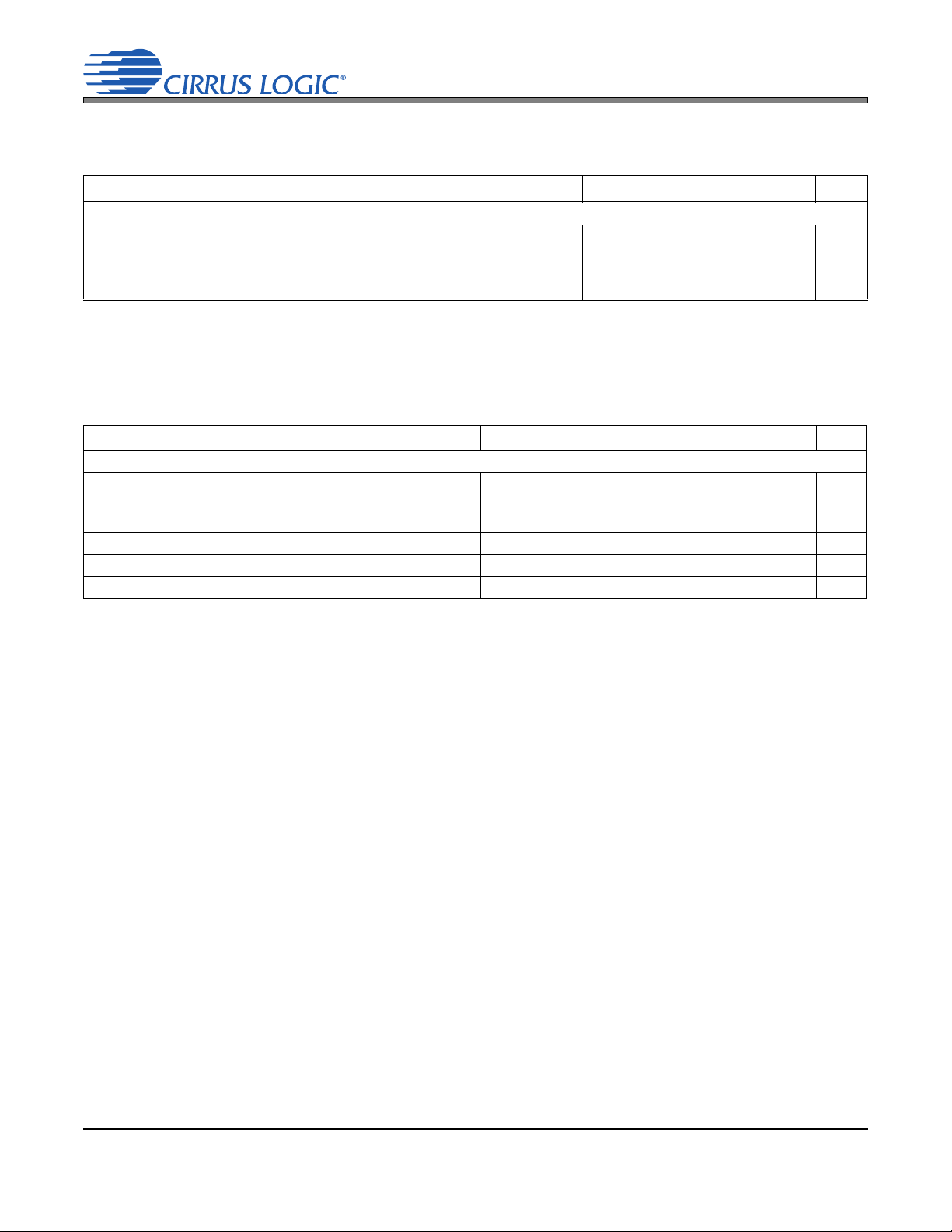

Figure 7.Ear Speaker Output Test Configuration ...................................................................................... 30

Figure 8.Speakerphone and Speakerphone Line Output Test Configuration ........................................... 32

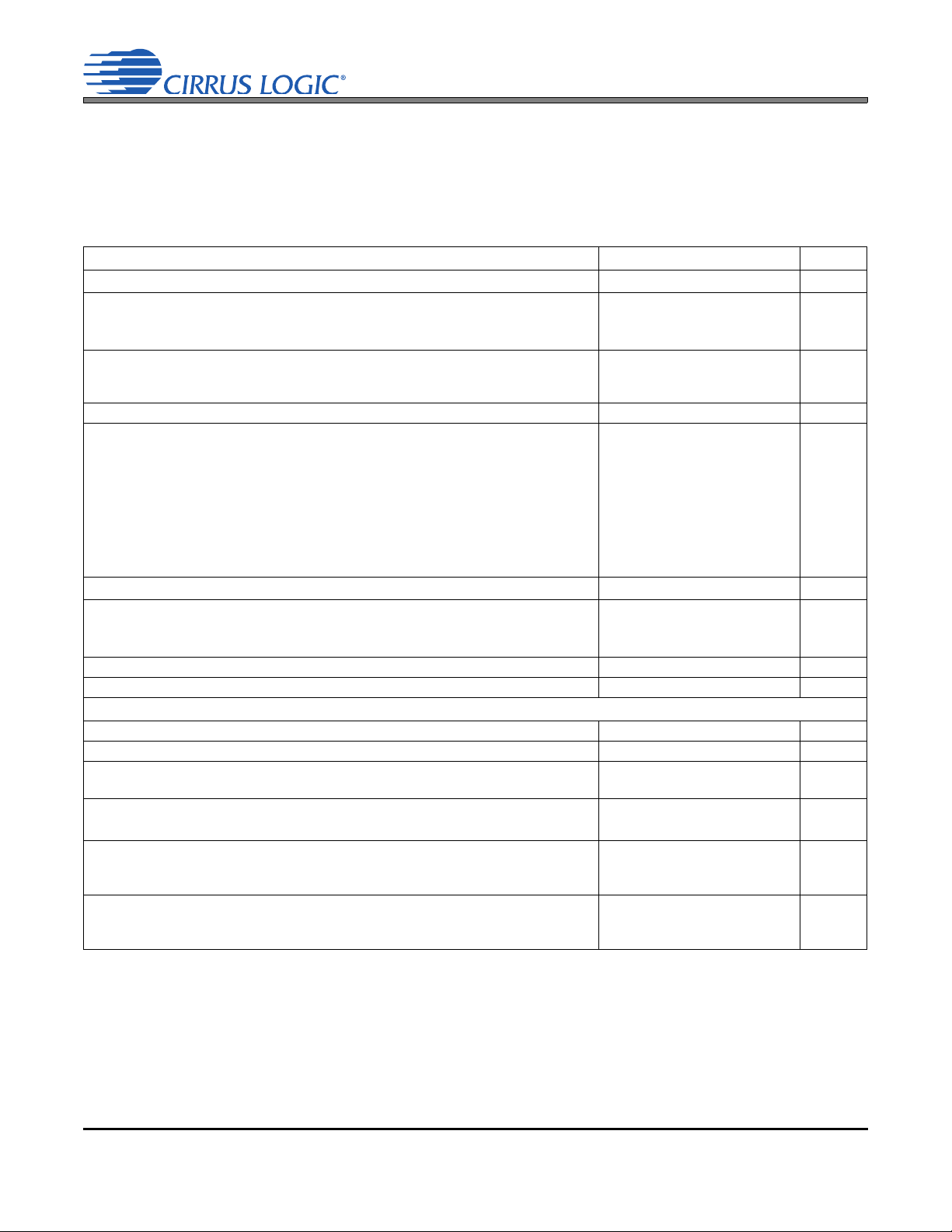

Figure 9.Power Consumption Test Configuration ..................................................................................... 34

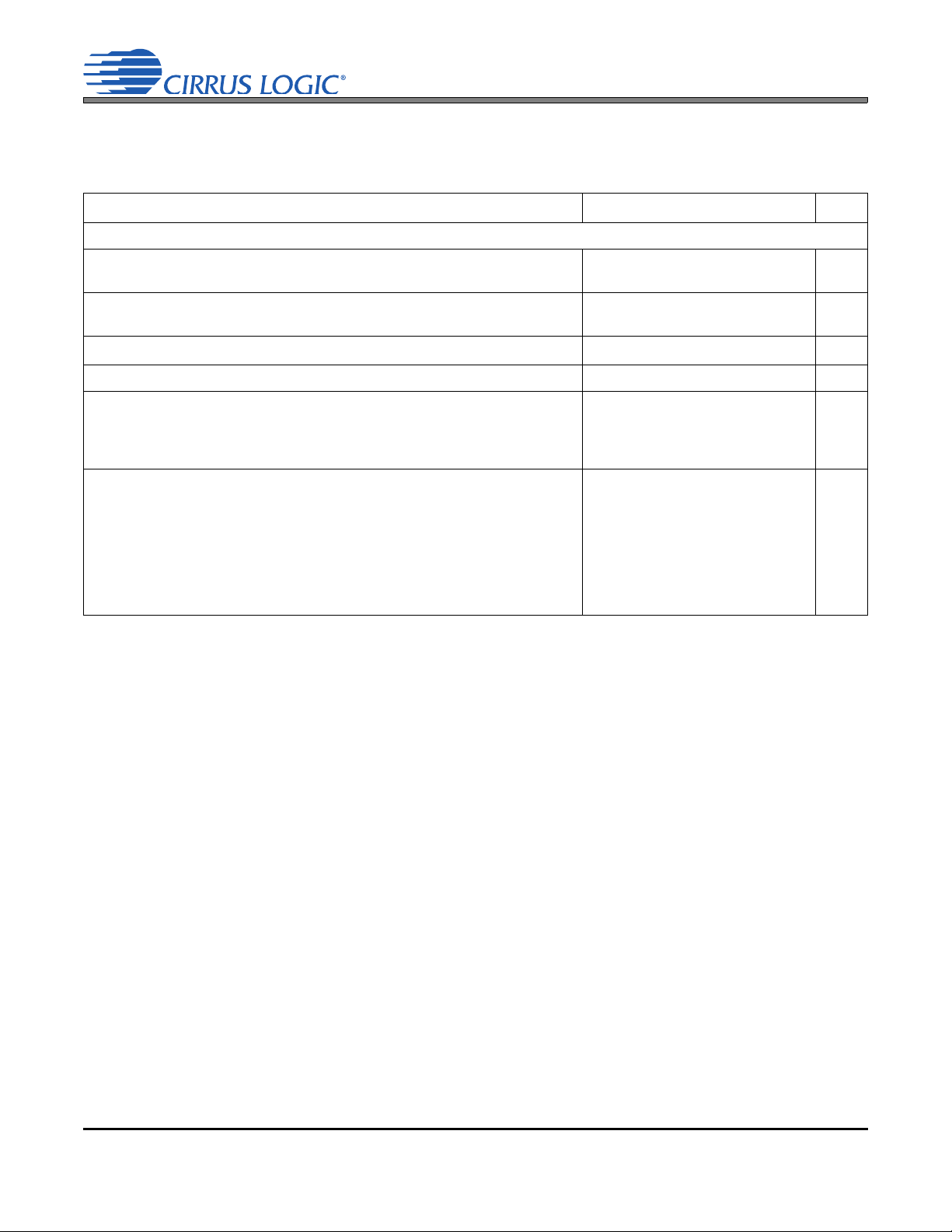

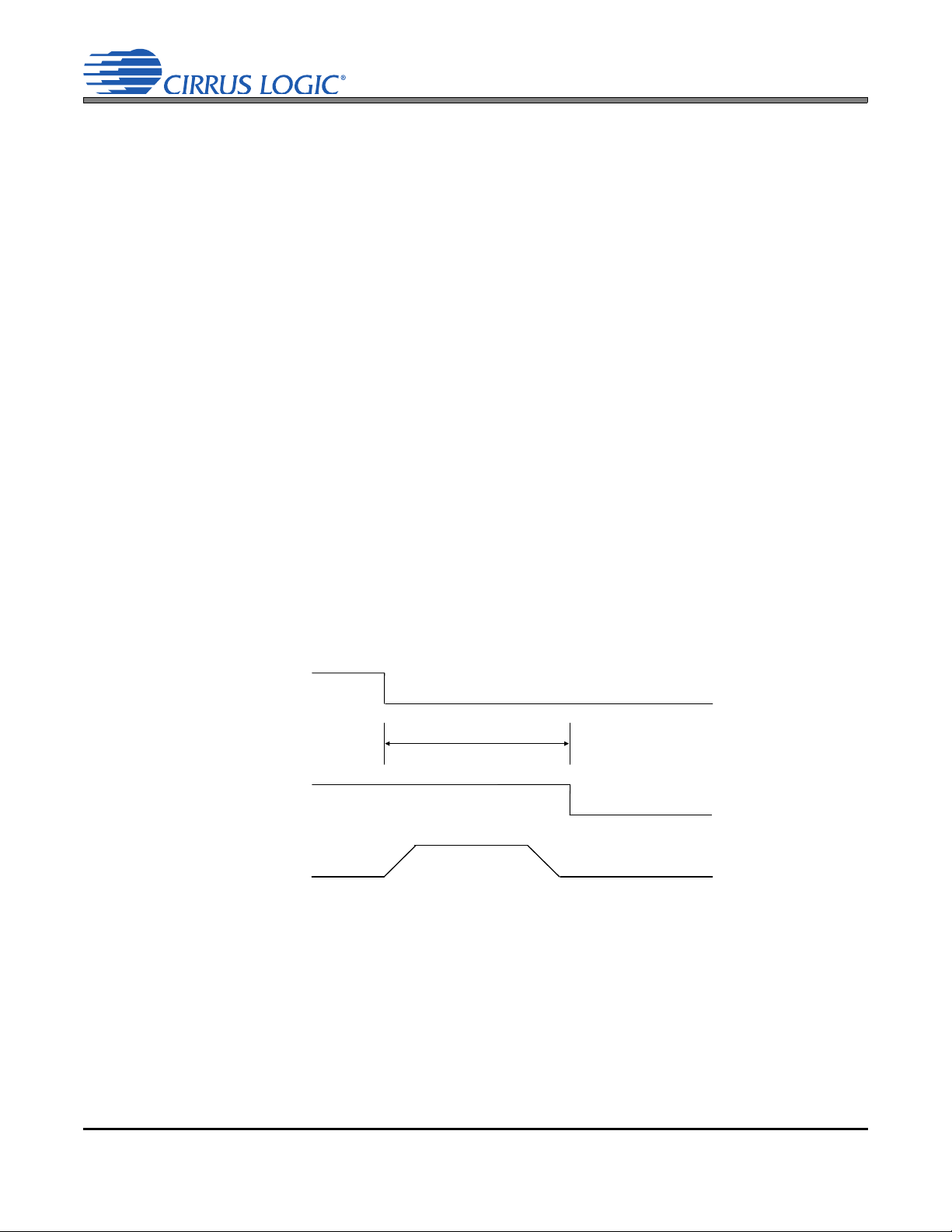

Figure 10.Power and Reset Sequencing .................................................................................................. 36

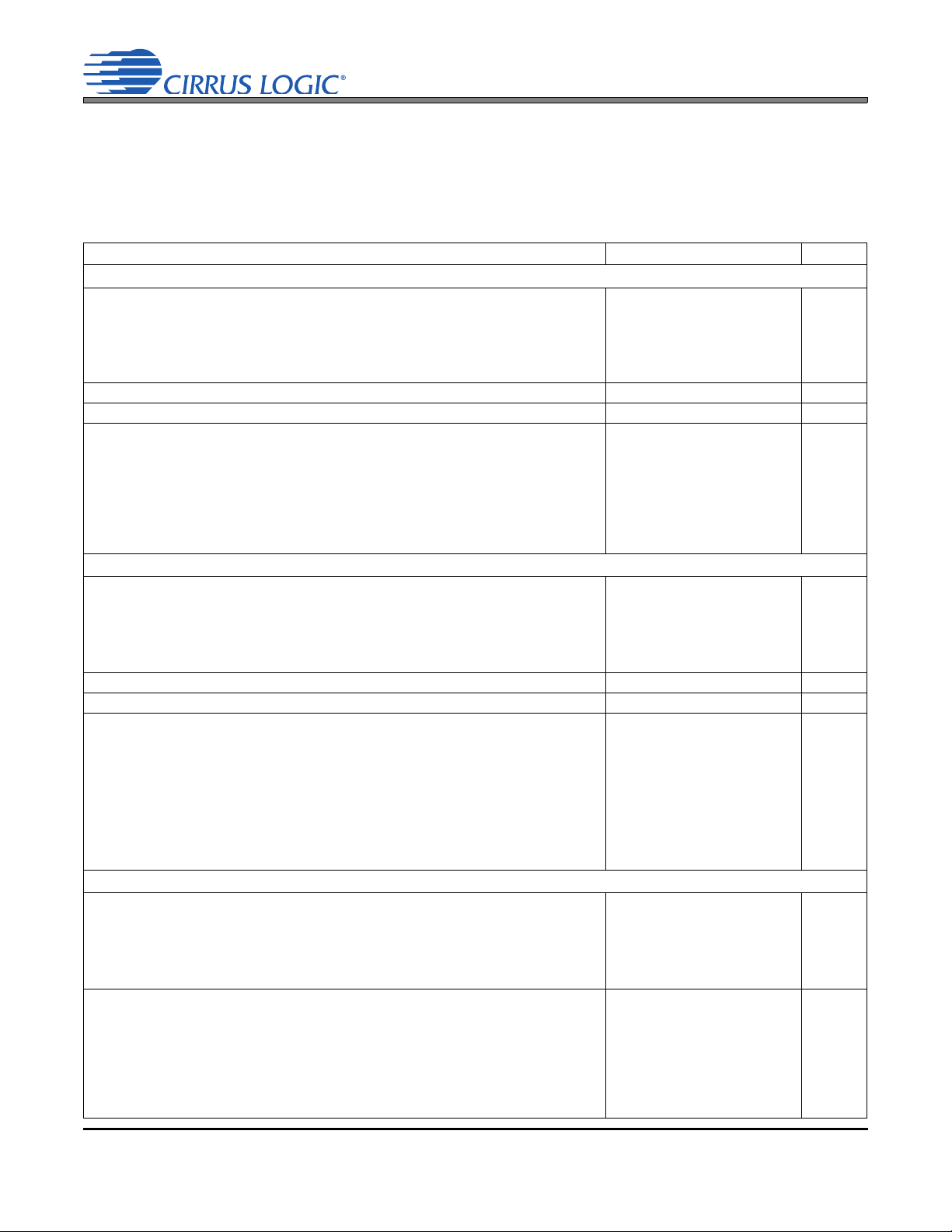

Figure 11.Digital Mic Interface Timing ....................................................................................................... 37

Figure 12.Serial Port Interface Timing—I²S Format .................................................................................. 39

Figure 13.Serial Port Interface Timing—PCM Format ..............................................................................39

Figure 14.I²C Control Port Timing ............................................................................................................. 40

Figure 15.Single-Ended Output Configuration .......................................................................................... 43

Figure 16.Pseudodifferential Output Configuration ................................................................................... 43

Figure 17.Class H Operation ..................................................................................................................... 44

Figure 18.Class H Control - Adapt-to-Volume Mode ................................................................................. 45

Figure 19.VCP_FILT Transitions ............................................................................................................... 47

Figure 20.VCP_FILT Hysteresis ............................................................................................................... 48

Figure 21.Input Power vs. Output Power .................................................................................................. 49

Figure 22.Peak Detect & Limiter ............................................................................................................... 50

Figure 23.HP Short Circuit Setup .............................................................................................................. 51

Figure 24.Line Short Circuit Setup ............................................................................................................ 51

Figure 25.Serial Port Busing when Mastering Timing ............................................................................... 52

Figure 26.Serial Port Busing When Slave Timed ...................................................................................... 52

DS882F1 9

Page 10

CS42L73

Figure 27.I²S Format ................................................................................................................................. 55

Figure 28.PCM Format—Mode 0 .............................................................................................................. 56

Figure 29.PCM Format—Mode 1 .............................................................................................................. 56

Figure 30.PCM Format—Mode 2 .............................................................................................................. 57

Figure 31.Digital Mic Interface Signaling ................................................................................................... 60

Figure 32.Digital Mixer Diagram ................................................................................................................ 62

Figure 33.Connection Diagram for Using MIC2_SDET as Headphone Detect ......................................... 69

Figure 34.Flow Diagram Showing the INT

Figure 35.Connection Diagram for Headphone Detect with Additional Short Detect ................................ 70

Figure 36.Example of Rising-Edge Sensitive, Sticky, Interrupt Status Bit Behavior ................................. 71

Figure 37.Control Port Timing, I²C Writes with Autoincrement ................................................................. 72

Figure 38.Control Port Timing, I²C Reads with Autoincrement ................................................................. 72

Figure 39.Control Port Timing, I²C Reads with Preamble and Autoincrement .......................................... 73

Figure 40.Fast Start Pop ........................................................................................................................... 74

Figure 41.Start Up Transition Diagram ..................................................................................................... 75

Figure 42.PGA DNL ................................................................................................................................ 126

Figure 43.PGA INL .................................................................................................................................. 126

Figure 44.PGA + Preamp (+10 dB) DNL ................................................................................................. 126

Figure 45.PGA + Preamp (+10 dB) INL .................................................................................................. 126

Figure 46.PGA + Preamp (+20 dB) DNL ................................................................................................. 127

Figure 47.PGA + Preamp (+20 dB) INL .................................................................................................. 127

Figure 48.Input Path LPF Frequency Response ..................................................................................... 127

Figure 49.Input Path LPF Stopband Rejection ........................................................................................ 127

Figure 50.Input Path LPF Transition Band .............................................................................................. 128

Figure 51.Input Path LPF Transition Band Detail .................................................................................... 128

Figure 52.Input Path HPF Frequency Response ....................................................................................128

Figure 53.ASRC Frequency Response ................................................................................................... 129

Figure 54.ASRC Passband Frequency Response .................................................................................. 129

Figure 55.ASRC Group Delay vs. Serial Port and Internal Sample Rates .............................................. 130

Figure 56.DAC LPF Frequency Response .............................................................................................. 131

Figure 57.DAC LPF Stopband Rejection to 1x Fs ................................................................................... 131

Figure 58.DAC LPF Stopband Rejection to 3x Fs ................................................................................... 131

Figure 59.DAC HPF Frequency Response ............................................................................................. 132

Figure 60.HPOUTx DNL (-50 to +12 dB) ................................................................................................ 132

Figure 61.HPOUTx DNL (-76 to -52 dB) ................................................................................................. 132

Figure 62.HPOUTx INL (-50 to +12 dB) .................................................................................................. 132

Figure 63.HPOUTx INL (-76 to -52 dB) ................................................................................................... 132

Figure 64.LINEOUTx DNL (-50 to +12 dB) ............................................................................................. 133

Figure 65.LINEOUTx DNL (-76 to -52 dB) .............................................................................................. 133

Figure 66.LINEOUTx INL (-50 to +12 dB) ............................................................................................... 133

Figure 67.LINEOUTx INL (-76 to -52 dB) ................................................................................................ 133

Pin State in Response to MIC2_SDET State Changes .......... 69

LIST OF TABLES

Table 1. Internal Master Clock Generation ............................................................................................... 42

Table 2. Example of Impedance in Reference Path .................................................................................. 44

Table 3. Current through VCP with Varying Short Circuits .......................................................................51

Table 4. Supported MCLK1/MCLK2 Rates for Pre-MCLK Mode .............................................................. 53

Table 5. Serial Port Rates and Master Mode Settings .............................................................................. 53

Table 6. Actual xSP_LRCK Rate/Deviation Selector for Note 3 ............................................................... 54

Table 7. Supported Serial Port Formats .................................................................................................... 54

Table 8. Input Path Source Select and Digital Power States .................................................................... 59

Table 9. Digital Mic Interface Power States .............................................................................................. 60

Table 10. Digital Microphone Interface Clock Generation ......................................................................... 61

10 DS882F1

Page 11

CS42L73

Table 11. Digital Mixer Soft Ramp Rates .................................................................................................. 63

Table 12. Digital Mixer Nonclipping Attenuation Settings ......................................................................... 64

Table 13. Start Up Times .......................................................................................................................... 73

Table 14. Start Up Transition Values ........................................................................................................ 75

Table 15. ASRC Lock Times ................................................................................................................... 130

Table 16. Analog Output Startup Times .................................................................................................. 133

Table 17. WLCSP Package Dimensions ................................................................................................. 135

Table 18. FBGA Package Dimensions .................................................................................................... 136

DS882F1 11

Page 12

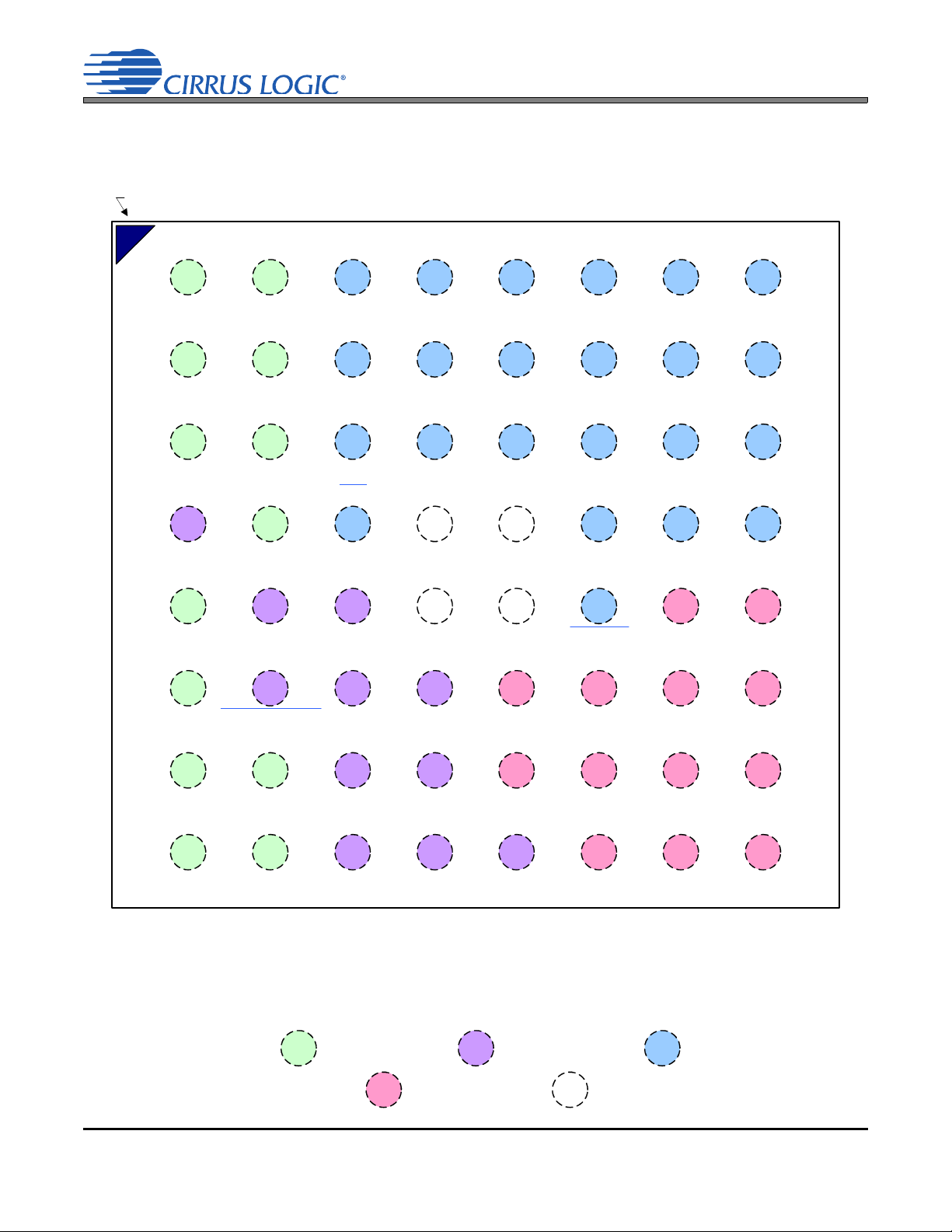

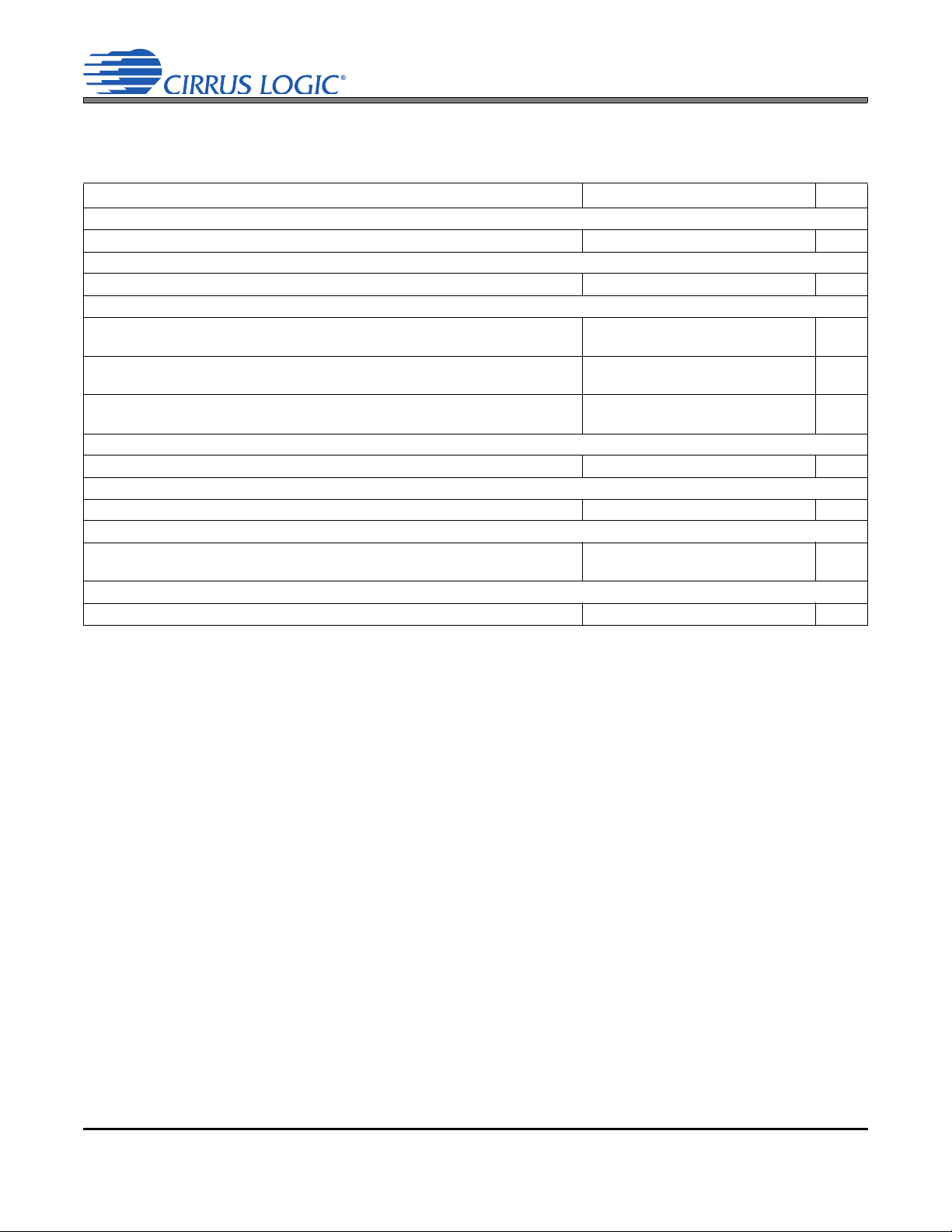

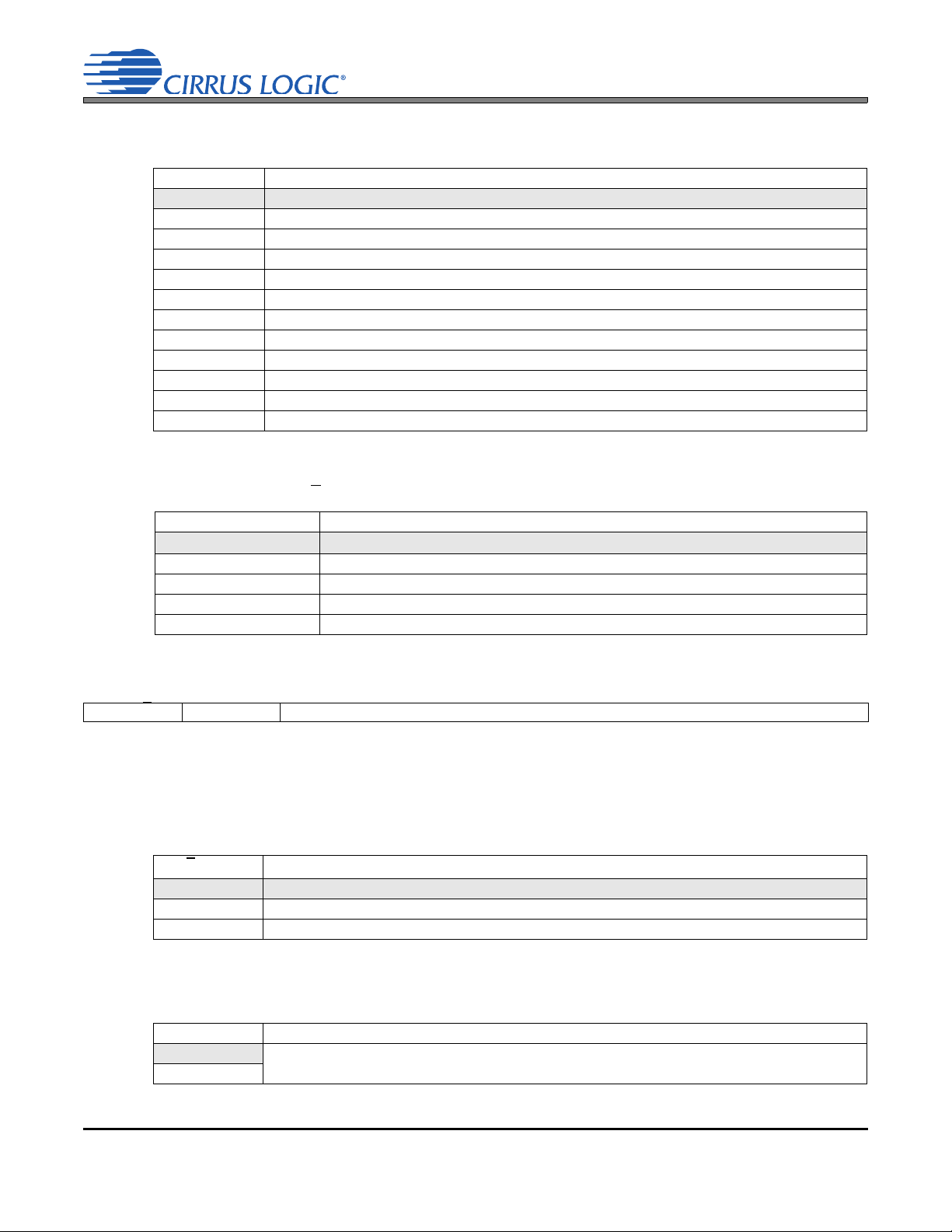

1. PACKAGE PIN/BALL ASSIGNMENTS AND CONFIGURATIONS

Top-Down

(Though Package)

View

H5

SPK_VQ

XSP_SDIN

DGND

B5

LINEINA

A5

MIC1

H6

HPOUTA

-VCP_FILT

XSP_SCLK

B6

ASP_LRCK

A6

XSP_SDOUT

H1 H2

B1 B2

A1 A2

H3 H4

VA

EAROUT-

B3 B4

LINEIN_REF

A3

LINEINB

A4

H7 H8

VL

B7

ASP_SDOUT

B8

A7

MCLK1

A8

ASP_SDIN

VD_FILT

Ball A1 Location Indicator

VP HPOUTB

DMIC_SCLK

PGND

C5

MIC2

C6

XSP_LRCK

DMIC_SD

C1 C2 C3 C4

MIC1_REF

VSP_SDOUT

C7

ASP_SCLK

C8

VSP_SDIN

SCL

D5

MICB_FILT

D6

THERM

D1 D2 D3 D4

MIC2_REF

VSP_SCLK

D7

MCLK2

D8

VSP_LRCK

E5

ANA_VQ

E6

THERM

THERM

E1 E2 E3 E4

MIC2_BIAS

VCP

E7 E8

FLYP

F5

FILT+

F6

LINEOUTB

SPKLINEO+

F1 F2 F3 F4

+VCP_FILT

F7

LINEOUTA

F8

FLYC

SPKLINEO-

G5

AGND

G6

LINEO_REF

SPKOUT+

G1 G2 G3 G4

EAROUT+

CPGND

G7

HPOUT_REF

G8

FLYN

SPKOUT-

SDA

INT

THERM

RESET

MIC2_SDET

MIC1_BIAS

VA I/O VL I/OVP I/O

VCP I/O Ground

1.1 64-Ball Wafer-Level Chip Scale Package (WLCSP)

CS42L73

12 DS882F1

Page 13

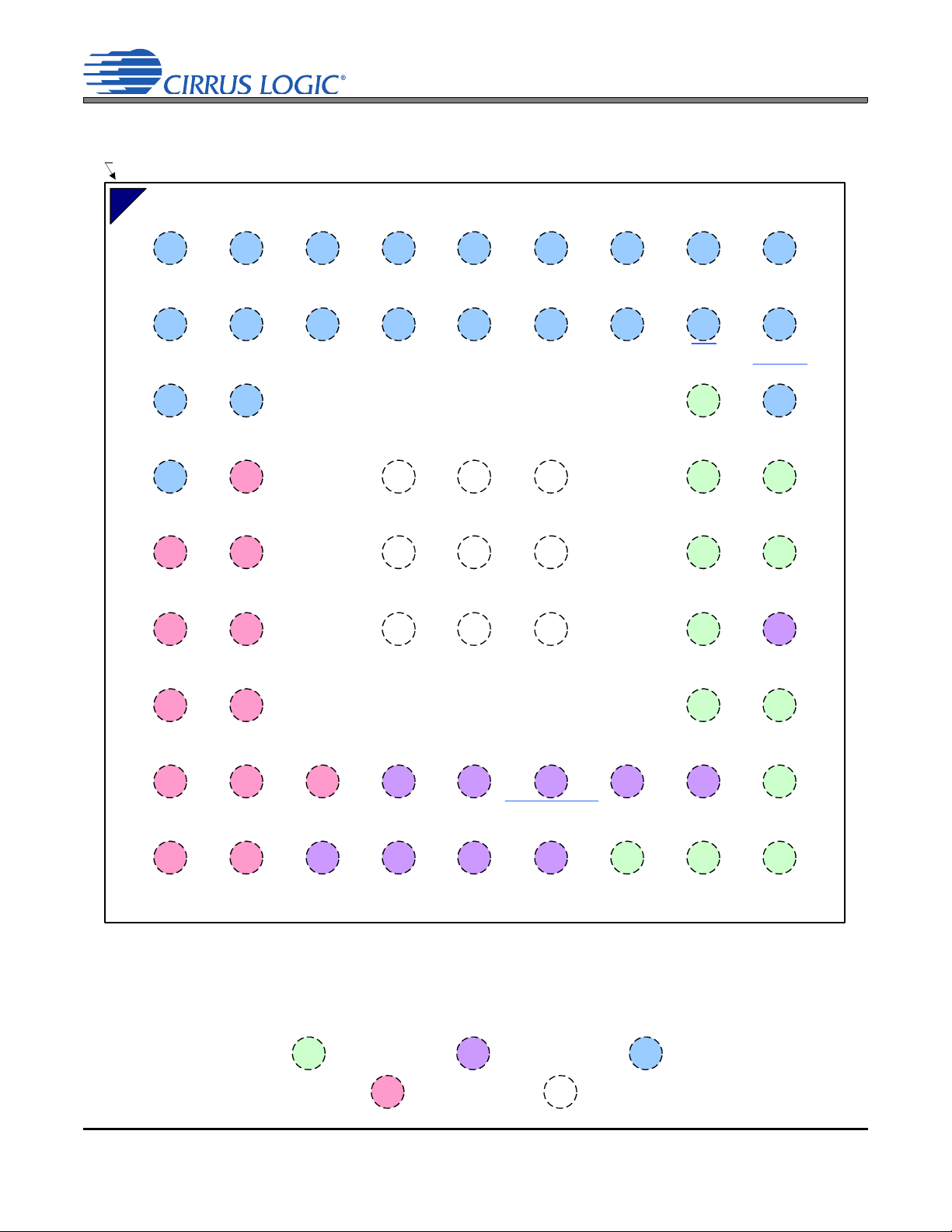

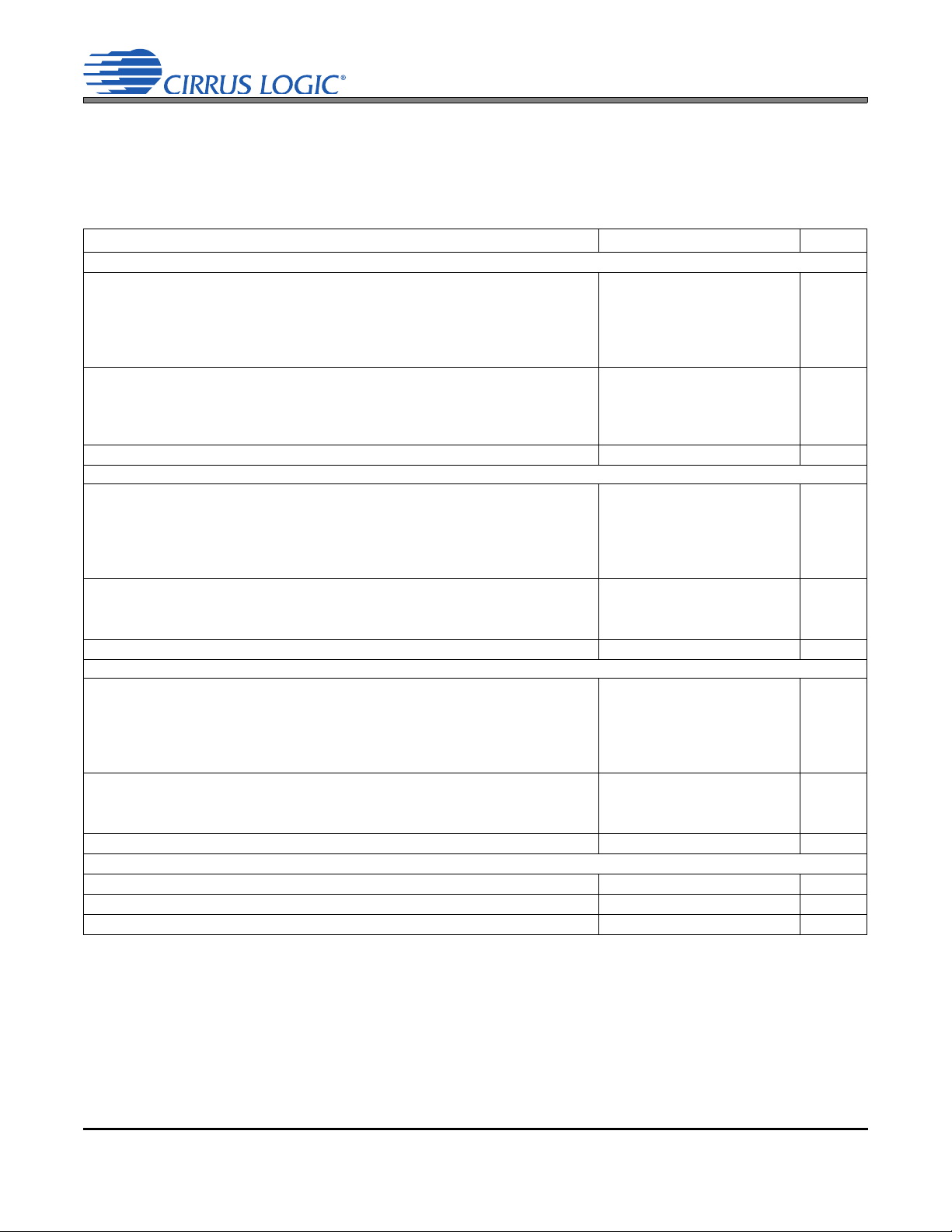

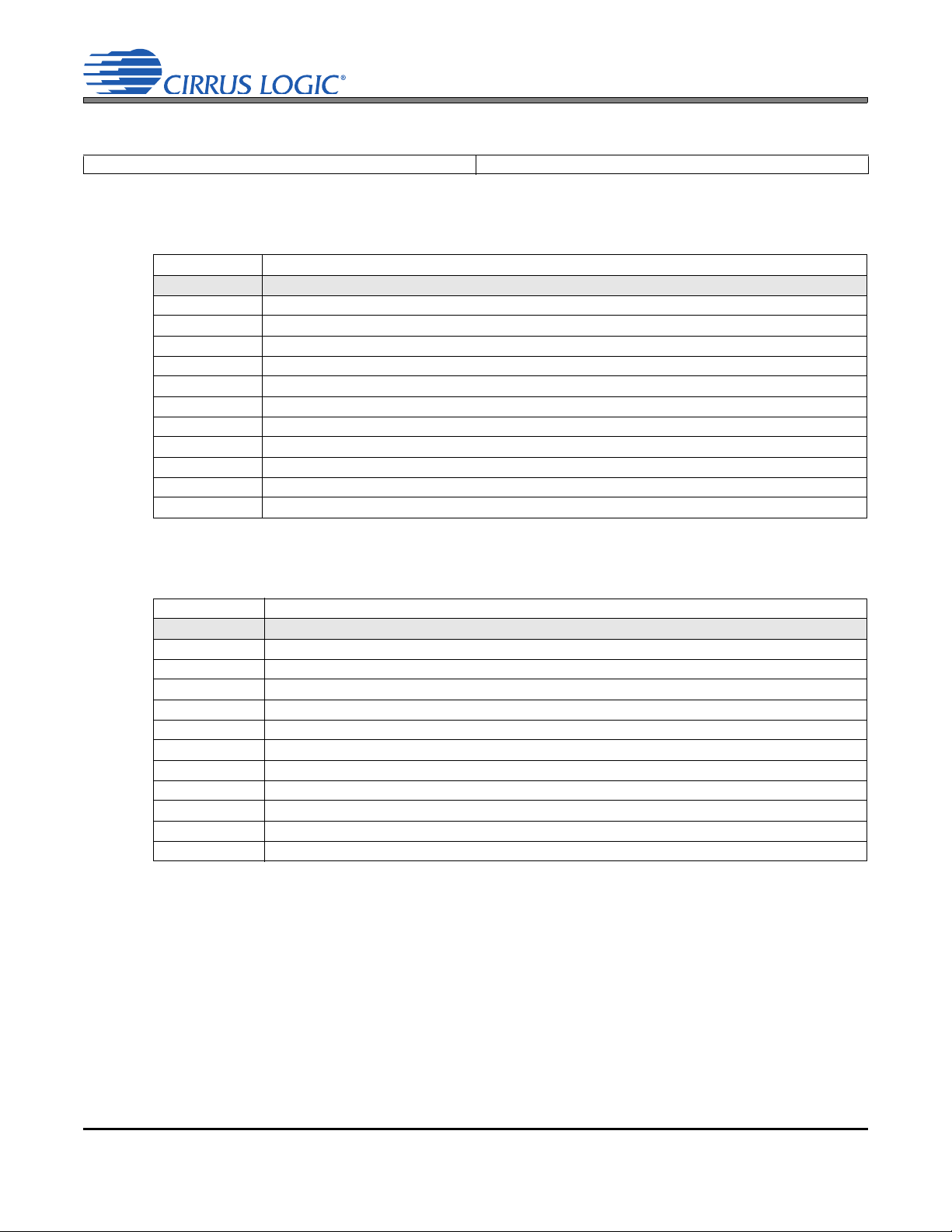

1.2 65-Ball Fine-Pitch Ball Grid Array (FBGA) Package

Top-Down

(Though Package)

View

H5

SPKLINEO-

ASP_LRCK

DMIC_SD

B5

VL

A5

VSP_SDIN

H6

MIC1_BIAS

MIC2_BIAS

ASP_SDOUT

B6

XSP_SDIN

A6

ASP_SCLK

H1 H2

B1 B2

A1 A2

H3 H4

-VCP_FILT

HPOUT_REF

B3 B4

VD_FILT

A3

MCLK2

A4

H7 H8

DMIC_SCLK

B7

XSP_SDOUT

B8

A7

XSP_SCLK

A8

XSP_LRCK

Ball A1 Location Indicator

SPKLINEO+

MCLK1

LINEO_REF

VSP_SDOUT

C1 C2

VSP_SCLK

C8

LINEIN_REF

D5

VSP_LRCK

D6

GND

D1 D2 D4

VCP GND

D8

LINEINA

E5

FLYP

E6

GND

GND

E1 E2 E4

+VCP_FILT

E8

MIC2_REF

F5

FLYC

F6

GND

GND

F1 F2 F4

GND

F8

MIC1_REF

FLYN

G1 G2

LINEOUTA

G8

MIC1

VA I/O VL I/OVP I/O

ASP_SDIN

GND

GND

LINEOUTB

SCL

FILT+

H9

B9

A9

SDA

C9

D9

LINEINB

E9

MIC2

F9

MICB_FILT

G9

ANA_VQ

J5

VP

J6

EAROUT-

EAROUT+

J1 J2 J3 J4

HPOUTA

HPOUTB

J7 J8

SPKOUT+ SPKOUT-

SPK_VQ VA

J9

INT

RESET

MIC2_SDET

VCP I/O Ground

CS42L73

DS882F1 13

Page 14

1.3 Pin/Ball Descriptions

Name Location Description

WLCSP FBGA

MCLK1

MCLK2

RESET

SCL C3 A9 Serial Control Port Clock (Input)

A6

D6

B3B2High Speed Clock (Input). Potential clock sources for the converters and the device core. Clock

source for optional serial port mastering.

E6 C9 Reset (Input). The device enters a low-power mode when this pin is driven low.

. Serial clock for the I²C control interfaces.

CS42L73

SDA A3 B9 Serial Control Data (Input/Output)

INT

LINEINA

LINEINB

LINEIN_REF A2 C8

MIC1

MIC2

MIC1_REF

MIC2_REF

MIC1_BIAS

MIC2_BIAS

D3 B8 Interrupt Request (Output). Open-drain active low interrupt request output.

A1

B2

D8D9Analog Line Inputs, A and B (LEFT and RIGHT) (Input)

Analog Input Characteristics specification table.

Analog Line Input Pseudodifferential Reference (Input)

input buffers LINEINA and LINEINB.

B1

C1

C2

D2

E3

E2

G8E9Microphone Inputs 1 and 2 (Input)

inputs. The full-scale level is specified in the Analog Input Characteristics specification table.

F8E8Microphone Inputs 1 and 2 Pseudodifferential References (Input)

microphone inputs MIC1 and MIC2.

H7

Microphone Bias Voltages 1 and 2 (Output)

H8

Microphone 2 Short Detect (Input)

MIC2_SDET

F2 H6

interrupts that represent the pressing and releasing of a button that shorts the headset

. SDA is the bidirectional data pin for the I²C control interface.

. The full-scale level is specified in the

. Ground reference for the analog line

. The handset (MIC1) and headset (MIC2) microphone signal

. Ground references for the

. Bias voltage for the microphones MIC1 and MIC2.

. Transitions on this input can be configured to cause

microphone to ground.

DMIC_SCLK B3 B7 Digital Mic Serial Clock (Output). The high-speed clock output to the digital microphone(s).

DMIC_SD

XSP_SCLK

XSP_LRCK C5 A7

C4 A8

A4 A6

Digital Mic Serial Data (Input)

Auxiliary Serial Port (XSP), Serial Clock (Input/Output)

XSP, Left/Right Clock (Input/Output)

. The serialized data input from the digital microphone(s).

. Serial shift clock for the interface.

. Identifies the start of each serialized PCM data word. When

the I²S interface format is selected, this signal also indicates which channel, Left or Right, is

currently active on the serial PCM audio data lines.

XSP_SDIN A5 B5 XSP, Data Input (Input)

XSP_SDOUT B4 B6 XSP, Data Output (Output)

. Input for two’s complement serial PCM audio data.

. Output for two’s complement serial PCM audio data.

ASP_SCLK C6 B4 Audio Serial Port (ASP), Serial Clock (Input/Output)

ASP_LRCK B5 A5

ASP_SDIN A7 A3 ASP, Data Input (Input)

ASP, Left/Right Clock (Input/Output)

indicates which channel, Left or Right, is currently active on the serial PCM audio data lines.

. Input for two’s complement serial PCM audio data.

ASP_SDOUT B6 A4 ASP, Data Output (Output)

. Output for two’s complement serial PCM audio data.

. Identifies the start of each serialized PCM data word and

VSP_SCLK D7 C2 Voice Serial Port (VSP), Serial Clock (Input/Output)

Voice Serial Port, Left/Right Clock (Input/Output)

VSP_LRCK D8 D1

data word. When the I²S interface format is selected, this signal also indicates which channel, Left

. Serial shift clock for the interface.

. Serial shift clock for the interface.

. Identifies the start of each serialized PCM

or Right, is currently active on the serial PCM audio data lines.

VSP_SDIN C8 B1 VSP, Data Input (Input)

VSP_SDOUT C7 C1 VSP, Data Output (Output)

HPOUTA

HPOUTB

HPOUT_REF G6 H2

H7

H6

J1J2Headphone Audio Output (Output)

Characteristics specification table.

Pseudodifferential Headphone Output Reference (Input)

amplifiers.

. Input for two’s complement serial PCM audio data.

. Output for two’s complement serial PCM audio data.

. The full-scale output level is specified in the HP Output

. Ground reference for the headphone

14 DS882F1

Page 15

Name Location Description

WLCSP FBGA

LINEOUTA

LINEOUTB

F6

F5

G2F2Line Audio Output (Output). The full-scale output level is specified in the Line Output

Characteristics specification table.

LINEO_REF G5 H3 Pseudodifferential Line Output Reference (Input)

EAROUT+

EAROUT-

SPKOUT+

SPKOUT-

SPKLINEO+

SPKLINEO-

VA H1 J9 Analog Power (Input)

VP

G2

J8J7Ear Speaker Audio Output (Output)

H2

G4

J4J6Speakerphone Audio Output (Output)

G3

F4

H4H5Speakerphone Audio Line Output (Output)

F3

H4 J5

Output Characteristics specification table.

Speakerphone Output Characteristics specification table.

Speakerphone Line Output Characteristics specification table.

. Power supply for the internal analog section.

Speakerphone Power (Input)

generators.

VCP E7 D2 Step-down Charge Pump Power (Input)

VL B7 A1

+VCP_FILT F7 E2

-VCP_FILT

FLYP

H8 H1

E8 E1

FLYC F8 F1

FLYN G8 G1

VD_FILT B8 A2

Digital Interface/Core Power (Input)

port, and digital mic interface. Power supply for the digital core logic step-down regulator.

Step-down Charge Pump Filter Connection (Output)

pump that provides the positive rail for the headphone and line amplifiers.

Inverting Charge Pump Filter Connection (Output)

pump that provides the negative rail for the headphone and line amplifiers.

Charge Pump Cap Positive Node (Output)

step-down charge pump’s flying capacitor.

Charge Pump Cap Common Node (Output)

amplifiers’ step-down and inverting charge pumps’ flying capacitors.

Charge Pump Cap Negative Node (Output)

amplifiers’ inverting charge pump’s flying capacitor.

Regulator Filter Connection (Output)

that provides the low voltage power to the digital section.

ANA_VQ E1 G9 Quiescent Voltage, Analog (Output)

. The full-scale output level is specified in the Ear Speaker

. The full-scale output level is specified in the

. The full-scale output level is specified in the

. Power supply for the speakerphone output amplifier and mic bias

. Power supply for the step-down charge pump.

. Power Supply for the serial PCM audio ports, I²C control

. Positive node for the headphone and line amplifiers’

. Common positive node for the headphone and line

. Negative node for the headphone and line

. Power supply filter connection for the step-down regulator

. Filter connection for the internal VA quiescent voltage.

CS42L73

. Ground reference for the line amplifiers.

. Power supply from the step-down charge

. Power supply from the inverting charge

SPK_VQ H5 J3 Quiescent Voltage, Speaker (Output)

FILT+ F1 H9 Positive Voltage Reference (Output)

MICB_FILT D1 F9

AGND G1 N/A Analog Ground (Input)

PGND H3 N/A

CPGND G7 N/A

DGND A8 N/A Digital Ground (Input)

D4, D5,

D6, E4,

GND N/A

E5, E6,

F4, F5,

THERM

D4, D5,

E4, E5

NC - -

Microphone Bias Source Voltage Filter (Output)

voltage used for the MICx_BIAS outputs.

. Ground reference for the internal analog section.

Speakerphone Ground (Input)

output amplifiers. Connect to ground plane(s) on board to conduct heat away from the part.

Charge Pump Ground (Input)

charge pump.

. Ground reference for the internal digital section.

Ground

. Ground reference for internal analog (AGND), speakerphone and speakerphone line

output amplifiers (PGND), internal headphone and line amplifiers (CPGND), and the internal

digital section (DGND). These balls also provide thermal relief for the device. Connect to the

Ground plane of the circuit board.

F6

Thermal Relief Balls

N/A

are not electrically connected to the device.

No Connect. No connection is required for these pins.

. Connect to the Ground plane of the circuit board. The Thermal Relief Balls

. Filter connection for the internal VP quiescent voltage.

. Positive reference voltage for the internal sampling circuits.

. Filter connection for the internal quiescent

. Ground reference for the speakerphone and speakerphone line

. Ground reference for the internal headphone and line amplifiers

DS882F1 15

Page 16

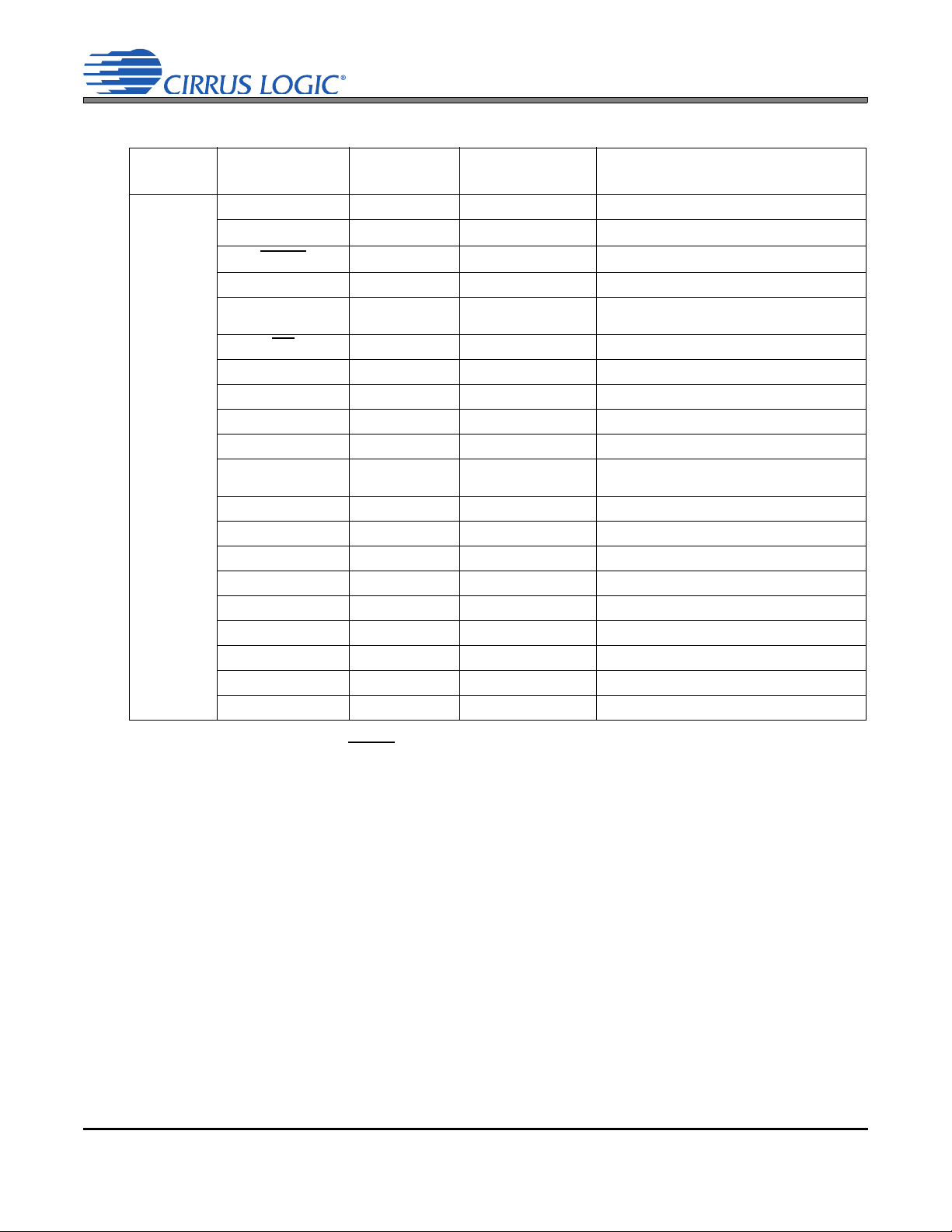

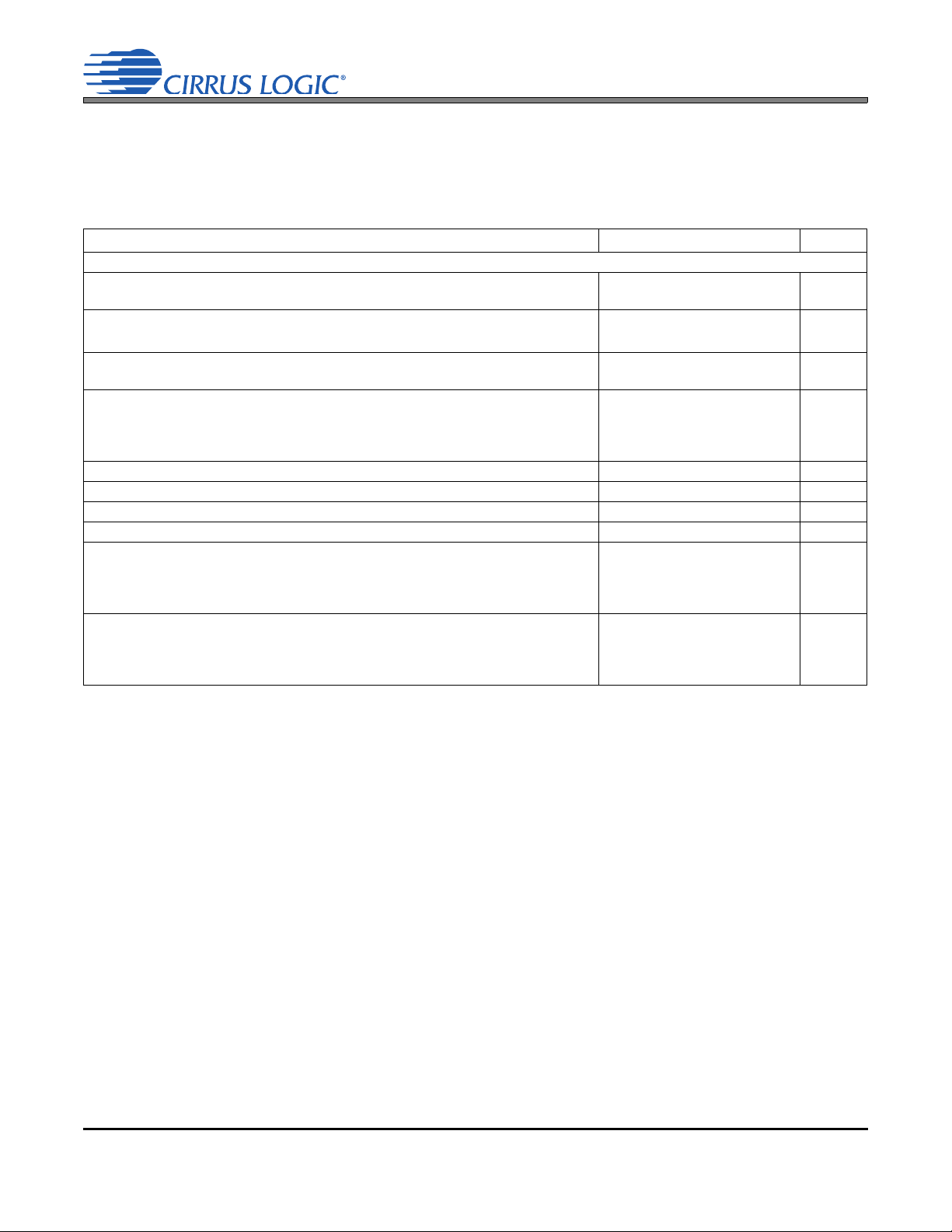

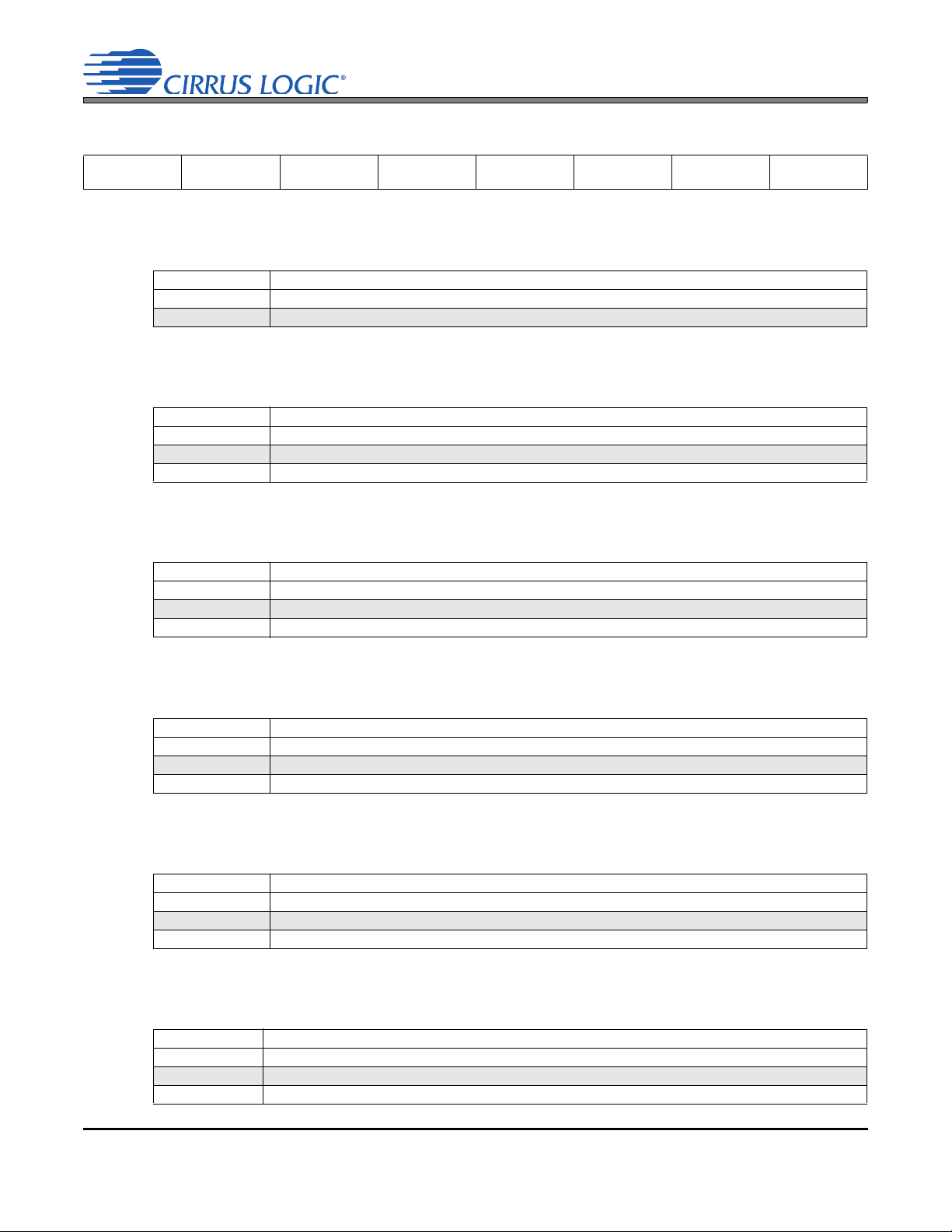

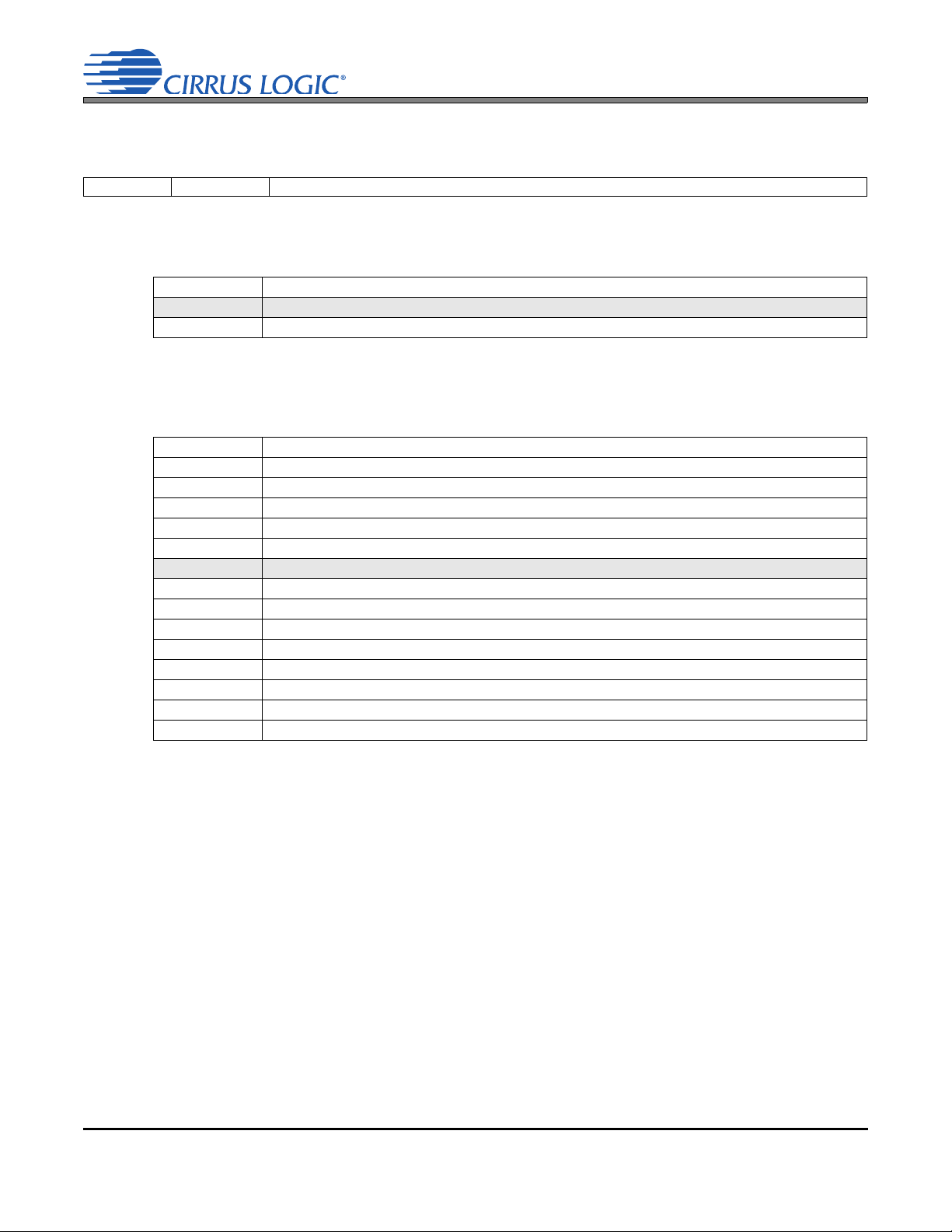

1.4 Digital Pin/Ball I/O Configurations

CS42L73

Power

Supply I/O Name Direction

VL

MCLK1 Input Weak Pull-down

MCLK2

RESET

Input Weak Pull-down

Input -

SCL Input -

SDA Input/Output -

INT Output Weak Pull-up

XSP_SCLK Input/Output Weak Pull-down

XSP_LRCK Input/Output Weak Pull-down

XSP_SDIN Input Weak Pull-down

XSP_SDOUT Output Weak Pull-down

ASP_SCLK Input/Output Weak Pull-down

ASP_LRCK Input/Output Weak Pull-down

ASP_SDIN Input Weak Pull-down

ASP_SDOUT Output Weak Pull-down

VSP_SCLK Input/Output Weak Pull-down

VSP_LRCK Input/Output Weak Pull-down

VSP_SDIN Input Weak Pull-down

VSP_SDOUT Output Weak Pull-down

DMIC_SCLK Output -

DMIC_SD Input Weak Pull-down

Internal

Connections Configuration

Hysteresis on CMOS Input

Hysteresis on CMOS Input

Hysteresis on CMOS Input

Hysteresis on CMOS Input

Hysteresis on CMOS Input/

CMOS Open-drain Output

CMOS Open-drain Output

Hysteresis on CMOS Input/CMOS Output

Hysteresis on CMOS Input/CMOS Output

Hysteresis on CMOS Input

Tristateable CMOS Output

Hysteresis on CMOS Input/

CMOS Output

Hysteresis on CMOS Input/CMOS Output

Hysteresis on CMOS Input

Tristateable CMOS Output

Hysteresis on CMOS Input/CMOS Output

Hysteresis on CMOS Input/CMOS Output

Hysteresis on CMOS Input

Tristateable CMOS Output

CMOS Output

Hysteresis on CMOS Input

Notes:

• All outputs are disabled when RESET is active.

• Internal weak pull up/down minimum and typical resistances are 550 k and 1 M

• Typical hysteresis is 500 mV within the 650 mV to 1.15 V window.

• The xSP_SCLK, xSP_LRCK, and xSP_SDOUT (x = X, A, or V) outputs may be disabled via register controls as

described in sections “High-impedance Mode” on page 52 and “Master and Slave Timing” on page 52.

• Refer to specification table “Digital Interface Specifications and Characteristics” on page 35 for details on the digital

I/O DC characteristics (output voltages/load-capacity, input switching threshold voltages, etc.). Inputs without integrated pull-ups/downs must not be left floating. All inputs must be driven or pulled (internally and/or externally) to a

valid high or low level, as defined in the specification table.

• Refer to specification tables “Switching Specifications—Serial Ports—I²S Format” on page 38 on page 47, “Switch-

ing Specifications—Serial Ports—PCM Format” on page 39, and “Switching Specifications—Control Port” on

page 40 for digital I/O AC characteristics (timing specifications).

• I/O voltage levels must not exceed the I/O’s corresponding power supply voltage. I/O voltage levels must not exceed

the voltage listed in “Absolute Maximum Ratings” on page 20.

16 DS882F1

Page 17

2. TYPICAL CONNECTION DIAGRAM

Note 13

Optional

Bias Res.

Note 9

Note 4

DGND

VL

SCL

SDA

R

P

ASP_LRCK

Applicati ons

Processor

ASP_SCLK

ASP_SDIN

ASP_SDOUT

CS42L73

MIC2_B IAS