Page 1

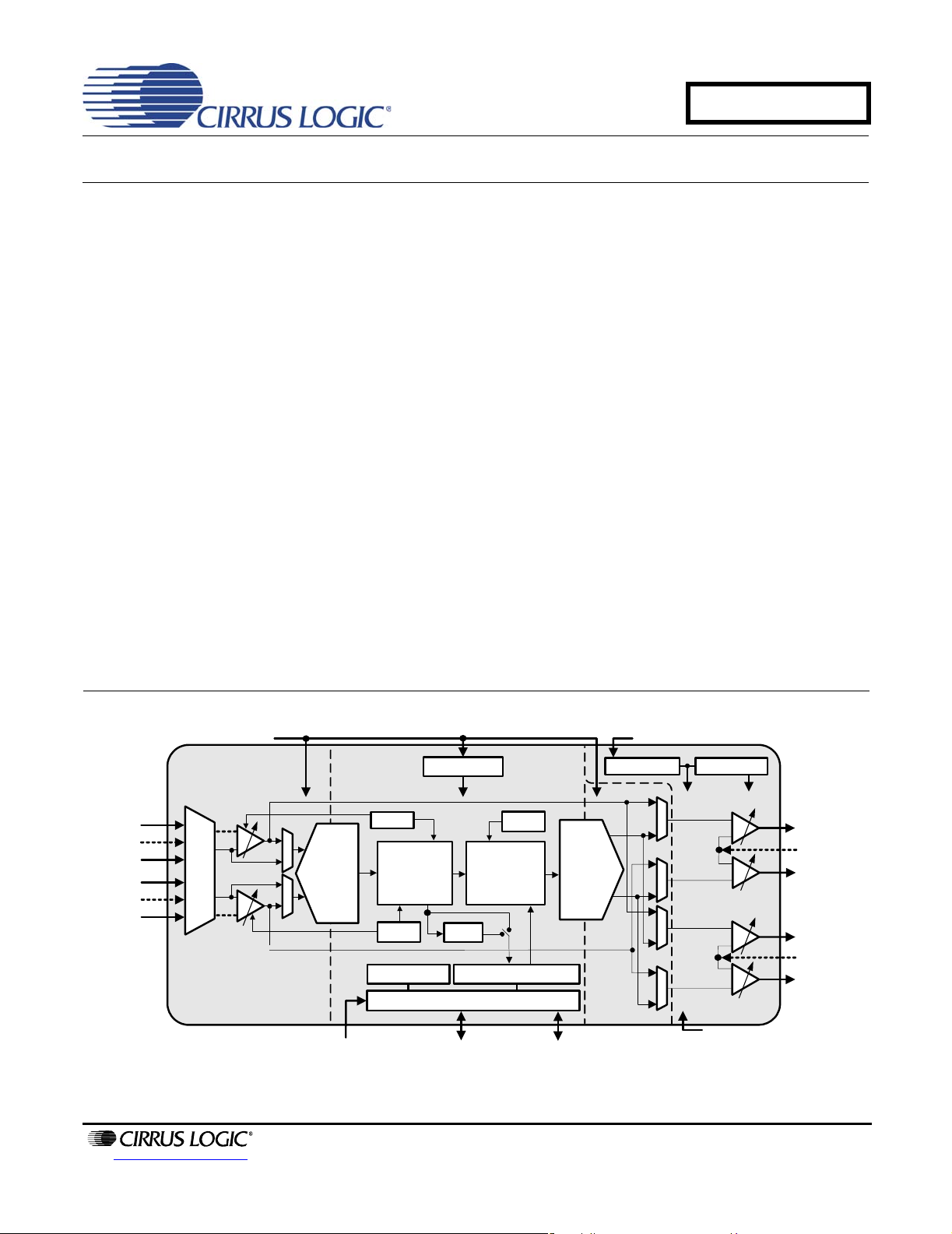

CS42L55

Ultra Low Power, Stereo CODEC w/Class H Headphone Amp

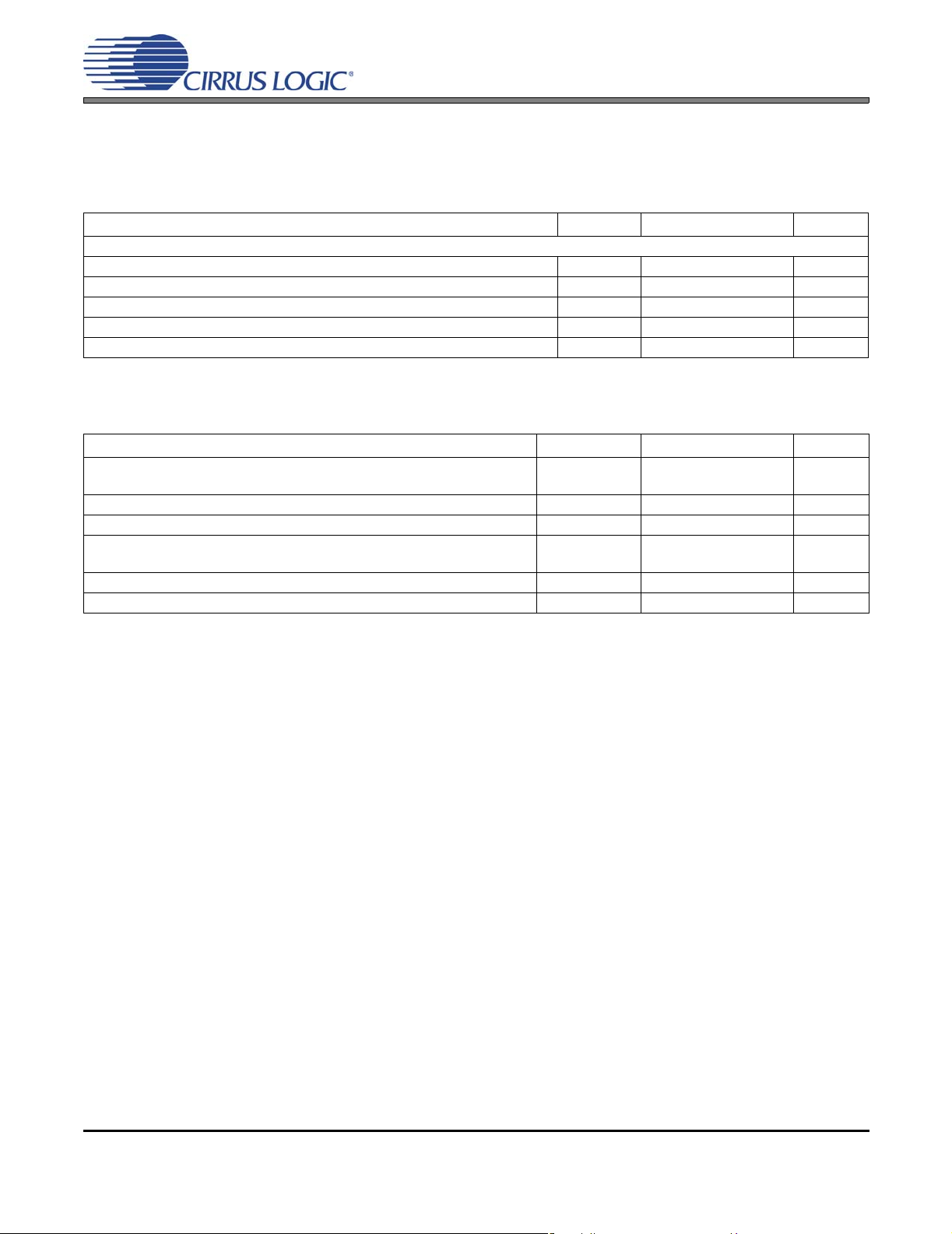

DIGITAL to ANALOG FEATURES

5 mW Stereo Playback Power Consumption

99 dB Dynamic Range (A-wtd)

-86 dB THD+N

Digital Signal Processing Engine

– Bass & Treble Tone Control, De-Emphasis

– Master Volume Control (+12 to -102 dB in

0.5 dB steps)

– Soft-Ramp & Zero-Cross Transitions

– Programmable Peak-Detect and Limiter

– Beep Generator w/Full Tone Control

Stereo Headphone and Line Amplifiers

Step-Down/Inverting Charge Pump

Class H Amplifier - Automatic Supply Adj.

– High Efficiency

– Low EMI

Pseudo-Differential Ground-Centered Outputs

High HP Power Output at -75 dB THD+N

– 2 x 20 mW Into 32 Ω @1.8 V

– 2 x 20 mW Into 16 Ω @1.8 V

1 V

Analog Vol. Ctl. (+12 to -55 dB in 1 dB steps)

Analog In to Analog Out Passthrough

Pop and Click Suppression

Line Output @1.8 V

RMS

ANALOG to DIGITAL FEATURES

3.5 mW Stereo Record Power Consumption

95 dB Dynamic Range (A-wtd)

-87 dB THD+N

2:1 Stereo Input MUX

Analog Programmable Gain Amplifier (PGA)

(+12 to -6 dB in 0.5 dB steps)

+20 dB Boost

Programmable Automatic Level Control (ALC)

– Noise Gate for Noise Suppression

– Programmable Threshold &

Attack/Release Rates

Independent ADC Channel Control

Digital Vol. Ctl. (0 to -96 dB in 1 dB steps)

High-Pass Filter Disable for DC Measurements

Pseudo Differential Inputs

SYSTEM FEATURES

12 MHz USB Master Clock Input

Low Power Operation

– Stereo Anlg. Passthrough: 3.3 mW @1.8 V

– Stereo Rec. and Playback: 8.3 mW @1.8 V

Headphone Detect Input

(SYSTEM FEATURES continued on page 2)

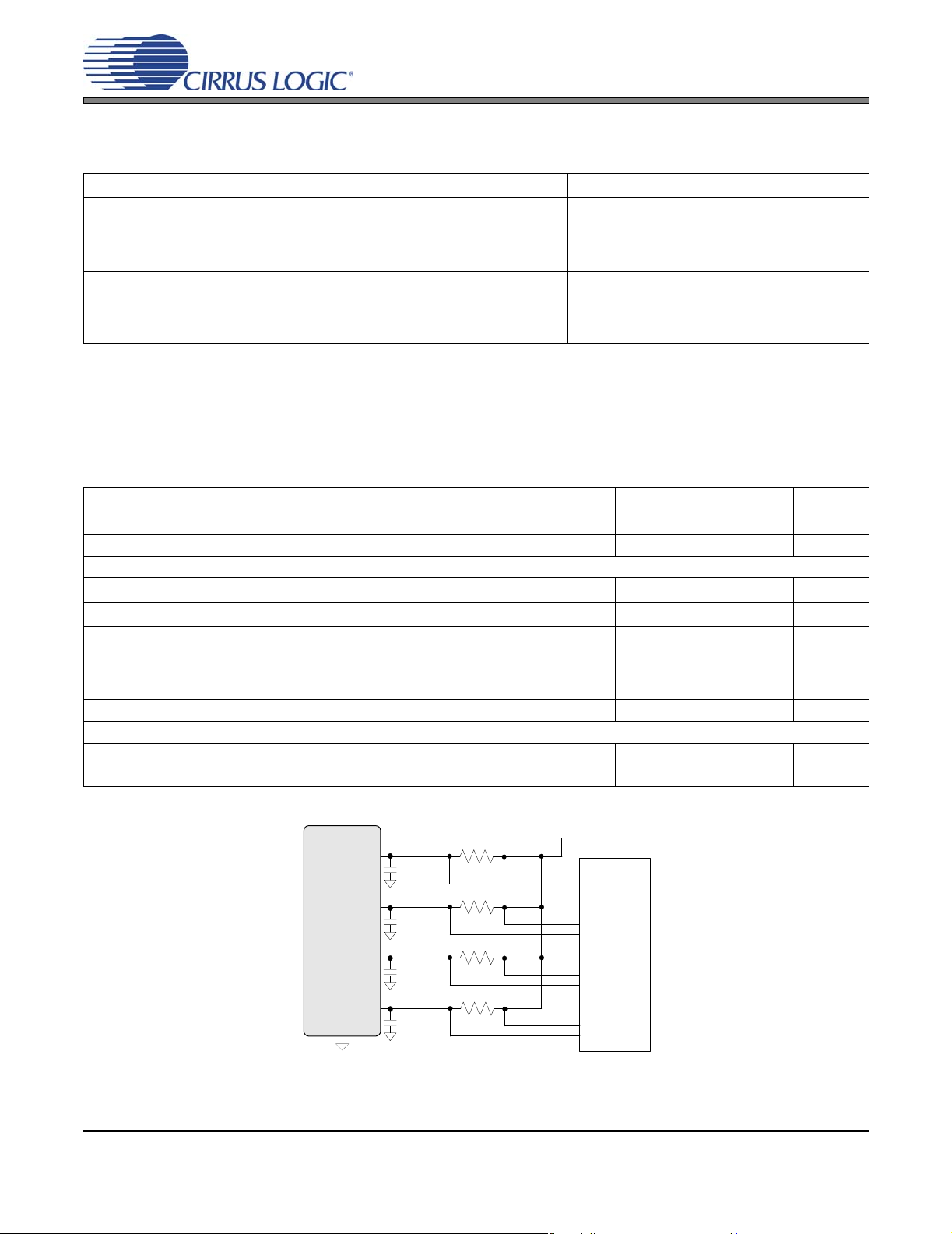

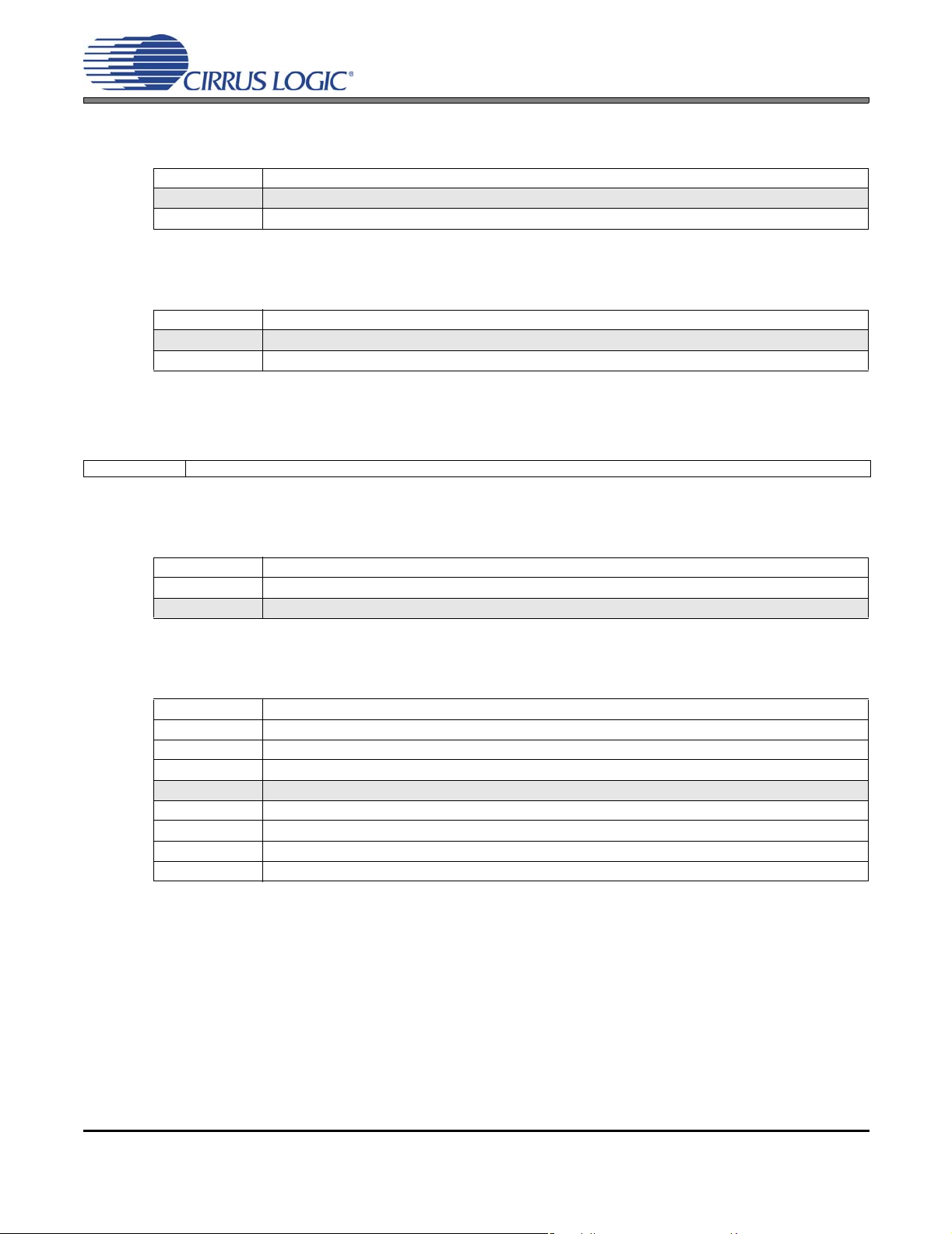

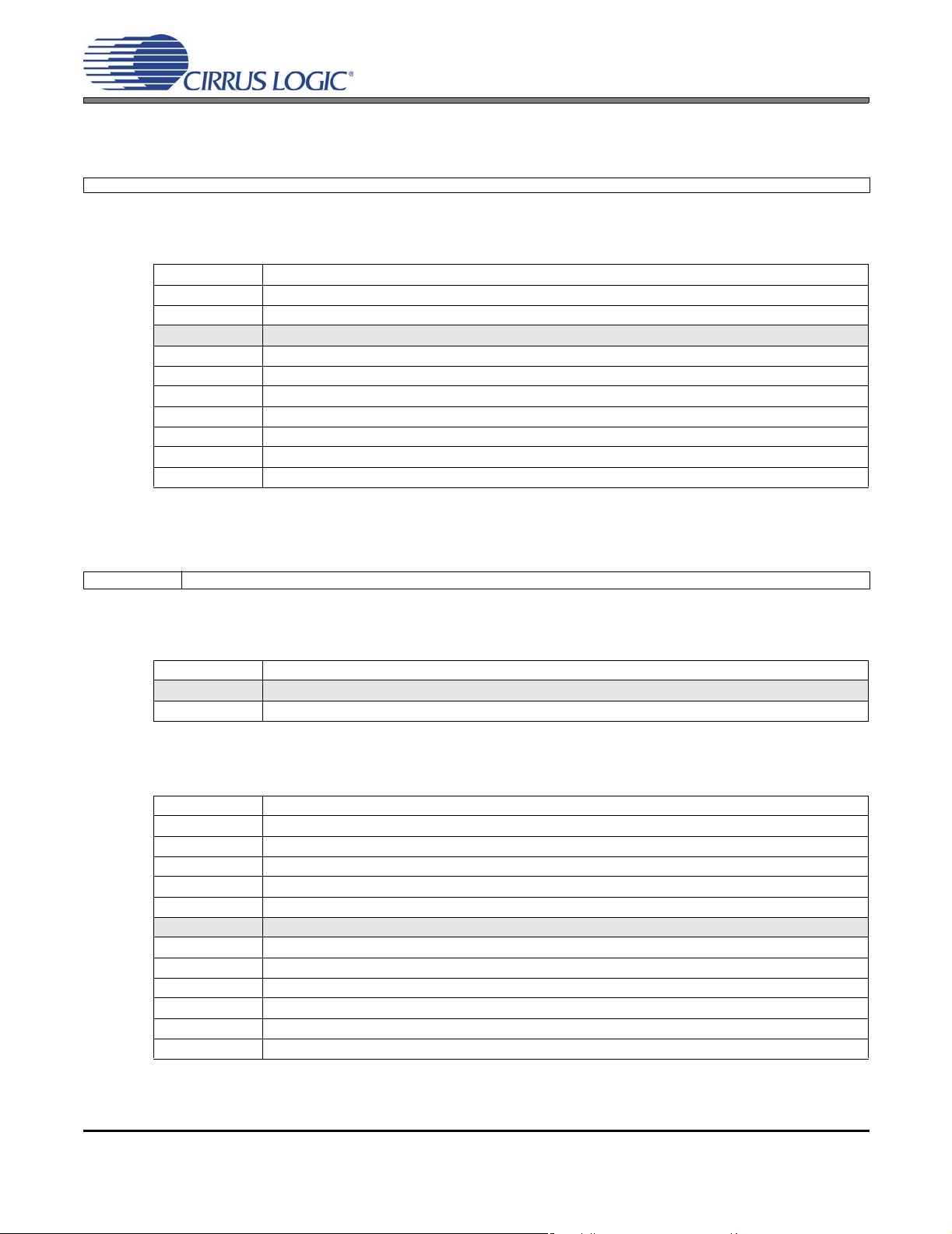

+1.65 V to +2.71 V

Analog/Digital Supply

Left 1

Pseudo Diff.

Input

Right 1

Left 2

Pseudo Diff.

Input

Right 2

http://www.cirrus.com

ALC

Multi-bit

Multi-bit

ΔΣ ADC

ΔΣ ADC

Control Port

+1.65 V to +3.47 V

Interface Supply

LDO Regulator

Beep

Attenuator,

Boost, Mix

ALC

2

I

C Control

Copyright © Cirrus Logic, Inc. 2007

(All Rights Reserved)

Mono mix,

Limiter, Bass,

Treble Adjust

HPF

Serial Audio Port

Level Shifter

I²S Serial Audio

Input/Output

Multi-bit

ΔΣ DAC

+1.65 V to +2.71 V

Charge Pump Supply

Step-Down

+VHP

Ground-Centered

Amplifiers

Inverting

-VHP

Headphone Detect

NOVEMBER '07

Left HP

Output

Pseudo Diff.

Input

Right HP

Output

Left Line

Output

Pseudo Diff.

Input

Right Line

Output

DS773F1

Page 2

CS42L55

SYSTEM FEATURES

High Performance 24-bit Converters

– Multi-bit Delta Sigma Architecture

Integrated High Efficient Power Management

Reduces Power Consumption

– Step-Down Charge Pump Improves

Efficiency

– Inverting Charge Pump Accommodates

Low System Voltage by Providing Negative

Rail for HP/Line Amp

– LDO Reg. Provides Low Digital Supply

Voltage

Digital Power Reduction

– Very Low Oversampling Rate for

Converters

– Bursted Serial Clock Providing 24 Bits per

Sample

Power Down Management

– ADC, DAC, CODEC, PGA, DSP

Analog & Digital Routing/Mixes

– Line/Headphone Out = Analog In (ADC

Bypassed)

– Line/Headphone Out = ADC Out

– Internal Digital Loopback

– Mono Mixes

I²C

I²S Digital Interface Format

Flexible Clocking Options

APPLICATIONS

HDD & Flash-Based Portable Audio Players

MD Players/Recorders

PDAs

Personal Media Players

Portable Game Consoles

Digital Voice Recorders

Digital Camcorders

Digital Cameras

Smart Phones

®

Control Port

– Master or Slave Operation

– High-Impedance Digital Output Select

(used for easy MUXing between CODEC

and other data sources)

– 8.000, 11.029, 12.000, 16.000, 22.059,

24.000, 32.000, 44.118 and 48.000 kHz

Sample Rates

GENERAL DESCRIPTION

The CS42L55 is a highly integrated, 24-bit, ultra-low

power stereo CODEC based on multi-bit delta-sigma

modulation. Both the ADC and DAC offer many features

suitable for low power portable system applications.

The analog input path allows independent channel

control of a variety of features. The Programmable Gain

Amplifier (PGA) provides analog gain with zero cross

transitions. The ADC path includes a digital volume attenuator with soft ramp transitions and a p rogrammable

ALC and noise gate monitor the input signals and adjust

the volume appropriately. An analog passthrough also

exists, accommodating a lower noise, lower power analog in to analog out path to the headphone and line

amplifiers, bypassing the ADC and DAC.

The DAC output path includes a fixed-function digital

signal processing engine. Tone control provides bass

and treble adjustment at four selectable corner freque ncies. The digital mixer provides independent volume

control for both the ADC output and PCM input signal

paths, as well as a master volume control. Digital volume controls may be configured to change on soft ramp

transitions while the analog controls can be configured

to occur on every zero crossing. The DAC path also includes de-emphasis, limiting functions and a beep

generator delivering tones selectable across a range of

two full octaves.

The Class H stereo headphone amplifier combines the

efficiency of an integrated step-down and inverting

charge pump with the linearity and low EMI of a Class

AB amplifier. A step-down/inverting charge pump operates in two modes: +/-VCP mode or +/-(VCP/2) mode.

Based on the amplifier’s output signal, internal logic automatically adjusts the output of the charge pump,

+VHPFILT and –VHPFILT, to optimize efficiency. With

these features, the amplifier delivers a ground-centered

output with a large signal swing even at low voltages

and eliminates the need for external DC-blocking

capacitors.

These features make the CS42L55 the ideal solution for

portable applications that require extremely low power

consumption in a minimal amount of space.

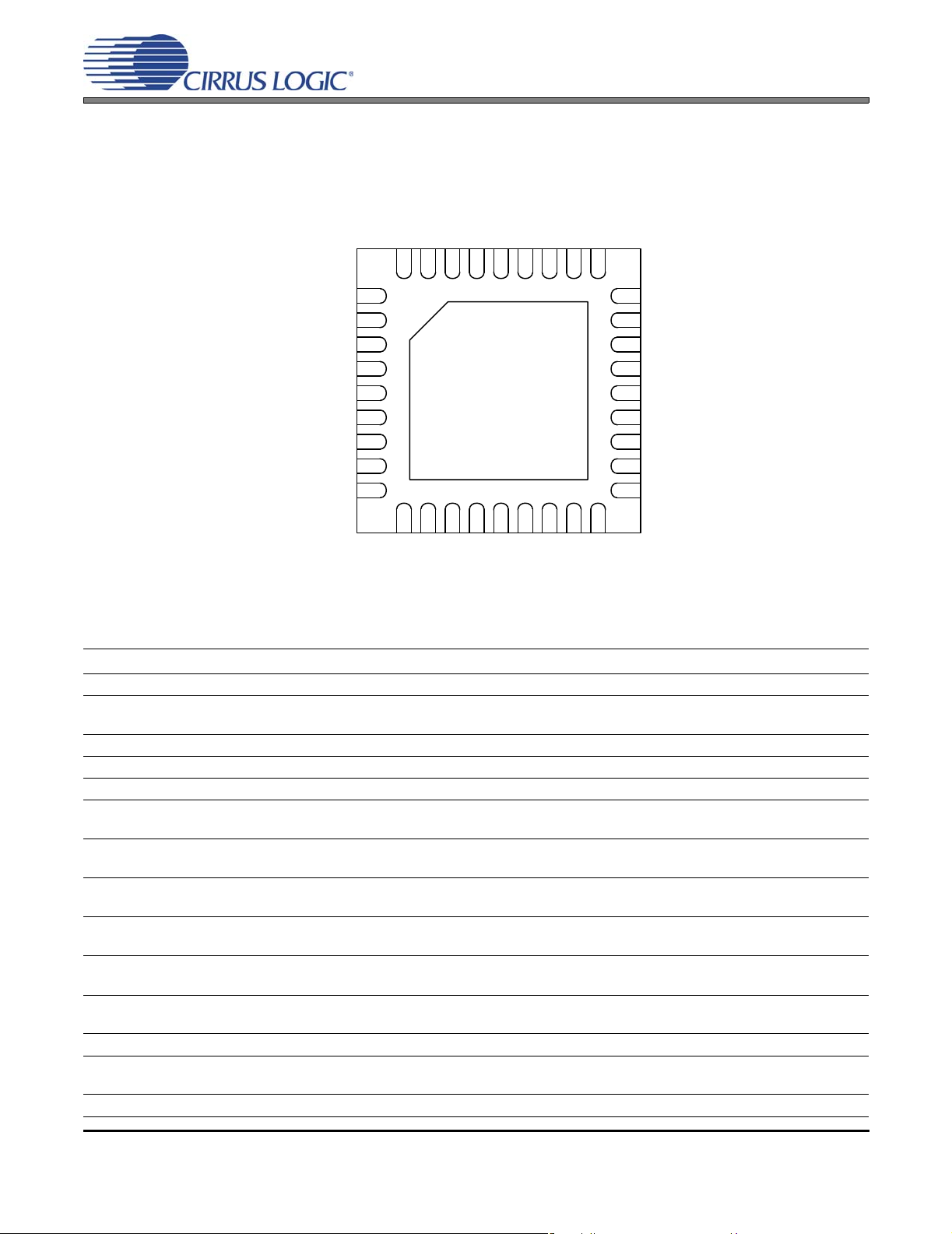

The CS42L55 is available in a 36-pin QFN package for

the Commercial (-40°C to +85°C) grade. The

CDB42L55 Customer Demonstration board is also

available for device evaluation and implementation suggestions. Please see “Ordering Information” on page 73

for complete details.

2 DS773F1

Page 3

TABLE OF CONTENTS

1. PIN DESCRIPTIONS .............................................................................................................................. 8

1.1 I/O Pin Characteristics .......................... ... .... ... ... ... .... ... ... ... .... ... ... ..................................................... 9

2. TYPICAL CONNECTION DIAGRAM ................................................................................................... 10

3. CHARACTERISTIC AND SPECIFICATION TABLES ......................................................................... 11

RECOMMENDED OPERATING CONDITIONS ................................................................................... 11

ABSOLUTE MAXIMUM RATINGS .......................................................................................................11

ANALOG INPUT CHARACTERISTICS ................................................................................................ 12

ADC DIGITAL FILTER CHARACTERISTICS ....................................... ... .... ... ... ... ................................ 13

HP OUTPUT CHARACTERISTICS ......................................................................................................14

LINE OUTPUT CHARACTERISTICS ................................................................................................... 15

ANALOG PASSTHROUGH CHARACTERISTICS ............................................................................... 16

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE .............................. 16

SWITCHING SPECIFICATIONS - SERIAL PORT ............................................................................... 17

SWITCHING SPECIFICATIONS - CONTROL PORT .......................................................................... 18

POWER SUPPLY REJECTION (PSRR) CHARACTERISTICS ........................................................... 19

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS ..................................................... 19

POWER CONSUMPTION - ALL SUPPLIES = 1.8 V ............................................................................ 20

POWER CONSUMPTION - ALL SUPPLIES = 2.5 V ............................................................................ 21

4. APPLICATIONS ................................................................................................................................... 22

4.1 Overview ......................................................................................................................................... 22

4.1.1 Basic Architecture ................................................................................................................. 22

4.1.2 Line Inputs ............................................................................................................................. 22

4.1.3 Line and Headphone Outputs (Class H, Ground-Centered Amplifiers) ................................. 22

4.1.4 Fixed-Function DSP Engine .................................................................................................. 22

4.1.5 Beep Generator ..................................................................................................................... 22

4.1.6 Power Management .............................................................................................................. 22

4.2 Analog Inputs ................................................................................................................................. 23

4.2.1 Pseudo-Differential Inputs ........................... ................................................................. .........24

4.2.2 Automatic Level Control (ALC) .............................................................................................. 24

4.3 Analog In to Analog Out Passthrough ............................................................................................ 25

4.4 Analog Outputs .............................................................................................................................. 26

4.5 Class H Amplifier ............................................................................................................................ 27

4.5.1 Power Control Options ................... .... ... ... ... .... ... ... ... .... ... ...................................................... 27

4.5.1.1 Standard Class AB Operation (Mode 01 and 10) ...................................................... 28

4.5.1.2 Adapted to Volume Settings (Mode 00) .................................. ... .... ... ... ... ... ................ 28

4.5.1.3 Adapted to Output Signal (Mode 11) ......................................................................... 29

4.5.2 Power Supply Transitions ...................................................................................................... 29

4.5.3 Efficiency ............................................................................................................................... 31

4.6 Beep Generator .............................................................................................................................. 31

4.7 Limiter ............................................................................................................................................. 32

4.8 Serial Port Clocking ........................................................................................................................ 34

4.9 Digital Interface Format .................................................................................................................. 34

4.10 Initialization ............................ .... ... ... ... ... ....................................... ... .... ... ... ... ................................ 34

4.11 Recommended DAC to HP or Line Power-Up Sequence (Playback) .... ... ... .... ... ... ... ... .... ... ... ... ... 35

4.11.1 Recommended Power-Down Sequence ............................................................................. 36

4.12 Recommended PGA to HP or Line Power-Up Sequence (Analog Passthrough) ................ ......... 36

4.12.1 Recommended Power-Down Sequence ............................................................................. 36

4.13 Required Initialization Settings ..................................................................................................... 37

4.14 Control Port Operation .................................................................................................................. 38

4.14.1 I²C Control .............. ... ... .... ... ... ....................................... ... ... ... .... ... ... ... .... ... ... ...................... 38

4.14.2 Memory Address Pointer (MAP) .................................... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... ... 39

4.14.2.1 Map Increment (INCR) ............................................................................................. 39

CS42L55

DS773F1 3

Page 4

CS42L55

5. REGISTER QUICK REFERENCE ........................................................................................................ 40

6. REGISTER DESCRIPTION .................................................................................................................. 42

6.1 Fab I.D. and Revision Register (Address 01h) (Read Only) ........................................................... 42

6.1.1 Chip Revision (Read Only) .................................................................................................... 42

6.2 Power Control 1 (Address 02h) ...................................................................................................... 42

6.2.1 Power Down ADC Charge Pump .......................................................................................... 42

6.2.2 Power Down ADC x ............................................................................................................... 42

6.2.3 Power Down ...... .... ... ....................................... ... ... ....................................... ... ... ... ................ 42

6.3 Power Control 2 (Address 03h) ...................................................................................................... 43

6.3.1 Headphone Power Control .... ... ... ... .... ... ....................................... ... ... ... .... ... ... ... ... .... ... ......... 43

6.3.2 Line Power Control ... ... ... ....................................... ... .... ... ... ... ... .... ... ... ... ................................ 43

6.4 Clocking Control 1 (Address 04h) ................................................................................................... 43

6.4.1 Master/Slave Mode .................................. ............................................................................. 43

6.4.2 SCLK Polarity ........ ... ... ....................................... ... ... ....................................... ... ... ................ 43

6.4.3 SCLK Equals MCLK ........................................ ... ... ... ....................................... ... ... .... ............ 44

6.4.4 MCLK Divide By 2 .......... ....................................... ... .... ... ...................................... .... ............ 44

6.4.5 MCLK Disable .......................... ....................................... ... ....................................... ............ 44

6.5 Clocking Control 2 (Address 05h) ................................................................................................... 44

6.5.1 Speed Mode ...... .... ... ....................................... ... ... ....................................... ... ... ... ................ 44

6.5.2 32 kHz Sample Rate Group ..................................................................................................45

6.5.3 Internal MCLK/LRCK Ratio ................................................................................................... 45

6.6 Class H Power Control (Address 06h) ............................................................................................ 45

6.6.1 Adaptive Power Adjustment ............... ... ... ... .... ... ... ... .... ...................................... ... .... ... ... ... ... 45

6.7 Miscellaneous Control (Address 07h) ............................................................................................. 45

6.7.1 Digital MUX ........................ ...................................... ....................................... ... ................... 45

6.7.2 Analog Zero Cross ............................. ... ... ... .... ...................................... .... ... ... ...................... 46

6.7.3 Digital Soft Ramp ........................ ... .... ...................................... ............................................. 46

6.7.4 Freeze Registers ...... ... ... .... ...................................... .... ... ... ... ... .... ......................................... 46

6.8 ADC, Line, HP MUX (Address 08h) ................................................................................................ 46

6.8.1 ADC x Input Select ... ... ... .... ...................................... .... ... ... ....................................... ............ 46

6.8.2 Line Input Select ............................. .... ... ....................................... ... ... ... ................................ 47

6.8.3 Headphone Input Select ........................................................................................................ 47

6.9 HPF Control (Address 09h) ............................................................................................................ 47

6.9.1 ADCx High-Pass Filter .......................................................................................................... 47

6.9.2 ADCx High-Pass Filter Freeze .............................................................................................. 47

6.9.3 HPF x Corner Frequency ................................ ... ... ... .... ... ... ... ... .... ... ... ................................... 47

6.10 Misc. ADC Control (Address 0Ah) ................................................................................................ 48

6.10.1 ADC Channel B=A .............................................................................................................. 48

6.10.2 PGA Channel B=A .............................................................................................................. 48

6.10.3 Digital Sum .......................................................................................................................... 48

6.10.4 Invert ADC Signal Polarity ................................................................................................... 48

6.10.5 ADC Mute ............................................................................................................................ 48

6.11 PGA x MUX, Volume:

PGA A (Address 0Bh) & PGA B (Address 0Ch) ................................................................................... 49

6.11.1 Boostx ................................................................................................................................. 49

6.11.2 PGA x Input Select .............................................................................................................. 49

6.11.3 PGAx Volume ...................................................................................................................... 49

6.12 ADCx Attenuator Control:

ADCAATT (Address 0Dh) & ADCBATT (Address 0Eh) ....................................................................... 50

6.12.1 ADCx Volume ...................................................................................................................... 50

6.13 Playback Control 1 (Address 0Fh) .........................................................................................

6.13.1 Power Down DSP ................................................................................................................ 50

6.13.2 HP/Line De-Emphasis ......................................................................................................... 50

6.13.3 Playback Channels B=A ...................................................................................................... 50

....... 50

4 DS773F1

Page 5

CS42L55

6.13.4 Invert PCM Signal Polarity .................................................................................................. 51

6.13.5 Master Playback Mute ......................................................................................................... 51

6.14 ADCx Mixer Volume:

ADCA (Address 10h) & ADCB (Address 11h) ...................................................................................... 51

6.14.1 ADC Mixer Channel x Mute ................................................................................................. 51

6.14.2 ADC Mixer Channel x Volume ............................................................................................. 51

6.15 PCMx Mixer Volume:

PCMA (Address 12h) & PCMB (Address 13h) ..................................................................................... 52

6.15.1 PCM Mixer Channel x Mute ................................................................................................52

6.15.2 PCM Mixer Channel x Volume ............................................................................................ 52

6.16 Beep Frequency & On Time (Address 14h) ................................................................................. 53

6.16.1 Beep Frequency ........... .... ... ... ....................................... ... ... ... .... ... ... ... .... ... ... ...................... 53

6.16.2 Beep On Time ..................... ... ... ... .... ... ... ... .... ... ... ... .... ...................................... ... .... ............ 54

6.17 Beep Volume & Off Time (Address 15h) ......................................................................................54

6.17.1 Beep Off Time ..................... ... ... ... .... ... ... ... .... ...................................... .... ... ... ... ... .... ............ 54

6.17.2 Beep Volume .......... ... ... .... ... ....................................... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ............ 55

6.18 Beep & Tone Configuration (Address 16h) ...................................................................................55

6.18.1 Beep Configuration ........................................... ... ... .... ... ... ... ................................................ 55

6.18.2 Treble Corner Frequency ................. ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ................... 55

6.18.3 Bass Corner Frequency ............................ .... ... ... ... .... ... ... ... ... ....................................... ...... 56

6.18.4 Tone Control Enable ........................................................................ ... .... ... ... ... ... .... ... ......... 56

6.19 Tone Control (Address 17h) ............ ... ... .... ... ... ... .... ... ... ....................................... ... ... ... .... ............ 56

6.19.1 Treble Gain .......................................................................... ... .... ... ... ... .... ... ... ... ... ................ 56

6.19.2 Bass Gain ..................................... .... ... ... ....................................... ... ... ................................ 56

6.20 Master Volume Control:

MSTA (Address 18h) & MSTB (Address 19h) ...................................................................................... 57

6.20.1 Master Volume Control ........................................................................................................ 57

6.21 Headphone Volume Control:

HPA (Address 1Ah) & HPB (Address 1Bh) ..........................................................................................57

6.21.1 Headphone Channel x Mute ................................................................................................57

6.21.2 Headphone Volume Control ................................................................................................57

6.22 Line Volume Control:

LINEA (Address 1Ch) & LINEB (Address 1Dh) .................................................................................... 58

6.22.1 Line Channel x Mute ........................................... ... .... ... ... ................................................... 58

6.22.2 Line Volume Control ............................................................................................................ 58

6.23 Analog Input Advisory Volume (Address 1Eh) ............................................................................. 59

6.23.1 Analog Input Advisory Volume ............... ... .... ... ... ... .... ... ... ... ... .... ... ......................................59

6.24 Digital Input Advisory Volume (Address 1Fh) ............ ............................................. ......................59

6.24.1 Digital Input Advisory Volume ............................................................................................. 59

6.25 ADC & PCM Channel Mixer (Address 20h) .................................................................................. 60

6.25.1 PCM Mix Channel Swap ........................................ .... ... ... ... ... .... ......................................... 60

6.25.2 ADC Mix Channel Swap ...................................... ... .... ... ... ... ... .... ... ... ... ................................ 60

6.26 Limiter Min/Max Thresholds (Address 21h) ..................................................................................60

6.26.1 Limiter Maximum Threshold ......... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... ... 60

6.26.2 Limiter Cushion Threshold .................................................................................................. 61

6.27 Limiter Control, Release Rate (Address 22h) ...............................................................................61

6.27.1 Peak Detect and Limiter ............ ... .... ... ... ... .... ... ... ....................................... ... ... ... .... ... ......... 61

6.27.2 Peak Signal Limit All Channels ........................................................................................... 61

6.27.3 Limiter Release Rate ........ ... ... ... ... ....................................... ... .... ... ... ... .... ... ... ... ... .... ... ......... 62

6.28 Limiter Attack Rate (Address 23h) ................................................................................................ 62

6.28.1 Limiter Attack Rate ....... .... ... ... ... ... .... ... ....................................... ... ... ... .... ... ... ... ... .... ..

6.29 ALC Enable & Attack Rate (Address 24h) ....................................................................................62

6.29.1 ALCx ............................. .... ... ... ... ... .... ... ... ....................................... ... ... .... ............................ 62

6.29.2 ALC Attack Rate .................................................................................................................. 63

.......... 62

DS773F1 5

Page 6

CS42L55

6.30 ALC Release Rate (Address 25h) ................................................................................................ 63

6.30.1 ALC Release Rate ............................................................................................................... 63

6.31 ALC Threshold (Address 26h) ...................................................................................................... 64

6.31.1 ALC Maximum Threshold .................................................................................................... 64

6.31.2 ALC Minimum Threshold ..................................................................................................... 64

6.32 Noise Gate Control (Address 27h) ............................................................................................... 64

6.32.1 Noise Gate All Channels ..................................................................................................... 64

6.32.2 Noise Gate Enable .............................................................................................................. 65

6.32.3 Noise Gate Threshold and Boost ........................................................................................ 65

6.32.4 Noise Gate Delay Timing .................................................................................................... 65

6.33 ALC and Limiter Soft Ramp, Zero Cross Disables (Address 28h) ................................................ 65

6.33.1 ALCx Soft Ramp Disable ..................... ... ....... ...... ....... ...... ...... ....... ...... ....... ...... ....... ...... ...... 65

6.33.2 ALCx Zero Cross Disable .................................................................................................... 65

6.33.3 Limiter Soft Ramp Disable ......................... ....... ...... ....... ...... ....... ...... ....... ...... ...... ....... ......... 66

6.34 Status (Address 29h) (Read Only) ............................................................................................... 66

6.34.1 HPDETECT Pin Status (Read Only) .......................................... ... ... ... .... ... ... ... ... .... ... ... ... ... 66

6.34.2 Serial Port Clock Error (Read Only) .................................................................................... 66

6.34.3 DSP Engine Overflow (Read Only) ..................................................................................... 66

6.34.4 MIXx Overflow (Read Only) ................................................................................................. 66

6.34.5 ADCx Overflow (Read Only) ...............................................................................................67

6.35 Charge Pump Frequency (Address 2Ah) ..................................................................................... 67

6.35.1 Charge Pump Frequency .................................................................................................... 67

7. PCB LAYOUT CONSIDERATIONS ..................................................................................................... 68

7.1 Power Supply ................................................................................................................................. 68

7.2 Grounding ....................................................................................................................................... 68

7.3 QFN Thermal Pad .......................................................................................................................... 68

8. ANALOG VOLUME NON-LINEARITY (DNL & INL) ............... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... ... 69

9. ADC & DAC DIGITAL FILTERS .......................................................................................................... 70

10. PARAMETER DEFINITIONS .............................................................................................................. 71

11. PACKAGE DIMENSIONS .................................................................................................................. 72

THERMAL CHARACTERISTICS .......................................................................................................... 72

12. ORDERING INFORMATION .............................................................................................................. 73

13. REFERENCES .................................................................................................................................... 73

14. REVISION HISTORY .......................................................................................................................... 73

LIST OF FIGURES

Figure 1.Typical Connection Diagram ....................................................................................................... 10

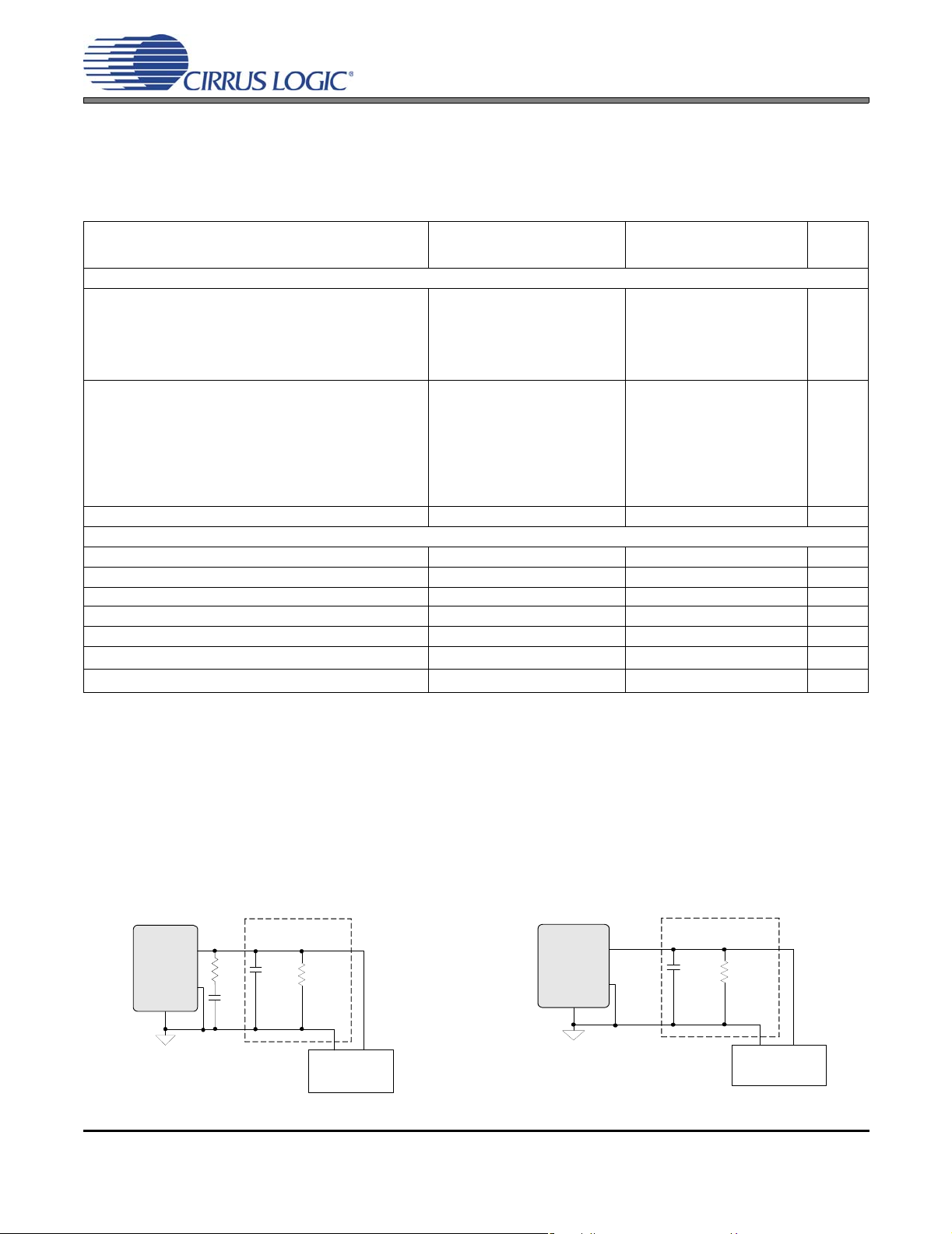

Figure 2.CMRR Test Configuration ................................. .......................................................................... 12

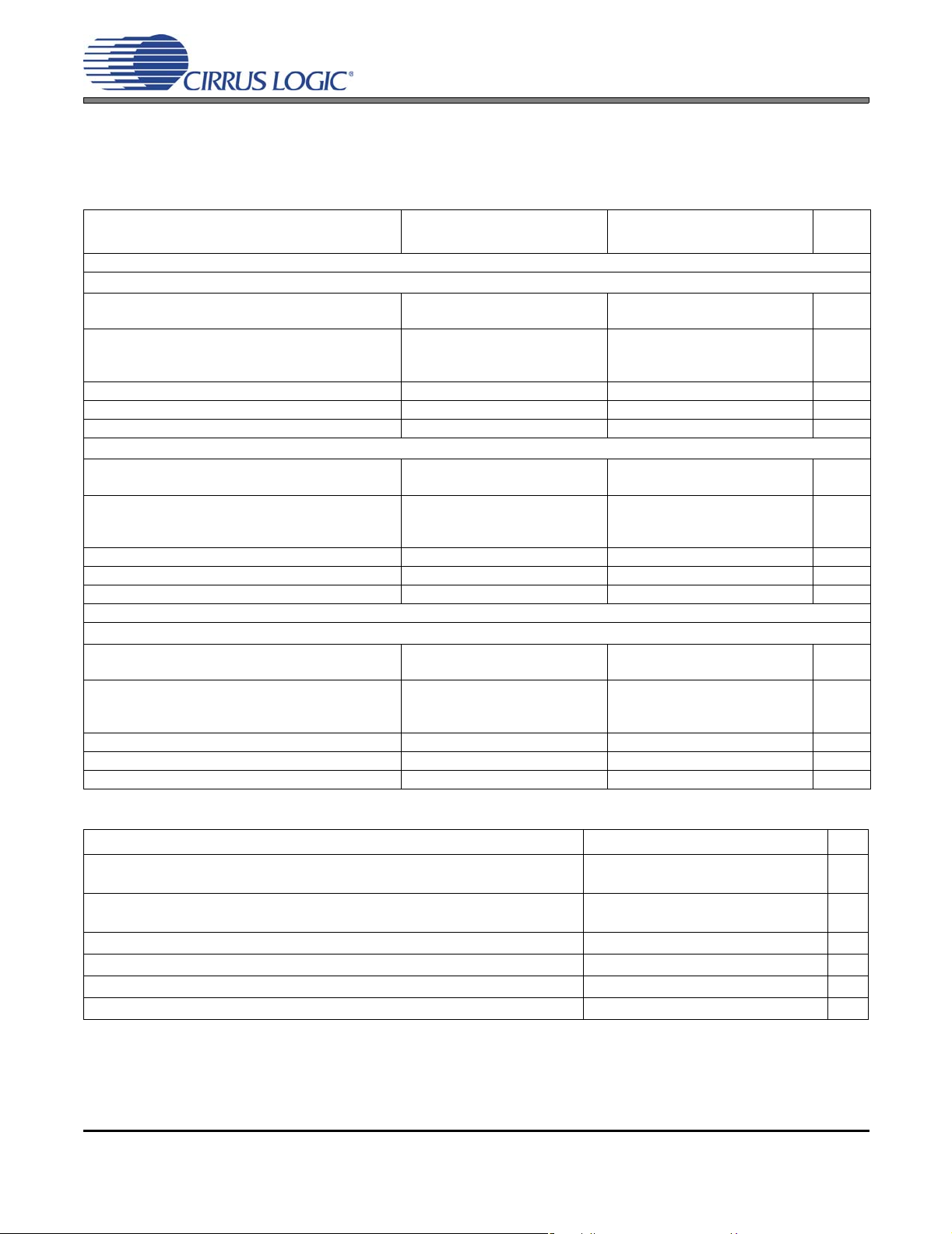

Figure 3.HP Output Test Configuration ............................... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ......................... 15

Figure 4.Line Output Test Configuration .......................................... ... ... ... ... .... ... ...................................... 15

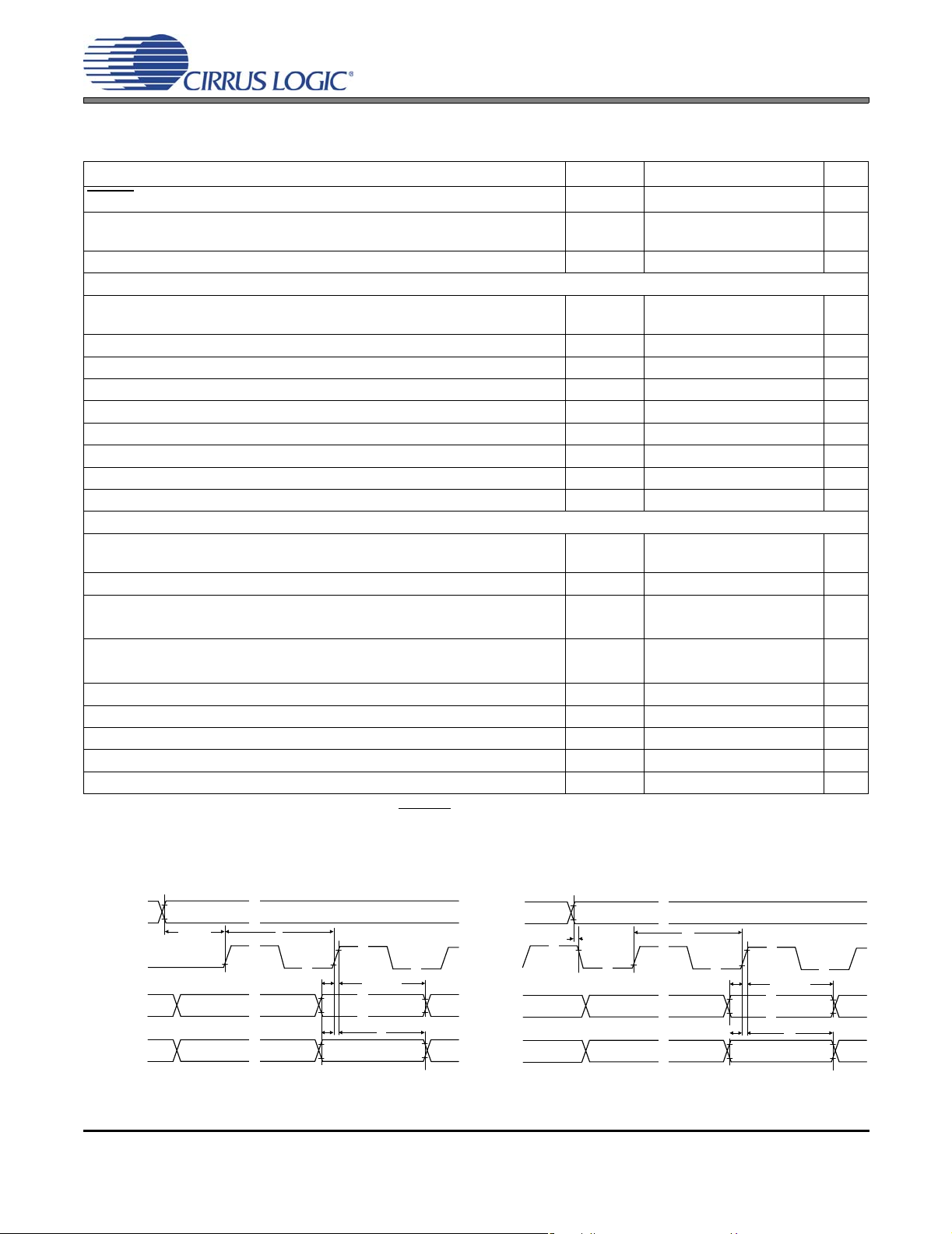

Figure 5.Serial Port Timing (Slave Mode) ....... ... .... ... ... ... .... ... ... ... .... ... ... ... ... ............................................. 17

Figure 6.Serial Port Timing (Master Mode) .. ............................................................................................. 17

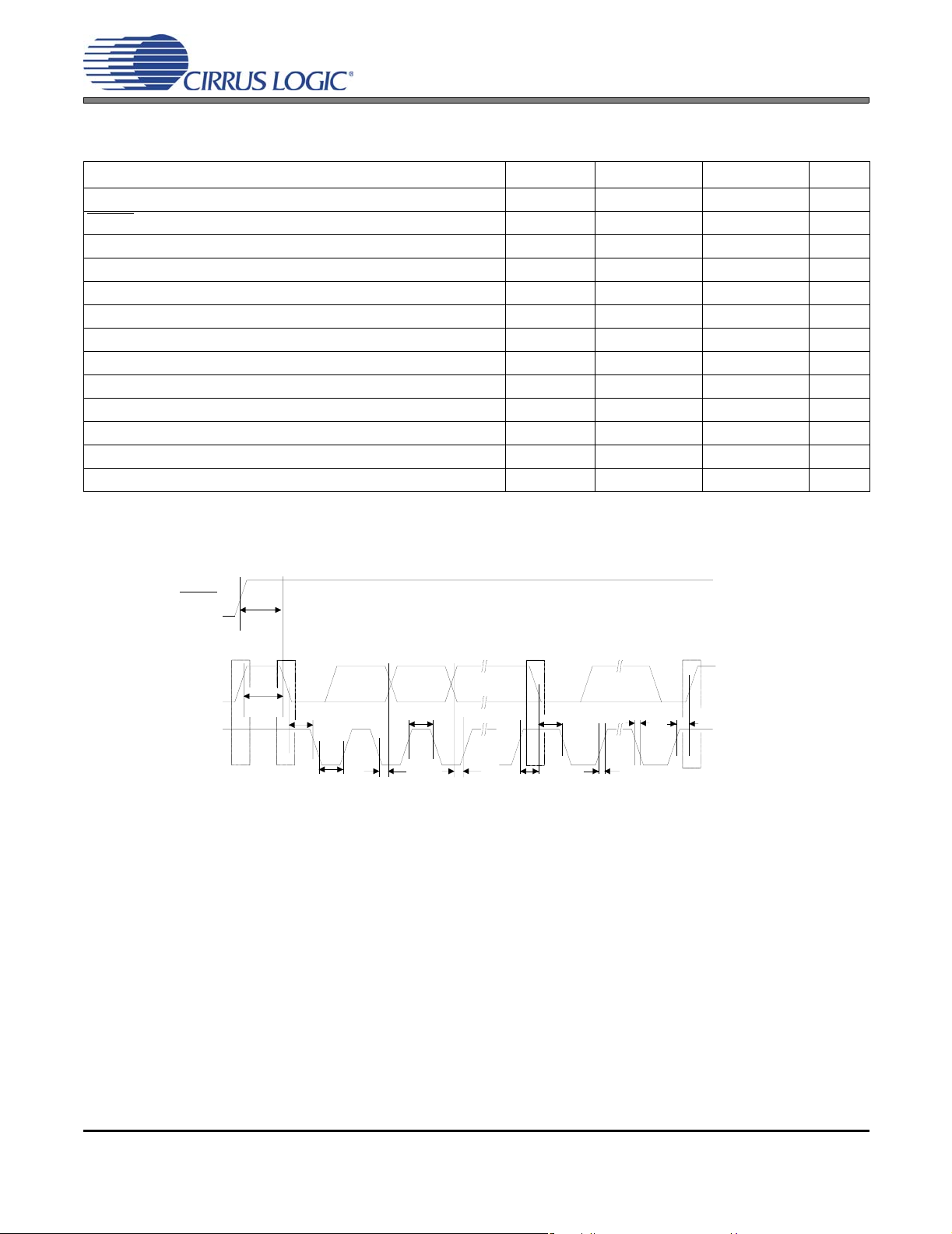

Figure 7.I²C Control Port Timing ............................................................................................................... 18

Figure 8.Power Consumption Test Configuration ..................................................................................... 19

Figure 9.Analog Input Signal Flow ............................................................................................................ 23

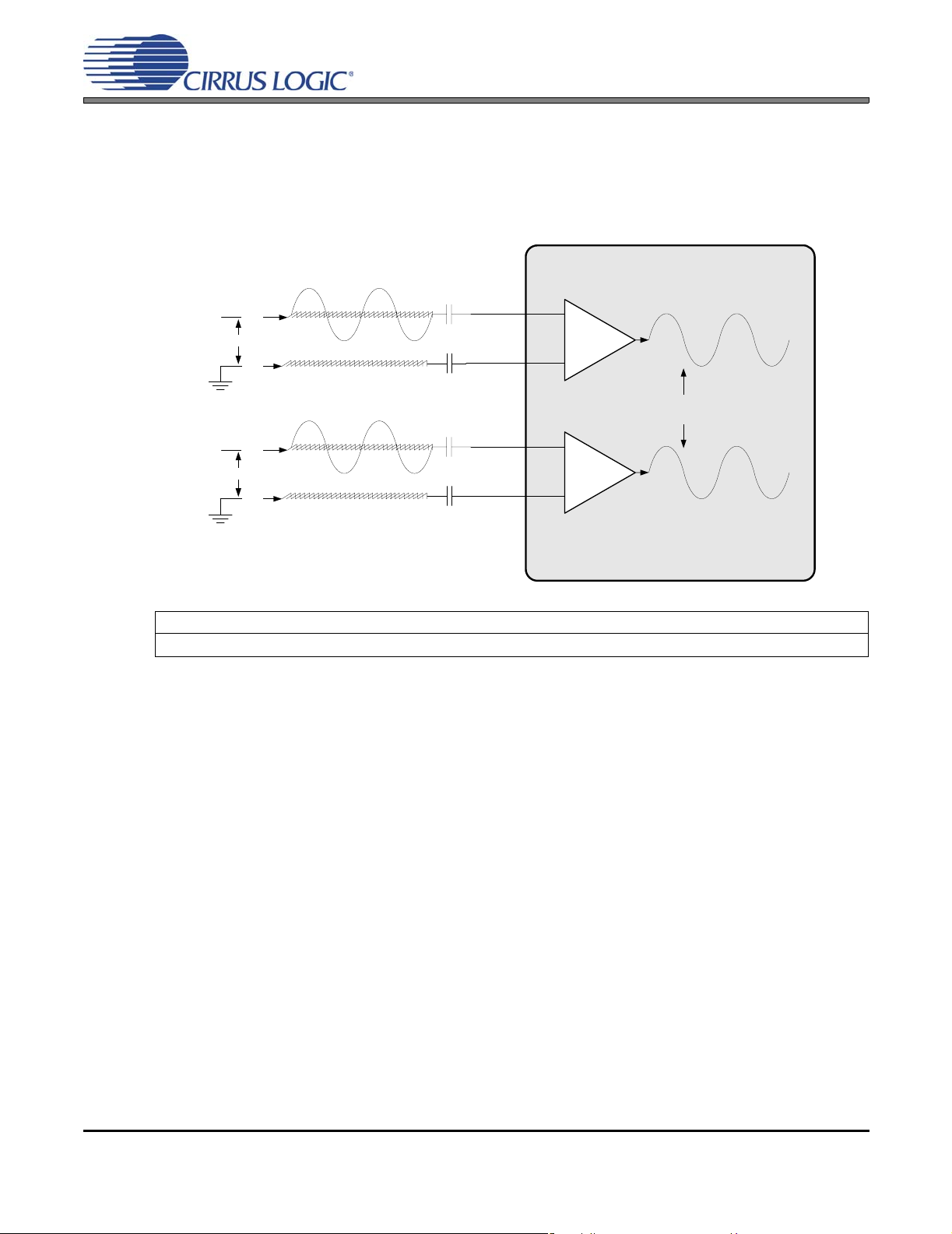

Figure 10.Stereo Pseudo-Differential Input ............................................................................................... 24

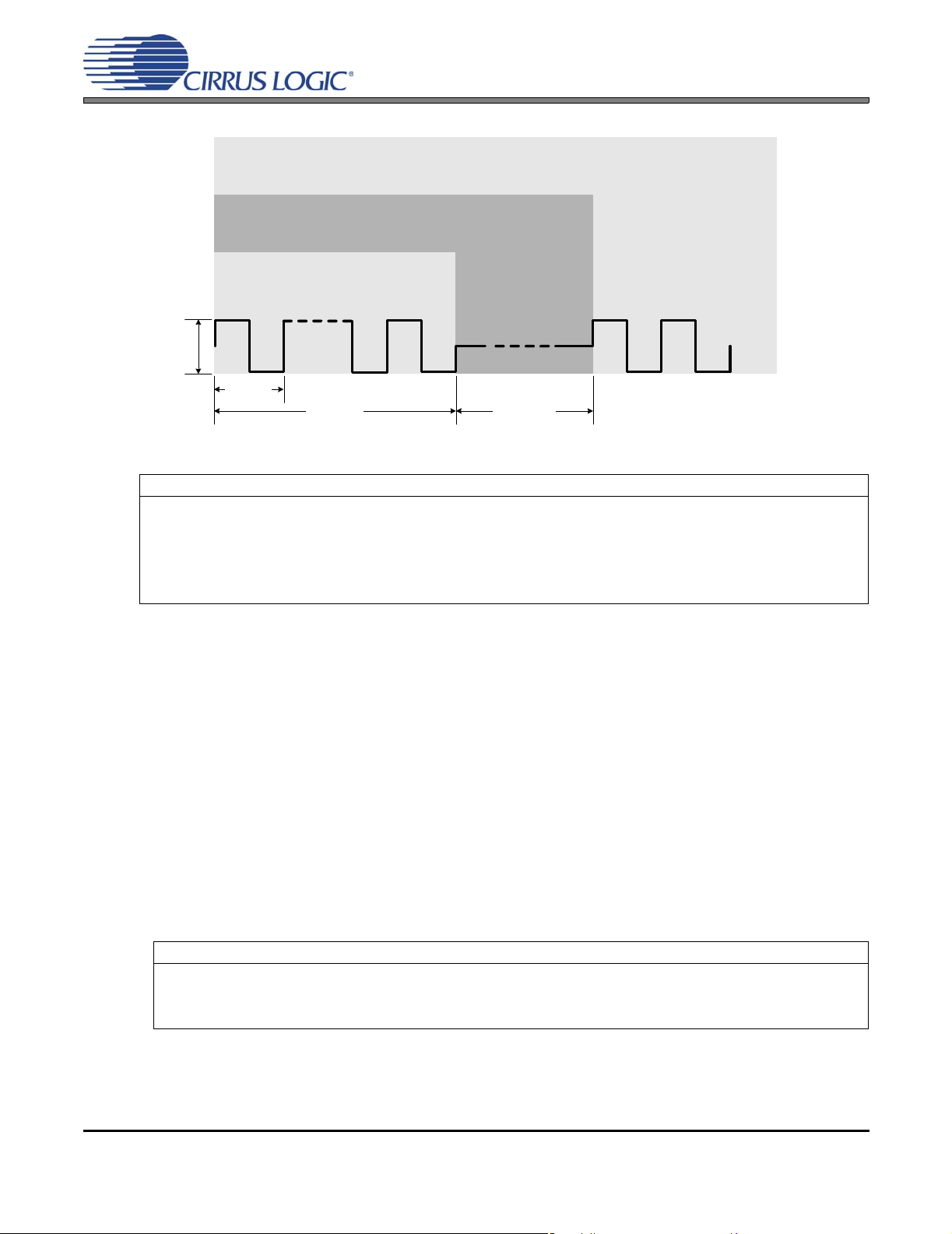

Figure 11.ALC Operation .......... ... ... ... .... ... ... ... ... .... ... ....................................... ... ... ... .... ... ... ...................... 25

Figure 12.DSP Engine Signal Flow ........................................................................................................... 26

Figure 13.Analog Output Stage ................................................................................................................. 27

Figure 14.Adaptive Mode 00 ..... ... ... ... .... ... ... ....................................... ... ... ... .... ... ... ... .... ... ... ...................... 28

Figure 15.VHPFILT Transitions ................................................................................................................. 30

Figure 16.VHPFILT Hysteresis .......... .... ... ... ... ... .... ... ....................................... ... ... ... .... ... ......................... 30

Figure 17.Class H Power to Load vs. Power from VCP Supply ................................................................ 31

6 DS773F1

Page 7

CS42L55

Figure 18.Beep Configuration Options ...................................................................................................... 32

Figure 19.Peak Detect & Limiter ............................................................................................................... 33

Figure 20.I²S Format ................................................................................................................................. 34

Figure 21.Control Port Timing, I²C Write ................................................................................................... 38

Figure 22.Control Port Timing, I²C Read ................................................................................................... 38

Figure 23.PGA Step Size vs. Volume Setting ........................................................................................... 69

Figure 24.PGA Output Volume vs. Volume Setting .................................................................................. 69

Figure 25.HP/Line Step Size vs. Volume Setting ...................................................................................... 69

Figure 26.HP/Line Output Volume vs. Volume Setting .............................................................................69

Figure 27.ADC Passband Ripple ........... ... ................................................................................................ 70

Figure 28.ADC Stopband Rejection .......................................................................................................... 70

Figure 29.ADC Transition Band ................................................................................................................ 70

Figure 30.ADC Transition Band Detail ...................................................................................................... 70

Figure 31.DAC Passband Ripple ........... ... ... ... ... .... ...................................... .... ... ... ... .... ... ... ... ... ................ 70

Figure 32.DAC Stopband .......................................................................................................................... 70

Figure 33.DAC Transition Band ................................................................................................................ 70

Figure 34.DAC Transition Band (Detail) .................................................................................................... 70

DS773F1 7

Page 8

1. PIN DESCRIPTIONS

CS42L55

SDIN

LRCK

SDA

SCL

VCP

FLYP

+VHPFILT

FLYC

FLYN

MCLK

SCLK

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 181716

SDOUT

35 28

333436

GND/Thermal Pad

Top-Down (Through Package)

VL

32

View

VLDO

VDFILT

HPDETECT

RESET

293031

AIN1B

27

26

25

24

23

22

21

20

19

AIN1REF

AIN1A

AIN2B

AIN2REF

AIN2A

AFILTB

AFILTA

VQ

FILT+

VA

HPREF

HPOUTA

-VHPFILT

HPOUTB

LINEOUTA

LINEREF

LINEOUTB

AGND

Pin Name # Pin Description

SDIN 1 Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

LRCK 2

SDA 3 Serial Control Data (Input/Output) - Serial data for the I²C serial control port.

SCL 4 Serial Control Port Clock (Input) - Serial clock for the I²C serial control port.

VCP 5 Step-Down Charge Pump Power (Input) - Power supply for the step-d own charge pump.

FLYP 6

+VHPFILT 7

FLYC 8

FLYN 9

-VHPFIL T 10

HPOUTA

HPOUTB

HPREF 12 Pseudo Diff. Hea dphone Output Reference (Input) - Ground reference for the headphone amplifiers

LINEOUTA

LINEOUTB

LINEREF 15 Pseudo Diff. Line Output Reference (Input) - Ground reference for the line amplifiers.

Left Right Clock (Input/Output) - Determines which channel, Left or Right, is currently active on the

serial audio data lines.

Charge Pump Cap Positive Node (Output) - Positive node for the step-down charge pump’s flying

capacitor.

Step-Down Charge Pump Filter Connection (Output) - Power supply from the step-down charge

pump that provides the positive rail for the headphone and line amplifiers

Charge Pump Cap Common Node (Output) - Common positive node for the step-down and inverting

charge pumps’ flying capacitors.

Charge Pump Cap Negative Node (Output) - Negative node for the inverting charge pump’s flying

capacitor.

Inverting Charge Pump Filter Connection (Output) - Power supply from the inverting charge pump

that provides the negative rail for the headphone and line amplifiers.

1113Headphone Audio Ou tput (Output) - The full-scale output level is specified in the HP Output Charac-

teristics specification table

1416Line Audio Output (Output) - The full-scale output level is specified in the Line Output Characteristics

specification table

8 DS773F1

Page 9

CS42L55

VA 17 Analog Power (Input) - Power supply for the internal analog section.

AGND 18 Analog Ground (Input) - Ground reference for the internal analog section.

FILT+ 19 Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.

VQ 20 Quiescent Voltage (Output) - Filter connection for the internal quiescent voltage.

AFILTA

AFILTB

AIN2A

AIN2B

AIN1A

AIN1B

AIN2REF

AIN1REF

HPDETECT 29

21

Antialias Filter Connection (Output) - Antialias filter connection for the ADC inputs.

22

23

25

Analog Input (Input) - The full-scale level is specified in the Analog Input Characteristics specification

26

table.

28

2427Pseudo Diff. Analog Input Reference (Input) - Ground reference for the programmable gain amplifi-

ers (PGA).

Headphone Detect (Input) - Powers down the left and/or right channel of the line and/or headphone

outputs as described in “Headphone Power Control” on page 43 and “Line Power Control” on page 43.

RESET

VLDO 31 Low Dropout Regulator (LDO) Power (Input) - Power supply for the LDO regulator.

VDFILT 32

VL 33

SDOUT 34 Serial Audio Data Output (Output) - Output for two’s complement serial audio data.

MCLK 35 Master Clock (Input) - Clock source for the delta-sigma modulators.

SCLK 36 Serial Clock (Input/Output) - Serial clock for the serial audio interface.

GND/

Thermal Pad

30 Reset (Input) - The device enters a low power mode when this pin is driven low.

Low Dropout Regulator (LDO) Filter Connectio n (Output) - Power supply from the LDO regulator

that provides the low voltage power to the digital section.

Digital Interface Power (Input) - Determines the required signal level for the serial audio inte rface

and I²C control port.

Ground reference for the internal charge pump and digital section; thermal relief pad. See “QFN Ther-

-

mal Pad” on page 68 for more information.

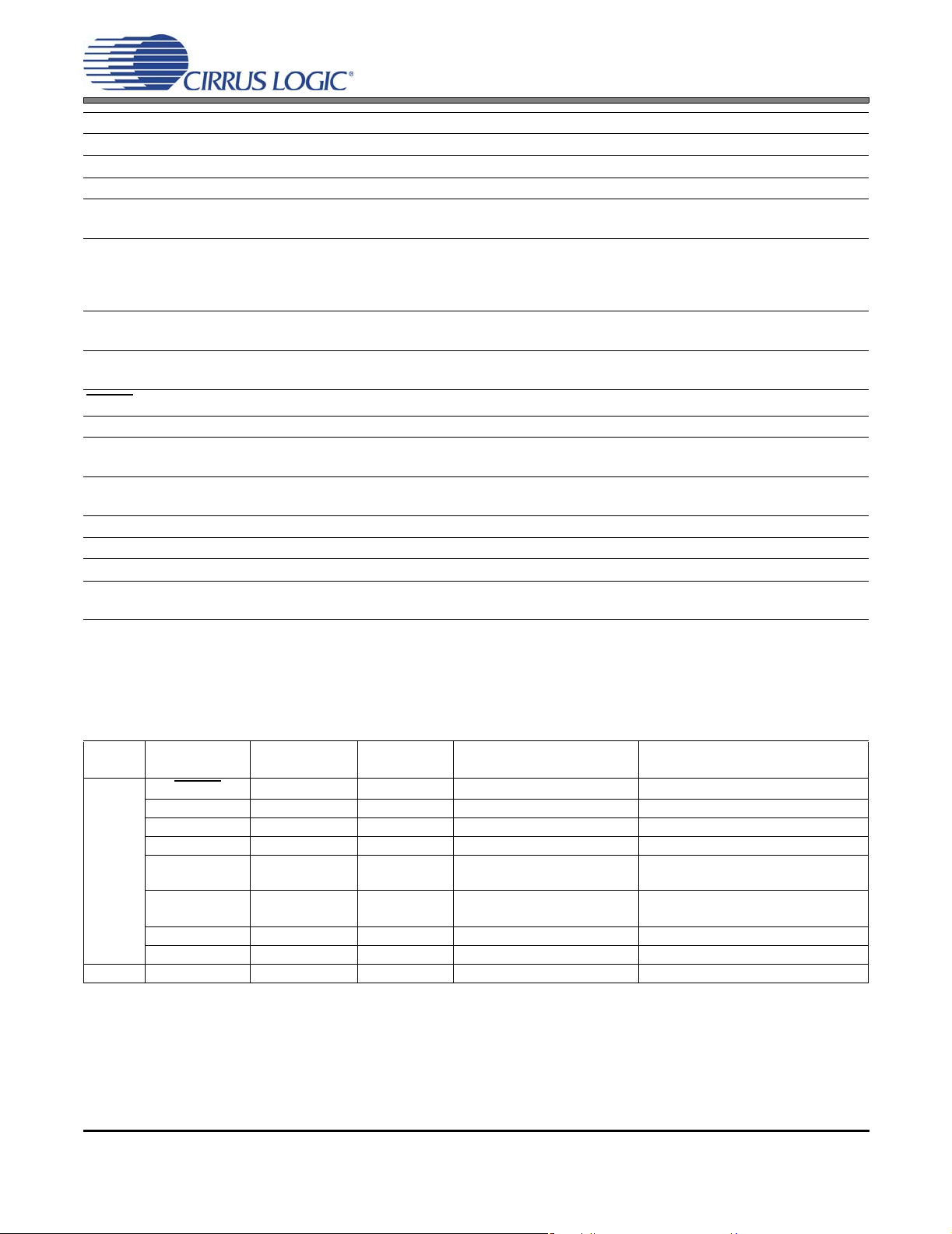

1.1 I/O Pin Characteristics

Input and output levels and associated power supply voltage are shown in the table below. Logic levels

should not exceed the corresponding power supply voltage.

Power

Supply

VL

VA HPDETECT Input - - 1.8 V - 2.5 V, with Hysteresis

Pin Name I/O Internal

Connections

RESET

SCL Input - - 1.8 V - 3.3 V, with Hysteresis

SDA Input/Output - CMOS/Open Drain 1.8 V - 3.3 V, with Hysteresis

MCLK Input - - 1.8 V - 3.3 V

LRCK Input/Output

SCLK Input/Output

SDOUT Output - 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

SDIN Input - - 1.8 V - 3.3 V

Input - - 1.8 V - 3.3 V, with Hysteresis

Weak Pull-up

(~1 MΩ)

Weak Pull-up

(~1 MΩ)

Driver Receiver

1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

DS773F1 9

Page 10

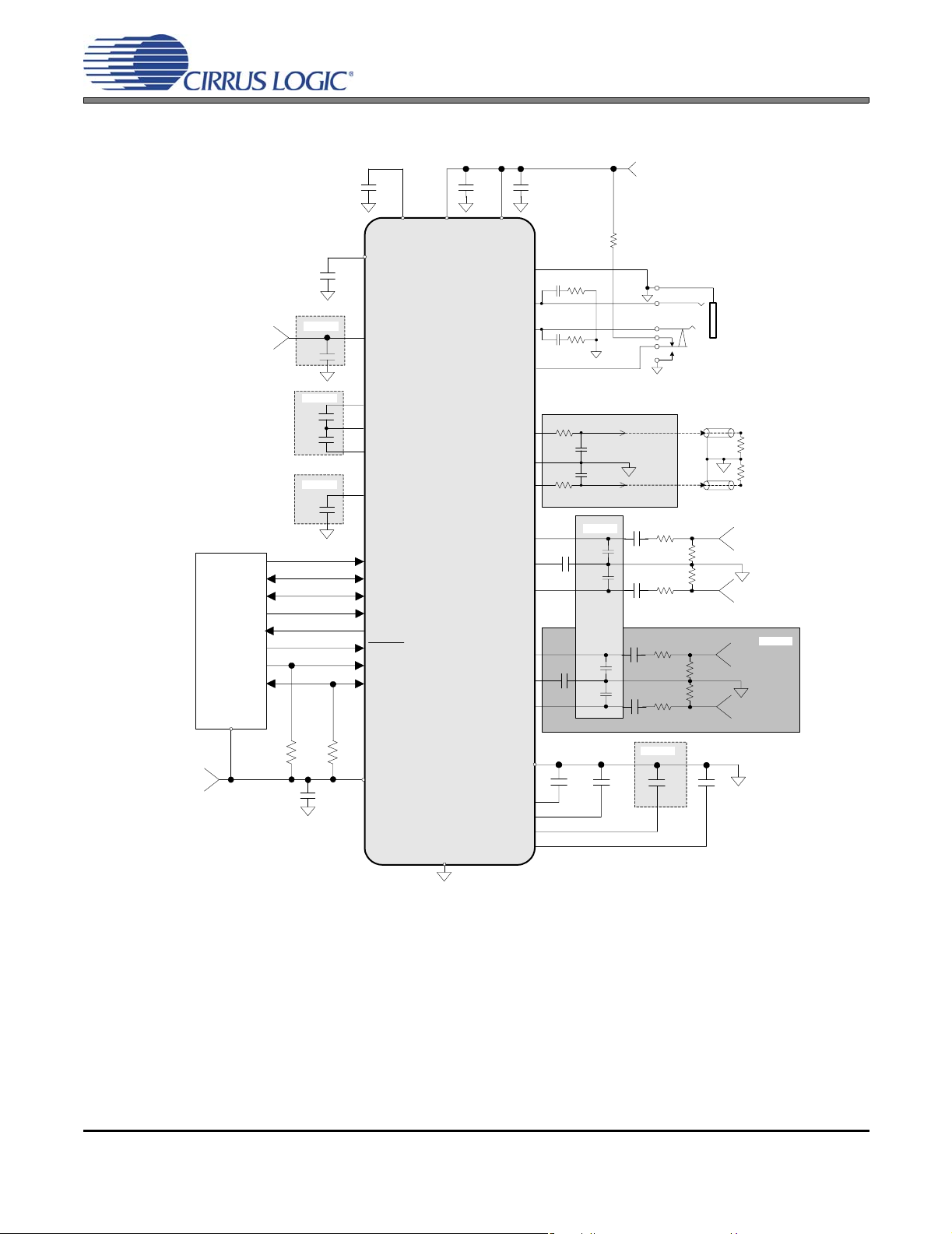

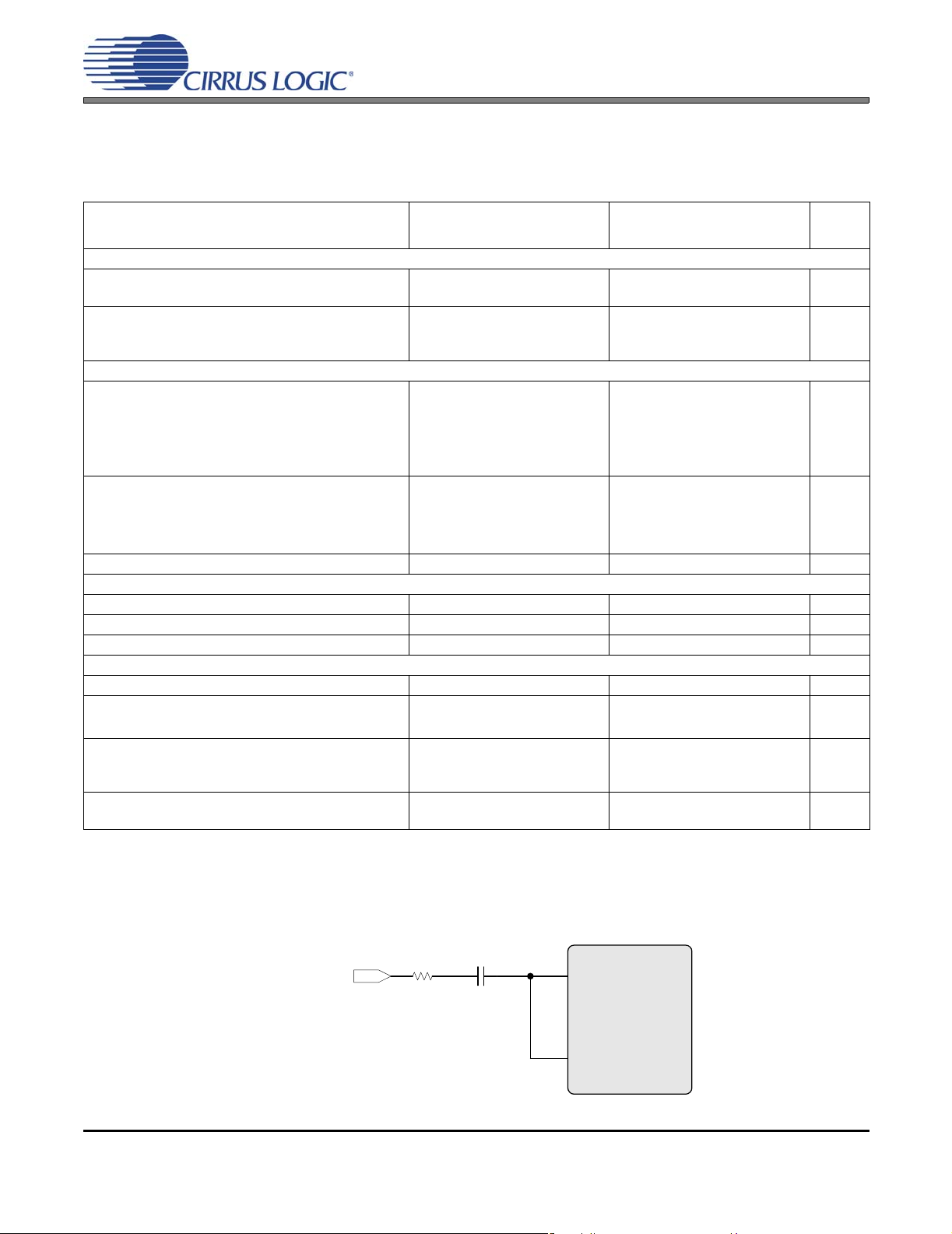

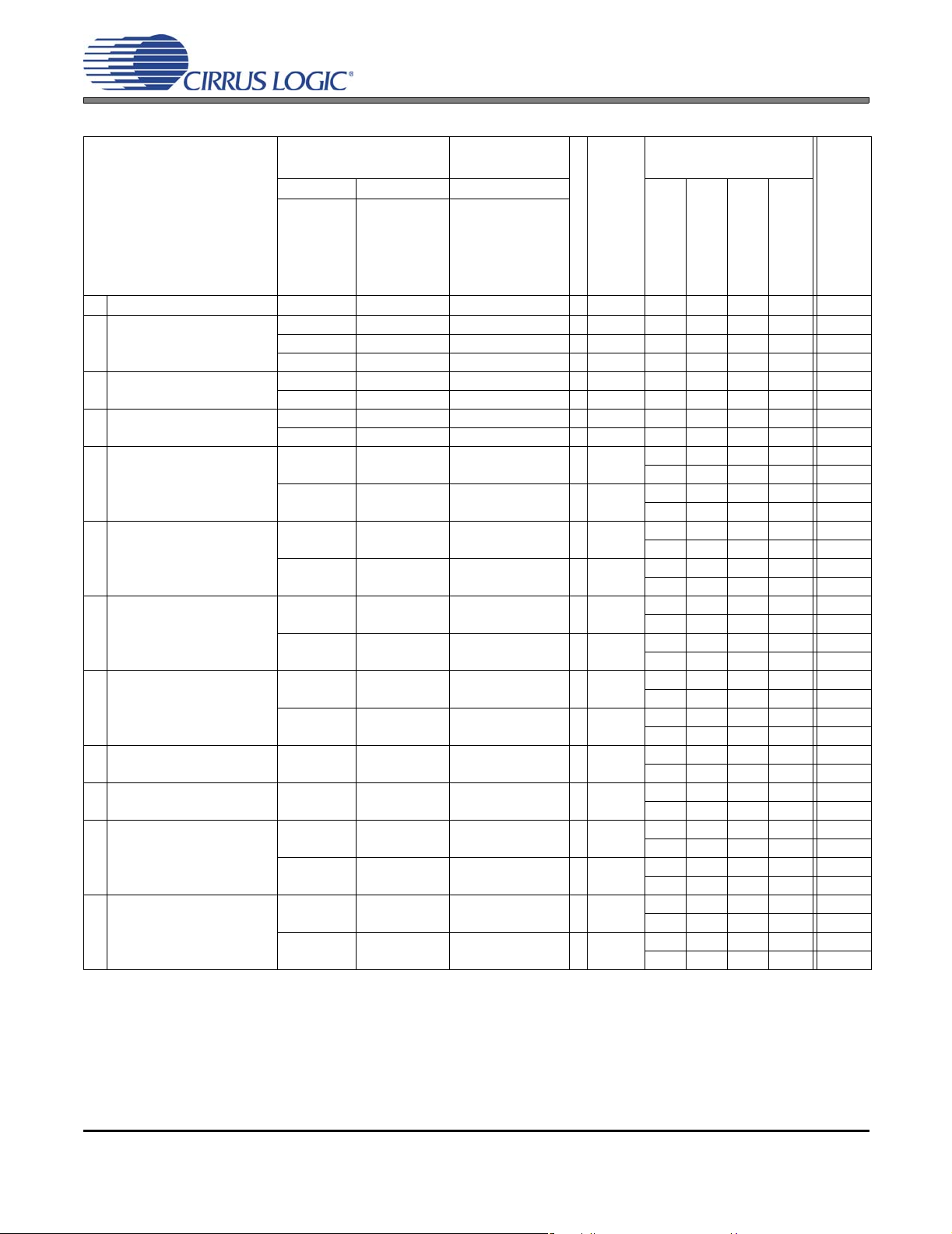

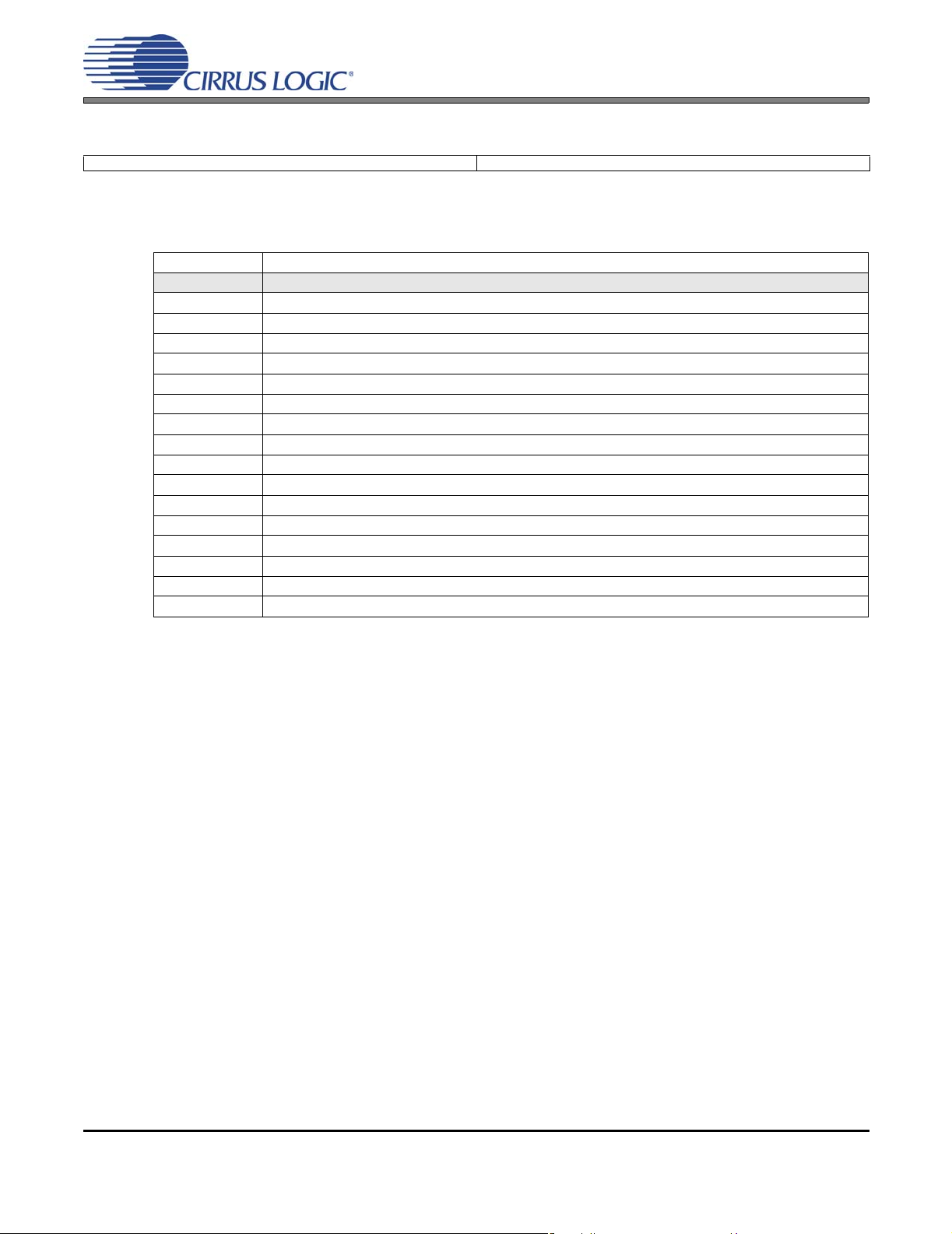

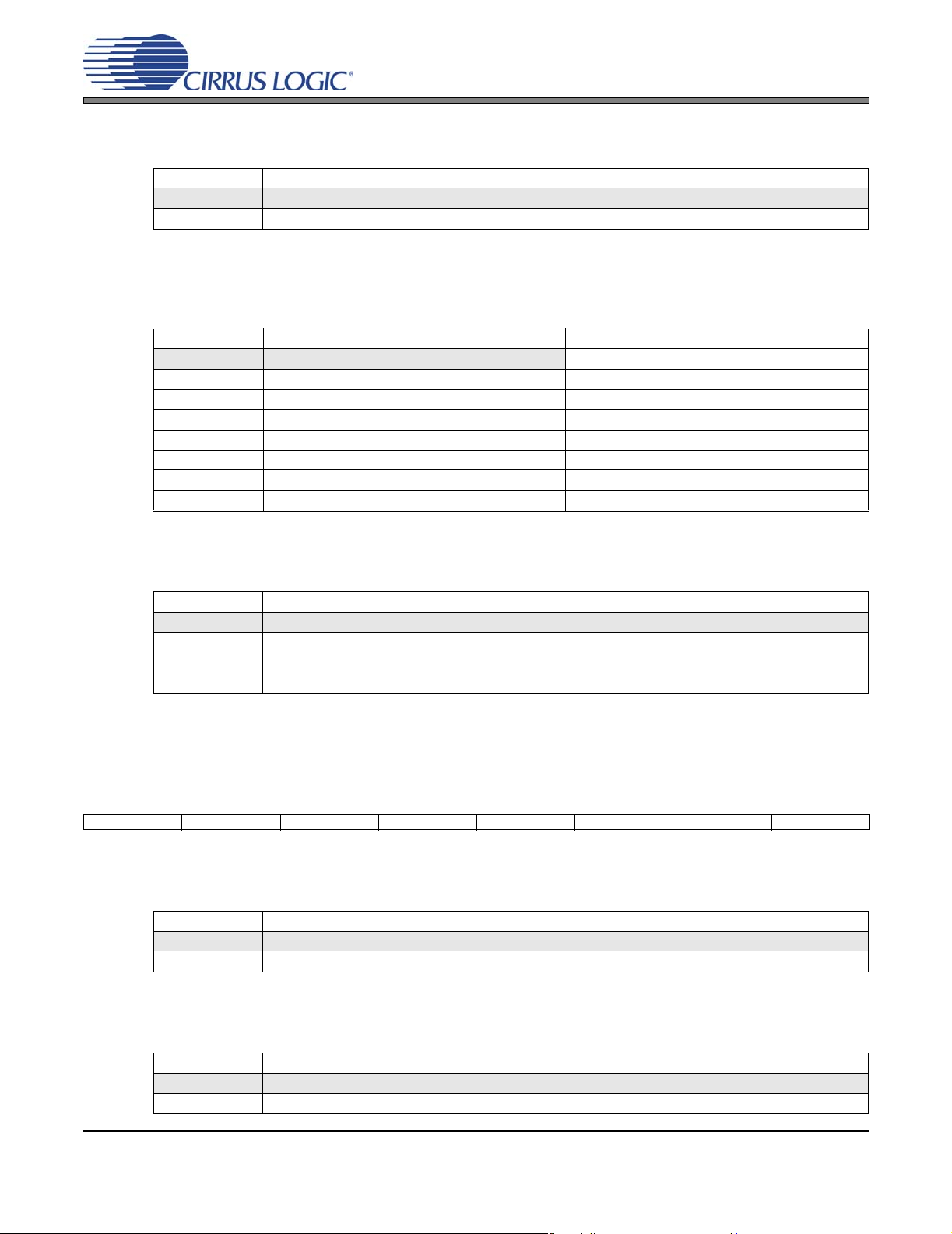

2. TYPICAL CONNECTION DIAGRAM

1 µF

** **

0.1 µF

CS42L55

0.1 µF

**

+1.65 V to +2.71 V

VA

HPREF

HPOUTB

HPOUTA

0.1 µF

**

**

0.1 µF

47 kΩ

33 Ω

33 Ω

+1.65 V to +2.71 V

2.2 µF

2.2 µF

Note 1

**

**

VDFILT

+VHPFILT

VCP

VLDO

HPDETECT

CS42L55

LINEOUTA

LINEREF

LINEOUTB

AIN1A

AIN1REF

AIN1B

AIN2A

AIN2REF

AIN2B

562 Ω

562 Ω

1 µF

1 µF

3300 pF

*

*

3300 pF

Note 4

1800 pF

**

1800 pF

1800 pF

**

1800 pF

Digital Audio

Processor

2 kΩ

Note 2

2.2 µF

2.2 µF

Note 1

2.2 µF

2 k

FLYP

**

FLYC

**

FLYN

-VHPFILT

**

MCLK

SCLK

LRCK

SDIN

SDOUT

RESET

SCL

SDA

Ω

AGND

+1.65 V to +3.47 V

0.1 µF

VL

**

AFILTA

*

1000 pF

1000 pF

AFILTB

VQ

GND/Thermal Pad

Notes:

1. The headphone amplifier’s output power and distortion are rated using the nominal capacitance shown. Larger capacitance

reduces the ripple on the internal amplifiers’ supplies and in turn reduces the amplifier’s distortion at high output power levels.

Smaller capacitance may not sufficiently reduce ripple to achieve the rated output power and distortion. Since the actual value

of typical X7R/X5R ceramic capacitors deviates from the nominal value by a percentage specified in the manufacturer’s data

sheet, capacitors should be selected based on the minimum output power and maximum distortion required.

2. The headphone amplifier’s output power and distortion are rated using the nominal capacitance shown and using the default

charge pump switching frequency. The required capacitance follows an inverse relationship with the charge pump’s switching

frequency. When increasing the switching frequency, the capacitance may decrease; when lowering the switching frequency,

the capacitance must increase. Since the actual value of typical X7R/X5R ceramic capacitors deviates from the nominal value

by a percentage specified in the manufacturer’s data sheet, capacitors should be selected based on the minimum output

power, maximum distortion and maximum charge pump switching frequency required.

3. Additional bulk capacitance may be added to improve PSRR at low frequencies.

4. These capacitors serve as a charge reservoir for the internal switched capacitor ADC modulators and should be placed as

close as possible to the inputs. They are only needed when the PGA (Programmable Gain Amplifier) is bypassed.

5. Input pairs (such as AIN2A, AIN2REF and AIN2B) may be left floating if they are not used.

FILT+

Headphone Out

Left & Right

LPF is Optional

**

*

1 µF

*

**

1 µF

**

*

1 µF

*

**

1 µF

Note 3

*

*

NPO/C0G dielectric capacitors.

**

Low ESR, X7R/X5R dielectric capacitors.

100 Ω

100 Ω

100 Ω

100 Ω

**

2.2 µF

100 kΩ

100 kΩ

100 kΩ

100 kΩ

R

R

**

2.2 µF

ext

Line Level Out

Left & Right

ext

Analog

Input 1

Note 5

Analog

Input 2

Figure 1. Typical Connection Diagram

10 DS773F1

Page 11

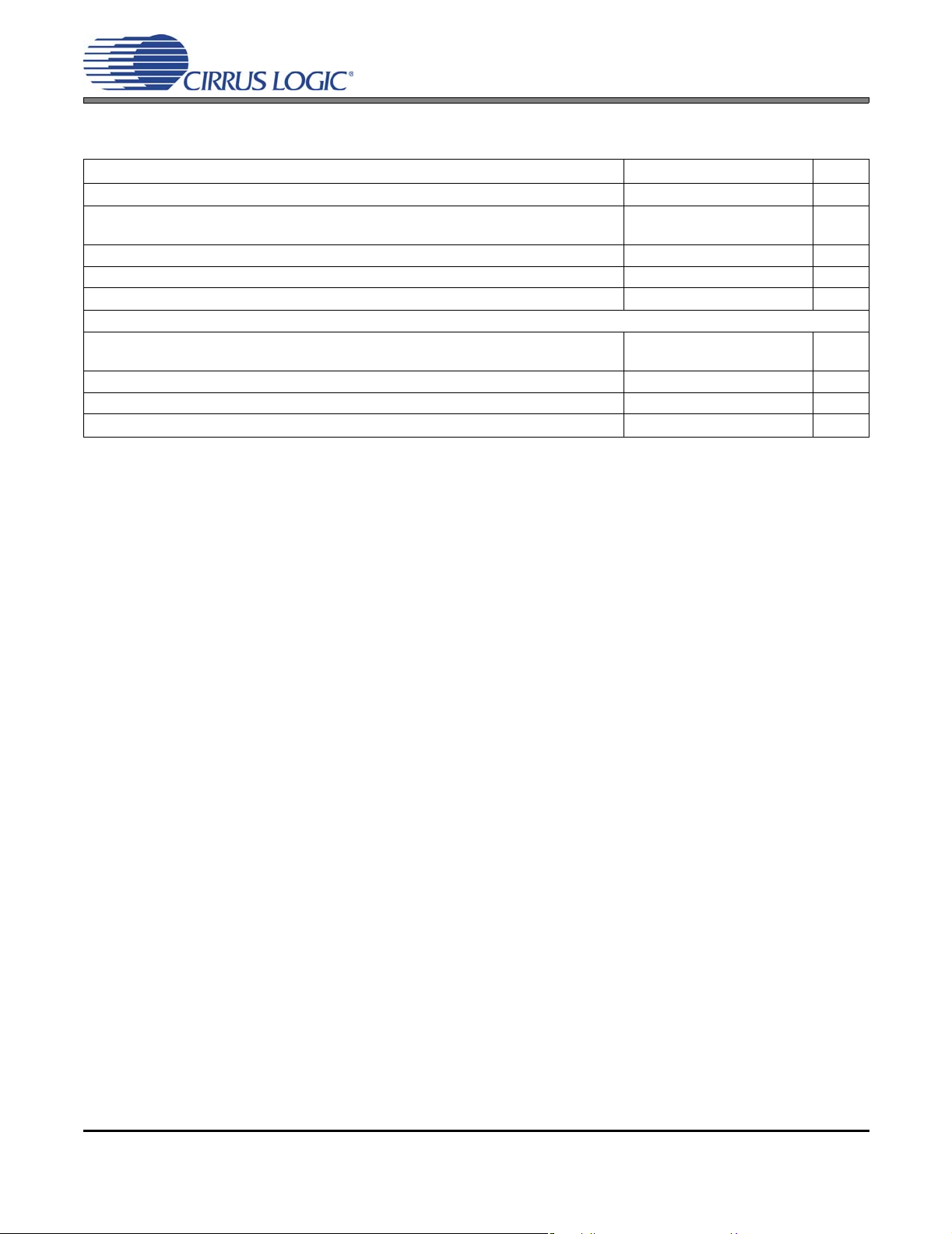

3. CHARACTERISTIC AND SPECIFICATION TABLES RECOMMENDED OPERATING CONDITIONS

GND = AGND = 0 V, all voltages with respect to ground.

Parameters Symbol Min Max Units

DC Power Supply

Analog

Charge Pump

LDO Regulator for Digital

Serial/Control Port Interface

Ambient Temperature Commercial - CNZ

VA 1.65 2.71 V

VCP 1.65 VA V

VLDO 1.65 2.71 V

VL 1.65 3.47 V

T

A

ABSOLUTE MAXIMUM RATINGS

GND = AGND = 0 V; all voltages with respect to ground.

Parameters Symbol Min Max Units

DC Power Supply Analog, Charge Pump, LDO

Serial/Control Port Interface

Input Current (Note 2)

Analog Input Voltage (Note 3) V

Digital Input Voltage (Note 3)

VA, VCP, VLDOVL-0.3

I

in

IN

V

IND

CS42L55

-40 +85 °C

3.0

-0.3

-±10mA

AGND-0.7 VA+0.7

-0.3 VL+0.4 V

4.0

V

V

V

Ambient Operating Temperature (power applied)

Storage Temperature

T

A

T

stg

-50 +115 °C

-65 +150 °C

WARNING:Operation at or beyond these limit s may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

Notes:

1. Due to the existence of parasitic body diodes between VCP and VA, cu rrent flows from VCP to V A whenever the VA power supply is lower than VCP. This causes a “back-powering” effect on the VA power

supply rails internal to the part. Hence VA should be maintained at an equal or greater voltage than VCP

at all times. While “back-powering” does not have any adverse effects on device operation with respect

to performance and reliability , it does lead to extra power consumption and therefore should be avoided.

2. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause

SCR latch-up.

3. The maximum over/under voltage is limited by the input current.

DS773F1 11

Page 12

CS42L55

ANALOG INPUT CHARACTERISTICS

Test Conditions (unless otherwise specified): Connections to the CS42L55 are shown in the Figure 1. "Typical Connection Dia-

gram" on page 10; Input is a 1 kHz sine wave through the passive input filter, PGA = 0 dB; All Supplies = VA;

GND = AGND = 0 V; TA=+25°C; Measurement bandwidth is 20 Hz to 20 kHz. Sample Frequency = 48 kHz.

VA = 2.5 V VA = 1.8 V

Parameter

Analog In to ADC (PGA bypassed)

Dynamic Range A-weighted

Total Harmonic Distortion + Noise -1 dBFS

Analog In to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

PGA Setting: +12 dB A-weighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

-60 dBFS

PGA Setting: +12 dB -1 dBFS

Common Mode Rejection (Note 5)

DC Accuracy

Interchannel Gain Mismatch

Gain Drift

Offset Error (Note 6)

Input

Interchannel Isolation (1 kHz)

HP Amp to Analog Input Isolation R

Full-scale Input Voltage ADC

Input Impedance (Note 7) ADC

(Note 4)

unweighted

-20 dBFS

-60 dBFS

unweighted

unweighted

= 10 kΩ

L

RL = 16 Ω

PGA (0 dB)

PGA (+12 dB)

PGA

Min Typ Max Min Typ Max Unit

89

86

-

-

-

88

85

81

78

-

-

- -83 -77 - -81 -75 dB

-40--40-dB

- 0.2 - - 0.2 - dB

- ±100 - - ±100 - ppm/°C

- 352 - - 352 - LSB

-90--90-dB

-

-

0.76•VA

0.78•VA

-

-

95

92

-85

-72

-32

94

91

87

84

-87

-31

90

83

0.80•VA

0.82•VA

0.198•VA

60

40

-

-

-79

-

-26

-

-

-

-

-81

-25

-

-

0.84•VA

0.86•VA

-

-

86

83

-

-

-

85

82

78

75

-

-

-

-

0.76•VA

0.78•VA

-

-

92

89

-85

-69

-29

91

88

84

81

-85

-28

90

83

0.80•VA

0.82•VA

0.198•VA

60

40

-

-

-79

-

-23

-

-

-

-

-79

-22

-

-

0.84•VA

0.86•VA

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

Vpp

Vpp

kΩ

kΩ

4. Referred to the typical full-scale voltage. Applies to all THD+N and Dynamic Range values in the table.

5. See test figure shown below.

6.

SDOUT Code with HPFx=1;HPFRZx=0.

7. Measured between AINxx and AGND.

100 mVPP,

25 Hz

100 Ω

1 μF

AINxA

AINxREF

Figure 2. CMRR Test Configuration

12 DS773F1

Page 13

ADC DIGITAL FILTER CHARACTERISTICS

Parameter (Note 8) Min Typ Max Unit

Frequency Response (20 Hz to 20 kHz)

Passband to -0.05 dB corner

to -3 dB corner

Stopband

Stopband Attenuation

Total Group Delay

High-Pass Filter Characteristics (48 kHz Fs) (Note 9)

Passband to -3.0 dB corner

to -0.05 dB corner

Passband Ripple

Phase Deviation @ 20 Hz

Filter Settling Time (Note 10)

Notes:

8. Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 27 to 30 on

page 70) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

HPF parameters are for Fs = 48 kHz.

9. Characteristics are based on the default setting in register “HPF Control (Address 09h)” on page 47.

10. Settling time decreases at higher corner frequency settings.

CS42L55

-0.07 - +0.02 dB

-

-

0.52 - - Fs

33 - - dB

- 7.6/Fs - s

-

-

- - 0.15 dB

-5.3-Deg

-

0.421

0.495

1.87

17.15

5

10

/Fs

-

-

-

-

-s

Fs

Fs

Hz

Hz

DS773F1 13

Page 14

CS42L55

HP OUTPUT CHARACTERISTICS

Test conditions (unless otherwise specified): Connections to the CS42L55 are shown in the “Typical Connection Diagram” on

page 10; Input test signal is a full-scale 997 Hz sine wave; All Supplies = VA, VCP Mode; GND = AGND = 0 V; TA = +25°C;

Measurement bandwidth is 20 Hz to 20 kHz; Sample Frequency = 48 kHz; Test load R

and test load R

=16 Ω, CL = 150 pF for a headphone load. (See Figure 3 on page 15).

L

VA = 2.5 V VA = 1.8 V

Parameter

Line Load RL = 3 kΩ (+2 dB Analog Gain)(Note 12)

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

16-Bit 0 dB

Full-scale Output Voltage (Note 13)

HP Load RL = 16 Ω (-4 dB Analog Gain)(Note 12)

Dynamic Range

18 to 24-Bit A-weighted

16-Bit A-weighted

Total Harmonic Distortion + Noise

Full-scale Output Voltage

Output Power (Note 13)

Other Characteristics for RL = 16 Ω or 3 k

Interchannel Isolation 3 kΩ

Interchannel Gain Mismatch

Output Offset Voltage (Note 14) DAC to HPOUT

Gain Drift

AC-Load Resistance (R

Load Capacitance (C

(Note 11)

unweighted

-20 dB

-60 dB

-20 dB

-60 dB

unweighted

unweighted

Ω

16 Ω

) (Note 14)

L

) (Note 14)

L

Min Typ Max M in Typ Max Unit

92

89

-

-

-

-

-

-

-

-

1.56•VA 1.64•VA 1.73•VA 1.56•VA 1.64•VA 1.73•VA V

89

86

-

-

- -75 -69 - -75 -69 dB

0.76•VA 0.82•VA 0.88•VA 0.76•VA 0.82•VA 0.88•VA V

-32--17-mW

-

-

- 0.1 0.25 - 0.1 0.25 dB

- 0.5 1.0 - 0.5 1.0 mV

- ±100 - - ±100 - ppm/°C

16 - - 16 - - Ω

- - 150 - - 150 pF

98

95

96

93

-84

-76

-36

-82

-74

-34

95

92

93

90

90

90

= 3 kΩ, CL= 150 pF for a Line Load,

L

-

-

-

-

-78

-

-30

-

-

-

-

-

-

-

-

-

90

87

88

85

96

93

-

-

-

-

-

-

-

-

-

-

-

-

94

91

-85

-74

-34

-83

-72

-32

94

91

92

89

90

90

-

-

-

-

-79

-

-28

-

-

-

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

PP

dB

dB

dB

dB

PP

dB

dB

14 DS773F1

Page 15

CS42L55

LINE OUTPUT CHARACTERISTICS

Test conditions (unless otherwise specified): Connections to the CS42L55 are shown in the “Typical Connection Diagram” on

page 10; Input test signal is a full-scale 997 Hz sine wave; All Supplies = VA, VCP Mode; GND = AGND = 0 V; TA = +25 °C;

Measurement bandwidth is 20 Hz to 20 kHz; Sample Frequency = 48 kHz; Test load R

page 15).

VA = 2.5 V VA = 1.8 V

Parameter

(+2 dB Analog Gain) (Note 12)

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

16-Bit 0 dB

Full-scale Output Voltage (Note 13)

Other Characteristics

Interchannel Isolation

Interchannel Gain Mismatch

Output Offset Voltage (Note 14) DAC to LINEOUT

Gain Drift

Output Impedance

AC-Load Resistance (RL) (Note 14)

Load Capacitance (C

(Note 11)

unweighted

-20 dB

-60 dB

-20 dB

-60 dB

) (Note 14)

L

Min Typ Max Min Typ Max Unit

93

90

-

-

-

-

-

-

-

-

1.50•VA 1.58•VA 1.66•VA 1.50•VA 1.58•VA 1.66•VA V

-90--90-dB

- 0.1 0.25 - 0.1 0.25 dB

-0.51.0-0.21.0mV

- ±100 - - ±100 - ppm/°C

- 100 - - 100 - Ω

3--3--kΩ

- - 150 - - 150 pF

99

96

96

93

-84

-76

-36

-82

-74

-34

= 3 kΩ, CL = 150 pF (see Figure 3 on

L

-

-

-

-

-78

-

-30

-

-

-

91

88

97

94

-

-

-

-

-

-

-

-

94

91

-86

-74

-34

-84

-72

-32

-80

-28

-

-

-

-

dB

dB

dB

dB

dB

-

dB

dB

-

-

-

dB

dB

dB

PP

Notes:

11. One-half LSB of triangular PDF dither is added to data.

12. The Analog Gain setting (refer to “ Headphone Volume Control” on page 57 or “Line Volume Control” on

page 58) must be configured as indicated to achieve the specified output characteristics. Hi gh gain set-

tings at certain VA and VCP supply levels may cause clipping when the audio signal approaches fullscale, maximum power output.

13. VCP settings lower than VA reduces the headroom of the headphone amplifier. As a result, the specified THD+N performance at full-scale output voltage and power may not be achieved.

14. See Figure 3 and Figure 4 on page 15. Refer to “Parameter Definitions” on page 71.

Test Load

CL=150 pF

RL=3 kΩ

-

Measurement

Device

+

HPOUTx

GND/AGND

HPREF

33 Ω

0.1 μF

Test Load

CL=150 pF

RL=16 Ω or

3 k

Ω

-

Measurement

Device

LINEOUTx

LINEREF

GND/AGND

+

Figure 3. HP Output Test Configuration Figure 4. Line Output Test Configuration

DS773F1 15

Page 16

CS42L55

ANALOG PASSTHROUGH CHARACTERISTICS

Test Conditions (unless otherwise specified): Connections to th e CS42L55 are shown in the “Typical Connection Diagram” on

page 10; Input is a 1 kHz sine wave through the passive input filter shown in Figure 1, PGA and HP/Line gain = 0 dB; All Sup-

plies = VA, VCP Mode; GND = AGND = 0 V; TA = +25 °C; Measurement bandwidth is 20 Hz to 20 kHz. Sample Frequency =

48 kHz.

VA = 2.5 V VA = 1.8 V

Parameter

Analog In to HP Amp (ADC is powered down)

R

= 3 kΩ (+2 dB Output Analog Gain)(Note 12)

L

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise -1 dB

-20 dB

-60 dB

Full-scale Input Voltage

Full-scale Output Voltage

Passband Ripple

= 16 Ω (-4 dB Output Analog Gain)(Note 12)

R

L

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise -1 dB

-20 dB

-60 dB

Full-scale Input Voltage

Output Power (Note 13)

Passband Ripple

Analog In to Line Amp (ADC is powered down)

RL = 3 kΩ (+2 dB Output Analog Gain) (Note 12)

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise -1 dB

-20 dB

-60 dB

Full-scale Input Voltage

Full-scale Output Voltage

Passband Ripple

Min Typ Max Min Typ Max Unit

-

-

-

-

-

- 0.80•VA - - 0.80•VA - Vpp

- 0.93•VA - - 0.93•VA - Vpp

-

-

-

-

-

- 0.80•VA - - 0.80•VA - Vpp

-12--6.5-mW

- 0/-0.3 - - 0/-0.3 - dB

-

-

-

-

-

- 0.80•VA - - 0.80•VA - Vpp

- 0.89•VA - - 0.89•VA - Vpp

94

91

-70

-71

-31

0/-0.3 0/-0.3 dB

94

91

-70

-71

-31

94

91

-70

-71

-31

0/-0.3 0/-0.3 dB

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

91

88

-80

-68

-28

91

88

-80

-68

-28

91

88

-80

-68

-28

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

Parameter (Note 15) Min Typ Max Unit

Frequency Response 20 Hz to 20 kHz Fs = 48.000 kHz

Fs = 44.118 kHz

Passband to -0.05 dB corner

to -3 dB corner

Stopband

Stopband Attenuation (Note 16)

Total Group Delay

De-emphasis Error Fs = 44.118 kHz

-0.04

-0.14

-

-

0.55 - - Fs

49 - - dB

-9/Fs -s

- - +0.05/-0.25 dB

Notes:

15. Response is clock dependent and will scale with Fs. Note that the response plots (Figures 31 to 34 on

page 70) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

16. Measurement bandwidth is from Stopband to 3 Fs.

16 DS773F1

-

-

0.48

0.49

+0.04

+0.14

-

-

dB

dB

Fs

Fs

Page 17

CS42L55

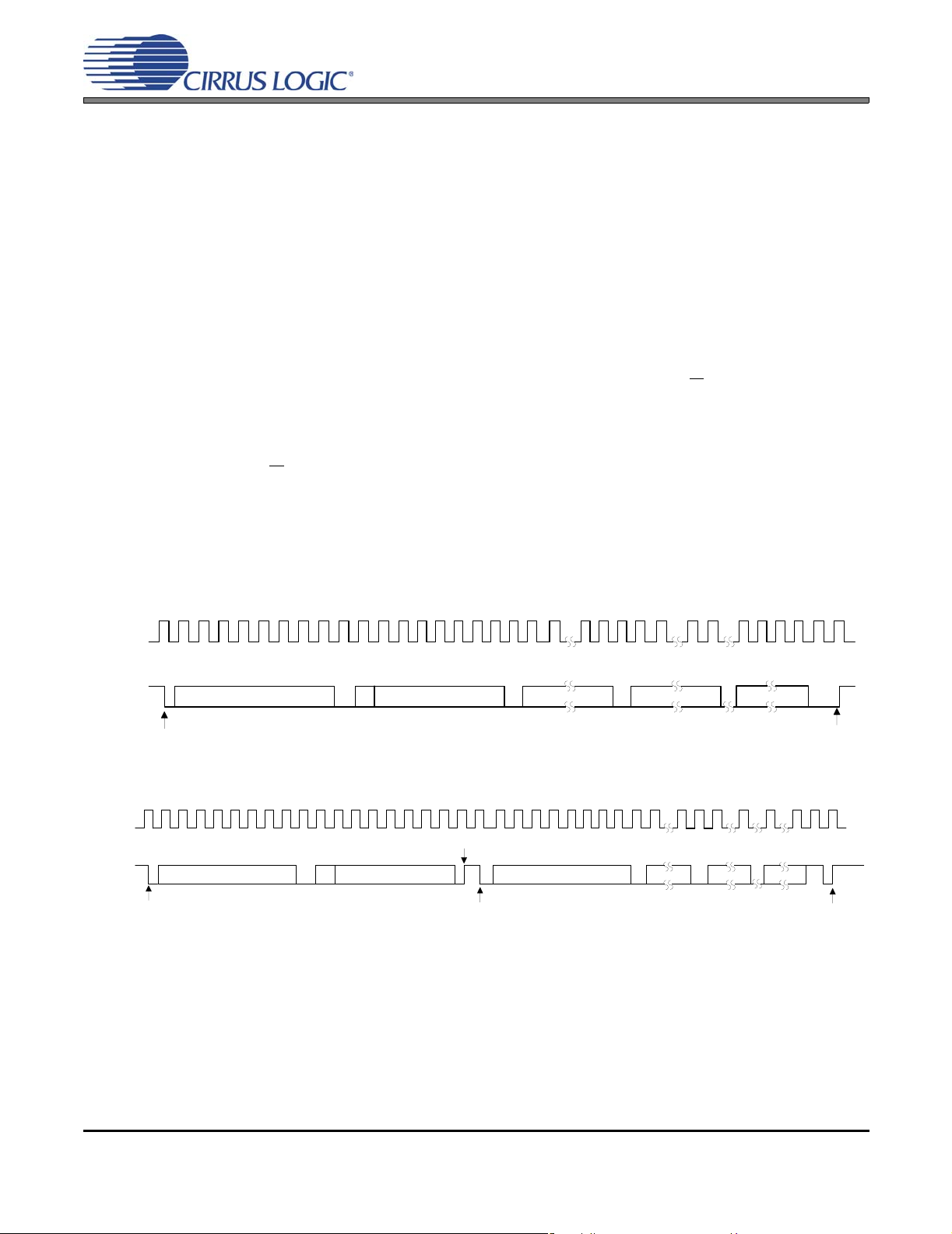

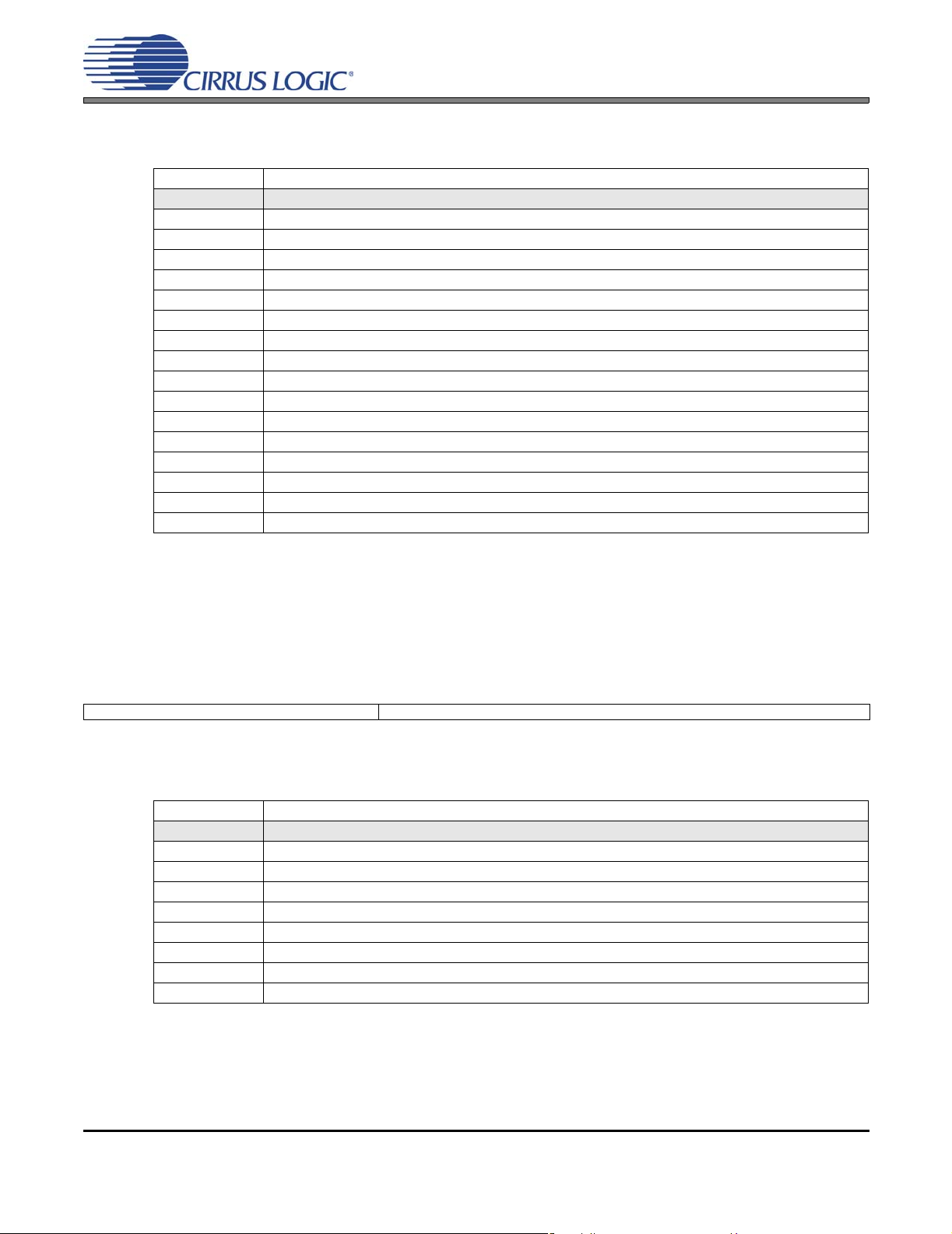

SWITCHING SPECIFICATIONS - SERIAL PORT

Inputs: Logic 0 = GND = AGND, Logic 1 = VL, LRCK, SCLK, SDOUT C

Parameters Symbol Min Max Units

RESET pin Low Pulse Width (Note 17)

MCLK Frequency

MCLK Duty Cycle 45 55 %

Slave Mode (Figure 5)

Input Sample Rate (LRCK) F

LRCK Duty Cycle 45 55 %

SCLK Frequency 1/t

SCLK Duty Cycle 45 55 %

LRCK Setup Time Before SCLK Rising Edge t

SDOUT Setup Time Before SCLK Rising Edge t

SDOUT Hold Time After SCLK Rising Edge t

SDIN Setup Time Before SCLK Rising Edge t

SDIN Hold Time After SCLK Rising Edge t

Master Mode (Figure 6)

Output Sample Rate (LRCK) All Speed Modes

LRCK Duty Cycle 45 55 %

SCLK Frequency SCLK = MCLK mode 1/t

All Other Modes 1/t

SCLK Duty Cycle RATIO[1:0] = ‘11’ 45 55 %

RATIO[1:0] = ‘01’ (Note 18) 33 66 %

LRCK Time Before SCLK Falling Edge t

SDOUT Setup Time Before SCLK Rising Edge t

SDOUT Hold Time After SCLK Rising Edge t

SDIN Setup Time Before SCLK Rising Edge t

SDIN Hold Time After SCLK Rising Edge t

LOAD

= 15 pF.

ss(LK-SK)

ss(SDO-SK)

hs(SK-SDO)

ss(SD-SK)

hs

F

sm(LK-SK)

sm(SDO-SK)

hm(SK-SDO)

sm(SD-SK)

hm

s

Ps

s

Pm

Pm

1

(See “Serial Port Clocking”

on page 34)

-ms

MHz

(See “Serial Port Clocking”

on page 34)

- 68•F

s

40 - ns

20 - ns

30 - ns

20 - ns

20 - ns

(See “Serial Port Clocking”

on page 34)

- 12.0000 MHz

- 68•F

s

-±2ns

20 - ns

30 - ns

20 - ns

20 - ns

kHz

Hz

Hz

Hz

Notes: 17. After powering up the CS42L55, RESET should be held low after the power supplies and clocks are

settled. This specification is valid with the recommended capacitor on VDFILT.

18. The device will periodically extend the SCLK high time to compensate for the fractional MCLK/SCLK

ratio.

LRCK

SCLK

SDOUT

SDIN

t

ss(LK-SK)

//

//

t

P

//

//

t

ss(SDO-SK)

//

//

t

ss(SD-SK)

//

//

//

t

hs(SK-SDO)

//

MSB

//

t

MSB

//

hs

LRCK

SCLK

SDOUT

SDIN

t

sm(LK-SK)

//

//

//

//

t

Pm

//

//

t

sm(SDO-SK)

//

//

t

sm(SD-SK)

//

//

//

t

hm(SK-SDO)

//

MSB

//

t

hm

MSB

//

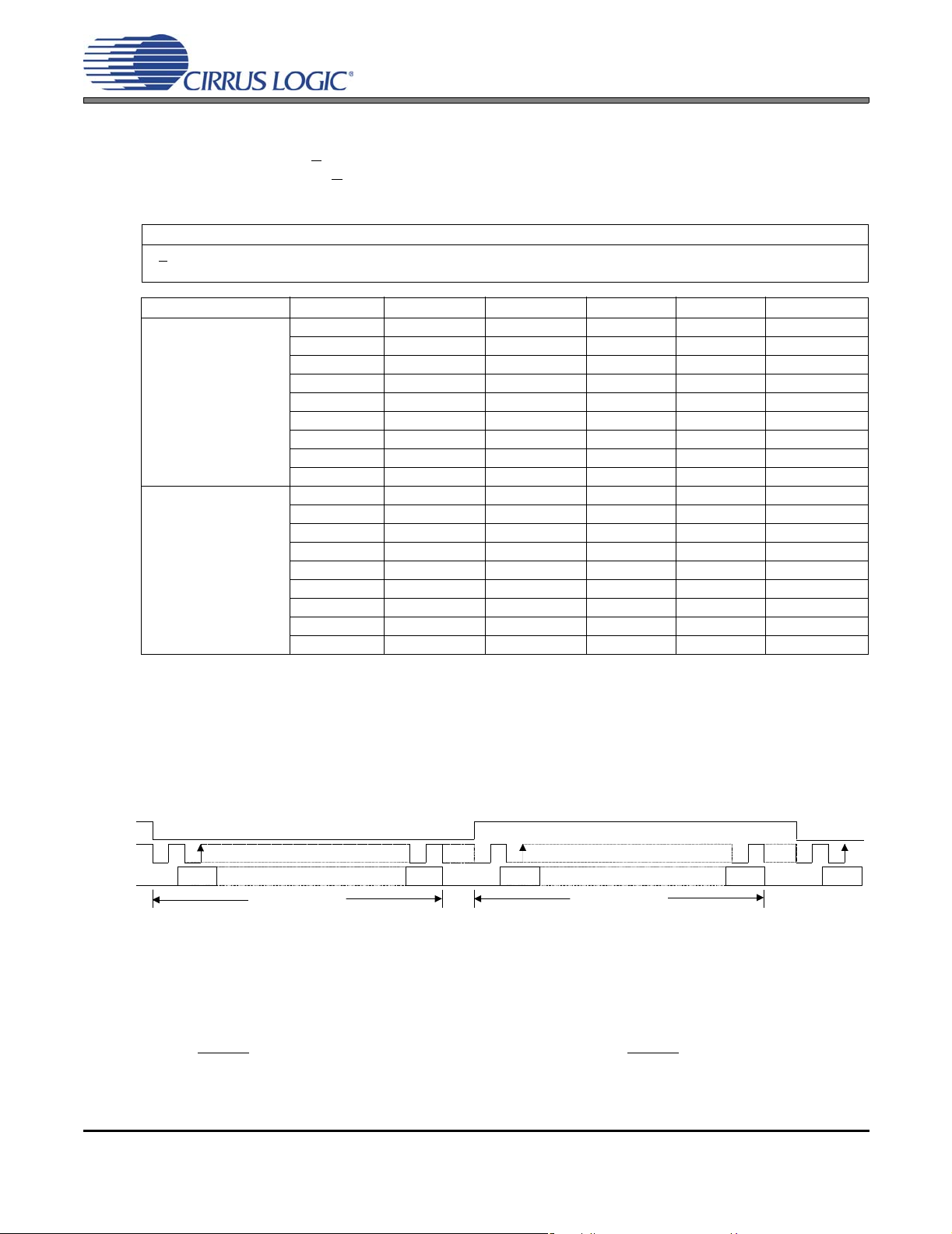

Figure 5. Serial Port Timing (Slave Mode) Figure 6. Serial Port Timing (Master Mode)

DS773F1 17

Page 18

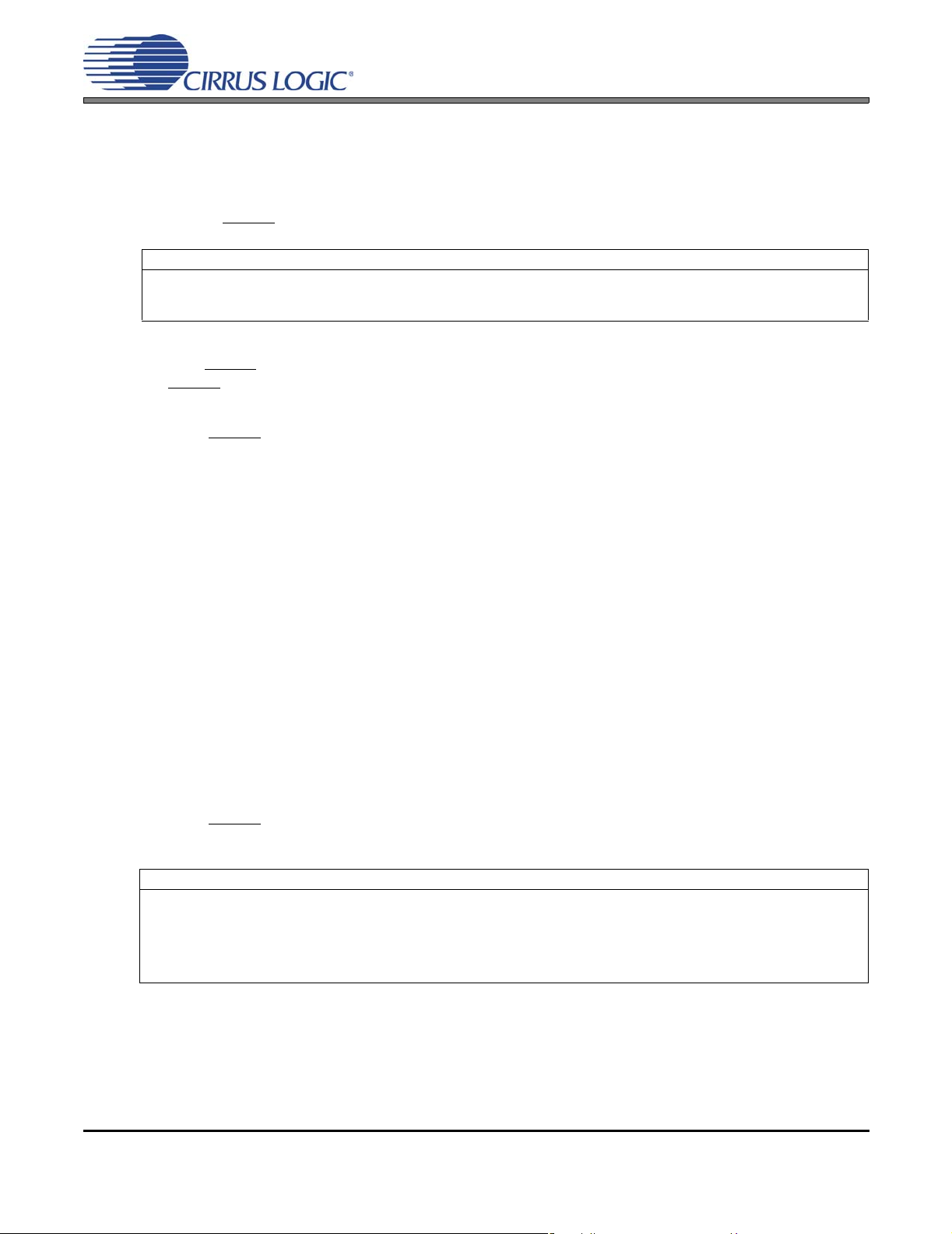

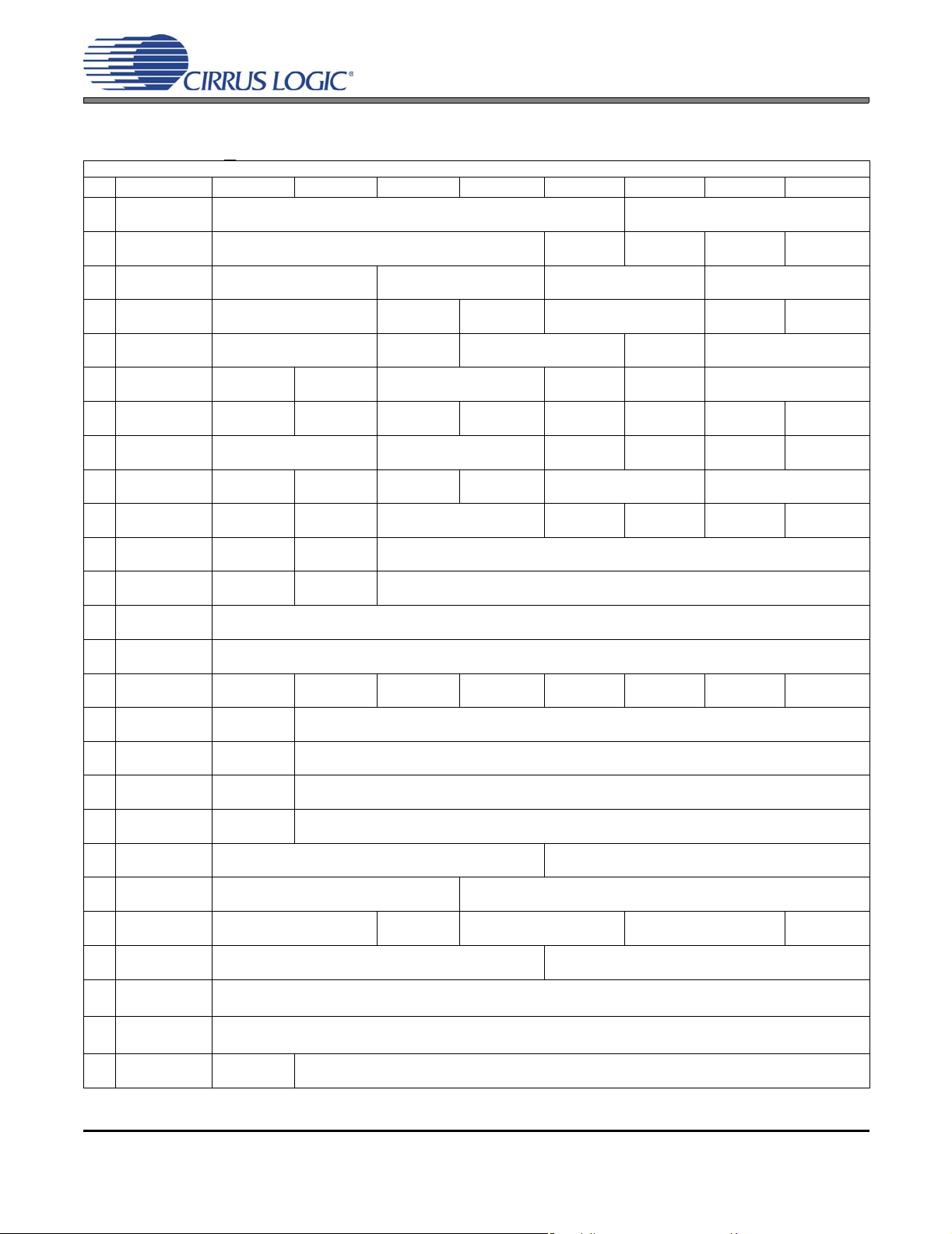

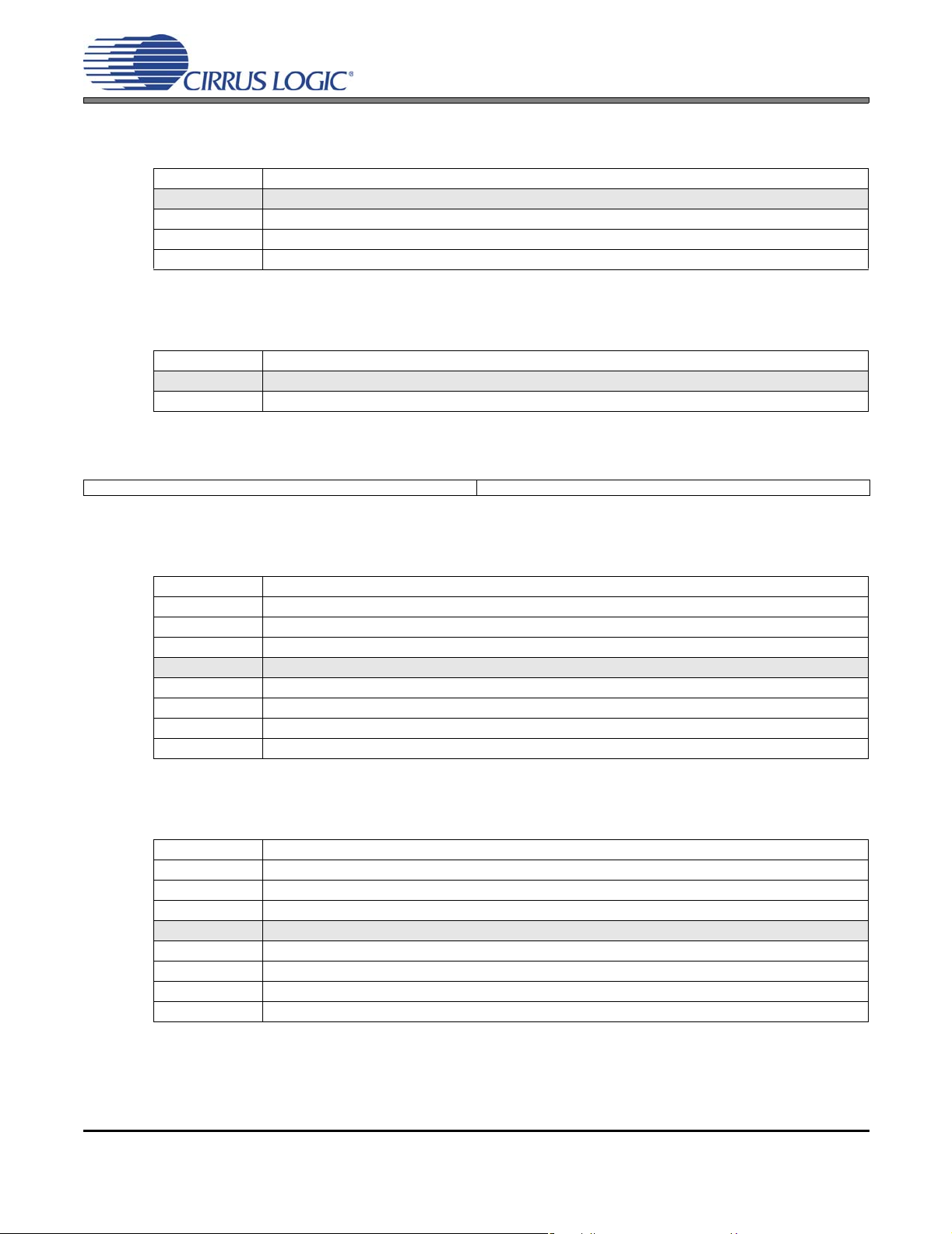

SWITCHING SPECIFICATIONS - CONTROL PORT

Inputs: Logic 0 = GND = AGND, Logic 1 = VL, SDA CL=30pF.

Parameter Symbol Min Max Unit

SCL Clock Frequency

RESET

Rising Edge to Start

Bus Free Time Between Transmissions

Start Condition Hold Time (prior to first clock pulse)

Clock Low time

Clock High Time

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling (Note 19)

SDA Setup time to SCL Rising

Rise Time of SCL and SDA

Fall Time SCL and SDA

Setup Time for Stop Condition

Acknowledge Delay from SCL Falling

Notes:

19. Data must be held for sufficient time to bridge the transition time, t

f

t

t

t

hdst

t

t

high

t

sust

t

hdd

t

sud

t

t

t

susp

t

ack

scl

irs

buf

low

rc

fc

CS42L55

- 100 kHz

500 - ns

4.7 - µs

4.0 - µs

4.7 - µs

4.0 - µs

4.7 - µs

0-µs

250 - ns

-1µs

- 300 ns

4.7 - µs

300 1000 ns

, of SCL.

fc

RESET

SDA

SCL

t

irs

Stop Start

t

buf

t

hdd

t

high

t

sud

t

t

hdst

low

Figure 7. I²C Control Port Timing

Repeated

Start

t

sust

t

hdst

Stop

t

f

t

r

t

susp

18 DS773F1

Page 19

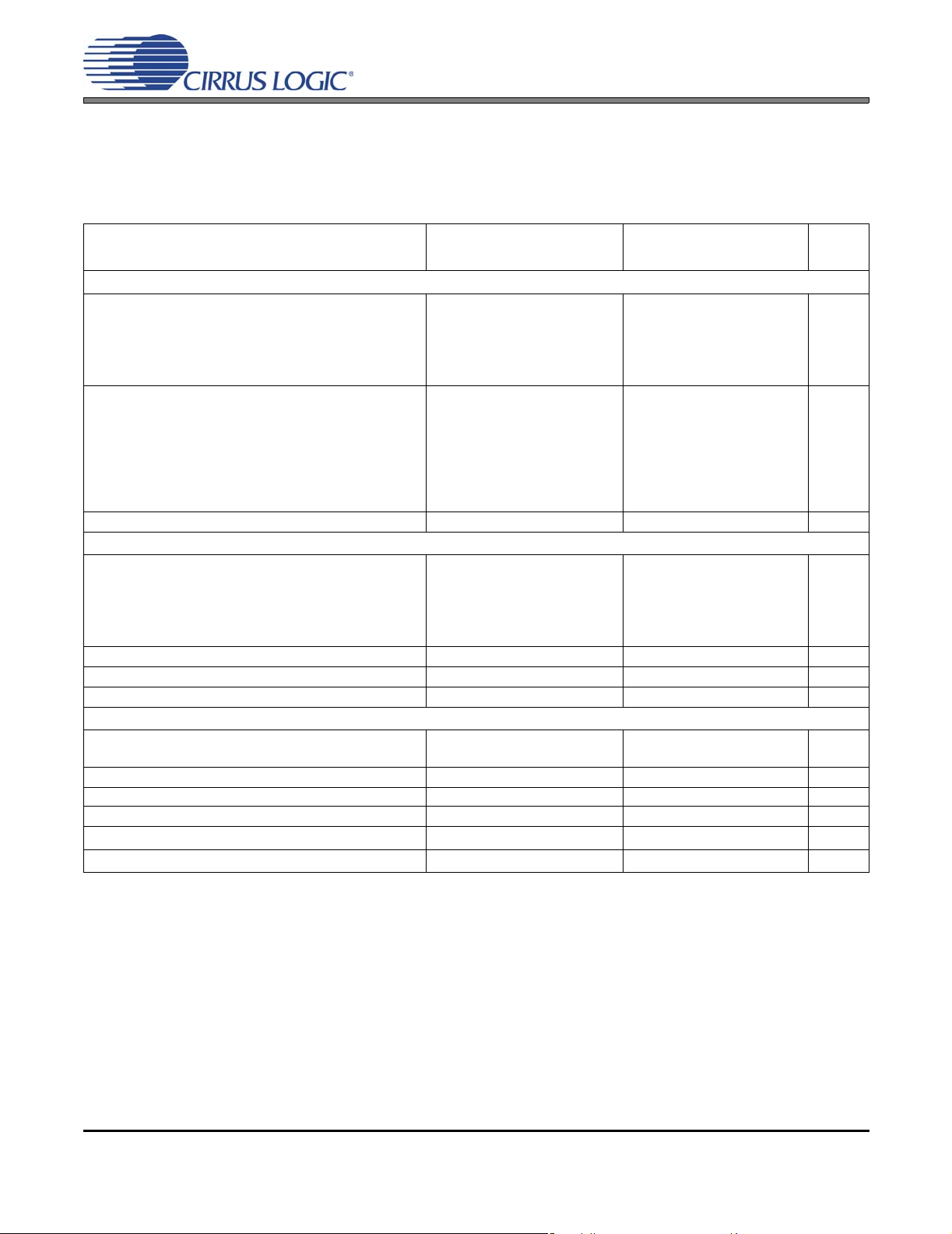

CS42L55

POWER SUPPLY REJECTION (PSRR) CHARACTERISTICS

Test Conditions (unless otherwise specified): Connections to the CS42L55 are shown in the “Typical Connection Diagram” on

page 10; GND = AGND = 0 V; all voltages with respect to ground.

Parameters Min Typ Max Units

PSRR with 100 mVpp, 1 kHz signal (Note 20) PGA to ADC

ADC

PGA to HP & Line Amps

DAC to HP & Line Amps

PSRR with 100 mVpp, 60 Hz signal (Note 20) PGA to ADC (Note 21)

ADC

PGA to HP & Line Amps

DAC to HP & Line Amps

-

-

-

-

-

-

-

-

55

50

50

50

35

25

50

60

-

-

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

Notes:

20. Valid with the recommended capacitor values on FILT+ and VQ, no load on HP and Line. Increasing

the capacitance on FILT+ and VQ will also increase the PSRR.

21. The PGA is biased with VQ, created by a resistor divider from the VA supply.

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS

Parameters (Note 22) Symbol Min Max Units

Input Leakage Current

Input Capacitance

1.8 V - 3.3 V Logic

High-Level Output Voltage (I

Low-Level Output Voltage (I

= -100 μA)

OH

= 100 μA)

OL

High-Level Input Voltage VL = 1.65 V

VL = 1.8 V

VL = 2.0 V

VL > 2.0 V

Low-Level Input Voltage

HPDETECT Input

High-Level Input Voltage

Low-Level Input Voltage

I

in

V

OH

V

OL

V

IH

V

IL

HPDV

HPDV

IH

IL

-±10μA

-10pF

VL - 0.2 - V

-0.2V

0.83•VL

0.76•VL

0.68•VL

0.65•VL

-

V

-

-

-

-0.30•VLV

0.65•VA - V

-0.35•VAV

22. See “I/O Pin Characteristics” on page 9 for serial and control port power rails.

VCP

VLDO

GND/AGND

Note: Current is derived from t he voltage drop across

a 1 Ω resistor in series with each supply input.

VA

VL

2.2 µF

0.1 µF

0.1 µF

0.1 µF

1 Ω

1 Ω

1 Ω

1 Ω

Power Sup p ly

+

-

+

Voltmeter

+

-

+

-

Figure 8. Power Consumption Test Configuration

DS773F1 19

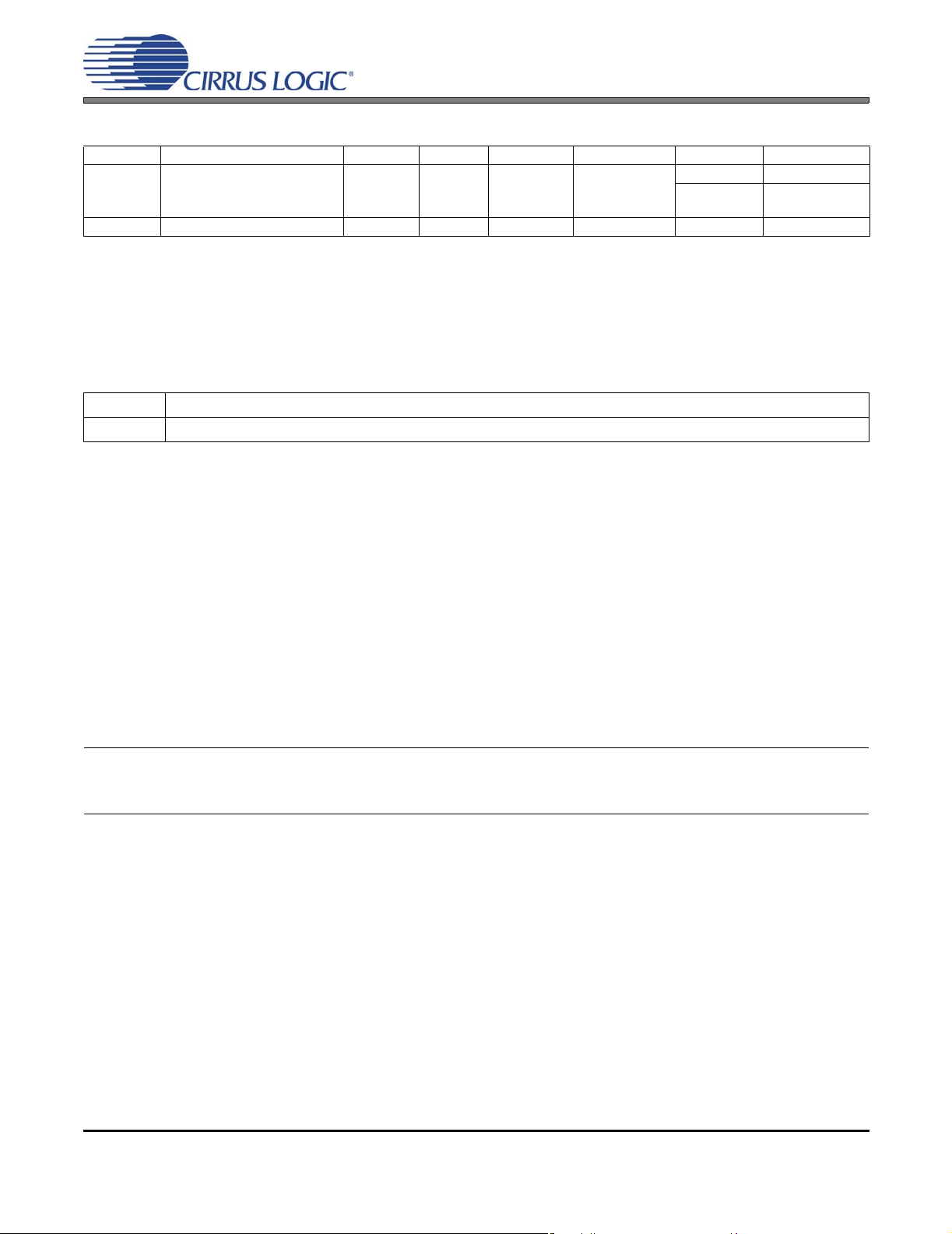

Page 20

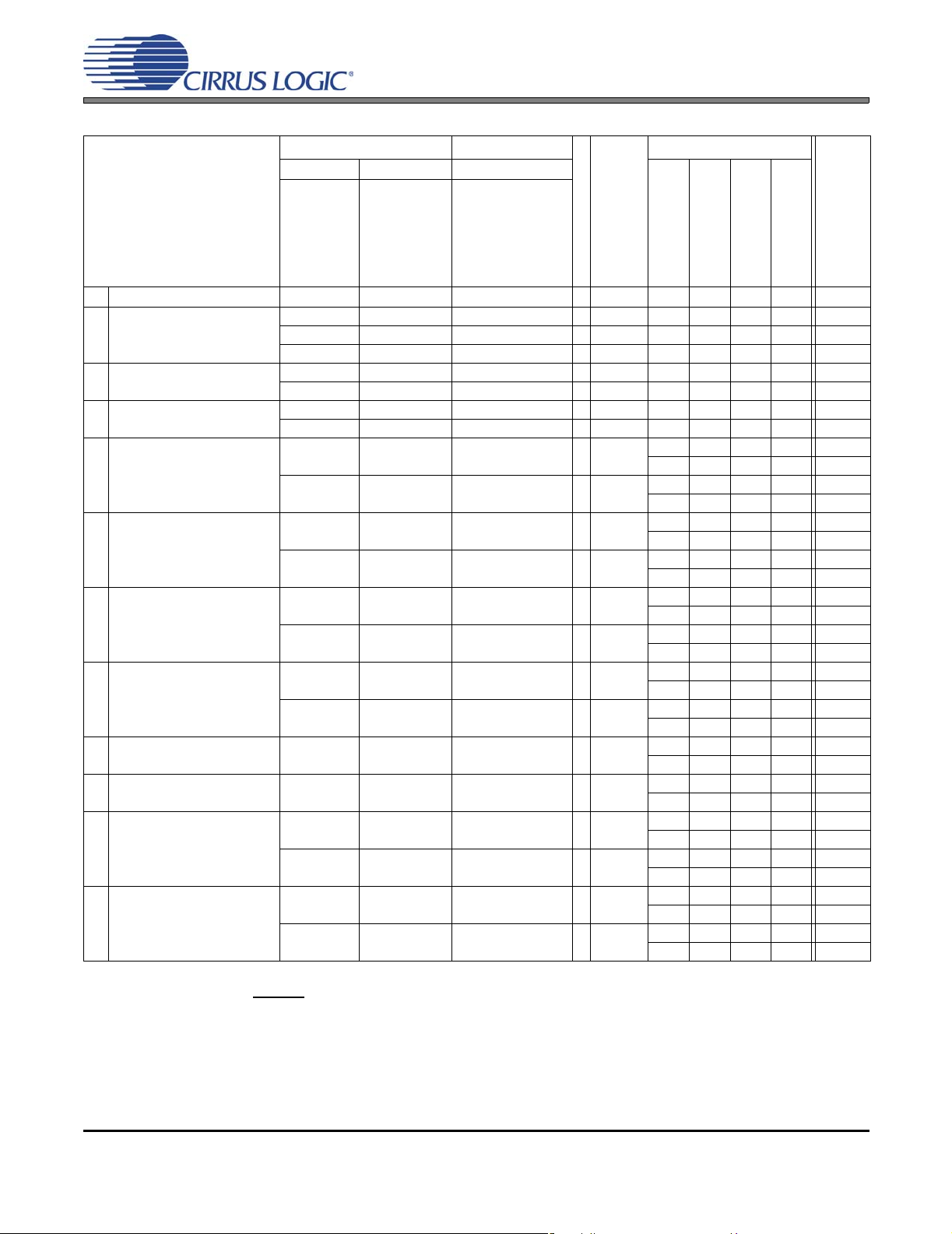

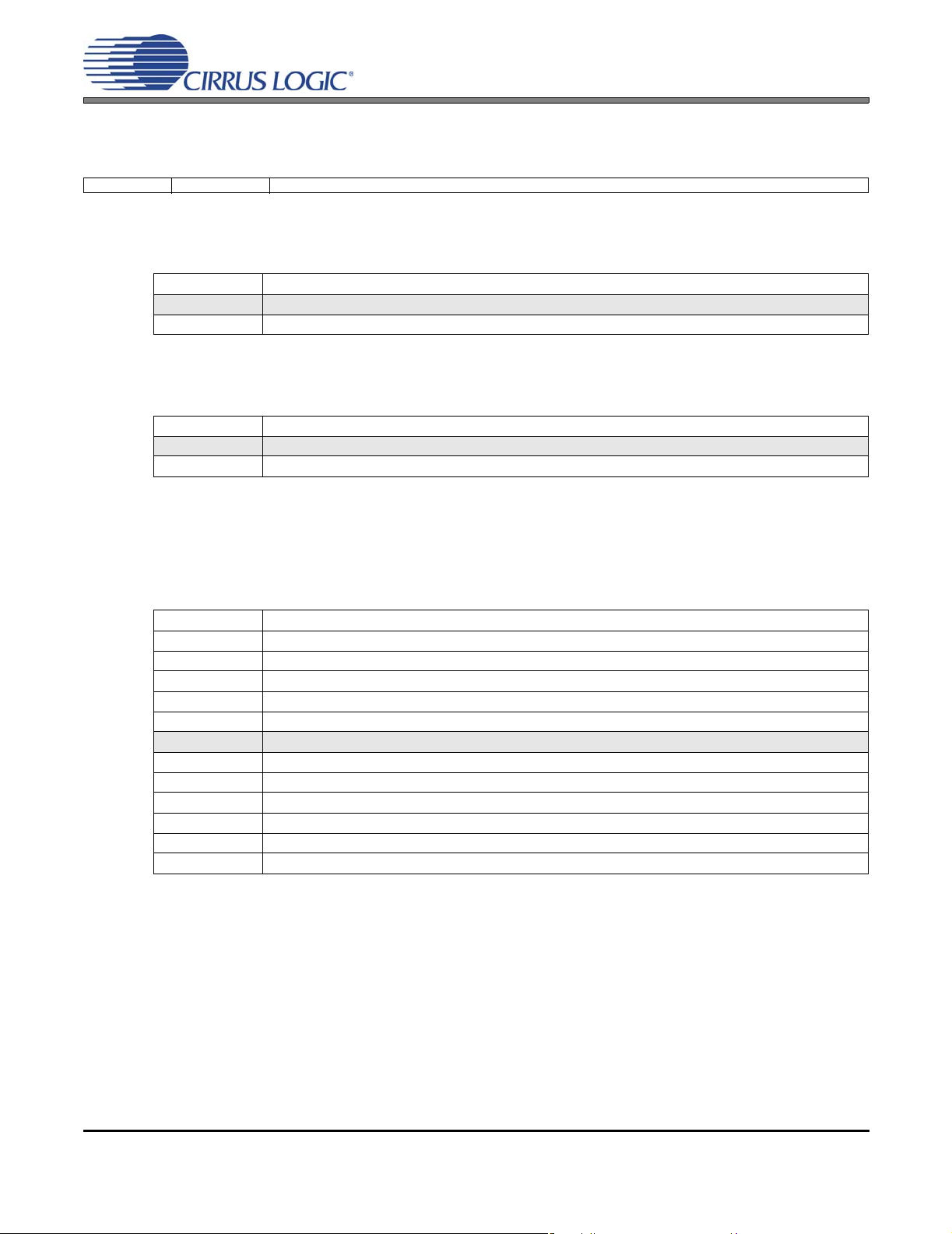

POWER CONSUMPTION - ALL SUPPLIES = 1.8 V

Power Ctl. Registers ADC, Line, HP

Sel. Registers

Operation Test Conditions (unless otherwise

specified): All zeros input,

slave mode, sample rate =

48 kHz; No load. Refer to

Figure 8 on page 19.

1

Off (Note 23)

Standby MCLKDIS=1

2

MCLKDIS=0

(Note 23) MCLKDIS=x

Mono Record (Note 24) ADC

3

PGA to ADC

Stereo Record (Note 24) ADC

4

PGA to ADC

Mono Play to HP No Effects

5

Effects

Mono Play to Line No Effects

6

Stereo Play to HP No Effects

7

Stereo Play to Line No Effects

8

Stereo Passthrough to HP

9

Stereo Passthrough to Li ne

10

Mono Rec. & Play No Effects

11

PGA In, HP Out

Stereo Rec. & Play No Effects

12

PGA In, HP Out

Effects

Effects

Effects

Effects

Effects

02h page 42

PDN_CHRG

PDN_ADCB

xxxxx x x x x xxxxxx

xxx1x x x x x xxxxxx

xxx1x x x x x xxxxxx

xxx1x x x x x xxxxxx

010011111111xx01xxxxx

010011111111xx00xxxxx

0000111111110101xxxxx

0000111111110000xxxxx

111011101111xxxxxxx01

111011101111xxxxxxx00

11 1 0 11111110xxxxx0x x1

11 1 0 11111110xxxxx0x x0

111010101111xxxxxx001

111010101111xxxxxx000

11 1 0 11111010xxxx00xx 1

11 1 0 11111010xxxx00xx 0

011010101111xxxxxx11x

01 1 0 11111010xxxx11xx x

010011101111xx00xxx01

010011101111xx00xxx00

0000101011110000xx001

0000101011110000xx000

03h page 43

PDN_ADCA

PDN

PDN_HPB[1:0]

PDN_HPA[1:0]

PDN_LINB[1:0]

08h page 46

ADCBMUX[1:0]

ADCAMUX[1:0]

PDN_LINA[1:0]

LINEBMUX

LINEAMUX

HPBMUX

HPAMUX

Class H

Mode

page 45

PDN_DSP - 0Fh page 50

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

Typical Current (mA)

i

VCPiVAiVLDOiVL

-

0.002 0.003 0.002 0.001 0.01

-

0.003 0.002 0.039 0.006 0.09

-

0.002 0.005 0.223 0.006 0.43

-

0.002 0.002 0.010 0.002 0.03

-

0.003 0.859 0.650 0.017 2.75

-

0.002 1.053 0.650 0.018 3.10

-

0.002 1.116 0.795 0.022 3.48

-

0.002 1.470 0.800 0.022 4.13

0.450 1.007 0.686 0.006 3.87

VCP

0.928 1.014 0.690 0.006 4.75

0.452 1.008 0.964 0.006 4.37

VCP

0.936 1.014 0.972 0.006 5.27

0.394 1.008 0.704 0.006 3.80

VCP

0.822 1.015 0.692 0.005 4.56

0.394 1.008 0.977 0.006 4.29

VCP

0.822 1.015 0.969 0.006 5.06

0.697 1.434 0.688 0.006 5.08

VCP

1.405 1.441 0.692 0.006 6.38

0.693 1.435 1.023 0.006 5.68

VCP

1.429 1.442 1.031 0.006 7.04

0.572 1.437 0.697 0.006 4.88

VCP

1.182 1.443 0.698 0.005 5.99

0.572 1.437 1.025 0.006 5.47

VCP

1.182 1.445 1.025 0.006 6.58

0.562 1.083 0.190 0.005 3.31

VCP

1.159 1.090 0.190 0.006 4.40

0.572 1.084 0.190 0.006 3.33

VCP

1.181 1.093 0.190 0.006 4.44

0.450 1.838 1.063 0.017 6.06

VCP

0.931 1.846 1.061 0.017 6.94

0.453 1.839 1.346 0.017 6.58

VCP

0.937 1.846 1.345 0.018 7.46

0.689 2.682 1.209 0.023 8.29

VCP

1.417 2.690 1.218 0.022 9.63

0.693 2.682 1.560 0.022 8.92

VCP

1.420 2.691 1.561 0.023 10.25

CS42L55

Total

Power

(mW)

20 DS773F1

Page 21

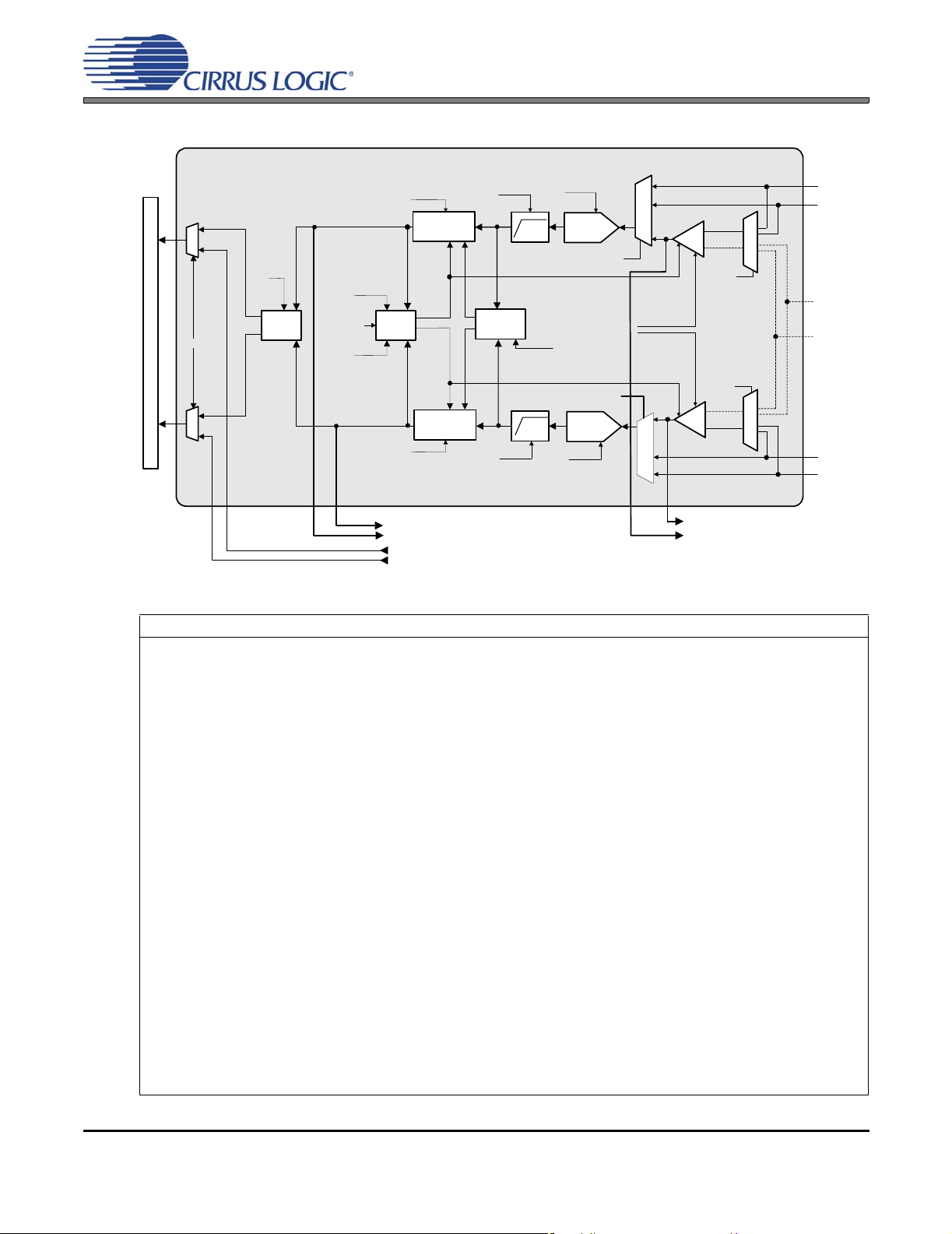

POWER CONSUMPTION - ALL SUPPLIES = 2.5 V

Power Ctl. Registers MUX Registers

Operation Test Condi-

tions (unless otherwise

specified): /All zeros input,

slave mode, sample rate =

48 kHz; No load. Refer to

Figure 8 on page 19.

1

Off (Note 23)

Standby MCLKDIS=1

2

MCLKDIS=0

(Note 23) MCLKDIS=x

Mono Record (Note 24) ADC

3

PGA to ADC

Stereo Record (Note 24) ADC

4

PGA to ADC

Mono Play to HP No Effects

5

Effects

Mono Play to Line No Effects

6

Stereo Play to HP No Effects

7

Stereo Play to Line No Effects

8

Stereo Passthrough to HP

9

Stereo Passthrough to Line

10

Mono Rec. & Play No Effects

11

PGA In, HP Out

Stereo Rec. & Play No Effects

12

PGA In, HP Out

Effects

Effects

Effects

Effects

Effects

02h page 42

PDN_CHRG

PDN_ADCB

xxxxx x x x x xxxxxx

xxx1x x x x x xxxxxx

xxx1x x x x x xxxxxx

xxx1x x x x x xxxxxx

110011111111xx01xxxxx

110011111111xx00xxxxx

1000111111110101xxxxx

1000111111110000xxxxx

111011101111xxxxxxx01

111011101111xxxxxxx00

111011111110xxxxx0xx1

111011111110xxxxx0xx0

111010101111xxxxxx001

111010101111xxxxxx000

111011111010xxxx00xx1

111011111010xxxx00xx0

111010101111xxxxxx11x

111011111010xxxx11xxx

110011101111xx00xxx01

110011101111xx00xxx00

1000101011110000xx001

1000101011110000xx000

PDN_ADCA

03hpage 43

PDN

PDN_HPB[1:0]

PDN_HPA[1:0]

PDN_LINB[1:0]

PDN_LINA[1:0]

ADCBMUX[1:0]

08h page 46

ADCAMUX[1:0]

LINEBMUX

LINEAMUX

HPBMUX

HPAMUX

Class H

Mode

page 45

PDN_DSP - 0Fh page 50

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

VCP/2

Typical Current (mA)

i

VCPiVAiVLDOiVL

-

0.001 0.001 0.001 0.000 0.01

-

0.000 0.000 0.064 0.007 0.18

-

0.000 0.013 0.385 0.007 1.01

-

0.000 0.000 0.018 0.000 0.05

-

0.000 0.752 0.743 0.019 3.79

-

0.000 0.997 0.750 0.019 4.42

-

0.000 1.031 0.918 0.025 4.94

-

0.000 1.511 0.926 0.024 6.15

0.676 1.327 0.705 0.007 6.79

VCP

1.694 1.339 0.709 0.007 9.37

0.677 1.325 1.032 0.007 7.60

VCP

1.728 1.337 1.049 0.007 10.30

0.585 1.328 0.738 0.007 6.65

VCP

1.516 1.339 0.739 0.007 9.00

0.585 1.324 1.030 0.006 7.36

VCP

1.515 1.338 1.030 0.007 9.73

0.943 1.833 0.711 0.007 8.74

VCP

2.250 1.850 0.744 0.007 12.13

0.945 1.835 1.090 0.007 9.69

VCP

2.237 1.846 1.121 0.007 13.03

0.760 1.835 0.730 0.007 8.33

VCP

1.888 1.848 0.740 0.006 11.21

0.760 1.836 1.085 0.007 9.22

VCP

1.888 1.851 1.058 0.007 12.01

0.751 1.174 0.212 0.007 5.36

VCP

1.880 1.188 0.212 0.007 8.22

0.759 1.175 0.211 0.007 5.38

VCP

1.886 1.189 0.211 0.007 8.23

0.676 2.055 1.159 0.018 9.77