Page 1

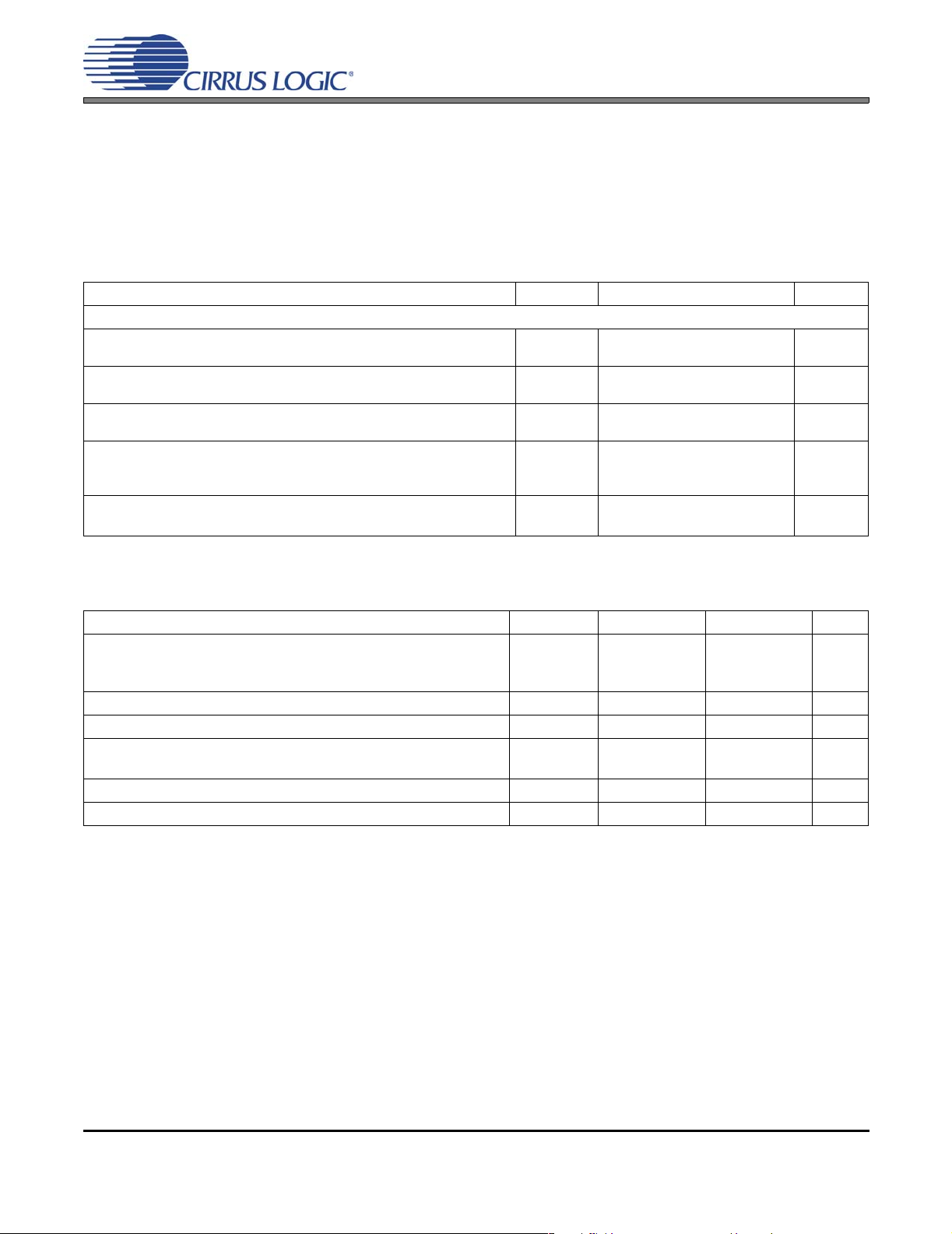

CS42L51

Low Power, Stereo CODEC with Headphone Amp

DIGITAL to ANALOG FEATURES

98 dB Dynamic Range (A-wtd)

-86 dB THD+N

Headphone Amplifier - GND Centered

– On-Chip Charge Pump Provides -VA_HP

– No DC-Blocking Capacitor Required

– 46 mW Power Into Stereo 16 Ω @ 1.8 V

– 88 mW Power Into Stereo 16 Ω @ 2.5 V

– -75 dB THD+N

Digital Signal Processing Engine

– Bass & Treble Tone Control, De-Emphasis

– PCM + ADC Mix w/Independent Vol Control

– Master Digital Volume Control

– Soft Ramp & Zero Cross Transitions

Beep Generator

– Tone Selections Across Two Octaves

– Separate Volume Control

– Programmable On & Off Time Intervals

– Continuous, Periodic or One-Shot Beep

Selections

Programmable Peak-Detect and Limiter

Pop and Click Suppression

ANALOG to DIGITAL FEATURES

98 dB Dynamic Range (A-wtd)

-88 dB THD+N

Analog Gain Controls

– +32 dB or +16 dB MIC Pre-Amplifiers

– Analog Programmable Gain Amplifier

(PGA)

+20 dB Digital Boost

Programmable Automatic Level Control (ALC)

– Noise Gate for Noise Suppression

– Programmable Threshold and

Attack/Release Rates

Independent Channel Control

Digital Volume Control

High-Pass Filter Disable for DC Measurements

Stereo 3:1 Analog Input MUX

Dual MIC Inputs

– Programmable, Low Noise MIC Bias Levels

– Differential MIC Mix for Common Mode

Noise Rejection

Very Low 64 Fs Oversampling Clock Reduces

Power Consumption

1.8 V to 3.3 V

Serial Audio

Input

Hardware

2

Mode or I

C &

SPI Software

Mode

Control Data

Reset

Serial Audio

Output

Level Translator

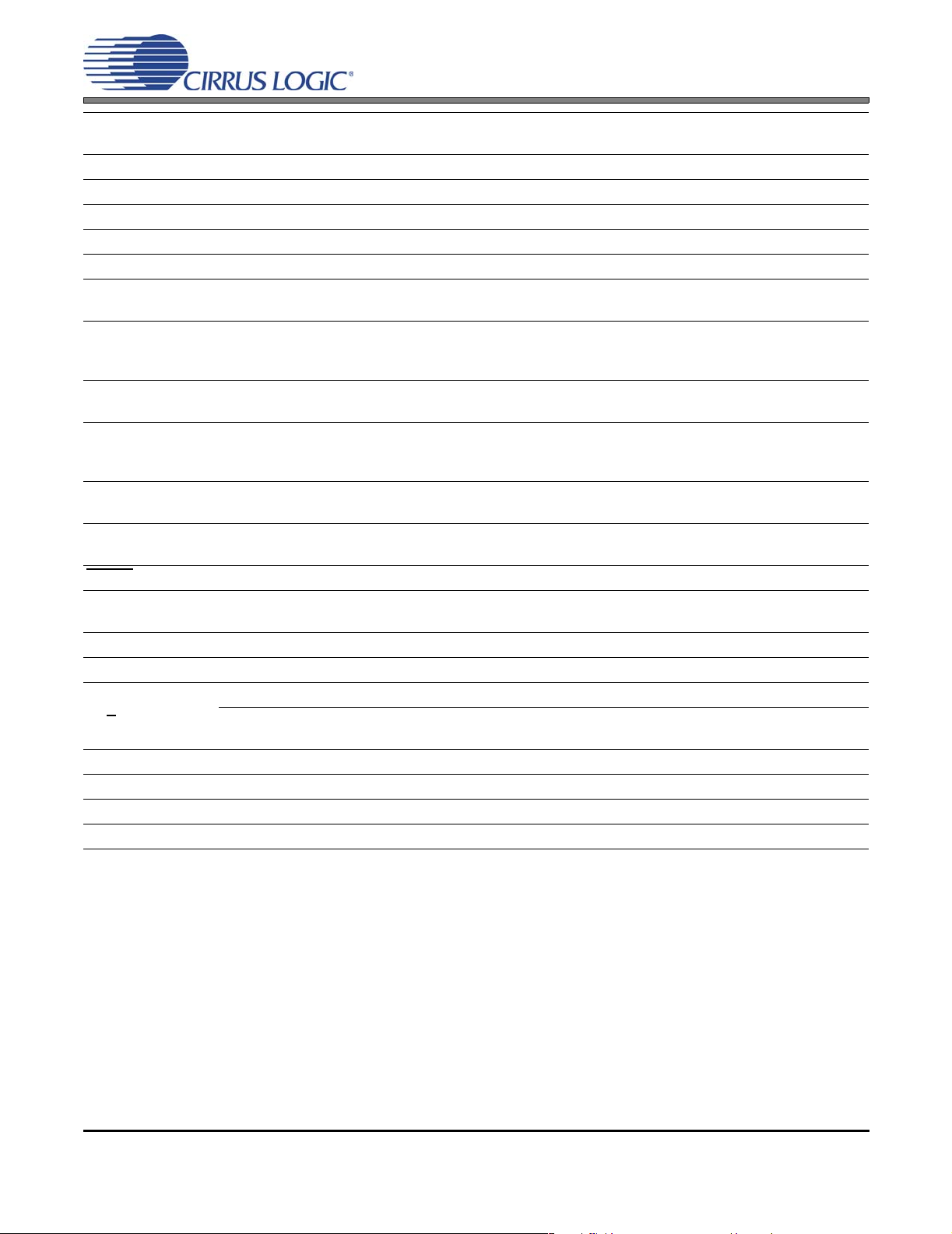

http://www.cirrus.com

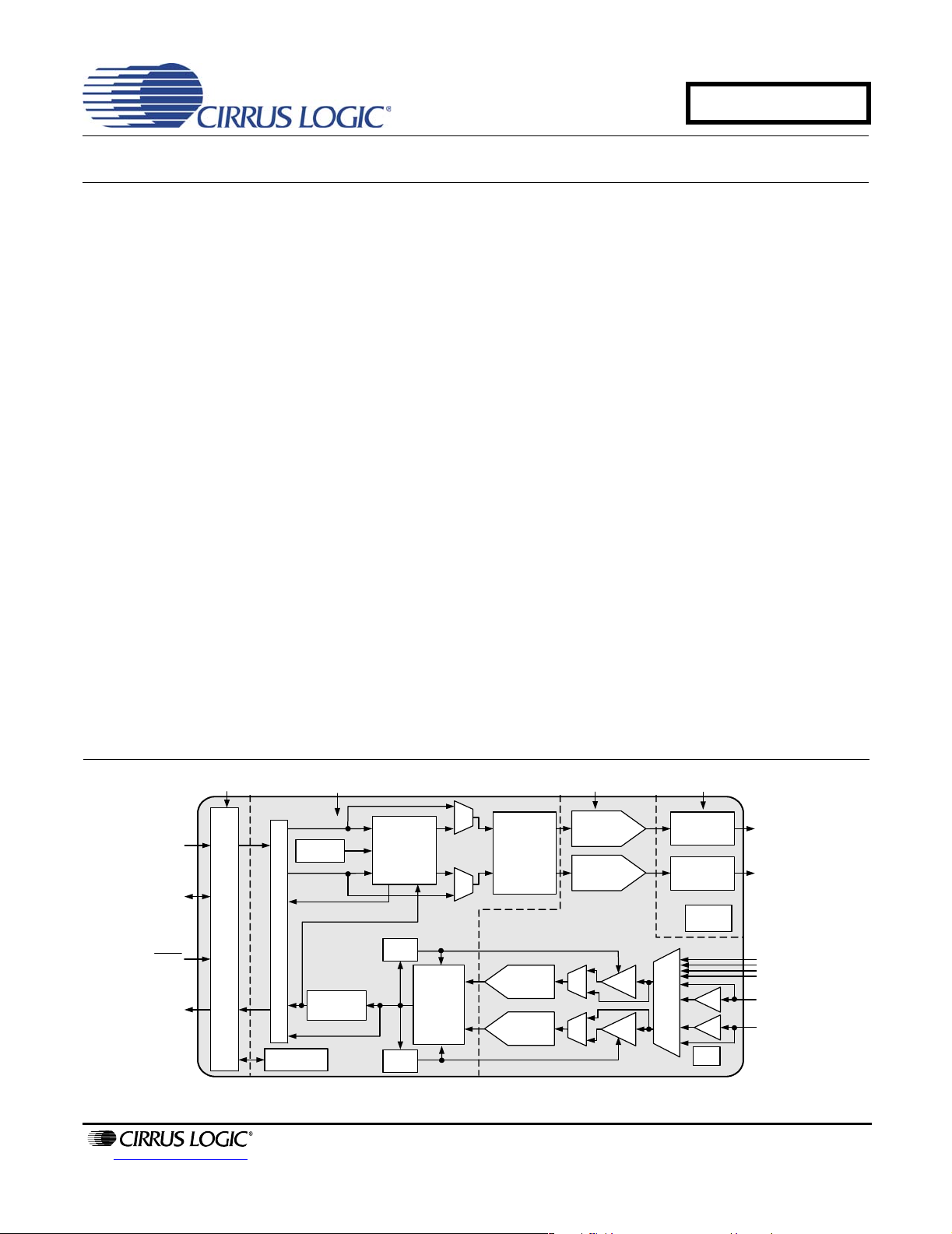

1.8 V to 2.5 V 1.8 V to 2.5 V

MUX

Digital

Generator

PCM Serial Interface

Register

Configuration

Beep

High Pass

Filters

Signal

Processing

Engine

ALC

ALC

Volume

Controls

MUX

Multibit

∆Σ Modulator

Multibit

Oversampling

ADC

Multibit

Oversampling

ADC

Copyright © Cirrus Logic, Inc. 2006

(All Rights Reserved)

Switched

Capacitor DAC

and Filter

Switched

Capacitor DAC

and Filter

MUX

PGA

MUX

PGA

1.8 V to 2.5 V

Headphone

Amp - GND

Centered

Headphone

Amp - GND

Centered

MUX

Charge

Pump

+32 dB

+32 dB

MIC

Bias

Left HP Out

Right HP Out

Stereo Input 1

Stereo Input 2

Stereo Input 3 /

Mic Input 1 & 2

JULY '06

DS679F1

Page 2

CS42L51

SYSTEM FEATURES

24-bit Converters

4 kHz to 96 kHz Sample Rate

Multi-bit Delta Sigma Architecture

Low Power Operation

– Stereo Playback: 12.93 mW @ 1.8 V

– Stereo Record and Playback: 20.18 mW @

1.8 V

Variable Power Supplies

– 1.8 V to 2.5 V Digital & Analog

– 1.8 V to 3.3 V Interface Logic

Power Down Management

– ADC, DAC, CODEC, MIC Pre-Amplifier,

PGA

Software Mode (I²C

Hardware Mode (Stand-Alone Control)

Digital Routing/Mixes:

– Analog Out = ADC + Digital In

– Digital Out = ADC + Digital In

– Internal Digital Loopback

– Mono Mixes

Flexible Clocking Options

– Master or Slave Operation

– High-Impedance Digital Output Option (for

easy MUXing between CODEC and Other

Data Sources)

– Quarter-Speed Mode - (i.e. Allows 8 kHz Fs

while maintaining a flat noise floor up to

16 kHz)

APPLICATIONS

HDD & Flash-Based Portable Audio Players

MD Players/Recorders

PDAs

Personal Media Players

Portable Game Consoles

Digital Voice Recorders

Digital Camcorders

Digital Cameras

Smart Phones

®

& SPI™ Control)

GENERAL DESCRIPTION

The CS42L51 is a highly integrated, 24-bit, 96 kHz, low

power stereo CODEC. Based on multi-bit, delta-sigma

modulation, it allows infinite sample rate adjustment between 4 kHz and 96 kHz. Both the ADC and DAC offer

many features suitable for low power, portable system

applications.

The ADC input path allows independent channel control

of a number of features. An input multiplexer selects between line-level or microphone level inputs for each

channel. The microphone input path includes a selectable programmable-gain pre-a mplifier stage and a low

noise MIC bias voltage supply. A PGA is available for

line or microphone inputs and provides analog gain with

soft ramp and zero cross transitions. The ADC also features a digital volume attenuator with soft ramp

transitions. A programmable ALC and Noise Gate monitor the input signals and adjust the volume levels

appropriately.

The DAC output path includes a digital signal pro cessing engine. Tone Control provides bass and treble

adjustment of four selectable corner frequencies. The

Mixer allows independent volume control for both the

ADC mix and the PCM mix, as well as a master digital

volume control for the analog output. All volume level

changes may be configured to occur on soft ramp and

zero cross transitions. The DAC also includes de-emphasis, limiting functions and a beep generator

delivering tones selectable across a range of two full

octaves.

The stereo headphone amplifier is powered from a separate positive supply and the integrated charge pump

provides a negative supply. This allows a gr ound-centered analog output with a wide signal swing and

eliminates external DC-blocking capacitors.

In addition to its many features, the CS42L51 operates

from a low-voltage analog and digital core, making this

CODEC ideal for portable systems that require extremely low power consumption in a minimal amount of

space.

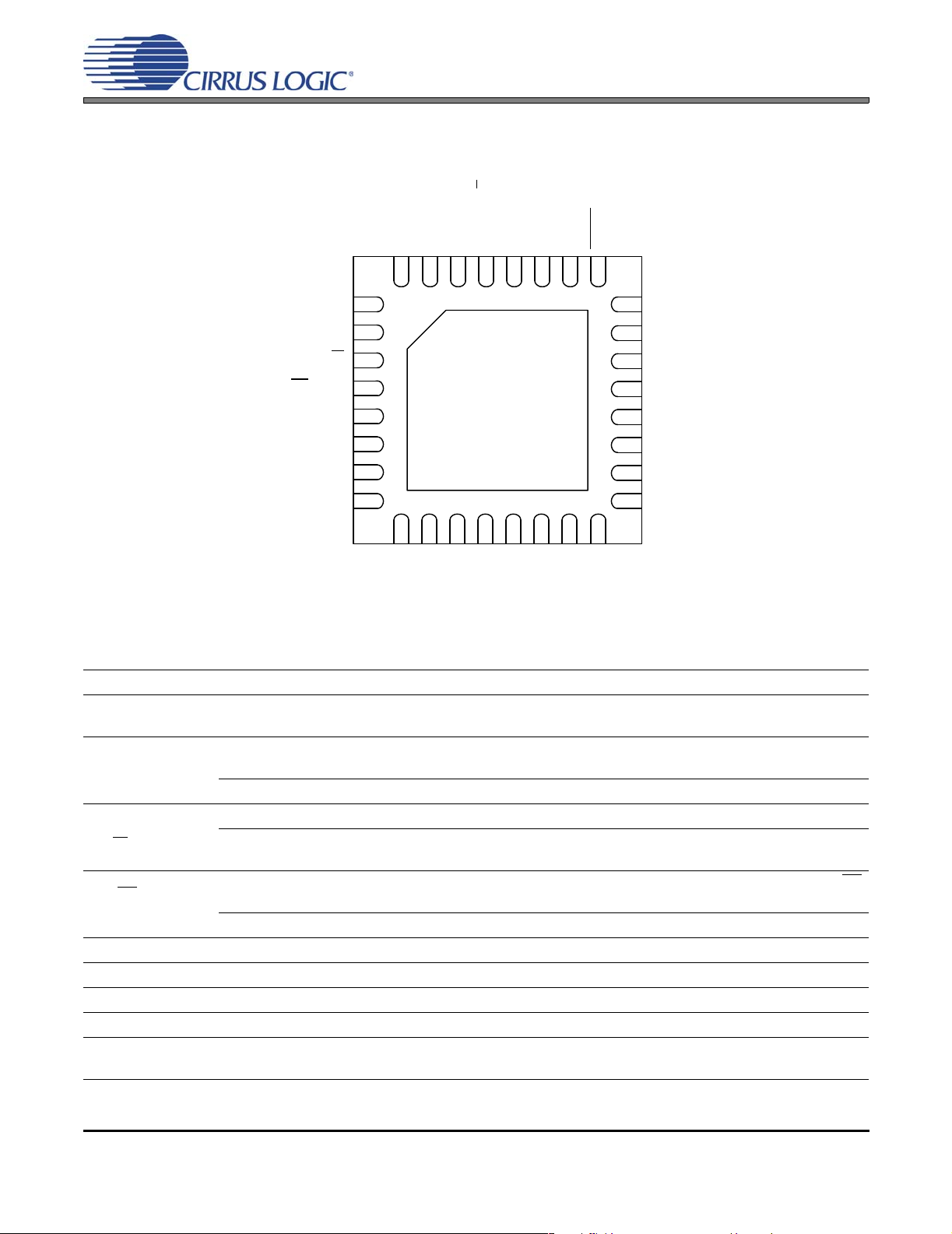

The CS42L51 is available in a 32-pin QFN package in

both Commercial (-10 to +70° C) and Automotive

grades (-40 to +85° C). The CDB42L51 Customer Demonstration board is also available for device evaluation

and implementation suggestions. Please see “Ordering

Information” on page 85 for complete details.

2 DS679F1

Page 3

TABLE OF CONTENTS

1. PIN DESCRIPTIONS - SOFTWARE (HARDWARE) MODE ..................................................................7

1.1 Digital I/O Pin Characteristics ........................................................................................................... 9

2. TYPICAL CONNECTION DIAGRAMS .................................................................................................10

3. CHARACTERISTIC AND SPECIFICATION TABLES ......................................................................... 12

SPECIFIED OPERATING CONDITIONS ............................................................................................. 12

ABSOLUTE MAXIMUM RATINGS .......................................................................................................12

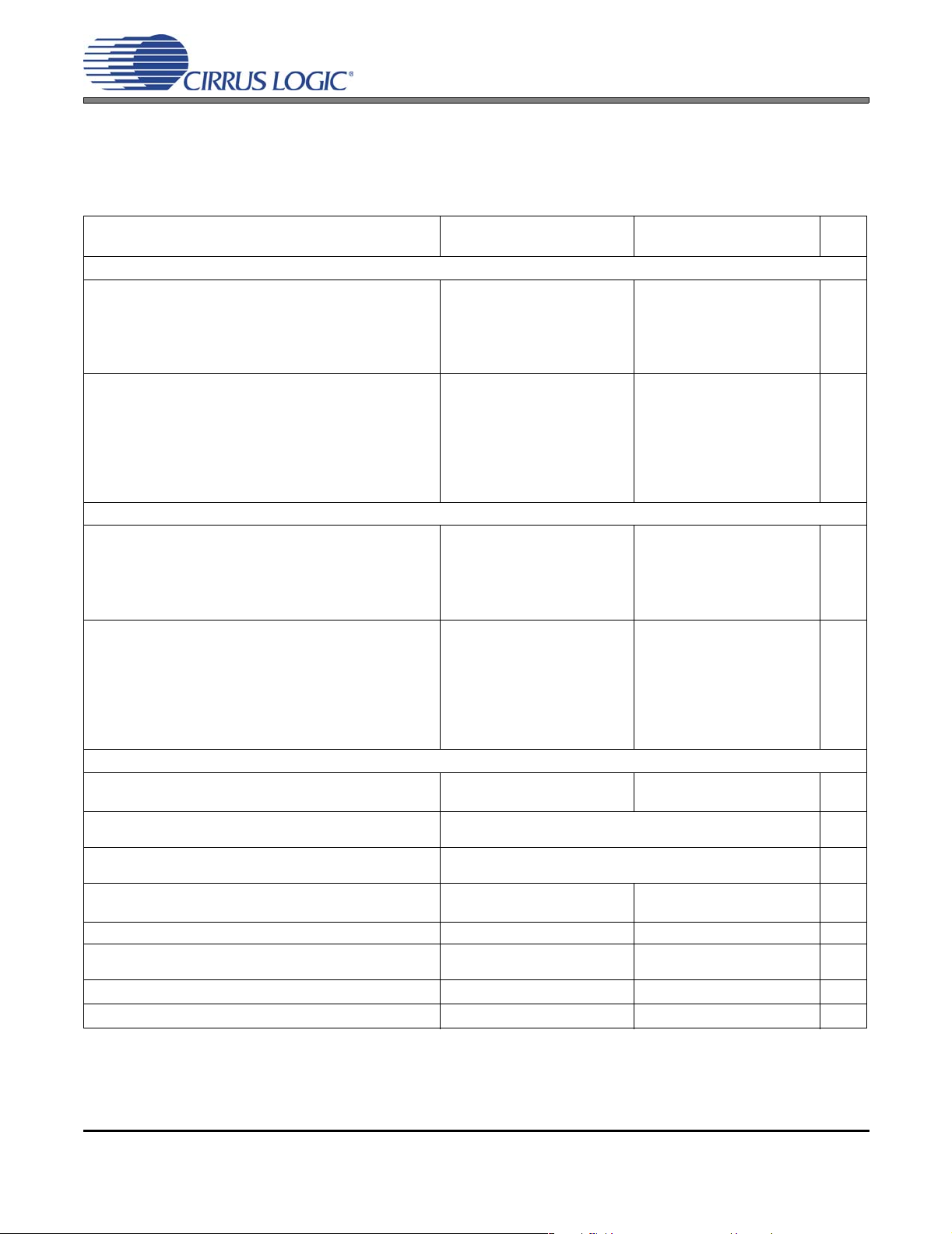

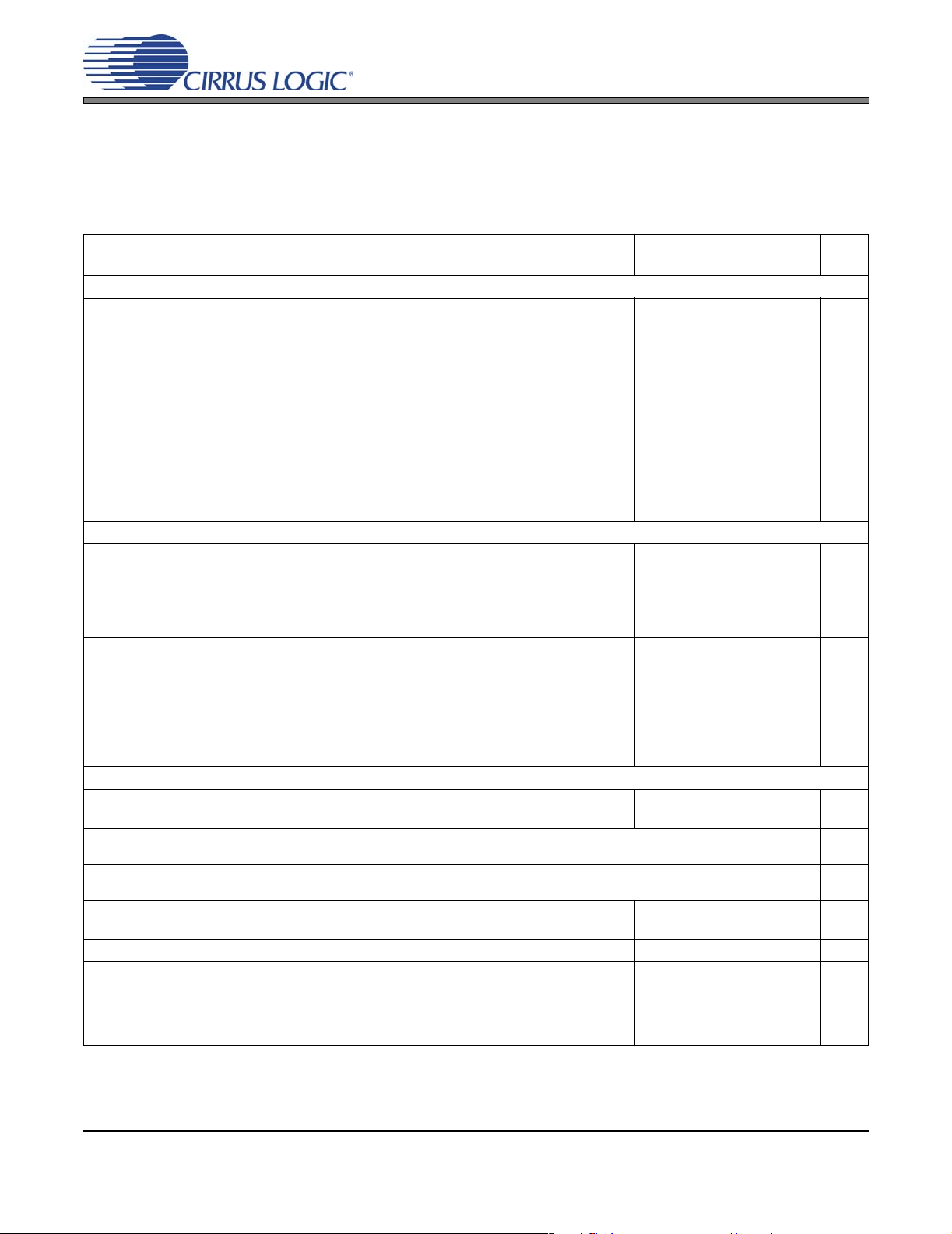

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ) .......................................................... 13

ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ..........................................................14

ADC DIGITAL FILTER CHARACTERISTICS .................................................................... ... .... ... ... ... ... 15

ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ) ...................................................... 16

ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ................ ... ................................... 17

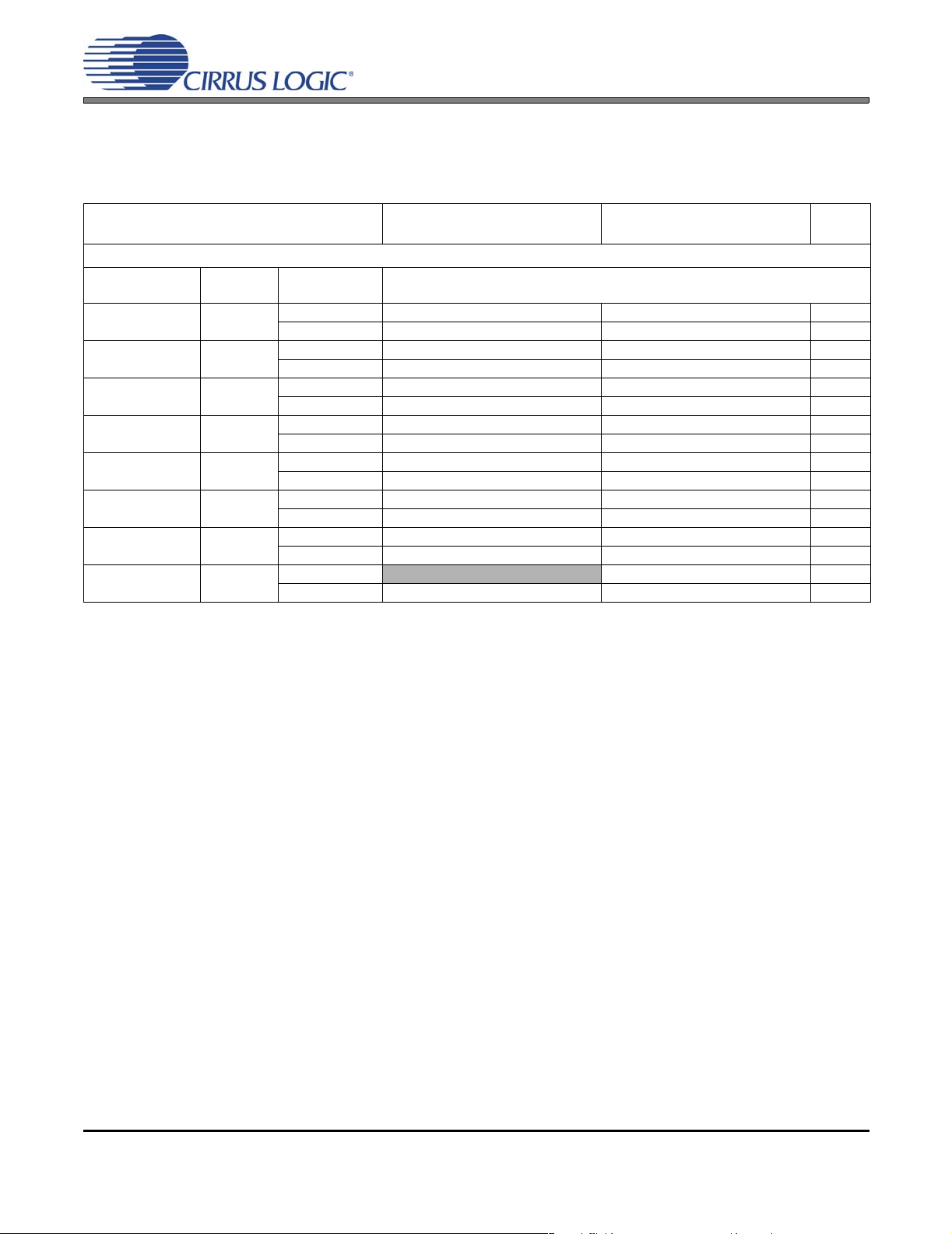

LINE OUTPUT VOLTAGE CHARACTERISTICS ................................................................................. 18

HEADPHONE OUTPUT POWER CHARACTERISTICS ................................................ ... ... .... ... ... ... ... 19

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE .............................. 20

SWITCHING SPECIFICATIONS - SERIAL PORT ............................................................................... 20

SWITCHING SPECIFICATIONS - I²C® CONTROL PORT .................................................................. 22

SWITCHING CHARACTERISTICS - SPI™ CONTROL PORT ............................................................ 23

DC ELECTRICAL CHARACTERISTICS .............................................................................................. 24

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS ..................................................... 24

POWER CONSUMPTION .................................................................................................................... 25

4. APPLICATIONS ...................................................................................................................................26

4.1 Overview .........................................................................................................................................26

4.1.1 Architecture ........................................................................................................................... 26

4.1.2 Line & MIC Inputs ..................................................................................................................26

4.1.3 Line & Headphone Outputs ................................................................................................... 26

4.1.4 Signal Processing Engine ..................................................................................................... 26

4.1.5 Beep Generator .....................................................................................................................26

4.1.6 Device Control (Hardware or Software Mode) ...................................................................... 26

4.1.7 Power Management .............................................................................................................. 26

4.2 Hardware Mode .............................................................................................................................. 27

4.3 Analog Inputs ................................................................................................................................. 28

4.3.1 Digital Code, Offset & DC Measurement ...............................................................................28

4.3.2 High-Pass Filter and DC Offset Calibration ........................................................................... 29

4.3.3 Digital Routing ....................................................................................................................... 29

4.3.4 Differential Inputs .................................................................................................................. 29

4.3.4.1 External Passive Components ......... ....... ...... ....... ...... ... ....... ...... ....... ...... ....... ...... ...... 29

4.3.5 Analog Input Multiplexer ........................................................................................................ 31

4.3.6 MIC & PGA Gain ...................................................................................................................31

4.3.7 Automatic Level Control (ALC) .............................................................................................. 32

4.3.8 Noise Gate ............................................................................................................................ 33

4.4 Analog Outputs ............................................................................................................................... 34

4.4.1 De-Emphasis Filter ................................................................................................................34

4.4.2 Volume Controls ....................................................................................................................35

4.4.3 Mono Channel Mixer ............................................................................................................. 35

4.4.4 Beep Generator .....................................................................................................................35

4.4.5 Tone Control .......................................................................................................................... 36

4.4.6 Limiter .................................................................................................................................... 36

4.4.7 Line-Level Outputs and Filtering ........................................................................................... 37

4.4.8 On-Chip Charge Pump ..........................................................................................................38

4.5 Serial Port Clocking ........................................................................................................................ 38

4.5.1 Slave ..................................................................................................................................... 39

4.5.2 Master ................................................................................................................................... 39

CS42L51

DS679F1 3

Page 4

CS42L51

4.5.3 High-Impedance Digital Output ............................................................................................. 40

4.5.4 Quarter- and Half-Speed Mode .............................................................................................40

4.6 Digital Interface Formats ................................................................................................................ 40

4.7 Initialization ..................................................................................................................................... 41

4.8 Recommended Power-Up Sequence ............................................................................................. 41

4.9 Recommended Power-Down Sequence ........................................................................................ 42

4.10 Software Mode .............................................................................................................................43

4.10.1 SPI Control .......................................................................................................................... 43

4.10.2 I²C Control ........................................................................................................................... 43

4.10.3 Memory Address Pointer (MAP) .......................................................................................... 45

4.10.3.1 Map Increment (INCR) ............................................................................................. 45

5. REGISTER QUICK REFERENCE ........................................................................................................ 46

6. REGISTER DESCRIPTION .................................................................................................................. 49

6.1 Chip I.D. and Revision Register (Address 01h) (Read Only) .........................................................49

6.2 Power Control 1 (Address 02h) ......................................................................................................49

6.3 MIC Power Control & Speed Control (Address 03h) ...................................................................... 50

6.4 Interface Control (Address 04h) ..................................................................................................... 52

6.5 MIC Control (Address 05h) .............................................................................................................53

6.6 ADC Control (Address 06h) ............................................................................................................54

6.7 ADCx Input Select, Invert & Mute (Address 07h) ........................................................................... 56

6.8 DAC Output Control (Address 08h) ................................................................................................ 57

6.9 DAC Control (Address 09h) ............................................................................................................58

6.10 ALCX & PGAX Control: ALCA, PGAA (Address 0Ah) & ALCB, PGAB (Address 0Bh) ............... 59

6.11 ADCx Attenuator: ADCA (Address 0Ch) & ADCB (Address 0Dh) ................................................ 60

6.12 ADCx Mixer Volume Control: ADCA (Address 0Eh) & ADCB (Address 0Fh) .............................. 61

6.13 PCMX Mixer Volume Control:

PCMA (Address 10h) & PCMB (Address 11h) ..................................................................................... 62

6.14 Beep Frequency & Timing Configuration (Address 12h) .............................................................. 62

6.15 Beep Off Time & Volume (Address 13h) ...................................... ... .... ... ... ... .... ... ... ... ... ................63

6.16 Beep Configuration & Tone Configuration (Address 14h) ............................................................ 64

6.17 Tone Control (Address 15h) ......................................................................................................... 65

6.18 AOUTx Volume Control:

AOUTA (Address 16h) & AOUTB (Address 17h) ................................................................................. 66

6.19 PCM Channel Mixer (Address 18h) .............................................................................................. 67

6.20 Limiter Threshold SZC Disable (Address 19h) ............................................................................. 67

6.21 Limiter Release Rate Register (Address 1Ah) .............................................................................. 69

6.22 Limiter Attack Rate Register (Address 1Bh) .................................................................................70

6.23 ALC Enable & Attack Rate (Address 1Ch) ................................................................................... 70

6.24 ALC Release Rate (Address 1Dh) ................ ............. ............. ............. ............. ............ ................ 71

6.25 ALC Threshold (Address 1Eh) ...................................................................................................... 71

6.26 Noise Gate Configuration & Misc. (Address 1Fh) ......................................................................... 72

6.27 Status (Address 20h) (Read Only) ............................................................................................... 73

6.28 Charge Pump Frequency (Address 21h) ...................................................................................... 74

7. ANALOG PERFORMANCE PLOTS .......... ... .... ... ... ... .... ... .......................................................... ... ......75

7.1 Headphone THD+N versus Output Power Plots ............................................................................75

7.2 Headphone Amplifier Efficiency ...................................................................................................... 77

7.3 ADC_FILT+ Capacitor Effects on THD+N ...................................................................................... 78

8. EXAMPLE SYSTEM CLOCK FREQUENCIES .................................................................................... 79

8.1 Auto Detect Enabled ....................................................................................................................... 79

8.2 Auto Detect Disabled ...................................................................................................................... 80

9. PCB LAYOUT CONSIDERATIONS ..................................................................................................... 81

9.1 Power Supply, Grounding ............................................................................................................... 81

9.2 QFN Thermal Pad .......................................................................................................................... 81

10. ADC & DAC DIGITAL FILTERS ........................................................................................................ 82

4 DS679F1

Page 5

11. PARAMETER DEFINITIONS .............. ... ... ... .... ... ... ... .... ... ....................................................... ............83

12. PACKAGE DIMENSIONS .......... .... ... ... ... ... .... ... ....................................................... ... ... ... .... ............84

THERMAL CHARACTERISTICS ........................................................................................................84

13. ORDERING INFORMATION .......... ... ... ... ... .... ... ... ... .... ... ... ... ............................................................. 85

14. REFERENCES ....................... ... ... .... ... ... ... ... .... ... ... ....................................................... ...................... 85

15. REVISION HISTORY ......... ... ... ... .... ... ... ... ... .... ....................................................... ... ... ... ................... 86

LIST OF FIGURES

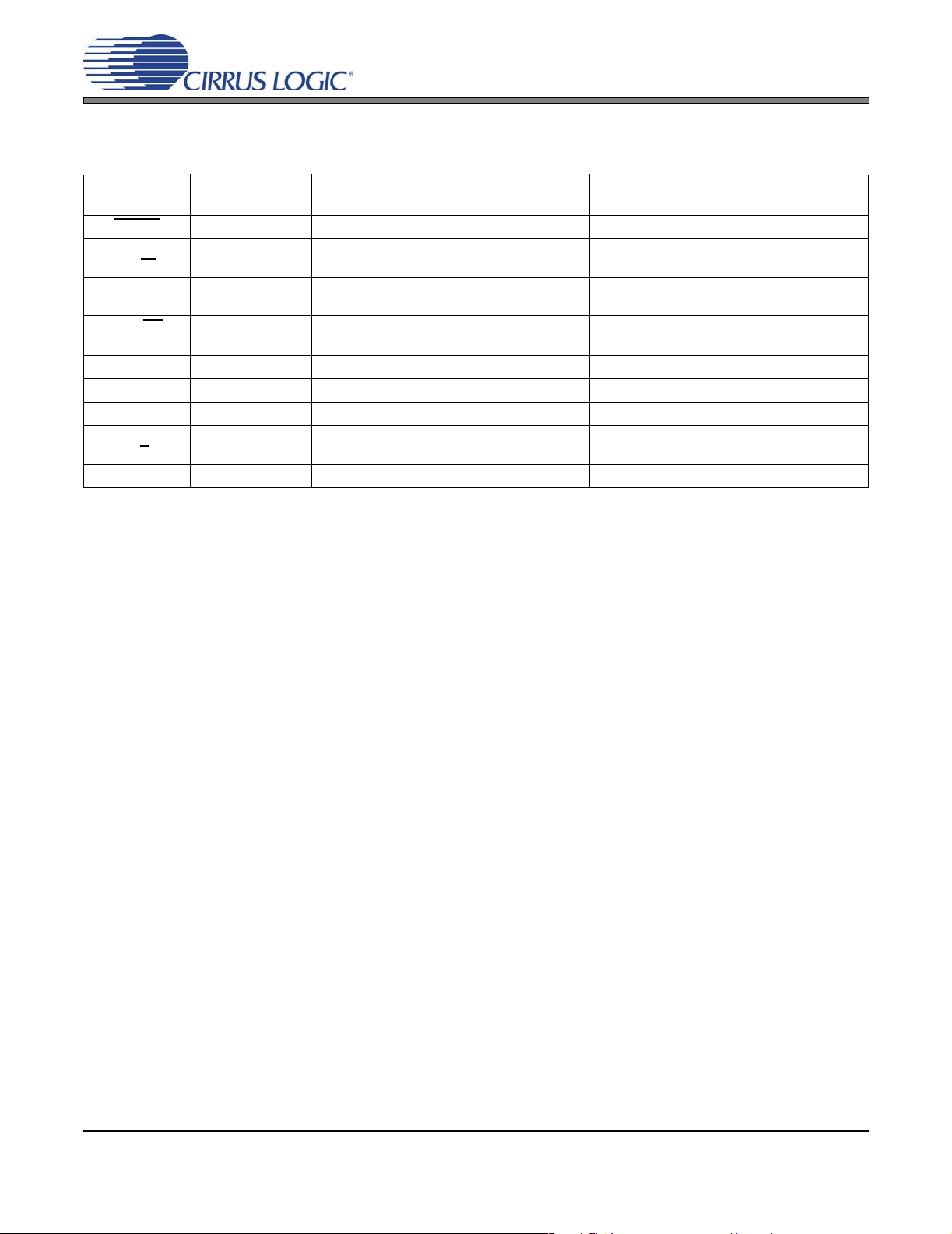

Figure 1.Typical Connection Diagram (Software Mode) ........................................................................... 10

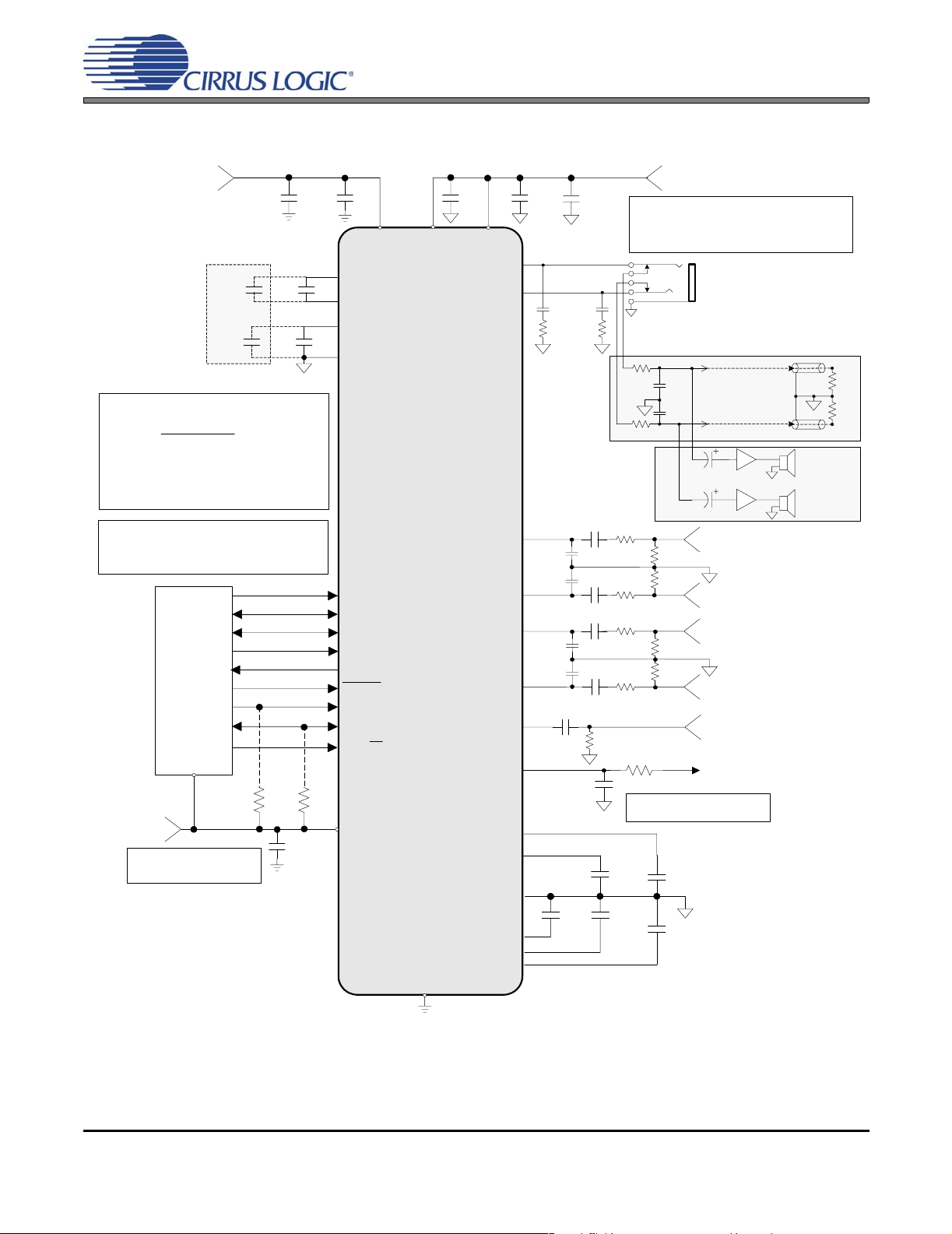

Figure 2.Typical Connection Diagram (Hardware Mode) .......................................................................... 11

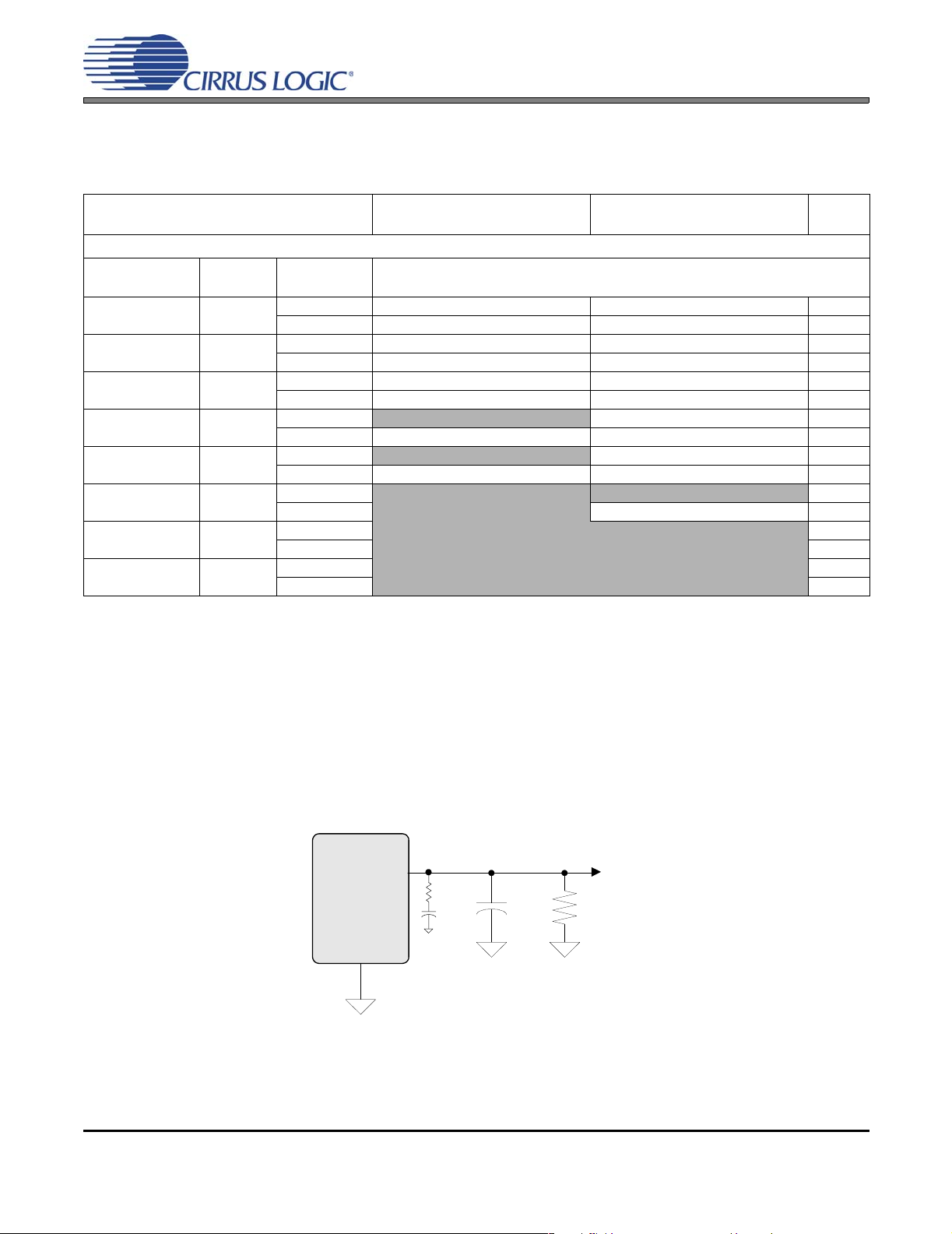

Figure 3.Headphone Output Test Load ..................................................................................................... 19

Figure 4.Serial Audio Interface Slave Mode Timing .................................................................................. 21

Figure 5.Serial Audio Interface Master Mode Timing ................................................................................ 21

Figure 6.Control Port Timing - I²C ............................................................................................................. 22

Figure 7.Control Port Timing - SPI Format ................................................................................................ 23

Figure 8.Analog Input Architecture ............................................................................................................ 28

Figure 9.MIC Input Mix w/Common Mode Rejection .................................................................................30

Figure 10.Differential Input ........................................................................................................................ 30

Figure 11.ALC ...........................................................................................................................................32

Figure 12.Noise Gate Attenuation .............................................................................................................33

Figure 13.Output Architecture ................................................................................................................... 34

Figure 14.De-Emphasis Curve ..................................................................................................................35

Figure 15.Beep Configuration Options ...................................................................................................... 36

Figure 16.Peak Detect & Limiter ...............................................................................................................37

Figure 17.Master Mode Timing ................................................................................................................. 39

Figure 18.Tri-State Serial Port ..................... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ... ............................................. 40

Figure 19.I²S Format .................................................................................................................................40

Figure 20.Left-Justified Format .................................................................................................................41

Figure 21.Right-Justified Format (DAC only) ............................................................................................ 41

Figure 22.Initialization Flowchart ............................................................................................................... 42

Figure 23.Control Port Timing in SPI Mode ..................................................................................... .........43

Figure 24.Control Port Timing, I²C Write ...................................................................................................44

Figure 25.Control Port Timing, I²C Read ................................................................................................... 44

Figure 26.AIN & PGA Selection ................................................................................................................56

Figure 27.THD+N vs. Output Power per Channel at 1.8 V (16 Ω load) .................................................... 75

Figure 28.THD+N vs. Output Power per Channel at 2.5 V (16 Ω load) .................................................... 75

Figure 29.THD+N vs. Output Power per Channel at 1.8 V (32 Ω load) .................................................... 76

Figure 30.THD+N vs. Output Power per Channel at 2.5 V (32 Ω load) .................................................... 76

Figure 31.Power Dissipation vs. Output Power into Stereo 16 Ω ......................................................................77

Figure 32.Power Dissipation vs. Output Power into Stereo 16 Ω (Log Detail) .... ... ... .... ... ......................... 77

Figure 33.ADC THD+N vs. Frequency w/Capacitor Effects ...................................................................... 78

Figure 34.ADC Passband Ripple ........................................................ ... ... ................................................ 82

Figure 35.ADC Stopband Rejection .......................................................................................................... 82

Figure 36.ADC Transition Band ................................................................................................................82

Figure 37.ADC Transition Band Detail ...................................................................................................... 82

Figure 38.DAC Passband Ripple ........................................................ ... ... ... .... ... ...................................... 82

Figure 39.DAC Stopband .......................................................................................................................... 82

Figure 40.DAC Transition Band ................................................................................................................82

Figure 41.DAC Transition Band (Detail) .................................................................................................... 82

CS42L51

DS679F1 5

Page 6

LIST OF TABLES

Table 1. I/O Power Rails ............................................................................................................................. 9

Table 2. Hardware Mode Feature Summary ............................................................................................. 27

Table 3. MCLK/LRCK Ratios .................................................................................................................... 39

CS42L51

6 DS679F1

Page 7

1. PIN DESCRIPTIONS - SOFTWARE (HARDWARE) MODE

)

CS42L51

SDIN

LRCK

SDA/CDIN (MCLKDIV2)

SCL/CCLK (I²S/LJ

ADO/CS

(DEM)

VA_HP

FLYP

GND_HP

FLYN

SCLK

MCLK

SDOUT (M/S

DGND

303132

29

1

2

)

3

4

5

6

7

8

CS42L51

109

11

AOUTA

AOUTB

VSS_HP

13 14 15 16

12

VA

AGND

VD

DAC_FILT+

VL

262728

VQ

Pin Name # Pin Description

Left Right Clock (Input/Output) - Determines which channel, Left or Right, is currently active on the

LRCK

SDA/CDIN

(MCLKDIV2)

SCL/CCLK

)

(I²S/LJ

AD0/CS

(DEM)

VA_HP

FLYP

GND_HP

FLYN

VSS_HP

1

serial audio data line.

Serial Control Data (Input/Output) - SDA is a data I/O in I²C Mode. CDIN is the input data line for the

control port interface in SPI Mode.

2

MCLK Divide by 2 (Input) - Hardware Mode: Divides the MCLK by 2 prior to all internal circuitry.

Serial Control Port Clock (Input) - Serial clock for the serial control port.

3

Interface Format Selection (Input) - Hardware Mode: Selects between I²S & Left-Justified interface for-

mats for the ADC & DAC.

Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C Mode; CS

is the chip-select signal for SPI format.

4

De-Emphasis (Input) - Hardware Mode: Enables/disables the de-emphasis filter.

5

Analog Power For Headphone (Input) - Positive power for the internal analog headphone section.

6

Charge Pump Cap Positive Node (Input) - Positive node for the external charge pump capacitor.

7

Analog Ground (Input) - Ground reference for the internal headphone/charge pump section.

8

Charge Pump Cap Negative Node (Input) - Negative node for the external charge pump capacitor.

Negative Voltage From Charge Pump (Output) - Negative voltage rail for the internal analog head-

9

phone section.

25

RESET

AIN1B

24

AIN1A

23

AFILTB

22

AFILTA

21

20

AIN2B/BIAS

AIN2A

19

MICIN2/BIAS/AIN3B

18

MICIN1/AIN3A

17

ADC_FILT+

DS679F1 7

Page 8

CS42L51

AOUTB

AOUTA

VA

AGND

DAC_FILT+

VQ

ADC_FILT+

MICIN1/

AIN3A

MICIN2/

BIAS/AIN3B

AIN2A

AIN2B/BIAS

AFILTA

AFILTB

AIN1A

AIN1B

RESET

VL

VD

DGND

SDOUT

)

(M/S

MCLK

SCLK

SDIN

Thermal Pad

10

Analog Audio Output (Output) - The full-scale output level is specified in the DAC Analog Characteris-

11

tics specification table

12

Analog Power (Input) - Positive power for the internal analog section.

13

Analog Ground (Input) - Ground reference for the internal analog section.

14

Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.

15

Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.

16

Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.

Microphone Input 1 (Input) - The full-scale level is specified in th e ADC Analog Characteristics specifi-

17

cation table.

Microphone Input 2 (Input/Output) - The full-scale level is specified in the ADC Analog Characteristics

18

specification table. This pin can also be configured as an output to provide a low noise bias supply for an

external microphone. Electrical characteristics are specified in the DC Electrical Characteristics table.

Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specification

19

table.

Analog Input (Input/Output) -

20

cation table. This pin can also be configured as an output to provide a low noise bias supply for an external microphone. Electrical characteristics are specified in the DC Electrical Characteristics table.

21

Filter Connection (Output) - Filter connection for the ADC inputs.

22

23

Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specification

24

table.

25

Reset (Input) - The device enters a low power mode when this pin is driven low.

Digital Interface Power (Input) - Determines the required signal level for the serial audio interface and

26

host control port. Refer to the Recommended Operating Conditions for appropriate voltages.

27

Digital Power (Input) - Positive power for the internal digital section.

28

Digital Ground (Input) - Ground reference for the internal digital section.

Serial Audio Data Output (Output) - Output for two’s complement serial au d io da ta.

29

Serial Port Master/Slave (Input/Output) - Hardware Mode Startup Option: Selects between Master and

Slave Mode for the serial port.

30

Master Clock (Input) - Clock source for the delta-sigma modulators.

31

Serial Clock (Input/Output) - Serial clock for the serial audio interface.

32

Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

-

Thermal relief pad for optimize d he a t di ssi pation. See “QFN Thermal Pad” on page 81.

The full-scale level is specified in the ADC Analog Characteristics specifi-

8 DS679F1

Page 9

1.1 Digital I/O Pin Characteristics

The logic level for each input should not exceed the maximum ratings for the VL power supply.

CS42L51

Pin Name

SW/(HW)

RESET Input

SCL/CCLK

)

(I²S/LJ

SDA/CDIN

(MCLKDIV2)

AD0/CS

(DEM)

MCLK Input

LRCK Input/Output

SCLK Input/Output

SDOUT

)

(M/S

SDIN Input

Input

Input/Output

Input

Input/Output

I/O Driver Receiver

- 1.8 V - 3.3 V

- 1.8 V - 3.3 V, with Hysteresis

1.8 V - 3.3 V, CMOS/Open Drain 1.8 V - 3.3 V, with Hysteresis

- 1.8 V - 3.3 V

- 1.8 V - 3.3 V

1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V

- 1.8 V - 3.3 V

Table 1. I/O Power Rails

DS679F1 9

Page 10

2. TYPICAL CONNECTION DIAGRAMS

+1.8 V o r +2.5 V

See Note 5

* *Use low ESR ceramic capacitors.

Note 2 :

For best response to Fs/2 :

C

This circuitry is intended fo r applications where the

CS42L51 connects directly to an unbalanced output of the

device. For internal routing applications please see the

DAC Analog Output Cha racteristics section for loading

limitations.

Note 5 :

Larger capacitors, such as 1.5 µF, improves the charge

pump performance (and subsequent THD+N) at the full

scale output power achieved with gain (G) settings

greater than default.

470×+

R

ext

=

()

RFs

π

ext

1.5 µF

1.5 µF

4704

**

**

1 µF

1 µF

1 µF

Digital Audio

Processor

2 k

2 k

Ω

+1.8 V, +2.5 V

See Note 1

or +3.3 V

Note 1:

Resistors are required for I²C

control port operation

Ω

0.1 µF

0.1 µF

**

**

VD

FLYP

FLYN

VSS_HP

GND_HP

CS42L51

MCLK

SCLK

LRCK

SDIN

SDOUT

RESET

SCL/CCLK

SDA/CDIN

AD0/CS

VL

DGND

0.1 µF

VA

AIN3B/MICIN2

ADC_FILT+

DAC_FILT+

VA_HP

AOUTB

AOUTA

AIN1A

AIN1B

AIN2A

AIN2B

BIAS1

MICIN1

AIN3A

BIAS2

AGND

AFILTA

AFILTB

0.1 µF

1800 pF

1800 pF

1800 pF

1800 pF

**

VQ

* Capacitors must be C0G or equivalent

0.022 µF

51.1 Ω

*

*

*

*

1 µF

0.1 µF

150 pF

1 µF

1 µF

1 µF

1 µF

1 µF

See Note 4

+1.8 V or +2.5 V

Note 4:

Series resistance in the path of the power supplies must

be avoided. Any voltage drop on VA_HP will dir ectly

impact the negative charge pump supply (VSS_HP) and

result in clipping on the audio output .

Headphone Out

Left & Right

470

Ω

C

Line Level Out

Left & Right

See Note 2

C

470

Ω

Speaker Driver

Left Analog Input 1

100 Ω

100 kΩ

100 kΩ

100 Ω

100 Ω

100 Ω

100 kΩ

R

L

Note 3: The value of RL is dictated

by the microphone cartridge.

1 µF

150 pF

Right Analog Input 1

Left Analog Input 2

100 kΩ

100 kΩ

Right Analog Input 2

Microphone Input

Microphone Bias

See Note 3

10 µF

1 µF

CS42L51

R

ext

R

ext

Figure 1. Typical Connection Diagram (Software Mode)

10 DS679F1

Page 11

CS42L51

+1.8V or +2.5V

* *Use low ESR ceramic capacitors.

Digital Audio

Processor

+1.8V, 2.5 V

or +3.3V

(1) Pull-up to VL (47 kΩ for Master Mode.

Pull-down to DGND for Slave Mode.

1 µF

1 µF

1 µF

VL or DGND (1)

0.1 µF

0.1 µF

**

**

VD

FLYP

FLYN

VSS_HP

GND_HP

MCLK

SCLK

LRCK

SDIN

SDOUT/

M/S

RESET

I²S/LJ

MCLKDIV2

DEM

VL

VA

CS42L51

DGND

0.1 µF

VA_HP

AOUTB

AOUTA

AIN1A

AIN1B

0.1 µF

1800 pF

1800 pF

0.022 µF

51.1 Ω

*

*

See Note 4

1 µF

Note 4:

Series resistance in the path of the power supplies (typically

used for added filtering) must be avoided. Any voltage drop

on VA_HP will directly impact the negative charge pump

supply (VSS_HP) and result in clipping on the audio output .

470Ω

470Ω

100 Ω

1 µF

100 Ω

1 µF

+1.8V or +2.5V

C

Line Level Out

Left & Right

See Note 2

C

Speaker Driver

Left Analog Input 1

100 kΩ

100 kΩ

Right Analog Input 1

Headphone Out

Left & Right

R

ext

R

ext

ADC_FILT+

DAC_FILT+

AGND

AFILTA

AFILTB

VQ

1 µF

**

* Capacitors must be C0G or equivalent

150 pF

150 pF

10 µF

1 µF

Note 2 :

This circuitry is intended for applications where the CS 42L51 connects directly to an unbalanced output of the device . For

internal routing applications please see the DAC Analog Output Characteristics section for loading limitations .

470×+

R

ext

=

For best response to Fs/2 :

C

()

RFs

π

ext

4704

Figure 2. Typical Connection Diagram (Hardware Mode)

DS679F1 11

Page 12

CS42L51

3. CHARACTERISTIC AND SPECIFICATION TABLES

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and

T

= 25° C.)

A

SPECIFIED OPERATING CONDITIONS

(AGND=DGND=0 V, all voltages with respect to ground.)

Parameters Symbol Min Nom Max Units

DC Power Supply (Note 1)

Analog Core

Headphone Amplifier

Digital Core

Serial/Control Port Interface

Ambient Temperature Commercial - CNZ

Automotive - DNZ

VA

VA_HP

VD

VL

T

A

1.65

2.37

1.65

2.37

1.65

2.37

1.65

2.37

3.14

-10

-40

1.8

2.5

1.8

2.5

1.8

2.5

1.8

2.5

3.3

1.89

2.63

1.89

2.63

1.89

2.63

1.89

2.63

3.47

-

-

+70

+85

V

V

V

V

V

V

V

V

V

°C

°C

ABSOLUTE MAXIMUM RATINGS

(AGND = DGND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supply Analog

Digital

Serial/Control Port Interface

Input Current (Note 2)

Analog Input Voltage

Digital Input Voltage

(Note 3)

Ambient Operating Temperature (power applied)

Storage Temperature

VA, VA_HP

VD

VL

I

in

V

IN

V

IND

T

A

T

stg

WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

Notes:

1. The device will operate properly over the full range of the analog, headphone amplifier, digital core and

serial/control port interface supplies.

2. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause

SCR latch-up.

3. The maximum over/under voltage is limited by the input current.

-0.3

-0.3

-0.3

-±10mA

AGND-0.7 VA+0.7

-0.3 VL+ 0.4 V

-50 +115 °C

-65 +150 °C

3.0

3.0

4.0

V

V

V

V

12 DS679F1

Page 13

CS42L51

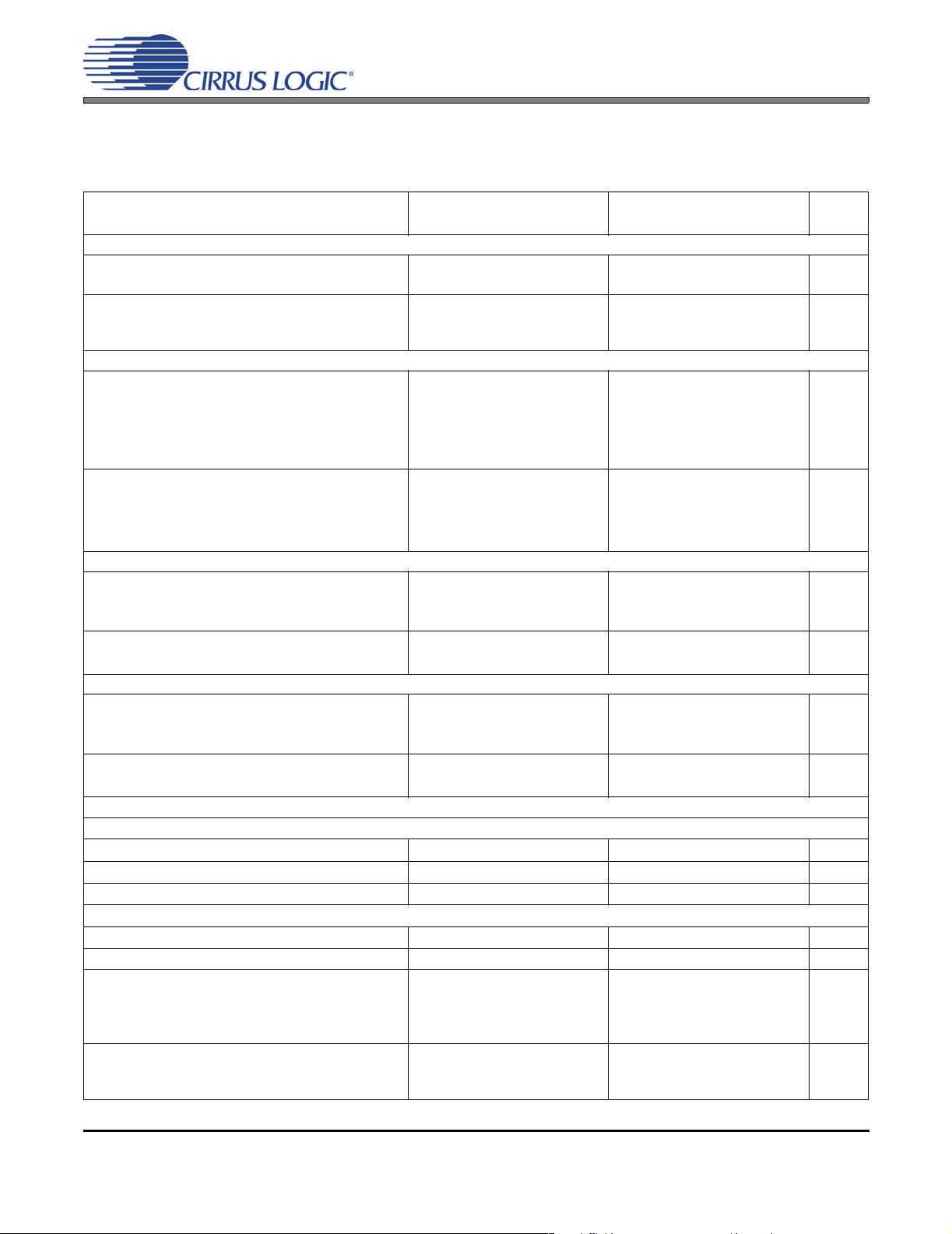

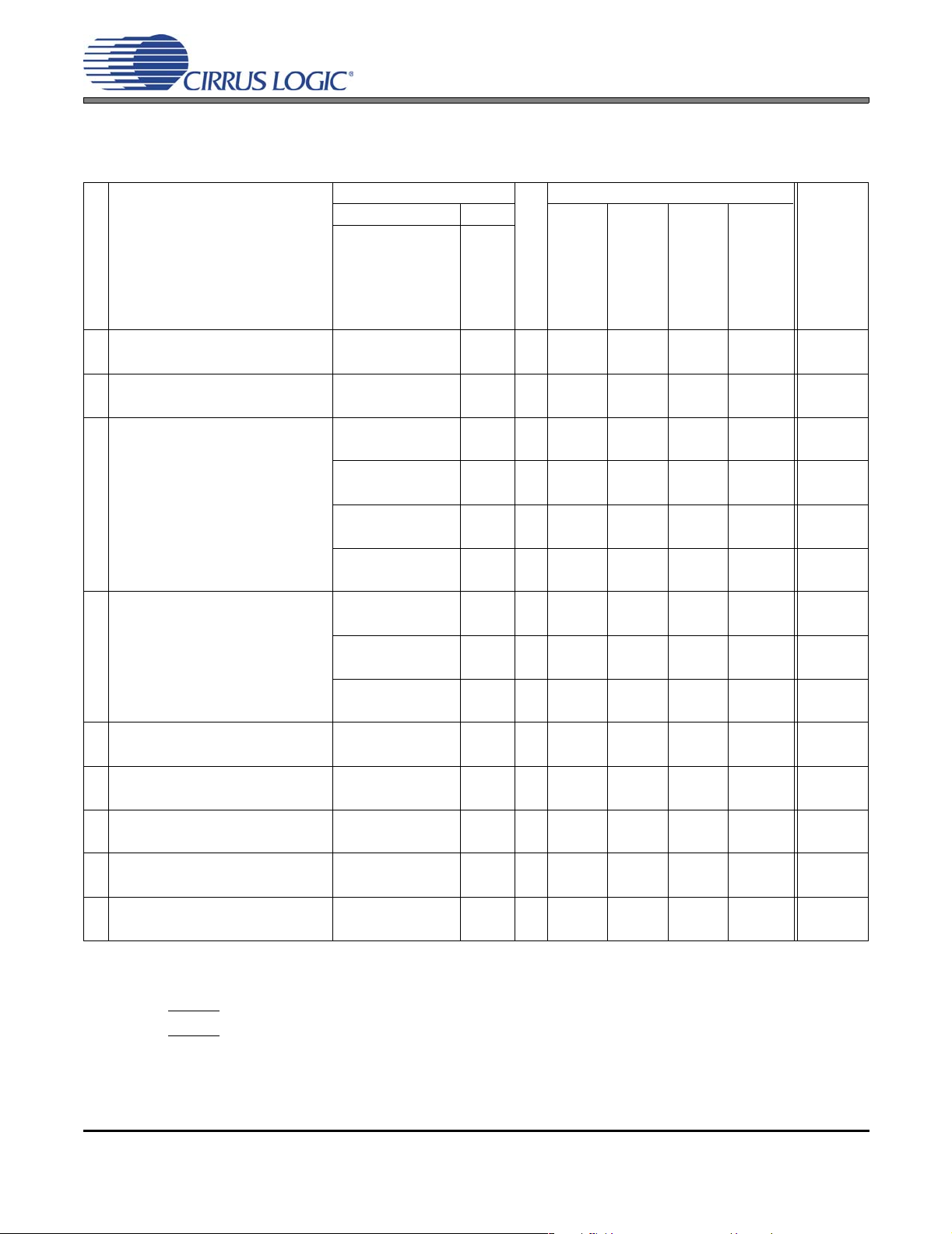

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ)

(Test Conditions (unless otherwise specified): Input sine wave (relative to digital full scale): 1 kHz through passive

input filter; Measurement Bandwidth is 10 Hz to 20 kHz unless otherwise specified. Sample Frequency = 48 kHz)

VA = 2.5 V (nominal) VA = 1.8 V (nominal)

Parameter (Note 5)

Analog In to ADC (PGA bypassed)

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise -1 dBFS

-20 dBFS

-60 dBFS

Analog In to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

PGA Setting: +12 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

-60 dBFS

PGA Setting: +12 dB -1 dBFS

Analog In to MIC Pre-Amp (+16 dB) to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

Analog In to MIC Pre-Amp (+32 dB) to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

Other Characteristics

DC Accuracy

Interchannel Gain Mismatch

Gain Drift

Offset Error SDOUT Code with HPF On

Input

Interchannel Isolation

DAC Isolation (Note 4)

Full-scale Input Voltage ADC

PGA (0 dB)

MIC (+16 dB)

MIC (+32 dB)

Input Impedance (Note 6) ADC

PGA

MIC

Min Typ Max Min Typ Max Unit

93

90

-

-

-

92

89

85

82

-

-

- -85 -79 - -83 -77 dB

-

-

--76- --74-dB

-

-

--74- --71-dB

-0.2- -0.2-dB

- ±100 - - ±100 - ppm/°C

- 352 - - 352 - LSB

-90--90-dB

-70--70-dB

0.74•VA

0.75•VA

-

-

-

99

96

-86

-76

-36

98

95

91

88

-88

-35

86

83

78

74

0.78•VA

0.794•VA

0.129•VA

0.022•VA

20

39

50

-

-

-80

-

-

-

-

-

-

-81

-

-

-

-

-

0.82•VA

0.83•VA

-

-

-

90

87

-

-

-

89

86

82

79

-

-

-

-

-

-

0.74•VA

0.75•VA

-

-

-

96

93

-84

-73

-33

95

92

88

85

-86

-32

83

80

75

71

0.78•VA

0.794•VA

0.129•VA

0.022•VA

20

39

50

-

-

-78

-

-

-

-

-

-

-80

-

-

-

-

-

0.82•VA

0.83•VA

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

Vpp

Vpp

Vpp

kΩ

kΩ

kΩ

DS679F1 13

Page 14

CS42L51

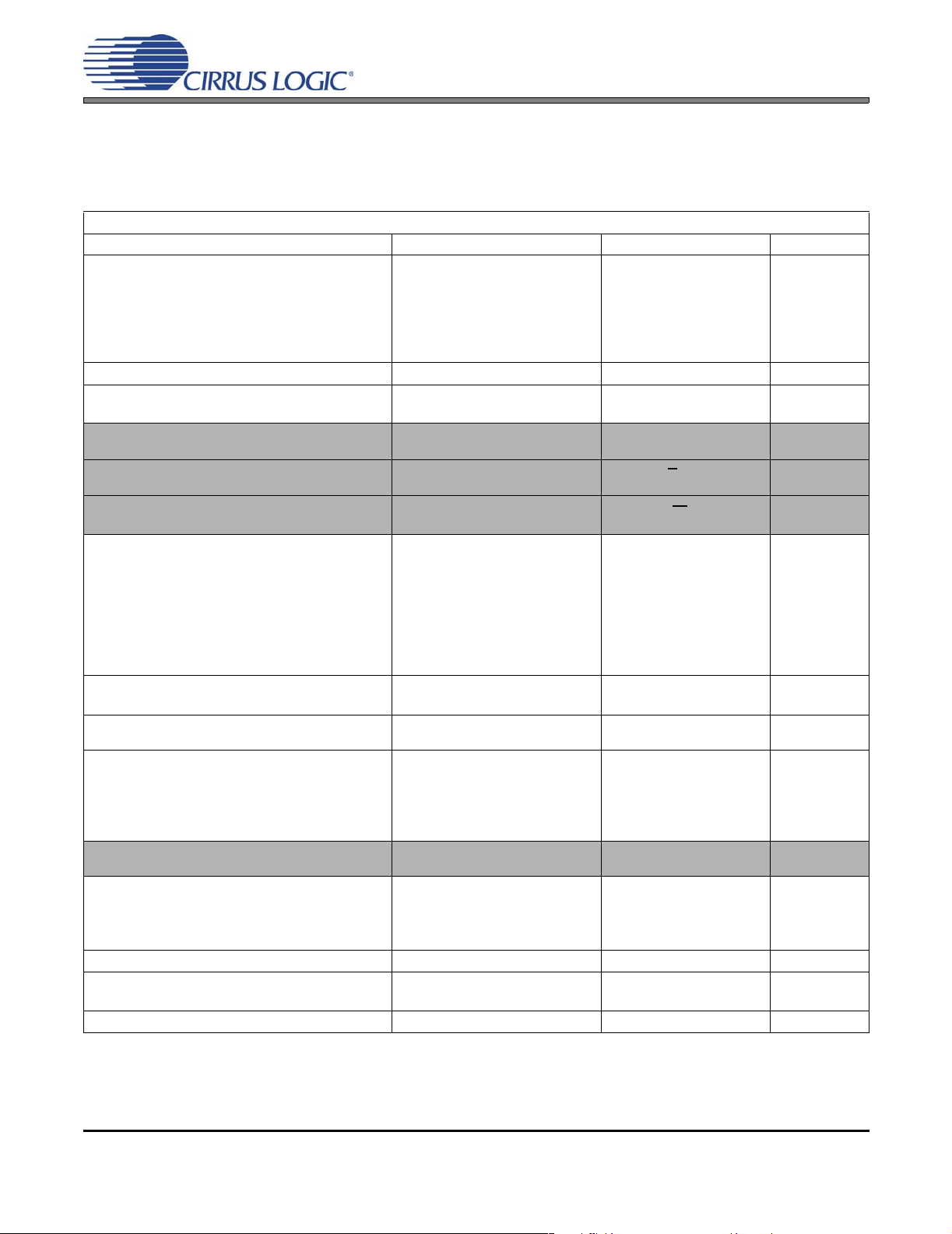

ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ)

(Test Conditions (unless otherwise specified): Input sine wave (relative to full scale): 1 kHz through passive input

filter; Measurement Bandwidth is 10 Hz to 20 kHz unless otherwise specified. Sample Frequency = 48 kHz)

VA = 2.5 V (nominal) VA = 1.8 V (nominal)

Parameter (Note 5)

Analog In to ADC

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise -1 dBFS

-20 dBFS

-60 dBFS

Analog In to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

PGA Setting: +12 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

-60 dBFS

PGA Setting: +12 dB -1 dBFS

Analog In to MIC Pre-Amp (+16 dB) to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

Analog In to MIC Pre-Amp (+32 dB) to PGA to ADC

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

Other Characteristics

DC Accuracy

Interchannel Gain Mismatch

Gain Drift

Offset Error SDOUT Code with HPF On

Input

Interchannel Isolation

DAC Isolation (Note 4)

Full-scale Input Voltage ADC

PGA (0 dB)

MIC (+16 dB)

MIC (+32 dB)

Input Impedance (Note 6) ADC

PGA

MIC

4. Measured with DAC delivering full-scale output power into 16 Ω.

Min Typ Max Min Typ Max Unit

91

78

-

-

-

90

87

83

80

-

-

- -85 -77 - -83 -75 dB

-

-

--76---74-dB

-

-

--74---71-dB

- 0.1 - - 0.1 - dB

- ±100 - - ±100 - ppm/°C

- 352 - - 352 - LSB

-90--90-dB

-70--70-dB

0.74•VA

0.75•VA

18

40

50

99

96

-86

-76

-36

98

95

91

88

-88

-35

86

83

78

74

0.78•VA

0.794•VA

0.129•VA

0.022•VA

-

-

-

-

-

-78

-

-

-

-

-

-

-80

-

-

-

-

-

0.82•VA

0.83•VA

-

-

-

88

85

-

-

-

87

84

80

77

-

-

-

-

-

-

0.74•VA

0.75•VA

18

40

50

96

93

-84

-73

-33

95

92

88

85

-86

-32

83

80

75

71

0.78•VA

0.794•VA

0.129•VA

0.022•VA

-

-

-

-

-

-76

-

-

-

-

-

-

-78

-

-

-

-

-

0.82•VA

0.83•VA

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

Vpp

Vpp

Vpp

kΩ

kΩ

kΩ

14 DS679F1

Page 15

5. Referred to the typical full-scale voltage. Applies to all THD+N and Dynamic Range values in the table.

6. Measured between AINxx and AGND.

ADC DIGITAL FILTER CHARACTERISTICS

Parameter (Note 7) Min Typ Max Unit

Passband (Frequency Response) to -0.1 dB corner

Passband Ripple

Stopband

Stopband Attenuation

Total Group Delay

High-Pass Filter Characteristics (48 kHz Fs)

Frequency Response -3.0 dB

-0.13 dB

Phase Deviation @ 20 Hz

Passband Ripple

Filter Settling Time

CS42L51

0 - 0.4948 Fs

-0.09 - 0.17 dB

0.6 - - Fs

33 - - dB

- 7.6/Fs - s

-

-

-10-Deg

- - 0.17 dB

-10

3.7

24.2

5

/Fs 0 s

-

-

Hz

Hz

7. Response is clock-dependent and will scale with Fs. Note that the response plots (Figure 33 to Figure 41)

have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs. HPF parameters are for Fs = 48 kHz.

DS679F1 15

Page 16

CS42L51

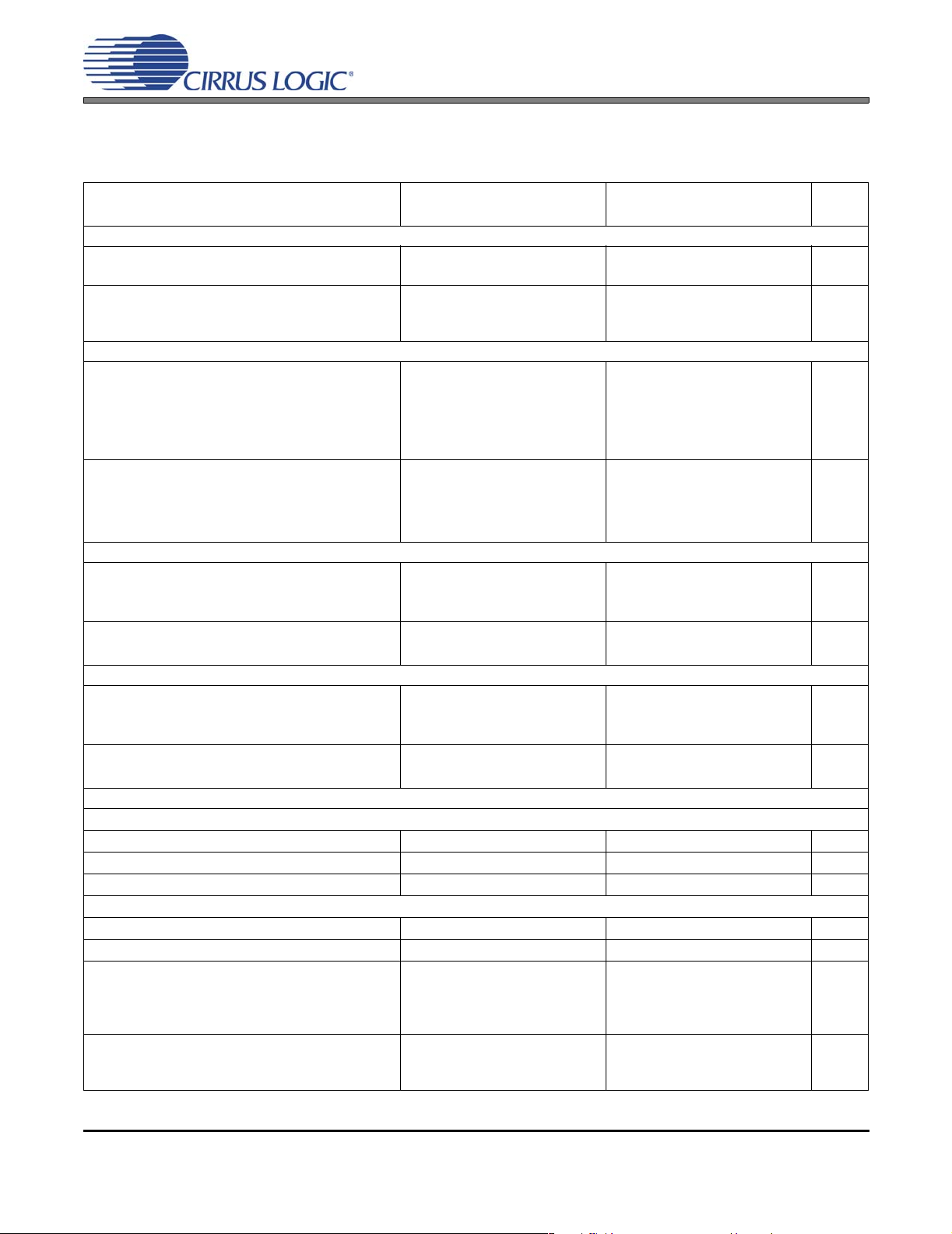

ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ)

(Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; measurement

bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz; test load R

(see Figure 3), and test load R

= 16 Ω, CL = 10 pF (see Figure 3) for the headphone output. HP_GAIN[2:0] = 011.)

L

= 10 kΩ, CL = 10 pF for the line output

L

Parameter (Note 8)

RL = 10 kΩ

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

RL = 16 Ω

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for RL = 16 Ω or 10 k

Output Parameters Modulation Index (MI)

(Note 9) Analog Gain Multiplier (G)

Full-scale Output Voltage (2•G•MI•VA) (Note 9)

Full-scale Output Power (Note 9)

Interchannel Isolation (1 kHz) 16 Ω

Interchannel Gain Mismatch

Gain Drift

AC-Load Resistance (R

Load Capacitance (C

) (Note 10)

L

) (Note 10)

L

Ω

10 kΩ

VA = 2.5V (nominal)

Min Typ Max

92

89

-

-

-

-

-

-

-

-

92

89

-

-

-

-

-

-

-

-

-

Refer to Table “Line Output Voltage Characteristics” on

Refer to Table “Headphone Output Power Characteristics”

-

-

- 0.1 0.25 - 0.1 0.25 dB

- ±100 - - ±100 -

16 - - 16 - - Ω

- - 150 - - 150 pF

98

95

96

93

-86

-75

-35

-86

-73

-33

98

95

96

93

-75

-75

-35

-75

-73

-33

0.6787

0.6047

80

95

-

-

-

-

-78

-

-

-

-

-

-

-

-

-

-69

-

-

-

-

-

--

page 18

on page 19

-

-

VA = 1.8V

(nominal)

Min Typ Max Unit

89

86

-

-

-

-

-

-

-

-

89

86

-

-

-

-

-

-

-

-

-

-

95

92

93

90

-88

-72

-32

-88

-70

-30

95

92

93

90

-75

-72

-32

-75

-70

-30

0.6787

0.6047

80

93

-

-

-

-

-82

-

-

-

-

-

-

-

-

-

-69

-

-

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

mW

dB

dB

ppm/°

C

16 DS679F1

Page 17

CS42L51

ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ)

(Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; measurement

bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz and 96 kHz; test load R

line output (see Figure 3), and test load R

= 16 Ω, CL = 10 pF (see Figure 3) for the headphone output.

L

HP_GAIN[2:0] = 011.)

= 10 kΩ, CL = 10 pF for the

L

Parameter (Note 8)

RL = 10 kΩ

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

RL = 16

Ω

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for RL = 16 Ω or 10 k

Output Parameters Modulation Index (MI)

(Note 9) Analog Gain Multiplier (G)

Full-scale Output Voltage (2•G•MI•VA) (Note 9)

Full-scale Output Power (Note 9)

Interchannel Isolation (1 kHz) 16 Ω

Interchannel Gain Mismatch

Gain Drift

AC-Load Resistance (R

Load Capacitance (C

) (Note 10)

L

) (Note 10)

L

Ω

10 kΩ

VA = 2.5V (nominal)

Min Typ Max

90

87

-

-

-

-

-

-

-

-

90

87

-

-

-

-

-

-

-

-

-

Refer to Table “Line Output Voltage Characteristics” on

Refer to Table “Headphone Output Power Characteristics”

-

-

- 0.1 0.25 - 0.1 0.25 dB

- ±100 - - ±100 -

16 - - 16 - - Ω

- - 150 - - 150 pF

98

95

96

93

-86

-75

-35

-86

-73

-33

98

95

96

93

-75

-75

-35

-75

-73

-33

0.6787

0.6047

80

95

-

-

-

-

-73

-

-

-

-

-

-

-

-

-

-67

-

-

-

-

-

--

page 18

on page 19

-

-

VA = 1.8V

(nominal)

Min Typ Max Unit

87

84

-

-

-

-

-

-

-

-

87

84

-

-

-

-

-

-

-

-

-

-

95

92

93

90

-88

-72

-32

-88

-70

-30

95

92

93

90

-75

-72

-32

-75

-70

-30

0.6787

0.6047

80

93

-

-

-

-

-80

-

-

-

-

-

-

-

-

-

-67

-

-

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

mW

dB

dB

ppm/°

C

DS679F1 17

Page 18

CS42L51

LINE OUTPUT VOLTAGE CHARACTERISTICS

Test conditions (unless otherwise specified): Inp ut test signal is a fu ll-scale 997 Hz sine wave; measurement bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz; test load R

= 10 kΩ, CL = 10 pF (see Figure 3).

L

Parameter

AOUTx Voltage Into RL = 10 k

HP_GAIN[2:0]

000 0.3959

001 0.4571

010 0.511 1

011 (default) 0.6047

100 0.7099

101 0.8399

110 1.0000

111 1.1430

Analog

Gain (G)

VA = 2.5V (nominal)

Min Typ Max

VA = 1.8V

(nominal)

Min Typ Max Unit

Ω

VA_HP

1.8 V - 1.34 - - 0.97 - V

2.5 V - 1.34 - - 0.97 - V

1.8 V - 1.55 - - 1.12 - V

2.5 V - 1.55 - - 1.12 - V

1.8 V - 1.73 - - 1.25 - V

2.5 V - 1.73 - - 1.25 - V

1.8 V - 2.05 - 1.41 1.48 1.55 V

2.5 V 1.95 2.05 2.15 - 1.48 - V

1.8 V - 2.41 - - 1.73 - V

2.5 V - 2.41 - - 1.73 - V

1.8 V - 2.85 - 2.05 V

2.5 V - 2.85 - - 2.05 - V

1.8 V - 3.39 - - 2.44 - V

2.5 V - 3.39 - - 2.44 - V

1.8 V

2.5 V - 3.88 - - 2.79 - V

(See (Note 11) 2.79 V

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

pp

18 DS679F1

Page 19

CS42L51

HEADPHONE OUTPUT POWER CHARACTERISTICS

Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; measurement bandwidth is 10 Hz to 20 kHz; Sample Frequency = 48 kHz; test load R

= 16 Ω, CL = 10 pF (see Figure 3).

L

Parameter

AOUTx Power Into RL = 16

HP_GAIN[2:0]

000 0.3959

001 0.4571

010 0.511 1

011 (default) 0.6 047

100 0.7099

101 0.8399

110 1.0000

111 1.1430

Analog

Gain (G)

8. One-half LSB of triangular PDF dither is added to data.

9. Full-scale output voltage and power is determined by the gain setting, G, in register “Headphone Analog

Gain (HP_GAIN[2:0])” on page 57. High gain settings at certain VA and VA_HP supply levels may

cause clipping when the audio signal approaches full-scale, maximum power output, as shown in

Figures 27 - 30 on page 76.

10. See Figure 3. R

quired for the internal op-amp's stability and signal integrity. In this circuit topology, C

move the band-limiting pole of the amp in the output stage. Increasing this value beyond the recommended 150 pF can cause the internal op-amp to become unstable.

11. VA_HP settings lower than VA reduces the headroom of the h eadphone amplifier. As a resu lt, the DAC

may not achieve the full THD+N performance at full-scale output voltage and power.

VA = 2.5V (nominal)

Min Typ Max

VA = 1.8V

(nominal)

Min Typ Max Unit

Ω

VA_HP

1.8 V - 14 - - 7 - mW

2.5 V - 14 - - 7 - mW

1.8 V - 19 - - 10 - mW

2.5 V - 19 - - 10 - mW

1.8 V - 23 - - 12 - mW

2.5 V - 23 - - 12 - mW

1.8 V (Note 11) -17 -mW

2.5 V - 32 - - 17 - mW

1.8 V (Note 11) -23 -mW

2.5 V - 44 - - 23 - mW

1.8 V (Note 9) mW

2.5 V -32 -mW

1.8 V

2.5 V mW

(Note 9, 11)

1.8 V mW

2.5 V mW

and CL reflect the recommended minimum resistance and maximum capacitance re-

L

will effectively

L

mW

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

rms

AOUTx

AGND

51 Ω

0.022 µF

C

L

R

L

Figure 3. Headphone Output Test Load

DS679F1 19

Page 20

CS42L51

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

Parameter (Note 12) Min Typ Max Unit

Frequency Response 10 Hz to 20 kHz

Passband to -0.05 dB corner

to -3 dB corner

StopBand

StopBand Attenuation (Note 13)

Group Delay

De-emphasis Error Fs = 32 kHz

Fs = 44.1 kHz

Fs = 48 kHz

-0.01 - +0.08 dB

0

0

0.5465 - - Fs

50 - - dB

- 10.4/Fs - s

-

-

-

-

-

-

-

-

0.4780

0.4996

+1.5/+0

+0.05/-0.25

-0.2/-0.4

Fs

Fs

dB

dB

dB

Notes:

12. Response is clock dependent and will scale with Fs. Note that the response plots (Figure 38 to Figure 41

on page 82) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

13. Measurement Bandwidth is from Stopband to 3 Fs.

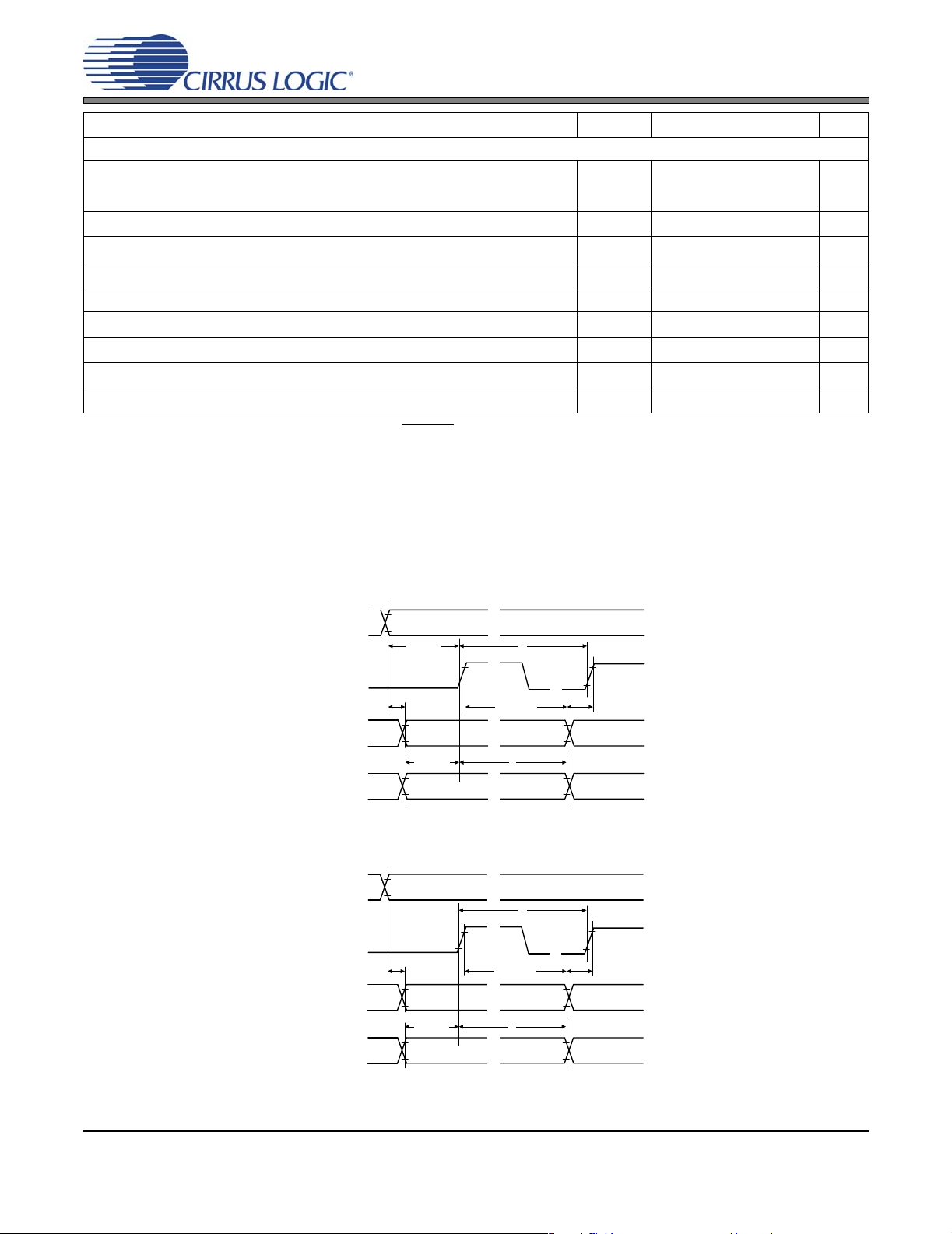

SWITCHING SPECIFICATIONS - SERIAL PORT

(Inputs: Logic 0 = DGND, Logic 1 = VL, SDOUT C

LOAD

= 15 pF.)

Parameters Symbol Min Max Units

RESET pin Low Pulse Width (Not e 14 )

MCLK Frequency

MCLK Duty Cycle (Note 15)

Slave Mode

Input Sample Rate (LRCK) Quarter-Speed Mode

Half-Speed Mode

Single-Speed Mode

Double-Speed Mode

LRCK Duty Cycle

SCLK Frequency

SCLK Duty Cycle

LRCK Setup Time Before SCLK Rising Edge

LRCK Edge to SDOUT MSB Output Delay

SDOUT Setup Time Before SCLK Rising Edge

SDOUT Hold Time After SCLK Rising Edge

SDIN Setup Time Before SCLK Rising Edge

SDIN Hold Time After SCLK Rising Edge

F

s

F

s

F

s

F

s

1/t

P

t

s(LK-SK)

t

d(MSB)

t

s(SDO-SK)

t

h(SK-SDO)

t

s(SD-SK)

t

h

1-ms

1.024 38.4 MHz

45 55 %

4

8

4

50

45 55 %

-64•FsHz

45 55 %

40 - ns

-52ns

20 - ns

30 - ns

20 - ns

20 - ns

12.5

25

50

100

kHz

kHz

kHz

kHz

20 DS679F1

Page 21

Master Mode (Note 17)

CS42L51

Parameters Symbol Min Max Units

Output Sample Rate (LRCK) All Speed Modes

(Note 17)

LRCK Duty Cycle

SCLK Frequency

SCLK Duty Cycle

LRCK Edge to SDOUT MSB Output Delay

SDOUT Setup Time Before SCLK Rising Edge

SDOUT Hold Time After SCLK Rising Edge

SDIN Setup Time Before SCLK Rising Edge

SDIN Hold Time After SCLK Rising Edge

14. After powering up the CS42L51, RESET should be held low after the power supplies and clocks are

settled.

15. See “Example System Clock Frequencies” on page 79 for typical MCLK frequencies.

16. See

17. “Master” on page 39

18. “MCLK” refers to the external master clock applied.

LRCK

//

t

s(LK-SK)

//

t

P

//

SCLK

//

SDOUT

SDIN

t

d(MSB)

t

s(SD-SK)

MSB

MSB

t

h(SK-SDO)

//

//

t

//

//

h

Figure 4. Serial Audio Interface Slave Mode Timing

F

s

1/t

P

t

d(MSB)

t

s(SDO-SK)

t

h(SK-SDO)

t

s(SD-SK)

t

h

t

s(SDO-SK)

MSB-1

MSB-1

MCLK

-Hz

----------------128

45 55 %

- 64•F

Hz

s

45 55 %

-52ns

20 - ns

30 - ns

20 - ns

20 - ns

LRCK

//

//

t

P

//

SCLK

//

SDOUT

SDIN

t

d(MSB)

t

s(SD-SK)

MSB

MSB

t

h(SK-SDO)

//

//

t

//

//

t

s(SDO-SK)

MSB-1

h

MSB-1

Figure 5. Serial Audio Interface Master Mode Timing

DS679F1 21

Page 22

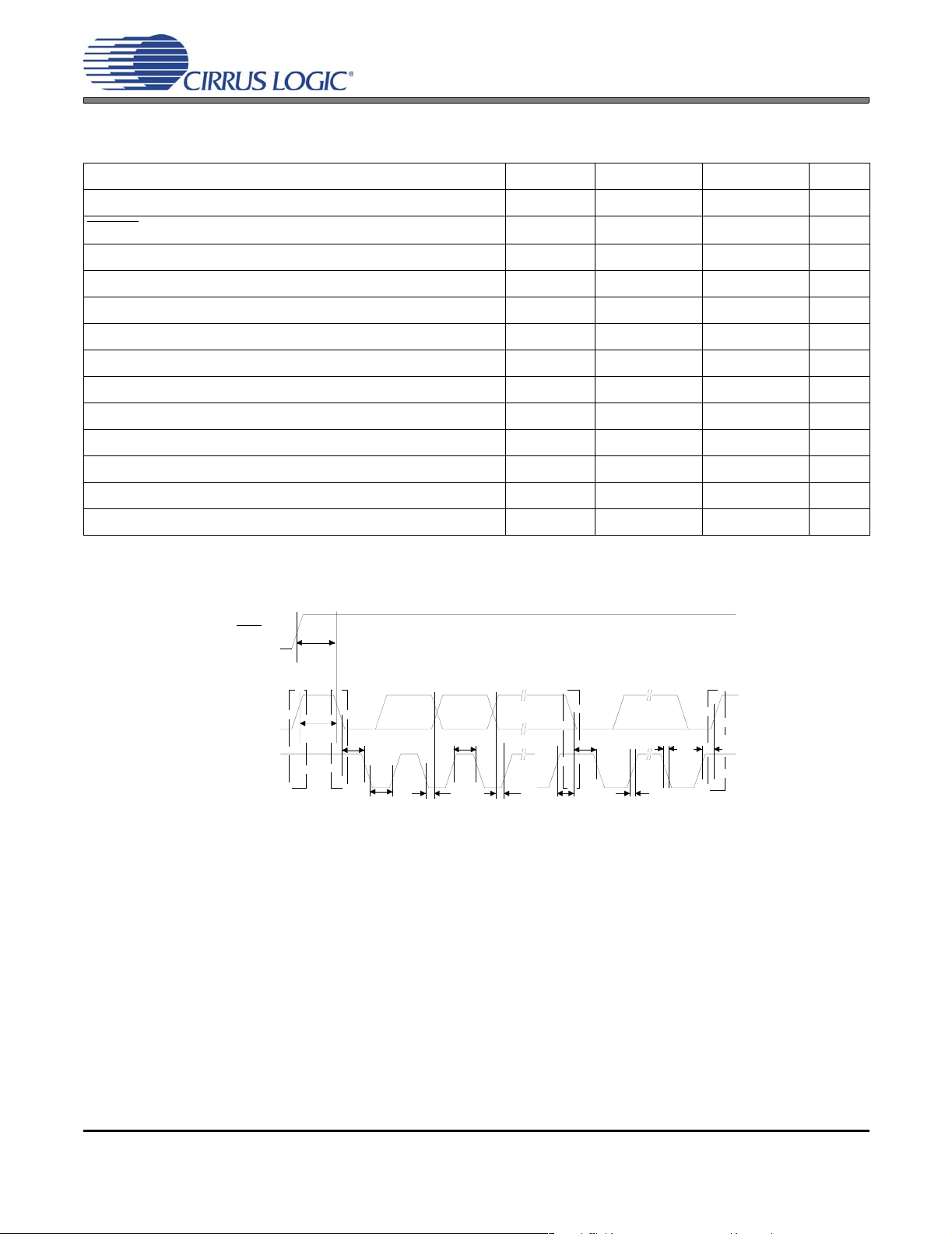

SWITCHING SPECIFICATIONS - I²C® CONTROL PORT

(Inputs: Logic 0 = DGND, Logic 1 = VL, SDA CL=30pF)

Parameter Symbol Min Max Unit

SCL Clock Frequency

RESET Rising Edge to Start

Bus Free Time Between Transmissions

Start Condition Hold Time (prior to first clock pulse)

Clock Low time

Clock High Time

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling (Note 19)

SDA Setup time to SCL Rising

Rise Time of SCL and SDA

Fall Time SCL and SDA

Setup Time for Stop Condition

Acknowledge Delay from SCL Falling

f

t

t

t

hdst

t

low

t

high

t

sust

t

hdd

t

sud

t

t

susp

t

ack

scl

irs

buf

rc

t

fc

CS42L51

- 100 kHz

500 - ns

4.7 - µs

4.0 - µs

4.7 - µs

4.0 - µs

4.7 - µs

0-µs

250 - ns

-1µs

- 300 ns

4.7 - µs

300 3450 ns

19. Data must be held for sufficient time to bridge the transition time, t

RST

t

SDA

SCL

irs

Stop Start

t

buf

t

t

hdst

low

t

high

t

hdd

Figure 6. Control Port Timing - I²C

t

sud

Repeated

Start

t

sust

t

hdst

, of SCL.

fc

t

t

r

Stop

f

t

susp

22 DS679F1

Page 23

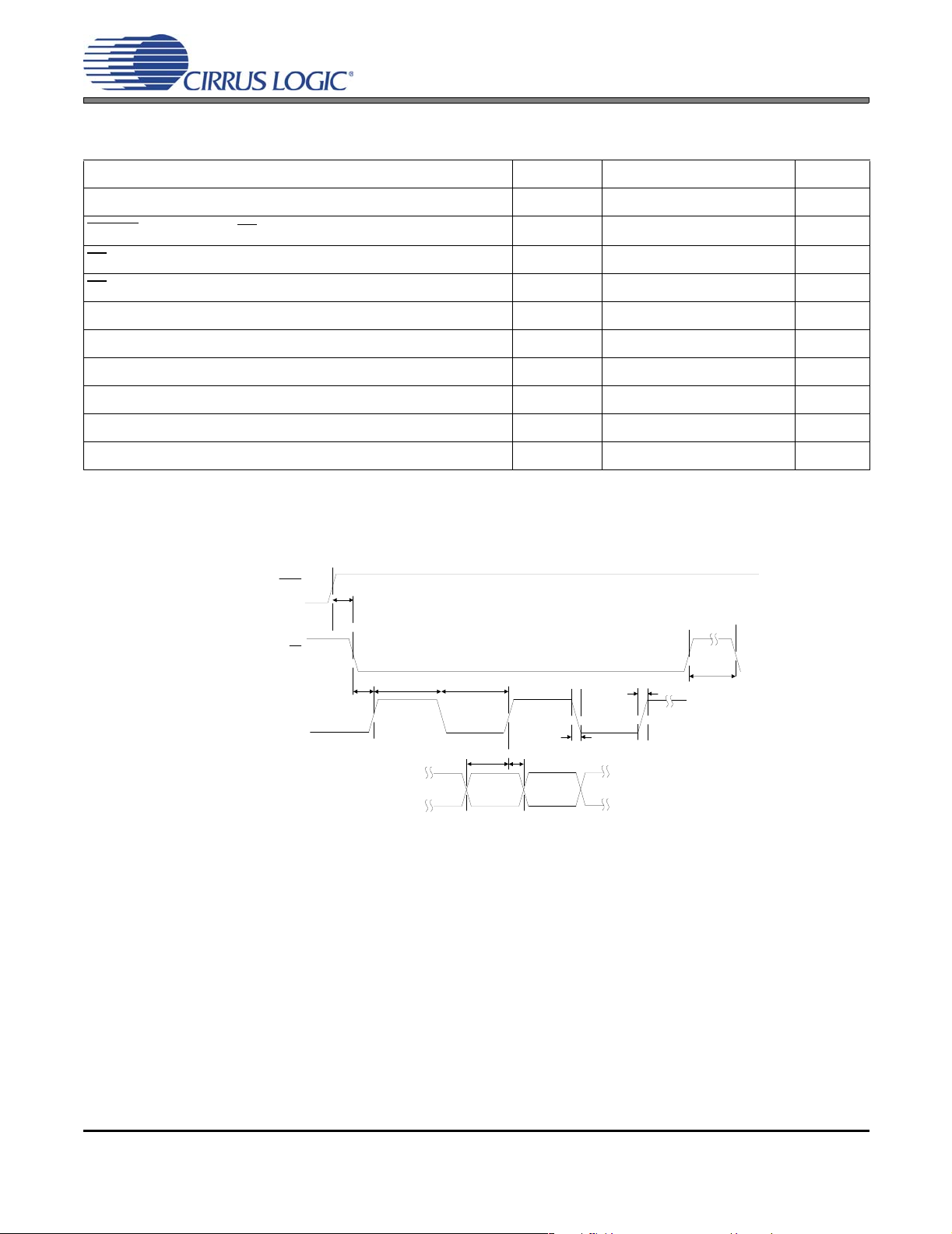

SWITCHING CHARACTERISTICS - SPI™ CONTROL PORT

(Inputs: Logic 0 = DGN D, Lo gic 1 = VL)

Parameter Symbol Min Max Units

CS42L51

CCLK Clock Frequency

RESET Rising Edge to CS Falling

Falling to CCLK Edge

CS

CS

High Time Between Transmissions

CCLK Low Time

CCLK High Time

CDIN to CCLK Rising Setup Time

CCLK Rising to DATA Hold Time (Note 20)

Rise Time of CCLK and CDIN (Note 21)

Fall Time of CCLK and CDIN (Note 21)

20. Data must be held for sufficient time to bridge the transition time of CCLK.

21. For f

<1 MHz.

sck

RST

CS

CCLK

t

srs

t

t

sch

css

t

scl

t

dsu

f

sck

t

srs

t

css

t

csh

t

scl

t

sch

t

dsu

t

dh

t

r2

t

f2

t

f2

t

dh

06.0MHz

20 - ns

20 - ns

1.0 - µs

66 - ns

66 - ns

40 - ns

15 - ns

-100ns

-100ns

t

csh

t

r2

CDIN

Figure 7. Control Port Timing - SPI Format

DS679F1 23

Page 24

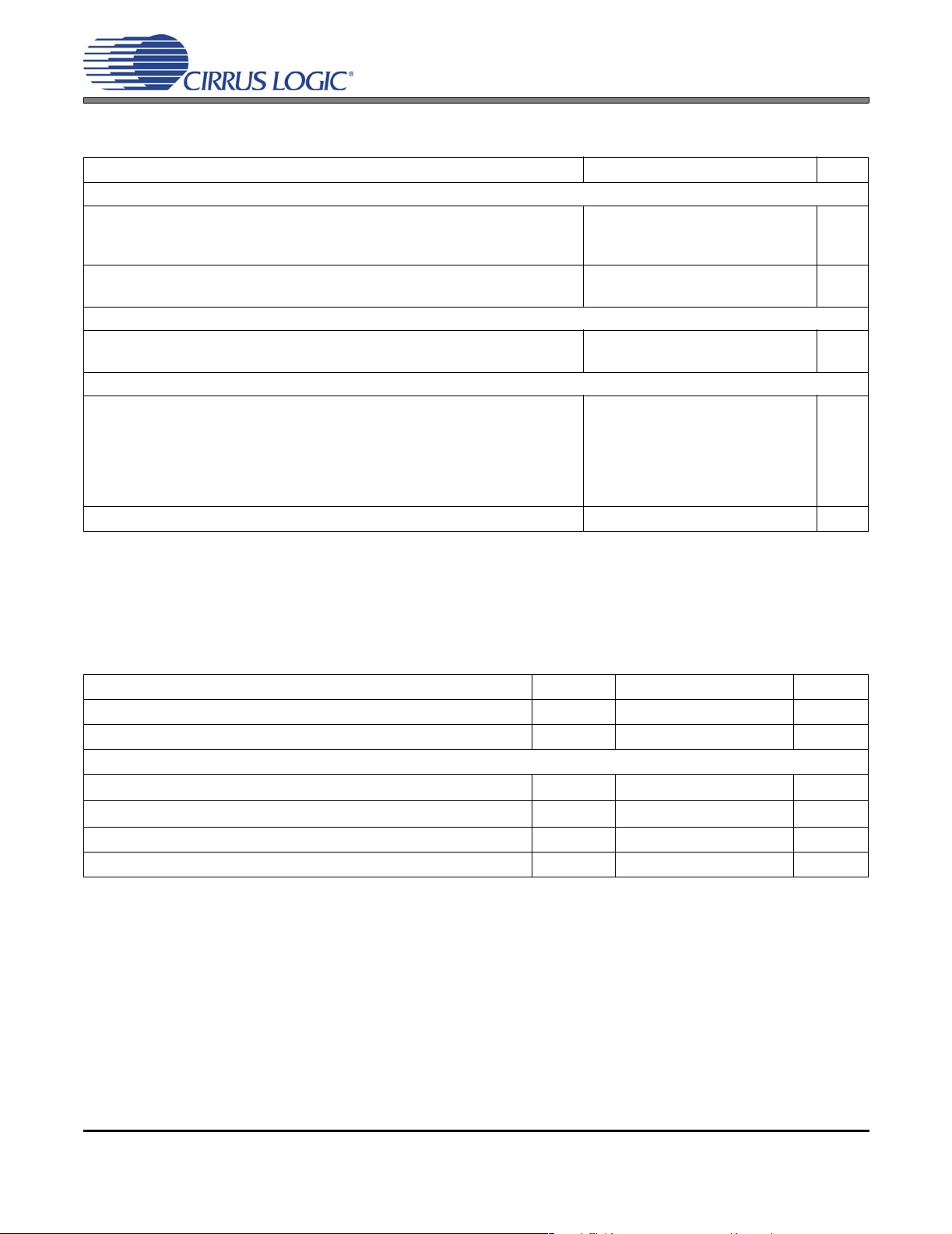

DC ELECTRICAL CHARACTERISTICS

(AGND = 0 V; all voltages with respect to ground.)

Parameters Min Typ Max Units

VQ Characteristics

Nominal Voltage

Output Impedance

DC Current Source/Sink (Note 22)

DAC_FILT+ Nominal Voltage

ADC_FILT+ Nominal Voltage

VSS_HP Characteristics

Nominal Voltage

DC Current Source

MIC BIAS Characteristics

Nominal Voltage MICBIAS_LVL[1:0] = 00

MICBIAS_LVL[1:0] = 01

MICBIAS_LVL[1:0] = 10

MICBIAS_LVL[1:0] = 11

DC Current Source

Power Supply Rejection Ratio (PSRR) 1 kHz

Power Supply Rejection Ratio (PSRR) (Note 23) 1 kHz

CS42L51

-

-

-

-

-

-

-

-

-

-

-

-

-

-60-dB

0.5•VA

23

-

VA

VA

-0.8•(VA_HP) -

0.8•VA

0.7•VA

0.6•VA

0.5•VA

-

50

10

10

-

-

-

-

-

-

-

-

1

-

V

kΩ

µA

V

V

V

µA

V

V

V

V

mA

dB

22. The DC current draw represents the allowed current draw from the VQ pin due to typical leakage

through electrolytic de-coupling capacitors.

23. Valid with the recommended capacitor values on DAC_FILT+, ADC_FILT+ and VQ. In crea sing the capacitance will also increase the PSRR.

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS

Parameters (Note 24) Symbol Min Max Units

Input Leakage Current

Input Capacitance

1.8 V - 3.3 V Logic

High-Level Output Voltage

Low-Level Output Voltage

High-Level Input Voltage

Low-Level Input Voltage

24. See “Digital I/O Pin Characteristics” on page 9 for serial and control port power rails.

(IOH = -100 µA)

(IOL = 100 µA)

I

in

V

OH

V

OL

V

IH

V

IL

-±10µA

-10pF

VL - 0.2 - V

-0.2V

0.68•VL - V

- 0.32•VL V

24 DS679F1

Page 25

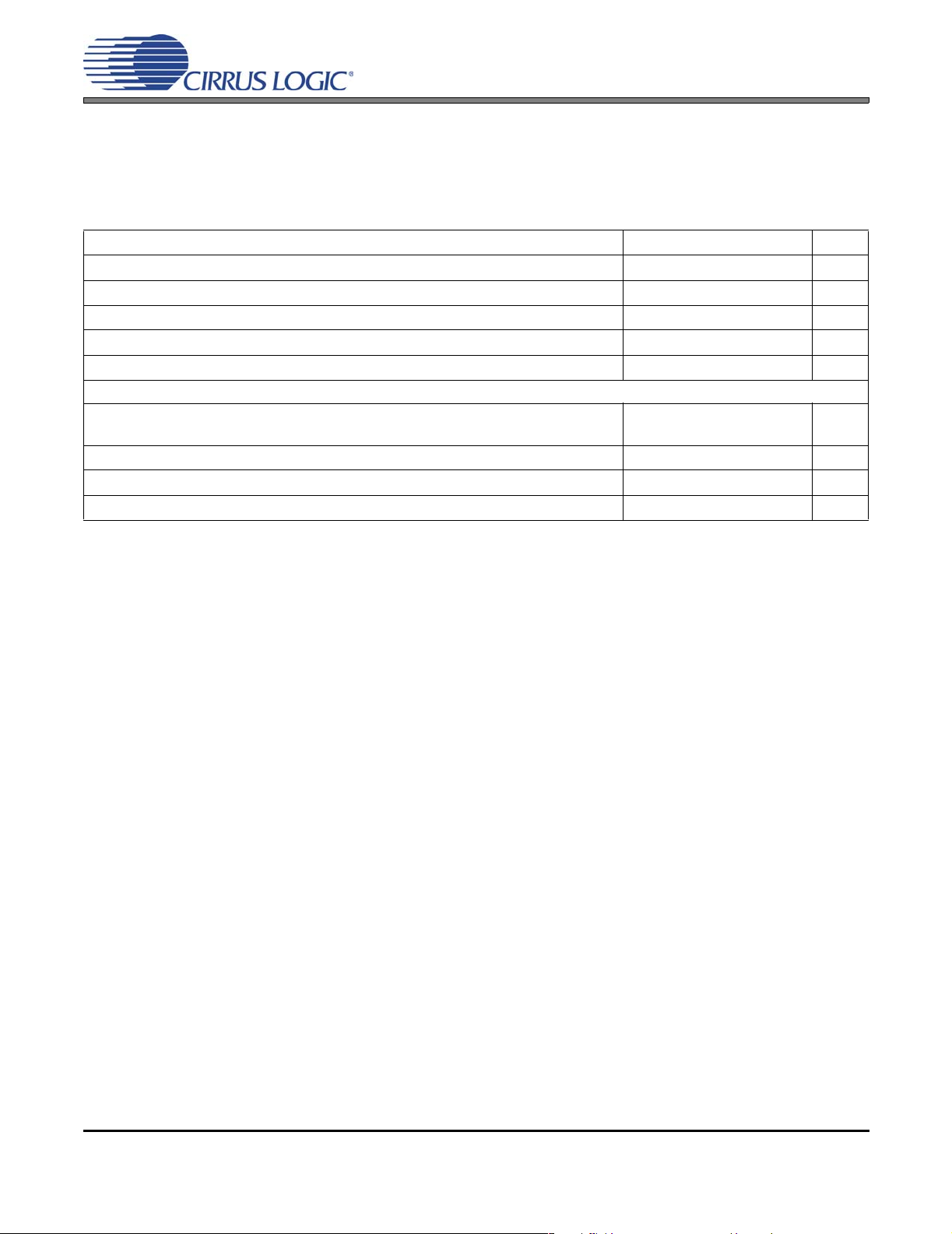

POWER CONSUMPTION

See (Note 25)

CS42L51

Power Ctl. Registers Typical Current (mA)

02h 03h

Operation

PDN_DACB

PDN_DACA

PDN_PGAB

PDN_PGAA

PDN_ADCB

PDN_ADCA

PDN

PDN_MICB

PDN_MICA

1

Off

(Note 26)

2 Standby (Note 27)

3 Mono Record ADC1111100111

PGA to ADC

MIC to PGA to ADC

(with Bias)

MIC to PGA to ADC

(no Bias)

4 Stereo Record ADC1111000111

PGA to ADC

MIC to PGA to ADC

(no Bias)

5 Mono Playback 1011110111

6 Stereo Playback

Mono Record & Playback

7

PGA in (no MIC) to Mono Out

Phone Monitor

8

MIC (w/bias) in to Mono Out

Stereo Record & Playback

9

PGA in (no MIC) to Stereo Out

xxxxxxxxxx

xxxxxx1xxx

1110100111

1110100100

1110100101

1100000111

1100000001

0011110111

1010100111

1010100100

0000000111

i

i

VA_HP

V

PDN_MICBIAS

1.8 0 0 0 0 0

2.5 0 0 0 0 0

1.8 0 0.01 0.02 0 0.05

2.5 0 0.01 0.03 0 0.10

1.8 0 1.85 2.03 0.03 7.05

2.5 0 2.07 3.05 0.05 12.94

1.8 0 2.35 2.03 0.03 7.95

2.5 0 2.58 3.08 0.05 14.29

1.8 0 3.67 2.05 0.03 10.36

2.5 0 3.95 3.09 0.05 17.71

1.8 0 3.27 2.03 0.03 9.61

2.5 0 3.52 3.08 0.05 16.62

1.8 0 2.69 2.12 0.03 8.72

2.5 0 2.93 3.18 0.04 15.40

1.8 0 3.65 2.12 0.03 10.45

2.5 0 3.91 3.17 0.04 17.84

1.8 0 5.48 2.11 0.03 13.73

2.5 0 5.76 3.17 0.04 22.45

1.8 1.66 1.40 2.35 0.01 9.74

2.5 2.03 1.71 3.48 0.02 18.08

1.8 2.77 2.05 2.35 0.01 12.93

2.5 3.21 2.50 3.49 0.02 23.02

1.8 1.66 3.63 2.73 0.03 14.49

2.5 2.03 4.16 4.08 0.05 25.79

1.8 1.66 4.95 2.75 0.03 16.90

2.5 2.03 5.52 4.08 0.05 29.20

1.8 2.77 5.59 2.82 0.03 20.18

2.5 3.21 6.28 4.19 0.04 34.30

i

VA

i

VD

VL

(Note 28)

Total

Power

(mW

rms

)

25. Unless otherwise noted, test conditions are as follows: All zeros input, slave mode, sample rate =

48 kHz; No load. Digital (VD) and logic (VL) supply current will vary depending on speed mode and master/slave operation.

26. RESET

27. RESET

pin 25 held LO, all clocks and data lines are held LO.

pin 25 held HI, all clocks and data lines are held HI.

28. VL current will slightly increase in master mode.

DS679F1 25

Page 26

4. APPLICATIONS

4.1 Overview

4.1.1 Architecture

The CS42L51 is a highly integrated, low power, 24-bit au dio CODEC comprised of stereo analog-to-digital

converters (ADC), and stereo digital-to-analog converters (DAC) designed using multi-bit delta-sigma

techniques. The DAC operates at an oversampling ratio of 128Fs and the ADC operates at 64Fs, where

Fs is equal to the system sample rate. The different clock rates ma ximize power savings while maintaining

high performance. The CODEC operates in one of four sample rate speed modes: Quarter, Half, Single

and Double. It accepts and is capable of generating serial port clocks (SCLK, LRCK) derived from an input

Master Clock (MCLK).

4.1.2 Line & MIC Inputs

The analog input portion of the CODEC allows selection from and configuration of multiple combinations

of stereo and microphone (MIC) sources. Six line inputs with configuration for two MIC inputs (or one MIC

input with common mode rejection), two MIC bias outputs and independent channel control (including a

high-pass filter disable function) are available. A Programmable Gain Amplifier (PGA), MIC boost, and Automatic Level Control (ALC), with noise gate settings, provide analog gain and adjustment. Digital volume

controls, including gain, boost, attenuation and inversion are also available.

CS42L51

4.1.3 Line & Headphone Outputs

The analog output portion of the D/A includes a headphone amplifier capable of driving headphone and

line-level loads. An on-chip charge pump creates a negative headphone supply allowing a full-scale output swing centered around ground. This eliminates the need for large DC-Blocking capacitors and allows

the amplifier to deliver more power to headphone loads at lower supply voltages. Eight gain settings for

the headphone amplifier are available.

4.1.4 Signal Processing Eng ine

A signal processing engine is available to process serial input D/A data be fore output to the DAC. The

D/A data has independent volume controls and mixing functions such as mo no mixes a nd left/right cha nnel swaps. A Tone Control provides bass and treble at four selectable corner frequencies. An automatic

level control provides limiting capabilities at programmable attack and release rates, maximum thresholds

and soft ramping. A 15/50 µs de-emphasis filter is also available at a 44.1 kHz sample rate.

4.1.5 Beep Generator

A beep may be generated internally at select frequencies across approximately two octave major scales

and configured to occur continuously, periodically or at single time interva ls controlled by the user. Volume

may be controlled independently.

4.1.6 Device Control (Hardware or Software Mode)

In Software Mode, all functions and features may be controlled via a two-wire I²C or three-wire SPI control

port interface. In Hardware Mode, a limited feature set may be controlled via stand-alone control pins.

4.1.7 Power Management

Two Software Mode control registers provide independent power-down control of the ADC, DAC, PGA,

MIC pre-amp and MIC bias, allowing operation in select applications with minimal power consumption.

26 DS679F1

Page 27

4.2 Hardware Mode

A limited feature-set is available when the CODEC powers up in Hardware Mode (see “Recommended Pow-

er-Up Sequence” on page 41) and may be controlled via stand-alone control pins. Table 2 shows a list of

functions/features, the default configuration and the associated stand-alone control available.

Hardware Mode Feature/Function Summary

Feature/Function Default Configuration Stand-Alone Control Note

Power Control CODEC

PGAx

ADCx

DACx

MIC Bias

MICx Pre-amplifier

Auto-Detect

Speed Mode Serial Port Slave

Serial Port Master

MCLK Divide

Serial Port Master / Slave Selection

Interface Control ADC

DAC

ADC Volume & Gain Digital Boost

Soft Ramp

Zero Cross

Invert

PGAx

Attenuator

ALC

Noise Gate

ADCx High-Pass Filter

ADCx High-Pass Filter Freeze

Line/MIC Input Select

DAC Volume & Gain HP Gain

AOUTx Volume

Invert

Soft Ramp

Zero Cross

DAC De-Emphasis

Signal Processing Engine (SPE) Mix

Beep

Tone Control

Peak Detect and Limiter

Data Selection

Channel Mix ADC

DAC

Charge Pump Frequency

Table 2. Hardware Mode Feature Summary

CS42L51

Powered Up

Powered Up

Powered Up

Powered Up

Powered Down

Powered Down

Enabled - -

Auto-Detect Speed Mode

Single-Speed Mode

(Selectable) “MCLKDIV2” pin 2

(Selectable) “M/S” pin 29

(Selectable) “I²S/LJ” pin 3

Disabled

Disabled

Disabled

Disabled

0 dB

0 dB

Disabled

Disabled

Enabled

Continuous DC Subtraction

AIN1A to PGAA

AIN1B to PGAB

G = 0.6047

0 dB

Disabled

Enabled

Disabled

(Selectable) “DEM” pin 4

Disabled

Disabled

Disabled

Disabled

Data Input (PCM) to DAC - -

ADCA = L; ADCB = R

PCMA = L; PCMB = R

(64xFs)/7 - -

--

-see Section

4.5 on page 38

see Section

4.5 on page 38

see Section

4.6 on page 40

--

--

--

--

see Section

on page 34

--

--

DS679F1 27

Page 28

4.3 Analog Inputs

AINxA and AINxB are the analog inputs, internally biased to VQ, that accepts line-level and MIC-level signals, allowing various gain and signal adjustments for each channel.

CS42L51

ADCA_MUTE

+20dB

Digital

Boost

ADCA_ATT[7:0]

0/-96dB

1dB steps

Attenuator

SOFTA

MUX

DIGMIX

MUX

MICMIX

ADCA_HPF FREEZE

ADCA_HPF ENABLE

ALC_ARATE[5:0]

ALC_RRATE[5:0]

Σ

ALCA_SRDIS

ALCA_ZCDIS

ALC_ENA

MAX[2:0]

MIN[2:0]

ALC_ENB

ALCB_SRDIS

ALCB_ZCDIS