Page 1

SF-7900E(LX-552A)

SF-8900(LX-552I/J)

JAN. 1995

(without price)

(with price)

SF-7900E

R

Page 2

CONTENTS

SPECIFICATIONS ................................................................................................................ 1

TO REPLACE THE BATTERY ............................................................................................. 2

TO CHECK THE MEMORY CAPACITY............................................................................... 2

ERROR MESSAGE............................................................................................................... 3

TO RESET THE SF UNIT'S MEMORY................................................................................. 4

TO SAVE THE DATA TO ANOTHER UNIT ......................................................................... 5

BLOCK DIAGRAM................................................................................................................ 8

CIRCUIT EXPLANATIONS

System chart................................................................................................................. 9

Power supply circuit .................................................................................................. 10

CPU pin description (HD62076C03).......................................................................... 12

Gate array pin descriptions (SSC2571F0A) ............................................................. 13

Gate array pin descriptions (SSC2571F0B) ............................................................. 14

Operation program ROM pin descriptions .............................................................. 15

RAM pin descriptions ................................................................................................ 15

DIAGNOSTIC OPERATION................................................................................................ 16

TROUBLESHOOTING........................................................................................................ 21

SCHEMATIC DIAGRAM

Main PCB .................................................................................................................... 23

Display PCB................................................................................................................ 25

Key Matrix ................................................................................................................... 26

Key Matrix (Display side)........................................................................................... 27

PARTS LIST........................................................................................................................ 29

ASSEMBLY VIEW .............................................................................................................. 31

Page 3

SPECIFICATIONS

Main modes: Telephone Directory, Business Card Library, Memo, Schedule Keeper,

Expense, Reminder, Calendar, Home Time, World Time and Calculator

Data storage: Storage and recall of telephone, business card, memo, schedule, expense,

reminder data, calendar display, secret area; editing; memory status display

Clock: World Time; reminder alarm; schedule alarm; daily alarm; accuracy under

normal temperatures: ±3 seconds average

Calculation: 12-digit arithmetic calculations; arithemetic constants (+, –, ×, ÷); independ-

ent memory; percentages; square roots; 24-digit approximations; date calculations; other mixed calculations

General:

Display element: 16-column × 8-line LCD

Memory capacity: SF-7900E: 128KB (103436 bytes)

SF-8900: 256KB (234508 bytes)

Main component: LSI

Power supply: 3 lithium batteries (CR2032)

Power consumption: 0.07 W

Battery life*: Approximately 170 hours continuous operation in Telephone Directory;

approximately 130 hours repeating one minute of input and 10 minutes of

display in Telephone Directory; approximately 12 months for memory back

up

* The batteries that come installed in this unit when you purchase it are for

factory test purposes, so they will probably not provide normal service life.

Auto power off: Approximately 6 minutes after last key operation

Operating temperature: 0°C ~ 40°C (32°F ~ 104°F)

Dimensions:

Unfolded: 9.55H × 144W × 155D mm (3/8"H × 5 11/16"W × 6 1/8"D)

Folded: 15.95H × 144W × 77.5D mm(5/8"H × 5 11/16"W × 3 1/16"D)

Weight: 123g (4.3 oz.)

• Design and specifications are subject to change without notice.

Current consumption:

Power switch TYP. [µA] MAX [µA]

OFF 11.7 37.1

ON 1,670.0 13,711.0

ON (Operating) 4,520.0 16,645.0

— 1 —

Page 4

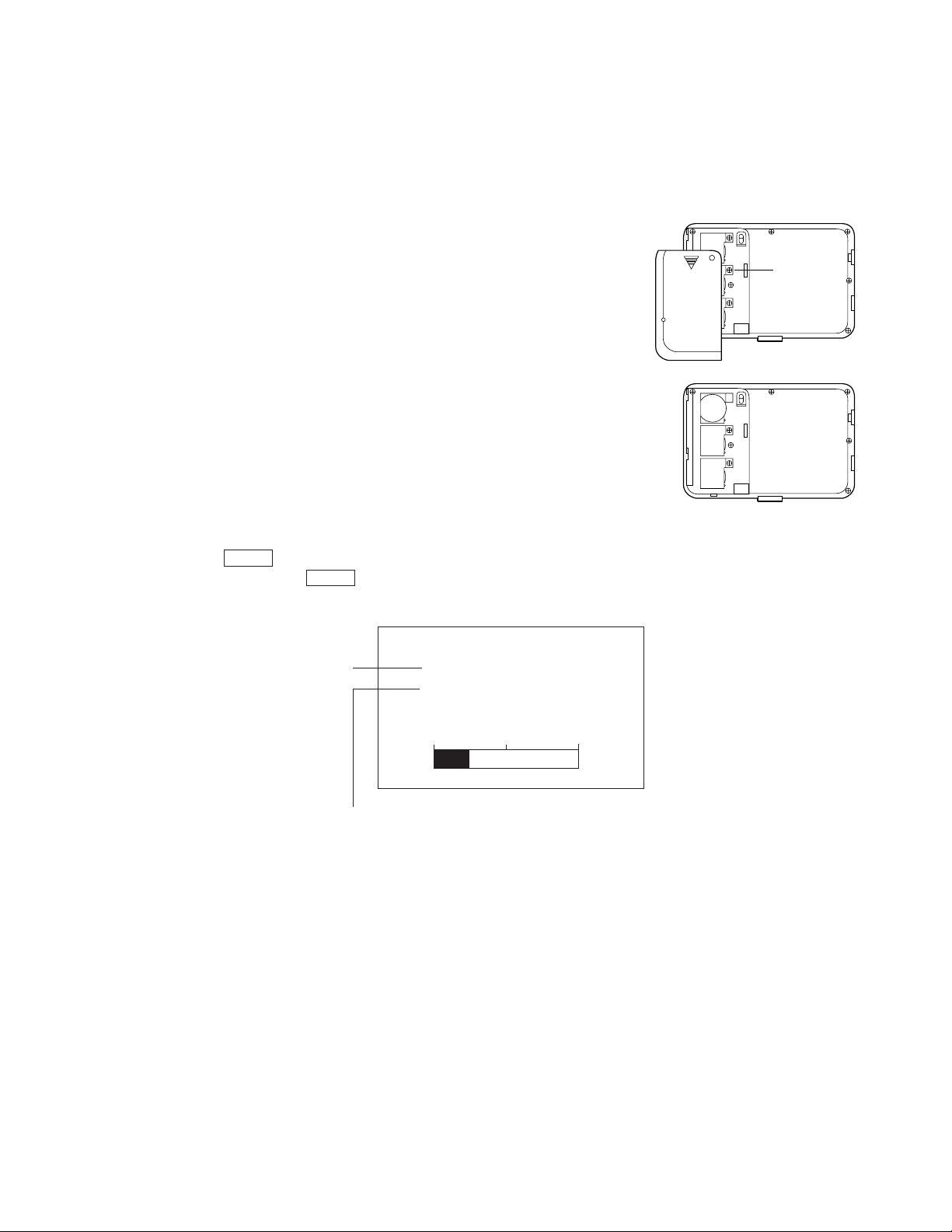

TO REPLACE THE BATTERY

Screw

RESET

+

To replace the batteries

1. Loosen the screw on the back of the SF unit that holds the battery compartment cover in

place, and remove the cover.

Caution

In the next step, be sure to remove only one battery at a time.

Otherwise, you will lose all data stored in memory.

2. Loosen the screw that secures one of the three battery holders

in place and remove the battery holder.

3. Replace the old battery with a new one, making sure that the

positive (+) side of the new battery is facing up (so you can see

it).

4. Replace the battery holder and secure it by tightening its screw.

TO CHECK THE MEMORY CAPACITY

Hold down CAPA to display a screen that shows the current memory status. To clear the memory

status display, release

Remaining memory

capacity

CAPA .

C A P A C I T Y

76420BytesFREE

27016BytesUSED

26 %

0

Total number of characters stored in memory

10050

— 2 —

Page 5

ERROR MESSAGE

Message Meaning Action

DATA ITEM Search operation Current search operation

NOT FOUND! attempted when no data cannot be performed.

NO DATA is stored in memory.

IN MEMORY!

DATA ITEM Data specified in search Change specification or

NOT FOUND! operation does not exist cancel search.

MEMORY FULL! No more room in memory Delete unnecessary data

ALARM TIME Attempt to set a Schedule Set a different alarm time

ALREADY USED! Keeper alarm time that or change the existing alarm

ALARM TIME Attempt to set a Schedule Set a different alarm time

ALREADY PASSED! Keeper alarm time for a (for a future time/date.)

in memory.

for storage of data. items from memory.

is already used for time to another one.

another entry.

time/date that is already

passed.

SECRET DATA! Alarm for a secret Enter the secret memory

memory area data item is area to view details of the

sounding. alarm.

PASSWORD Attempt to enter the Use the correct password.

MISMATCH! secret memory area

using a password that

does not match the one

preset for the secret area.

TRANSMIT ERROR! Error during data Cancel the data

communications. communications

STOPPED! operation and try again.

DATA ERROR! Data corrupted by strong See page 11 of the

CONSULT THE impact, electrostatic owner's manual.

OWNER'S MANUAL! charge, etc.

SAME TYPE Attempt to store a label Use a different label.

ALREADY USED! that is identical to one

already stored.

— 3 —

Page 6

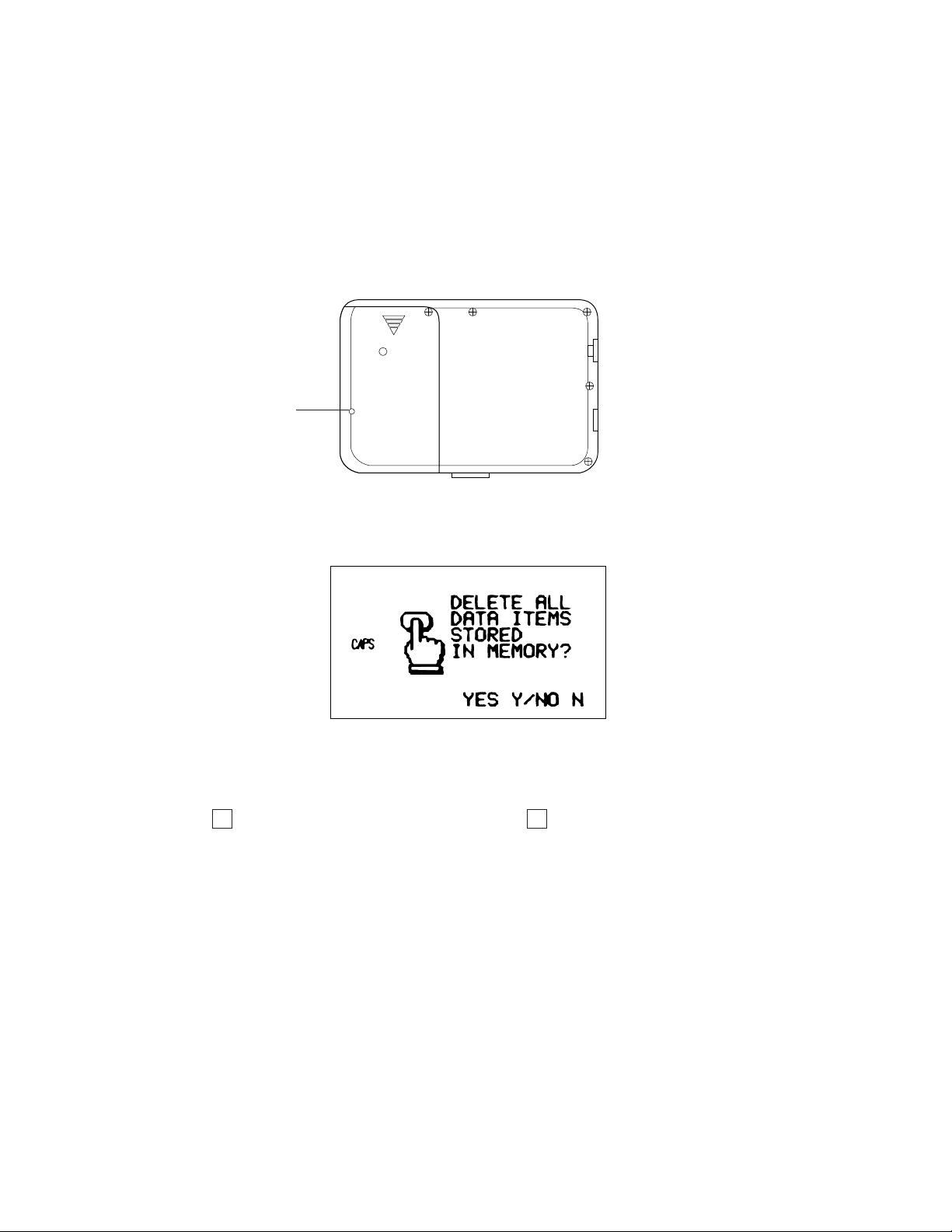

TO RESET THE SF UNIT'S MEMORY

The following procedure erases all data stored in the memory of the SF unit.

Perform the following operation only when you want to delete all data and initialize the settings of the SF

unit.

Remember – you should always keep copies of important data by writing it down, by transferring it to a

personal computer or other SF unit.

To reset the SF Unit's memory

RESET button

RESET

1. Switch on power and press the RESET button with a thin, pointed object.

Warning!

The next step deletes all data stored in the SF unit's memory. Make sure that you really want

to delete the data before you continue!

2. Press Y to reset the memory and delete all data or N to abort the reset operation without

deleting anything.

Following the reset operation described above, the Home Time display appears and the SF unit

settings are initialized as noted below.

Home Time: 12-hour format

JAN/1/1995

AM/12:00 00

World Time: Washington D.C.

Daily Alarm: 12:00 PM

Sound: Schedule alarm → ON

Reminder alarm → ON

Daily alarm → OFF

Key → ON

Character input: CAPS

— 4 —

Page 7

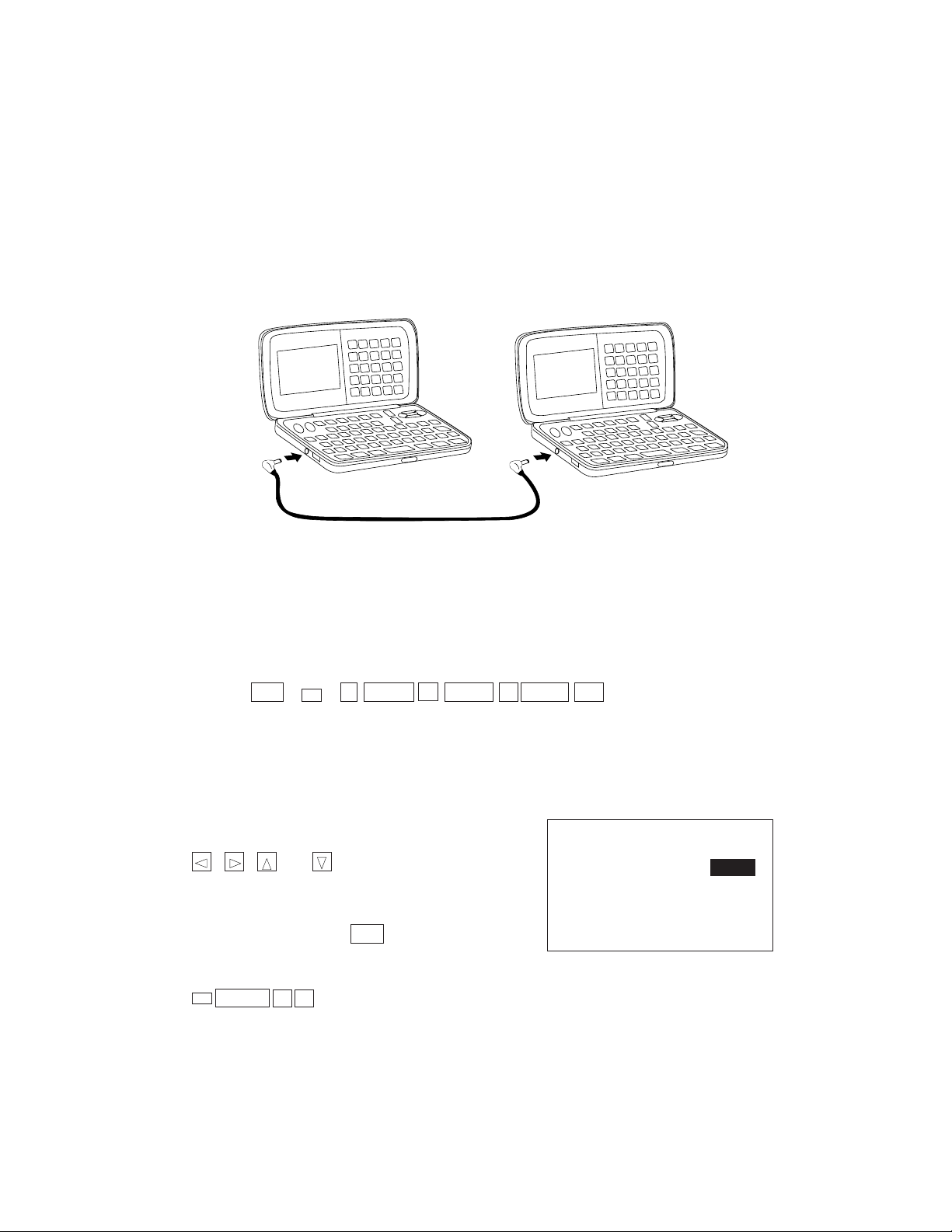

TO SAVE THE DATA TO ANOTHER UNIT

SF-7900 can transfer customers data to another SF-7900 with memory protection only when replacing

the LCD or the outer case.

How to transfer the data

* Before connecting the cable (SB-60 or SB-62), be sure to reset the slave unit to clear all

data.

1) Turn off the power switch and connect the two units using the cable (SB-60 or SB-62) as shown in

the drawing.

2) Turn on the power switch of both units.

3) The slave unit must be set the date of Feb. 3rd, 1901 into the memory under the calculator

mode.

Operation: 1 DATE 2 DATE 3 DATE M+

CLEAR

CAL

ON

If you don't set the date, the "PASSWORD" isn't transferred to the slave unit.

4) Check the hardware parameters, and if the units have another condition, reset as follows.

To change the hardware

parameters, press the

, , and

cursol keys.

PARITY NONE

BIT LENGTH 7

SET UP

To set the hardware

parameters, press the SET

BPS 9600

key.

TEL

FUNC 4 4

— 5 —

Page 8

5) Set up the slave unit.

1 While in the Calendar Display, Telephone Directory, Business Card Library, Memo Mode, or

Schedule Keeper, press the FUNCTION key followed by 4 to select " DATA COMM", and

the following menu appears.

TEL

FUNCTION 4

1 SEND

2 RECEIVE

3 PRINT

4 SET UP

2 Press 2 to select "RECEIVE" and the following display appears to indicate that the slave unit

is ready to receive data.

2

DATA

RECEIVE OK

TO STOP

PRESS [ESC]

6) Set up the customer's unit.

1 While the transmitting unit is in the Calendar Display, Telephone Directory, Business Card

Library, Memo Mode, or Schedule Keeper, press the FUNCTION key followed by 4 to

select "DATA COMM", and the following menu appears.

TEL

FUNCTION 4

1 SEND

2 RECEIVE

3 PRINT

4 SET UP

2 Press 1 to select "SEND" and the following menu appears.

SEND

1

1 ONE ITEM

2 MODE DATA

3 ALL DATA

— 6 —

Page 9

3 Press 3 to select "ALL DATA". The following display appears to confirm if you wish to

proceed.

SEND ALL

3

DATA ITEM ?

SET / ESC

4 Press the SET key to proceed with the data transmission, or press ESC if you wish to

cancel.

SET

NOW SENDING !

TO STOP, PRESS ESC

Data are transmitted in the sequence of Telephone Directory data, Memo data, Reminder data,

Schedule Keeper data and Calendar data.

* The following messages appear on the display of the receiving unit when a problem occurs during

data communications. All data transferred up to display of the message is retained in memory, but

data communication is terminated.

If one of the following error messages appear, press the , , , , ,

CAL

CALENDAR

, keys, to clear the error message. Then, take corrective action and try data

TEL

MEMO

HOME/WORLDSCHEDULE

REMINDER

communication again.

Message Meaning Action

TRANSMIT ERROR! Error during data Cancel the data

STOPPED! communications. communications operation

and try again.

DATA ERROR! Data corrupted by strong See page 9 of the owner's

CONSULT THE impact, electrostatic manual.

OWNER'S MANUAL! charge, etc.

— 7 —

Page 10

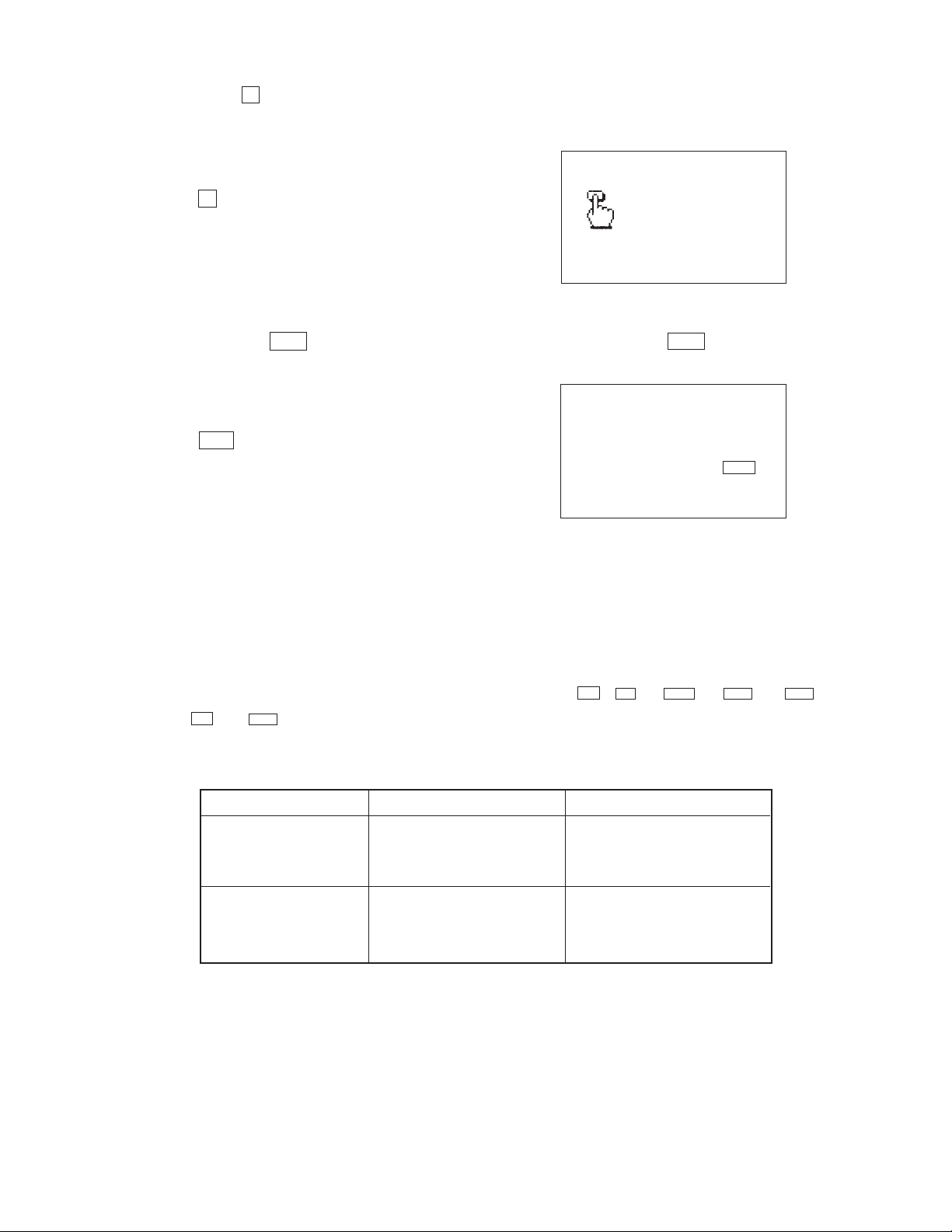

BLOCK DIAGRAM

LCD 96 × 64 dots

CD760-TS

KEYBOARD

PCB-L589-E4

TO KEYBOARD

C0~C63

MSM6585AV

-Z-358B

DATA BUS

CPU

HD62076C03

LSI1

ROM

(Operation Program)

LSI5

S16~S95S0~S15

LCD DRIVER LCD DRIVER

MSM6585AV

-Z-358B

OPEN (OFF)

LOCK (ON)

MAIN SWITCH

LCD DRIVE

VOLTAGES

V1 ~ V5

VDD

GND

PCB-L589-E2

PCB-L522-1(SF-7900E)

or

PCB-L552-1(SF-8900)

RAM

MSM51008AFP-10LL

LSI3, LSI4

SF-7900E: RAM × 1

SF-8900: RAM × 2

Power supply circuit

GATE ARRAY

SSC2571

LSI2

INTERFACE FOR

DATA TRANSMISSION

& DATA RECEPTION

— 8 —

Page 11

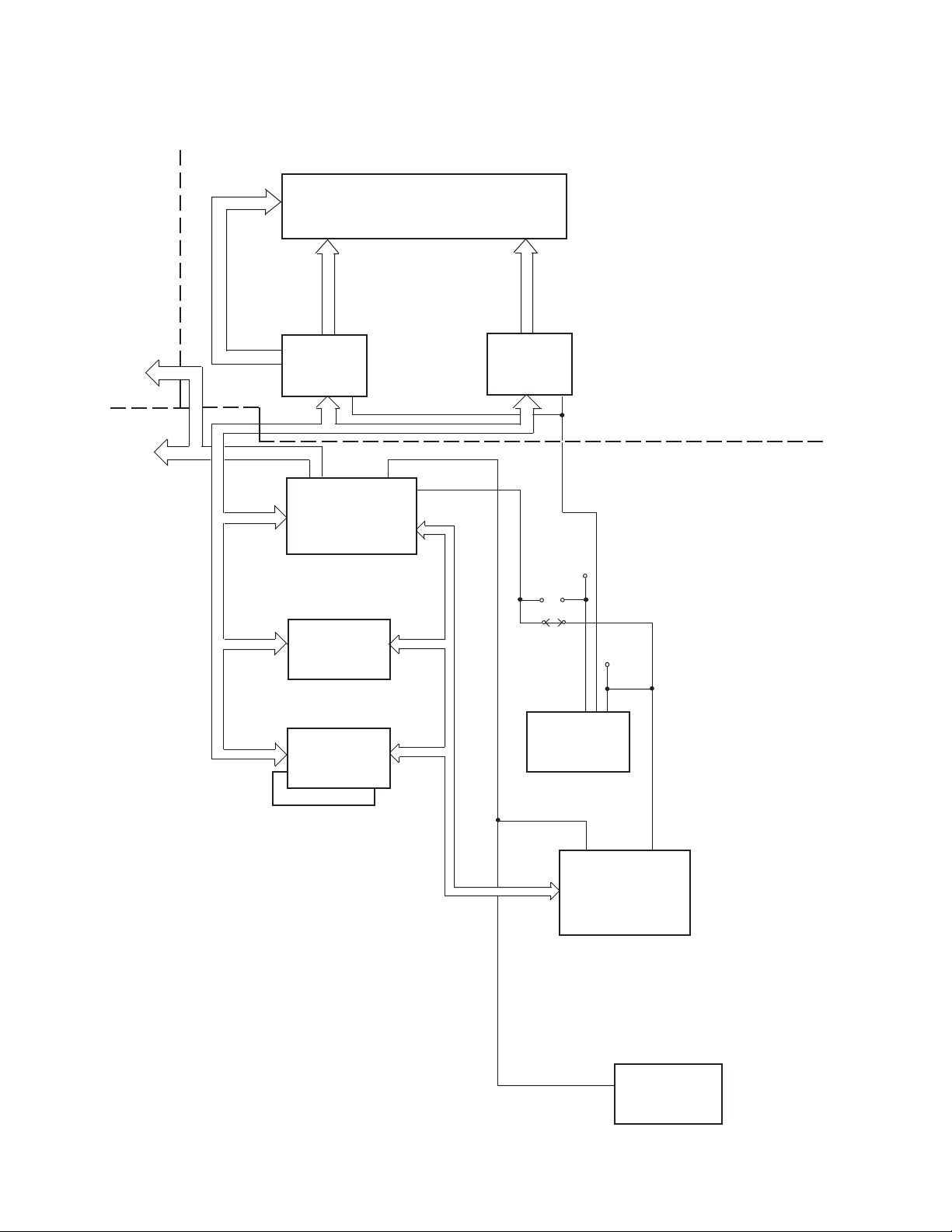

CIRCUIT EXPLANATIONS

System chart

The circuitry operates in the following order:

VDD

1

(Pin41)

Low battery

detector

IC4

2 MHz

OSCOOSCI

8

(Pin40)(Pin45)

INT0

SW

(Pin70)

(Pin36)

11

V1~V5

for LCD

VDD

VDD1

GND

(Pin54)

Power supply

KAC

(Pin53)

"L"

circuit

"H"

9

V2ON

CPU

HD62076C03

KIO

"H"

6

7

ADDRESS BUS

MAIN SWITCH

4

5

"L"

14

(Pin24)

ON

VIN

PDN

(Pin35)

3

"L"

VDD

OFF

ADDRESS

VDD

Gate array

SWO

(Pin62)

2

"L"

OEO

VSS

VOB

MSO

(Pin58)

12

"L"

(Pin24)

10

(Pin28)

(Pin49)

13

"L"

(Pin22)

CEOE GND

ROM

(Operation program)

1. Supply 5V to VDD1 and VDD2.

2. Output "L" from SWO terminal.

3. Output "L" from IC4 and Q5 terminal.

4. Main switch ON.

5. Input "L" to SW terminal.

6. Input "L" from KAC terminal.

7. Push power on button switch.

8. CPU oscillation is generated.

9. Output "H" from V2ON terminal.

10. Output "L" from VOB terminal.

DATA BUS

— 9 —

15

DATA

11. Output all LCD drive voltages.

12. Gate array sends ROM output enable

signal to OE terminal.

13. Gate array sends ROM Chip enable

signal to CE terminal.

14. CPU sends address to ROM.

15. CPU receives data from ROM.

Page 12

Power supply circuit

1) Power supply circuit for CPU, GATE ARRAY and RAMs.

When the main batteries are set, the voltage (9V) is applied to the terminal VDD1 of CPU (LSI1), GATE

ARRAY (LSI2) and RAM (LSI4).

When IC2 receives the voltage, it provides 4V to the GND lines from the terminal OUT (Pin No.1).

2) Main switch

The CPU (LSI1) detects the informations of the Main switch by the terminal SW (Pin No.36) from the

SWO signal of the GATE ARRAY (LSI2).

3) How to turn the display ON.

When pressing "ON" key under the ON side of the Main switch , the CPU (LSI1) generates the signal

to turn the display ON on the terminal V2ON (Pin No.45).

This signal goes to the terminal VIN (Pin No.24) of the GATE ARRAY (LSI2), then the GATE ARRAY

(LSI2) generates "L" level on the terminal VOB (Pin No.28). When the transistor 2SA1179 (Q2) receives "L" level, the transistor 2SC2812 (Q1) will be also turned ON. Then LCD drive voltage V1~V4

will be applied.

4) How to detect the voltage for the main batteries.

When the voltage of the VDD lines becomes +6.6V±0.18V, the terminal OUT (Pin No.1) of the detector

RH5V60BA (IC4) becomes "L" level, then this signal goes to the terminal INTO (Pin No.70) of the CPU

(LSI1) and the terminal PDN (Pin No.35) of the GATE ARRAY (LSI2).

The CPU detects the low battery condition, then the display turns OFF.

— 10 —

Page 13

5) Main switch and power on switch

CPU

HD62076C03

KAC

(Pin54)

KIO

(Pin53)

OSCI

OSCO

4S66F

SW

(Pin36)

"L"

MAIN SWITCH

2 MHz

OFF

ON

VDD

(Pin62)

"L"

from IC4

(Pin35)

PDN

GATE ARRAY

SWO

KON

(Pin26)

"L"

POWER ON SWITCH

"H"

When the main switch is set to on position, SW terminal of CPU receives "L", then KAC terminal will be

"L" to enable the system power on. The KI0 terminal is "H" when VDD is applied to CPU. Therefore,

when pressing the power on switch, CPU will generate a clock pulse (2 MHz) at OSCO terminal for

start up the system.

When the PDN terminal will be receiving "L" level, GATE ARRAY will send "L" signal from KON terminal for cutting the line of power on switch.

6) Power supply for LCD

VDD

(Pin1)

R3

(Pin2)

(Pin3)

"L"

(Pin28) (Pin31)

VOB

(Pin3)

R2

C20

VR1

GND

V1~V4

CPU

HD62076C03

V2ON

(Pin45) (Pin24)

VIN

GATE ARRAY

"H"

When the system is start up, CPU will send "H" signal to VIN terminal of gate array from V2ON terminal. Then, gate array will send "L" signal from VOB terminal to turn ON the transistors Q2 and Q1 for

LCD drive voltages.

— 11 —

Page 14

CPU pin description (HD62076C03)

Pin No. Name In/Out Status Status Description

of OFF of ON

1~14,16,17 A0~A15 Out L Pulse Address Bus line

15,39, 100 VSS I n GND GND GND terminal

24 WE O u t H Pulse Write signal

25 OE Out H Pulse Read signal

2 6 FE Out H Pulse Chip select signal for Gate array

2 7 CS1 Out H H Chip select signal

2 8 CS2 Out H H Chip select signal

29 CS3 Out H Pulse Chip select signal

3 0 E0 Out L Pulse Chip enable signal (Not used)

3 1 E1 Out L H Chip enable signal (Not used)

3 2 E2 Out L H Chip enable signal (Not used)

3 3 E3 Out L H Chip enable signal (Not used)

34 BCON Out H H BCN signal (Not used)

3 5 MDP2 Out H L MDP signal (Not used)

3 6 SW In L L Switch signal (When switches are at ON position)

37 ONMK In H H Battery detection

3 8 TEST In L L TEST terminal (connect to GND)

40,41 OSC O/I In L Pulse Clock input

4 2 VDSC In L H Power input for Clock

43, 91 VDD1 In H H VDD input terminal

4 4 VDD2 I n H H VDD input terminal

45 V2ON Out L H Power on output signal

46~53 KI7~KI0 In H H Key input signal

5 4 KAC O u t L Pulse Power on switch signal output

55~65,67 KC0~KC11 Out H Pulse Key common signal output

66 GND In L L GND terminal

6 8 INT2 In H H Interrupt signal from Gate array

6 9 INT1 In L H Interrupt signal for transmission

7 0 INT0 In H H Interrupt signal for Power down

7 1 BRK In H H VDD input terminal

7 2 P0 Out H H Transmission data output

73 P1 In L H Reception data input

7 4 P 2 In H H Card lock switch input (Not used)

7 5 P3 In L H IC card detection signal input (Not used)

76 P4 Out H Pulse Not used

77 P5 Out H Pulse Not used

7 8 P6 In H H Memory back-up battery detection input (Not used)

7 9 P7 In H H Battery detection input (Not used)

80 H1 Out H H Not used

81 WENL I n L L GND terminal

82 H2 Out H H Not used

83 L1 Out L H Not used

84 L2 Out L L Not used

8 5 DT Out H Pulse DT signal output

8 6 PRO Out L H LCD driver mode selection signal

87 FR O u t L Pulse LCD driver synchronous signal

88 LP Out H Pulse LCD driver latch pulse signal

89 GC Out H Pulse GC signal output

90 DE Out H Pulse LCD driver data latch clock signal

92~99 IO7~IO0 In/Out L Pulse Data bus line

18~23 RA14~19 Out L Pulse Address line (Not used)

— 12 —

Page 15

e

e

e

e

e

e

e

e

Gate array pin descriptions (SSC2571F0A): Used in SF-7900E

Pin No. Name In/Out Description

1 VSS1 In GND terminal

2 OSO Out Clock out

3 OSI In Clock in

4 VL1 In 6V input

5~10 A0~3,A14,15 In Address input

11 FE In Chip select signal from CPU

12 CS1 In Chip select signal from CPU

13 CS2 In Chip select signal from CPU

14 CS3 In Chip select signal from CPU

15 OEI In Output enable signal from CPU

16 VSS(GND) In GND terminal

17 VH1(VCC) In 9V input

18 TXI In Transmission data input from CPU

19 WEI In Write enable signal from CPU

20 GC In GC signal from CPU

21 IO0 In/Out Data bus lin

22 DT In DT signal input

23 IO1 In/Out Data bus lin

24 VIN In Power ON signal from CPU (V2ON)

25 IO2 In/Out Data bus lin

26 KON Out Switch control signal

27 IO3 In/Out Data bus lin

28 VOB Out Inverted signal for VIN

29 IO4 In/Out Data bus lin

30 INT Out Interrupt signal

31 VH2(VCC) In 9V input

32 VL2(VLL) In 6V input

33 VSS(GND) In GND terminal

34 BBC Out Not used

35 PDN In Power down detection input

36 IO5 In/Out Data bus lin

37 RLD Out Not used

38 RA15 Out Address bus output

39 IO6 In/Out Data bus lin

40 RA16 Out Inverted signal for VIN

41 IO7 In/Out Data bus lin

42 RA17 Out Address bus output

43 RA18 Out Address bus output

44 MS3 Out Not used

45 RA19 Out Not used

46 RA20 Out Not used

47 R15 Out Address bus

48 VSS(GND) In GND terminal

49 VH3(VCC) In 9V input

50 VDD1(VLL) In 6V input

51 R16 Out Address bus

52 R17 Out Address bus

53 MSO Out Chip enable signal for ROM

54 MS4 Out Chip select signal for RAM (Not used)

55 MS1 Out Not used

56 MS5 Out Not used

— 13 —

Page 16

Pin No. Name In/Out Description

e

e

e

e

e

e

e

e

57 MS2 Out Not used

58 OEO Out Output enable for ROM

59 BZ1 Out Buzzer signal

60 OTP In Connected to GND

61 BZ2 Out Buzzer signal

62 SWO Out Main switch control signal

63 VH4(VCC) In 9V input

64 TXO Out Transmission data output terminal

Gate array pin descriptions (SSC2571F0B): Used in SF-8900

Pin No. Name In/Out Description

1 VSS1 In GND terminal

2 OSO Out Clock out

3 OSI In Clock in

4 VL1 In 6V input

5~10 A0~3,A14,15 In Address input

11 FE In Chip select signal from CPU

12 CS1 In Chip select signal from CPU

13 CS2 In Chip select signal from CPU

14 CS3 In Chip select signal from CPU

15 OEI In Output enable signal from CPU

16 VSS(GND) In GND terminal

17 VH1(VCC) In 9V input

18 TXI In Transmission data input from CPU

19 WEI In Write enable signal from CPU

20 GC In GC signal from CPU

21 IO0 In/Out Data bus lin

22 DT In DT signal input

23 IO1 In/Out Data bus lin

24 VIN In Power ON signal from CPU (V2ON)

25 IO2 In/Out Data bus lin

26 KON Out Switch control signal

27 IO3 In/Out Data bus lin

28 VOB Out Inverted signal for VIN

29 IO4 In/Out Data bus lin

30 INT Out Interrupt signal

31 VH2(VCC) In 9V input

32 VL2(VLL) In 6V input

33 VSS(GND) In GND terminal

34 BBC Out Not used

35 PDN In Power down detection input

36 IO5 In/Out Data bus lin

37 LRAM Out Connected to 9V

38 CM32 Out Connected to GND

39 IO6 In/Out Data bus lin

40 RA16 Out Inverted signal for VIN

41 IO7 In/Out Data bus lin

42 RA17 Out Address bus output

43 RA18 Out Address bus output

44 MS3 Out Not used

45 RA19 Out Not used

— 14 —

Page 17

Pin No. Name In/Out Description

46 RA20 Out Not used

47 R15 Out Address bus

48 VSS(GND) In GND terminal

49 VH3(VCC) In 9V input

50 VL3 In 6V input

51 CAC Out Address bus

52 MS7 Out Address bus

53 MSO Out Chip enable signal for ROM (Not used)

54 MS4 Out Chip select signal for RAM (Not used)

55 MS1 Out Chip select signal

56 MS5 Out Not used

57 MS2 Out Not used

58 MS6 Out Chip select signal

59 BZ1 Out Buzzer signal

60 OTP In Connected to GND

61 BZ2 Out Buzzer signal

62 SWO Out Main switch control signal

63 VH4(VCC) In 9V input

64 TXO Out Transmission data output terminal

Operation program ROM pin descriptions

Pin No. Name In/Out Status Status Description

of OFF of ON

2~12,23, A0~A17 In L Pulse Address bus line (A0~A14, RA15~RA17)

25~30

13~15, 17~21 O0~O7 Out L Pulse Data bus line (IO0~IO7)

16 GND In L L GND terminal

2 2 CE In H Pulse Chip enable signal from Gate array

2 4 OE In L Pulse Output enable signal from Gate array

31 A1 8 In L Pulse Address line (RA18)

1, 3 2 VPP, VCC In L H VDD terminal

RAM pin descriptions

Pin No. Name In/Out Status Status Description

of OFF of ON

3~12, 23 A0~A15 In L Pulse Address bus line (A0~A15)

25~28, 31

13~15, 17~21 IO0~IO7 Out L Pulse Data bus line (IO0~IO7)

16 GND In L L GND terminal

22 S1 In H Pulse Chip enable signal from Gate array

24 OE In L Pulse Output enable signal from Gate array

29 W In H Pulse Write enable signal from CPU

32 VCC In L H VDD terminal

— 15 —

Page 18

DIAGNOSTIC OPERATION

Main switch

Check pad

SELF TEST PROG.

PRESS SET

QUIT BY OFF

CASIO 1993. 11. 09

MENU TOP SHEET

1 : DISP CHECK

2 : RAM TEST

3 : MEMORY TEST

4 : KEY / BUZZER

5 : INTERFACE

CASIO 1993. 11. 09

MENU DISPLAY

1 : LCD ALIGNING

2 : ALL DOTS ON

3 : ALTERNATIVE

4 : REVERSE

5 : LCD FRAMING

CASIO 1993. 11. 09

1. Diagnostic mode

The diagnostic mode appears when main switch is turned on

while there is a short in the checkpad. After this operation,

the machine will beep and display "SELF-TEST".

The menu appears after pressing SET key. Tests are conducted by selecting the mode from the list on screen. The

each test can be selected by numeral keys.

DISPLAY TEST : LCD display check

RAM TEST : RAM chip check

MEMORY TEST : ROM/Clock check

KEY/BUZZER : Keys and Buzzer check

INTERFACE : Transmission check

To return to the menu display, press DISP CHNG button .

2. Display check

LCD ALIGNING: Lights on dot at corners

ALL DOTS ON : Lights on in all dots (black screen)

ALTERNATIVE : Checker display

REVERSE : Reverse checker display

LCD FRAMING: Lights on dot along the screen edge (frame)

— 16 —

Page 19

3. RAM check

DISP CHNG key :Return to menu

MENU RAM #1

1 : DATE WRITE

2 : DATA READ

3 : PAT. CHANGE

4 :

5 :

CASIO 1993. 11. 09

#1---Test data pattern(00,01,02...)

#2---Test data pattern(FF,FE,FD....)

1) RAM write

The unit will beep after a second.

The menu will be appeared.

RAM WRITING #1

NOW EXECUTING!

DATA WRITE : Write the set pattern to the RAM area

DATA READ : Compare the pattern displayed after # with

the write data of RAM and displays the

results.

PAT. CHANGE : Change the test data pattern.

CASIO 1993. 11. 09

It means RAM write is succeeded.

2) RAM read

Normal end display is;

RAM COMPARE #1

COMPLETE!

CASIO 1993. 11. 09

Error end display is;

RAM COMPARE #1

DATA ERROR!

ADDRESS CORR RAM

XXXX XX XX

CASIO 1993. 11. 09

To escape from this message, press DISP CHNG

key.

— 17 —

Page 20

4. ROM/Clock check

MENU MEMORY

1 : CHECK–SUM

2 : SPECIFIC ADDR

3 : TIME DISPLAY

4 :

CHECK-SUM : Call up check sum and XOR

SPECIFIC ADDR : Call up check sum for certain

TIME DISPLAY : Bring up clock display. The

5 :

CASIO 1993. 11. 09

1) Check sum 3) Time display

CHECKSUM CALC

TP SZ SUM XOR

TIME DISPLAY

1990-03-00

C0 O 256 XXXX XX

10:10 00

XXXXXXXXXXXXXXX

CASIO 1993. 11. 09

2) Specific address

CASIO 1993. 11. 09

Input can be made in the line which

shows "x" using the numeric keys.

Entry of 12 or more digits sets the time

SPECIFIC ADDR

and date. Entry of 4 or 6 digits sets the

daily alarm. The ON key clears cur-

TP SZ SUM XOR

rent entries.

D0 O 256 XXXX XX

values for connected ROM.

address.

present time, date and daily

alarm can be set.

CASIO 1993. 11. 09

5. Key/Buzzer check

MENU KEY / BZR

1 : RANDOM

2 : COMPULSORY

3 : BEEP

4 : ALARM NOTE 1

5 : ALARM NOTE 2

CASIO 1993. 11. 09

RANDOM :

The 'key code' will be displayed.

The 'key code' is numbered incrementally from

left to right with the DATE key as "00", and

HOME/WORLD key as "34" etc. Accordingly,

the left cursor key is "40". To release this test, press

SEARCH key.

COMPULSORY :

Limits the mode mentioned above so that the

keys must be pressed according to the key code.

If an error is made, a buzzer sounds for about 1

second. (A correct entry results in a beep tone.)

BEEP : Key input sound every 1 second

ALARM NOTE 1 : Sound alarm 1

ALARM NOTE 2 : Sound alarm 2

— 18 —

Page 21

Pressing of the SEARCH key in either mode will return to the screen of the menu mode.

Sound can be stopped by pressing any key.

While an alarm is sounding the screen display is as shown left. If an irregularity is found in voltage

of battery while the alarm is sounding, the alarm will stop. After 256 seconds, the alarm will stop

automatically.

6. Interface check

MENU INTERFACE

1: DATA RECEIVE

2: DATA TRANSMIT

3: ASCII CODE

4: LOOP BACK

5:

CASIO 1993.11.09

EXECUTING !

7N9

Parameter

The three charactors that appear on the right side at display

represent the parameter. In the case of the example display,

it indicates 7 BIT, NON PARITY, 9600 BPS. The operation

continues until stopped by pressing the ESC key and then

pressing the ON key for all modes.

DISP CHNG key : Return to menu mode

1 key : Transmission mode. The data of trans-

mission is "H" and it is sent out by the data

of H34 and H38 by the Xon/Xoff control.

2 key : Reception mode. Make sure to set the

parameter to match that of the transitting

side. The data received appears on the

display.

3 key : Output the following ASCII code by Xon/

Xoff control.

!"#*+,-/0123456789:

ABCDEFGHIJKLMNOPQRSTUVWXYZ

abcdefghijklmnopqrstuvwxyz

A line end code is added with each line.

4 key : Loop back test. Short the Tx and Rx

terminals for this test. Transmit and check

from H20 to H7E. When complete, the

message 'CHECK COMPLETE' is displayed.

6 key : Switch the data length 7 bit(7) or 8 bit(8)

7 key : Switch the parity bit : NON(N)—EVEN(E) —NON(N) —ODD(O)

8 key : Switch the transmission speed : 9600(9)—4800(4)—2400(2)—1200(1)

NOTE : As diagnostic program area does not have all ASCII code, to display a reception data, some

charactor will be changed to other charactor. For example, a capital letter will be changed

to small letter.

— 19 —

Page 22

LOOP BACK

LOOP BACK

NOW EXECUTING!

CASIO 1993. 11. 09

COMPLETE!

CASIO 1993. 11. 09

Break display (Broken transmission) Error display

TRANS BREAK!

CASIO 1993. 11. 09

TRANS ERROR!

CASIO 1993. 11. 09

7. Others

1) When power is off after presetting an alarm time, the unit automatically powered on at the alarm

time. However, the display is not reserved in this case.

2) When executing memory sum check, execute the RAM write check before.

3) To release diagnostic mode, press RESET button.

4) The display contrast can be changed by the contrast dial.

— 20 —

Page 23

TROUBLESHOOTING

Before the following solutions will be done, save data if possible.

SYMPTOM CAUSE SOLUTION

No power Battery shortage Replace batteries

Poor soldering of the power supply Resolder

circuit

Defective LSI-1 or LSI-2 Replace it

No display at all or wrong Defective TAB LSI Replace it

display

Defective heat seal Replace it

Defective LCD Replace it

No key input at all Poor soldering LSI-1 or LSI-2 Resolder

Defective LSI-1 or LSI-2 Replace it

— 21 —

Page 24

SCHEMATIC DIAGRAM

Main PCB: SF-7900E

IC4 D2 Q5 R22 R27 R28 R29

S-80766AH —OOO—O

RH5VA60BA

O—O—O—

Note: The following parts are not mounted.

C16, R24

— 23 —

Page 25

Main PCB: SF8900

— 24 —

Page 26

Display PCB

— 25 —

Page 27

Key Matrix

— 26 —

Page 28

Key Matrix (Display side)

— 27 —

Page 29

AT : SF-7900E

IT : SF-8900

PARTS LIST

N Item Code No. Parts Name Specification Quantity M N.R.Yen R

AT IT JT Unit Price

CPU BOARD ASS'Y

C1 2803 6813 Capapcitor CB0011341R3

C4 2845 2289 Chip capacitor MCH215C471KK

C5 2845 1673 Chip capacitor MCH215A221JK

C6,C7 2845 2499 Chip capacitor MCH215A300JK

C8,C9 6411 8550 Chip capacitor CP016F602T3

C10,11,16 2845 1540 Chip capacitor MCH212F104ZK

C81~87

C20 2845 3486 Chip capacitor MCH312F474ZP

D1 2390 0847 Chip diode MA718-(TX)

D2 2305 1028 Chip diode MA157-(TX)

N D2 2390 2338 Diode BC10SB007T4

D3 2390 0364 Shottky diode MA713-(TX)

IC2 2105 2982 IC S-80250AG-GB-T1

IC3 2105 2989 IC S-81220PG-PS-T1

IC4 2105 3794 IC, CMOS S-80766AL-EX-T1

IC4 2105 2247 CMOS-IC RH5VA60BA-T1

IC6 2105 1141 L-MOS IC TC4S66F-TE85R

N IC7 2114 3759 IC ABT7S080007

N IC8 2114 3752 IC ABT7S320008

J1 3501 6538 Jack HSJ1169-012010

LSI1 2011 3843 LSI HD62076C03

LSI2 2011 7350 LSI SSC2571FOA

N LSI2 2011 8393 LSI SSC2571FOB

LSI3, 4 2011 6300 LSI M5M51008AFP-10LL

N LSI5 2011 9478 LSI UPD23C4001EBGW-J14

Q1 2221 0378 Chip transistor 2SC2812-L5, L6-TB

Q2 2200 4417 Transistor 2SA1179M5, M6-TB

Q4 2259 0959 Chip digital transistor DTC114YKT-146

R1,R2 2795 1309 Chip resistor MCR10EZHJ684

R3,R22 2795 0532 Chip resistor MCR10EZHJ105

R6,R7 2792 0217 Chip resistor MCR10EZHJ101

R10 2792 0462 Chip resistor MCR10EZHJ473

R12 2792 1191 Chip resistor MCR10EZHJ182

R13,R31 2792 0470 Chip resistor MCR10EZHJ102

N R14~R18 2775 1939 Chip resistor CC0512D10E8

R19 2792 0209 Chip resistor MCR10EZHJ104

N R23 2775 1946 Chip resistor CC2201D11C3

N R24 2775 1953 Chip resistor CC3902D15E7

R25,R28 2795 0056 Chip resistor MCR10EZHJ000

N VR1 6414 1300 Volume CF100230002

X1 2590 0777 Ceramic oscillator CSAC2.01MGCM001-TC

X2 6510 4550 Crystal BD0063P2509

1 6411 8490 Battery spring (+) EF01DB21109

2 6409 6310 Battery contact plate (-) EF02DB10100

N 3 6414 1280 CPU board ass'y DB21BX3100N*1

N 3 6414 1420 CPU board ass'y DB21CX3100V*1

DISPLAY PCB ASS'Y

LSI6,7 2011 1974 LSI MSM6385AV-Z-358B

N 4 6414 1270 Display PCB ass'y DB21BX3F00U

Notes: N – New parts R – A : Essential

M – Minimum order/supply quantity B : Stock recommended

R – Rank C : Others

Q – Quantity used per unit X : No stock recommended

JT : SF-8900 (B.O.S.S.)

FOB Japan

1 1 20 22 C

1

1120 3 C

1

1120 4 C

1

2220 3 C

2

2 2 20 13 C

2

10 10 20 4 C

9

1 1 20 21 C

1

11 5 47 B

1

0 0 10 34 B

1

11 5 64 B

0

1 1 10 33 B

1

1 1 1 100 B

1

1 1 10 45 B

1

11 5 70 B

0

00 5 65 B

1

11 5 39 B

1

1 1 1 130 A

0

1 1 1 130 A

0

11 5 56 X

1

1 1 1 720 A

1

0 0 1 460 A

1

1 1 1 460 A

0

2 2 1 1270 A

1

1 1 1 630 A

1

1 1 20 12 B

1

1 1 20 15 B

1

1 1 20 12 B

1

2210 9 C

2

2220 3 C

2

2220 3 C

2

1120 3 C

1

1110 9 C

1

2220 3 C

2

5 5 20 13 C

5

1120 3 C

1

1 1 20 13 C

1

1 1 20 13 C

1

0020 3 C

2

1 1 1 720 C

1

11 1 98 B

1

11 5 55 C

1

3 3 20 12 X

3

3 3 20 16 X

3

0 0 1 4,750 B

1

1 1 1 6,000 AA

0

2 2 1 370 A

2

1 1 1 940 J

1

— 29 —

Page 30

FOB Japan

N Item Code No. Parts Name Specification Quantity M N.R.Yen R

AT IT JT Unit Price

COMPONENT

5 3335 5257 LCD CD791-TS

6 6411 6340 Heat seal FX20P320003

7 6512 1280 Haet seal FX200P80074

8 6512 1230 Heat seal FX200P60014

9 6512 1240 Protection tape HGFC0007409

10 6411 8470 Protection tape HGJ00003706

N 11 6414 0980 Sponge cushion FH100030702

12 6411 8450 Keyboard PCB DADB21XX304

N 12 4311 9690 Keyboard PCB DADB21CX105

13 6408 5920 Switch knob ass'y DB2AXX4A00M

14 6412 8240 Battery cover FADDB211014

N 14 6414 1410 Battery cover FADDB211022

15 6412 8250 Battery cover label HGFC0010507

16 6412 8230 Lower case (KB) FABDB211018

N 16 6414 3850 Lower case (KB) FABDB211034

N 16 6414 1400 Lower case (KB) FABDB211042

17 6510 4440 Insulation seal HGFC0001206

18 6512 1080 Nut MD100000602

19 3122 2380 Buzzer EFB-S55C41A8

20 6510 4500 Buzzer tape HGFC0000501

21 6412 8200 Upper case (DIS) FAADB212018

22 6412 8210 Upper case (KB) FAADB211020

N 22 6414 1390 Upper case (KB) FAADB211046

23 6412 8220 Hinge A FC0DB061017

24 6512 1210 Pin FC002870000

25 6512 1220 Pin (L) FC002870018

N 26 6414 1250 Lower case(DIS) FABDB212031

N 26 6414 3860 Lower case(DIS) FABDB212049

N 26 6414 1350 Lower case(DIS) FABDB212057

27 6409 6120 Battery holder ECDB1011108

28 6511 8400 Key contact rubber C LADB0220105

29 6411 8250 Knob FB3DB211007

30 6411 8260 Key contact rubber (61) LADB2110005

31 6411 8270 Key contact rubber (25) LADB2120001

32 6511 7160 RB insert LC120000102

33 6510 4310 Decoration screw MAA80006311

34 6510 4350 Decoration screw MAA80006302

35 6512 1000 Screw MABA0004207

36 6510 5260 Screw MAB10032301

37 6406 8750 Screw MAB20070302

38 6412 8130 Hinge B FC0DB062013

39 6412 8140 Battery insulation EL4F0002111

N 40 6414 1260 Display plate EL5F0008405

N 40 6414 3870 Display plate EL5F0008707

N 40 6414 1370 Display plate EL5F0008600

41 6410 9680 Mask tape HGC00001609

42 6412 8170 Hinge tape HGFC0010604

43 6512 0730 Hinge stopper EF15DB06102

44 6411 8370 Screw MABA0006307

45 6412 8180 Alphabet key set KGDB2110106

N 45 6414 1380 Alphabet key set KGDB2110203*1

46 6412 8190 Numeric key set KCDB2120105

Notes: N – New parts R – A : Essential

M – Minimum order/supply quantity B : Stock recommended

R – Rank C : Others

Q – Quantity used per unit X : No stock recommended

— 30 —

1 1 1 760 A

1

1 1 1 200 A

1

1 1 10 49 B

1

1 1 1 120 A

1

1 1 20 22 B

1

1 1 20 22 B

1

2 2 20 19 C

2

00 5 65 C

1

1 1 1 650 C

0

1 1 10 30 C

1

0 0 20 27 X

1

1 1 20 28 X

0

1 1 20 15 X

1

00 5 95 X

1

0 1 1 110 X

0

1 0 1 110 X

0

4420 6 X

4

4 4 20 13 X

4

1 1 10 36 X

1

1 1 20 17 X

1

11 1 68 X

1

0 0 1 250 X

1

1 1 1 150 X

0

1 1 20 21 X

1

2220 9 X

2

2 2 20 16 X

2

0 0 1 110 X

1

0 1 1 110 X

0

1 0 1 110 X

0

3 3 20 26 X

3

1 1 20 10 C

1

1120 9 X

1

1 1 1 200 C

1

11 5 83 C

1

1 1 20 17 C

1

3320 3 B

3

1120 2 B

1

5520 3 C

5

3320 3 C

3

10 10 20 10 C

10

1 1 20 18 X

1

1 1 20 24 X

1

0 0 1 110 C

1

0 1 1 110 C

0

1 0 1 110 C

0

1120 7 X

1

1 1 20 22 C

1

2 2 20 27 X

2

5520 3 X

5

0 0 1 120 X

1

1 1 1 180 X

0

1 1 1 120 X

1

Page 31

ASSEMBLY VIEW

26

37

41

37

12

44

33

35

37

28

27

4

6

10

8

9

7

17

39

13

18

44

34

J1

16

20

19

14

15

32

VR1

31

46

21

11

38

2

42

35

5

23

25

24

36

1

37

43

3

30

45

37

43

22

40

29

— 31 —

Page 32

MA0400751A

Loading...

Loading...