Page 1

User’s Manual

E-Ray

FlexRay IP-Module

Revision 1.2.5 E-Ray

manual_cover.fm

User’s Manual

Revision 1.2.5

15.12.2006

Robert Bosch GmbH

Automotive Electronics

-1/165-

15.12.2006

Page 2

User’s Manual

Revision 1.2.5 E-Ray

Copyright Notice

Copyright © 2002-2006 Robert Bosch GmbH. All rights reserved. This manual is owned by Robert

Bosch GmbH. No part of this publication may be reproduced, transmitted, or translated, in any form

or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written

permission of Robert Bosch GmbH, or as expressly provided by the license agreement.

Disclaimer

ROBERT BOSCH GMBH, MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED,

WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED

WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

ROBERT BOSCH GMBH, RESERVES THE RIGHT TO MAKE CHANGES WITHOUT

FURTHER NOTICE TO THE PRODUCTS DESCRIBED HEREIN. ROBERT BOSCH GMBH

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF

ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN.

manual_cover.fm

-2/165-

15.12.2006

Page 3

User’s Manual

Revision 1.2.5 E-Ray

Contents

1. About this Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1 Change Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.1 Current Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

1.1.2 Change History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

1.2 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.3 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.4 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.5 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.6 Terms and Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

2. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3. Generic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4. Programmer’s Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

4.2 Customer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

4.3 Special Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.1 Lock Register (LCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.4 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

4.4.1 Error Interrupt Register (EIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

4.4.2 Status Interrupt Register (SIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.4.3 Error Interrupt Line Select (EILS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

4.4.4 Status Interrupt Line Select (SILS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

4.4.5 Error Interrupt Enable Set / Reset (EIES, EIER) . . . . . . . . . . . . . . . . . . . .33

4.4.6 Status Interrupt Enable Set / Reset (SIES, SIER) . . . . . . . . . . . . . . . . . . .34

4.4.7 Interrupt Line Enable (ILE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

manualTOC.fm

4.4.8 Timer 0 Configuration (T0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

4.4.9 Timer 1 Configuration (T1C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.4.10 Stop Watch Register 1 (STPW1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

4.4.11 Stop Watch Register 2 (STPW2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.5 CC Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

4.5.1 SUC Configuration Register 1 (SUCC1) . . . . . . . . . . . . . . . . . . . . . . . . . . .40

4.5.2 SUC Configuration Register 2 (SUCC2) . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.5.3 SUC Configuration Register 3 (SUCC3) . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.5.4 NEM Configuration Register (NEMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

4.5.5 PRT Configuration Register 1 (PRTC1) . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.5.6 PRT Configuration Register 2 (PRTC2) . . . . . . . . . . . . . . . . . . . . . . . . . . .48

-3/165-

15.12.2006

Page 4

User’s Manual

Revision 1.2.5 E-Ray

4.5.7 MHD Configuration Register (MHDC) . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

4.5.8 GTU Configuration Register 1 (GTUC1) . . . . . . . . . . . . . . . . . . . . . . . . . . .50

4.5.9 GTU Configuration Register 2 (GTUC2) . . . . . . . . . . . . . . . . . . . . . . . . . . .50

4.5.10 GTU Configuration Register 3 (GTUC3) . . . . . . . . . . . . . . . . . . . . . . . . . .51

4.5.11 GTU Configuration Register 4 (GTUC4) . . . . . . . . . . . . . . . . . . . . . . . . . .52

4.5.12 GTU Configuration Register 5 (GTUC5) . . . . . . . . . . . . . . . . . . . . . . . . . .53

4.5.13 GTU Configuration Register 6 (GTUC6) . . . . . . . . . . . . . . . . . . . . . . . . . .53

4.5.14 GTU Configuration Register 7 (GTUC7) . . . . . . . . . . . . . . . . . . . . . . . . . .54

4.5.15 GTU Configuration Register 8 (GTUC8) . . . . . . . . . . . . . . . . . . . . . . . . . .54

4.5.16 GTU Configuration Register 9 (GTUC9) . . . . . . . . . . . . . . . . . . . . . . . . . .55

4.5.17 GTU Configuration Register 10 (GTUC10) . . . . . . . . . . . . . . . . . . . . . . . .55

4.5.18 GTU Configuration Register 11 (GTUC11) . . . . . . . . . . . . . . . . . . . . . . . .56

4.6 CC Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4.6.1 CC Status Vector (CCSV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4.6.2 CC Error Vector (CCEV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

4.6.3 Slot Counter Value (SCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

4.6.4 Macrotick and Cycle Counter Value (MTCCV) . . . . . . . . . . . . . . . . . . . . . .61

4.6.5 Rate Correction Value (RCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

4.6.6 Offset Correction Value (OCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

4.6.7 Sync Frame Status (SFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.6.8 Symbol Window and NIT Status (SWNIT) . . . . . . . . . . . . . . . . . . . . . . . . .64

4.6.9 Aggregated Channel Status (ACS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.6.10 Even Sync ID [1…15] (ESIDn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.6.11 Odd Sync ID [1…15] (OSIDn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

4.6.12 Network Management Vector [1…3] (NMVn) . . . . . . . . . . . . . . . . . . . . . .70

4.7 Message Buffer Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.7.1 Message RAM Configuration (MRC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

4.7.2 FIFO Rejection Filter (FRF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.7.3 FIFO Rejection Filter Mask (FRFM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.7.4 FIFO Critical Level (FCL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.8 Message Buffer Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

manualTOC.fm

4.8.1 Message Handler Status (MHDS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

4.8.2 Last Dynamic Transmit Slot (LDTS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

4.8.3 FIFO Status Register (FSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

4.8.4 Message Handler Constraints Flags (MHDF) . . . . . . . . . . . . . . . . . . . . . . .78

4.8.5 Transmission Request 1/2/3/4 (TXRQ1/2/3/4) . . . . . . . . . . . . . . . . . . . . . .80

4.8.6 New Data 1/2/3/4 (NDAT1/2/3/4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

4.8.7 Message Buffer Status Changed 1/2/3/4 (MBSC1/2/3/4) . . . . . . . . . . . . . .82

4.9 Identification Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

4.9.1 Core Release Register (CREL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

4.9.2 Endian Register (ENDN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

-4/165-

15.12.2006

Page 5

User’s Manual

Revision 1.2.5 E-Ray

4.10 Input Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

4.10.1 Write Data Section [1…64] (WRDSn) . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

4.10.2 Write Header Section 1 (WRHS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

4.10.3 Write Header Section 2 (WRHS2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

4.10.4 Write Header Section 3 (WRHS3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

4.10.5 Input Buffer Command Mask (IBCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

4.10.6 Input Buffer Command Request (IBCR) . . . . . . . . . . . . . . . . . . . . . . . . . .88

4.11 Output Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

4.11.1 Read Data Section [1…64] (RDDSn) . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

4.11.2 Read Header Section 1 (RDHS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

4.11.3 Read Header Section 2 (RDHS2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

4.11.4 Read Header Section 3 (RDHS3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

4.11.5 Message Buffer Status (MBS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

4.11.6 Output Buffer Command Mask (OBCM) . . . . . . . . . . . . . . . . . . . . . . . . . .96

4.11.7 Output Buffer Command Request (OBCR) . . . . . . . . . . . . . . . . . . . . . . .97

5. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.1 Communication Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

5.1.1 Static Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

5.1.2 Dynamic Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

5.1.3 Symbol Window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

5.1.4 Network Idle Time (NIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

5.1.5 Configuration of NIT Start and Offset Correction Start . . . . . . . . . . . . . . .100

5.2 Communication Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

5.2.1 Time-triggered Distributed (TT-D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

5.3 Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

5.3.1 Global Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

5.3.2 Local Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

5.3.3 Synchronization Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

5.3.3.1 Offset (phase) Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.3.3.2 Rate (frequency) Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

manualTOC.fm

5.3.3.3 Sync Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.3.4 External Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

5.4 Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

5.4.1 Clock Correction Failed Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

5.4.2 Passive to Active Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

5.4.3 HALT Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

5.4.4 FREEZE Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

5.5 Communication Controller States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

5.5.1 Communication Controller State Diagram . . . . . . . . . . . . . . . . . . . . . . . .106

5.5.2 DEFAULT_CONFIG State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

-5/165-

15.12.2006

Page 6

User’s Manual

Revision 1.2.5 E-Ray

5.5.3 CONFIG State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

5.5.4 MONITOR_MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

5.5.5 READY State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

5.5.6 WAKEUP State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

5.5.6.1 Host activities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

5.5.6.2 Wakeup pattern (WUP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.5.7 STARTUP State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

5.5.7.1 Coldstart Inhibit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

5.5.7.2 Startup Timeouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

5.5.7.3 Path of leading Coldstart Node (initiating coldstart) . . . . . . . . . . . . . . . . . 117

5.5.7.4 Path of following Coldstart Node (responding to leading Coldstart Node) 118

5.5.7.5 Path of Non-coldstart Node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

5.5.8 NORMAL_ACTIVE State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.5.9 NORMAL_PASSIVE State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.5.10 HALT State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

5.6 Network Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

5.7 Filtering and Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.7.1 Slot Counter Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

5.7.2 Cycle Counter Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

5.7.3 Channel ID Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.7.4 FIFO Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.8 Transmit Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

5.8.1 Static Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

5.8.2 Dynamic Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

5.8.3 Transmit Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

5.8.4 Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

5.8.5 Null Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

5.9 Receive Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

5.9.1 Dedicated Receive Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

5.9.2 Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

5.9.3 Null Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

5.10 FIFO Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

manualTOC.fm

5.10.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

5.10.2 Configuration of the FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.10.3 Access to the FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.11 Message Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

5.11.1 Reconfiguration of Message Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . .131

5.11.2 Host access to Message RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

5.11.2.1 Data Transfer from Input Buffer to Message RAM . . . . . . . . . . . . . . . . . 134

5.11.2.2 Data Transfer from Message RAM to Output Buffer . . . . . . . . . . . . . . . 136

5.11.3 FlexRay Protocol Controller access to Message RAM . . . . . . . . . . . . . .139

5.12 Message RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

-6/165-

15.12.2006

Page 7

User’s Manual

Revision 1.2.5 E-Ray

5.12.1 Header Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

5.12.2 Data Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

5.12.3 Parity Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

5.13 Module Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

6. Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.1 Register Bit Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

6.2 Assignment of FlexRay Configuration Parameters . . . . . . . . . . . . . . . . . . . . .162

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

manualTOC.fm

-7/165-

15.12.2006

Page 8

User’s Manual

Revision 1.2.5 E-Ray

1. About this Document

1.1 Change Control

1.1.1 Current Status

Revision 1.2.5

1.1.2 Change History

Issue Date By Change

Revision 1.0 29.10.04 C. Horst First complete revision

Revision 1.0.1 16.11.04 C. Horst Message Buffer Status bits PLE, MLST, ES

replaced by bits ESA, ESB, MLST

Revision 1.0.2 28.01.05 C. Horst IBCR, IBCM, OBCR, OBCM: addresses changed

MHDC2: register removed

MHDC1: renamed to MHDC

Message buffer 0 dedicated to hold key slot ID

SFS: description updated

ESIDn, OSIDn: description updated

EIR: bit SCE removed

EILS: bit SCEL removed

EIES, EIER: bit SCEE removed

Revision 1.1 29.04.05 C. Horst State DEFAULT_CONFIG added to POC

working CCSV: assignment of states to POCS[5:0] changed:

POCS[5:0] = 00 0000 = DEFAULT_CONFIG

POCS[5:0] = 00 1111 = CONFIG

CCSV: bit DCREQ removed

SIR: bit MBSI added

SILS: bit MBSIL added

SIES, SIER: bit MBSIE added

Register BGSC removed

EIR: bits SMEB, SMEA removed

EILS: bits SMEBL, SMEAL removed

EIES, EIER: bits SMEBE, SMEAE removed

Registers TXRQ3, TXRQ4, NDAT3, NDAT4,

MBSC3, MBSC4 added

manual_about.fm

Bus guardian related pins eray_arm, eray_bgt,

eray_mt, eray_bge1, and eray_bge2 have no function

PRTC1: Configuration parameter CASM[6:0] added

WRHS1: Bit NME changed to PPIT

RDHS1: Bit NME changed to PPIT

Pin eray_scanmode for scan mode control added

Revision 1.1 04.08.05 C. Horst EIR: Flags CCL, EFA, IIBA, IOBA, TABA,

TABB added

SIR: Flag SDS added

EILS: Control bits CCLL, EFAL, IIBAL, IOBAL,

TABAL, TABBL added

SILS: Control bit SDSL added

-8/165-

15.12.2006

Page 9

User’s Manual

Revision 1.2.5 E-Ray

EIES: Control bits CCLE, EFAE, IIBAE, IOBAE,

TABAE, TABBE added

EIER: Control bits CCLE, EFAE, IIBAE, IOBAE,

TABAE, TABBE added

SIES: Control bit SDSE added

SIER: Control bit SDSE added

SUCC2: LT[20:0] range modified

PRTC1: TSST[3:0] range modified, SPP[1:0] added,

configuration of BRP[1:0] for 1.25 MBit/s removed

PRTC2: RXL[5:0] range modified

MHDC: SLT[12:0] range modified

GTUC1: UT[19:0] range modified

GTUC2: MPC[13:0] range modified

GTUC3: Configuration parameterMTIO[5:0] replaced

by MIOA[6:0] and MIOB[6:0]

GTUC4: NIT[13:0] and OCS[13:0] range modified

GTUC5: DEC[7:0] range modified

GTUC7: SSL[9:0] range modified

GTUC8: NMS[12:0] range modified

GTUC9: APO[5:0] and DSI[1:0] range modified

GTUC10: MOC[13:0] range modified

GTUC11: Configuration parameter ECC[1:0] replaced

by EOCC[1:0] and ERCC[1:0]

OCV: OCV[18:0] range modified

SCV: SCCA[10:0], SCCB[10:0] range modified

ACS: Flags can only be reset

MRC: Configuration bits SEC[1:0] added

Register LDTS added

Bus guardian related pins eray_arm, eray_bgt,

eray_mt, eray_bge1, and eray_bge2 removed from

physical layer interface

Chapter 6. Restrictions removed. Description of timing

requirements for data transfers between Message RAM

and IBF / OBF moved to "Addendum to E-Ray

FlexRay IP-Module Specification Revision 1.1"

Revision 1.2 09.12.05 C. Horst Section 3.2 renamed from "Interrupt Flag Interface" to

"Internal Signal and Flag Interface"

manual_about.fm

With this revision it is possible to use message buffer 1

for sync frame transmission in addition to message

buffer 0 if sync frames should have different payloads

on channel A and B

EIR: Handling of bits PERR and RFO same as for

other bits, bit MHF added

SIR: Bit RFF renamed to RFCL, handling of bits

RFNE, RFCL same as for other bits

EILS: Bit MHFL added

SILS: Bit RFFL renamed to RFCLL

EIES, EIER: Bit MHFE added

SIES, SIER: Bit RFFE renamed to RFCLE

-9/165-

15.12.2006

Page 10

User’s Manual

Revision 1.2.5 E-Ray

Register STPW renamed to STPW1

STPW2: Register added

CCSV: Bits PSL[5:0] added

SWNIT: Bits MTSA, MTSB added

MRC: Bit SPLM added

FCL: Register added

FSR: Register added

MHDF: Register added

MBSC1/2/3/4: Naming of bits changed from MBS to

MBC to distinguish between message buffer status flag

(MBC) and message buffer status register (MBS)

CREL: Register added

ENDN: Register added

Message buffers in Message RAM:

Header 2 and 3updated from received dataframes only

MBS: Bits FTA, FTB, CCS[5:0], RCIS, SFIS, SYNS,

NFIS, PPIS, RESS added

Revision 1.2.1 17.03.06 C. Horst All changes to previous release are described in

detail in [5].

Revision 1.2.2 19.05.06 C. Horst All changes to previous release are described in

detail in [6].

Revision 1.2.3 15.08.06 C. Horst All changes to previous release are described in

detail in [7].

Revision 1.2.4 Not published.

Revision 1.2.5 15.12.06 C. Horst All changes to previous release are described in

detail in [8], [9].

manual_about.fm

-10/165-

15.12.2006

Page 11

User’s Manual

Revision 1.2.5 E-Ray

1.2 Conventions

The following conventions are used within this document:

Times bold Names of bits and signals

CAPITALS POC states and CHI commands

1.3 Definitions

FlexRay Frame: Header Segment + Payload Segment

Message Buffer: Header Section + Data Section

Message RAM: Header Partition + Data Partition

Data Frame: FlexRay frame that is not a null frame

1.4 Scope

This document describes the E-Ray FlexRay IP-module and its features from the application programmer’s point of view. All information necessary to integrate the E-Ray module into an user-defined

ASIC is located in the Module Integration Guide. Information about a specific Customer CPU Interface can be found in the respective Customer CPU Interface Specification document.

1.5 References

This document refers to the following E-Ray release:

Revision 1.0.1

This document refers to the following documents:

Ref Author(s) Title

[1] FlexRay Group FlexRay Communication System Protocol Specification v2.1 (05/05/12)

[2] FlexRay Group FlexRay Communication System Protocol Specification v2.1 Revision A

Errata Sheet Version 1 (06/03/29)

[3] FlexRay Group FlexRay Data Link Layer Conformance Test Specification v2.1 (06/03/27)

[4] AE/EIP Addendum to E-Ray FlexRay IP-Module Specification Revision 1.2.2

[5] AE/EIP Changes E-Ray FlexRay IP-Module Specification v1.2 to v1.2.1

[6] AE/EIP Changes E-Ray FlexRay IP-Module Specification v1.2.1 to v1.2.2

manual_about.fm

[7] AE/EIP Changes E-Ray FlexRay IP-Module Specification v1.2.2 to v1.2.3

[8] AE/EIP Changes E-Ray FlexRay IP-Module Specification v1.2.3 to v1.2.4

[9] AE/EIP Changes E-Ray FlexRay IP-Module Specification v1.2.4 to v1.2.5

-11/165-

15.12.2006

Page 12

User’s Manual

1.6 Terms and Abbreviations

This document uses the following terms and abbreviations:

Term Meaning

AP Action Point

BD Bus Driver

BSS Byte Start Sequence

CAS Collision Avoidance Symbol

CC Communication Controller

CHI Controller Host Interface

CIF Customer Interface Block

CRC Cyclic Redundancy Check

FES Frame End Sequence

FSS Frame Start Sequence

Revision 1.2.5 E-Ray

FIFO First In First Out (message buffer structure)

FSM Finite State Machine

FSP Frame and Symbol Processing Block

FTM Fault Tolerant Midpoint

GIF Generic Interface Block

GTU Global Time Unit Block

IBF Input Buffer

INT Interrupt Control Block

MHD Message Handler Block

MT Macrotick

MTS Media Access Test Symbol

NCT Network Communication Time

NEM Network Management Block

NIT Network Idle Time

manual_about.fm

NM Network Management

OBF Output Buffer

POC Protocol Operation Control

PRT Protocol Controller Block

SDL Specification and Description Language

SUC System Universal Control Block

TBF Transient Buffer

TDMA Time Division Multiple Access (media access method)

-12/165-

15.12.2006

Page 13

User’s Manual

TSS Transmission Start Sequence

TT-D Time Triggered Distributed Synchronization

µT Microtick

WUP Wakeup Pattern

WUS Wakeup Symbol

Revision 1.2.5 E-Ray

manual_about.fm

-13/165-

15.12.2006

Page 14

User’s Manual

Revision 1.2.5 E-Ray

2. Overview

The E-Ray module is a FlexRay IP-module that can be integrated as stand-alone device or as part of

an ASIC. It is described in VHDL on RTL level, prepared for synthesis. The E-Ray IP-module performs communication according to the FlexRay protocolspecification v2.1. With maximum specified

sample clock the bitrate is 10 MBit/s. Additional bus driver (BD) hardware is required for connection

to the physical layer.

For communication on a FlexRay network, individual message buffers with up to 254 data bytes are

configurable. The message storage consists of a single-ported Message RAM that holds up to 128

message buffers. All functions concerning the handling of messages are implemented in the Message

Handler. Those functions are the acceptance filtering, the transfer of messages between the two

FlexRay Channel Protocol Controllers and the Message RAM, maintaining the transmissionschedule

as well as providing message status information.

The register set of the E-Ray IP-module can be accessed directlyby an external Host via the module’s

Host interface. These registers are used to control/configure/monitor the FlexRay Channel Protocol

Controllers, Message Handler, Global Time Unit, System Universal Control, Frame and Symbol

Processing, Network Management, Interrupt Control, and to access the Message RAM via Input /

Output Buffer.

The E-Ray IP-module can be connected to a wide range of customer-specific Host CPUs via its

8/16/32-bit Generic CPU Interface.

The E-Ray IP-module supports the following features:

• Conformance with FlexRay protocol specification v2.1

• Data rates of up to 10 Mbit/s on each channel

• Up to 128 message buffers configurable

• 8 Kbyte of Message RAM for storage of e.g. 128 message buffers with max. 48 byte data section

or up to 30 message buffers with 254 byte data section

• Configuration of message buffers with different payload lengths possible

• One configurable receive FIFO

• Each message buffer can be configured as receive buffer, as transmit buffer

or as part of the receive FIFO

• Host access to message buffers via Input and Output Buffer

Input Buffer: Holds message to be transferred to the Message RAM

manual_overview.fm

Output Buffer: Holds message read from the Message RAM

• Filtering for slot counter, cycle counter, and channel

• Maskable module interrupts

• Network Management supported

• 8/16/32-bit Generic CPU Interface, connectable to a wide range of customer-specific Host CPUs

-14/165-

15.12.2006

Page 15

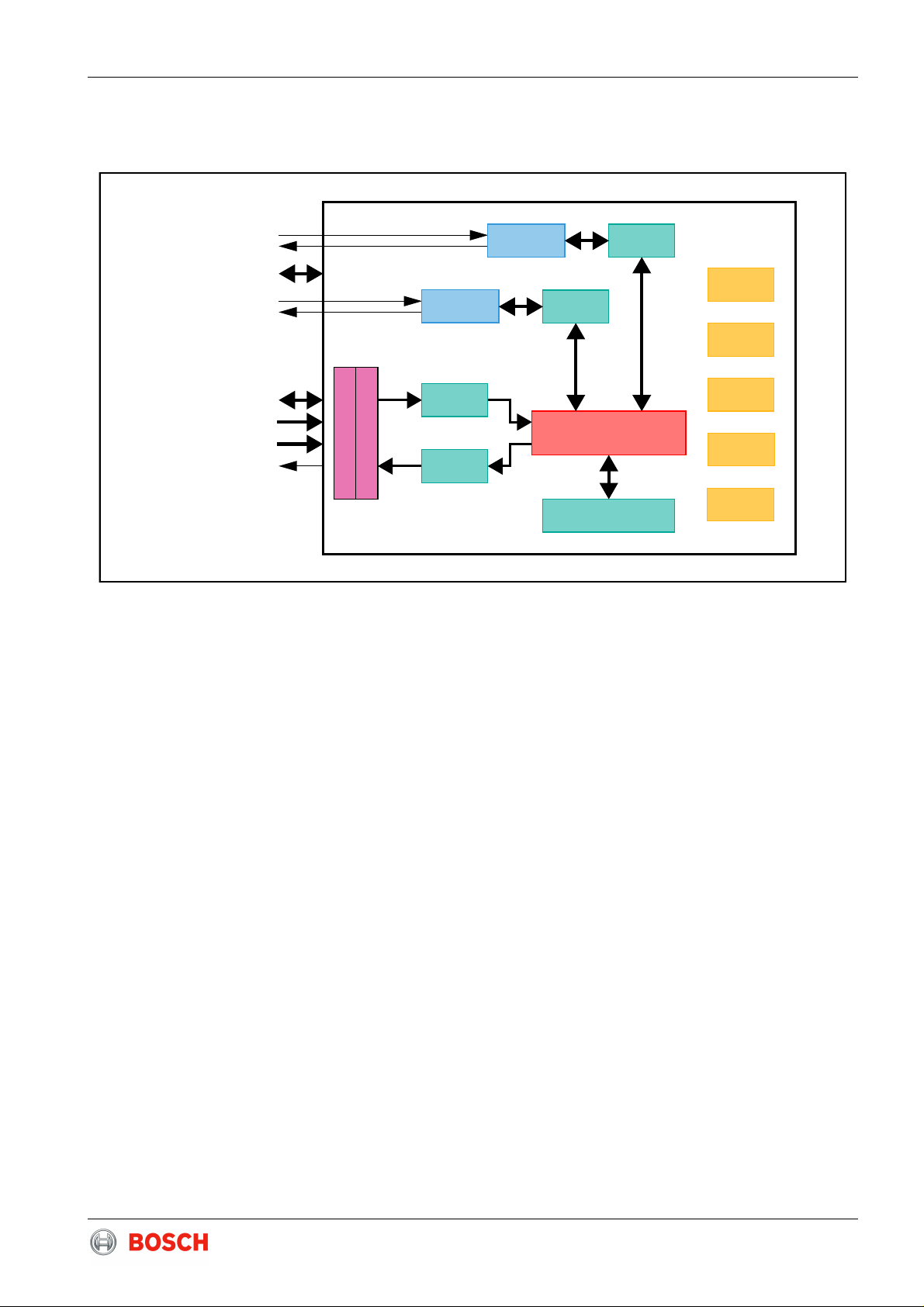

2.1 Block Diagram

User’s Manual

Revision 1.2.5 E-Ray

Rx_A

Physical

Layer

Host

CPU

Figure 1: E-Ray block diagram

Tx_A

Control

Rx_B

Tx_B

Data

Addr

Control

Interrupt

PRT B

IBF

OBF

Generic CPU IF

Customer CPU IF

PRT A

TBF B

Message Handler

Message RAM

TBF A

GTU

SUC

FSP

NEM

INT

Customer CPU Interface (CIF)

Connects a customer specific Host CPU to the E-Ray IP-module via the Generic CPU Interface.

Generic CPU Interface (GIF)

The E-Ray IP-module is provided with an 8/16/32-bit Generic CPU Interface prepared for the connection to a wide range of customer-specific Host CPUs. Configuration registers, status registers, and

interrupt registers are attached to the respective blocks and can be accesssed via the Generic CPU Interface.

Input Buffer (IBF)

For write access to the message buffers configured in the Message RAM, the Host can write the header and data section for a specific message buffer to the Input Buffer. The Message Handler then transfers the data from the Input Buffer to the selected message buffer in the Message RAM.

manual_overview.fm

Output Buffer (OBF)

For read access to a message buffer configured in the Message RAM the Message Handler transfers

the selected message buffer to the Output Buffer. After the transfer has completed, the Host can read

the header and data section of the transferred message buffer from the Output Buffer.

Message Handler (MHD)

The E-Ray Message Handler controls data transfers between the following components:

• Input / Output Buffer and Message RAM

• Transient Buffer RAMs of the two FlexRay Protocol Controllers and Message RAM

-15/165-

15.12.2006

Page 16

User’s Manual

Revision 1.2.5 E-Ray

Message RAM (MRAM)

The Message RAM consists of a single-ported RAM that stores up to 128 FlexRay message buffers

together with the related configuration data (header and data partition).

Transient Buffer RAM (TBF A/B)

Stores the data section of two complete messages.

FlexRay Channel Protocol Controller (PRT A/B)

The FlexRay Channel Protocol Controllers consist of shift register and FlexRay protocol FSM. They

are connected to the Transient Buffer RAMs for intermediatemessage storage and to thephysical layer via bus driver BD.

They perform the following functionality:

• Control and check of bit timing

• Reception / transmission of FlexRay frames and symbols

• Check of header CRC

• Generation / check of frame CRC

• Interfacing to bus driver

The FlexRay Channel Protocol Controllers have interfaces to:

• Physical Layer (bus driver)

• Transient Buffer RAM

• Message Handler

• Global Time Unit

• System Universal Control

• Frame and Symbol Processing

• Network Management

• Interrupt Control

Global Time Unit (GTU)

The Global Time Unit performs the following functions:

• Generation of microtick

• Generation of macrotick

• Fault tolerant clock synchronization by FTM algorithm

manual_overview.fm

- rate correction

- offset correction

• Cycle counter

• Timing control of static segment

• Timing control of dynamic segment (minislotting)

• Support of external clock correction

-16/165-

15.12.2006

Page 17

User’s Manual

System Universal Control (SUC)

The System Universal Control controls the following functions:

• Configuration

• Wakeup

• Startup

• Normal Operation

• Passive Operation

• Monitor Mode

Frame and Symbol Processing (FSP)

The Frame and Symbol Processing controls the following functions:

• Checks the correct timing of frames and symbols

• Tests the syntactical and semantical correctness of received frames

• Sets the slot status flags

Network Management (NEM)

Revision 1.2.5 E-Ray

Handles the network management vector.

Interrupt Control (INT)

The Interrupt Controller performs the following functions:

• Provides error and status interrupt flags

• Enable / disable interrupt sources

• Assignment of interrupt sources to one of the two module interrupt lines

• Enable / disable module interrupt lines

• Manages the two interrupt timers

• Stop watch time capturing

manual_overview.fm

-17/165-

15.12.2006

Page 18

User’s Manual

Revision 1.2.5 E-Ray

3. Generic Interface

The Generic Interface encapsulates the synthesizable code of the E-Ray design (E-Ray core).All customer specific components like Customer CPU Interfaces and RAM blocks are connected to the Generic Interface.

The Generic CPU Interface connects the E-Ray module to a customer specific Host CPU via the Customer CPU Interface. It supports 8/16/32-bit access modes.

manual_generic_if.fm

-18/165-

15.12.2006

Page 19

User’s Manual

Revision 1.2.5 E-Ray

4. Programmer’s Model

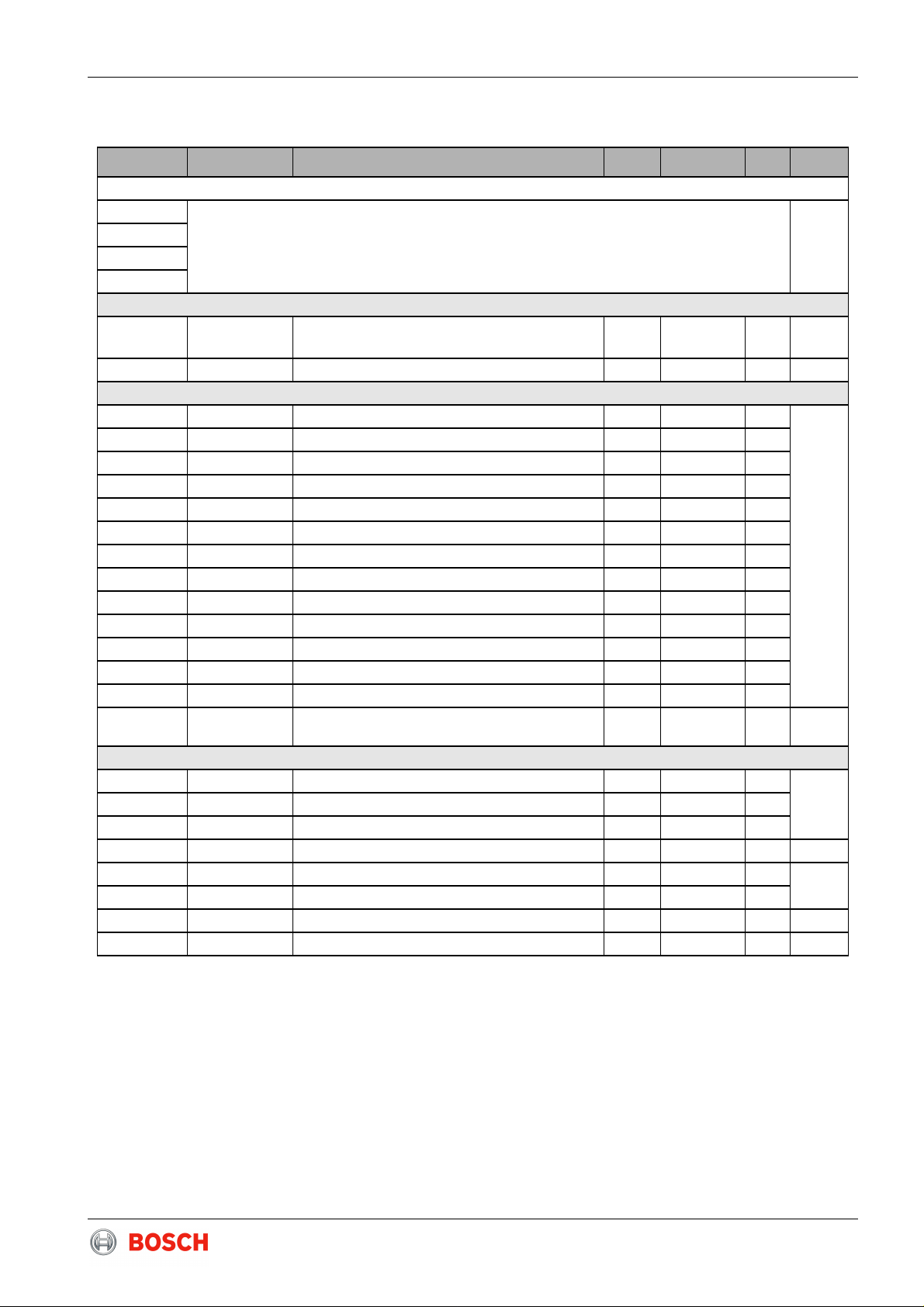

4.1 Register Map

The E-Ray module allocates an address space of 2 Kbytes (0x0000 to 0x07FF). The registers are organized as 32-bit registers. 8/16-bit accesses are also supported. Host access to the Message RAM is

done via the Input and Output Buffers. They buffer data to be transferred to and from the Message

RAM under control of the Message Handler, avoiding conflicts between Host accesses and message

reception / transmission. Addresses 0x0000 to 0x000F are reserved for customer specific purposes.

All functions related to these addresses are located in the Customer CPU Interface.

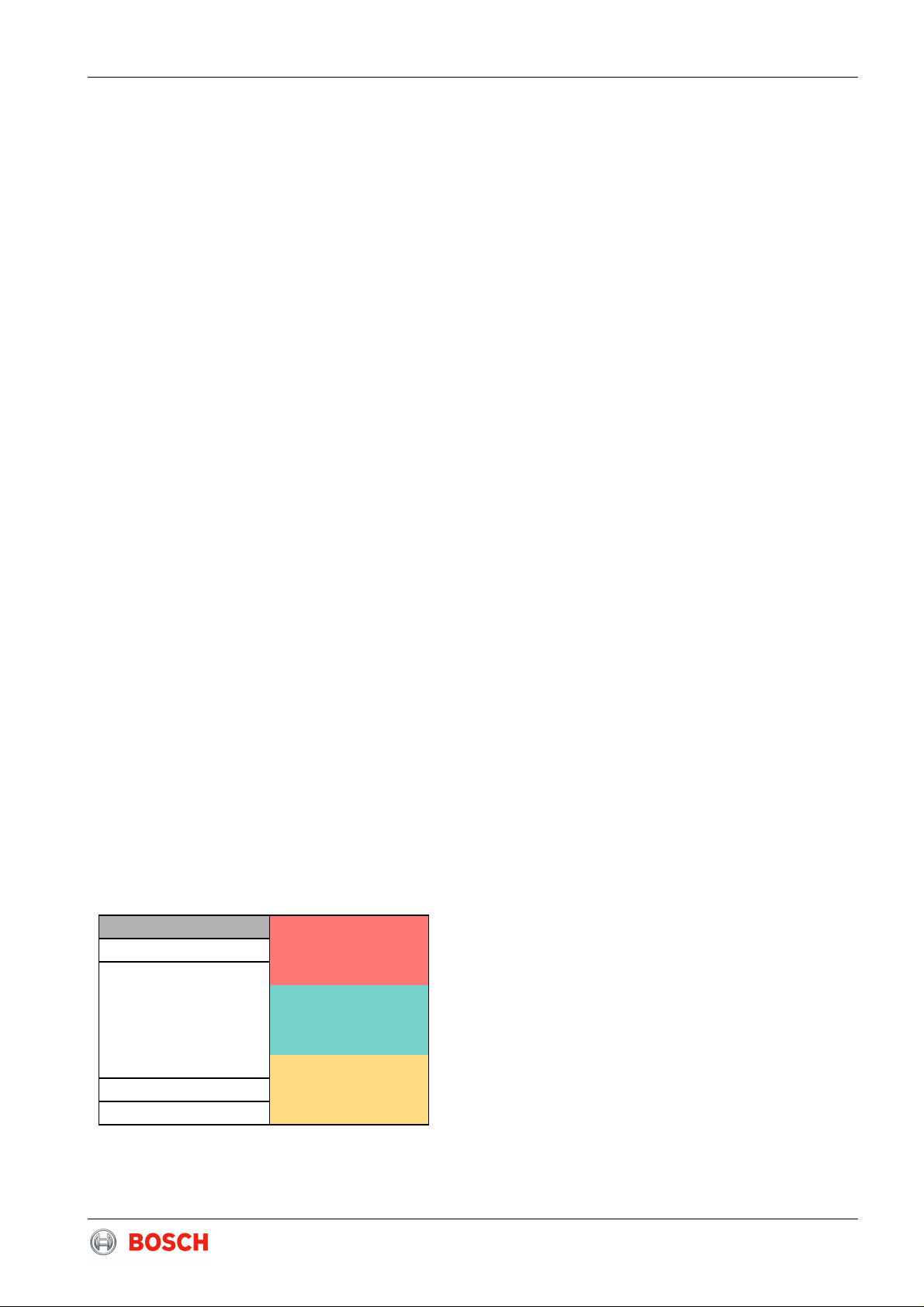

The assignment of the message buffers is done according to the scheme shown in Table 1 below. The

number N of available message buffers depends on the payload length of the configured message

buffers. The maximum number of message buffers is 128. The maximum payload length supported is

254 bytes.

The message buffers are separated into three consecutive groups:

• Static Buffers - Transmit / receive buffers assigned to static segment

• Static + Dynamic Buffers - Transmit / receive buffers assigned to static or dynamic segment

• FIFO - Receive FIFO

The message buffer separation configuration can be changed only in DEFAULT_CONFIG or CON-

FIG state only by programming register MRC (see 4.7.1 Message RAM Configuration (MRC)).

The first group starts with message buffer0 andconsists of static message buffers only. Message buff-

er 0 is dedicated to hold the startup / sync frame or the single slot frame, if the node transmits one, as

configured by SUCC1.TXST, SUCC1.TXSY, and SUCC1.TSM. In addition, message buffer 1 may

be used for sync frame transmission in case that sync frames or single-slot frames should have different payloads on the two channels. In this case bit MRC.SPLM has to be programmed to ’1’ and message buffers 0 and 1 have to be configured with the key slot ID and can be (re)configured in

DEFAULT_CONFIG or CONFIG state only.

The second group consists of message buffers assigned to the static or to the dynamic segment. Message buffers belonging to this group may be reconfigured during run time from dynamic to static or

vice versa depending on the state of MRC.SEC[1:0].

The message buffers belonging to the third group are concatenated to a single receive FIFO.

Message Buffer 0 ⇓ Static Buffers

manual_programmers_model.fm

Message Buffer 1

⇓ Static + Dynamic ⇐ FDB

…

Message Buffer N-1

Message Buffer N ⇐ LCB

Table 1: Assignment of message buffers

Buffers

⇓ FIFO ⇐ FFB

-19/165-

15.12.2006

Page 20

User’s Manual

Revision 1.2.5 E-Ray

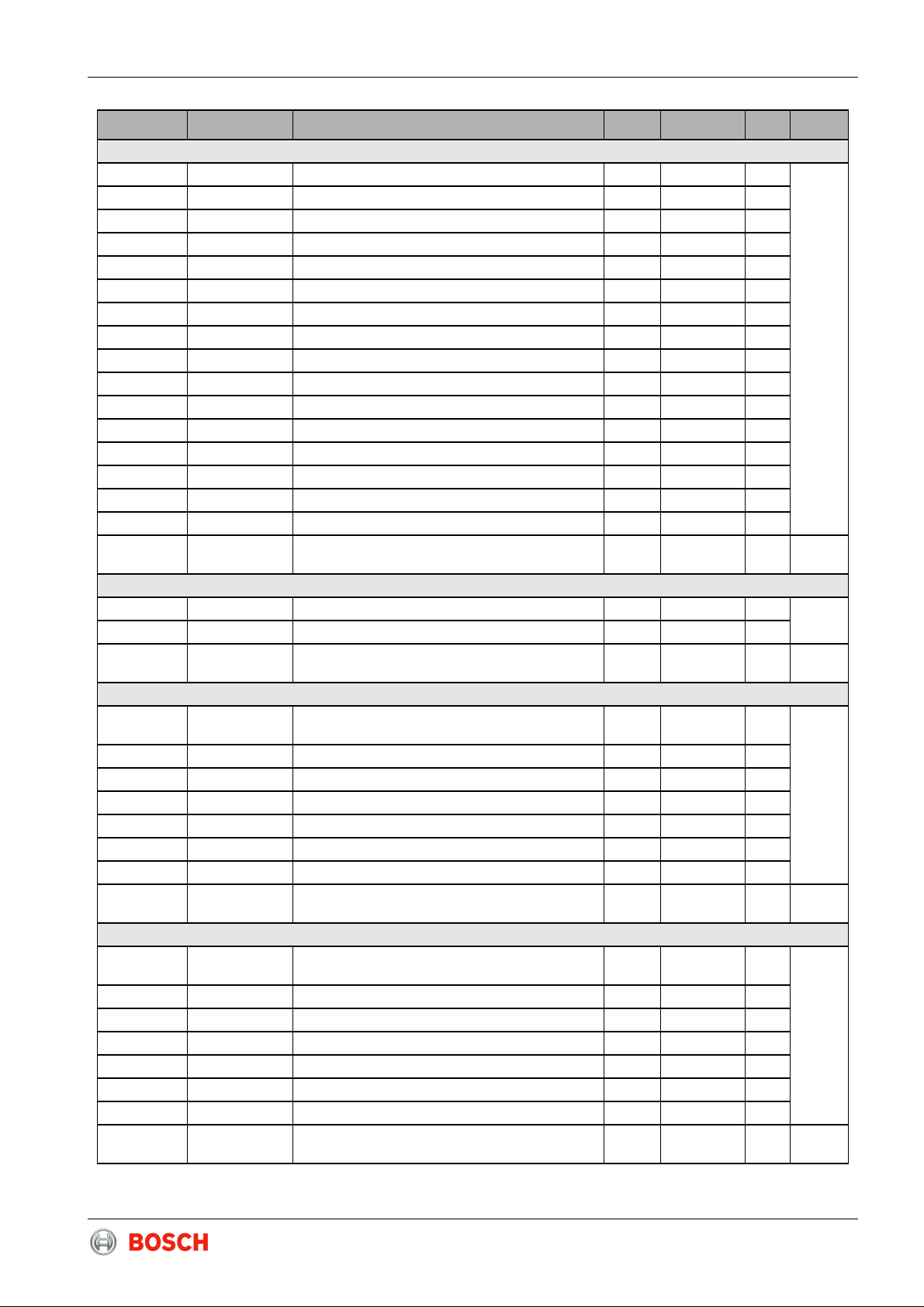

Address Symbol Name

Customer Registers

0x0000

0x0004

0x0008

see Customer CPU Interface Specification CIF

0x000C

Special Registers

0x0010-

0x0018

reserved (3)

0x001C LCK Lock Register 24

Interrupt Registers

0x0020 EIR Error Interrupt Register 25

0x0024 SIR Status Interrupt Register 28

0x0028 EILS Error Interrupt Line Select 31

0x002C SILS Status Interrupt Line Select 32

0x0030 EIES Error Interrupt Enable Set 33

0x0034 EIER Error Interrupt Enable Reset 33

0x0038 SIES Status Interrupt Enable Set 34

0x003C SIER Status Interrupt Enable Reset 34

0x0040 ILE Interrupt Line Enable 35

0x0044 T0C Timer 0 Configuration 36

0x0048 T1C Timer 1 Configuration 37

0x004C STPW1 Stop Watch Register 1 38

0x0050 STPW2 Stop Watch Register 2 39

0x0054 -

0x007C

reserved (11)

CC Control Registers

0x0080 SUCC1 SUC Configuration Register 1 40

0x0088 SUCC3 SUC Configuration Register 3 45

0x008C NEMC NEM Configuration Register 46

0x0090 PRTC1 PRT Configuration Register 1 47

0x0094 PRTC2 PRT Configuration Register 2 48

0x0098 MHDC MHD Configuration Register 49

manual_programmers_model.fm

0x009C reserved (1)

Page

Reset

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0303 FFFF

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0002 0000

0000 0000

0000 0000

0000 0000

0C40 1080

0100 0504

0000 0011

0000 0000

084C 0633

0F2D 0A0E

0000 0000

0000 0000

Acc Block

r

r/w GIF

r/w

r/w

r/w

r/w

r/w

r/w

r/w

INT

r/w

r/w

r/w

r/w

r/w

r/w

r

r/w

SUC0x0084 SUCC2 SUC Configuration Register 2 45

r/w

r/w

r/w NEM

r/w

PRT

r/w

r/w MHD

r

-20/165-

15.12.2006

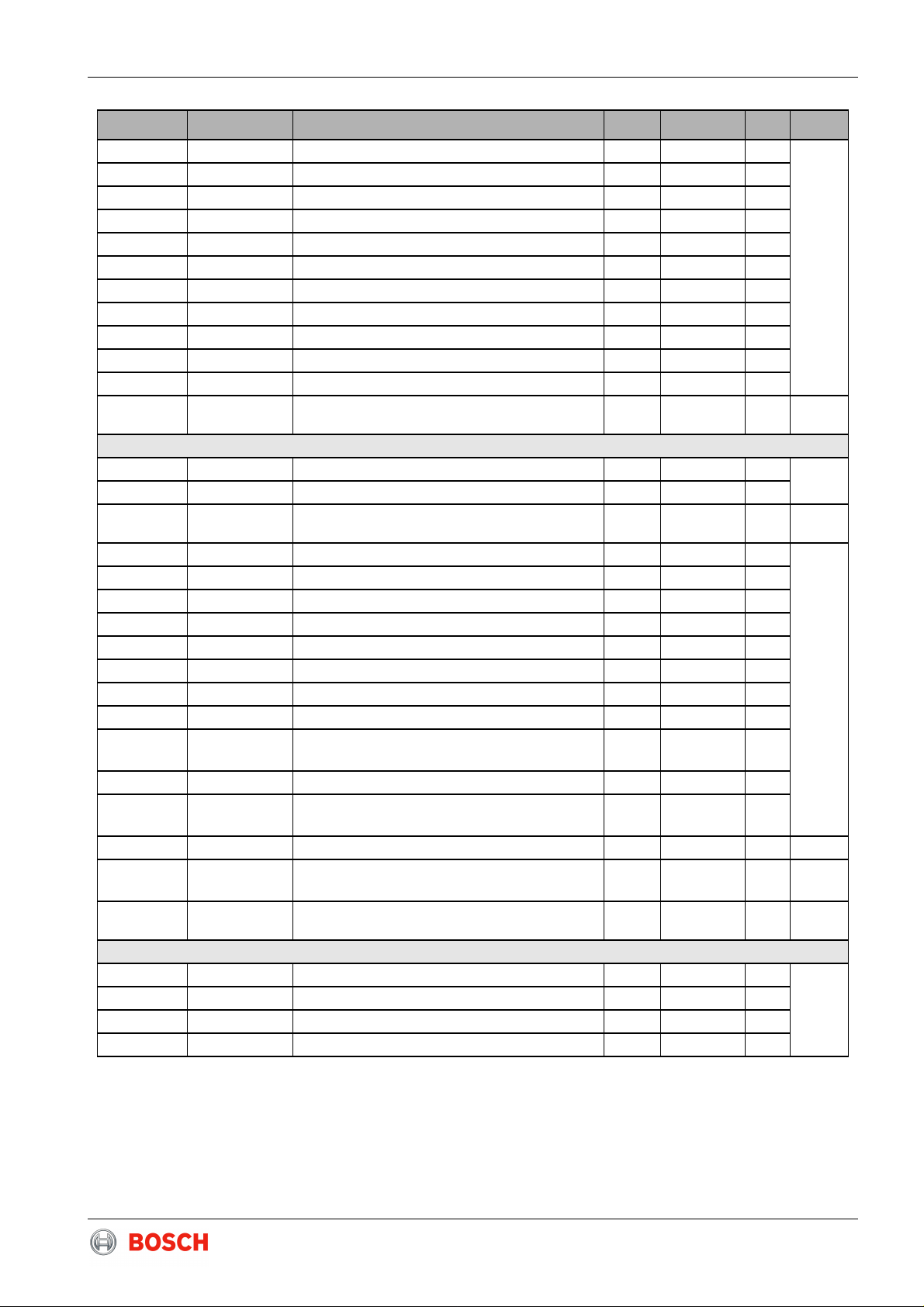

Page 21

User’s Manual

Revision 1.2.5 E-Ray

Address Symbol Name

0x00A0 GTUC1 GTU Configuration Register 1 50

0x00A4 GTUC2 GTU Configuration Register 2 50

0x00A8 GTUC3 GTU Configuration Register 3 51

0x00AC GTUC4 GTU Configuration Register 4 52

0x00B0 GTUC5 GTU Configuration Register 5 53

0x00B4 GTUC6 GTU Configuration Register 6 53

0x00B8 GTUC7 GTU Configuration Register 7 54

0x00BC GTUC8 GTU Configuration Register 8 54

0x00C0 GTUC9 GTU Configuration Register 9 55

0x00C4 GTUC10 GTU Configuration Register 10 55

0x00C8 GTUC11 GTU Configuration Register 11 56

0x00CC -

0x00FC

reserved (13)

CC Status Registers

0x0100 CCSV CC Status Vector 57

0x0104 CCEV CC Error Vector 60

0x0108 -

0x010C

reserved (2)

0x0110 SCV Slot Counter Value 61

0x0114 MTCCV Macrotick and Cycle Counter Value 61

0x0118 RCV Rate Correction Value 62

0x011C OCV Offset Correction Value 62

0x0120 SFS Sync Frame Status 63

0x0124 SWNIT Symbol Window and NIT Status 64

0x0128 ACS Aggregated Channel Status 66

0x012C reserved (1)

0x0130 -

0x0168

ESIDn Even Sync ID [1…15] 68

0x016C reserved (1)

0x0170 -

0x01A8

OSIDn Odd Sync ID [1…15] 69

0x01AC reserved (1)

0x01B0 -

0x01B8

0x01BC -

0x02FC

manual_programmers_model.fm

NMVn Network Management Vector [1…3] 70

reserved (81)

Message Buffer Control Registers

0x0300 MRC Message RAM Configuration 71

0x0304 FRF FIFO Rejection Filter 73

0x0308 FRFM FIFO Rejection Filter Mask 74

0x030C FCL FIFO Critical Level 74

Page

Reset

0000 0280

0002 000A

0202 0000

0008 0007

0E00 0000

0002 0000

0002 0004

0000 0002

0000 0101

0002 0005

0000 0000

0000 0000

0010 4000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0180 0000

0180 0000

0000 0000

0000 0080

Acc Block

r/w

r/w

r/w

r/w

r/w

GTU

r/w

r/w

r/w

r/w

r/w

r/w

r

r

SUC

r

r

r

r

r

r

r

r

GTU

r/w

r

r

r

r

r

r NEM

r

r/w

r/w

MHD

r/w

r/w

-21/165-

15.12.2006

Page 22

User’s Manual

Revision 1.2.5 E-Ray

Address Symbol Name

Message Buffer Status Registers

0x0310 MHDS Message Handler Status 75

0x0314 LDTS Last Dynamic Transmit Slot 76

0x0318 FSR FIFO Status Register 77

0x031C MHDF Message Handler Constraints Flags 78

0x0320 TXRQ1 Transmission Request 1 80

0x0324 TXRQ2 Transmission Request 2 80

0x0328 TXRQ3 Transmission Request 3 80

0x032C TXRQ4 Transmission Request 4 80

0x0330 NDAT1 New Data 1 81

0x0334 NDAT2 New Data 2 81

0x0338 NDAT3 New Data 3 81

0x033C NDAT4 New Data 4 81

0x0340 MBSC1 Message Buffer Status Changed 1 82

0x0344 MBSC2 Message Buffer Status Changed 2 82

0x0348 MBSC3 Message Buffer Status Changed 3 82

0x034C MBSC4 Message Buffer Status Changed 4 82

0x0350 -

0x03EC

reserved (40)

Identification Registers

0x03F0 CREL Core Release Register 83

0x03F4 ENDN Endian Register 83

0x03F8 -

0x03FC

reserved (2)

Input Buffer

0x0400 -

0x04FC

WRDSn Write Data Section [1…64] 84

0x0500 WRHS1 Write Header Section 1 85

0x0504 WRHS2 Write Header Section 2 86

0x0508 WRHS3 Write Header Section 3 86

0x050C reserved (1)

0x0510 IBCM Input Buffer Command Mask 87

0x0514 IBCR Input Buffer Command Request 88

0x0518 -

0x05FC

manual_programmers_model.fm

0x0600 -

0x06FC

RDDSn Read Data Section [1…64] 89

reserved (58)

Output Buffer

0x0700 RDHS1 Read Header Section 1 90

0x0704 RDHS2 Read Header Section 2 91

0x0708 RDHS3 Read Header Section 3 92

0x070C MBS Message Buffer Status 93

0x0710 OBCM Output Buffer Command Mask 96

0x0714 OBCR Output Buffer Command Request 97

0x0718 -

0x07FC

reserved (58)

Page

Reset

0000 0080

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

[release info]

8765 4321

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

Acc Block

r/w

r

r

r/w

r

r

r

r

MHD

r

r

r

r

r

r

r

r

r

r

GIF

r

r

r/w

r/w

r/w

r/w

IBF

r/w

r/w

r/w

r

r

r

r

OBF

r

r

r/w

r/w

r

Table 2: E-Ray register map

-22/165-

15.12.2006

Page 23

User’s Manual

Revision 1.2.5 E-Ray

4.2 Customer Registers

The address space from 0x0000to 0x000F is reserved for customer-specificregisters. These registers,

if implemented, are located in the Customer CPU Interface block. A description can be found in the

specific Customer CPU Interface specification document.

manual_programmers_model.fm

-23/165-

15.12.2006

Page 24

User’s Manual

Revision 1.2.5 E-Ray

4.3 Special Registers

4.3.1 Lock Register (LCK)

The Lock Register is write-only. Reading the register will return 0x0000 0000.

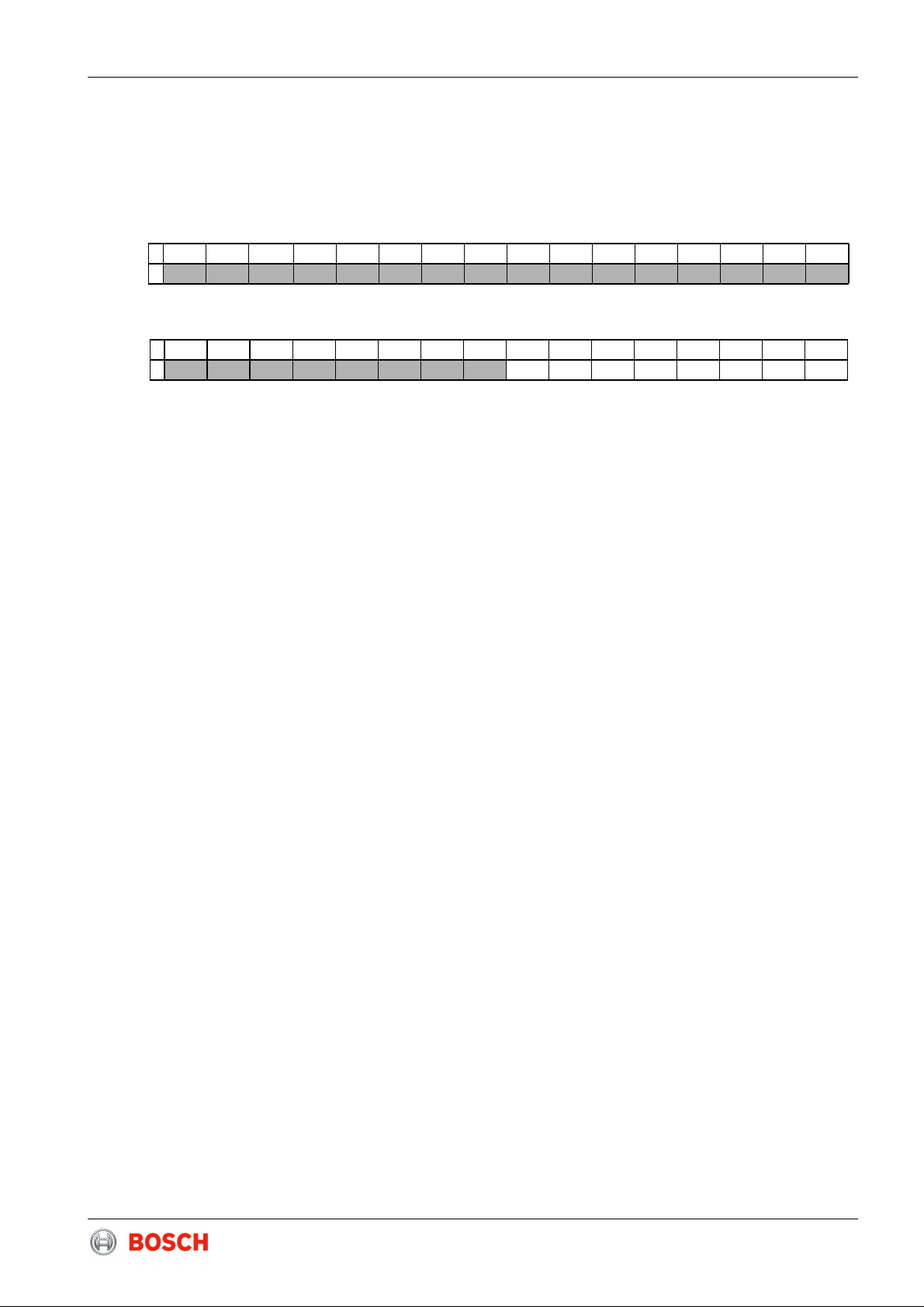

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LCK R0000000000000000

0x001C W

Reset 0 0 0 0000000000000

Bit 1514131211109876543210

R0000000000000000

W CLK7 CLK6 CLK5 CLK4 CLK3 CLK2 CLK1 CLK0

Reset 0 000000000000000

CLK[7:0] Configuration Lock Key

To leave CONFIG state by writing SUCC1.CMD[3:0] (commands READY,

MONITOR_MODE, ATM, LOOP_BACK), the write operation has to be directly preceded by

two write accesses to the Configuration Lock Key (unlock sequence). If the write sequence

below is interrupted by other write accesses between the second write to the Configuration Lock

Key and the write access to the SUCC1 register, the CC remains in CONFIG state and the

sequence has to be repeated.

First write: LCK.CLK[7:0] = "1100 1110" (0xCE)

Second write: LCK.CLK[7:0] = "0011 0001" (0x31)

Third write: SUCC1.CMD[3:0]

Note: In case that the Host uses 8/16-bit accesses to write CLK[7:0], the programmer has to ensure

that no "dummy accesses" e.g. to the remaining register bytes / words are inserted by the compiler.

manual_programmers_model.fm

-24/165-

15.12.2006

Page 25

User’s Manual

Revision 1.2.5 E-Ray

4.4 Interrupt Registers

4.4.1 Error Interrupt Register (EIR)

The flags are set when the CC detects one of the listed error conditions. The flags remain set until the

Host clears them.A flag is cleared by writing a ’1’ to the corresponding bit position. Writing a ’0’has

no effect on the flag. A hard reset will also clear the register.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EIR R00000

0x0020 W

Reset 0 000000000000000

Bit 1514131211109876543210

R0000

W

Reset 0 000000000000000

TABB LTVB EDB

MHF IOBA IIBA EFA RFO PERR CCL CCF SFO SFBM CNA PEMC

PEMC POC Error Mode Changed

This flag is set whenever the error mode signalled by CCEV.ERRM[1:0] has changed.

1 = Error mode has changed

0 = Error mode has not changed

00000

TABA LTVA EDA

CNA Command Not Accepted

The flag signals that the write access to the CHI command vector SUCC1.CMD[3:0] was not

successful because the requested command was not valid in the actual POC state, or because the

CHI command was locked (CCL = ’1’).

1 = CHI command not accepted

0 = CHI command accepted

SFBM Sync Frames Below Minimum

This flag signals that the number of sync frames received during the last communication cycle

was below the limit required by the FlexRay protocol. May be set during startup and therefore

should be cleared by the Host after the CC entered NORMAL_ACTIVE state.

1 = Less than the required minimum of sync frames received

0 = Sync node: 1 or more sync frames received, non-sync node: 2 or more sync frames received

SFO Sync Frame Overflow

Set when either the number of sync frames received during the last communication cycle or the

total number of sync frames received during the last double cycle exceeds the maximum number

of sync frames as defined by GTUC2.SNM[3:0].

manual_programmers_model.fm

1 = More sync frames received than configured by GTUC2.SNM[3:0]

0 = Number of received sync frames ≤ GTUC2.SNM[3:0]

CCF Clock Correction Failure

This flag is set at the end of the cycle whenever one of the following errors occurred:

• Missing offset and / or rate correction

• Clock correction limit reached

The clock correction status is monitored in registers CCEV and SFS. A failure may occur during

startup, therefore bit CCF should be cleared by the Host after the CC entered

NORMAL_ACTIVE state.

1 = Clock correction failed

0 = No clock correction error

-25/165-

15.12.2006

Page 26

User’s Manual

Revision 1.2.5 E-Ray

CCL CHI Command Locked

The flag signals that the write access to the CHI command vector SUCC1.CMD[3:0] was not

successful because the execution of the previous CHI command has not yet completed. In this

case bit CNA is also set to ’1’.

1 = CHI command not accepted

0 = CHI command accepted

PERR Parity Error

The flag signals a parity error to the Host. It is set whenever one of the flags MHDS.PIBF,

MHDS.POBF, MHDS.PMR, MHDS.PTBF1, MHDS.PTBF2 changes from ’0’ to ’1’.

1 = Parity error detected

0 = No parity error detected

RFO Receive FIFO Overrun

The flag is set by the CC when a receive FIFO overrun is detected. When a receive FIFO overrun

occurs, the oldest message is overwritten with the actual received message. The actual state of

the FIFO is monitored in register FSR.

1 = A receive FIFO overrun has been detected

0 = No receive FIFO overrun detected

EFA Empty FIFO Access

This flag is set by the CC when the Host requests the transfer of a message from the receive

FIFO via Output Buffer while the receive FIFO is empty.

1 = Host access to empty FIFO occurred

0 = No Host access to empty FIFO occurred

IIBA Illegal Input Buffer Access

This flag is set by the CC when the Host wants to modify a message buffer via Input Buffer

while the CC is not in CONFIG or DEFAULT_CONFIG state and one of the following conditions applies:

1) The Host writes to the Input Buffer Command Request register to modify the

• Header section of message buffer 0, 1 if configured for transmission in key slot

• Header section of static message buffers with buffer number < MRC.FDB[7:0]

while MRC.SEC[1:0] = "01"

• Header section of any static or dynamic message buffer while MRC.SEC[1:0] = "1x"

• Header and / or data section of any message buffer belonging to the receive FIFO

2) The Host writes to any register of the Input Buffer while IBCR.IBSYH is set to ’1’.

1 = Illegal Host access to Input Buffer occurred

0 = No illegal Host access to Input Buffer occurred

manual_programmers_model.fm

IOBA Illegal Output buffer Access

This flag is set by the CC when the Host requests the transfer of a message buffer from the Message RAM to the Output Buffer while OBCR.OBSYS is set to ’1’.

1 = Illegal Host access to Output Buffer occurred

0 = No illegal Host access to Output Buffer occurred

MHF Message Handler Constraints Flag

The flag signals a Message Handler constraints violation condition. It is set whenever one of the

flags MHDF.SNUA, MHDF.SNUB, MHDF.FNFA, MHDF.FNFB, MHDF.TBFA,

MHDF.TBFB, MHDF.WAHP changes from ’0’ to ’1’.

1 = Message Handler failure detected

0 = No Message Handler failure detected

-26/165-

15.12.2006

Page 27

User’s Manual

Revision 1.2.5 E-Ray

Channel-specific error flags:

EDA Error Detected on Channel A

This bit is set whenever one of the flags ACS.SEDA, ACS.CEDA, ACS.CIA, ACS.SBVA

changes from ’0’ to ’1’.

1 = Error detected on channel A

0 = No error detected on channel A

LTVA Latest Transmit Violation Channel A

The flag signals a latest transmit violation on channel A to the Host.

1 = Latest transmit violation detected on channel A

0 = No latest transmit violation detected on channel A

TABA Transmission Across Boundary Channel A

The flag signals to the Host that a transmission across a slot boundary occurred for channel A.

1 = Transmission across slot boundary detected on channel A

0 = No transmission across slot boundary detected on channel A

EDB Error Detected on Channel B

This bit is set whenever one of the flags ACS.SEDB, ACS.CEDB, ACS.CIB, ACS.SBVB

changes from ’0’ to ’1’.

1 = Error detected on channel B

0 = No error detected on channel B

LTVB Latest Transmit Violation Channel B

The flag signals a latest transmit violation on channel B to the Host.

1 = Latest transmit violation detected on channel B

0 = No latest transmit violation detected on channel B

TABB Transmission Across Boundary Channel B

The flag signals to the Host that a transmission across a slot boundary occurred for channel B.

1 = Transmission across slot boundary detected on channel B

0 = No transmission across slot boundary detected on channel B

manual_programmers_model.fm

-27/165-

15.12.2006

Page 28

User’s Manual

Revision 1.2.5 E-Ray

4.4.2 Status Interrupt Register (SIR)

The flags are set when the CC detects one of the listed events. The flags remain set until the Host

clears them. A flag is cleared by writing a ’1’ to the corresponding bit position. Writing a ’0’ has no

effect on the flag. A hard reset will also clear the register.

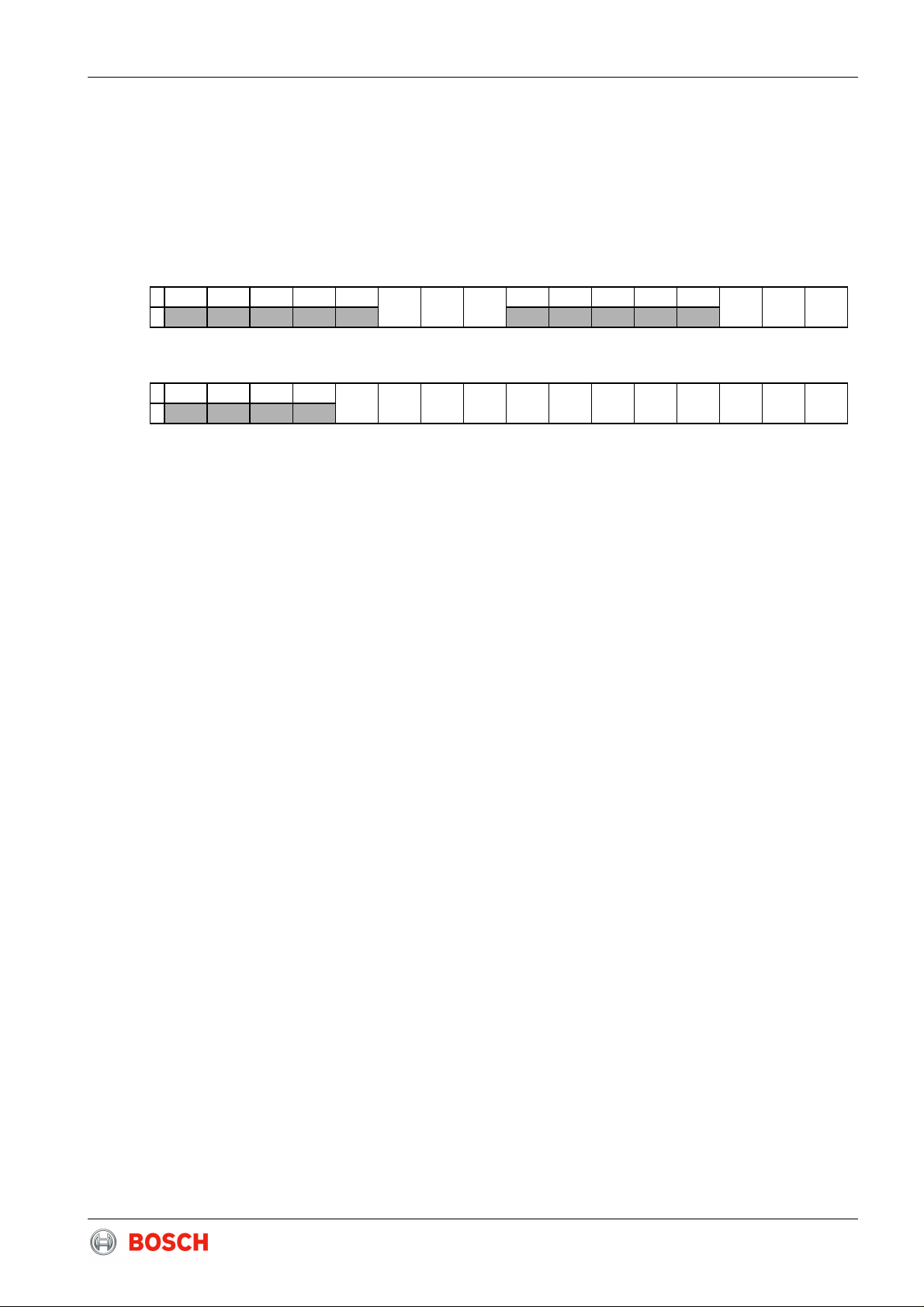

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SIR R000000

0x0024 W

Reset 0 000000000000000

Bit 1514131211109876543210

R

SDS MBSI SUCS SWE TOBC TIBC TI1 TI0 NMVC RFCL RFNE RXI TXI CYCS CAS WST

W

Reset 0 000000000000000

MTSB WUPB

000000

MTSA WUPA

WST Wakeup Status

This flag is set when the wakeup status vector CCSV.WSV[2:0] is changed by a protocol event.

1 = Wakeup status changed

0 = Wakeup status unchanged

CAS Collision Avoidance Symbol

This flag is set by the CC during STARTUP state when a CAS or a potential CAS was received.

1 = Bit pattern matching the CAS symbol received

0 = No bit pattern matching the CAS symbol received

CYCS Cycle Start Interrupt

This flag is set by the CC when a communication cycle starts.

1 = Communication cycle started

0 = No communication cycle started

TXI Transmit Interrupt

This flag is set by the CC at the end of frame transmission if bit MBI in the respective message

buffer is set to ’1’ (see Table 17).

1 = At least one frame was transmitted from a transmit buffer with MBI = ’1’

0 = No frame transmitted from a transmit buffer with MBI = ’1’

RXI Receive Interrupt

This flag is set by the CC whenever the set condition of a message buffers ND flag is fulfilled

(see 4.8.6 New Data 1/2/3/4 (NDAT1/2/3/4)), and if bit MBI of that message buffer is set to ’1’

(see Table 17).

manual_programmers_model.fm

1 = At least one ND flag of a receive buffer with MBI = ’1’ has been set to ’1’

0 = No ND flag of a receive buffer with MBI = ’1’ has been set to ’1’

RFNE Receive FIFO Not Empty

This flag is set by the CC when a received valid frame was stored into the empty receive FIFO.

The actual state of the receive FIFO is monitored in register FSR.

1 = Receive FIFO is not empty

0 = Receive FIFO is empty

RFCL Receive FIFO Critical Level

This flag is set when the receive FIFO fill level FSR.RFFL[7:0] is equal or greater than the critical level as configured by FCL.CL[7:0].

1 = Receive FIFO critical level reached

0 = Receive FIFO below critical level

-28/165-

15.12.2006

Page 29

User’s Manual

Revision 1.2.5 E-Ray

NMVC Network Management Vector Changed

This interrupt flag signals a change in the Network Management Vector visible to the Host.

1 = Network management vector changed

0 = No change in the network management vector

TI0 Timer Interrupt 0

This flag is set whenever timer 0 matches the conditions configured in register T0C. A Timer

Interrupt 0 is also signalled on pin eray_tint0.

1 = Timer Interrupt 0 occurred

0 = No Timer Interrupt 0

TI1 Timer Interrupt 1

This flag is set whenever timer 1 matches the conditions configured in register T1C. A Timer

Interrupt 1 is also signalled on pin eray_tint1.

1 = Timer Interrupt 1 occurred

0 = No Timer Interrupt 1

TIBC Transfer Input Buffer Completed

This flag is set whenever a transfer from Input Buffer to the Message RAM has completed and

IBCR.IBSYS has been reset by the Message Handler.

1 = Transfer between Input Buffer and Message RAM completed

0 = No transfer completed

TOBC Transfer Output Buffer Completed

This flag is set whenever a transfer from the Message RAM to the Output Buffer has completed

and OBCR.OBSYS has been reset by the Message Handler.

1 = Transfer between Message RAM and Output Buffer completed

0 = No transfer completed

SWE Stop Watch Event

This flag is set after a stop watch activation when the actual cycle counter and macrotick value

are stored in the Stop Watch register (see section 4.4.10 Stop Watch Register 1 (STPW1)).

1 = Stop Watch Event occurred

0 = No Stop Watch Event

SUCS Startup Completed Successfully

This flag is set whenever a startup completed successfully and the CC entered

NORMAL_ACTIVE state.

1 = Startup completed successfully

0 = No startup completed successfully

manual_programmers_model.fm

MBSI Message Buffer Status Interrupt

This flag is set by the CC when the message buffer status MBS has changed if bit MBI of that

message buffer is set (see Table 17).

1 = Message buffer status of at least one message buffer with MBI = ’1’ has changed

0 = No message buffer status change of message buffer with MBI = ’1’

SDS Start of Dynamic Segment

This flag is set by the CC when the dynamic segment starts.

1 = Dynamic segment started

0 = Dynamic segment not yet started

-29/165-

15.12.2006

Page 30

User’s Manual

Revision 1.2.5 E-Ray

Channel-specific status flags:

WUPA Wakeup Pattern Channel A

This flag is set by the CC when a wakeup pattern was received on channel A. Only set when the

CC is in WAKEUP, READY, or STARTUP state, or when in Monitor mode.

1 = Wakeup pattern received on channel A

0 = No wakeup pattern received on channel A

MTSA MTS Received on Channel A (vSS!ValidMTSA)

Media Access Test symbol received on channel A during the preceding symbol window.

Updated by the CC for each channel at the end of the symbol window.

1 = MTS symbol received on channel A

0 = No MTS symbol received on channel A

WUPB Wakeup Pattern Channel B

This flag is set by the CC when a wakeup pattern was received on channel B. Only set when the

CC is in WAKEUP, READY, or STARTUP state, or when in Monitor mode.

1 = Wakeup pattern received on channel B

0 = No wakeup pattern received on channel B

MTSB MTS Received on Channel B (vSS!ValidMTSB)

Media Access Test symbol received on channel B during the preceding symbol window.

Updated by the CC for each channel at the end of the symbol window.

1 = MTS symbol received on channel B

0 = No MTS symbol received on channel B

manual_programmers_model.fm

-30/165-

15.12.2006

Page 31

User’s Manual

Revision 1.2.5 E-Ray

4.4.3 Error Interrupt Line Select (EILS)

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EILS R00000

0x0028 W

Reset 0 0 0 0000000000000

Bit 1514131211109876543210

R0000

W

Reset 0 000000000000000

TABBL LTVBL EDBL

MHFL IOBAL IIBAL EFAL RFOL PERRL CCLL CCFL SFOL

00000

TABAL

SFBML

LTVAL EDAL

PEMCL

CNAL

The Error Interrupt Line Select register assigns an interruptgenerated by a specific errorinterrupt flag

from register EIR to one of the two module interrupt lines:

1 = Interrupt assigned to interrupt line eray_int1

0 = Interrupt assigned to interrupt line eray_int0

PEMCL POC Error Mode Changed Interrupt Line

CNAL Command Not Accepted Interrupt Line

SFBML Sync Frames Below Minimum Interrupt Line

SFOL Sync Frame Overflow Interrupt Line

CCFL Clock Correction Failure Interrupt Line

CCLL CHI Command Locked Interrupt Line

PERRL Parity Error Interrupt Line

RFOL Receive FIFO Overrun Interrupt Line

EFAL Empty FIFO Access Interrupt Line

IIBAL Illegal Input Buffer Access Interrupt Line

IOBAL Illegal Output Buffer Access Interrupt Line

MHFL Message Handler Constraints Flag Interrupt Line

EDAL Error Detected on Channel A Interrupt Line

LTVAL Latest Transmit Violation Channel A Interrupt Line

TABAL Transmission Across Boundary Channel A Interrupt Line

EDBL Error Detected on Channel B Interrupt Line

manual_programmers_model.fm

LTVBL Latest Transmit Violation Channel B Interrupt Line

TABBL Transmission Across Boundary Channel B Interrupt Line

-31/165-

15.12.2006

Page 32

User’s Manual

Revision 1.2.5 E-Ray

4.4.4 Status Interrupt Line Select (SILS)

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SILS R000000

0x002C W

Reset 0 0 0 0001100000011

Bit 1514131211109876543210

R

SDSL MBSIL SUCSL SWEL

W

Reset 1 111111111111111

TOBCL

MTSBL WUPBL

TIBCL TI1L TI0L

000000

NMVCL

RFCLL RFNEL RXIL TXIL

CYCSL

MTSAL WUPAL

CASL WSTL

The Status Interrupt Line Select register assign an interrupt generated by a specific status interrupt

flag from register SIR to one of the two module interrupt lines:

1 = Interrupt assigned to interrupt line eray_int1

0 = Interrupt assigned to interrupt line eray_int0

WSTL Wakeup Status Interrupt Line

CASL Collision Avoidance Symbol Interrupt Line

CYCSL Cycle Start Interrupt Line

TXIL Transmit Interrupt Line

RXIL Receive Interrupt Line

RFNEL Receive FIFO Not Empty Interrupt Line

RFCLL Receive FIFO Critical Level Interrupt Line

NMVCL Network Management Vector Changed Interrupt Line

TI0L Timer Interrupt 0 Line

TI1L Timer Interrupt 1 Line

TIBCL Transfer Input Buffer Completed Interrupt Line

TOBCL Transfer Output Buffer Completed Interrupt Line

SWEL Stop Watch Event Interrupt Line

SUCSL Startup Completed Successfully Interrupt Line

MBSIL Message Buffer Status Interrupt Line

SDSL Start of Dynamic Segment Interrupt Line

manual_programmers_model.fm

WUPAL Wakeup Pattern Channel A Interrupt Line

MTSAL Media Access Test Symbol Channel A Interrupt Line

WUPBL Wakeup Pattern Channel B Interrupt Line

MTSBL Media Access Test Symbol Channel B Interrupt Line

-32/165-

15.12.2006

Page 33

User’s Manual

Revision 1.2.5 E-Ray

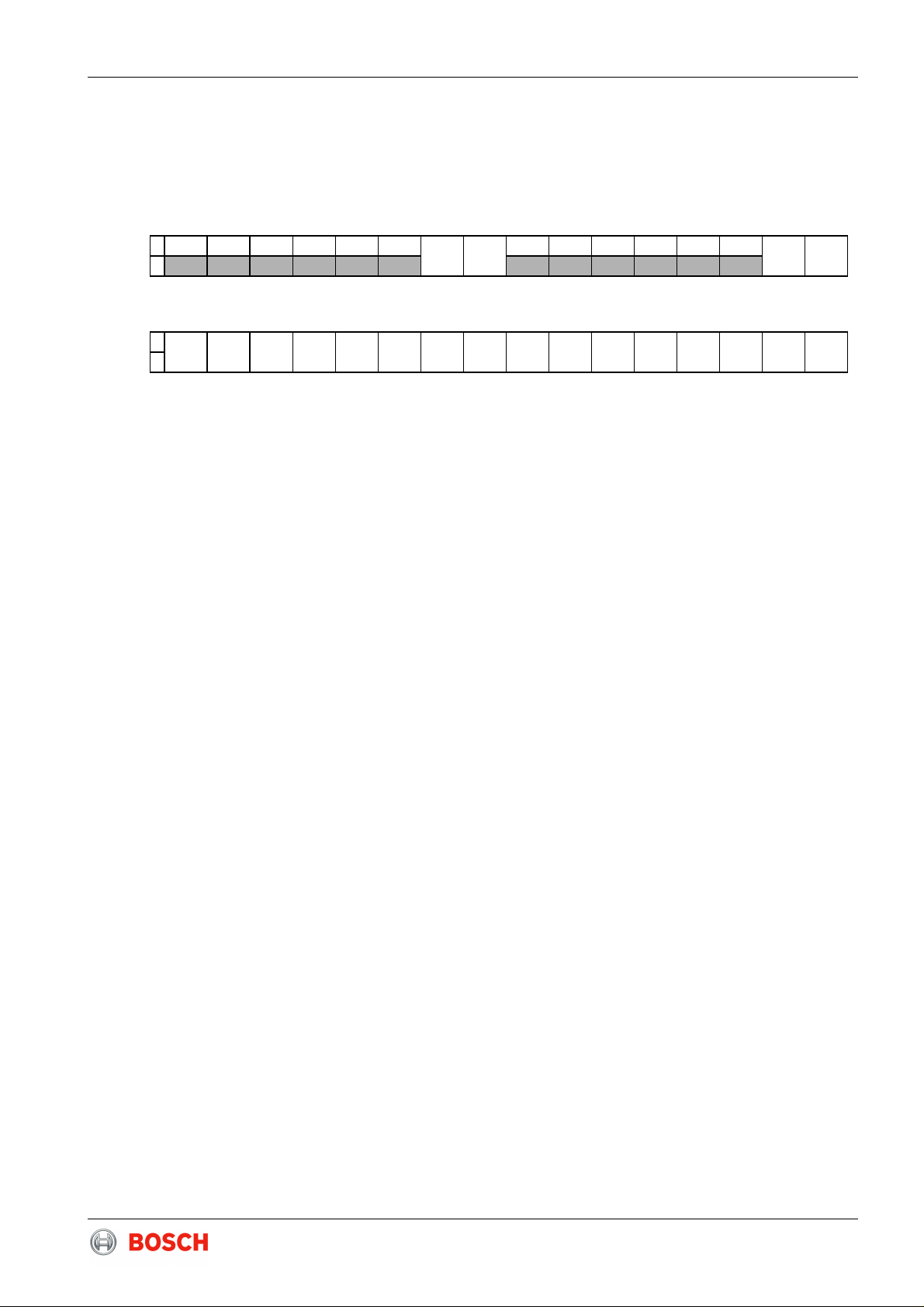

4.4.5 Error Interrupt Enable Set / Reset (EIES, EIER)

The settings in the Error Interrupt Enable register determine which status changes in the Error Interrupt Register will result in an interrupt.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EIES,R R0 0 0 0 0

S:0x0030

R:0x0034

W

Reset 0 0 0 0 000000000000

Bit 1514131211109876543210

R0000

W

Reset 0 000000000000000

TABBE LTVBE EDBE

MHFE IOBAE IIBAE EFAE RFOE PERRE CCLE CCFE SFOE

00000

TABAE

SFBME

LTVAE EDAE

PEMCE

CNAE

The enable bits are set by writing to address 0x0030 and reset by writing to address 0x0034. Writing

a ’1’ sets / resets the specific enable bit, writing a ’0’ has no effect. Reading from both addresses will

result in the same value.

1 = Interrupt enabled

0 = Interrupt disabled

PEMCE POC Error Mode Changed Interrupt Enable

CNAE Command Not Accepted Interrupt Enable

SFBME Sync Frames Below Minimum Interrupt Enable

SFOE Sync Frame Overflow Interrupt Enable

CCFE Clock Correction Failure Interrupt Enable

CCLE CHI Command Locked Interrupt Enable

PERRE Parity Error Interrupt Enable

RFOE Receive FIFO Overrun Interrupt Enable

EFAE Empty FIFO Access Interrupt Enable

IIBAE Illegal Input Buffer Access Interrupt Enable

IOBAE Illegal Output Buffer Access Interrupt Enable

MHFE Message Handler Constraints Flag Interrupt Enable

EDAE Error Detected on Channel A Interrupt Enable

manual_programmers_model.fm

LTVAE Latest Transmit Violation Channel A Interrupt Enable

TABAE Transmission Across Boundary Channel A Interrupt Enable

EDBE Error Detected on Channel B Interrupt Enable

LTVBE Latest Transmit Violation Channel B Interrupt Enable

TABBE Transmission Across Boundary Channel B Interrupt Enable

-33/165-

15.12.2006

Page 34

User’s Manual

Revision 1.2.5 E-Ray

4.4.6 Status Interrupt Enable Set / Reset (SIES, SIER)

The settings in the Status Interrupt Enable register determine which status changes in the Status Interrupt Register will result in an interrupt.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SIES,R R0 0 0 0 0 0

S:0x0038

R:0x003C

W

Reset 0 0 0 0 000000000000

Bit 1514131211109876543210

R

SDSE MBSIE SUCSE SWEE

W

Reset 0 000000000000000

TOBCE

MTSBE WUPBE

TIBCE TI1E TI0E

000000

NMVCE

RFCLE RFNEE RXIE TXIE

CYCSE

MTSAE WUPAE

CASE WSTE

The enable bits are set by writing to address 0x0038 and reset by writing to address 0x003C. Writing

a ’1’ sets / resets the specific enable bit, writing a ’0’ has no effect. Reading from both addresses will

result in the same value.

1 = Interrupt enabled

0 = Interrupt disabled

WSTE Wakeup Status Interrupt Enable

CASE Collision Avoidance Symbol Interrupt Enable

CYCSE Cycle Start Interrupt Enable

TXIE Transmit Interrupt Enable

RXIE Receive Interrupt Enable

RFNEE Receive FIFO Not Empty Interrupt Enable

RFCLE Receive FIFO Critical Level Interrupt Enable

NMVCE Network Management Vector Changed Interrupt Enable

TI0E Timer Interrupt 0 Enable

TI1E Timer Interrupt 1 Enable

TIBCE Transfer Input Buffer Completed Interrupt Enable

TOBCE Transfer Output Buffer Completed Interrupt Enable

SWEE Stop Watch Event Interrupt Enable

manual_programmers_model.fm

SUCSE Startup Completed Successfully Interrupt Enable

MBSIE Message Buffer Status Interrupt Enable

SDSE Start of Dynamic Segment Interrupt Enable

WUPAE Wakeup Pattern Channel A Interrupt Enable

MTSAE MTS Received on Channel A Interrupt Enable

WUPBE Wakeup Pattern Channel B Interrupt Enable

MTSBE MTS Received on Channel B Interrupt Enable

-34/165-

15.12.2006

Page 35

User’s Manual

Revision 1.2.5 E-Ray

4.4.7 Interrupt Line Enable (ILE)

Each of the two interrupt lines to the Host (eray_int0, eray_int1) can be enabled / disabled separately

by programming bit EINT0 and EINT1.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ILE R0000000000000000

0x0040 W

Reset 0 000000000000000

Bit 1514131211109876543210

R00000000000000

W

Reset 0 000000000000000

EINT1 EINT0

EINT0 Enable Interrupt Line 0

1 = Interrupt line eray_int0 enabled

0 = Interrupt line eray_int0 disabled

EINT1 Enable Interrupt Line 1

1 = Interrupt line eray_int1 enabled

0 = Interrupt line eray_int1 disabled

manual_programmers_model.fm

-35/165-

15.12.2006

Page 36

User’s Manual

Revision 1.2.5 E-Ray

4.4.8 Timer 0 Configuration (T0C)

Absolute timer. Specifies in terms of cycle count and macrotick the point in time when the timer 0

interrupt occurs. When the timer 0 interrupt is asserted, output signal eray_tint0 is set to ’1’ for the

duration of one macrotick and SIR.TI0 is set to ’1’.

Timer 0 can be activated as long as the POC is either in NORMAL_ACTIVE state or in

NORMAL_PASSIVE state. Timer 0 is deactivated when leaving NORMAL_ACTIVE state or

NORMAL_PASSIVE state except for transitions between the two states.

Before reconfiguration of the timer, the timer has to be halted first by writing bit T0RC to ’0’.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

T0C R0 0

0x0044 W

Reset 0 000000000000000

Bit 1514131211109876543210

R0

W

Reset 0 000000000000000

T0MO13T0MO12T0MO11T0MO10T0MO9T0MO8T0MO7T0MO6T0MO5T0MO4T0MO3T0MO2T0MO1T0MO

T0CC6 T0CC5 T0CC4 T0CC3 T0CC2 T0CC1 T0CC0

000000

0

T0MS T0RC

T0RC Timer 0 Run Control

1 = Timer 0 running

0 = Timer 0 halted

T0MS Timer 0 Mode Select

1 = Continuous mode

0 = Single-shot mode

T0CC[6:0] Timer 0 Cycle Code

The 7-bit timer 0 cycle code determines the cycle set used for generation of the timer 0 interrupt.

For details about the configuration of the cycle code see Section 5.7.2 Cycle Counter Filtering.

T0MO[13:0] Timer 0 Macrotick Offset

Configures the macrotick offset from the beginning of the cycle where the interrupt is to occur.

The Timer 0 Interrupt occurs at this offset for each cycle of the cycle set.

Note: The configuration of timer 0 is compared against the macrotick counter value, there is no sep-

arate counter for timer 0.In case the CC leaves NORMAL_ACTIVEor NORMAL_PASSIVE

state, or if timer 0 is halted by Host command, output signal eray_tint0 is reset to ’0’ immediately.

manual_programmers_model.fm

-36/165-

15.12.2006

Page 37

User’s Manual

Revision 1.2.5 E-Ray

4.4.9 Timer 1 Configuration (T1C)

Relative timer. After the specified number of macroticks has expired, the timer 1 interrupt is asserted,

output signal eray_tint1 is set to ’1’ for the duration of one macrotick and SIR.TI1 is set to ’1’.

Timer 1 can be activated as long as the POC is either in NORMAL_ACTIVE state or in

NORMAL_PASSIVE state. Timer 1 is deactivated when leaving NORMAL_ACTIVE state or

NORMAL_PASSIVE state except for transitions between the two states.

Before reconfiguration of the timer, the timer has to be halted first by writing bit T1RC to ’0’.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

T1C R0 0

0x0048 W

Reset 0 000000000000010

Bit 1514131211109876543210

R00000000000000

W

Reset 0 000000000000000

T1MC13T1MC12T1MC11T1MC

10

T1MC9 T1MC8 T1MC7 T1MC6 T1MC5 T1MC4 T1MC3 T1MC2 T1MC1 T1MC0

T1MS T1RC

T1RC Timer 1 Run Control

1 = Timer 1 running

0 = Timer 1 halted

T1MS Timer 1 Mode Select

1 = Continuous mode

0 = Single-shot mode

T1MC[13:0] Timer 1 Macrotick Count

When the configured macrotick count is reached the timer 1 interrupt is generated.

Valid values are: 2 to 16383 MT in continuous mode

1 to 16383 MT in single-shot mode

Note: In case the CC leaves NORMAL_ACTIVE or NORMAL_PASSIVEstate, orif timer1 ishalt-

ed by Host command, output signal eray_tint1 is reset to ’0’ immediately.

manual_programmers_model.fm

-37/165-

15.12.2006

Page 38

User’s Manual

Revision 1.2.5 E-Ray

4.4.10 Stop Watch Register 1 (STPW1)

The stop watch is activated by a rising or falling edge on pin eray_stpwt, by an interrupt 0,1 event

(rising edge on pin eray_int0 or eray_int1) or by theHost by writing bit SSWT to ’1’. With the macrotick counter increment following next to the stop watchactivation the actual cycle counter andmacrotick values are captured in register STPW1 while the slot counter values for channel A and B are

captured in register STPW2.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

STPW1 R0 0

0x004C W

Reset 0 000000000000000

Bit 1514131211109876543210

R 0 0 SCCV5 SCCV4 SCCV3 SCCV2 SCCV1 SCCV0 0

W

Reset 0 000000000000000

SMTV13SMTV12SMTV11SMTV

SMTV9 SMTV8 SMTV7 SMTV6 SMTV5 SMTV4 SMTV3 SMTV2 SMTV1 SMTV0

10

EINT1 EINT0 EETP SSWT EDGE SWMS ESWT

ESWT Enable Stop Watch Trigger

If enabled an edge on input eray_stpwt or an interrupt 0,1 event (rising edge on pin eray_int0

or eray_int1) activates the stop watch. In single-shot mode this bit is reset to ’0’ after the actual

cycle counter and macrotick value are stored in the Stop Watch register.

1 = Stop watch trigger enabled

0 = Stop watch trigger disabled

SWMS Stop Watch Mode Select

1 = Continuous mode

0 = Single-shot mode

EDGE Stop Watch Trigger Edge Select

1 = Rising edge

0 = Falling edge

SSWT Software Stop Watch Trigger

When the Host writes this bit to ’1’ the stop watch is activated. After the actual cycle counter

and macrotick value are stored in the Stop Watch register this bit is reset to ’0’. The bit is only

writeable while ESWT = ’0’.

1 = Stop watch activated by software trigger

0 = Software trigger reset

EETP Enable External Trigger Pin

manual_programmers_model.fm

Enables stop watch trigger event via pin eray_stpwt if ESWT = ’1’.

1 = Edge on pin eray_stpwt triggers stop watch

0 = Stop watch trigger via pin eray_stpwt disabled

EINT0 Enable Interrupt 0 Trigger

Enables stop watch trigger by interrupt 0 event if ESWT = ’1’.

1 = Interrupt 0 event triggers stop watch

0 = Stop watch trigger by interrupt 0 disabled

EINT1 Enable Interrupt 1 Trigger

Enables stop watch trigger by interrupt 1event if ESWT = ’1’.

1 = Interrupt 1 event triggers stop watch

0 = Stop watch trigger by interrupt 1 disabled

-38/165-

15.12.2006

Page 39

User’s Manual

Revision 1.2.5 E-Ray

SCCV[5:0] Stop Watch Captured Cycle Counter Value

State of the cycle counter when the stop watch event occurred. Valid values are 0 to 63.

SMTV[13:0] Stop Watch Captured Macrotick Value

State of the macrotick counter when the stop watch event occurred. Valid values are 0 to 16000.