Biostar TA57A Schematics

5

A

PAGE

1

2

3

4

5

D D

C C

B B

6-10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

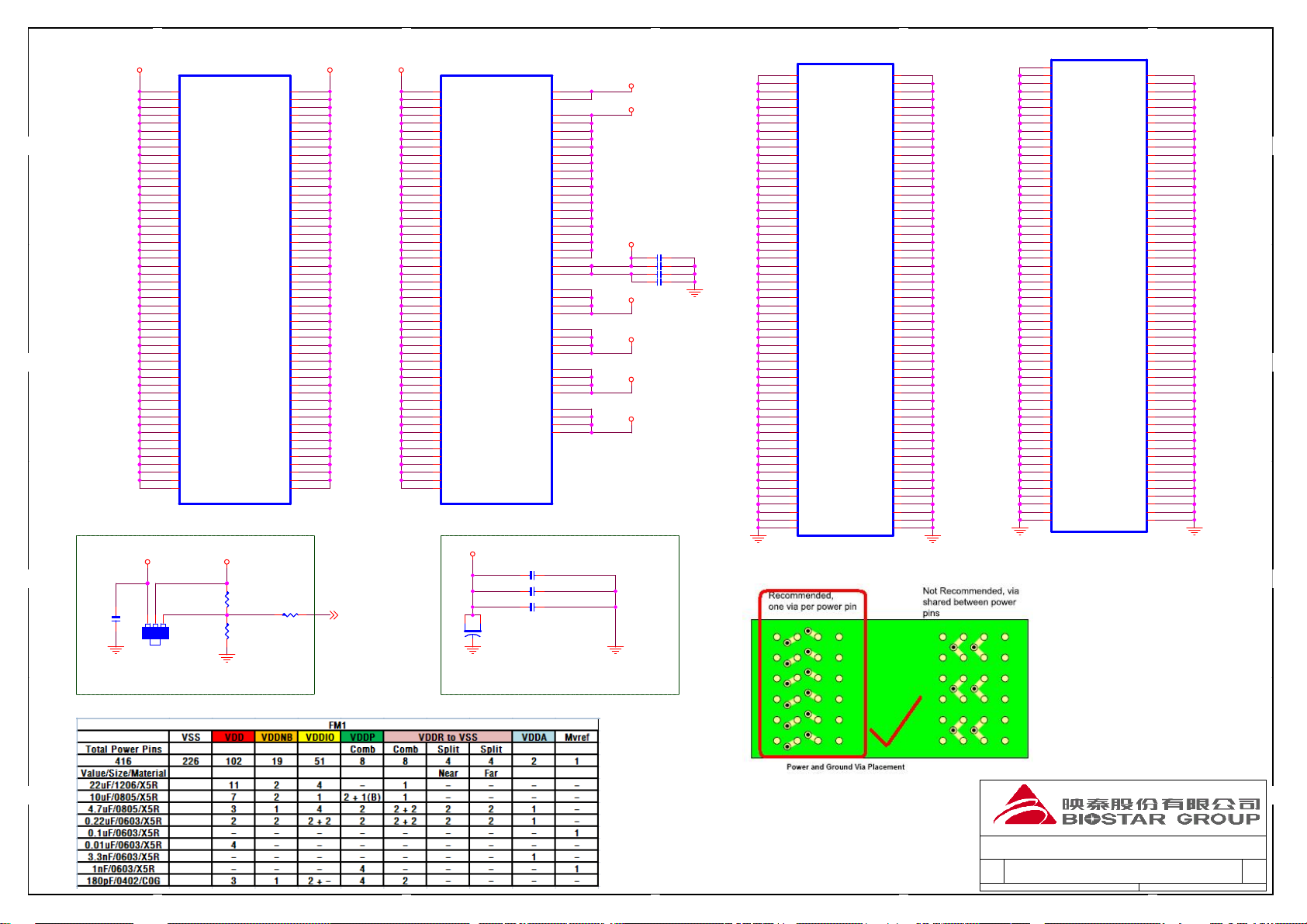

CONTENTS

COVER

BLOCK DIAGRAM

POWER DELIVERY

CLOCK DISTRIBUTION

REVISION HISTROY

SKT 941 K8 AM3 CPU

CPU DECOUPLING

DDR CLK BYPASS

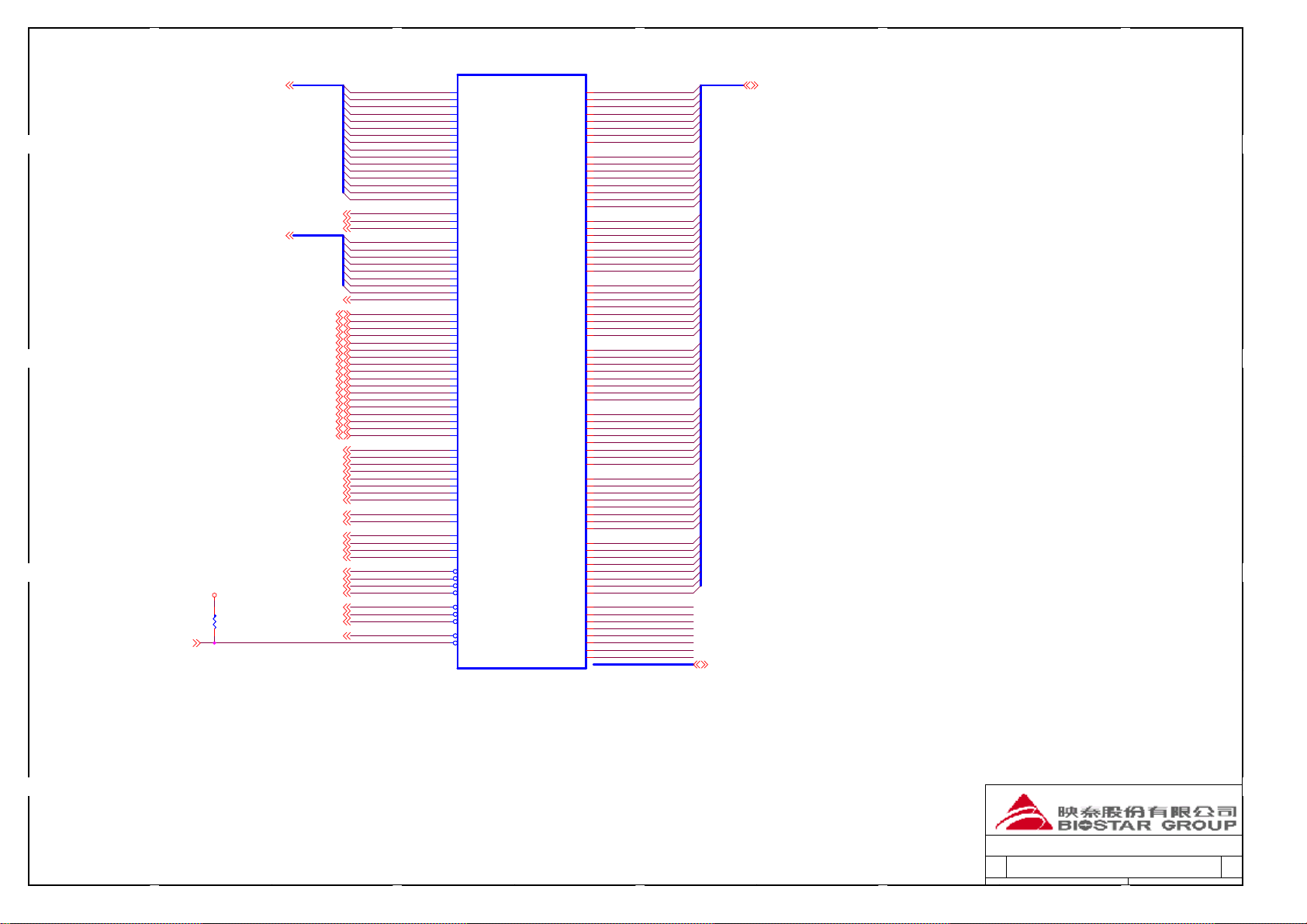

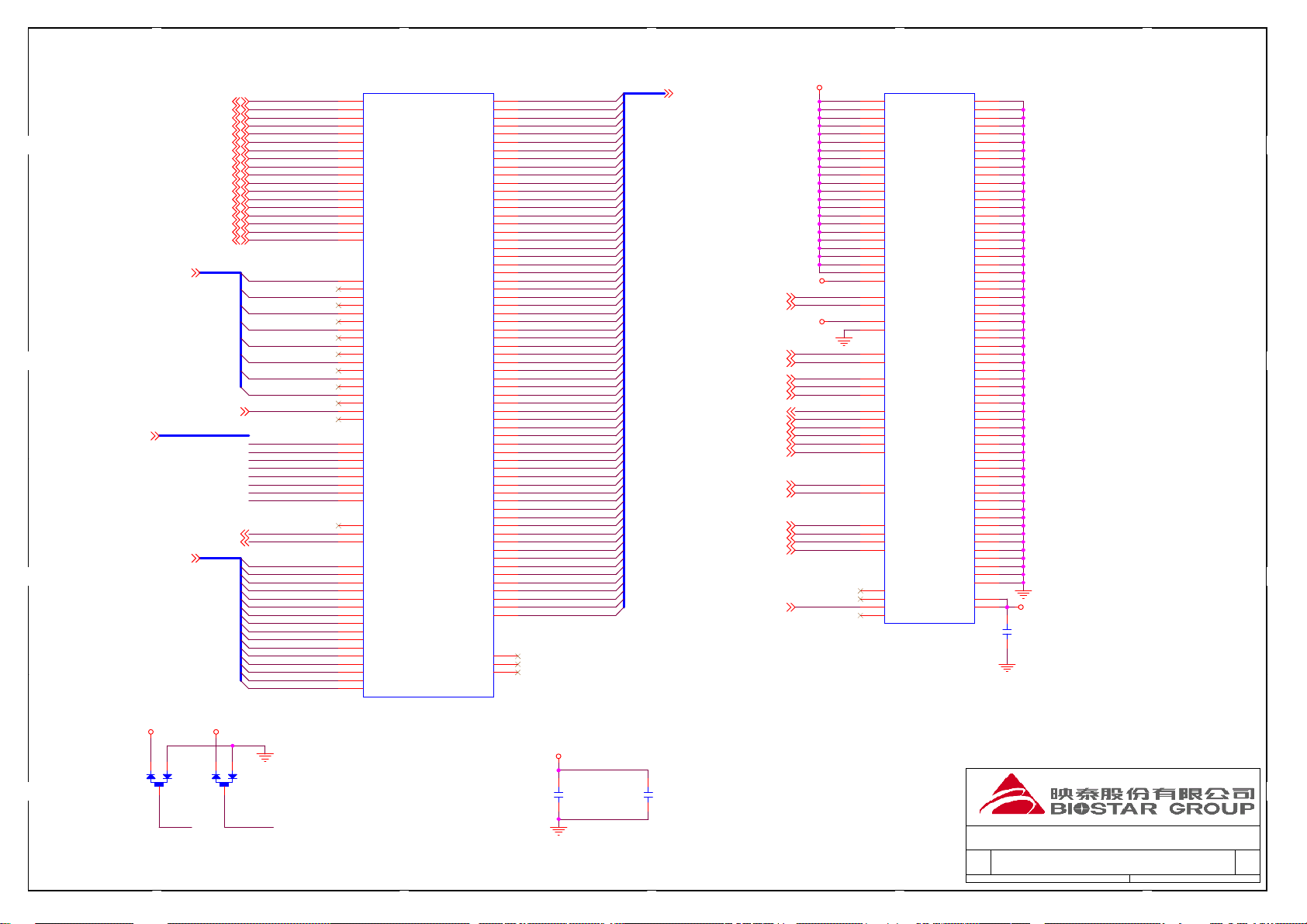

DDR3 DIMM A1

DDR3 DIMM B1

ADO FUNCTION

RS780-HT LINK

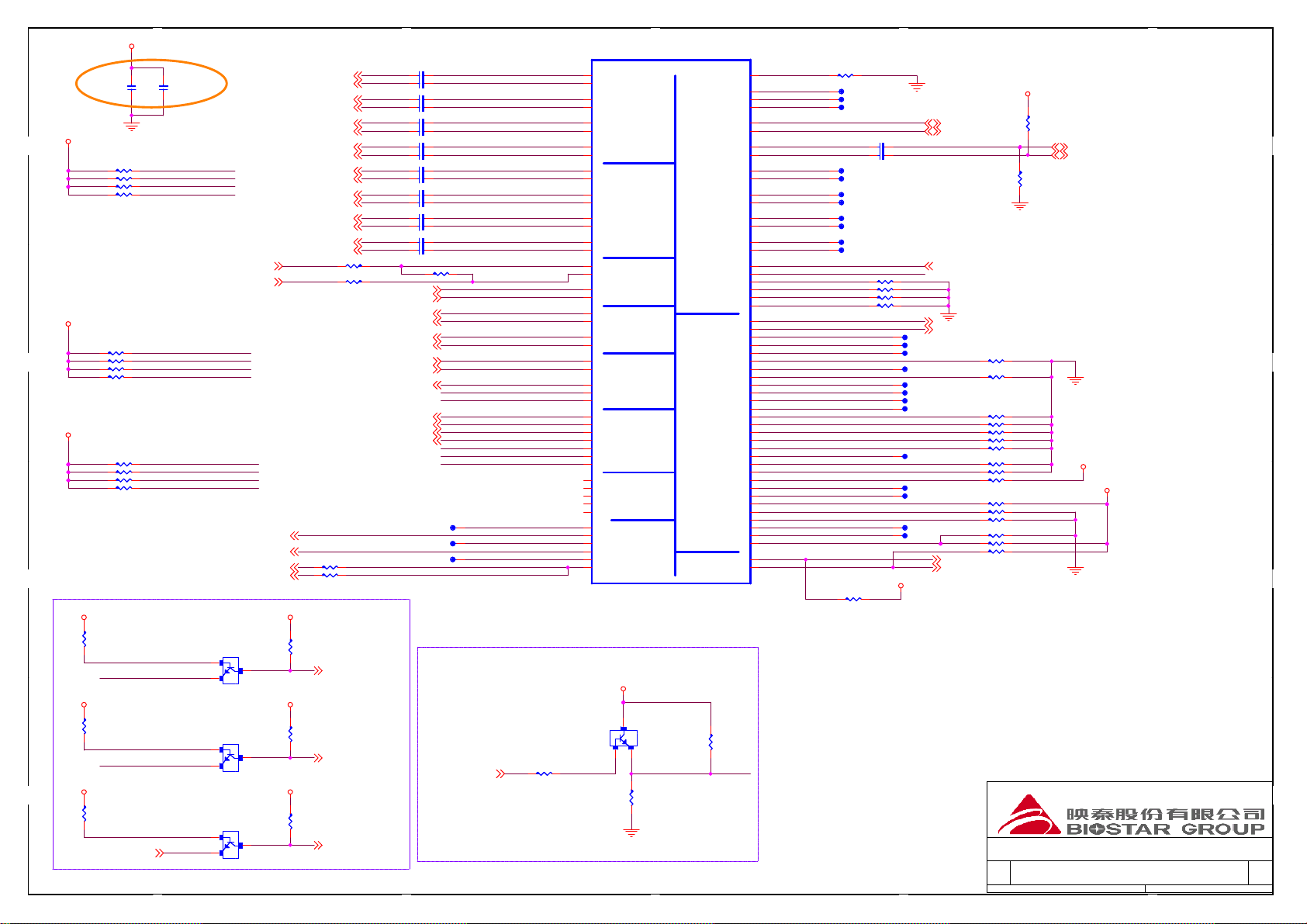

RS780-PCIE

RS780-SYSTEM

RS780-PWOER&SBD_MEM

CLOCK GEN

SB710-PCIE/PCI/CPU/LPC

SB710-ACPI/GPIO/USB/AUD

SB710-SATA/IDE/HWM/SPI

SB710-POWER&DECOUPLING

SB710-STRAPS

CRT

PCI-E 16X SLOT

PCI SLOT

NONE

USB CONN

CODEC VT1708B/ALC662

AUDIO CONNECTOR

SUPER I/O ITE8728

FAN CONTROL

PS2 CONN

COM&LPT CONNECTOR

ATX PWR / FRONT PANEL / LED

OVER VOLTAGE IC

FRONT USB

PWRGD / MISC DC-DC

VCC_CORE DC-DC CONVER

MEMORY POWER

NB/SB CORE POWER

Realtek RTL8111E

BOM

4 3

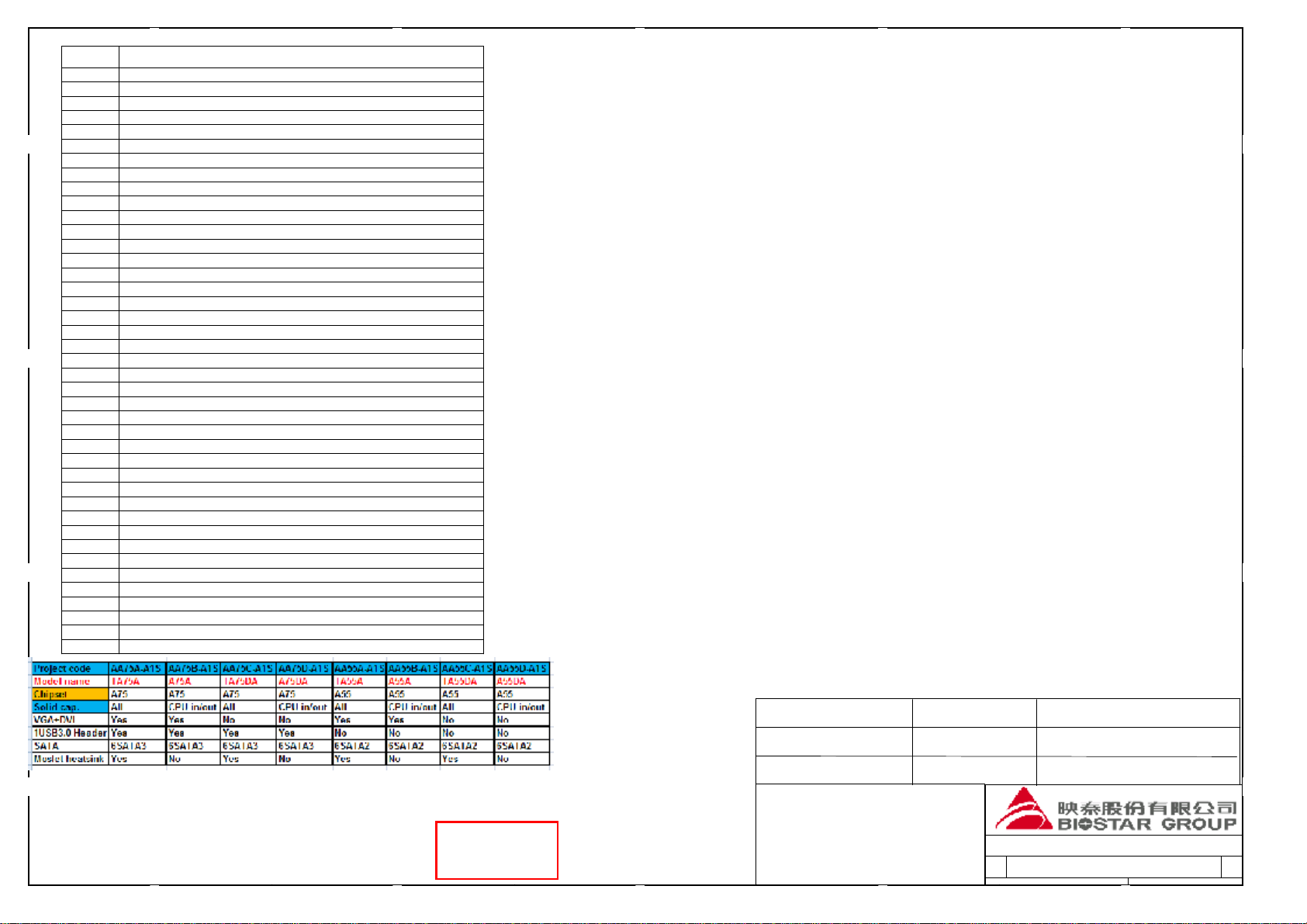

AA55C-A1S

CPU:

AMD FM1

System Chipset:

HUDSON-D2 (A55 FCH)

Main Memory:

Dual Channel/DDR-III*4(Max 32GB) 800/1066/1333/1600/1866

Onboard Device:

Super I/O:IT8728

LAN:Realtek 8111E(RTL8111E-VL-CG QFN48)

HD Codec:VT1708B 3 jacks

Power solution:

CPU Voltage Regulators:3phase by ST6717A

VDDNB voltage Regulators:1phase by ST6717A

APU_VDDR/P_RUN voltage Regulators:1Phase by FP6326

DDR voltage Regulators:1Phase by FP6326

Expansion Slots:

PCI EXPRESS*2 (16X Slot*1+4X Slot*1)

PCI EXPRESS 1X Slot*2

PCI Slot*2

REAR IO:

PS/2 Keyboard +Mouse

COM Port

2 layer USB3.0

2 layer USB2.0 + Gb RJ-45 Ports

REV 6.0

2

Model Name:TA57A

1

Audio Jackets

PCB Size:304.80*219.91mm.

HW Engineer:

HW Leader1:

HW Leader2:

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Date:

Date:

Date:

AA55C-A1S

AA55C-A1S

AA55C-A1S

COVER

COVER

COVER

1 45Friday, July 29, 2011

1 45Friday, July 29, 2011

1 45Friday, July 29, 2011

BIOSTAR STANDARD

NO:2011_AMD_FM1_01

2011-03-21

Front I/O:

6 SATA2

USB2.0 Header * 2

Serial header

SPDIF Out Header

Parallel Header

Front Audio Header

CPU /System1/System2

it

A

6.0

6.0

6.0

5

A

D D

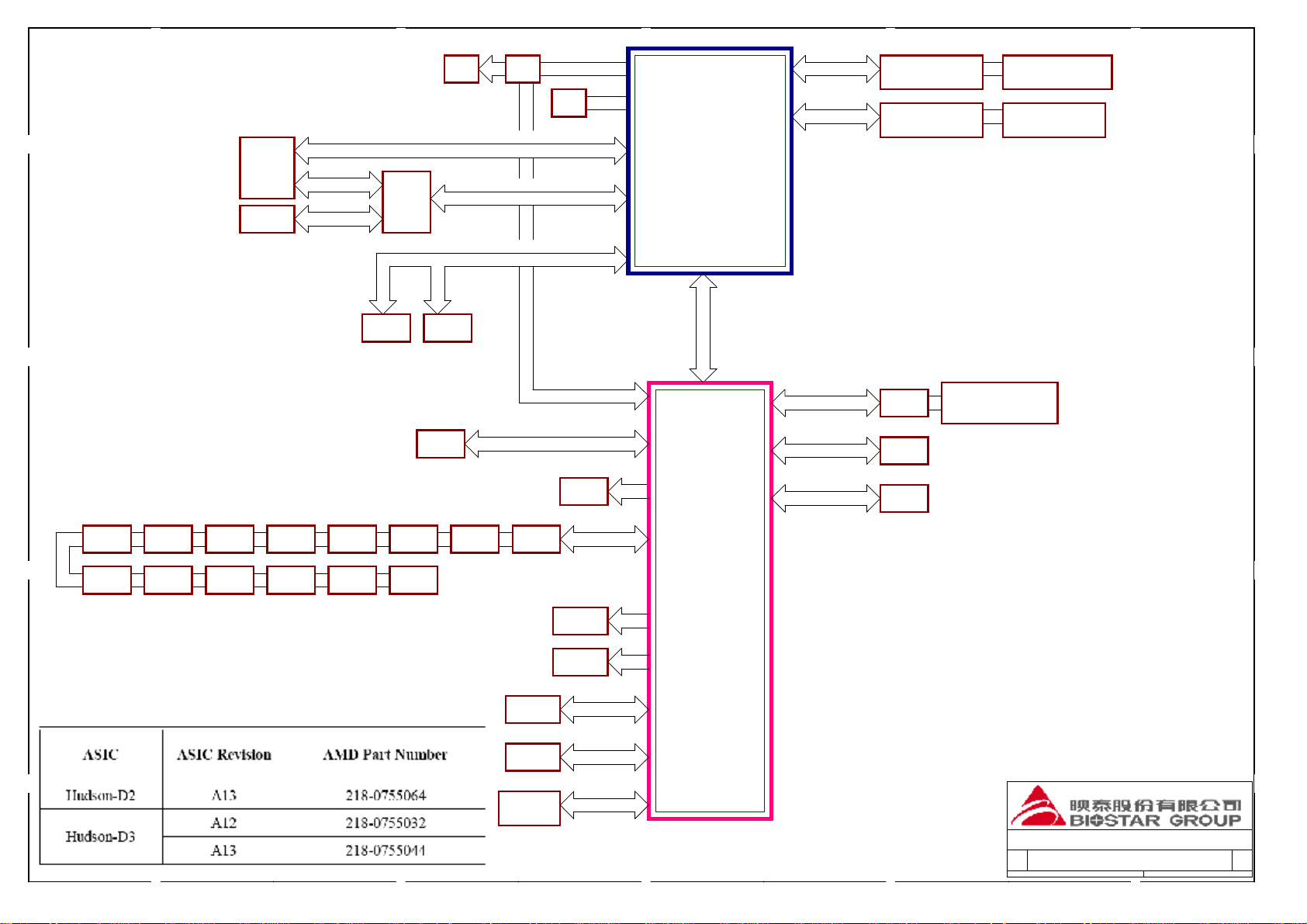

X16 GFX

DT SLOT

X8 GFX

DT SLOT

PCIE X8

PCIE X8

4 3

DP1

HDMI

DP0

SWITCH

DP

CONN

PCIE GEN2 X8(Upper APU Lanes)

PCIE GEN2 X8(Lower Lanes)

GPP PCIE INTERFACE GEN2 X4

SW

AMD

Fusion

Llano FM1

AM3 SOCKET 937 PIN

uFCPGA

DX10.1 IGP

DISPLAY PORT X4

1X16 PCIE GFX I/F

4X1 PCIE GPP I/F

4X1 PCIE I/F WITH HUDSON-D1

Channel A

128bit

Channel B

2

UNBUFFERED DDRIII

DIMM1

UNBUFFERED DDRIII

DIMM3

UNBUFFERED DDRIII

DIMM2

UNBUFFERED DDRIII

DIMM4

1

Mini

PCIE

X1

X4 DT

SLOT

X3

PCIE GEN2

X4

C C

FCH

USB2.0 (14)+USB1.1 (2)

SATA III (6)

4X1 PCIE GEN2 I/F

X4 DT

SLOT

GPP PCIE INTERFACE GEN2 X4

HUDSON-D2

VGA

CONN

USB3.0X4

SD CARD

READER

USB2.0

PCI BUS

USB-7

usb3.0

B B

USB-8

usb3.0

USB-6

usb3.0

USB-9

usb3.0

USB-5

Header

USB-10

Header

USB-4

Header

USB-11

Header

USB-3

Header

USB-12

CONN

USB-2

Header

USB-13

CONN

USB-1

Header

USB-0

Header

PCI SLOT

INT CLK GEN

GB MAC

HW MONITOR

PCI/PCI BDGE

INT RTC

HD AUDIO

EC

SPI I/F

ACPI 1.1

LPC I/F

HD AUDIO I/F

RGMII I/F

SATAII I/F

AZALIA

CODEC

BCM

PHY

BCM

PHY

Speaker header

Headphone & SPDIF JACK

MIC jack Array

SPI ROM

BOOT

STRAPS

ROM

SPI I/F

I2C I/F

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

AA55C-A1S

AA55C-A1S

AA55C-A1S

2 45Friday, July 29, 2011

2 45Friday, July 29, 2011

2 45Friday, July 29, 2011

A

6.0

6.0

6.0

it

A

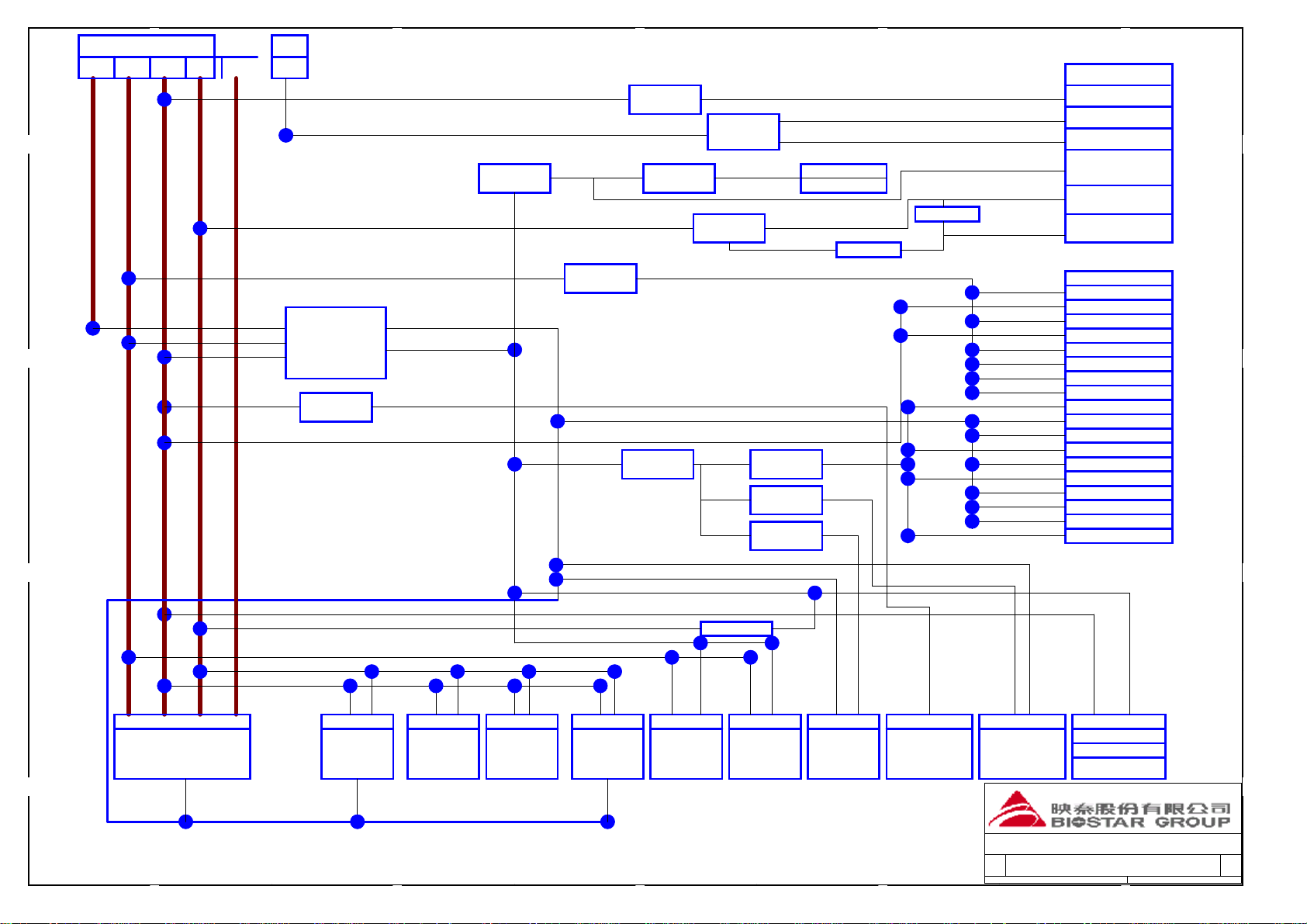

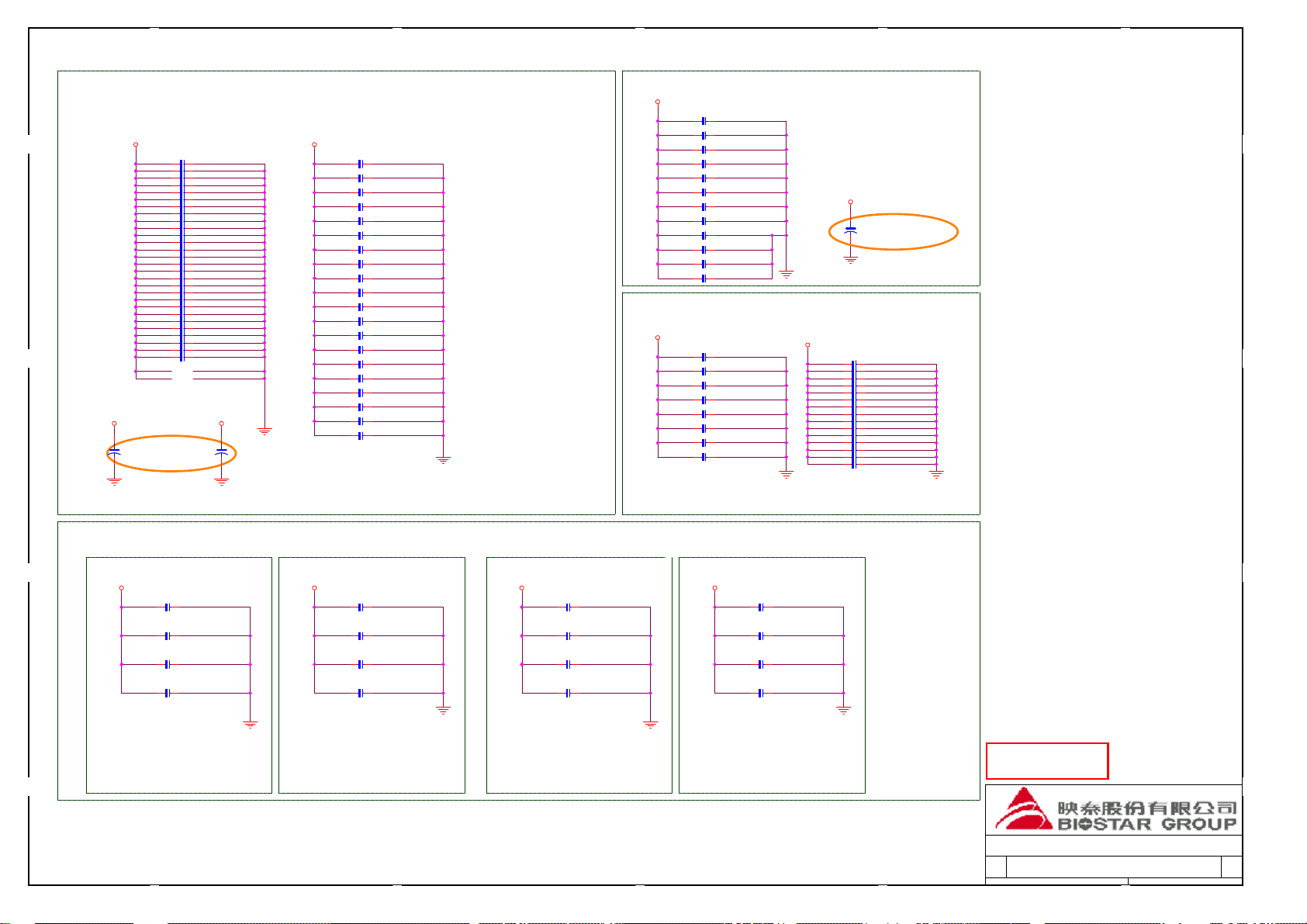

5V

+/-5%

5

12V

3.3V

+/-5%

+/-5%

+3.3V _RUN 2.5V SHUNT

ATX P/S WITH 1A STBY CURRENT

5VSB

+/-5%

-12V

+/-5%

APU

PW

12V

+/-5%

APUVRM_ATX12V

D D

+12V_RUN +12V +12V

+5V_RUN VCC 1.1V SW

+5V_SB

+5V_RUN

+3.3V_RUN

+3.3VSB

REGULATOR

ACPI CONTROLLER

C C

+3.3V_RUN +1.8V_RUN

+3.3V_RUN

uPI7701UB

1.8V LDO

B B

4 3

ISL6539

REGULATOR

+3.3V_ALW(S0,S1,S3,S4,S5)

+5V_ALW(S0,S1,S3,S4,S5)

+3.3V_ALW

APU_VDDIO_SUS APU_VTT_SUS DDR III DIMM

REGULATOR

+3.3V_ALW +3.3V_ALW

+5V_ALW 1.1V LDO

+3.3V_ALW

+3.3V_ALW

+5V_ALW

REGULATOR

0.75V Divider

1/2 vddio

AOZ1024DI

1.5V Switcher

2

+2.5V APU_VDDA_RUN(S0,S1)

VRM L6717A

REGULATOR

ISL6539

REGULATOR

+1.1V_RUN(S0,S1)

+1.5V_ALW

+5V_ALW Not enabled

APU_VDD_RUN

APU_VDDNB_RUN

+12V

UP7704U8

Si2301DS

Pch MOSFET

UP7704U8

1.2V LDO

APU_VTT_SUS 2A

0.001R_1W

+1.1V_ALW

+1.5V_RUN

+1.2V_ALW

APU_VDD_RUN(S0,S1)

APU_VDDNB_RUN(S0,S1)

APU_VDDIO_SUS(S0,S1,S3)

APU_VDDP_RUN(S0,S1,)

SEPARATR VDDP PW

0.001R_1W

APU_VDDR_RUN(S0,S1,)

SEPARATR VDDR PW

+3.3V_RUN

+3.3V_RUN

+1.1V_RUN

+1.1V_RUN

+1.1V_RUN

+1.1V_RUN

+1.1V_RUN

+1.1V_RUN

+1.1V_ALW

+3.3V_ALW

+1.1V_ALW

+3.3V_ALW

+1.1V_ALW

+3.3V_ALW

+3.3V_ALW

+3.3V_ALW

+1.1V_ALW

1

APU FM1

VDDA 2.5V(1.8-2.7V) 0.5A

VDD CORE 0.8V-2.0V /120A

VDDNB 1.2V /20A

DDR III MEM I/F

VDDIO 0.8-2.3V 30A

DDRP

1.2V 5A

DDRR

1.2V 5A

FCH HUDSON-D2

VDDPL_11_DAC 20mA

VDDIO_33_PCIGP 300mA

VDDAN_11_ML 100mA

VDDPL_33_*_RUN 320mA

VDDCR_11 500mA

VDDAN_11_SATA 700mA

VDDAN_11_CLK 400mA

VDDAN_11_PCIE 900mA

VDDCR/AN_11_SUSB_S 500mA

VDDPL_33_*_ALW 34mA

VDDIO_33_GBE_S 1mA

VDDCR/AN_11_USB_S 52mA

VDDIO_GBE_S 200mA

VDDCR_11_GBE_S 100mA

VDDAN_33_USB_S 130mA

VDDXL_33_S 6mA

VDDIO_33_S 30mA

VDDCR_11_S 100mA

PCI SLOT

5V 5A

3.3V 7.6A

3.3Vaux 0.375A

12V 0.5A

-12V 0.1A

X1 PCIE per

+3.3V 3.0A

3.3Vaux 0.1A

12V 0.5A

X16 PCIE

3.3V 3.0A

12V 5.5A

X8 PCIE

3.3V 3.0A

12V 5.5A

X4 PCIE

+3.3V 3.0A

3.3Vaux 0.1A

12V 0.5A

5V LDO U2101

+5V

5V_DUAL

3A

USB2.0 X6 RLUSB2.0 X10 RL

+5V

5V_DUAL

3A

Default

GIGABIT PHY

+3.3V 271mA

ESATA REDRIVER

+1.8V_RUN

276mA

MINI PCIE SLOT

+3.3V_DUAL 2.75A

+1.5V 0.5A

AZALIA CODEC CON

3.3V VDDIO

3.3V CORE 0.3A

5V ANALOG 0.1A

A

+3.3V_ALW

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

POWER DELIVERY

POWER DELIVERY

POWER DELIVERY

AA55C-A1S

AA55C-A1S

AA55C-A1S

3 45Friday, July 29, 2011

3 45Friday, July 29, 2011

3 45Friday, July 29, 2011

6.0

6.0

6.0

it

5

DCCBBAA

4 3

2

1

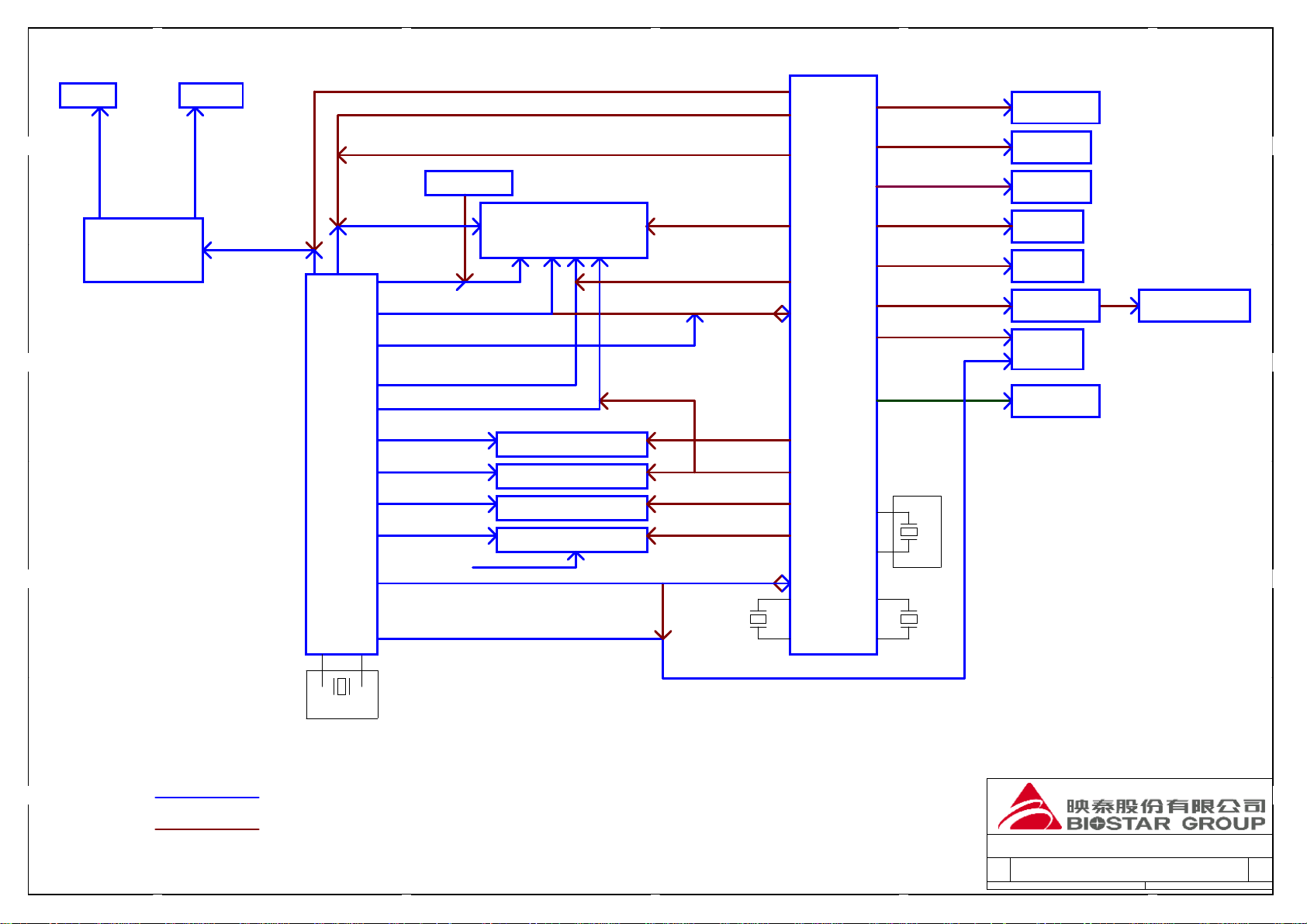

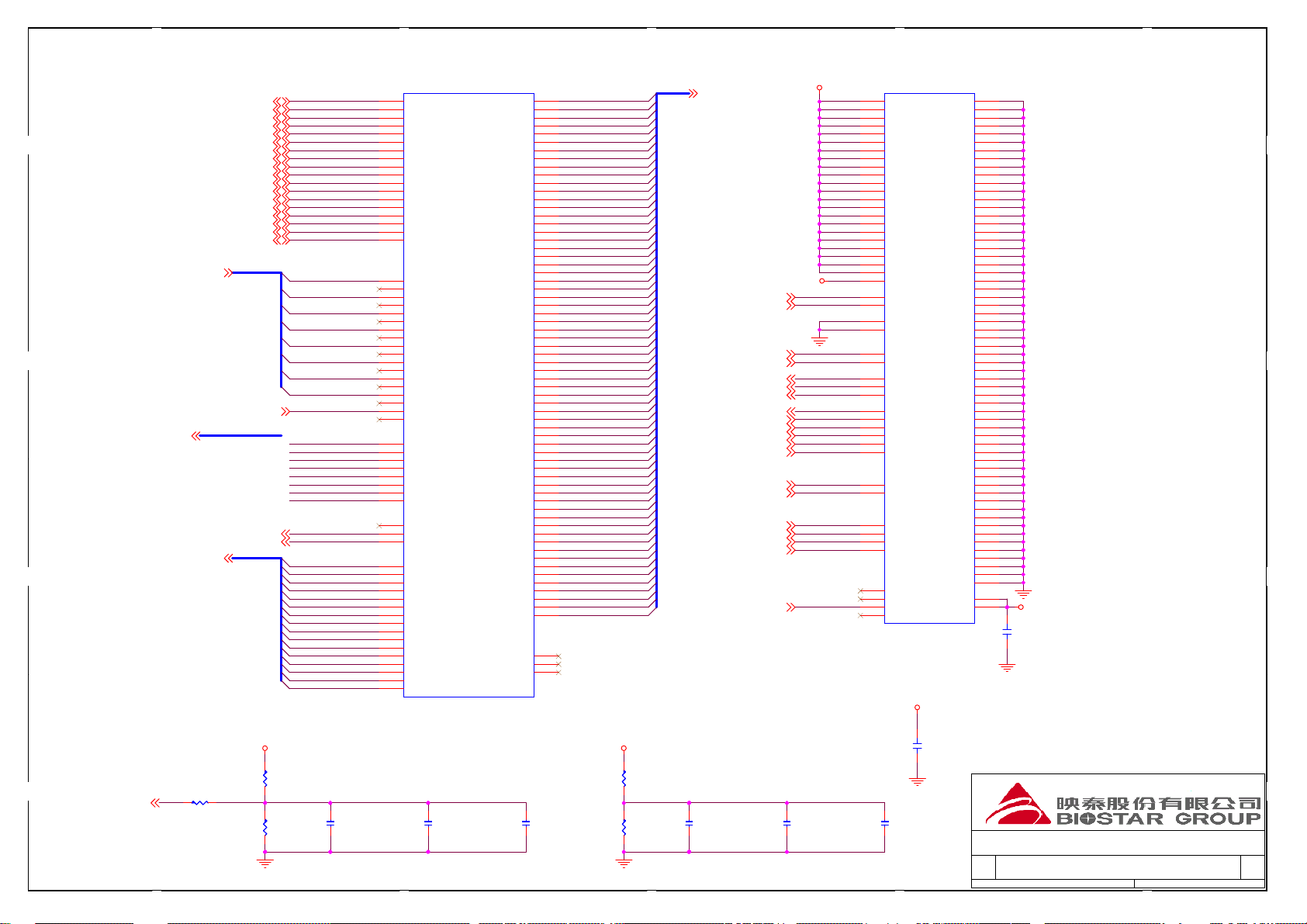

1 PAIR CPU CLK

DIMM1

DIMM2

D

200MHZ

HT ref clock

100MHZ DIFF(RX780/RS780)

HT REFCLK

66MHz SE(RS740)

14.318MHZ OSC

3 PAIR MEM CLK

3 PAIR MEM CLK

AM3/AM2g2 CPU

AM3 SOCKET

3 PAIR MEM CLK

3 PAIR MEM CLK

1 PAIR CPU CLK

200MHZ

HT REFCLK

66MHz SE(RS740)

100MHz

DIFF(RX780/RS780)

EXTERNAL

CLK GEN.

(RS740/RX780)

NB-OSCIN

14.318MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

NB GFX PCIE CLK

100MHZ

NB GPP PCIE CLK

100MHZ

PCIE GFX CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

USB CLK

48MHZ

(RX780)

25MHZ OSC INPUT

AMD NB

RS780

PCIE GFX SLOT 1 - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 4 LANES

PCIE GBE

NB PCIE Ref clock

100MHZ

NB Disp clock

100MHZ DIFF(RS780)

GPP Ref clock

100MHZ

GFX Ref clock

100MHZ

GPP Ref clock

100MHZ

GPP Ref clock

100MHZ

GPP Ref clock

100MHZ

25MHz

SATA

CPU_HT_CLK

NB_HT_CLK

25M_48M_66M_OSC

AMD SB

SB700

NB_DISP_CLK

GPP_CLK3

PCIE_RCLK/

NB_LNK_CLK

SLT_GFX_CLK

GPP_CLK0

GPP_CLK1

GPP_CLK2

USB_CLK

SB_BITCLK

48MHZ

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK2

33MHZ

LPC_CLK0

33MHZ

LPC CLK1

33MHZ

PCI CLK3

33MHZ

PCI CLK4

33MHZ

25MHz

PCI SLOT 0

PCI SLOT 1

PCI SLOT 2

TPM

LPC BIOS

DEBUG POST

SUPER IO

IT8728

HD AUDIO CON

TPM (BCM5755/5761)

SIO CLK

48MHZ

32.768KHz

External clock mode

Internal clock mode

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

AA55C-A1S

AA55C-A1S

AA55C-A1S

4 45Friday, July 29, 2011

4 45Friday, July 29, 2011

4 45Friday, July 29, 2011

6.0

6.0

6.0

it

A

V0.60:

5

Base on Standard circuit.

Ver0.61:

1.Gigabit LAN From APU_GPP3 to GPP2;

4 3

ECN:

2011-07-26:

PEX16-2

From PCIEX16-164 PIN-B to PCIEX16-164 PIN-R.

2

1

2.del STAT3,USB 3.0 SILKSCREEN.

3.add GR23/GR25 FOR matching DVI MONITOR.

D D

4.change YR7 for detect APU_VDDNB_RUN.

5.change GR7/GR8 from 4.7K to 5.1k.

6.add YR50,YR152:0/NI for PME Function,

7.R3: From 1.1k to 1k 1% FOR +1.1V_ALW.

8.add EC20 FOR PCI_AD31.

2011-07-26 pm:

MOSFETHEATSINK

20-120-105300H1 MOSHS-AA75B

MOS

汃

/?伎 /105.3x30.7x22.3mm/(0288-0175F)/(HF)/.KG

-----> 20-120-981500H11 MOSHS-A88PC

MOS

汃

98.26x15.5x18mm/?伎/

邐蹬

/

糯

/H1-NB384-HS01/.

杻

9.REAR USB3.0 USE USB2.0 FUNCTION.

10.+1.1V_RUN use VIN4 instead of VIN6.

11.add SC21---->NI for Measuring T14.

12.JFRONT_USB3_1---->NI,parts circuit NI.

13.R79/R80/R81/Q121/Q122/C118

---->NI FOR PWRGD_PS control SB_PWRGD.

14.PWM compaesation R/C network change for ST6717A

15.MEMORY Voltage default from 1.55 to 1.6V.

C C

change MR17/MR18,MR22/MR23/MR24.

16.change EUPR5 From 4.7k to 10k. for prevent drop.

Ver6.0:

1.REAR USB3.0 location:USB1.

2.SR12:PU from 3.3V_STBY to 3.3V_DUAL,

3.remove CIR Header.

4.ADD R82 PU to +3.3V_DUAL

5.ADD PCT13/PCT14 FOR APU_VDDNB_RUN.

B B

6. LOCATION change:

DIMM_A0--->DIMM_A1,DIMM_A1--->DIMM_A2,

DIMM_B0--->DIMM_B1,DIMM_B1--->DIMM_B2,

7.all RN---->Single Resitor.

V6.0 EMI SOLUTION:

1.ADD SC22 :FOR CLK_48M_SIO

2.ADD SC28:close to SFB1.

3.ADD CC83/CC86:

4.ADD SC29: FOR -XRI1 SWAP LAYERS

5. ADD YC87/YC88/YC89:FCH_VGA_R/G/B

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

REVISION HISTORY

REVISION HISTORY

REVISION HISTORY

AA55C-A1S

AA55C-A1S

AA55C-A1S

5 45Friday, July 29, 2011

5 45Friday, July 29, 2011

5 45Friday, July 29, 2011

6.0

6.0

6.0

i

A

CPU1H

<APU>

<APU>

CPU1H

PCI EXPRESS

PCI EXPRESS

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

GPP GRAPHICS

GPP GRAPHICS

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

UMI_LINK

UMI_LINK

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

2

GFX_TX0PP

AE2

AE1

GFX_TX1PP

AE4

GFX_TX1NN

AE5

GFX_TX2PP

AD2

AD3

GFX_TX3PP

AC2

GFX_TX3NN

AC1

GFX_TX4PP

AC4

GFX_TX4NN

AC5

GFX_TX5PP

AB2

AB3

GFX_TX6PP

AA2

AA1

GFX_TX7PP

AA4

GFX_TX7NN

AA5

GFX_TX8PP

Y2

Y3

GFX_TX9PP

W2

W1

GFX_TX10PP

W4

W5

GFX_TX11PP

V2

GFX_TX11NN

V3

GFX_TX12PP

U2

GFX_TX12NN

U1

GFX_TX13PP

U4

GFX_TX13NN

U5

GFX_TX14PP

T2

T3

GFX_TX15PP

R2

GFX_TX15NN

R1

AH2

P_GPP_TX0N

AH3

P_GPP_TX1P

AG2

P_GPP_TX1N

AG1

P_GPP_TX2P

AG4

P_GPP_TX2N GPP_APU_GBE_TX2N

AG5

AF2

AF3

P_UMI_TX0P

AK8

AK9

P_UMI_TX1P

AL7

P_UMI_TX1N

AL8

P_UMI_TX2P

AK5

P_UMI_TX2N

AK6

P_UMI_TX3P

AJ7

AJ8

J6

CC1 0.1UF 16V X7R 0402CC1 0.1UF 16V X7R 0402

CC3 0.1UF 16V X7R 0402CC3 0.1UF 16V X7R 0402

CC5 0.1UF 16V X7R 0402CC5 0.1UF 16V X7R 0402

CC7 0.1UF 16V X7R 0402CC7 0.1UF 16V X7R 0402

CC9 0.1UF 16V X7R 0402CC9 0.1UF 16V X7R 0402

CC110.1UF 16V X7R 0402CC110.1UF 16V X7R 0402

CC130.1UF 16V X7R 0402CC130.1UF 16V X7R 0402

CC150.1UF 16V X7R 0402CC150.1UF 16V X7R 0402

CC170.1UF 16V X7R 0402CC170.1UF 16V X7R 0402

CC190.1UF 16V X7R 0402CC190.1UF 16V X7R 0402

CC210.1UF 16V X7R 0402CC210.1UF 16V X7R 0402

CC230.1UF 16V X7R 0402CC230.1UF 16V X7R 0402

CC250.1UF 16V X7R 0402CC250.1UF 16V X7R 0402

CC270.1UF 16V X7R 0402CC270.1UF 16V X7R 0402

CC290.1UF 16V X7R 0402CC290.1UF 16V X7R 0402

CC310.1UF 16V X7R 0402CC310.1UF 16V X7R 0402

CC124 0.1UF 16V X7R 0402CC124 0.1UF 16V X7R 0402

CC126 0.1UF 16V X7R 0402CC126 0.1UF 16V X7R 0402

CC130 0.1UF 16V X7R 0402CC130 0.1UF 16V X7R 0402

CC330.1UF 16V X7R 0402CC330.1UF 16V X7R 0402

CC350.1UF 16V X7R 0402CC350.1UF 16V X7R 0402

CC370.1UF 16V X7R 0402CC370.1UF 16V X7R 0402

CC390.1UF 16V X7R 0402CC390.1UF 16V X7R 0402

CR2 196 1% 0402CR2 196 1% 0402

CC2 0.1UF 16V X7R 0402CC2 0.1UF 16V X7R 0402

CC4 0.1UF 16V X7R 0402CC4 0.1UF 16V X7R 0402

CC6 0.1UF 16V X7R 0402CC6 0.1UF 16V X7R 0402

CC8 0.1UF 16V X7R 0402CC8 0.1UF 16V X7R 0402

CC10 0.1UF 16V X7R 0402CC10 0.1UF 16V X7R 0402

CC12 0.1UF 16V X7R 0402CC12 0.1UF 16V X7R 0402

CC14 0.1UF 16V X7R 0402CC14 0.1UF 16V X7R 0402

CC16 0.1UF 16V X7R 0402CC16 0.1UF 16V X7R 0402

CC18 0.1UF 16V X7R 0402CC18 0.1UF 16V X7R 0402

CC20 0.1UF 16V X7R 0402CC20 0.1UF 16V X7R 0402

CC22 0.1UF 16V X7R 0402CC22 0.1UF 16V X7R 0402

CC24 0.1UF 16V X7R 0402CC24 0.1UF 16V X7R 0402

CC26 0.1UF 16V X7R 0402CC26 0.1UF 16V X7R 0402

CC28 0.1UF 16V X7R 0402CC28 0.1UF 16V X7R 0402

CC30 0.1UF 16V X7R 0402CC30 0.1UF 16V X7R 0402

CC32 0.1UF 16V X7R 0402CC32 0.1UF 16V X7R 0402

CC125 0.1UF 16V X7R 0402CC125 0.1UF 16V X7R 0402

CC127 0.1UF 16V X7R 0402CC127 0.1UF 16V X7R 0402

CC131 0.1UF 16V X7R 0402CC131 0.1UF 16V X7R 0402

Modify:2011-06-01,V0.61.

CC34 0.1UF 16V X7R 0402CC34 0.1UF 16V X7R 0402

CC36 0.1UF 16V X7R 0402CC36 0.1UF 16V X7R 0402

CC38 0.1UF 16V X7R 0402CC38 0.1UF 16V X7R 0402

CC40 0.1UF 16V X7R 0402CC40 0.1UF 16V X7R 0402

GFX_TX0P

GFX_TX0NGFX_TX0NN

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2NGFX_TX2NN

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5NGFX_TX5NN

GFX_TX6P

GFX_TX6NGFX_TX6NN

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8NGFX_TX8NN

GFX_TX9P

GFX_TX9NGFX_TX9NN

GFX_TX10P

GFX_TX10NGFX_TX10NN

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14NGFX_TX14NN

GFX_TX15P

GFX_TX15N

GPP_APU_TX0PP_GPP_TX0P

GPP_APU_TX0N

GPP_APU_TX1P

GPP_APU_TX1N

GPP_APU_GBE_TX2P

UMI_APU_FCH_TX0PUMI_FCH_APU_RX0P

UMI_APU_FCH_TX0NP_UMI_TX0N

UMI_APU_FCH_TX1P

UMI_APU_FCH_TX1N

UMI_APU_FCH_TX2P

UMI_APU_FCH_TX2N

UMI_APU_FCH_TX3P

UMI_APU_FCH_TX3NP_UMI_TX3N

GFX_TX0P27

GFX_TX0N27

GFX_TX1P27

GFX_TX1N27

GFX_TX2P27

GFX_TX2N27

GFX_TX3P27

GFX_TX3N27

GFX_TX4P27

GFX_TX4N27

GFX_TX5P27

GFX_TX5N27

GFX_TX6P27

GFX_TX6N27

GFX_TX7P27

GFX_TX7N27

GFX_TX8P27

GFX_TX8N27

GFX_TX9P27

GFX_TX9N27

GFX_TX10P27

GFX_TX10N27

GFX_TX11P27

GFX_TX11N27

GFX_TX12P27

GFX_TX12N27

GFX_TX13P27

GFX_TX13N27

GFX_TX14P27

GFX_TX14N27

GFX_TX15P27

GFX_TX15N27

GPP_APU_TX0P29

GPP_APU_TX0N29

GPP_APU_TX1P29

GPP_APU_TX1N29

GPP_APU_GBE_TX2P44

GPP_APU_GBE_TX2N44

UMI_APU_FCH_TX0P 21

UMI_APU_FCH_TX0N 21

UMI_APU_FCH_TX1P 21

UMI_APU_FCH_TX1N 21

UMI_APU_FCH_TX2P 21

UMI_APU_FCH_TX2N 21

UMI_APU_FCH_TX3P 21

UMI_APU_FCH_TX3N 21

1

Modify:2011-06-01;V0.61.

From GPP3 to GPP2 for IRQ Interrupt ,

Due to LAN ghost issue,

Giga LAN controller and PCIe x1 slot

avoid to route to INTD#.

5

GFX_RX0P27

GFX_RX0N27

GFX_RX1P27

GFX_RX1N27

PEX16

D D

GPP_APU_RX0/TX0 :PEX1_1.

GPP_APU_RX1/TX1 :PEX1_2.

GPP_APU_GBE_RX2/TX2:Gigabit LAN.

C C

UMI

GFX_RX2P27

GFX_RX2N27

GFX_RX3P27

GFX_RX3N27

GFX_RX4P27

GFX_RX4N27

GFX_RX5P27

GFX_RX5N27

GFX_RX6P27

GFX_RX6N27

GFX_RX7P27

GFX_RX7N27

GFX_RX8P27

GFX_RX8N27

GFX_RX9P27

GFX_RX9N27

GFX_RX10P27

GFX_RX10N27

GFX_RX11P27

GFX_RX11N27

GFX_RX12P27

GFX_RX12N27

GFX_RX13P27

GFX_RX13N27

GFX_RX14P27

GFX_RX14N27

GFX_RX15P27

GFX_RX15N27

GPP_APU_RX0P29

GPP_APU_RX0N29

GPP_APU_RX1P29

GPP_APU_RX1N29

GPP_APU_GBE_RX2P44

GPP_APU_GBE_RX2N44

UMI_FCH_APU_RX0P21

UMI_FCH_APU_RX0N21

UMI_FCH_APU_RX1P21

UMI_FCH_APU_RX1N21

UMI_FCH_APU_RX2P21

UMI_FCH_APU_RX2N21

UMI_FCH_APU_RX3P21

UMI_FCH_APU_RX3N21

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_APU_RX0P

GPP_APU_RX0N

GPP_APU_RX1P

GPP_APU_RX1N

GPP_APU_GBE_RX2P

GPP_APU_GBE_RX2N

Modify:2011-06-01,V0.61.

UMI_FCH_APU_RX0N

UMI_FCH_APU_RX1P

UMI_FCH_APU_RX1N

UMI_FCH_APU_RX2P

UMI_FCH_APU_RX2N

UMI_FCH_APU_RX3P

UMI_FCH_APU_RX3N

APU_VDDP_B_RUN

4 3

AF8

P_GFX_RXP0

AF9

P_GFX_RXN0

AE7

P_GFX_RXP1

AE8

P_GFX_RXN1

AD5

P_GFX_RXP2

AD6

P_GFX_RXN2

AD8

P_GFX_RXP3

AD9

P_GFX_RXN3

AC7

P_GFX_RXP4

AC8

P_GFX_RXN4

AB5

P_GFX_RXP5

AB6

P_GFX_RXN5

AB8

P_GFX_RXP6

AB9

P_GFX_RXN6

AA7

P_GFX_RXP7

AA8

P_GFX_RXN7

Y5

P_GFX_RXP8

Y6

P_GFX_RXN8

Y8

P_GFX_RXP9

Y9

P_GFX_RXN9

W7

P_GFX_RXP10

W8

P_GFX_RXN10

V5

P_GFX_RXP11

V6

P_GFX_RXN11

V8

P_GFX_RXP12

V9

P_GFX_RXN12

U7

P_GFX_RXP13

U8

P_GFX_RXN13

T5

P_GFX_RXP14

T6

P_GFX_RXN14

T8

P_GFX_RXP15

T9

P_GFX_RXN15

AH5

P_GPP_RXP0

AH6

P_GPP_RXN0

AH8

P_GPP_RXP1

AH9

P_GPP_RXN1

AG7

P_GPP_RXP2

AG8

P_GPP_RXN2

AF5

P_GPP_RXP3

AF6

P_GPP_RXN3

AL5

P_UMI_RXP0

AL4

P_UMI_RXN0

AK3

P_UMI_RXP1

AK2

P_UMI_RXN1

AJ2

P_UMI_RXP2

AJ1

P_UMI_RXN2

AJ4

P_UMI_RXP3

AJ5

APU_PCIE_P_ZVDD APU_PCIE_P_ZVSS

CR1

CR1

196 1% 0402

196 1% 0402

P_UMI_RXN3

J7

P_ZVDDP

Place Within 1.5"from APU Place Within 1.5"from APU

196 OHM for DG requried 196 OHM for DG requried

B B

?

?

Title

Title

BIOSTAR STANDARD

NO:2011_AMD_FM1_01

2011-03-21

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

FM1 CPU HT

FM1 CPU HT

FM1 CPU HT

AA55C-A1S

AA55C-A1S

AA55C-A1S

6 45Friday, July 29, 2011

6 45Friday, July 29, 2011

6 45Friday, July 29, 2011

it

A

6.0

6.0

6.0

DCCBBAA

APU_VDD_RUN

5

For DVI/HDMI

CC86

CC86

CC83

CC83

0.01UF 25V X7R 0402

0.01UF 25V X7R 0402

APU_SIC

APU_SID

APU_SVC

APU_SVD

APU_VDDIO_SUS

D

0.01UF 25V X7R 0402

0.01UF 25V X7R 0402

FOR EMI

Modify:2011-06-28,V0.61.

CR49 1K 0402CR49 1K 0402

CR50 1K 0402CR50 1K 0402

CR51 1K 0402CR51 1K 0402

CR52 1K 0402CR52 1K 0402

For VGA

PLACE R3 TO CPU PIN LESS THAN 600MIL

APU_CLKP21

APU_CLKN21

PLACE R1 & R2 TO CPU PIN LESS THAN 1250MIL

APU_VDDIO_SUS

CR53 330 0402CR53 330 0402

CR54 330 0402CR54 330 0402

CR55 330 0402CR55 330 0402

CR56 330 0402CR56 330 0402

APU_VDDIO_SUS

CR58 1K 0402CR58 1K 0402

CR59 1K 0402CR59 1K 0402

CR60 1K 0402CR60 1K 0402

CR57 1K 0402CR57 1K 0402

CR32

CR32

10K 0402

10K 0402

APU_THERMTRIP#_B

APU_THERMTRIP#_VDDIO

APU_VDDIO_SUS +3.3V_DUAL

CR34

CR34

10K 0402 /NI

10K 0402 /NI

APU_ALERT#_VDDIO_B

APU_ALERT#_VDDIO

CR36

CR36

330 1% 0402

330 1% 0402

HTCPU_PWRGD_G

APU_VDDIO_PG21

FCH_APU_RST#

APU_VDDIO_PG

APU_PROCHOT#_VDDIO

APU_DBREQ#

APU_THERMTRIP#_VDDIO

APU_ALERT#_VDDIO

APU_TRST#

APU_DBRDY

APU_VDDNB_FB_H41

APU_VDD_FB_H41

APU_VDD_FB_L41

APU_VDDNB_FB_L41

CQ1

CQ1

2N3904 SOT23

2N3904 SOT23

B

E

Modify:2011-06-30;V6.0

NI:CQ2.,CR34,CR35

CQ2

CQ2

2N3904 SOT23 /NI

2N3904 SOT23 /NI

B

E

CQ3

CQ3

2N3904 SOT23

2N3904 SOT23

B

E

it

4 3

APU_THERMTRIP: X-X-XX

DP0_TX0P_APU18

DP0_TX0N_APU18

DP0_TX1P_APU18

DP0_TX1N_APU18

DP0_TX2P_APU18

DP0_TX2N_APU18

DP0_TX3P_APU18

DP0_TX3N_APU18

DP1_TX0P23

DP1_TX0N23

DP1_TX1P23

DP1_TX1N23

DP1_TX2P23

DP1_TX2N23

DP1_TX3P23

DP1_TX3N23

CR29 0 0402CR29 0 0402

CR30 0 0402CR30 0 0402

+3.3V_DUALAPU_VDDIO_SUS

R1

CR6 0 0402CR6 0 0402

R2

CR8 0 0402CR8 0 0402

APU_PROCHOT#_VDDIO21

CC43 0.1UF 16V X7R 0402 /NICC43 0.1UF 16V X7R 0402 /NI

CC44 0.1UF 16V X7R 0402 /NICC44 0.1UF 16V X7R 0402 /NI

CC45 0.1UF 16V X7R 0402 /NICC45 0.1UF 16V X7R 0402 /NI

CC41 0.1UF 16V X7R 0402 /NICC41 0.1UF 16V X7R 0402 /NI

CC46 0.1UF 16V X7R 0402 /NICC46 0.1UF 16V X7R 0402 /NI

CC47 0.1UF 16V X7R 0402 /NICC47 0.1UF 16V X7R 0402 /NI

CC48 0.1UF 16V X7R 0402 /NICC48 0.1UF 16V X7R 0402 /NI

CC50 0.1UF 16V X7R 0402 /NICC50 0.1UF 16V X7R 0402 /NI

CC42 0.1UF 16V X7R 0402CC42 0.1UF 16V X7R 0402

CC52 0.1UF 16V X7R 0402CC52 0.1UF 16V X7R 0402

CC53 0.1UF 16V X7R 0402CC53 0.1UF 16V X7R 0402

CC54 0.1UF 16V X7R 0402CC54 0.1UF 16V X7R 0402

CC55 0.1UF 16V X7R 0402CC55 0.1UF 16V X7R 0402

CC56 0.1UF 16V X7R 0402CC56 0.1UF 16V X7R 0402

CC57 0.1UF 16V X7R 0402CC57 0.1UF 16V X7R 0402

CC58 0.1UF 16V X7R 0402CC58 0.1UF 16V X7R 0402

CR7 169 1% 0402 /NICR7 169 1% 0402 /NI

APU_DISP_CLKP21

APU_DISP_CLKN21

APU_SVC41

APU_SVD41

APU_SIC33

APU_SID33

FCH_APU_RST#17,21,40

APU_VDDIO_PG21

APU_TDI17

APU_TDO17

APU_TCK17

APU_TMS17

APUVDDPFB1APUVDDPFB1

APUVDDIOFB1APUVDDIOFB1

APUVDDRFB1APUVDDRFB1

R3

APU_THERMTRIP#: 10-4-10

CR33

CR33

10K 0402

10K 0402

C

APU_THERMTRIP# 22

VGA HPD CONTROL

DP0_TX0P

DP0_TX0N

DP0_TX1P

DP0_TX1N

DP0_TX2P

DP0_TX2N

DP0_TX3P

DP0_TX3N

DP1_TX0P_APU

DP1_TX0N_APU

DP1_TX1P_APU

DP1_TX1N_APU

DP1_TX2P_APU

DP1_TX2N_APU

DP1_TX3P_APU

DP1_TX3N_APU

APU_CLKIN_P

APU_CLKIN_N

APU_SVC

APU_SVD

APU_SIC

APU_SID

FCH_APU_RST#

APU_VDDIO_PG

APU_PROCHOT#_VDDIO

APU_THERMTRIP#_VDDIO

APU_ALERT#_VDDIO

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

APU_VDDP_FB_H

APU_VDDIO_FB_H

APU_VDDR_FB_H

VSS_SENSE

M2

DP0_TXP0

M3

DP0_TXN0

L2

DP0_TXP1

L1

DP0_TXN1

L4

DP0_TXP2

L5

DP0_TXN2

K2

DP0_TXP3

K3

DP0_TXN3

R4

DP1_TXP0

R5

DP1_TXN0

P2

DP1_TXP1

P3

DP1_TXN1

N2

DP1_TXP2

N1

DP1_TXN2

N4

DP1_TXP3

N5

DP1_TXN3

AL12

CLKIN_H

AK12

CLKIN_L

AH12

DISP_CLKIN_H

AG12

DISP_CLKIN_L

A8

SVC

B8

SVD

AF10

SIC

AG10

SID

AJ13

RESET_L

AG11

PWROK

AL14

PROCHOT_L

AK14

THERMTRIP_L

AD10

ALERT_L

E9

TDI

G10

TDO

E8

TCK

D8

TMS

F10

TRST_L

D7

DBRDY

F8

DBREQ_L

E11

RSVD_1

H9

RSVD_2

K23

RSVD_3

K25

RSVD_4

AF13

RSVD_5

B5

VDDP_SENSE

A6

VDDNB_SENSE

B6

VDDIO_SENSE

C7

VDD_SENSE

A5

VDDR_SENSE

C6

VSS_SENSE

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

APU_VDDIO_SUS

CPU1C

CPU1C

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DISPLAY

PORT 0

DISPLAY

PORT 0

DISPLAY

PORT 1

DISPLAY

PORT 1

CLK

CLK

SER.

SER.

CTRL

CTRL

RSVD JTAG

RSVD JTAG

SENSE

SENSE

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DISPLAY PORT

MISC.

DISPLAY PORT

MISC.

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

THERMDA

THERMDC

TEST2

TEST3

TEST6

TEST9

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST

TEST

TEST19

TEST20

TEST21

TEST22

TEST23

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FM1R1

DMAACTIVE_L

DP_AUX_ZVSS

J9

G9

G7

H8

K6

K8

L7

L8

R7

R8

P8

P9

N7

N8

M8

M9

K9

K5

P5

P6

M5

M6

AH14

AG14

AB23

AC24

AG13

D10

C10

F6

D9

C9

B9

A9

E4

F5

D4

D5

E5

F7

E6

AE11

AD11

G5

G6

AD14

AE14

AG31

AE13

AD13

A7

AC12

AF11

CR3 150 1% 0402CR3 150 1% 0402

DP_BLON

DP_DIGON

DP_VARY_BL

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP1_HPD_C

DP2_HPD_C

DP3_HPD_C

DP4_HPD_C

DP5_HPD_C

APU_TEST2_DRAIN2

APU_TEST3_GATE2

APU_TEST6_DIECRACKMON

APU_TEST9_ANALOGIN

APU_TEST10_ANALOGOUT

APU_TEST12_SCANSHIFTEND

APU_TEST14_BP0

APU_TEST15_BP1

APU_TEST16_BP2

APU_TEST17_BP3

APU_TEST18_PLLTEST1

APU_TEST19_PLLTEST0

APU_TEST20_SCANCLK2

APU_TEST21_SCANEN

APU_TEST22_SCANSHIFTEN

APU_TEST23_TSTUPD

APU_TEST24_SCANCLK1

APU_TEST25_H_BYPASSCLK_H

APU_TEST25_L_BYPASSCLK_L

APU_TEST28_H_PLLCHRZ_H

APU_TEST28_L_PLLCHRZ_L

APU_TEST30_H_ANATSTIN_H

APU_TEST30_L_ANATSTIN_L

APU_TEST31_M_TEST

APU_TEST32_H_ANATSTOUT_H

APU_TEST32_L_ANATSTOUT_L

APU_TEST35

FM1R1

FCH_DMA_ACTIVE#VSS_SENSE

DPBLON1DPBLON1

DPDIGON1DPDIGON1

DPVARYBL1DPVARYBL1

DP2AUXP1DP2AUXP1

DP2AUXN1DP2AUXN1

DP3AUXP1DP3AUXP1

DP3AUXN1DP3AUXN1

DP4AUXP1DP4AUXP1

DP4AUXN1DP4AUXN1

DP5AUXP1DP5AUXP1

DP5AUXN1DP5AUXN1

CR31 10K 0402CR31 10K 0402

Modify:2011-06-01,V0.61

2

CC49 0.1UF 16V X7R 0402CC49 0.1UF 16V X7R 0402

CC51 0.1UF 16V X7R 0402CC51 0.1UF 16V X7R 0402

CR9 100K 0402CR9 100K 0402

CR10 100K 0402CR10 100K 0402

CR11 100K 0402CR11 100K 0402

CR12 100K 0402CR12 100K 0402

+3.3V_DUAL

DP0_HPD_C 18

APU_THERMDA 33

APU_THERMDC 33

APUTEST1APUTEST1

APUTEST2APUTEST2

APUTEST3APUTEST3

APUTEST4APUTEST4

APUTEST5APUTEST5

APUTEST6APUTEST6

APUTEST7APUTEST7

APUTEST8APUTEST8

APUTEST9APUTEST9

APUTEST28H1APUTEST28H1

APUTEST28L1APUTEST28L1

APUTEST32H1APUTEST32H1

APUTEST32L1APUTEST32L1

DP0_AUXP_C18

DP0_AUXN_C 18

CR13 0 0402CR13 0 0402

CR14 1K 0402CR14 1K 0402

CR15 1K 0402CR15 1K 0402

CR16 1K 0402CR16 1K 0402

CR17 1K 0402CR17 1K 0402

CR18 1K 0402CR18 1K 0402

CR19 1K 0402CR19 1K 0402

CR20 1K 0402CR20 1K 0402

CR21 511 1% 0402CR21 511 1% 0402

CR22 511 1% 0402CR22 511 1% 0402

CR23 39.2 1% 0402 /NICR23 39.2 1% 0402 /NI

CR24 39.2 1% 0402 /NICR24 39.2 1% 0402 /NI

CR25 39.2 1% 0402CR25 39.2 1% 0402

CR26 300 0402 /NICR26 300 0402 /NI

CR27 300 0402CR27 300 0402

CR28 1K 0402CR28 1K 0402

FM1R1 40

FCH_DMA_ACTIVE# 21

+3.3V

CR5

CR5

100K 0402

100K 0402

CR4

CR4

100K 0402

100K 0402

DP1_AUXP_C23

DP1_AUXN_C 23

APU_VDDP_RUN

APU_VDDIO_SUS

1

add CR61---> NI

CQ5

CR35

CR35

10K 0402 /NI

10K 0402 /NI

C

+3.3VAPU_VDDIO_SUS

C

CR37

CR37

10K 0402 /NI

10K 0402 /NI

PWM_PWROK41

TALERT#23

ML_VGA_HPD23

CR48 10K 0402 /NICR48 10K 0402 /NI

CQ5

2N3904 SOT23 /NI

2N3904 SOT23 /NI

ECB

DP1_HPD_C

CR47

CR47

1K 0402

1K 0402

CR61

CR61

1K 0402 /NI

1K 0402 /NI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

FM1 CPU MISC

FM1 CPU MISC

FM1 CPU MISC

AA55C-A1S

AA55C-A1S

AA55C-A1S

7 45Friday, July 29, 2011

7 45Friday, July 29, 2011

7 45Friday, July 29, 2011

6.0

6.0

6.0

5

MEM_MA_ADD[15..0]13,15

D D

MEM_MA_DM[7..0]13,15

FOR ECC

C C

FOR ECC

B B

APU_VDDIO_SUS

CR38

CR38

1K 0402

1K 0402

MEM_MA_EVENT_L13,15

APU_VDDIO_SUS

CR39

CR39

1K 1% 0402

OV_VDDIOVTT_CPU38

A A

CR41 0 0402 /NICR41 0 0402 /NI

1K 1% 0402

CR42

CR42

1K 1% 0402

1K 1% 0402

4

MEM_MA_BANK013,15

MEM_MA_BANK113,15

MEM_MA_BANK213,15

MEM_MA_DM813,15

MEM_MA_DQS_H013,15

MEM_MA_DQS_L013,15

MEM_MA_DQS_H113,15

MEM_MA_DQS_L113,15

MEM_MA_DQS_H213,15

MEM_MA_DQS_L213,15

MEM_MA_DQS_H313,15

MEM_MA_DQS_L313,15

MEM_MA_DQS_H413,15

MEM_MA_DQS_L413,15

MEM_MA_DQS_H513,15

MEM_MA_DQS_L513,15

MEM_MA_DQS_H613,15

MEM_MA_DQS_L613,15

MEM_MA_DQS_H713,15

MEM_MA_DQS_L713,15

MEM_MA_DQS_H813,15

MEM_MA_DQS_L813,15

MEM_MA0_CLK_H015

MEM_MA0_CLK_L015

MEM_MA0_CLK_H113

MEM_MA0_CLK_L113

MEM_MA0_CLK_H213

MEM_MA0_CLK_L213

MEM_MA0_CLK_H315

MEM_MA0_CLK_L315

MEM_MA0_ODT013

MEM_MA0_ODT113

MEM_MA1_ODT015

MEM_MA1_ODT115

MEM_MA0_CS_L013

MEM_MA0_CS_L113

MEM_MA1_CS_L015

MEM_MA1_CS_L115

MEM_MA_RAS_L13,15

MEM_MA_CAS_L13,15

MEM_MA_WE_L13,15

MEM_MA_RESET_L13,15

APU_VDDIO_SUS

Place Within 1.5"from APU

MEM_MA_DM8

MEM_MA_CKE013,15

MEM_MA_CKE113,15

CR40

CR40

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H8

MEM_MA_DQS_L8

APU_M_VREF

M_ZVDDIO

39.2 1% 0402

39.2 1% 0402

V27

P27

R25

P26

R24

P24

P23

N26

N23

M25

V24

N25

M24

Y23

W26

V25

H12

E17

H21

F25

AF29

AE25

AG21

AF17

G29

G13

F13

H17

G17

F21

E21

G26

G25

AE28

AE29

AG24

AG25

AF20

AF21

AE16

AD16

F30

E30

U27

U26

T23

U23

T25

T26

R27

R28

K26

AA24

AC27

AA25

AC26

Y27

AB26

W23

AB25

W25

Y24

Y26

U24

J24

L27

L24

L26

L23

J25

K22

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DM8

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_DQS_H8

MA_DQS_L8

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CLK_H2

MA_CLK_L2

MA_CLK_H3

MA_CLK_L3

MA_CKE0

MA_CKE1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

MA_EVENT_L

M_VREF

M_ZVDDIO

<APU>

<APU>

3

CPU1A

CPU1A

MEMORY CHANNEL A

MEMORY CHANNEL A

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

?

?

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

E12

F12

H14

E15

G11

H11

E14

G14

F16

G16

H18

F19

F15

H15

E18

F18

G20

H20

E23

G23

G19

E20

F22

G22

F24

H24

E27

F27

H23

E24

E26

H26

AD30

AF30

AG27

AF27

AD31

AE31

AG28

AD28

AF26

AD25

AF23

AE23

AD27

AE26

AF24

AD24

AG22

AD21

AE19

AG19

AD22

AE22

AE20

AD19

AG18

AE17

AF15

AG15

AD18

AF18

AG16

AD15

F28

E29

G31

H30

H27

G28

F31

H29

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK4

MEM_MA_CHECK5

MEM_MA_CHECK6

MEM_MA_CHECK7

2

MEM_MA_DATA[63..0] 13,15

FOR ECC

MEM_MA_CHECK[7..0] 13,15

1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FM1 CPU MEMORY-1

FM1 CPU MEMORY-1

FM1 CPU MEMORY-1

AA55C-A1S

AA55C-A1S

AA55C-A1S

8 45Friday, July 29, 2011

8 45Friday, July 29, 2011

8 45Friday, July 29, 2011

1

6.0

6.0

6.0

5

A

MEM_MB_ADD[15..0]14,16

D D

MEM_MB_BANK014,16

MEM_MB_BANK114,16

MEM_MB_DM[7..0]14,16

FOR ECC

C C

FOR ECC

B B

MEM_MB_EVENT_L14,16

APU_VDDIO_SUS

CR43

CR43

1K 0402

1K 0402

MEM_MB_BANK214,16

MEM_MB_DM814,16

MEM_MB_DQS_H014,16

MEM_MB_DQS_L014,16

MEM_MB_DQS_H114,16

MEM_MB_DQS_L114,16

MEM_MB_DQS_H214,16

MEM_MB_DQS_L214,16

MEM_MB_DQS_H314,16

MEM_MB_DQS_L314,16

MEM_MB_DQS_H414,16

MEM_MB_DQS_L414,16

MEM_MB_DQS_H514,16

MEM_MB_DQS_L514,16

MEM_MB_DQS_H614,16

MEM_MB_DQS_L614,16

MEM_MB_DQS_H714,16

MEM_MB_DQS_L714,16

MEM_MB_DQS_H814,16

MEM_MB_DQS_L814,16

MEM_MB0_CLK_H016

MEM_MB0_CLK_L016

MEM_MB0_CLK_H114

MEM_MB0_CLK_L114

MEM_MB0_CLK_H214

MEM_MB0_CLK_L214

MEM_MB0_CLK_H316

MEM_MB0_CLK_L316

MEM_MB_CKE014,16

MEM_MB_CKE114,16

MEM_MB0_ODT014

MEM_MB0_ODT114

MEM_MB1_ODT016

MEM_MB1_ODT116

MEM_MB0_CS_L014

MEM_MB0_CS_L114

MEM_MB1_CS_L016

MEM_MB1_CS_L116

MEM_MB_RAS_L14,16

MEM_MB_CAS_L14,16

MEM_MB_WE_L14,16

MEM_MB_RESET_L14,16

4 3

CPU1B

CPU1B

MEMORY CHANNEL B

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DM8

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H8

MEM_MB_DQS_L8

AB28

AH25

AK21

AH29

AK25

AA30

AC30

AA31

AC29

V31

MB_ADD0

N28

MB_ADD1

P29

MB_ADD2

N29

MB_ADD3

N31

MB_ADD4

M30

MB_ADD5

M31

MB_ADD6

M28

MB_ADD7

M27

MB_ADD8

L30

MB_ADD9

W31

MB_ADD10

L29

MB_ADD11

K28

MB_ADD12

MB_ADD13

K31

MB_ADD14

J31

MB_ADD15

W29

MB_BANK0

V30

MB_BANK1

K29

MB_BANK2

B12

MB_DM0

D16

MB_DM1

B20

MB_DM2

A25

MB_DM3

AL29

MB_DM4

MB_DM5

MB_DM6

AJ17

MB_DM7

D29

MB_DM8

D13

MB_DQS_H0

C13

MB_DQS_L0

A17

MB_DQS_H1

B17

MB_DQS_L1

B21

MB_DQS_H2

C21

MB_DQS_L2

D25

MB_DQS_H3

C25

MB_DQS_L3

AJ29

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

AL25

MB_DQS_L5

AJ20

MB_DQS_H6

AJ21

MB_DQS_L6

AL16

MB_DQS_H7

AL17

MB_DQS_L7

B29

MB_DQS_H8

A29

MB_DQS_L8

U30

MB_CLK_H0

U29

MB_CLK_L0

T29

MB_CLK_H1

T28

MB_CLK_L1

R31

MB_CLK_H2

T31

MB_CLK_L2

P30

MB_CLK_H3

R30

MB_CLK_L3

J30

MB_CKE0

J28

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

Y29

MB0_CS_L0

AB29

MB0_CS_L1

Y30

MB1_CS_L0

AB31

MB1_CS_L1

W28

MB_RAS_L

AA27

MB_CAS_L

AA28

MB_WE_L

J27

MB_RESET_L

V28

MB_EVENT_L

<APU>

<APU>

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

MEMORY CHANNEL B

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

D11

C12

A14

B14

B11

A11

A13

D14

A16

C16

B18

A19

C15

B15

D17

C18

D20

A20

D22

D23

C19

D19

A22

C22

C24

B24

B26

C27

A23

B23

D26

A26

AJ30

AK30

AH28

AJ27

AG30

AH31

AK28

AL28

AJ26

AH26

AH23

AJ23

AK27

AL26

AJ24

AK24

AK22

AH22

AL19

AK19

AL23

AL22

AH20

AL20

AJ18

AH17

AJ15

AK15

AH19

AK18

AK16

AH16

A28

D28

C30

D31

B27

C28

B30

C31

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_CHECK0

MEM_MB_CHECK1

MEM_MB_CHECK2

MEM_MB_CHECK3

MEM_MB_CHECK4

MEM_MB_CHECK5

MEM_MB_CHECK6

MEM_MB_CHECK7

MEM_MB_DATA[63..0] 14,16

FOR ECC

MEM_MB_CHECK[7..0] 14,16

2

1

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

FM1 CPU MEMORY-2

FM1 CPU MEMORY-2

FM1 CPU MEMORY-2

AA55C-A1S

AA55C-A1S

AA55C-A1S

9 45Friday, July 29, 2011

9 45Friday, July 29, 2011

9 45Friday, July 29, 2011

6.0

6.0

6.0

it

5

DCCBBAA

APU_VDD_RUN APU_VDD_RUN

M12

VDD

P12

VDD

H10

VDD

H6

VDD

U19

VDD

J11

VDD

J13

VDD

J15

+5V

CQ4

CQ4

OIA

J17

J19

J21

K10

K12

K14

K16

K18

K20

L11

W19

L15

L17

N19

L21

M10

W13

M16

M18

M20

U21

N11

N21

P10

P20

R11

R21

T10

T12

T20

J5

K4

L3

L6

M1

M4

M7

P1

R3

R6

T1

T4

T7

VDDA_REF

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

R1

R2

D

CC66

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V CR46

CC66

AZ1117H-ADJ SOT-223

AZ1117H-ADJ SOT-223

Vout=Vref (1.25V) X ( 1+R2/R1 )=2.50V

CPU1D

CPU1D

VDD

VDD

APU_VDDA_RUN

CR44

CR44

49.9 1% 0402

49.9 1% 0402

CR46

49.9 1% 0402

49.9 1% 0402

U11

VDD

U13

VDD

V1

VDD

V10

VDD

V12

VDD

V20

VDD

W11

VDD

W21

VDD

W3

VDD

W6

VDD

Y1

VDD

Y10

VDD

Y12

VDD

Y14

VDD

Y16

VDD

Y18

VDD

Y20

VDD

Y4

VDD

Y7

VDD

AA11

VDD

AA13

VDD

AA15

VDD

AA17

VDD

AA19

VDD

AA21

VDD

AB1

VDD

AB10

VDD

R13

VDD

AB14

VDD

AB16

VDD

AB18

VDD

R19

VDD

AC11

VDD

AC13

VDD

AC15

VDD

AC17

VDD

AC19

VDD

AC21

VDD

AC3

VDD

AC6

VDD

AD1

VDD

AD4

VDD

AD7

VDD

AF1

VDD

AG3

VDD

AG6

VDD

AH1

VDD

AH4

VDD

AH7

VDD

AK4

VDD

AK7

VDD

500mA

CR45 0 0402 /NICR45 0 0402 /NI

4 3

APU_VDDIO_SUS

OV_VDDA_2P5_FB 38

CPU1E

CPU1E

POWER

POWER

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

APU_VDDA_RUN

+

+

Solid:100UF-S 16V 6.3X8 5x11

NON-Solid:100UF 16V 5X11 2mm LR 6.3X5

CLOSE TO CPU

VDDA

VDDA

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB_CAP_1

VDDNB_CAP_2

VDDP_A_1

VDDP_A_2

VDDP_A_3

VDDP_A_4

VDDR

VDDR

VDDR

VDDR

VDDP_B_1

VDDP_B_2

VDDP_B_3

VDDP_B_4

VDDR

VDDR

VDDR

VDDR

CC6310UF 10V 0805 Y5VCC6310UF 10V 0805 Y5V

CC6410UF 10V 0805 Y5VCC6410UF 10V 0805 Y5V

CC653900P 50V X7R 0402 CC653900P 50V X7R 0402

CCT1

CCT1

100UF-S 16V 6.3X8 5x11 /NI

100UF-S 16V 6.3X8 5x11 /NI

M23

M26

M29

N24

N27

N30

R23

R26

R29

U25

U28

U31

W24

W27

W30

AA23

AA26

AA29

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

M22

J26

J29

K24

K27

K30

L25

L28

L31

P22

P25

P28

P31

T22

T24

T27

T30

V22

V23

V26

V29

Y22

Y25

Y28

Y31

AD12

AE12

A3

A4

B3

B4

C1

C2

C3

C4

C5

D1

D2

D3

E1

E2

E3

F1

F2

F3

F4

M14

N13

AH10

AJ10

AK10

AL10

AH11

AJ11

AK11

AL11

J1

J2

J3

J4

H1

H2

H3

H4

APU_VDDA_RUN

APU_VDDNB_RUN

VDDNB_CAP

APU_VDDP_RUN

APU_VDDR_RUN

APU_VDDP_B_RUN

APU_VDDR_B_RUN

CPU_VDDA CAPS

2

CPU1F

CPU1F

T11

VSS

VSS

VSS

A10

A12

A15

A18

A21

A24

A27

AL9

B10

B13

B16

B19

B22

B25

B28

B7

C11

C14

C17

C20

C23

C26

10UF 10V 0805 Y5VCC59 10UF 10V 0805 Y5VCC59

10UF 10V 0805 Y5VCC60 10UF 10V 0805 Y5VCC60

10UF 10V 0805 Y5VCC61 10UF 10V 0805 Y5VCC61

10UF 10V 0805 Y5VCC62 10UF 10V 0805 Y5VCC62

C29

D12

D15

D18

D21

D24

D27

D30

E10

E13

E16

E19

E22

E25

E28

E31

F11

F14

F17

F20

F23

F26

F29

G12

G15

G18

G21

G24

G27

C8

D6

E7

F9

G1

G2

G3

VSS

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

G30

G4

G8

H13

H16

H19

H22

H25

H28

H31

H5

H7

J10

J12

J14

J16

J18

J20

J22

J23

J8

K1

K11

V13

K15

K17

V19

K21

K7

L10

L12

L14

L16

L18

L20

L22

L9

M11

M13

M15

M17

M21

N10

N12

N20

N22

N3

N6

N9

P11

P21

P4

P7

R10

R12

R20

R22

R9

U10

U12

U20

U22

W10

W12

W20

W22

AA10

AA14

AA16

AA18

AA22

AA3

AA6

AA9

AB11

AB13

AB15

AB17

AB19

AB21

AB4

AB7

AC10

AC14

AC16

AC18

AC20

AC22

AC9

AD17

AD20

AD23

AD26

AD29

AE10

AE15

AE18

AE21

AE24

AE27

T21

V11

V21

Y11

Y13

Y15

Y17

Y19

Y21

U3

U6

U9

V4

V7

W9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

CPU1G

CPU1G

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

AE3

AE30

AE6

AE9

AF12

AF14

AF16

AF19

AF22

AF25

AF28

AF31

AF4

AF7

AG17

AG20

AG23

AG26

AG29

AG9

AH13

AH15

AH18

AH21

AH24

AH27

AH30

AJ12

AJ14

AJ16

AJ19

AJ22

AJ25

AJ28

AJ3

AJ31

AJ6

AJ9

AK13

AK17

AK20

AK23

AK26

AK29

AL13

AL15

AL18

AL21

AL24

AL27

AL3

AL6

M19

P13

P19

T13

T19

?

?

SOCKET FM1 905 SMD

SOCKET FM1 905 SMD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

K8 CPU POWER

K8 CPU POWER

K8 CPU POWER

AA55C-A1S

AA55C-A1S

AA55C-A1S

6.0

6.0

6.0

10 45Friday, July 29, 2011

10 45Friday, July 29, 2011

10 45Friday, July 29, 2011

it

5

A

4 3

2

1

APU_VDDNB_RUNAPU_VDD_RUN

(CPU CORE)

D D

C C

APU_VDD_RUN

BCC8 10UF 10V 0805 Y5VBCC8 10UF 10V 0805 Y5V

BCC10 10UF 10V 0805 Y5VBCC10 10UF 10V 0805 Y5V

BCC39 10UF 10V 0805 Y5VBCC39 10UF 10V 0805 Y5V

BCC41 10UF 10V 0805 Y5VBCC41 10UF 10V 0805 Y5V

BCC42 10UF 10V 0805 Y5VBCC42 10UF 10V 0805 Y5V

BCC30 10UF 10V 0805 Y5VBCC30 10UF 10V 0805 Y5V

BCC40 10UF 10V 0805 Y5VBCC40 10UF 10V 0805 Y5V

BCC31 10UF 10V 0805 Y5VBCC31 10UF 10V 0805 Y5V

BCC32 10UF 10V 0805 Y5VBCC32 10UF 10V 0805 Y5V

BCC5 10UF 10V 0805 Y5VBCC5 10UF 10V 0805 Y5V

BCC7 10UF 10V 0805 Y5VBCC7 10UF 10V 0805 Y5V

BCC9 10UF 10V 0805 Y5VBCC9 10UF 10V 0805 Y5V

BCC11 10UF 10V 0805 Y5VBCC11 10UF 10V 0805 Y5V

BCC12 10UF 10V 0805 Y5VBCC12 10UF 10V 0805 Y5V

BCC13 10UF 10V 0805 Y5VBCC13 10UF 10V 0805 Y5V

BCC14 10UF 10V 0805 Y5VBCC14 10UF 10V 0805 Y5V

BCC15 10UF 10V 0805 Y5VBCC15 10UF 10V 0805 Y5V

BCC16 10UF 10V 0805 Y5VBCC16 10UF 10V 0805 Y5V

BCC17 10UF 10V 0805 Y5VBCC17 10UF 10V 0805 Y5V

BCC18 10UF 10V 0805 Y5VBCC18 10UF 10V 0805 Y5V

BCC19 10UF 10V 0805 Y5VBCC19 10UF 10V 0805 Y5V

BCC20 10UF 10V 0805 Y5VBCC20 10UF 10V 0805 Y5V

BCC21 10UF 10V 0805 Y5VBCC21 10UF 10V 0805 Y5V

BCC22 10UF 10V 0805 Y5VBCC22 10UF 10V 0805 Y5V

BCC24 10UF 10V 0805 Y5VBCC24 10UF 10V 0805 Y5V

BCC26 10UF 10V 0805 Y5VBCC26 10UF 10V 0805 Y5V

BCC28 10UF 10V 0805 Y5VBCC28 10UF 10V 0805 Y5V

BOTTOM

APU_VDD_RUN APU_VDD_RUN

Tan CAP

+

BCC33

+

BCC33

330UF 2.5V 9M 7X4X2 MSK /NI

330UF 2.5V 9M 7X4X2 MSK /NI

+

BCC34

+

BCC34

330UF 2.5V 9M 7X4X2 MSK /NI

330UF 2.5V 9M 7X4X2 MSK /NI

APU_VDD_RUN

CC71 0.1UF 16V X7R 0402CC71 0.1UF 16V X7R 0402

CC72 0.1UF 16V X7R 0402CC72 0.1UF 16V X7R 0402

CC74 0.01UF 25V X7R 0402CC74 0.01UF 25V X7R 0402

CC77 0.01UF 25V X7R 0402CC77 0.01UF 25V X7R 0402

CC79 0.1UF 16V X7R 0402CC79 0.1UF 16V X7R 0402

CC82 0.1UF 16V X7R 0402CC82 0.1UF 16V X7R 0402

CC84 0.1UF 16V X7R 0402CC84 0.1UF 16V X7R 0402

CC87 0.1UF 16V X7R 0402CC87 0.1UF 16V X7R 0402

CC89 0.1UF 16V X7R 0402CC89 0.1UF 16V X7R 0402

CC92 0.1UF 16V X7R 0402CC92 0.1UF 16V X7R 0402

CC104 0.1UF 16V X7R 0402CC104 0.1UF 16V X7R 0402

CC134 0.1UF 16V X7R 0402CC134 0.1UF 16V X7R 0402

CC103 0.1UF 16V X7R 0402CC103 0.1UF 16V X7R 0402

CC133 0.1UF 16V X7R 0402CC133 0.1UF 16V X7R 0402

CC136 0.1UF 16V X7R 0402CC136 0.1UF 16V X7R 0402

CC138 0.1UF 16V X7R 0402CC138 0.1UF 16V X7R 0402

CC135 0.1UF 16V X7R 0402CC135 0.1UF 16V X7R 0402

CC137 0.1UF 16V X7R 0402CC137 0.1UF 16V X7R 0402

CC78 0.01UF 25V X7R 0402CC78 0.01UF 25V X7R 0402

CC81 0.01UF 25V X7R 0402CC81 0.01UF 25V X7R 0402

TOP

place TOP layer, close to APU_VDD_RUN pin.place BOTTOM layer, close to APU_VDD_RUN pin.

APU_VDDNB_RUN

CC69 10UF 10V 0805 Y5VCC69 10UF 10V 0805 Y5V

CC75 10UF 10V 0805 Y5VCC75 10UF 10V 0805 Y5V

CC80 10UF 10V 0805 Y5VCC80 10UF 10V 0805 Y5V

CC85 10UF 10V 0805 Y5VCC85 10UF 10V 0805 Y5VBCC6 10UF 10V 0805 Y5VBCC6 10UF 10V 0805 Y5V

CC90 10UF 10V 0805 Y5VCC90 10UF 10V 0805 Y5V

CC67 10UF 10V 0805 Y5VCC67 10UF 10V 0805 Y5V

CC68 10UF 10V 0805 Y5VCC68 10UF 10V 0805 Y5V

CC132 10UF 10V 0805 Y5VCC132 10UF 10V 0805 Y5V

CC70 0.1UF 16V X7R 0402CC70 0.1UF 16V X7R 0402

CC142 10UF 10V 0805 Y5VCC142 10UF 10V 0805 Y5V

CC88 10UF 10V 0805 Y5VCC88 10UF 10V 0805 Y5V

CC91 10UF 10V 0805 Y5VCC91 10UF 10V 0805 Y5V

place close to APU_VDDNB_RUN pin.

APU_VDDNB_RUN

Tan CAP

APU_VDDIO_SUS

APU_VDDIO_SUS

CC94 0.1UF 16V X7R 0402CC94 0.1UF 16V X7R 0402

CC95 0.1UF 16V X7R 0402CC95 0.1UF 16V X7R 0402

CC97 0.01UF 25V X7R 0402CC97 0.01UF 25V X7R 0402

CC99 0.01UF 25V X7R 0402CC99 0.01UF 25V X7R 0402

CC100 0.1UF 16V X7R 0402CC100 0.1UF 16V X7R 0402

CC101 0.1UF 16V X7R 0402CC101 0.1UF 16V X7R 0402

CC106 0.1UF 16V X7R 0402CC106 0.1UF 16V X7R 0402

CC107 0.1UF 16V X7R 0402CC107 0.1UF 16V X7R 0402

BCC35,CC98,CC102,CC105,CC96,BCC25,BCC27,BCC29

place close to APU VDDIO pin.

APU_VDDIO_SUS

CC93 10UF 10V 0805 Y5VCC93 10UF 10V 0805 Y5V

CC96 10UF 10V 0805 Y5VCC96 10UF 10V 0805 Y5V

CC98 10UF 10V 0805 Y5VCC98 10UF 10V 0805 Y5V

CC128 10UF 10V 0805 Y5VCC128 10UF 10V 0805 Y5V

CC102 10UF 10V 0805 Y5VCC102 10UF 10V 0805 Y5V

CC141 10UF 10V 0805 Y5VCC141 10UF 10V 0805 Y5V

CC105 10UF 10V 0805 Y5VCC105 10UF 10V 0805 Y5V

BCC23 10UF 10V 0805 Y5VBCC23 10UF 10V 0805 Y5V

BCC25 10UF 10V 0805 Y5VBCC25 10UF 10V 0805 Y5V

BCC27 1UF 16V 0805 Y5VBCC27 1UF 16V 0805 Y5V

BCC29 1UF 16V 0805 Y5VBCC29 1UF 16V 0805 Y5V

BCC35 1UF 16V 0805 Y5VBCC35 1UF 16V 0805 Y5V

CC129 1UF 10V Y5V 0402CC129 1UF 10V Y5V 0402

CC139 1UF 10V Y5V 0402CC139 1UF 10V Y5V 0402

CC140 1UF 10V Y5V 0402CC140 1UF 10V Y5V 0402

+

CC73

+

CC73

330UF 2.5V 9M 7X4X2 MSK /NI

330UF 2.5V 9M 7X4X2 MSK /NI

APU_VDDP_RUN,

APU_VDDR_RUN

B B

APU_VDDP_RUN APU_VDDR_RUN APU_VDDP_B_RUN APU_VDDR_B_RUN

PUT 2*10UF AND 2*0.1UF AT

THE UPSIDE OF CPU

place TOP layer, close to APU_VDDP_RUN pin.

CC108 10UF 10V 0805 Y5VCC108 10UF 10V 0805 Y5V

CC112 10UF 10V 0805 Y5VCC112 10UF 10V 0805 Y5V

CC116 0.1UF 16V X7R 0402CC116 0.1UF 16V X7R 0402

CC120 1UF 10V Y5V 0402CC120 1UF 10V Y5V 0402

PUT 2*10UF AND 2*0.1UF AT

THE DOWNSIDE OF CPU

2*10UF 0805

2*0.1UF 0402

CC109 10UF 10V 0805 Y5VCC109 10UF 10V 0805 Y5V

CC113 10UF 10V 0805 Y5VCC113 10UF 10V 0805 Y5V

CC117 0.1UF 16V X7R 0402CC117 0.1UF 16V X7R 0402

CC121 1UF 10V Y5V 0402CC121 1UF 10V Y5V 0402

2*10UF 0805

2*0.1UF 0402

CC110 10UF 10V 0805 Y5VCC110 10UF 10V 0805 Y5V

CC114 10UF 10V 0805 Y5VCC114 10UF 10V 0805 Y5V

CC118 0.1UF 16V X7R 0402CC118 0.1UF 16V X7R 0402

CC122 1UF 10V Y5V 0402CC122 1UF 10V Y5V 0402

PUT 2*10UF AND 2*0.1UF AT

THE UPSIDE OF CPU

2*10UF 0805

2*0.1UF 0402

CC111 10UF 10V 0805 Y5VCC111 10UF 10V 0805 Y5V

CC115 10UF 10V 0805 Y5VCC115 10UF 10V 0805 Y5V

CC119 0.1UF 16V X7R 0402CC119 0.1UF 16V X7R 0402

CC123 1UF 10V Y5V 0402CC123 1UF 10V Y5V 0402

PUT 2*10UF AND 2*0.1UF AT

THE DOWNSIDE OF CPU

2*10UF 0805

2*0.1UF 0402

BIOSTAR STANDARD

NO:2011_AMD_FM1_01

place TOP layer, close to APU_VDDP_B_RUN pin.place TOP layer, close to APU_VDDP_RUN pin.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU DECPOULING CAP

APU DECPOULING CAP

APU DECPOULING CAP

Custom

Custom

Custom

AA55C-A1S

AA55C-A1S

AA55C-A1S

11 45Friday, July 29, 2011

11 45Friday, July 29, 2011

11 45Friday, July 29, 2011

it

A

6.0

6.0

6.0

5

4 3

2

1

D D

C C

B B

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR CAP BYPASS

DDR CAP BYPASS

DDR CAP BYPASS

AA55C-A1S

AA55C-A1S

AA55C-A1S

12 45Friday, July 29, 2011

12 45Friday, July 29, 2011

12 45Friday, July 29, 2011

6.0

6.0

6.0

it

5

DCC

A

4 3

2

1

DDR3_A1

DDR3_A1A

MEM_MA_DQS_L08,15

MEM_MA_DQS_H08,15

MEM_MA_DQS_L18,15

MEM_MA_DQS_H18,15

MEM_MA_DQS_L28,15

D

FOR ECC

MEM_MA_DM[7..0]8,15

FOR ECC

MEM_MA_CHECK[7..0]8,15

MEM_MA_DQS_H28,15

MEM_MA_DQS_L38,15

MEM_MA_DQS_H38,15

MEM_MA_DQS_L48,15

MEM_MA_DQS_H48,15

MEM_MA_DQS_L58,15

MEM_MA_DQS_H58,15

MEM_MA_DQS_L68,15

MEM_MA_DQS_H68,15

MEM_MA_DQS_L78,15

MEM_MA_DQS_H78,15

MEM_MA_DQS_L88,15

MEM_MA_DQS_H88,15

MEM_MA_DM88,15

MEM_MA_CHECK[7..0]

FOR ECC

SDATA14,15,16,22,38,41

MEM_MA_ADD[15..0]8,15

SCLK14,15,16,22,38,41

B B

MEM_MA_DQS_L0

MEM_MA_DQS_H0

MEM_MA_DQS_L1

MEM_MA_DQS_H1

MEM_MA_DQS_L2

MEM_MA_DQS_H2

MEM_MA_DQS_L3

MEM_MA_DQS_H3

MEM_MA_DQS_L4

MEM_MA_DQS_H4

MEM_MA_DQS_L5

MEM_MA_DQS_H5

MEM_MA_DQS_L6

MEM_MA_DQS_H6

MEM_MA_DQS_L7

MEM_MA_DQS_H7

MEM_MA_DQS_L8

MEM_MA_DQS_H8

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DM8

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK6

MEM_MA_CHECK7

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

DDR3_A1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DM0/DQS9

126

DQS9-

134

DM1/DQS10

135

DQS10-

143

DM2/DQS11

144

DQS11-

152

DM3/DQS12

153

DQS12-

203

DM4/DQS13

204

DQS13-

212

DM5/DQS14

213

DQS14-

221

DM6/DQS15

222

DQS15-

230

DM7/DQS16

231

DQS16-

161

DM8/DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

DDR3-240 PIN-W

DDR3-240 PIN-W

BLACK

BLACK

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA56

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA61

MEM_MA_DATA51

MEM_MA_DATA55

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA50

MEM_MA_DATA54

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA42

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA47

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA38

MEM_MA_DATA33

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA39

MEM_MA_DATA32

MEM_MA_DATA26

MEM_MA_DATA30

MEM_MA_DATA24

MEM_MA_DATA29

MEM_MA_DATA27

MEM_MA_DATA31

MEM_MA_DATA25

MEM_MA_DATA28

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA1

MEM_MA_DATA4

MEM_MA_DATA2

MEM_MA_DATA3