Page 1

5

A

4 3 2 1

Model Name :A88PC-M3S

DD

PAGE

1

2

3

4

5

6-10

11

12

13

14

15

16

17

18

CC

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

BB

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

CONTENTS

COVER

BLOCK DIAGRAM

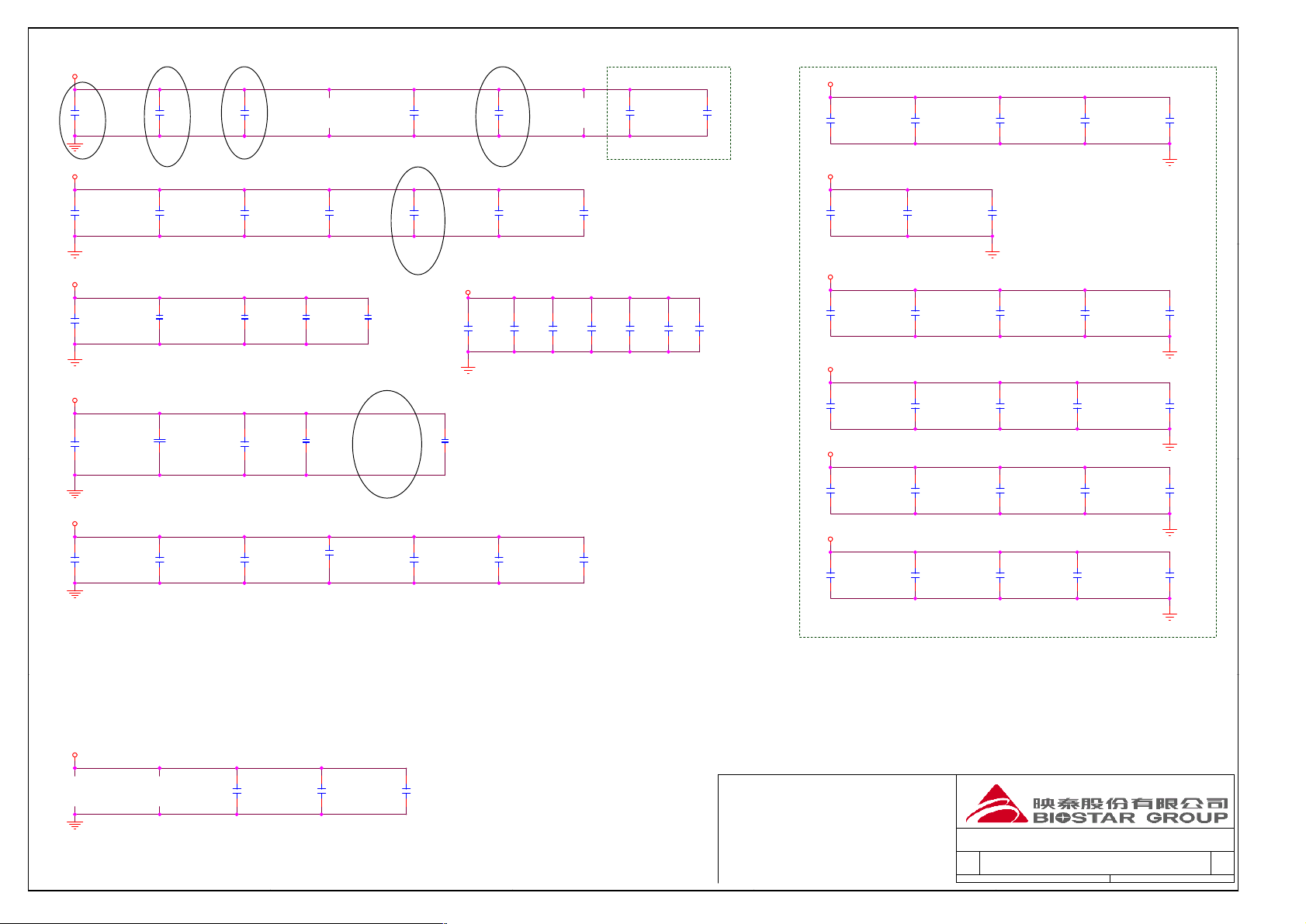

POWER DELIVERY

CLOCK DISTRIBUTION

REVISION HISTROY

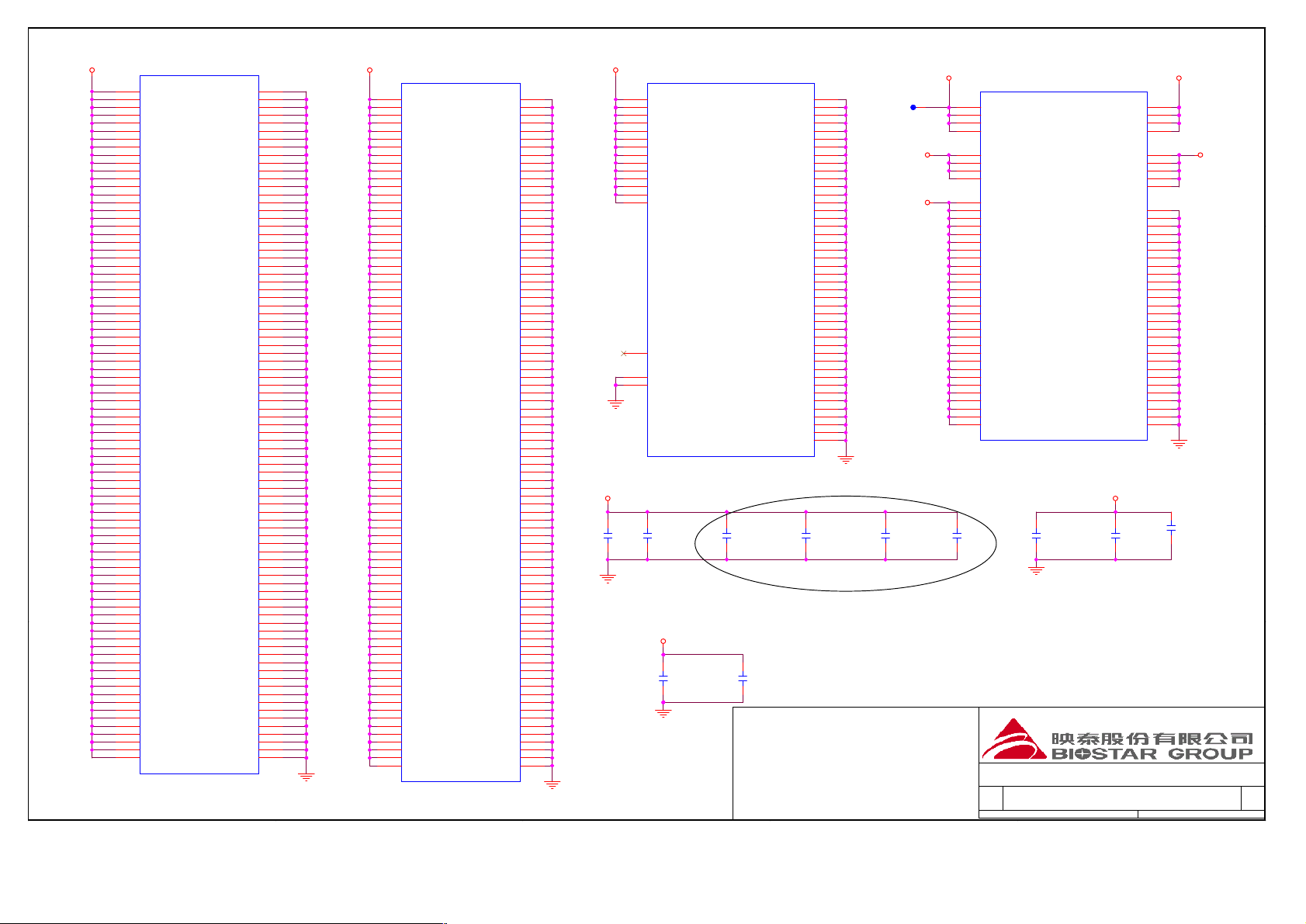

SKT AM3 CPU

DDR3 DIMM A1

DDR3 DIMM B1

REVERSE

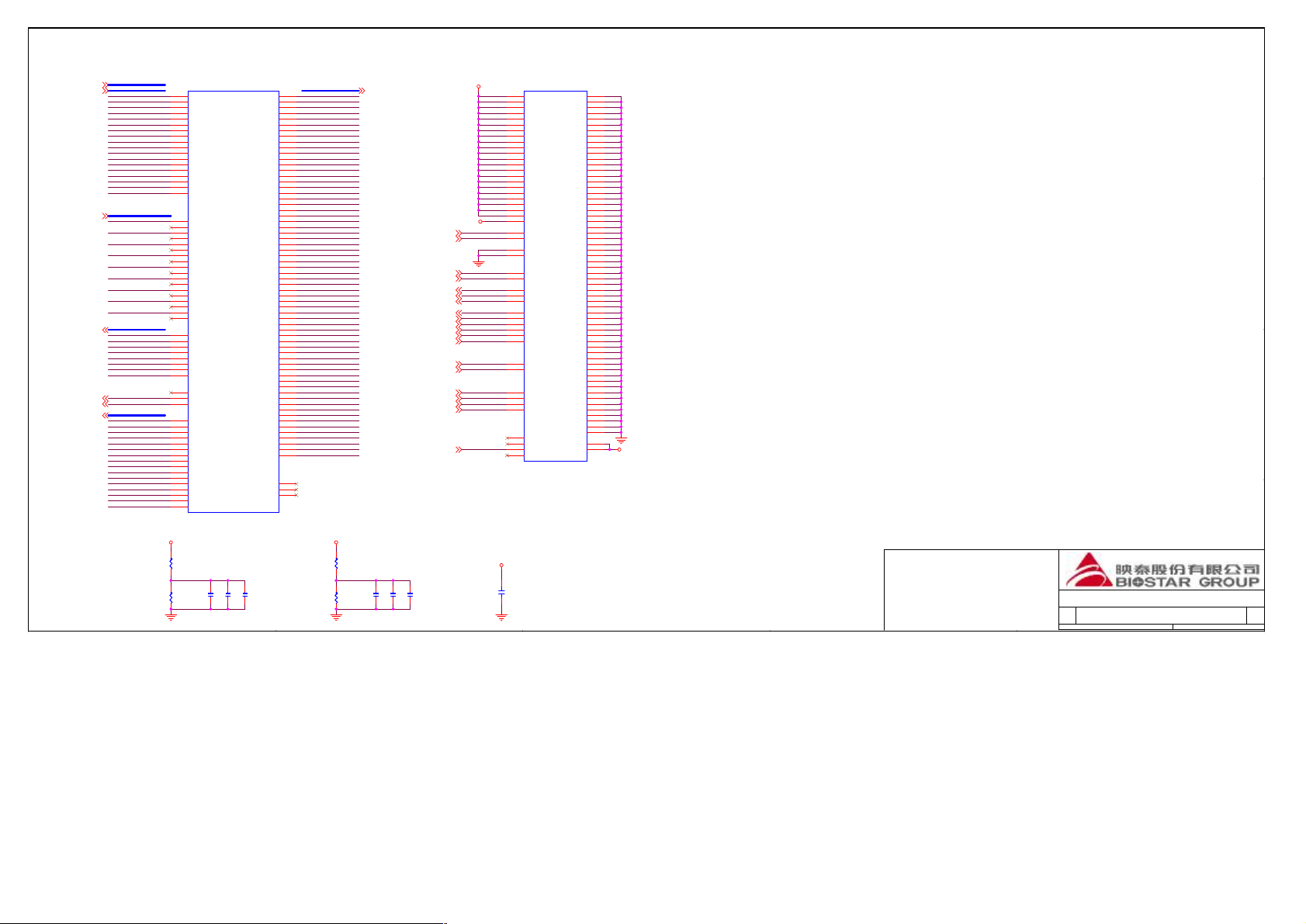

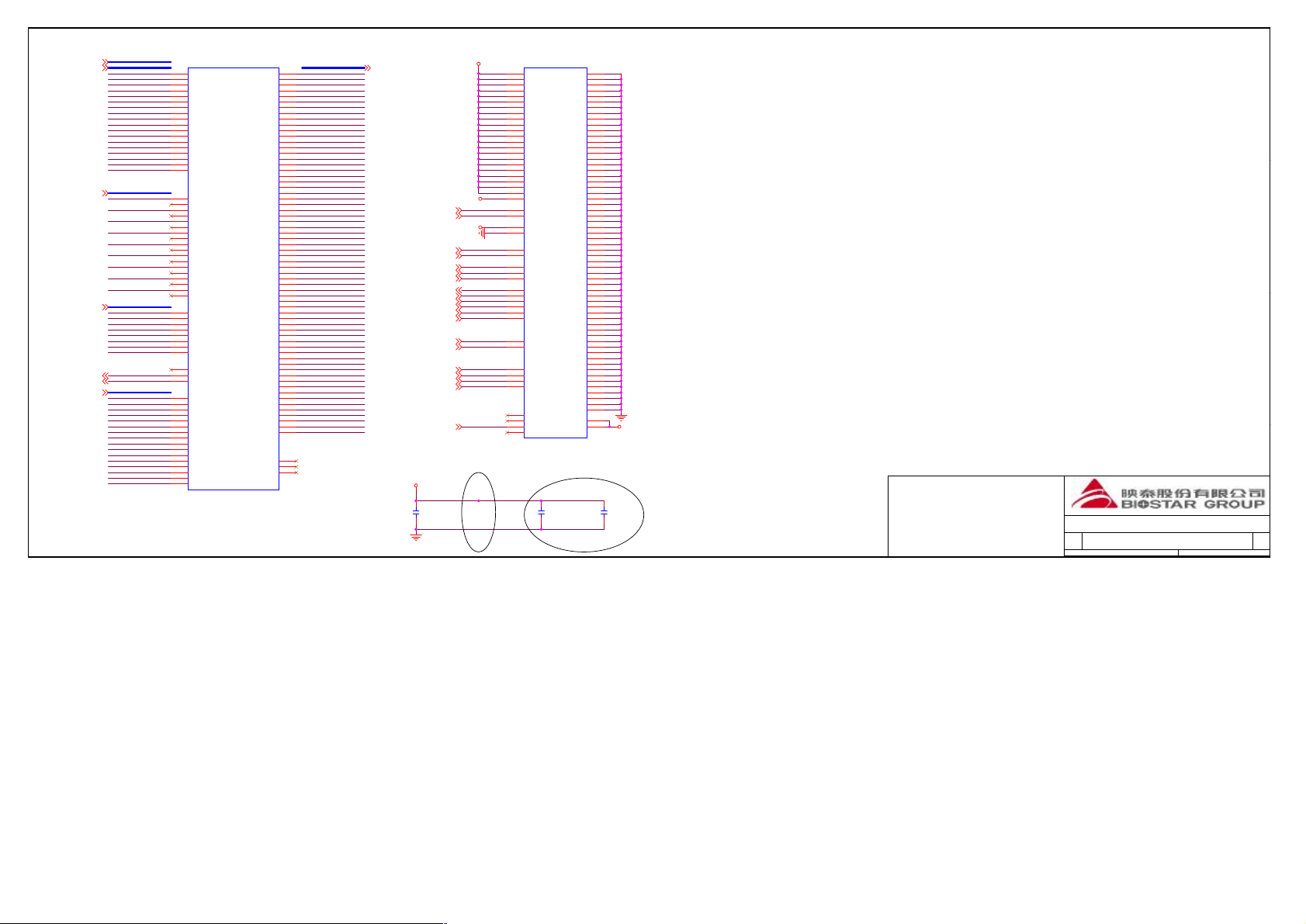

RS880-HT LINK

RS880-PCIE

RS880-SYSTEM

RS880-PWOER&SBD_MEM

CLOCK RTM880N-793

SB710-PCIE/PCI/CPU/LPC

SB710-ACPI/GPIO/USB/AUD

SB710-SATA/IDE/HWM/SPI

SB710-POWER&DECOUPLING

SB710-STRAP

CRT & DVI

PCI-E SLOT 1/2

PCI SLOT

IDE ATA 133

USB CONN

CODEC ALC662

AUDIO CONNECTOR

SUPER I/O ITE8721

H/W MON / FAN CONTROL

FDD / PS2 CONN / MH

COM&LPT CONNECTOR

ATX PWR / FRONT PANEL / LED

OVER VOLTAGE

FRONT USB

PWRGD / MISC DC-DC

VCC_CORE DC-DC CONVER

MEM POWER

NB/SB CORE POWER

REL8111DL/8102EL

BOM

Marketing name :A880G+

VER:6.1

CPU :

AM3,Including AthlonII / Phenom II/ Sempron

System Chipset :

AMD 880G

AMD SB710

On Board Chip :

Clock Gen. -- RealTek RTM880N-793

Azalia Codec -- RealTek ALC662

GigaBit Lan -- RealTek RTL8111DL

PWM Controller -- L6717

Super I/O -- IT8721FBX

SPI Flash 8Mb

Main Memory :

2 Channel DDR 3 * 2 (Max 4GB)

Expansion Slot :

PCI Express x16 Slot * 1

PCI Slot * 2

Heatsink :

NB: NBHS-A88G

SB: SBHS-A78G

I/O Pannel :

47-RIOBRACKET-84

PCB SIZE :

200.01 X 243.84mm

4-layers-2116

HW Engineer:

HW Leader:

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Custom

Custom

Custom

Date:

Date:

COVER

COVER

COVER

A88PC-M3S

A88PC-M3S

A88PC-M3S

A

6.1

6.1

1 43Tuesday, June 29, 2010

1 43Tuesday, June 29, 2010

1 43Tuesday, June 29, 2010

6.1

of

of

of

i

Page 2

5

A

4 3 2 1

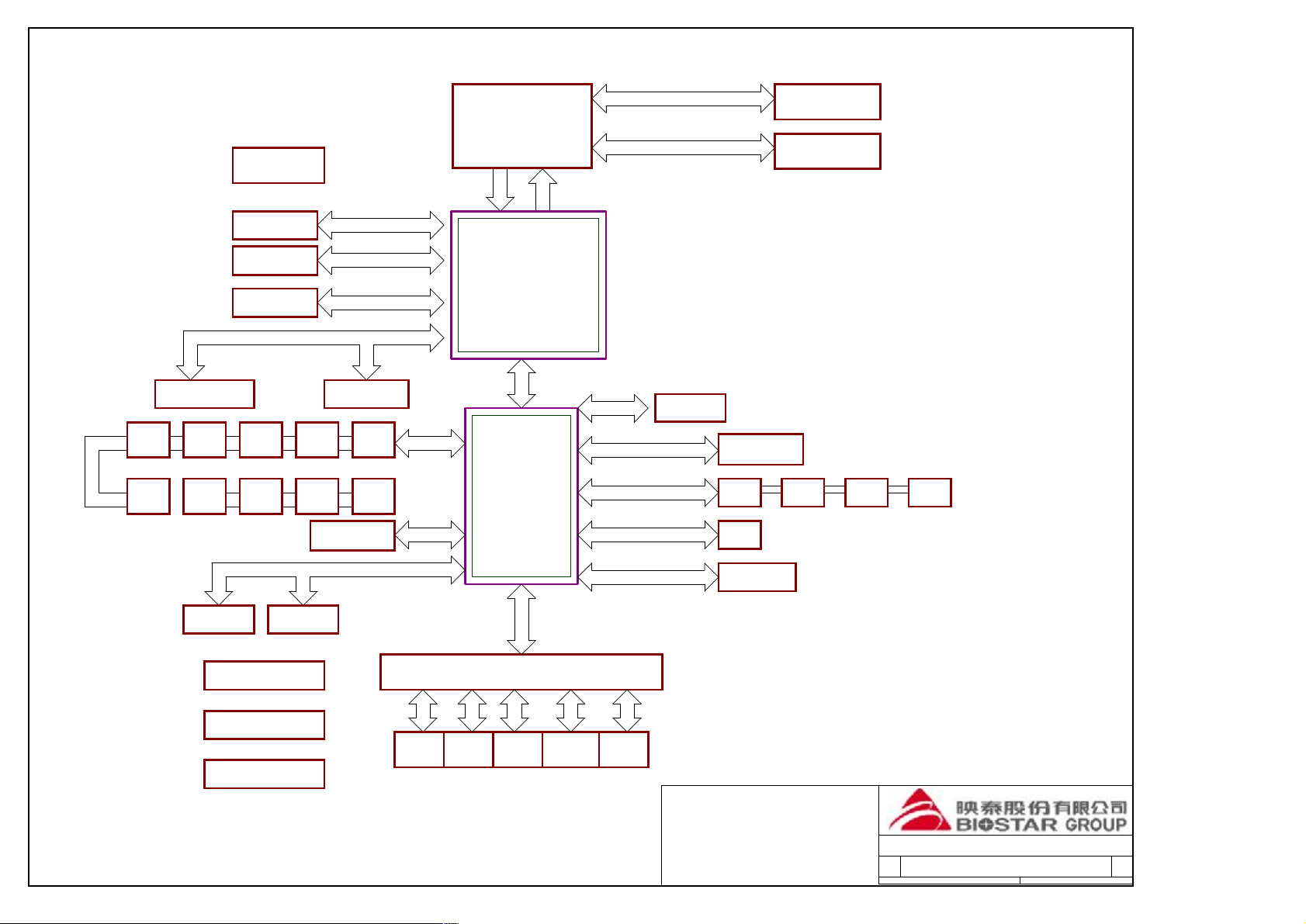

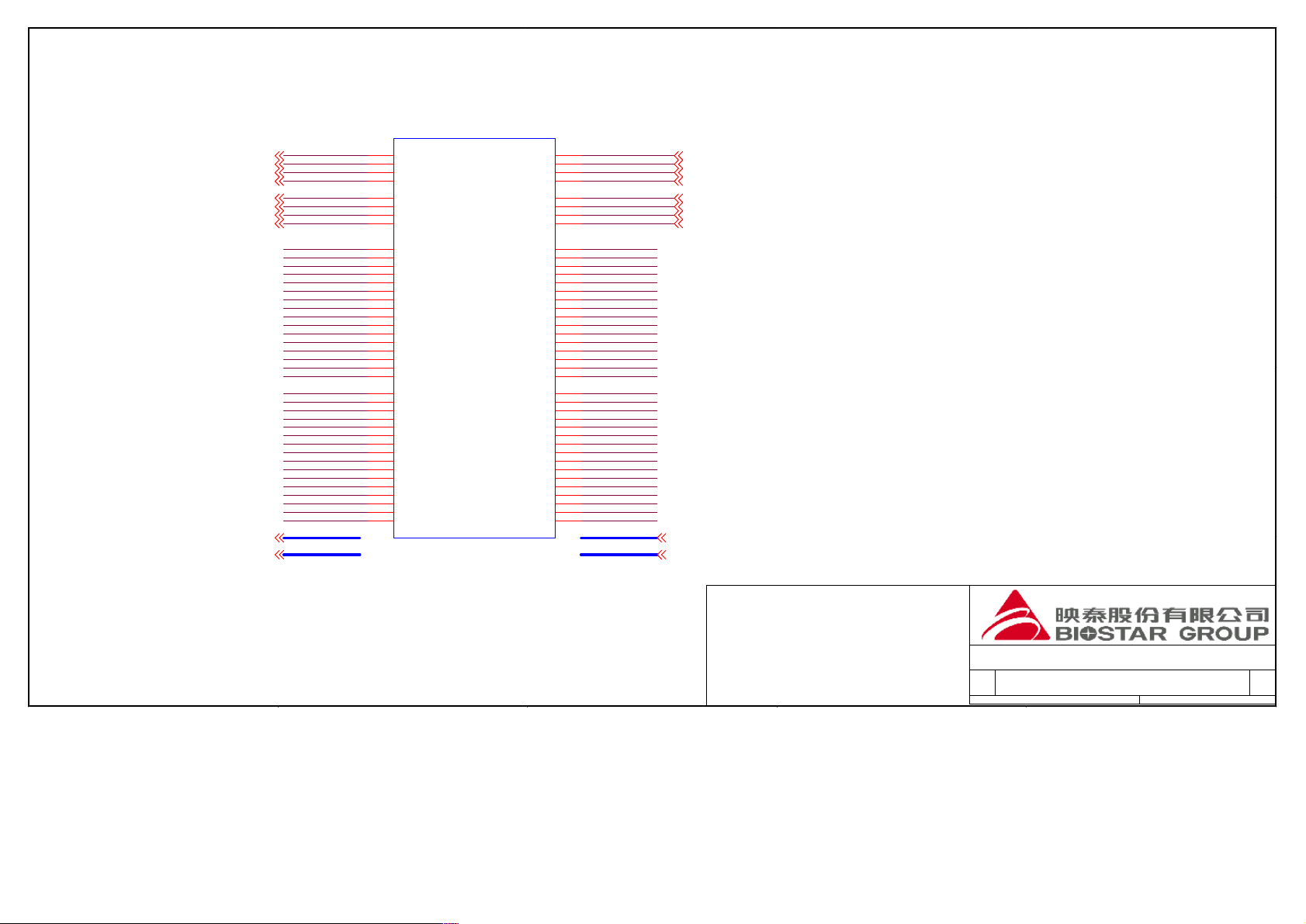

AMD

AM3

DD

Clock Generator

RTM880N-793

DVI/TMDS CON

VGA CON

PCIE

16X

SLOT1

TMDS

16X

HyperTransport

LINK

M3 SOCKET

OUT

AMD NB

RS880

HyperTransport LINK0 CPU I/F

INTEGRATED GRAPHICS

LVTM

1 16X PCIE VIDEO I/F

1 1X PCIE I/F

16x16

IN

DDRIII 800,1066,1333

128bit

DDRIII 800,1066,1333

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

CC

AMD SB

4X

PCIE

SPI I/F

HD AUDIO I/F

SATA II I/F

ATA 66/100/133 I/F

SPI ROM

AZILIA CODEC

ALC662

SATA#1

IDE1

HW

MONITOR

SATA#2

SATA#3

SATA#4

Realtek RTL8111DL

Realtek RTL8102EL

USB-4

USB-5

BB

USB-3

USB-6

USB-2

USB-7

PCI BUS

USB-1

USB-8

STAP ROM

PCIE GPP0

X1

USB-0

USB-9

USB 2.0

I2C I/F

A LINK

SB700/SB710

USB2.0 (12)

SATA II (6)

AZALIA

ATA 66/100/133

ACPI

LPC I/F

INT RTC

HW MONITOR

PCI SLOT #1

DESKTOP M2 POWER

RS780C

CORE & PCIE POWER

DDR MEMORY POWER

PCI SLOT #2

ITE LPC SIO8721

FLOPPY

KBD

MOUSE

HW

MONITOR

LPTCOM

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

A88PC-M3S

A88PC-M3S

A88PC-M3S

2 43Tuesday, June 29, 2010

2 43Tuesday, June 29, 2010

2 43Tuesday, June 29, 2010

of

of

of

A

6.1

6.1

6.1

w

Page 3

5 4 3 2 1

A

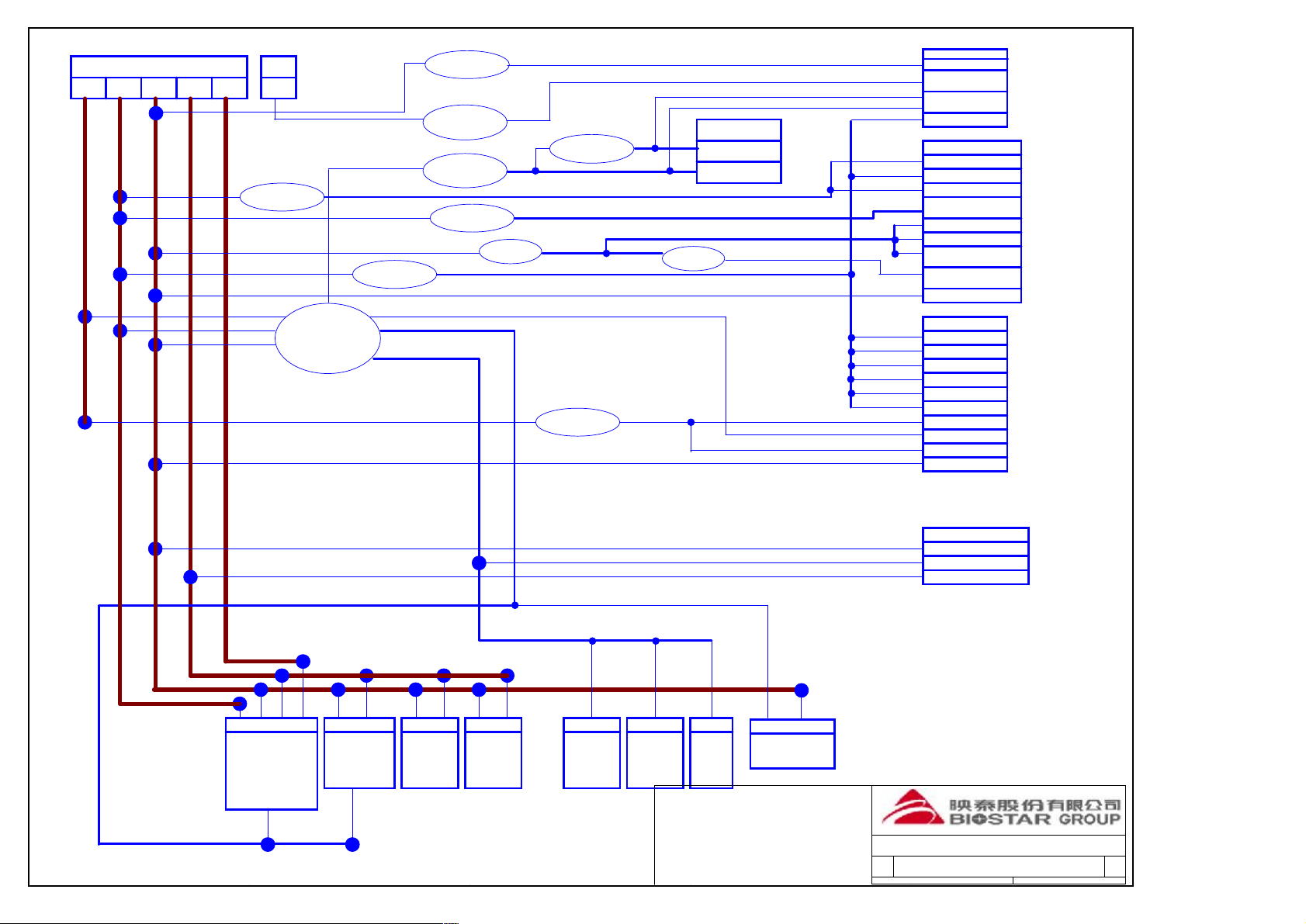

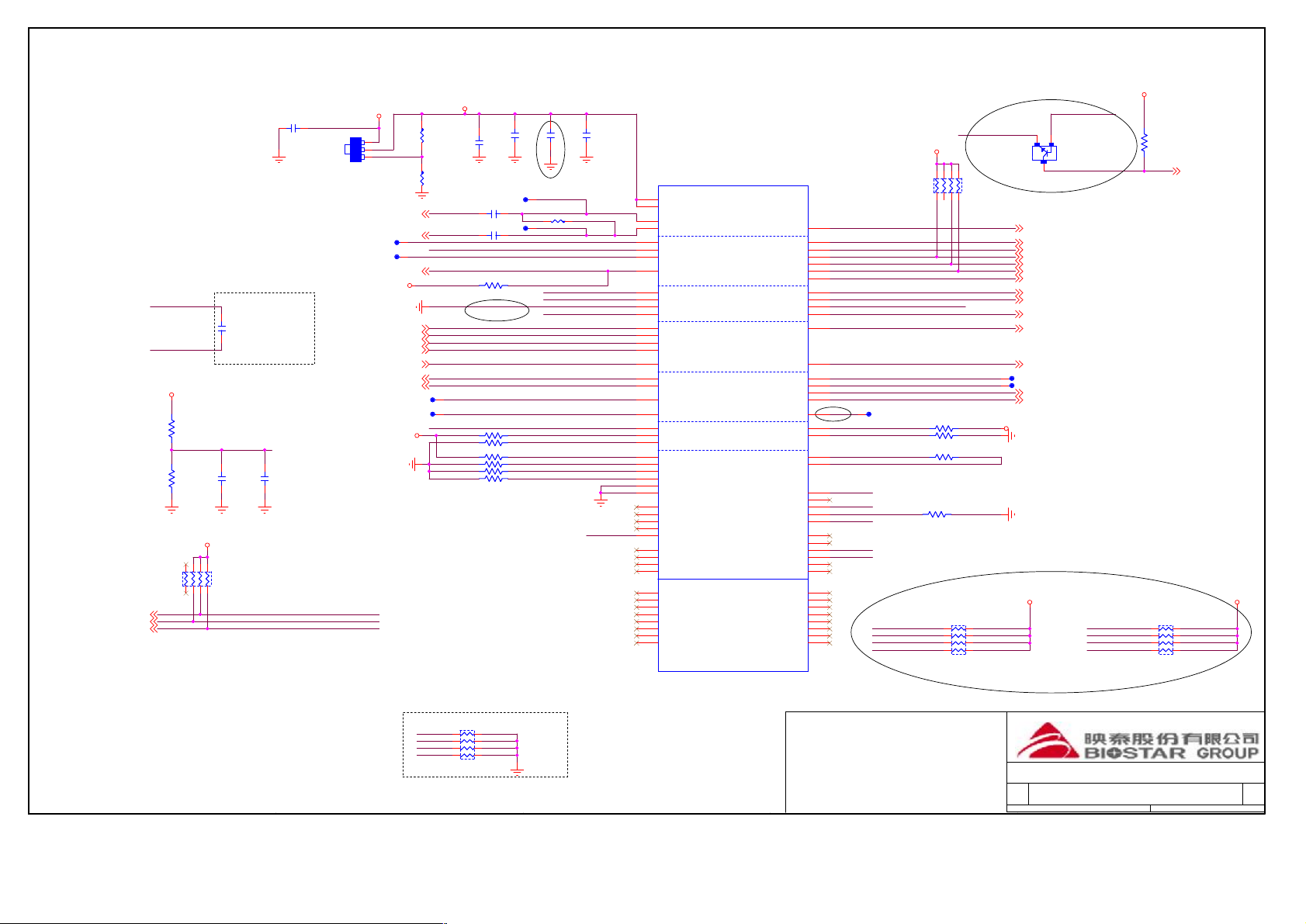

ATX P/S WITH 1A STBY CURRENT

5VSB

+/-5%

5V

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

DD

+5VDUAL_MEM (S0,S5)

VCC 1.1V SW

REGULATOR

VCC 1.2V SW

REGULATOR

2.5V SHUNT

REGULATOR

VRM SW

REGULATOR

1.5V VDD SW

REGULATOR

VCC 1.1V SW

REGULATOR

0.75V VTT_DDR

REGULATOR

+1.1V RX780/RS780; +1.2V RS740 (S0, S1)

+1.1V RX780/RS780; +1.2V RS740 (S0, S1)

1.8V LINEAR

REGULATOR

+1.8V(S0, S1)

+1.2V(S0, S1)

VDD_CPUCORE_RUN (S0, S1)/VDD_CPUNB_RUN (S0, S1)

DDRIII DIMMs

VTT_DDR 2A

VDD MEM 12A

1.5V LINEAR

REGULATOR

+1.5V(S0, S1)

CPU_VDDA_RUN

CPU_VTT_SUS (S0,S1,S3)

CPU_VDDIO_SUS(S0,S1,S3)

(S0, S1)

+3.3VSB (S0, S1, S3, S4, S5)

+3.3VSB REGULATOR

ACPI CONTROLLER

CC

+3.3VDUAL (S0, S1, S3, S4, S5)

+5VDUAL (S0, S1, S3, S4, S5)

1.2V STB LDO

REGULATOR

+1.2VSB (S5)

AM3

VDDA 2.5V 0.2A

VDDCORE

0.8-1.55V

110A

DDRIII MEM I/F

VTT 2A, VDD

10A

VLDT 1.2V 0.5A

RS880

VDDHT/RX 1.1V 1.2A

VDDHTTX 1.2V 0.5A

VDDPCIE 1.1V 2A

NB CORE VDDC

1.1V 7A

VDDA18PCIE 1.8V 0.9A

PLLs 1.8V 0.1A

VDD18/VDD18_MEM

1.8V 0.01A

VDD_MEM 1.8V/1.5V 0.5A

AVDD 3.3V 0.135A

SB710

X4 PCI-E 0.8A

ATA I/O 0.5A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

CLOCK

1.2V S5 PW 0.22A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

3.3V I/O 0.45A

AZALIA CODEC CON

3.3V CORE 0.3A

BB

X1 PCIE per

7.6A 5VDual

12V

3.3Vaux

0.5A

0.1A

12V

3.3V

3.0A

3.3V

5.0A

0.1A

3.0A

5.5A

X16 PCIE

3.3V

12V

5.5A

USB X6 FR

VDD 3.0A

5VDual

2.0A0.5A

USB X6 RL

VDD

2.0A

◇◆

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

2XPS/2

5VDual

1.0A

GBE

3.3V 0.5A (S0, S1)

3.3V 0.1A (S3)

BIOSTAR'S PROPRIETARY INFORMATION

Any unauthorized use, reproduction,

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

+3.3VDUAL (S0, S1, S3)

PCI Slot (per slot) X16 PCIE

5V

3.3V

12V

3.3Vaux

0.375A

-12V

5V ANALOG 0.1A

12V 0.1A

POWER DELIVERY

POWER DELIVERY

POWER DELIVERY

A88PC-M3S

A88PC-M3S

A88PC-M3S

A

6.1

6.1

3 43Tuesday, June 29, 2010

3 43Tuesday, June 29, 2010

3 43Tuesday, June 29, 2010

6.1

of

of

of

Page 4

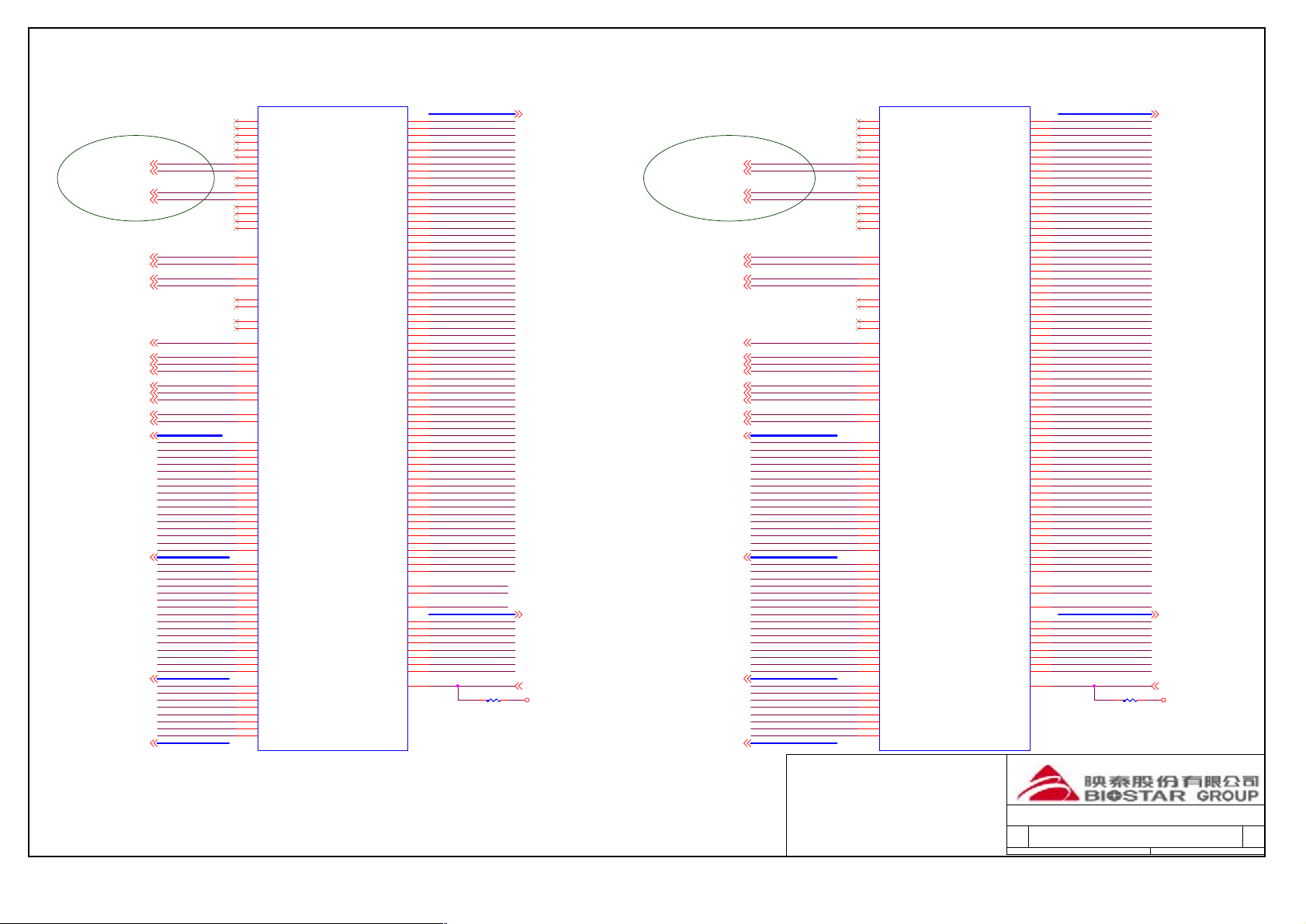

5 4 3 2 1

A

DD

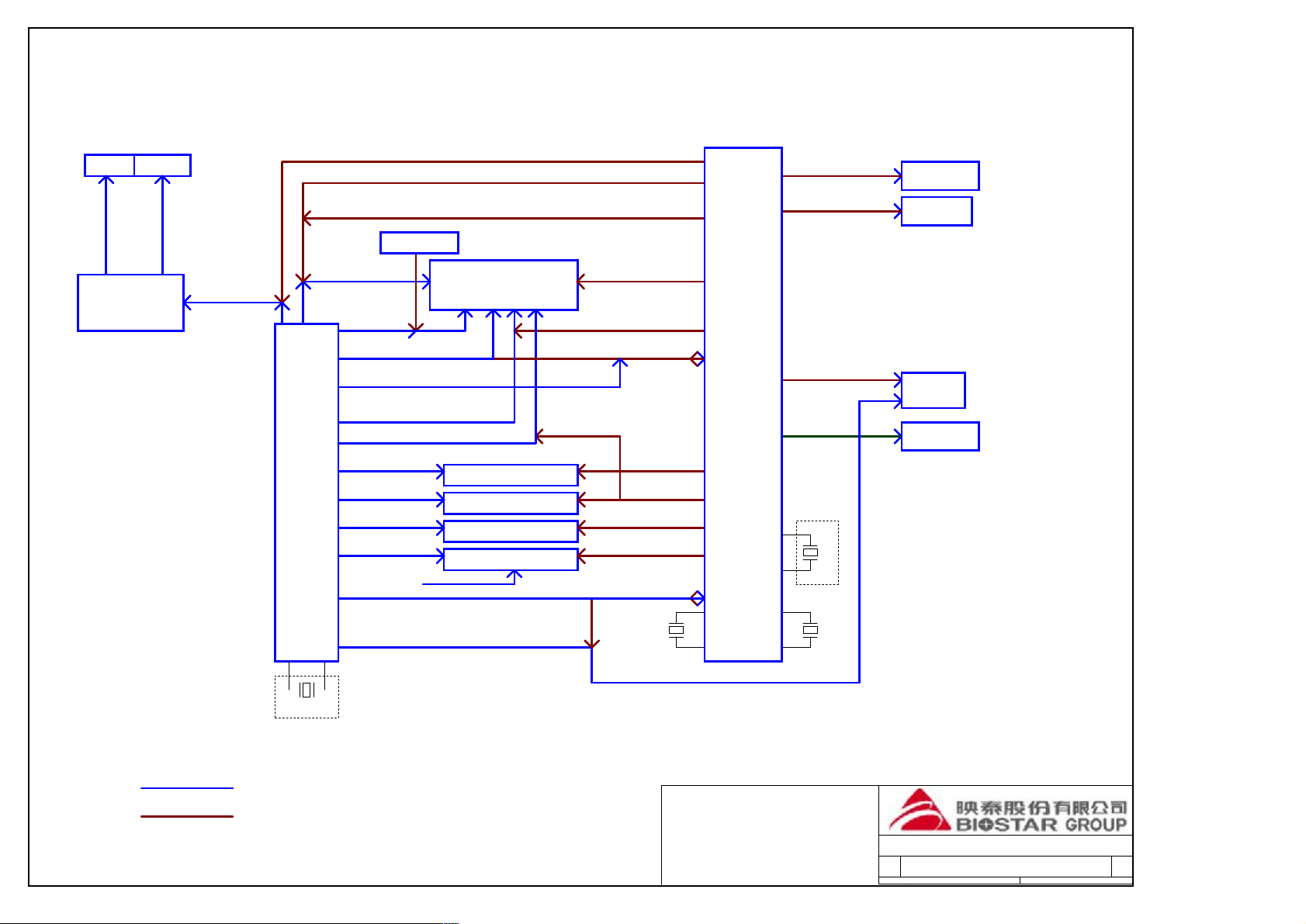

DIMM1

AM3 SOCKET

CC

BB

3 PAIR MEM CLK

AM3 CPU

DIMM2

3 PAIR MEM CLK

1 PAIR CPU CLK

200MHZ

EXTERNAL

CLK GEN.

(RS740/RX780)

HT REFCLK

66MHz SE(RS740)

100MHz

DIFF(RX780/RS780)

NB-OSCIN

14.318MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

NB GFX PCIE CLK

100MHZ

NB GPP PCIE CLK

100MHZ

PCIE GFX CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

USB CLK

48MHZ

14.318MHZ OSC

AMD NB

RS880

(RX780)

PCIE GFX SLOT 1 - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 4 LANES

PCIE GBE

25MHZ OSC INPUT

1 PAIR CPU CLK

200MHZ

HT ref clock

100MHZ DIFF(RX780/RS780)

HT REFCLK

66MHz SE(RS740)

NB PCIE Ref clock

100MHZ

NB Disp clock

100MHZ DIFF(RS780)

GPP Ref clock

100MHZ

GFX Ref clock

100MHZ

GPP Ref clock

100MHZ

GPP Ref clock

100MHZ

GPP Ref clock

100MHZ

25MHz

SATA

CPU_HT_CLK

NB_HT_CLK

25M_48M_66M_OSC

AMD SB

SB710

NB_DISP_CLK

GPP_CLK3

PCIE_RCLK/

NB_LNK_CLK

SLT_GFX_CLK

GPP_CLK0

GPP_CLK1

GPP_CLK2

USB_CLK

SB_BITCLK

48MHZ

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK4

33MHZ

25MHz

PCI SLOT 1

PCI SLOT 2

SUPER IO

IT8718F

HD AUDIO CON

External clock mode

Internal clock mode

SIO CLK

48MHZ

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

32.768KHz

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

A88PC-M3S

A88PC-M3S

A88PC-M3S

4 43Tuesday, June 29, 2010

4 43Tuesday, June 29, 2010

4 43Tuesday, June 29, 2010

6.1

6.1

6.1

of

of

of

Page 5

5 4 3 2 1

A

DD

CC

Date Rev Description

2010/05/14

2010/05/14

2010/05/14

2010/05/14

2010/05/18

2010/05/18

2010/05/19

2010/05/19

2010/05/19

2010/05/19

6.0

6.0

6.0

6.0

6.02010/05/14 CPU SOCKET /SATA CONNECTOR VALUE CHANGE

6.0

6.0

6.0

6.0

6.0

6.0

6.0

R329 change to 121 1% 0402

R332 change to 226 1% 0402

Q68 E connect to SB IMC_CRST_L

R228 NI

CS4+ pull high to +V_CPU

2010/05/18

ADD CT25

2010/05/18

ADD CT34

ㄛ

PC51ㄛPC7

PC2

ㄛ

PC10ㄛPC39

PC3

ADD C52,C53 FOR +1.5V_SUS6.0

ADD cpu socket bottom CAP

ADD R1616.02010/05/19

2010/05/19 UPDATE PWM_EN CIRCUIT

CAP COLAY

R386 change to 1k ohm6.0

2010/05/21 ADD AR2 /C307/LC24 FOR EMI

2010/05/21

LCT1/LCT3/CT30/CT3/CT31 NI

2010/05/21

PC9/PC11/PC42 change to 4.7UF 16V Y5V 0805

PC8 change to 1000P

BB

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

REVISION HISTORY

REVISION HISTORY

REVISION HISTORY

A88PC-M3S

A88PC-M3S

A88PC-M3S

5 43Tuesday, June 29, 2010

5 43Tuesday, June 29, 2010

5 43Tuesday, June 29, 2010

of

of

of

A

6.1

6.1

6.1

Page 6

5

DCCBBAA

4

3

2

1

D

HTCPU_UPCLK114

HTCPU_UPCLK1_14

HTCPU_UPCLK014

HTCPU_UPCLK0_14

HTCPU_UPCNTL114

HTCPU_UPCNTL1_14

HTCPU_UPCNTL14

HTCPU_UPCNTL_14

HTCPU_UP[15..0]14

HTCPU_UP_[15..0]14

HTCPU_UPCLK1

HTCPU_UPCLK1_

HTCPU_UPCLK0

HTCPU_UPCLK0_

HTCPU_UPCNTL1

HTCPU_UPCNTL1_

HTCPU_UPCNTL

HTCPU_UPCNTL_

HTCPU_UP15

HTCPU_UP_15

HTCPU_UP14

HTCPU_UP_14

HTCPU_UP13

HTCPU_UP_13

HTCPU_UP12

HTCPU_UP_12

HTCPU_UP11

HTCPU_UP_11

HTCPU_UP10

HTCPU_UP_10

HTCPU_UP9

HTCPU_UP_9

HTCPU_UP8

HTCPU_UP_8

HTCPU_UP7

HTCPU_UP_7

HTCPU_UP6

HTCPU_UP_6

HTCPU_UP5

HTCPU_UP_5

HTCPU_UP4

HTCPU_UP_4

HTCPU_UP3

HTCPU_UP_3

HTCPU_UP2

HTCPU_UP_2

HTCPU_UP1

HTCPU_UP_1

HTCPU_UP0

HTCPU_UP_0

HTCPU_UP[15..0]

HTCPU_UP_[15..0]

CPU1A

CPU1A

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

HyperTransport

HTCPU_DWNCLK1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

HT LINK

HT LINK

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

AD5

HTCPU_DWNCLK1_

AD4

HTCPU_DWNCLK0

AD1

HTCPU_DWNCLK0_

AC1

HTCPU_DWNCNTL1

Y6

HTCPU_DWNCNTL1_

W6

HTCPU_DWNCNTL

W2

HTCPU_DWNCNTL_

W3

HTCPU_DWN15

Y5

HTCPU_DWN_15

Y4

HTCPU_DWN14

AB6

HTCPU_DWN_14

AA6

HTCPU_DWN13

AB5

HTCPU_DWN_13

AB4

HTCPU_DWN12

AD6

HTCPU_DWN_12

AC6

HTCPU_DWN11

AF6

HTCPU_DWN_11

AE6

HTCPU_DWN10

AF5

HTCPU_DWN_10

AF4

HTCPU_DWN9

AH6

HTCPU_DWN_9

AG6

HTCPU_DWN8

AH5

HTCPU_DWN_8

AH4

HTCPU_DWN7

Y1

HTCPU_DWN_7

W1

HTCPU_DWN6

AA2

HTCPU_DWN_6

AA3

HTCPU_DWN5

AB1

HTCPU_DWN_5

AA1

HTCPU_DWN4

AC2

HTCPU_DWN_4

AC3

HTCPU_DWN3

AE2

HTCPU_DWN_3

AE3

HTCPU_DWN2

AF1

HTCPU_DWN_2

AE1

HTCPU_DWN1

AG2

HTCPU_DWN_1

AG3

HTCPU_DWN0

AH1

HTCPU_DWN_0

AG1

HTCPU_DWN[15..0]

HTCPU_DWN_[15..0]

HTCPU_DWNCLK1 14

HTCPU_DWNCLK1_ 14

HTCPU_DWNCLK0 14

HTCPU_DWNCLK0_ 14

HTCPU_DWNCNTL1 14

HTCPU_DWNCNTL1_ 14

HTCPU_DWNCNTL 14

HTCPU_DWNCNTL_ 14

HTCPU_DWN[15..0] 14

HTCPU_DWN_[15..0] 14

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

5

4

3

◆

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

AM3 CPU HT

AM3 CPU HT

AM3 CPU HT

A88PC-M3S

A88PC-M3S

A88PC-M3S

of

of

of

6 43Tuesday, June 29, 2010

6 43Tuesday, June 29, 2010

6 43Tuesday, June 29, 2010

1

6.1

6.1

6.1

Page 7

5

A

4

3

2

1

Vout=Vref (1.25V) X ( 1+R2/R1 )

=2.5V

R1

R1

49.9 1% 0402

49.9 1% 0402

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

R2

R2

51 1% 0402

51 1% 0402

SB_CPUPWRGD

LDT_STOP#

LDT_RST#

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

CPU_CORE_FB

CPU_CORE_FB_

TP /NI

TP /NI

CPU_M_VREFF

CPU_VDDA

C520

C520

1 2

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

CPU_CLK

CPU_CLK

C5 3900P 50V X7R 0402C5 3900P 50V X7R 0402

CPU_CLK_ TP /NICPU_CLK_ TP /NI

C6 3900P 50V X7R 0402C6 3900P 50V X7R 0402

R6 10K 0402R6 10K 0402

R13 39.2 1% 0402R13 39.2 1% 0402

R15 39.2 1% 0402R15 39.2 1% 0402

R16 510 0402R16 510 0402

R18 510 0402R18 510 0402

R20 300 0402R20 300 0402

R25 300 0402R25 300 0402

CPU_VDDA

CPU_VDDA

12

12

C21

C21

C55

C55

3900P 50V X7R 0402

3900P 50V X7R 0402

TP /NI

TP /NI

R3 169 1% 0402R3 169 1% 0402

CPU_SIC

CPU_SID

CPU_ALERT_L

CPU_VDDA

C521

C521

1 2

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

TEST12

CPU1D

CPU1D

C10

VDDA_1

D10

VDDA_2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AK4

SA0

AL4

ALERT_L

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

F3

M_VDDIO_PWRGD

E12

VDDR_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

M_ZP

A10

TEST25_H

B10

TEST25_L

F10

TEST19

E9

TEST18

AJ7

TEST13

F6

TEST9

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

AH9

TEST12

E5

TEST7

AJ5

TEST6

AH7

TEST3

AJ6

TEST2

C18

RSVD1

C20

RSVD2

F2

RSVD3

G24

RSVD4

G25

RSVD5

H25

RSVD6

L25

RSVD7

L26

RSVD8

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

MISC.

MISC.

THERMTRIP_L

VDDNB_FB_H

INT. MISC.

INT. MISC.

CORE_TYPE

VID5

VID4

SVC/VID3

SVD/VID2

PVIEN/VID1

VID0

THERMDC

THERMDA

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

G5

D2

D1

C1

E3

E2

E1

AG9

AG8

AK7

AL7

AK10

B6

AK11

AL11

G4

G3

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

FBCLKOUT

FBCLKOUT*

TEST24

TEST22

TEST20

TEST27

TEST26

2010/04/14

+1.5V_SUS

K8_VID5

K8_VID4

K8_VID3

K8_VID1

K8_VID0

CPU_THERMTRIP

CPU_TDO

CPU_DBRDY

TP_PSI_L TP /NITP_PSI_L TP /NI

CPU_SID

CPU_ALERT_L

CPU_SIC

CPU_THERMTRIP#_B

R12 44.2 1% 0402R12 44.2 1% 0402

R14 44.2 1% 0402R14 44.2 1% 0402

R17 80.6 1% 0402R17 80.6 1% 0402

R30 330 0402R30 330 0402

1 2

3 4

5 6

RN4

RN4

1K 8P4R 0402

1K 8P4R 0402

CPU_THERMTRIP

RN1

RN1

1K 8P4R 0402

1K 8P4R 0402

7 8

78

56

34

12

CPU_THERMTRIP#_B

ECB

Q79

Q79

2N3904 SOT23

2N3904 SOT23

CPU_CORE_TYPE 39

K8_VID5 39

K8_VID4 39

K8_VID3 39

K8_VID2 39

K8_VID1 39

K8_VID0 39

CPU_THERMDC 31

CPU_THERMDA 31

CPU_PROCHOT# 19

CPU_TDO 23

CPU_DBRDY 23

TP_VDDIOFB1 TP /NITP_VDDIOFB1 TP /NI

TP_VDDIOFB_1 TP /NITP_VDDIOFB_1 TP /NI

VDDNB_FB_H 39

VDDNB_FB_L 39

+1.2V_HT

8/5/8/20

LAYOUT: ROUTE 80 OHM DIFF IMPEDENCE

LAYOUT: PLACE WITHIN 1 INCH OF CPU

for cost down

+1.5V_SUS +1.5V_SUS

TEST27

CPU_PROCHOT#

CPU_THERMTRIP

TEST26

C1 1UF 16V 0805 Y5VC1 1UF 16V 0805 Y5V

1 2

DD

CPU_CORE_FB

CC

CPU_CORE_FB_

+1.5V_SUS

R11

R11

16.9 1% 0402

16.9 1% 0402

R19

R19

16.9 1% 0402

16.9 1% 0402

BB

LDT_RST#16,19,23

LDT_STOP#16,19

SB_CPUPWRGD19,39

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

+1.5V_SUS

RN3

RN3

330 8P4R 0402

330 8P4R 0402

1 2

3 4

5 6

7 8

CLOSE TO CPU

C7

C7

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

1 2

CPU_M_VREFF

12

12

C47

C47

1000P 50V X7R 0402

1000P 50V X7R 0402

C50

C50

+5V

I

O

A

Q1

Q1

AZ1117H-ADJ SOT-223

AZ1117H-ADJ SOT-223

CPU_CLKIN_P18

CPU_CLKIN_N18

HT_CPUPWRGD

HT_CPUPWRGD

LDT_RST_

LDT_RST_

CPU_PRESENT#20

+1.5V_SUS

CPU_TRST#23

CPU_DBREQ#23

CPU_CORE_FB39

CPU_CORE_FB_39

TP_VDDIOSENSE1 TP /NITP_VDDIOSENSE1 TP /NI

VDDR_SENSE

VDDR_SENSE

+1.5V_SUS

LDT_RST#

LDT_STOP#

SB_CPUPWRGD

R1

R2

TP /NI

TP /NI

TP /NI

TP /NI

for cost down

CPU_TDI23

CPU_TCK23

CPU_TMS23

+3.3V_DUAL

R382

R382

10K 0402 /NI

10K 0402 /NI

1 2

2010/05/28

RN5

RN5

330 8P4R 0402

330 8P4R 0402

CPU_THERMTRIP# 20

78

56

34

12

RN34

RN34

TEST20

TEST12

TEST24

TEST22

5

4

78

56

34

12

330 8P4R 0402

330 8P4R 0402

3

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

AM3 CPU CTRL/STRAPS

AM3 CPU CTRL/STRAPS

AM3 CPU CTRL/STRAPS

A88PC-M3S

A88PC-M3S

A88PC-M3S

2

A

6.1

6.1

6.1

of

of

of

7 43Tuesday, June 29, 2010

7 43Tuesday, June 29, 2010

7 43Tuesday, June 29, 2010

1

Page 8

5

A

CPU1B

CPU1B

AG21

MA_CLK_H7

AG20

MA_CLK_L7

AE20

MA_CLK_H6

AE19

DD

MEM_MA0_CLK_H011

MEM_MA0_CLK_L011

MEM_MA0_CLK_H111

MEM_MA0_CLK_L111

MEM_MA0_CS_L111

MEM_MA0_CS_L011

MEM_MA0_ODT111 MEM_MB0_ODT112

MEM_MA0_ODT011

CC

BB

MEM_MA_CAS_L11

MEM_MA_WE_L11

MEM_MA_RAS_L11

MEM_MA_BANK211

MEM_MA_BANK111

MEM_MA_BANK011

MEM_MA_CKE111

MEM_MA_CKE011

MEM_MA_ADD[15..0]11

MEM_MA_DQS_H[8..0]11

MEM_MA_DQS_L[8..0]11

MEM_MA_DM[8..0]11

MEM_MA_ADD[15..0]

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DM[8..0]

U27

U26

W27

W26

W25

U24

G19

H19

G20

G21

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

N25

AA27

M25

M27

N24

AC26

N26

N27

R24

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

G15

AF15

AF19

AJ25

AH29

H15

V27

V24

E20

Y27

L27

P25

Y25

P27

T25

T27

E19

F19

F15

B29

E24

E18

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MEM CHA

MEM CHA

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

5

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

4

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

W30

4

MEM_MA_DATA[0..63]

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DM8

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

R348 1K 0402R348 1K 0402

MEM_MA_DATA[0..63] 11

MEM_MA_CHECK[7..0] 11

3

MEM_MB0_CLK_H012

MEM_MB0_CLK_L012

MEM_MB0_CLK_H112

MEM_MB0_CLK_L112

MEM_MB0_CS_L112

MEM_MB0_CS_L012

MEM_MB0_ODT012

MEM_MB_RESET_L12MEM_MA_RESET_L11

MEM_MB_CAS_L12

MEM_MB_WE_L12

MEM_MB_RAS_L12

MEM_MB_BANK212

MEM_MB_BANK112

MEM_MB_BANK012

MEM_MB_CKE112

MEM_MB_CKE012

MEM_MB_ADD[15..0]12

MEM_MB_DQS_H[8..0]12

MEM_MB_DQS_L[8..0]12

MEM_MB_DM[8..0]12

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DM[8..0]

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

3

CPU1C

CPU1C

AJ19

MB_CLK_H7

AK19

MB_CLK_L7

AL19

MB_CLK_H6

AL18

MB_CLK_L6

U31

MB_CLK_H5

U30

MB_CLK_L5

W29

MB_CLK_H4

W28

MB_CLK_L4

Y31

MB_CLK_H3

Y30

MB_CLK_L3

V31

MB_CLK_H2

W31

MB_CLK_L2

A18

MB_CLK_H1

A19

MB_CLK_L1

C19

MB_CLK_H0

D19

MB_CLK_L0

AE30

MB0_CS_L1

AC31

MB0_CS_L0

AF31

MB0_ODT1

AD29

MB0_ODT0

AE29

MB1_CS_L1

AB31

MB1_CS_L0

AG31

MB1_ODT1

AD31

MB1_ODT0

B19

MB_RESET_L

AC29

MB_CAS_L

AC30

MB_WE_L

AB29

MB_RAS_L

N31

MB_BANK2

AA31

MB_BANK1

AA28

MB_BANK0

M31

MB_CKE1

M29

MB_CKE0

N28

MB_ADD15

N29

MB_ADD14

AE31

MB_ADD13

N30

MB_ADD12

P29

MB_ADD11

AA29

MB_ADD10

P31

MB_ADD9

R29

MB_ADD8

R28

MB_ADD7

R31

MB_ADD6

R30

MB_ADD5

T31

MB_ADD4

T29

MB_ADD3

U29

MB_ADD2

U28

MB_ADD1

AA30

MB_ADD0

AK13

MB_DQS_H7

AJ13

MB_DQS_L7

AK17

MB_DQS_H6

AJ17

MB_DQS_L6

AK23

MB_DQS_H5

AL23

MB_DQS_L5

AL28

MB_DQS_H4

AL29

MB_DQS_L4

D31

MB_DQS_H3

C31

MB_DQS_L3

C24

MB_DQS_H2

C23

MB_DQS_L2

D17

MB_DQS_H1

C17

MB_DQS_L1

C14

MB_DQS_H0

C13

MB_DQS_L0

AJ14

MB_DM7

AH17

MB_DM6

AJ23

MB_DM5

AK29

MB_DM4

C30

MB_DM3

A23

MB_DM2

B17

MB_DM1

B13

MB_DM0

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

2

MEM_MB_DATA[0..63]

MEM_MB_DATA63

AH13

MEM CHB

MEM CHB

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK[7..0]

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

1

R347 1K 0402R347 1K 0402

MEM_MB_DATA[0..63] 12

MEM_MB_CHECK[7..0] 12

MEM_MB_EVENT_L 12MEM_MA_EVENT_L 11

+1.5V_SUS+1.5V_SUS

A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

AM3 CPU MEMORY CHA/B

AM3 CPU MEMORY CHA/B

AM3 CPU MEMORY CHA/B

A88PC-M3S

A88PC-M3S

A88PC-M3S

of

of

of

8 43Tuesday, June 29, 2010

8 43Tuesday, June 29, 2010

8 43Tuesday, June 29, 2010

1

6.1

6.1

6.1

Page 9

5

A

+V_CPU +V_CPU CPU_VDDNB

DD

CC

BB

CPU1E

CPU1E

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

H11

VDD_13

H23

VDD_14

J8

VDD_15

J12

VDD_16

J14

VDD_17

J16

VDD_18

J18

VDD_19

J20

VDD_20

J22

VDD_21

J24

VDD_22

K7

VDD_23

K9

VDD_24

K11

VDD_25

K13

VDD_26

K15

VDD_27

K17

VDD_28

K19

VDD_29

K21

VDD_30

K23

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

L10

VDD_35

L12

VDD_36

L14

VDD_37

L16

VDD_38

L18

VDD_39

L20

VDD_40

L22

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

M11

VDD_46

M13

VDD_47

M15

VDD_48

M17

VDD_49

M19

VDD_50

M21

VDD_51

M23

VDD_52

N8

VDD_53

N10

VDD_54

N12

VDD_55

N14

VDD_56

N16

VDD_57

N18

VDD_58

N20

VDD_59

N22

VDD_60

P7

VDD_61

P9

VDD_62

P11

VDD_63

P13

VDD_64

P15

VDD_65

P17

VDD_66

P19

VDD_67

P21

VDD_68

P23

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

R10

VDD_73

R12

VDD_74

R14

VDD_75

R16

VDD_76

R18

VDD_77

R20

VDD_78

R22

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

T11

VDD_84

T13

VDD_85

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

A3

VSS_1

A7

VSS_2

A9

VSS_3

A11

VSS_4

B4

VSS_5

B9

VSS_6

B11

VSS_7

B14

VSS_8

B16

VSS_9

B18

VSS_10

B20

VSS_11

B22

VSS_12

B24

VSS_13

B26

VSS_14

B28

VSS_15

B30

VSS_16

C3

VSS_17

D14

VSS_18

D16

VSS_19

D18

VSS_20

D20

VSS_21

D22

VSS_22

D24

VSS_23

D26

VSS_24

D28

VSS_25

D30

VSS_26

E11

VSS_27

F4

VSS_28

F14

VSS_29

F16

VSS_30

F18

VSS_31

F20

VSS_32

F22

VSS_33

F24

VSS_34

F26

VSS_35

F28

VSS_36

F30

VSS_37

G9

VSS_38

G11

VSS_39

H8

VSS_40

H10

VSS_41

H12

VSS_42

H14

VSS_43

H16

VSS_44

H18

VSS_45

H24

VSS_46

H26

VSS_47

H28

VSS_48

H30

VSS_49

J4

VSS_50

POWER/GND1

POWER/GND1

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

5

4

CPU1F

CPU1F

T15

VDD_86

T17

VDD_87

T19

VDD_88

T21

VDD_89

T23

VDD_90

U8

VDD_91

U10

VDD_92

U12

VDD_93

U14

VDD_94

U16

VDD_95

U18

VDD_96

U20

VDD_97

U22

VDD_98

V9

VDD_99

V11

VDD_100

V13

VDD_101

V15

VDD_102

V17

VDD_103

V19

VDD_104

V21

VDD_105

V23

VDD_106

W4

VDD_107

W5

VDD_108

W8

VDD_109

W10

VDD_110

W12

VDD_111

W14

VDD_112

W16

VDD_113

W18

VDD_114

W20

VDD_115

W22

VDD_116

Y2

VDD_117

Y3

VDD_118

Y7

VDD_119

Y9

VDD_120

Y11

VDD_121

Y13

VDD_122

Y15

VDD_123

Y17

VDD_124

Y19

VDD_125

Y21

VDD_126

Y23

VDD_127

AA8

VDD_128

AA10

VDD_129

AA12

VDD_130

AA14

VDD_131

AA16

VDD_132

AA18

VDD_133

AA20

VDD_134

AA22

VDD_135

AB7

VDD_136

AB9

VDD_137

AB11

VDD_138

AB13

VDD_139

AB15

VDD_140

AB17

VDD_141

AB19

VDD_142

AB21

VDD_143

AB23

VDD_144

AC4

VDD_145

AC5

VDD_146

AC8

VDD_147

AC10

VDD_148

AC12

VDD_149

AC14

VDD_150

AC16

VDD_151

AC18

VDD_152

AC20

VDD_153

AC22

VDD_154

AD2

VDD_155

AD3

VDD_156

AD7

VDD_157

AD9

VDD_158

AD11

VDD_159

AD23

VDD_160

AE10

VDD_161

AE12

VDD_162

AF7

VDD_163

AF9

VDD_164

AF11

VDD_165

AG4

VDD_166

AG5

VDD_167

AG7

VDD_168

AH2

VDD_169

AH3

VDD_170

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

4

3

CPU1G

CPU1G

M12

VSS_86

M14

VSS_87

M16

VSS_88

M18

VSS_89

M20

VSS_90

M22

VSS_91

N4

VSS_92

N5

VSS_93

N7

VSS_94

N9

VSS_95

N11

VSS_96

N13

VSS_97

N15

VSS_98

N17

VSS_99

N19

VSS_100

N21

VSS_101

N23

VSS_102

P2

VSS_103

P3

VSS_104

P8

VSS_105

P10

VSS_106

P12

VSS_107

P14

VSS_108

P16

VSS_109

P18

VSS_110

P20

VSS_111

P22

VSS_112

R7

VSS_113

R9

VSS_114

R11

VSS_115

R13

VSS_116

R15

VSS_117

R17

VSS_118

R19

VSS_119

R21

VSS_120

R23

VSS_121

T8

VSS_122

T10

VSS_123

T12

VSS_124

T14

VSS_125

T16

VSS_126

T18

VSS_127

T20

VSS_128

T22

VSS_129

U4

VSS_130

U5

VSS_131

U7

VSS_132

U9

VSS_133

U11

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W7

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

AA4

AA5

AA7

AA9

POWER/GND2

POWER/GND2

E10

F11

G10

G12

H20

AE7

+1.2V_HT

12

C57

C57

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

A4

VDDNB_1

A6

VDDNB_2

B5

VDDNB_3

B7

VDDNB_4

C6

VDDNB_5

C8

VDDNB_6

D7

VDDNB_7

D9

VDDNB_8

E8

VDDNB_9

VDDNB_10

F9

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

B2

NP/RSVD

NP/VSS1

NP/VSS2

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

C499

C499

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

1 2

+1.2V_HT

12

C498

C498

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

POWER/GND3

POWER/GND3

C501

C501

1UF 16V 0805 Y5V /NI

1UF 16V 0805 Y5V /NI

1 2

12

C519

C519

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

C502

C502

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

1 2

◆

3

2

TP /NI

TP /NI

1P2V_HT

1P2V_HT

+1.2V_HT

+1.5V_SUS

C500

C500

1UF 16V 0805 Y5V /NI

1UF 16V 0805 Y5V /NI

1 2

2

1

+1.2V_HT

CPU1H

CPU1H

AJ1

VLDT_A_1

AJ2

VLDT_A_2

AJ3

VLDT_A_3

AJ4

VLDT_A_4

A12

VDDR_1

B12

VDDR_2

C12

VDDR_3

D12

VDDR_4

M24

VDDIO_1

M26

VDDIO_2

M28

VDDIO_3

M30

VDDIO_4

P24

VDDIO_5

P26

VDDIO_6

P28

VDDIO_7

P30

VDDIO_8

T24

VDDIO_9

T26

VDDIO_10

T28

VDDIO_11

T30

VDDIO_12

V25

VDDIO_13

V26

VDDIO_14

V28

VDDIO_15

V30

VDDIO_16

Y24

VDDIO_17

Y26

VDDIO_18

Y28

VDDIO_19

Y29

VDDIO_20

AB24

VDDIO_21

AB26

VDDIO_22

AB28

VDDIO_23

AB30

VDDIO_24

AC24

VDDIO_25

AD26

VDDIO_26

AD28

VDDIO_27

AD30

VDDIO_28

AF30

VDDIO_29

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

12

C59

C59

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

12

C504

C504

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

POWER/GND4

POWER/GND4

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

+1.2V_HT_CPU

12

C503

C503

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

AM3 CPU POWER/GND

AM3 CPU POWER/GND

AM3 CPU POWER/GND

A88PC-M3S

A88PC-M3S

A88PC-M3S

1

+1.2V_HT_CPU

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

12

C56

C56

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

9 43Tuesday, June 29, 2010

9 43Tuesday, June 29, 2010

9 43Tuesday, June 29, 2010

+1.2V_HT

of

of

of

A

6.1

6.1

6.1

Page 10

A

+1.5V_SUS

12

C33

C33

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

5 4 3 2

12

C34

C34

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

C37

C37

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C38

C38

1UF 10V Y5V 0402

1UF 10V Y5V 0402

12

C39

C39

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

2010/05/19

ADD C52,C53

12

C52

C52

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C53

C53

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

Place cpu socket bottom

+1.5V_SUS

12

BC21

BC21

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC22

BC22

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

2010/05/19 ADD

12

BC43

BC43

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

DD

+1.5V_SUS

12

C13

C13

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

PLACE BOTTOM SIDE

12

C14

C14

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C15

C15

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C16

C16

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C17

C17

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C18

C18

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C19

C19

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

CPU_VDDNB

12

BC48

BC48

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC49

BC49

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC44

BC44

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

1

12

BC41

BC41

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC20

BC20

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+1.5V_SUS

DECOUPLING BETWEEN PROCESSOR AND DIMMS

12

C20

C20

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C25

C25

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

CC

CPU_VDDNB

12

C36

C36

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU

12

C40

C40

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C330

C330

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C41

C41

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C22

C22

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C11

C11

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C42

C42

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C48

C48

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C23

C23

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C46

C46

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C49

C49

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

+V_CPU

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C60

C60

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C43

C43

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C24

C24

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C26

C26

12

C44

C44

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

12

C27

C27

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

C45

C45

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C28

C28

12

12

C29

C29

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C30

C30

12

C31

C31

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BB

+V_CPU

12

BC24

BC24

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU

12

BC47

BC47

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

+V_CPU

12

BC32

BC32

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU

12

BC37

BC37

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC25

BC25

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC29

BC29

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC33

BC33

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC38

BC38

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC26

BC26

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC30

BC30

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC34

BC34

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC39

BC39

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC27

BC27

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC31

BC31

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC35

BC35

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC40

BC40

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC46

BC46

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

BC51

BC51

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

12

BC36

BC36

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

12

BC50

BC50

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

+V_CPU

12

C51

C51

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C32

C32

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

12

C35

C35

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DECOUPLING

DECOUPLING

DECOUPLING

A88PC-M3S

A88PC-M3S

A88PC-M3S

A

6.1

6.1

10 43Tuesday, June 29, 2010

10 43Tuesday, June 29, 2010

10 43Tuesday, June 29, 2010

6.1

of

of

of

Page 11

5

A

4

3

2

1

DDR3_A1

DDR3_A1A

DDR3_A1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DM0/DQS9

126

DQS9-

134

DM1/DQS10

135

DQS10-

143

DM2/DQS11

144

DQS11-

152

DM3/DQS12

153

DQS12-

203

DM4/DQS13

204

DQS13-

212

DM5/DQS14

213

DQS14-

221

DM6/DQS15

222

DQS15-

230

DM7/DQS16

231

DQS16-

161

DM8/DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

BLACK

A10

A11

A12

A13

A14

A15

DDR3-240 PIN-R

DDR3-240 PIN-R

BLACK

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

0.1UF 16V Y5V 0402C515 0.1UF 16V Y5V 0402C515

0.1UF 16V Y5V 0402C514 0.1UF 16V Y5V 0402C514

0.1UF 16V Y5V 0402C513 0.1UF 16V Y5V 0402C513 0.1UF 16V Y5V 0402C483 0.1UF 16V Y5V 0402C483

70

55

174

196

172

171

+1.5V_SUS +1.5V_SUS

R325

R325

16.9 1% 0402

16.9 1% 0402

DIMM_DQ_VREF DIMM_CA_VREF

R322

R322

16.9 1% 0402

16.9 1% 0402

5

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

MEM_MA_DATA[0..63]

MEM_MA_DATA63

234

MEM_MA_DATA62

233

MEM_MA_DATA61

228

MEM_MA_DATA60

227

MEM_MA_DATA59

115

MEM_MA_DATA58

114

MEM_MA_DATA57

109

MEM_MA_DATA56

108

MEM_MA_DATA55

225

MEM_MA_DATA54

224

MEM_MA_DATA53

219

MEM_MA_DATA52

218

MEM_MA_DATA51

106

MEM_MA_DATA50

105

MEM_MA_DATA49

100

MEM_MA_DATA48

99

MEM_MA_DATA47

216

MEM_MA_DATA46

215

MEM_MA_DATA45

210

MEM_MA_DATA44

209

MEM_MA_DATA43

97

MEM_MA_DATA42

96

MEM_MA_DATA41

91

MEM_MA_DATA40

90

MEM_MA_DATA39

207

MEM_MA_DATA38

206

MEM_MA_DATA37

201

MEM_MA_DATA36

200

MEM_MA_DATA35

88

MEM_MA_DATA34

87

MEM_MA_DATA33

82

MEM_MA_DATA32

81

MEM_MA_DATA31

156

MEM_MA_DATA30

155

MEM_MA_DATA29

150

MEM_MA_DATA28

149

MEM_MA_DATA27

37

MEM_MA_DATA26

36

MEM_MA_DATA25

31

MEM_MA_DATA24

30

MEM_MA_DATA23

147

MEM_MA_DATA22

146

MEM_MA_DATA21

141

MEM_MA_DATA20

140

MEM_MA_DATA19

28

MEM_MA_DATA18

27

MEM_MA_DATA17

22

MEM_MA_DATA16

21

MEM_MA_DATA15

138

MEM_MA_DATA14

137

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

19

MEM_MA_DATA10

18

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0

3

DQ0

68

53

167

MEM_MA_DATA[0..63]8

R310

R310

16.9 1% 0402

16.9 1% 0402

R345

R345

16.9 1% 0402

16.9 1% 0402

DIMM_CA_VREF12

DIMM_DQ_VREF12

MEM_MA_CKE08

MEM_MA_CKE18

MEM_MA_BANK08

MEM_MA_BANK18

MEM_MA_BANK28

MEM_MA_RESET_L8

MEM_MA_WE_L8

MEM_MA_RAS_L8

MEM_MA_CAS_L8

MEM_MA0_CS_L08

MEM_MA0_CS_L18

MEM_MA0_ODT08

MEM_MA0_ODT18

MEM_MA0_CLK_L18

MEM_MA0_CLK_H18

MEM_MA0_CLK_L08

MEM_MA0_CLK_H08

MEM_MA_EVENT_L8

0.1UF 16V Y5V 0402C481 0.1UF 16V Y5V 0402C481

0.1UF 16V Y5V 0402C509 0.1UF 16V Y5V 0402C509

4

SDATA12,18,20,39

SCLK12,18,20,39

MEM_MA_DQS_L[8..0]

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_L0

MEM_MA_DQS_H0

MEM_MA_DQS_L1

MEM_MA_DQS_H1

MEM_MA_DQS_L2

MEM_MA_DQS_H2

MEM_MA_DQS_L3

MEM_MA_DQS_H3

MEM_MA_DQS_L4

MEM_MA_DQS_H4

MEM_MA_DQS_L5

MEM_MA_DQS_H5

MEM_MA_DQS_L6

MEM_MA_DQS_H6

MEM_MA_DQS_L7

MEM_MA_DQS_H7

MEM_MA_DQS_L8

MEM_MA_DQS_H8

MEM_MA_DM[8..0]

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DM8

MEM_MA_CHECK[7..0]

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK4

MEM_MA_CHECK5

MEM_MA_CHECK6

MEM_MA_CHECK7

MEM_MA_ADD[15..0]

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_DQS_L[8..0]8

MEM_MA_DQS_H[8..0]8

DD

MEM_MA_DM[8..0]8

CC

MEM_MA_CHECK[7..0]8

MEM_MA_ADD[15..0]8

BB

+1.5V_SUS

+3.3V

DIMM_CA_VREF

DIMM_DQ_VREF

MEM_VTT

DDR3_A1B

DDR3_A1B

51

54

57

60

62

65

66

69

72

75

78

170

173

176

179

182

183

186

189

191

194

197

236

67

1

117

237

50

169

71

190

52

168

73

192

74

193

76

195

77

64

63

185

184

48

49

187

198

DDR3-240 PIN-R

DDR3-240 PIN-R

C518

C518

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

1 2

VDDQ1 (P)

VDDQ2 (P)

VDDQ3 (P)

VDDQ4 (P)

VDDQ5 (P)

VDDQ6 (P)

VDDQ7 (P)

VDDQ8 (P)

VDDQ9 (P)

VDDQ10 (P)

VDDQ11 (P)

VDD1 (P)

VDD2 (P)

VDD3 (P)

VDD4 (P)

VDD5 (P)

VDD6 (P)

VDD7(P)

VDD8(P)

VDD9(P)

VDD10(P)

VDD11(P)

VDDSPD(P)

VREFCA

VREFDQ

SA0

SA1

CKE0

CKE1

BA0

BA1

A16/BA2

RESET

WERASCASS-0

S-1

ODT0

ODT1

CK-1

CK1

CK-0

CK0

FREE1

FREE2

FREE3

FREE4

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

SA2

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

VTT

240

VTT

MEM_VTT

BIOSTAR'S PROPRIETARY INFORMATION

◇◆

Any unauthorized use, reproduction,

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

3

◆

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR3 DIMMA1

DDR3 DIMMA1

DDR3 DIMMA1

A88PC-M3S

A88PC-M3S

A88PC-M3S

11 43Tuesday, June 29, 2010

11 43Tuesday, June 29, 2010

11 43Tuesday, June 29, 2010

1

A

6.1

6.1

6.1

of

of

of

Page 12

5

DCCBBAA

DDR3_B1

DDR3_B1A

DDR3_B1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DM0/DQS9

126

DQS9-

134

DM1/DQS10

135

DQS10-

143

DM2/DQS11

144

DQS11-

152

DM3/DQS12

153

DQS12-

203

DM4/DQS13

204

DQS13-

212

DM5/DQS14

213

DQS14-

221

DM6/DQS15

222

DQS15-

230

DM7/DQS16

231

DQS16-

161

DM8/DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

BLACK

A10

A11

A12

A13

A14

A15

DDR3-240 PIN-R

DDR3-240 PIN-R

BLACK

NC/PAR_IN

NC/ERR_OUT

70

55

174

196

172

171

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

NC/TEST4

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

MEM_MB_DATA[0..63]

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

SDATA11,18,20,39

SCLK11,18,20,39

MEM_MB_DQS_L[8..0]

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_L0

MEM_MB_DQS_H0

MEM_MB_DQS_L1

MEM_MB_DQS_H1

MEM_MB_DQS_L2

MEM_MB_DQS_H2

MEM_MB_DQS_L3

MEM_MB_DQS_H3

MEM_MB_DQS_L4

MEM_MB_DQS_H4

MEM_MB_DQS_L5

MEM_MB_DQS_H5

MEM_MB_DQS_L6

MEM_MB_DQS_H6

MEM_MB_DQS_L7

MEM_MB_DQS_H7

MEM_MB_DQS_L8

MEM_MB_DQS_H8

MEM_MB_DM[8..0]

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DM8

MEM_MB_CHECK[7..0]

MEM_MB_CHECK0

MEM_MB_CHECK1

MEM_MB_CHECK2

MEM_MB_CHECK3

MEM_MB_CHECK4

MEM_MB_CHECK5

MEM_MB_CHECK6

MEM_MB_CHECK7

MEM_MB_ADD[15..0]

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_DQS_L[8..0]8

MEM_MB_DQS_H[8..0]8

D

MEM_MB_DM[8..0]8

MEM_MB_CHECK[7..0]8

MEM_MB_ADD[15..0]8

5

4

MEM_MB_DATA[0..63]8

DIMM_CA_VREF11

DIMM_DQ_VREF11

MEM_MB_CKE08

MEM_MB_CKE18

MEM_MB_BANK08

MEM_MB_BANK18

MEM_MB_BANK28

MEM_MB_RESET_L8

MEM_MB_WE_L8

MEM_MB_RAS_L8

MEM_MB_CAS_L8

MEM_MB0_CS_L08

MEM_MB0_CS_L18

MEM_MB0_ODT08

MEM_MB0_ODT18

MEM_MB0_CLK_L18

MEM_MB0_CLK_H18

MEM_MB0_CLK_L08

MEM_MB0_CLK_H08

MEM_MB_EVENT_L8

MEM_VTT

1 2

4

C472

C472

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+1.5V_SUS

+3.3V

DIMM_CA_VREF

DIMM_DQ_VREF

+3.3V

DDR3_B1B

DDR3_B1B

51

54

57

60

62

65