Page 1

5

4

3

2

1

PAGE

1

2

D D

C C

B B

3

4

5

6-10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

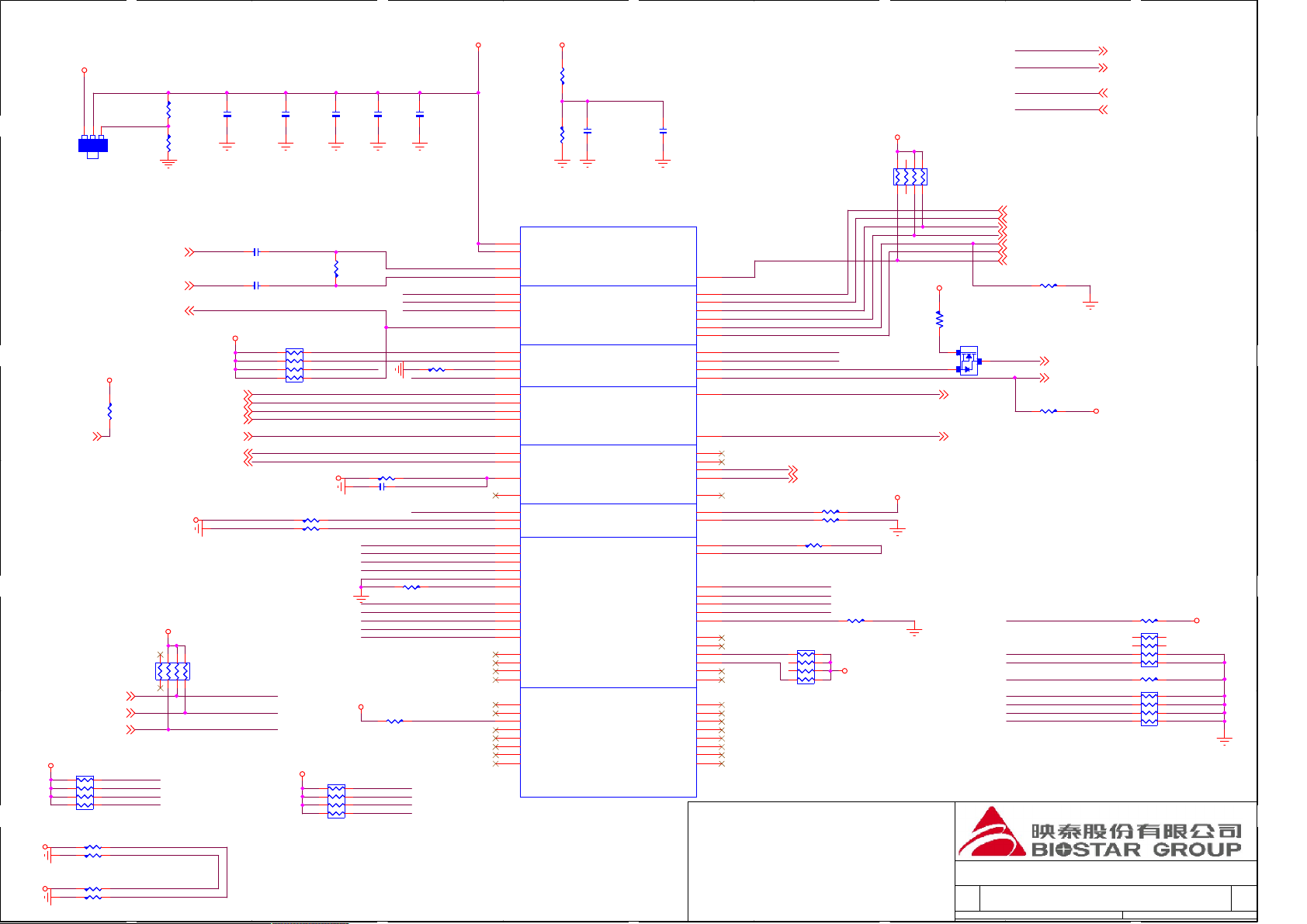

CONTENTS

COVER

BLOCK DIAGRAM

POW ER DE LIVERY

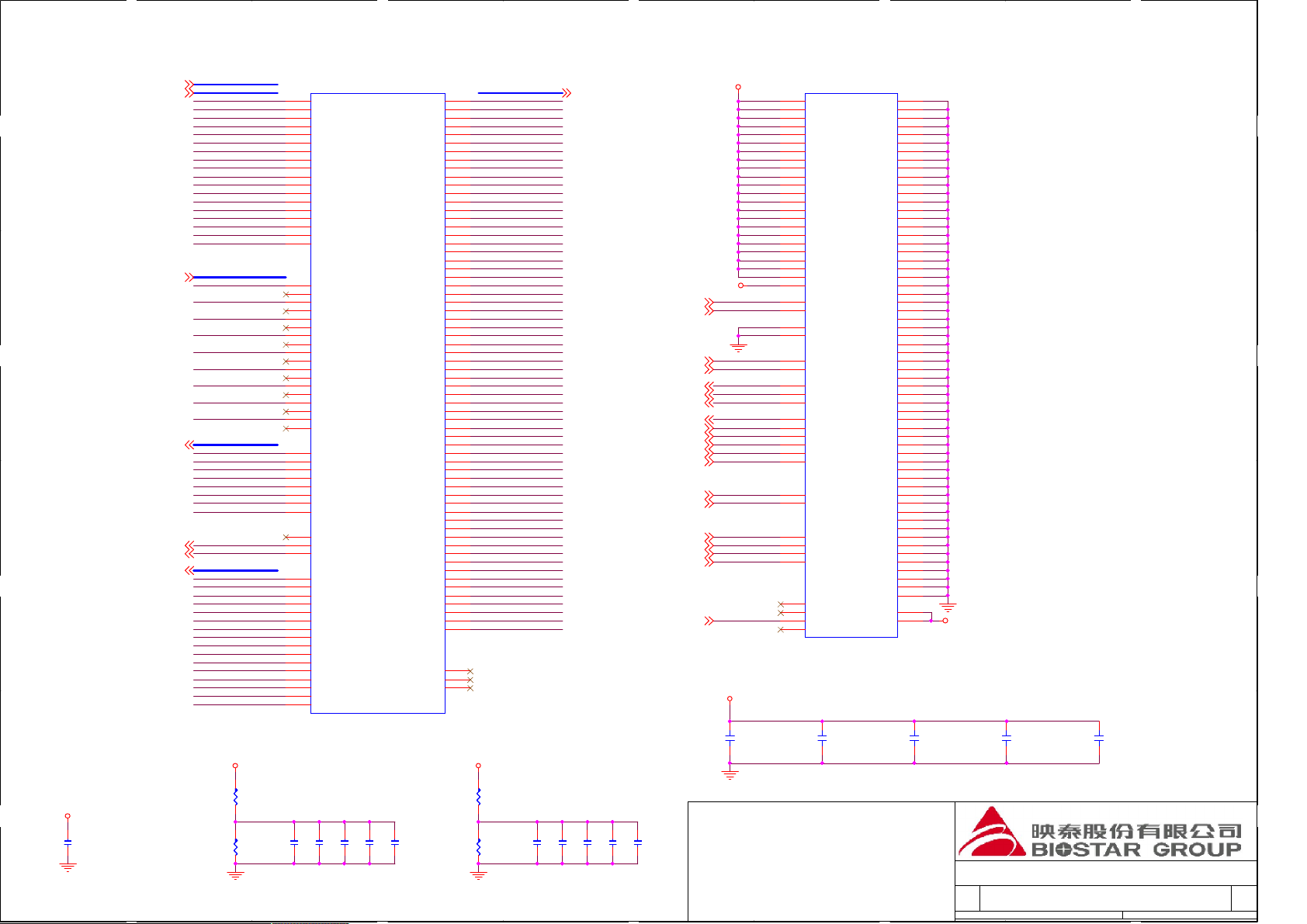

CLOCK DISTRIB UTION

REVIS ION HISTROY

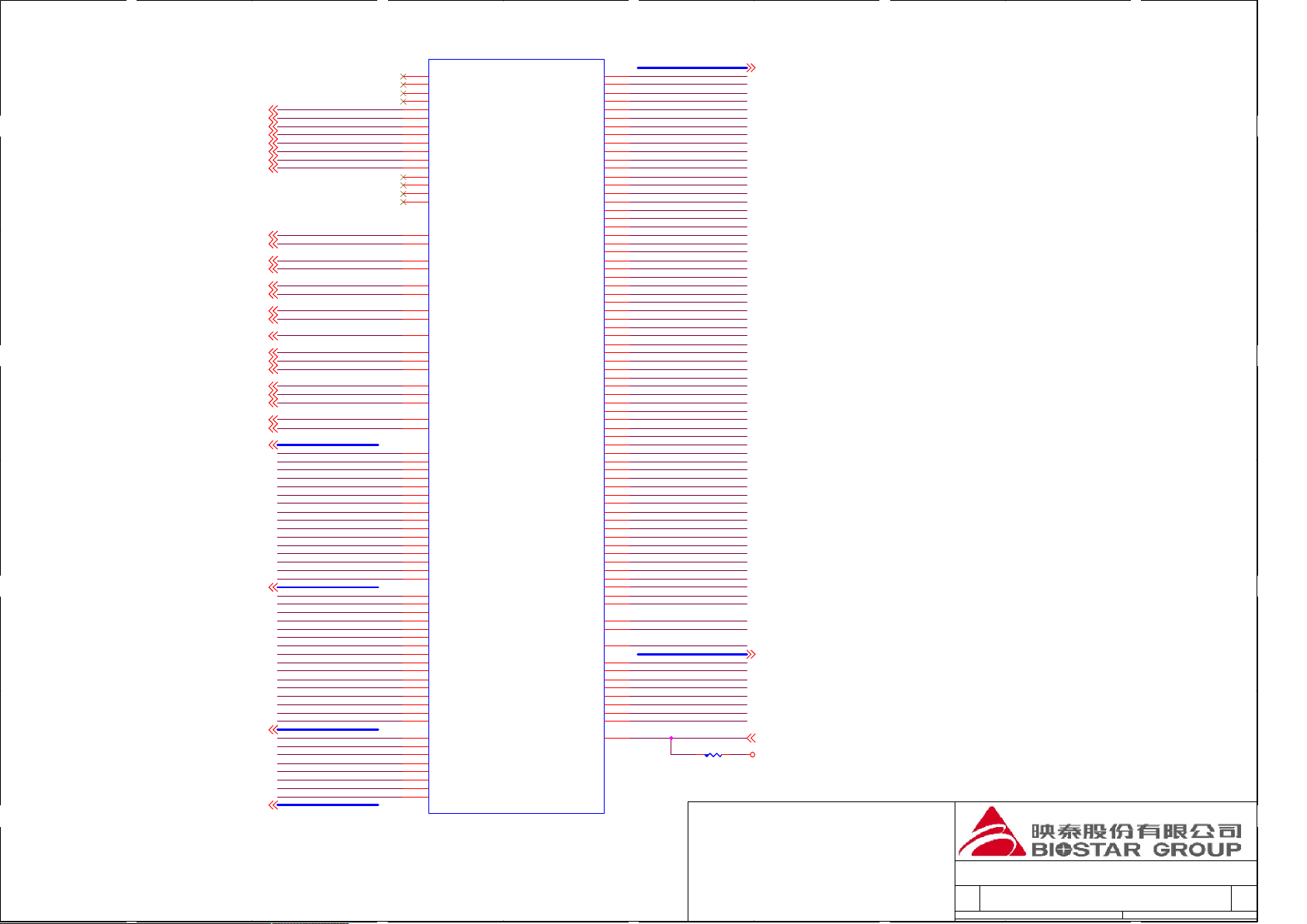

SKTAM3 CPU

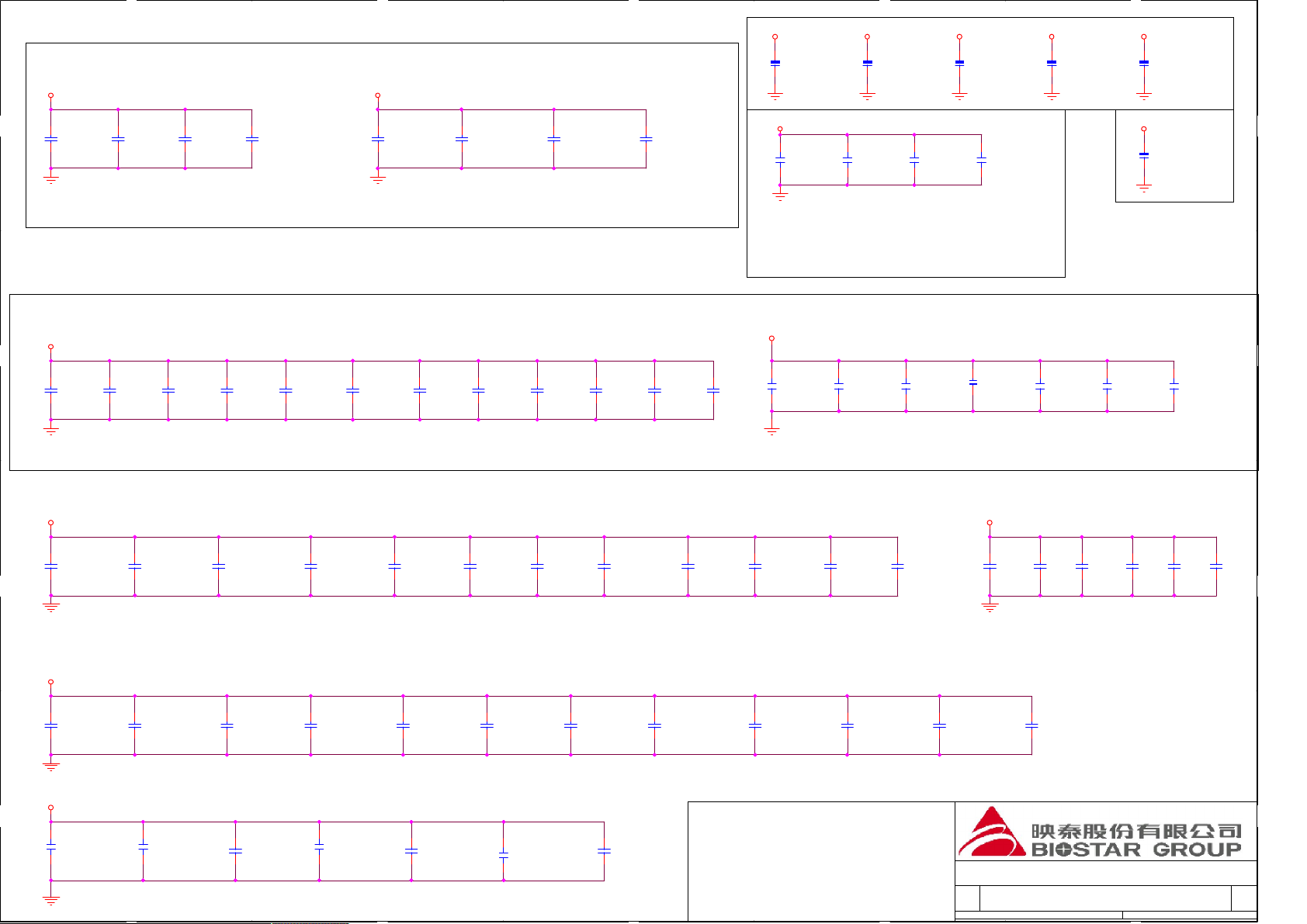

CPU DE COUPL ING

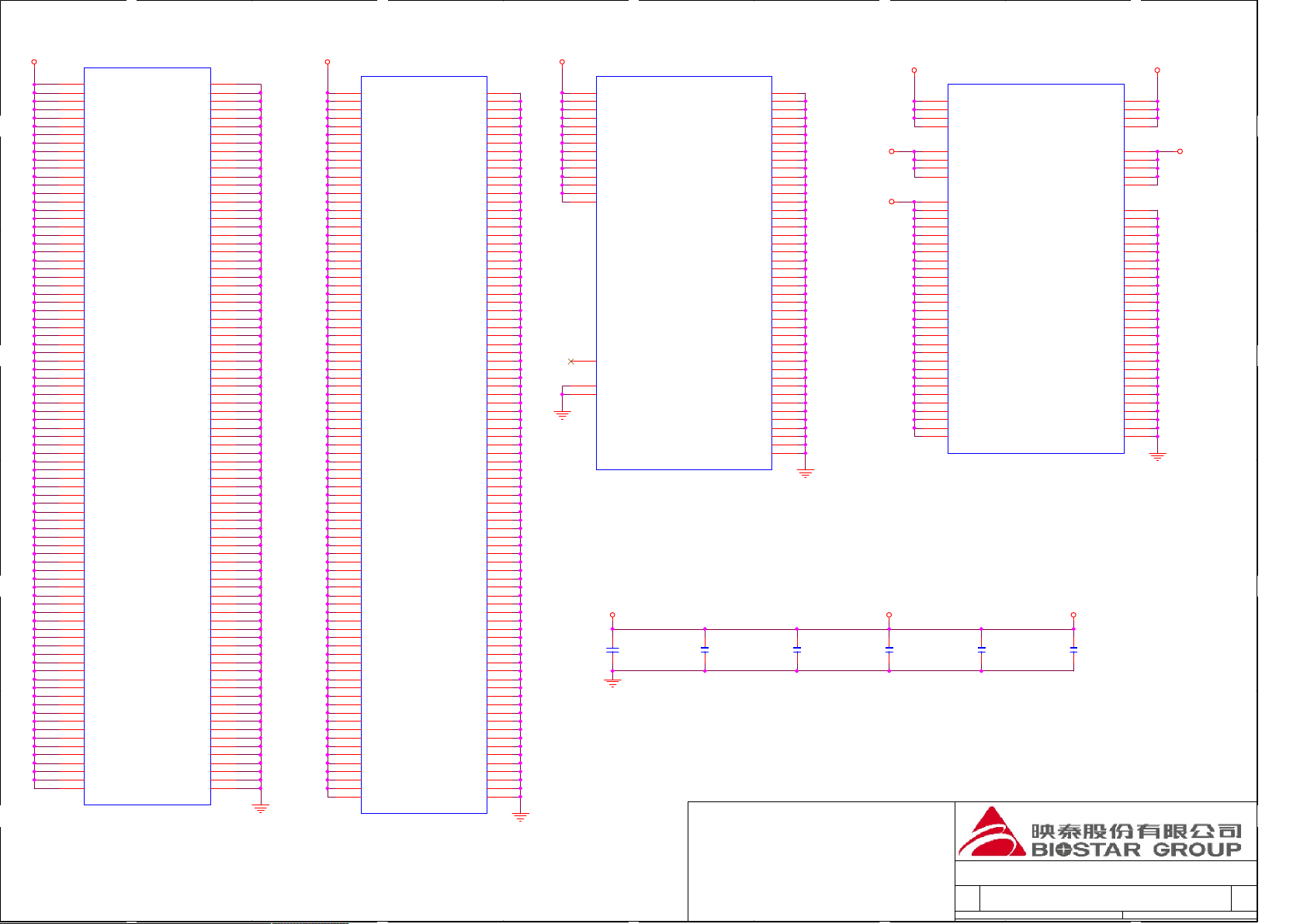

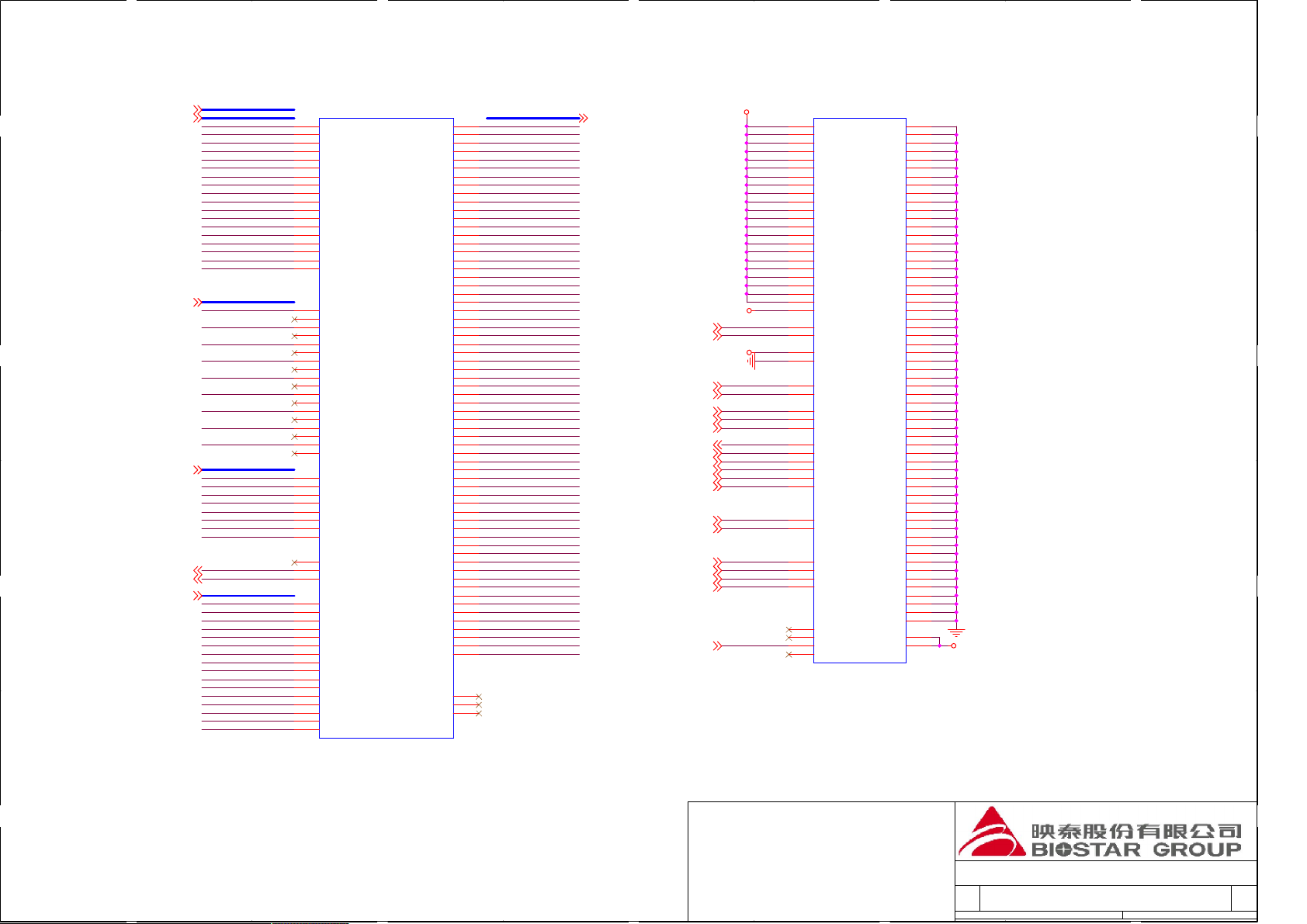

DDR3 DIMM A1

DDR3 DIMM B1

DDR3 DIMM A2

DDR3 DIMM B2

RS780-HT LINK

RS780-PCIE

RS780-SYSTEM

RS780-POW ER

CLOCK GEN

SB71 0-PCIE/PCI/C PU/LPC

SB71 0-ACP I/GPIO /USB /AUD

SB71 0-SATA/IDE/HWM/SPI

SB71 0-POWER DECOUPLING

SB71 0-STRAP S

SB71 0-ACC

PCI-E X 16 S LOT

PCI SLOT

IDE ATA 133 & FORNT USB

USB CONN

CODEC ALC662

AUDIO CONNECTOR

SUPER I/O I TE8728

FAN CO NTROL/E UP

FDD / P S2 CONN

COM&L PT CONNECTOR

ATX PW R / FRONT PANEL / LED

PW RGD / MISC DC-DC

VCC_CO RE DC-D C CONV ER

MEMORY POW ER

NB/SB CORE POW ER

PCI-E G IGA LAN(RE ALTEK 8111EL)

BOM

REV:6.0

2011/02/09

CPU :

AM3

DDR3 X 4 Dual channel , PCI-Ex16 X 1 , PCI-Ex1

X 2 , PCI X 3 , RTL8111EL PCI-E Lan , AMD AM3

System Chipset :

AMD RS780

AMD SB750

On Board Chip :

Clock Gen. -- RTM880N-793

Azalia Codec -- ALC662

GigaBit Lan -- RealTek RTL8111EL

PWM Controller -- ST6717A

Super I/O -- IT8728

SPI Flash 8Mb

Expansion Slot :

PCI Express x16 Slot * 1

PCI Express x1 Slot * 2

PCI Slot * 3

Heatsink :

NB: NB-NF61

SB: SB SMALL-AMD

MOS: NONE

A78LA-A3S ( RS780L&SB710)

I/O Pannel :

HW Engineer:

47-RIOBRACKET-68

A A

PCB SIZE :

205.09 X 304.80

1080

HW Leader:

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Custom

Custom

Custom

Date:

Date:

A78LA-A3S

A78LA-A3S

A78LA-A3S

COVER

COVER

COVER

6.0

6.0

1 43Wednesday, February 09, 2011

1 43Wednesday, February 09, 2011

1 43Wednesday, February 09, 2011

6.0

of

of

of

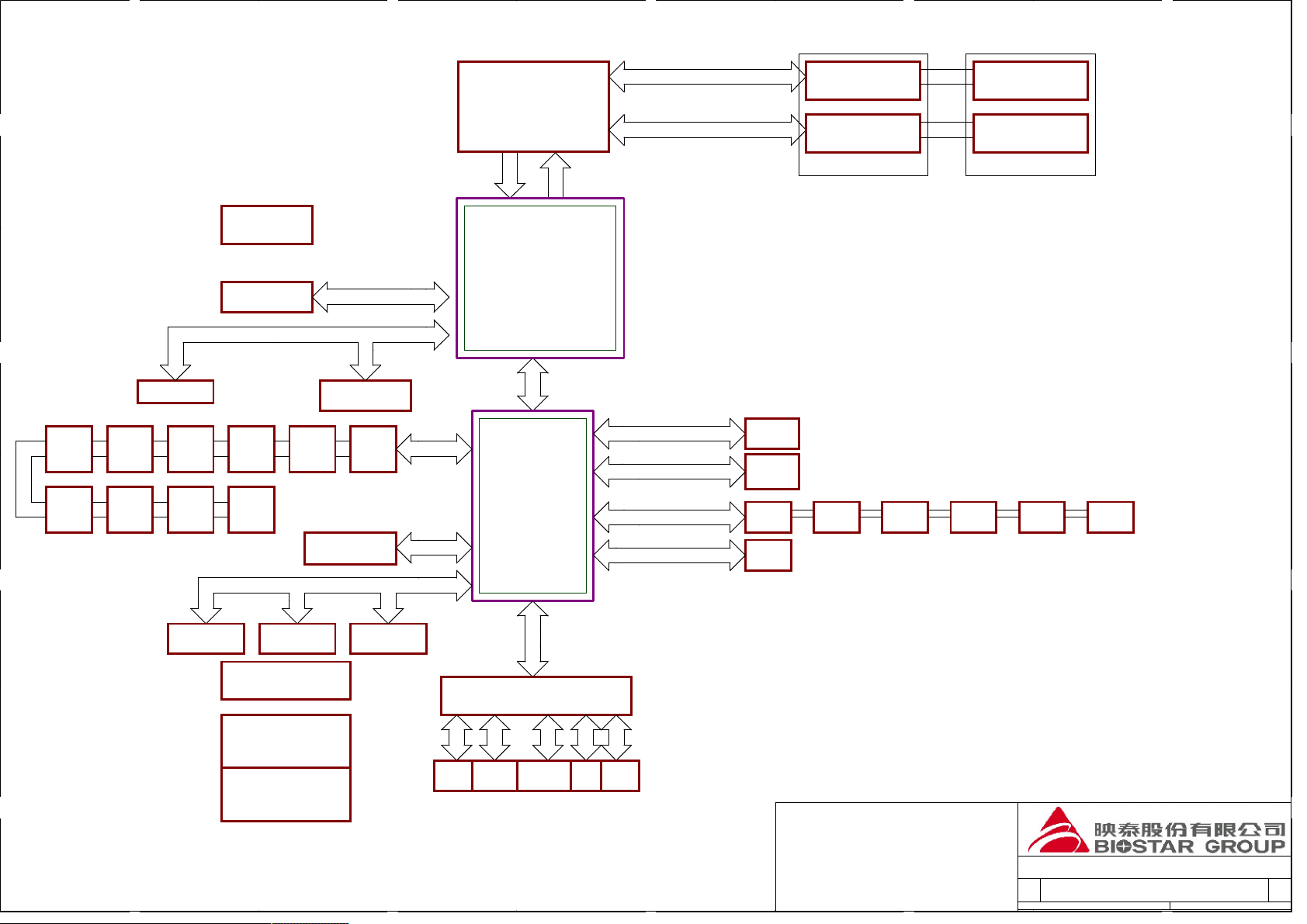

Page 2

5

4

3

2

1

UNBUFFERED

AMD

AM3

D D

HyperTransport

LINK

Clock

Generator

RTM880N-793

16X

PCIE

16X

AM 3 SOCKET

16x16

OUT

IN

AMD NB

RS780

HyperT ransport LIN K0 CP U I/F

INTEG RATED GRA PHI CS

LVTM

1 16X PCI E VID EO I/F

1 4X PCI E I/F W ITH SB

6 1X PCI E I/F

128bit

DDR3 DIMM1

UNBUFFERED

DDR3 DIMM2

DDRII FIRST LOGICAL DIMM

UNBUFFERED

DDR3 DIMM3

UNBUFFERED

DDR3 DIMM4

DDRII SECOND LOGICAL DIMM

C C

ATI SB

SB710

USB2.0 (12)

SATA II

ACP I

LPC I/F

INT R TC

4X

PCIE

SPI I/F SPI ROM

HD AUDIO I/F

SATA II I/F

ATA 66/100/133

I/F

AZILIA

CODEC

SATA#1

IDE

SATA#2

SATA#3

SATA#5 SATA#6

GIGABIT

RTL8111EL

USB-5

USB-6

USB-4

USB-7 SATA#4

USB-3

USB-8

B B

USB-2

USB-9

4 1X PCIE

INTERFACE

PCI BUS

PCIE GPP0

X1

USB-1

BOOTSTRAPS

ROM (SB)

USB-0

I2C

I/F

USB

2.0

AC97 2.3/ A ZALI A

ATA 66/100/133

HW M ONITOR

PCI SLOT

#1

A A

PCI SLOT

#2

DESKTOP M2

POWER

RX780/RX740

CORE & PCIE

POWER

DDR

MEMORY

POWER

PCI SLOT

#3

FLOPPY

ITE LPC SIO

8728

KBD

MOUSE

HW

MONITOR

LPT

COM*2

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

A78LA-A3S

A78LA-A3S

A78LA-A3S

2 43Thursday, January 27, 2011

2 43Thursday, January 27, 2011

2 43Thursday, January 27, 2011

of

of

6.0

6.0

6.0

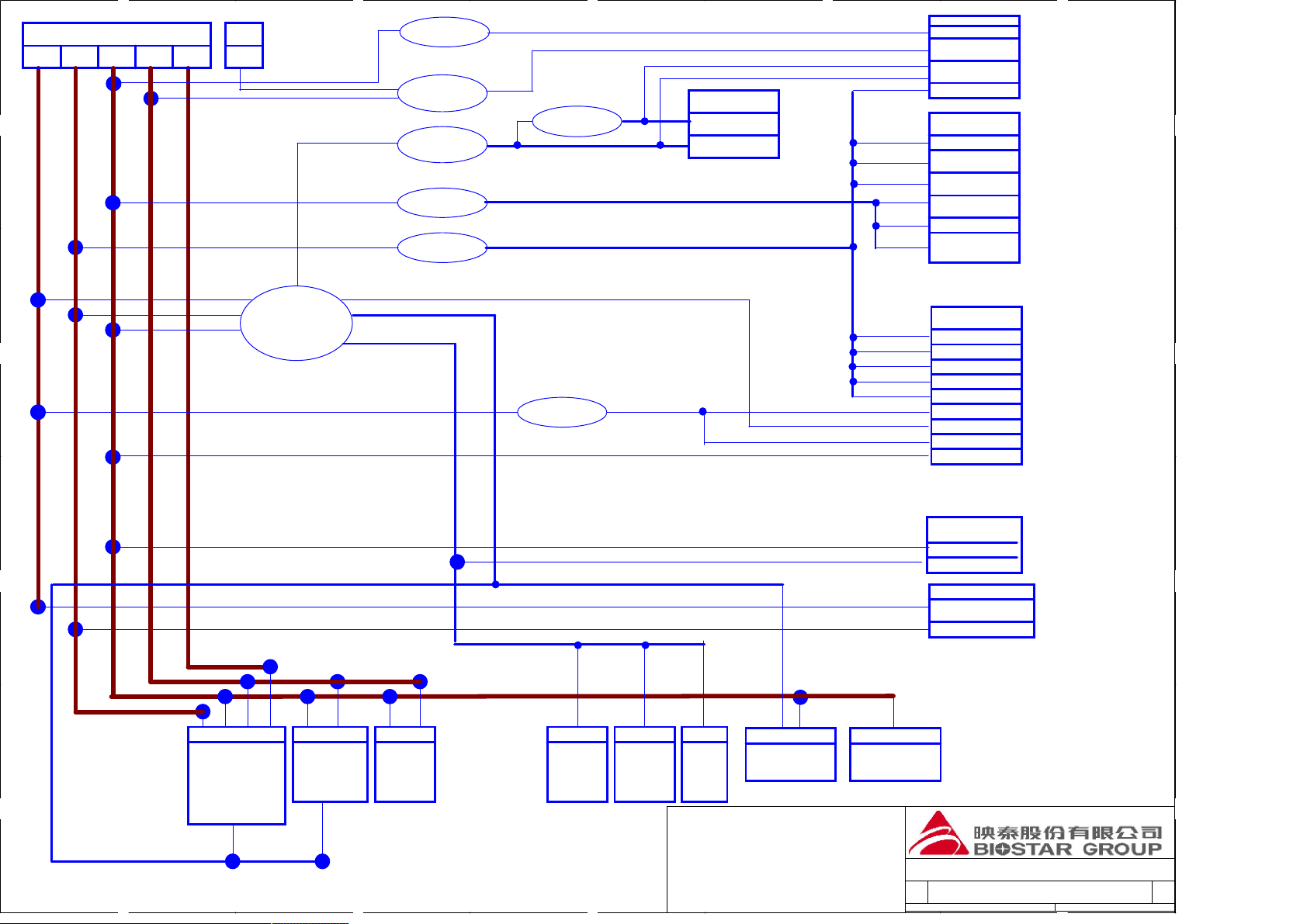

Page 3

5

ATX P /S WIT H 1A ST BY CURREN T

5VSB

+/-5%

5V

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

D D

CPU

PW

12V

+/-5%

+5VDUAL_MEM (S0,S5)

+3.3VSB REGULATOR

ACPI CONTROLLER

C C

4

+3.3VSB (S0, S1, S3, S4, S5)

+3.3VDUAL (S0, S1, S3, S4, S5)

+5VDUAL (S0, S1, S3, S4, S5)

2.5V SHUNT

REGULATOR

VRM SW

REGULATOR

1.5V VDD SW

REGULATOR

1.8V LINEAR

REGULATOR

VCC 1.2V SW

REGULATOR

0.75V VTT_DDR

REGULATOR

+1.8V(S0, S1)

VCC_NB (S0, S1)

1.2V STB LDO

REGULATOR

3

+1.2VSB (S5)

DDRIII D IM Ms

VTT_DDR 2A

VDD MEM 12A

2

CPU_VTT_SUS (S0,S1,S3)

CPU_VDDIO_SUS(S0,S1,S3)

VDDA 2.5V 0.1A

DDRIII MEM I/F VTT

0.125A, VDD 3A

VLDT 1.2V 0.5A

RS780

VDDHT 1.2V 0.5A

PCI-E CORE&VCO

& I/O &PLL 2.25A

NB CORE VDDC

1.2V 5A

DAC 200mA LVDS

1.8V 300mA

PLL & DAC-Q 0.1A

PCI-E PLL

SB710

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.2V S5 PW 0.22A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

3.3V I/O 0.45A

1

AZAL IA CODEC

3.3V CORE 0.3A

5V ANALOG 0.1A

B B

5.0A

7.6A

0.5A

0.1A

X1 PCI E per

12V

3.3Vaux

PCI Slot (per slo t)

5V 3.3V

3.3V

12V

A A

+3.3VDUAL (S0, S1, S3)

3.3Vaux

-12V

0.375A

3.0A

0.5A

0.1A

X16 PCI E

3.3V

12V

3.0A

5.5A

USB X4 F R

VDD

5VDual

2.0A

USB X6 R L

VDD

5VDual

3.0A

2XPS/2

5VDual

1.0A

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

GBE

3.3V 0.5A (S0, S1)

3.3V 0.1A (S3)

◆

SATA

3.3V 0.3A (S0, S1)

SUPER I/O

+5V SD 0.01A

+5V 0.1A

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

POWER DELIVERY

POWER DELIVERY

POWER DELIVERY

A78LA-A3S

A78LA-A3S

A78LA-A3S

3 43Thursday, January 27, 2011

3 43Thursday, January 27, 2011

3 43Thursday, January 27, 2011

of

of

of

6.0

6.0

6.0

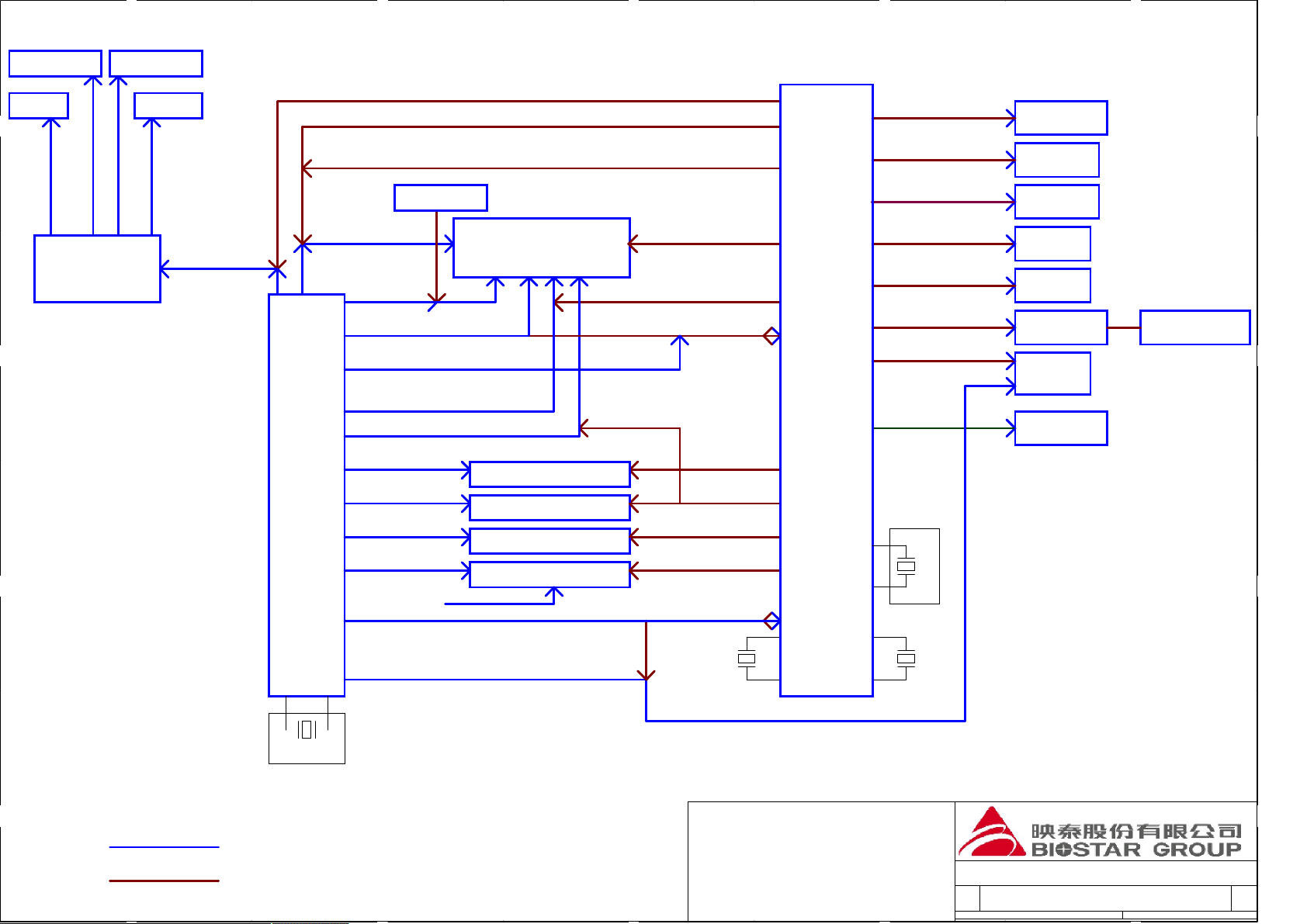

Page 4

5

4

3

2

1

DIMM3

DIMM1

D D

3 PAIR MEM CLK

3 PAIR MEM CLK

AM3/AM3r2 CPU

AM3 SOCKET

C C

B B

DIMM4

1 PAIR CPU CL K

DIMM2

200MHZ

HT ref clock

100MHZ DIFF (RX780/ RS780)

HT RE FCLK

66MHz SE(R S740)

14.318MHZ OSC

3 PAIR MEM CLK

3 PAIR MEM CLK

HT RE FCLK

66MHz SE(R S740)

1 PAIR CPU CL K

200MHZ

100MHz

DIFF (RX780/RS 780)

EXTERNAL

CLK GEN.

(RS740/RX780)

NB-OSCI N

14.318M HZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

NB GF X PCI E CL K

100MHZ

NB GP P PCI E CLK

100MHZ

PCIE GFX CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

USB CL K

48MHZ

(RX780)

25MHZ OSC INP UT

AMD NB

RS740/RX780/RS780

PCIE GFX SLOT 1 - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 4 LANES

PCIE GBE

NB PCI E Ref clock

100MHZ

NB Disp clo ck

100MHZ DIFF (RS780)

GPP Ref clo ck

100MHZ

GFX Ref clo ck

100MHZ

GPP Ref clo ck

100MHZ

GPP Ref clo ck

100MHZ

GPP Ref clo ck

100MHZ

25MHz

SATA

CPU_HT _CLK

NB_HT_C LK

25M_48 M_66M _OSC

AMD SB

SB700

NB_DIS P_CLK

GPP_C LK3

PCIE_R CLK/

NB_LNK _CLK

SLT_G FX_CLK

GPP_C LK0

GPP_C LK1

GPP_C LK2

USB_CL K

SB_BIT CLK

48MHZ

PCI CL K0

33MHZ

PCI CL K1

33MHZ

PCI CL K2

33MHZ

LPC_CL K0

33MHZ

LPC CL K1

33MHZ

PCI CL K3

33MHZ

PCI CL K4

33MHZ

25MHz

PCI SLOT 0

PCI SLOT 1

PCI SLOT 2

TPM

LPC BIOS

DEBUG POST

SUPER IO

IT8716F

HD AUDIO CON

TPM (BCM5755/5761)

SIO CL K

48MHZ

A A

External clock mode

Internal clock mode

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

32.768KHz

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

A78LA-A3S

A78LA-A3S

A78LA-A3S

4 43Thursday, January 27, 2011

4 43Thursday, January 27, 2011

4 43Thursday, January 27, 2011

6.0

6.0

6.0

Page 5

5

4

3

2

1

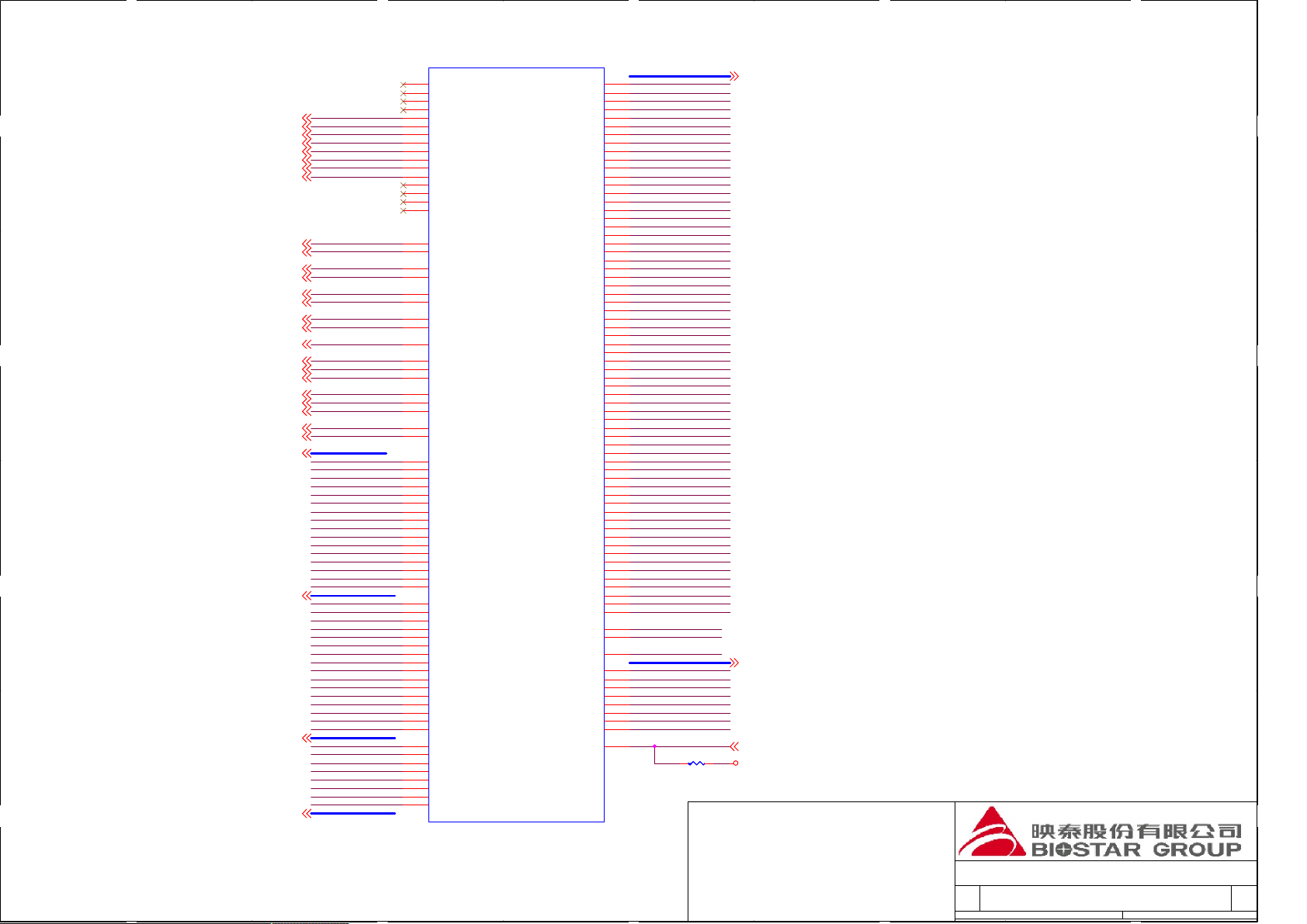

Change list From 6.1 to 6.2

1. (PAGE 39) Add CPU_NB low side MOS PQ22

2. (PAGE 38) Change MEM POWER control circuit (S3_STATE change to S5)

3. (PAGE 40) Change CT23 from 560uF to 270uF

D D

4. (PAGE 41) Change CT35 from 560uF to 270uF

5. (PAGE 40) Change MEM POWER OV circuit

6. (PAGE 39) Change some RES and CAP Value by following TW test report

7. (PAGE 22) Change Board ID

C C

B B

A A

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

REVISION HISTORY

REVISION HISTORY

REVISION HISTORY

A78LA-A3S

A78LA-A3S

A78LA-A3S

5 43T hursday, January 27, 2011

5 43T hursday, January 27, 2011

5 43T hursday, January 27, 2011

of

of

of

6.0

6.0

6.0

Page 6

5

4

3

2

1

D D

HyperTransport

CPU1A

CPU1A

HT_CLKIN1_P16

HT_CLKIN1_N16

HT_CLKIN0_P16

HT_CLKIN0_N16

HT_CTLIN1_P16

HT_CTLIN1_N16

C C

B B

HT_CTLIN0_N16

HT_CADIN15_P16

HT_CADIN15_N16

HT_CADIN14_P16

HT_CADIN14_N16

HT_CADIN13_P16

HT_CADIN13_N16

HT_CADIN12_P16

HT_CADIN12_N16

HT_CADIN11_P16

HT_CADIN11_N16

HT_CADIN10_P16

HT_CADIN10_N16

HT_CADIN9_P16

HT_CADIN9_N16

HT_CADIN8_P16

HT_CADIN8_N16

HT_CADIN7_P16

HT_CADIN7_N16

HT_CADIN6_P16

HT_CADIN6_N16

HT_CADIN5_P16

HT_CADIN5_N16

HT_CADIN4_P16

HT_CADIN4_N16

HT_CADIN3_P16

HT_CADIN3_N16

HT_CADIN2_P16

HT_CADIN2_N16

HT_CADIN1_P16

HT_CADIN1_N16

HT_CADIN0_P16

HT_CADIN0_N16

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

HT LINK

HT LINK

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CLKOUT1_P 16

HT_CLKOUT1_N 16

HT_CLKOUT0_P 16

HT_CLKOUT0_N 16

HT_CTLOUT1_P 16

HT_CTLOUT1_N 16

HT_CTLOUT0_P 16HT_CTLIN0_P16

HT_CTLOUT0_N 16

HT_CADOUT15_P 16

HT_CADOUT15_N 16

HT_CADOUT14_P 16

HT_CADOUT14_N 16

HT_CADOUT13_P 16

HT_CADOUT13_N 16

HT_CADOUT12_P 16

HT_CADOUT12_N 16

HT_CADOUT11_P 16

HT_CADOUT11_N 16

HT_CADOUT10_P 16

HT_CADOUT10_N 16

HT_CADOUT9_P 16

HT_CADOUT9_N 16

HT_CADOUT8_P 16

HT_CADOUT8_N 16

HT_CADOUT7_P 16

HT_CADOUT7_N 16

HT_CADOUT6_P 16

HT_CADOUT6_N 16

HT_CADOUT5_P 16

HT_CADOUT5_N 16

HT_CADOUT4_P 16

HT_CADOUT4_N 16

HT_CADOUT3_P 16

HT_CADOUT3_N 16

HT_CADOUT2_P 16

HT_CADOUT2_N 16

HT_CADOUT1_P 16

HT_CADOUT1_N 16

HT_CADOUT0_P 16

HT_CADOUT0_N 16

A A

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

K8 CPU HT

K8 CPU HT

K8 CPU HT

A78LA-A3S

A78LA-A3S

A78LA-A3S

6 43Thursday, March 03, 2011

6 43Thursday, March 03, 2011

6 43Thursday, March 03, 2011

6.0

6.0

6.0

Page 7

5

+5V

Vout=Vref (1.25V) X ( 1+R4/R3 )=2.5V

CT1

R3

R3

49.9 1% 0402

CPU_VDDA_A

D D

OIA

Q1

Q1

AZ1117H-ADJ SOT-223

AZ1117H-ADJ SOT-223

49.9 1% 0402

R4

R4

51 1% 0402

51 1% 0402

CPU_CLKIN_P20

CPU_CLKIN_N20

CPU_PRESENT#22

C C

+1.5V_SUS

R554

R554

300 0402

300 0402

CPU_CORE_FB39

CPU_CORE_FB_39

FOR AM3+-->ADD R0:1K

FOR AM3-->REMOVE R0

+1.5V_SUS

B B

+1.5V_SUS

RN1

LDT_RST#18,21,26

HTCPU_PWRGD21,39

LDT_STOP#18,21

RN2

+1.5V_SUS

RN76

RN76

CPU_TRST#

12

CPU_TDI

34

CPU_TMS

56

CPU_TCK

78

1K 8P4R 0402

A A

+1.5V_SUS

+1.5V_SUS

1K 8P4R 0402

R15 510 0402 /NIR15 510 0402 /NI

R16 510 0402 /NIR16 510 0402 /NI

R593 510 0402R593 510 0402

R594 510 0402R594 510 0402

R5

R6

R7

R8

3 4

5 6

7 8

FOR AM3+-->ADD RN2:1K

FOR AM3-->REMOVE RN2

CPU_TEST25_P

CPU_TEST25_N

CT1

100UF-S 16V 6.3X8 ELITE /NI

100UF-S 16V 6.3X8 ELITE /NI

+1.5V_SUS

CPU_TDI26

CPU_TRST#26

CPU_TCK26

CPU_TMS26

CPU_DBREQ#26CPU_DBREQ#26

FOR AM3+-->REMOVE R1

FOR AM3-->ADD R1-->39.2

FOR AM3+-->REMOVE R13

FOR AM3-->ADD R13:0 R13

FOR AM3+-->ADD RN1:1K

FOR AM3-->ADD RN1:330

RN5

RN5

1K 8P4R 0402

1K 8P4R 0402

1 2

LDT_RST#

HTCPU_PWRGD

LDT_STOP#

FOR AM3-->ADD R5 R6-->510

FOR AM3-->REMOVE R7 R8

FOR AM3+-->ADD R7 R8-->510

FOR AM3+-->REMOVE R5 R6

C1

C1

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

3900P 50V X7R 0402C3 3900P 50V X7R 0402C3

3900P 50V X7R 0402C4 3900P 50V X7R 0402C4

RN24 1K 8P4R 0402RN24 1K 8P4R 0402

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

+1.5V_SUS

R12 39.2 1% 0402R12 39.2 1% 0402

R14 39.2 1% 0402R14 39.2 1% 0402

R1

+1.5V_SUS

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

34

56

78

SIO_SIC

SIO_SID

ALERT_

RN7

FOR AM3+-->ADD RN7:1K

FOR AM3-->REMOVE RN2

RN84

RN84

1K 8P4R 0402

1K 8P4R 0402

4

CPU_VDDA

C111

C111

C20

C20

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

R5

R5

169 1% 0402

169 1% 0402

R0

R587 1K 0402R587 1K 0402

CPU_TEST25_P

CPU_TEST25_N

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST12

+1.5V_SUS

R599 1K 0402R599 1K 0402

FOR AM3+-->ADD R17:1K

FOR AM3-->REMOVE R17

CPU_TEST15

12

CPU_TEST16

34

CPU_TEST17

56

CPU_TEST14

78

C2

C2

3900P 50V X7R 0402

3900P 50V X7R 0402

CLKIN_H

CLKIN_L

HTCPU_PWRGD

LDT_STOP#

LDT_RST#

CPU_PRESENT#

R590 1K 0402R590 1K 0402

CPU_CORE_FB

CPU_CORE_FB_

1UF 10V Y5V 0402 /NIC551 1UF 10V Y5V 0402 /NIC551

CPU_M_VREFF

M_ZN

M_ZP

R592

R592

0 0402 /NI

0 0402 /NI

R17

ALERT_

CPU_TEST36

CPU_TEST9

CPU_TEST11

CPU_VDDA

SA0

16.9 1% 0402

16.9 1% 0402

16.9 1% 0402

16.9 1% 0402

CPU1D

CPU1D

C10

VDDA_1

D10

VDDA_2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AK4

SA0

AL4

ALERT_L

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

F3

M_VDDIO_PWRGD

E12

VDDR_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

M_ZP

A10

TEST25_H

B10

TEST25_L

F10

TEST19

E9

TEST18

AJ7

TEST13

F6

TEST9

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

AH9

TEST12

E5

TEST7

AJ5

TEST6

AH7

TEST3

AJ6

TEST2

C18

RSVD1

C20

RSVD2

F2

RSVD3

G24

RSVD4

G25

RSVD5

H25

RSVD6

L25

RSVD7

L26

RSVD8

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

+1.5V_SUS

R9

R9

CPU_M_VREFF

C5

R10

R10

C5

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

MISC.

MISC.

INT. MISC.

INT. MISC.

3

CORE_TYPE

PVIEN/VID1

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

C6

C6

1000P 50V X7R 0402

1000P 50V X7R 0402

G5

D2

VID5

D1

VID4

C1

SVC/VID3

E3

SVD/VID2

E2

E1

VID0

THERMDC

THERMDA

TDO

DBRDY

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

CPU_THERMDC

AG9

CPU_THERMDA

AG8

CPU_THERMTRIP

AK7

CPU_PROCHOT#

AL7

AK10

B6

AK11

AL11

G4

G3

F1

HTREF1

V8

HTREF0

V7

FBCLKOUT

C11

FBCLKOUT_

D11

CPU_TEST24

AK8

CPU_TEST23

AH8

CPU_TEST22_SCANEN

AJ9

CPU_TEST21_SCANEN

AL8

CPU_TEST20

AJ8

J10

H9

CPU_TEST27

AK9

CPU_TEST26

AK5

G7

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

5/10

CPU_TDO

CPU_DBRDY

VDDNB_FB_H 39

VDDNB_FB_L 39

R11 46.4 1% 0402R11 46.4 1% 0402

R13 46.4 1% 0402R13 46.4 1% 0402

R17 80.6 1% 0402R17 80.6 1% 0402

R373 1K 0402R373 1K 0402

RN2

RN2

1K 8P4R 0402

1K 8P4R 0402

1 2

3 4

5 6

7 8

RN4 FOR AM3-->ADD R12:330

2

+1.5V_SUS

RN1

RN1

1K 8P4R 0402

1K 8P4R 0402

1 2

3 4

5 6

7 8

+1.5V_SUS

R51

R51

330 0402

330 0402

Q2 FDV301N SOT23Q2 FDV301N SOT23

G

S

CPU_TDO 26

CPU_DBRDY 26

CPU_VDDHT

FOR AM3+-->ADD R2 R3:46.4 1%

R2

FOR AM3-->ADD R2 R3:44.2 1%

R3

R16

FOR AM3+-->REMOVE R16

FOR AM3-->ADD R16:80.6

R11

FOR AM3+-->ADD R11:1K

FOR AM3-->ADD R11:330

+1.5V_SUS

FOR AM3+-->ADD R12:1K

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

SIO_SIC

SIO_SID

CPU_THERMDA

CPU_THERMDC

K8_VID5 39

K8_VID4 39

SVC 39

SVD 39

K8_VID1 39

K8_VID0 39

CORE_TYPE 39

R589 330 0402R589 330 0402

D

CPU_THERMTRIP# 22

CPU_PROCHOT# 21

R591 330 0402R591 330 0402

R4

FOR AM3+-->ADD R4:1K

FOR AM3-->ADD R4:330

CPU_THERMTRIP

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST21_SCANEN

CPU_TEST23

CPU_TEST24

CPU_TEST12

CPU_TEST22_SCANEN

FOR AM3+-->ADD RN4 RN5 RN6:1K

FOR AM3-->ADD RN4 RN5 RN6:330

K8 CPU MISC

K8 CPU MISC

K8 CPU MISC

SIO_SIC 33

SIO_SID 33

TMPIN1 33

TS_D- 33

+1.5V_SUS

R544 1K 0402R544 1K 0402

RN5

RN4 1K 8P4R 0402RN4 1K 8P4R 0402

R12

R344 1K 0402R344 1K 0402

RN47 1K 8P4R 0402RN47 1K 8P4R 0402

1 2

3 4

7 8

5 6

A78LA-A3S

A78LA-A3S

A78LA-A3S

+1.5V_SUS

12

34

56

78

RN6

6.0

6.0

6.0

7 43Thursday, March 03, 2011

7 43Thursday, March 03, 2011

7 43Thursday, March 03, 2011

Page 8

5

MEM_MA1_CLK_H114

D D

C C

B B

A A

MEM_MA1_CLK_L114

MEM_MA0_CLK_H012

MEM_MA0_CLK_L012

MEM_MA1_CLK_H014

MEM_MA1_CLK_L014

MEM_MA0_CLK_H112

MEM_MA0_CLK_L112

MEM_MA0_CS_L112

MEM_MA0_CS_L012

MEM_MA0_ODT112

MEM_MA0_ODT012

MEM_MA1_CS_L114

MEM_MA1_CS_L014

MEM_MA1_ODT114

MEM_MA1_ODT014

MEM_MA_RESET_L12,14

MEM_MA_CAS_L12,14

MEM_MA_WE_L12,14

MEM_MA_RAS_L12,14

MEM_MA_BANK212,14

MEM_MA_BANK112,14

MEM_MA_BANK012,14

MEM_MA_CKE112,14

MEM_MA_CKE012,14

MEM_MA_ADD[15..0]12,14

MEM_MA_DQS_H[8..0]12,14

MEM_MA_DQS_L[8..0]12,14

MEM_MA_DM[8..0]12,14

MEM_MA_ADD[15..0]

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DM[8..0]

4

CPU1B

CPU1B

AG21

AG20

AE20

AE19

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

E20

AB25

AB27

AA26

N25

Y27

AA27

L27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

MEM CHA

MEM CHA

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

3

MEM_MA_DATA[0..63]

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

MEM_MA_DM8

J25

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

K25

MEM_MA_CHECK6

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1

H29

MEM_MA_CHECK0

H27

W30

2

MEM_MA_DATA[0..63] 12,14

MEM_MA_CHECK[7..0] 12,14

R321 1K 1% 0402R321 1K 1% 0402

MEM_MA_EVENT_L 12,14

+1.5V_SUS

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

1

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

K8 CPU MEMORY-1

K8 CPU MEMORY-1

K8 CPU MEMORY-1

A78LA-A3S

A78LA-A3S

A78LA-A3S

8 43Thursday, March 03, 2011

8 43Thursday, March 03, 2011

8 43Thursday, March 03, 2011

6.0

6.0

6.0

Page 9

5

MEM_MB1_CLK_H115

MEM_MB1_CLK_L115

D D

C C

B B

MEM_MB0_CLK_H013

MEM_MB0_CLK_L013

MEM_MB1_CLK_H015

MEM_MB1_CLK_L015

MEM_MB0_CLK_H113

MEM_MB0_CLK_L113

MEM_MB0_CS_L113

MEM_MB0_CS_L013

MEM_MB0_ODT113

MEM_MB0_ODT013

MEM_MB1_CS_L115

MEM_MB1_CS_L015

MEM_MB1_ODT115

MEM_MB1_ODT015

MEM_MB_RESET_L13,15

MEM_MB_CAS_L13,15

MEM_MB_WE_L13,15

MEM_MB_RAS_L13,15

MEM_MB_BANK213,15

MEM_MB_BANK113,15

MEM_MB_BANK013,15

MEM_MB_CKE113,15

MEM_MB_CKE013,15

MEM_MB_ADD[15..0]13,15

MEM_MB_DQS_H[8..0]13,15

MEM_MB_DQS_L[8..0]13,15

MEM_MB_DM[8..0]13,15

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DM[8..0]

A A

4

CPU1C

CPU1C

AJ19

MB_CLK_H7

AK19

MB_CLK_L7

AL19

MB_CLK_H6

AL18

MB_CLK_L6

U31

MB_CLK_H5

U30

MB_CLK_L5

W29

MB_CLK_H4

W28

MB_CLK_L4

Y31

MB_CLK_H3

Y30

MB_CLK_L3

V31

MB_CLK_H2

W31

MB_CLK_L2

A18

MB_CLK_H1

A19

MB_CLK_L1

C19

MB_CLK_H0

D19

MB_CLK_L0

AE30

MB0_CS_L1

AC31

MB0_CS_L0

AF31

MB0_ODT1

AD29

MB0_ODT0

AE29

MB1_CS_L1

AB31

MB1_CS_L0

AG31

MB1_ODT1

AD31

MB1_ODT0

B19

MB_RESET_L

AC29

MB_CAS_L

AC30

MB_WE_L

AB29

MB_RAS_L

N31

MB_BANK2

AA31

MB_BANK1

AA28

MB_BANK0

M31

MB_CKE1

M29

MB_CKE0

N28

MB_ADD15

N29

MB_ADD14

AE31

MB_ADD13

N30

MB_ADD12

P29

MB_ADD11

AA29

MB_ADD10

P31

MB_ADD9

R29

MB_ADD8

R28

MB_ADD7

R31

MB_ADD6

R30

MB_ADD5

T31

MB_ADD4

T29

MB_ADD3

U29

MB_ADD2

U28

MB_ADD1

AA30

MB_ADD0

AK13

MB_DQS_H7

AJ13

MB_DQS_L7

AK17

MB_DQS_H6

AJ17

MB_DQS_L6

AK23

MB_DQS_H5

AL23

MB_DQS_L5

AL28

MB_DQS_H4

AL29

MB_DQS_L4

D31

MB_DQS_H3

C31

MB_DQS_L3

C24

MB_DQS_H2

C23

MB_DQS_L2

D17

MB_DQS_H1

C17

MB_DQS_L1

C14

MB_DQS_H0

C13

MB_DQS_L0

AJ14

MB_DM7

AH17

MB_DM6

AJ23

MB_DM5

AK29

MB_DM4

C30

MB_DM3

A23

MB_DM2

B17

MB_DM1

B13

MB_DM0

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

MEM CHB

MEM CHB

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

3

MEM_MB_DATA[0..63]

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK[7..0]

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

R322 1K 1% 0402R322 1K 1% 0402

◇

◇

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

MEM_MB_DATA[0..63] 13,15

MEM_MB_CHECK[7..0] 13,15

MEM_MB_EVENT_L 13,15

+1.5V_SUS

BIOSTAR'S PROPRIETARY INFORMATION

Any unauthorized use, reproduction,

◆

2

1

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

K8 CPU MEMORY-2

K8 CPU MEMORY-2

K8 CPU MEMORY-2

A78LA-A3S

A78LA-A3S

A78LA-A3S

9 43Thursday, March 03, 2011

9 43Thursday, March 03, 2011

9 43Thursday, March 03, 2011

6.0

6.0

6.0

Page 10

5

4

3

2

1

CPU1E

CPU1E

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

D D

C C

B B

A A

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

H11

VDD_13

H23

VDD_14

J8

VDD_15

J12

VDD_16

J14

VDD_17

J16

VDD_18

J18

VDD_19

J20

VDD_20

J22

VDD_21

J24

VDD_22

K7

VDD_23

K9

VDD_24

K11

VDD_25

K13

VDD_26

K15

VDD_27

K17

VDD_28

K19

VDD_29

K21

VDD_30

K23

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

L10

VDD_35

L12

VDD_36

L14

VDD_37

L16

VDD_38

L18

VDD_39

L20

VDD_40

L22

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

M11

VDD_46

M13

VDD_47

M15

VDD_48

M17

VDD_49

M19

VDD_50

M21

VDD_51

M23

VDD_52

N8

VDD_53

N10

VDD_54

N12

VDD_55

N14

VDD_56

N16

VDD_57

N18

VDD_58

N20

VDD_59

N22

VDD_60

P7

VDD_61

P9

VDD_62

P11

VDD_63

P13

VDD_64

P15

VDD_65

P17

VDD_66

P19

VDD_67

P21

VDD_68

P23

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

R10

VDD_73

R12

VDD_74

R14

VDD_75

R16

VDD_76

R18

VDD_77

R20

VDD_78

R22

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

T11

VDD_84

T13

VDD_85

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

POWER/GND1

POWER/GND1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

A3

A7

A9

A11

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

+V_CPU+V_CPU CPU_VDDNB

CPU1F

CPU1F

T15

VDD_86

T17

VDD_87

T19

VDD_88

T21

VDD_89

T23

VDD_90

U8

VDD_91

U10

VDD_92

U12

VDD_93

U14

VDD_94

U16

VDD_95

U18

VDD_96

U20

VDD_97

U22

VDD_98

V9

VDD_99

V11

VDD_100

V13

VDD_101

V15

VDD_102

V17

VDD_103

V19

VDD_104

V21

VDD_105

V23

VDD_106

W4

VDD_107

W5

VDD_108

W8

VDD_109

W10

VDD_110

W12

VDD_111

W14

VDD_112

W16

VDD_113

W18

VDD_114

W20

VDD_115

W22

VDD_116

Y2

VDD_117

Y3

VDD_118

Y7

VDD_119

Y9

VDD_120

Y11

VDD_121

Y13

VDD_122

Y15

VDD_123

Y17

VDD_124

Y19

VDD_125

Y21

VDD_126

Y23

VDD_127

AA8

VDD_128

AA10

VDD_129

AA12

VDD_130

AA14

VDD_131

AA16

VDD_132

AA18

VDD_133

AA20

VDD_134

AA22

VDD_135

AB7

VDD_136

AB9

VDD_137

AB11

VDD_138

AB13

VDD_139

AB15

VDD_140

AB17

VDD_141

AB19

VDD_142

AB21

VDD_143

AB23

VDD_144

AC4

VDD_145

AC5

VDD_146

AC8

VDD_147

AC10

VDD_148

AC12

VDD_149

AC14

VDD_150

AC16

VDD_151

AC18

VDD_152

AC20

VDD_153

AC22

VDD_154

AD2

VDD_155

AD3

VDD_156

AD7

VDD_157

AD9

VDD_158

AD11

VDD_159

AD23

VDD_160

AE10

VDD_161

AE12

VDD_162

AF7

VDD_163

AF9

VDD_164

AF11

VDD_165

AG4

VDD_166

AG5

VDD_167

AG7

VDD_168

AH2

VDD_169

AH3

VDD_170

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

M12

VSS_86

M14

VSS_87

M16

VSS_88

M18

VSS_89

M20

VSS_90

M22

VSS_91

N4

VSS_92

N5

VSS_93

N7

VSS_94

N9

VSS_95

N11

VSS_96

N13

VSS_97

N15

VSS_98

N17

VSS_99

N19

VSS_100

N21

VSS_101

N23

VSS_102

P2

VSS_103

P3

VSS_104

P8

VSS_105

P10

VSS_106

P12

VSS_107

P14

VSS_108

P16

VSS_109

P18

VSS_110

P20

VSS_111

P22

VSS_112

R7

VSS_113

R9

VSS_114

R11

VSS_115

R13

VSS_116

R15

VSS_117

R17

VSS_118

R19

VSS_119

R21

VSS_120

R23

VSS_121

T8

VSS_122

T10

VSS_123

T12

VSS_124

T14

VSS_125

T16

VSS_126

T18

VSS_127

T20

VSS_128

T22

VSS_129

U4

VSS_130

U5

VSS_131

U7

VSS_132

U9

VSS_133

U11

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W7

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

AA4

AA5

AA7

AA9

POWER/GND2

POWER/GND2

CPU1G

CPU1G

A4

VDDNB_1

A6

VDDNB_2

B5

VDDNB_3

B7

VDDNB_4

C6

VDDNB_5

C8

VDDNB_6

D7

VDDNB_7

D9

VDDNB_8

E8

VDDNB_9

E10

VDDNB_10

F9

VDDNB_11

F11

VDDNB_12

G10

VDDNB_13

G12

VDDNB_14

B2

NP/RSVD

H20

NP/VSS1

AE7

NP/VSS2

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

CPU_VDDHT

C525

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

CPU_VDDHT

AA11

VSS_171

AA13

VSS_172

AA15

VSS_173

AA17

VSS_174

AA19

VSS_175

AA21

VSS_176

AA23

VSS_177

AB2

VSS_178

AB3

VSS_179

AB8

VSS_180

AB10

VSS_181

AB12

VSS_182

AB14

VSS_183

AB16

VSS_184

AB18

VSS_185

AB20

VSS_186

AB22

VSS_187

AC7

VSS_188

AC9

VSS_189

AC11

VSS_190

AC13

VSS_191

AC15

VSS_192

AC17

VSS_193

AC19

VSS_194

AC21

VSS_195

AC23

VSS_196

AD8

VSS_197

AD10

VSS_198

AD12

VSS_199

AD14

VSS_200

AD16

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

◆

POWER/GND3

POWER/GND3

C7

C7

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

CPU_VDDHT

+1.5V_SUS

CPU_VDDHT CPU_VDDHT

C8

C8

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C18

C18

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

CPU_VDDHT

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

CPU1H

CPU1H

AJ1

VLDT_A_1

AJ2

VLDT_A_2

AJ3

VLDT_A_3

AJ4

VLDT_A_4

A12

VDDR_1

B12

VDDR_2

C12

VDDR_3

D12

VDDR_4

M24

VDDIO_1

M26

VDDIO_2

M28

VDDIO_3

M30

VDDIO_4

P24

VDDIO_5

P26

VDDIO_6

P28

VDDIO_7

P30

VDDIO_8

T24

VDDIO_9

T26

VDDIO_10

T28

VDDIO_11

T30

VDDIO_12

V25

VDDIO_13

V26

VDDIO_14

V28

VDDIO_15

V30

VDDIO_16

Y24

VDDIO_17

Y26

VDDIO_18

Y28

VDDIO_19

Y29

VDDIO_20

AB24

VDDIO_21

AB26

VDDIO_22

AB28

VDDIO_23

AB30

VDDIO_24

AC24

VDDIO_25

AD26

VDDIO_26

AD28

VDDIO_27

AD30

VDDIO_28

AF30

VDDIO_29

SOCKET AM3 941 SMD

SOCKET AM3 941 SMD

C9

C9C525

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

POWER/GND4

POWER/GND4

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

C238

C238

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

K8 CPU POWER

K8 CPU POWER

K8 CPU POWER

A78LA-A3S

A78LA-A3S

A78LA-A3S

10 43Thursday, January 27, 2011

10 43Thursday, January 27, 2011

10 43Thursday, January 27, 2011

CPU_VDDHT

6.0

6.0

6.0

Page 11

CPU_VDDHT

5

4

+1.2V_HT

CPU_VDDHT

3

+V_CPU

BCC1

BCC1

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

2

+V_CPU

BCC2

BCC2

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU +V_CPU

BCC3

BCC3

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BCC4

BCC4

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

1

+V_CPU

BCC5

BCC5

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BOTTOM

D D

C11

C11

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C12

C12

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C15

C15

1UF 10V Y5V 0402

1UF 10V Y5V 0402

C16

C16

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C10

C10

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C14

C14

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C13

C13

1UF 10V Y5V 0402

1UF 10V Y5V 0402

C109

C109

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

奻狟跪侐跺

+1.5V_SUS

+1.8V_SUS

C C

C228

C226

C226

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU

BC7

BC7

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C228

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C229

C229

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

BC8

BC8

C230

C230

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

BC9

BC9

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C231

C231

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

B B

C285

C285

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC10

BC10

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC24

BC24

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C286

C286

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC25

BC25

C240

C240

C241

C241

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC11

BC11

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C242

C242

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC12

BC12

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C287

C287

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC28

BC28

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+1.5V_SUS

+1.5V_SUS

C243

C243

12

C19

C19

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

C281

C281

180P 50V NPO 0402

180P 50V NPO 0402

溫婓

CPU迵DIMM

BC32

BC32

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

C282

C282

180P 50V NPO 0402

180P 50V NPO 0402

12

BC23

BC23

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C153

C153

12

C283

C283

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

眳潔

12

BC27

BC27

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C154

C154

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

C284

C284

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC26

BC26

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

+V_CPU

C227

C227

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

12

BC5

BC5

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C296

C296

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

+1.5V_SUS

12

BC39

BC39

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C244

C244

C293

C293

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

BCC6

BCC6

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BOTTOM

12

BC29

BC29

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C294

C294

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

C295

C295

+V_CPU

+V_CPU

BC14

BC13

BC13

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

CPU_VDDNB

BC14

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC15

BC15

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

A A

C411

C232

C232

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C411

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C233

C233

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC16

BC16

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C239

C239

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC17

BC17

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC240

BC240

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

BC18

BC18

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC241

BC241

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

BC19

BC19

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

C277

C277

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

BC20

BC20

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

BC21

BC21

10UF 10V 0805 Y5V

10UF 10V 0805 Y5V

◆

C180

C180

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

C183

C183

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

C189

C189

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU DECPOULING CAP

CPU DECPOULING CAP

CPU DECPOULING CAP

A78LA-A3S

A78LA-A3S

A78LA-A3S

11 43Thursday, January 27, 2011

11 43Thursday, January 27, 2011

11 43Thursday, January 27, 2011

6.0

6.0

6.0

Page 12

5

4

3

2

1

DDR3_A1

DDR3_A1A

DDR3_A1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DM0/DQS9

126

DQS9-

134

DM1/DQS10

135

DQS10-

143

DM2/DQS11

144

DQS11-

152

DM3/DQS12

153

DQS12-

203

DM4/DQS13

204

DQS13-

212

DM5/DQS14

213

DQS14-

221

DM6/DQS15

222

DQS15-

230

DM7/DQS16

231

DQS16-

161

DM8/DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

DDR3-240 PIN-B

DDR3-240 PIN-B

BLACK

BLACK

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

0.1UF 16V Y5V 0402C484 0.1UF 16V Y5V 0402C484

0.1UF 16V Y5V 0402 /NIC519 0.1UF 16V Y5V 0402 /NIC519

0.1UF 16V Y5V 0402C485 0.1UF 16V Y5V 0402C485

0.1UF 16V Y5V 0402 /NIC487 0.1UF 16V Y5V 0402 /NIC487

0.1UF 16V Y5V 0402C489 0.1UF 16V Y5V 0402C489

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

MEM_MA_DATA[0..63]MEM_MA_DQS_H[8..0]

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

R330

R330

16.9 1% 0402

16.9 1% 0402

R329

R329

16.9 1% 0402

16.9 1% 0402

MEM_MA_DATA[0..63] 8,14

DIMM_CA_VREF13,14,15

DIMM_DQ_VREF13,14,15

MEM_MA_CKE08,14

MEM_MA_CKE18,14

MEM_MA_BANK08,14

MEM_MA_BANK18,14

MEM_MA_BANK28,14

MEM_MA_RESET_L8,14

MEM_MA_WE_L8,14

MEM_MA_RAS_L8,14

MEM_MA_CAS_L8,14

MEM_MA0_CS_L08

MEM_MA0_CS_L18

MEM_MA0_ODT08

MEM_MA0_ODT18

MEM_MA0_CLK_L18

MEM_MA0_CLK_H18

MEM_MA0_CLK_L08

MEM_MA0_CLK_H08

MEM_MA_EVENT_L8,14

0.1UF 16V Y5V 0402 /NIC498 0.1UF 16V Y5V 0402 /NIC498

0.1UF 16V Y5V 0402C516 0.1UF 16V Y5V 0402C516

0.1UF 16V Y5V 0402C501 0.1UF 16V Y5V 0402C501

0.1UF 16V Y5V 0402 /NIC502 0.1UF 16V Y5V 0402 /NIC502

0.1UF 16V Y5V 0402C503 0.1UF 16V Y5V 0402C503

SDATA13,14,15,20,22,39

SCLK13,14,15,20,22,39

MEM_MA_DQS_L[8..0]

MEM_MA_DQS_L0

MEM_MA_DQS_H0

MEM_MA_DQS_L1

MEM_MA_DQS_H1

MEM_MA_DQS_L2

MEM_MA_DQS_H2

MEM_MA_DQS_L3

MEM_MA_DQS_H3

MEM_MA_DQS_L4

MEM_MA_DQS_H4

MEM_MA_DQS_L5

MEM_MA_DQS_H5

MEM_MA_DQS_L6

MEM_MA_DQS_H6

MEM_MA_DQS_L7

MEM_MA_DQS_H7

MEM_MA_DQS_L8

MEM_MA_DQS_H8

MEM_MA_DM[8..0]

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DM8

MEM_MA_CHECK[7..0]

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK4

MEM_MA_CHECK5

MEM_MA_CHECK6

MEM_MA_CHECK7

MEM_MA_ADD[15..0]

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

+1.5V_SUS +1.5V_SUS

R309

R309

16.9 1% 0402

16.9 1% 0402

DIMM_DQ_VREF DIMM_CA_VREF

R328

R328

16.9 1% 0402

16.9 1% 0402

MEM_MA_DQS_L[8..0]8,14

MEM_MA_DQS_H[8..0]8,14

D D

MEM_MA_DM[8..0]8,14

C C

MEM_MA_CHECK[7..0]8,14

MEM_MA_ADD[15..0]8,14

B B

A A

+3.3V

C570

C570

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

+1.5V_SUS

+3.3V

DIMM_CA_VREF

DIMM_DQ_VREF

MEM_VTT

C474

C474

10UF 10V 0805 Y5V /NI

10UF 10V 0805 Y5V /NI

1 2

◇

BIOSTAR'S PROPRIETARY INFORMATION

◇

Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

◆

DDR3_A1B

DDR3_A1B

51

VDDQ1 (P)

54

VDDQ2 (P)

57

VDDQ3 (P)

60

VDDQ4 (P)

62

VDDQ5 (P)

65

VDDQ6 (P)

66

VDDQ7 (P)

69

VDDQ8 (P)

72

VDDQ9 (P)

75

VDDQ10 (P)

78

VDDQ11 (P)

170

VDD1 (P)

173

VDD2 (P)

176

VDD3 (P)

179

VDD4 (P)

182

VDD5 (P)

183

VDD6 (P)

186

VDD7(P)

189

VDD8(P)

191

VDD9(P)

194

VDD10(P)

197

VDD11(P)

236

VDDSPD(P)

67

VREFCA

1

VREFDQ

117

SA0

237

SA1

50

CKE0

169

CKE1

71

BA0

190

BA1

52

A16/BA2

168

RESET

73

WE-

192

RAS-

74

CAS-

193

S-0

76

S-1

195

ODT0

77

ODT1

64

CK-1

63

CK1

185

CK-0

184

CK0

48

FREE1

49

FREE2

187

FREE3

198

FREE4

DDR3-240 PIN-B

DDR3-240 PIN-B

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

C473

C473

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

1 2

SA2

VTT

VTT

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

240

1 2

MEM_VTT

C524

C524

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

C530

C530

0.1UF 16V Y5V 0402 /NI

0.1UF 16V Y5V 0402 /NI

1 2

C531

C531

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

1 2

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR DIMM-1

DDR DIMM-1

DDR DIMM-1

A78LA-A3S

A78LA-A3S

A78LA-A3S

12 43Thursday, March 03, 2011

12 43Thursday, March 03, 2011

12 43Thursday, March 03, 2011

6.0

6.0

6.0

Page 13

5

4

3

2

1

MEM_MB_DQS_L[8..0]9,15

D D

MEM_MB_DQS_H[8..0]9,15

MEM_MB_DM[8..0]9,15

C C

MEM_MB_CHECK[7..0]9,15

SDATA12,14,15,20,22,39

B B

MEM_MB_ADD[15..0]9,15

SCLK12,14,15,20,22,39

MEM_MB_DQS_L[8..0]

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_L0

MEM_MB_DQS_H0

MEM_MB_DQS_L1

MEM_MB_DQS_H1

MEM_MB_DQS_L2

MEM_MB_DQS_H2

MEM_MB_DQS_L3

MEM_MB_DQS_H3

MEM_MB_DQS_L4

MEM_MB_DQS_H4

MEM_MB_DQS_L5

MEM_MB_DQS_H5

MEM_MB_DQS_L6

MEM_MB_DQS_H6

MEM_MB_DQS_L7

MEM_MB_DQS_H7

MEM_MB_DQS_L8

MEM_MB_DQS_H8

MEM_MB_DM[8..0]

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DM8

MEM_MB_CHECK[7..0]

MEM_MB_CHECK0

MEM_MB_CHECK1

MEM_MB_CHECK2

MEM_MB_CHECK3

MEM_MB_CHECK4

MEM_MB_CHECK5

MEM_MB_CHECK6

MEM_MB_CHECK7

MEM_MB_ADD[15..0]

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

DDR3_B1

DDR3_B1A

DDR3_B1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DM0/DQS9

126

DQS9-

134

DM1/DQS10

135

DQS10-

143

DM2/DQS11

144

DQS11-

152

DM3/DQS12

153

DQS12-

203

DM4/DQS13

204

DQS13-

212

DM5/DQS14

213

DQS14-

221

DM6/DQS15

222

DQS15-

230

DM7/DQS16

231

DQS16-

161

DM8/DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

DDR3-240 PIN-B

DDR3-240 PIN-B

BLACK

BLACK

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

MEM_MB_DATA[0..63]

MEM_MB_DATA63

234

MEM_MB_DATA62

233

MEM_MB_DATA61

228

MEM_MB_DATA60

227

MEM_MB_DATA59

115

MEM_MB_DATA58

114

MEM_MB_DATA57

109

MEM_MB_DATA56

108

MEM_MB_DATA55

225

MEM_MB_DATA54

224

MEM_MB_DATA53

219

MEM_MB_DATA52

218

MEM_MB_DATA51

106