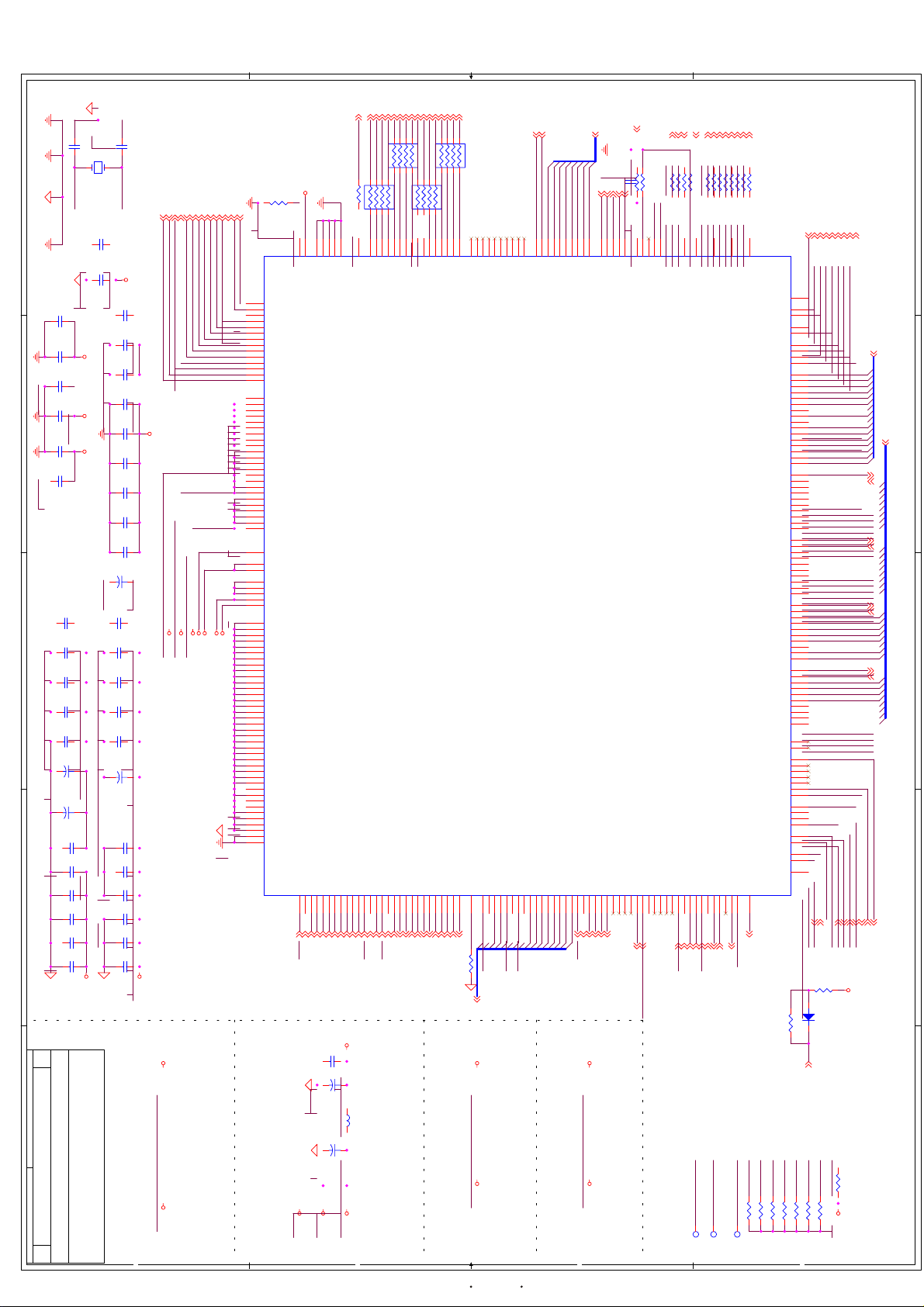

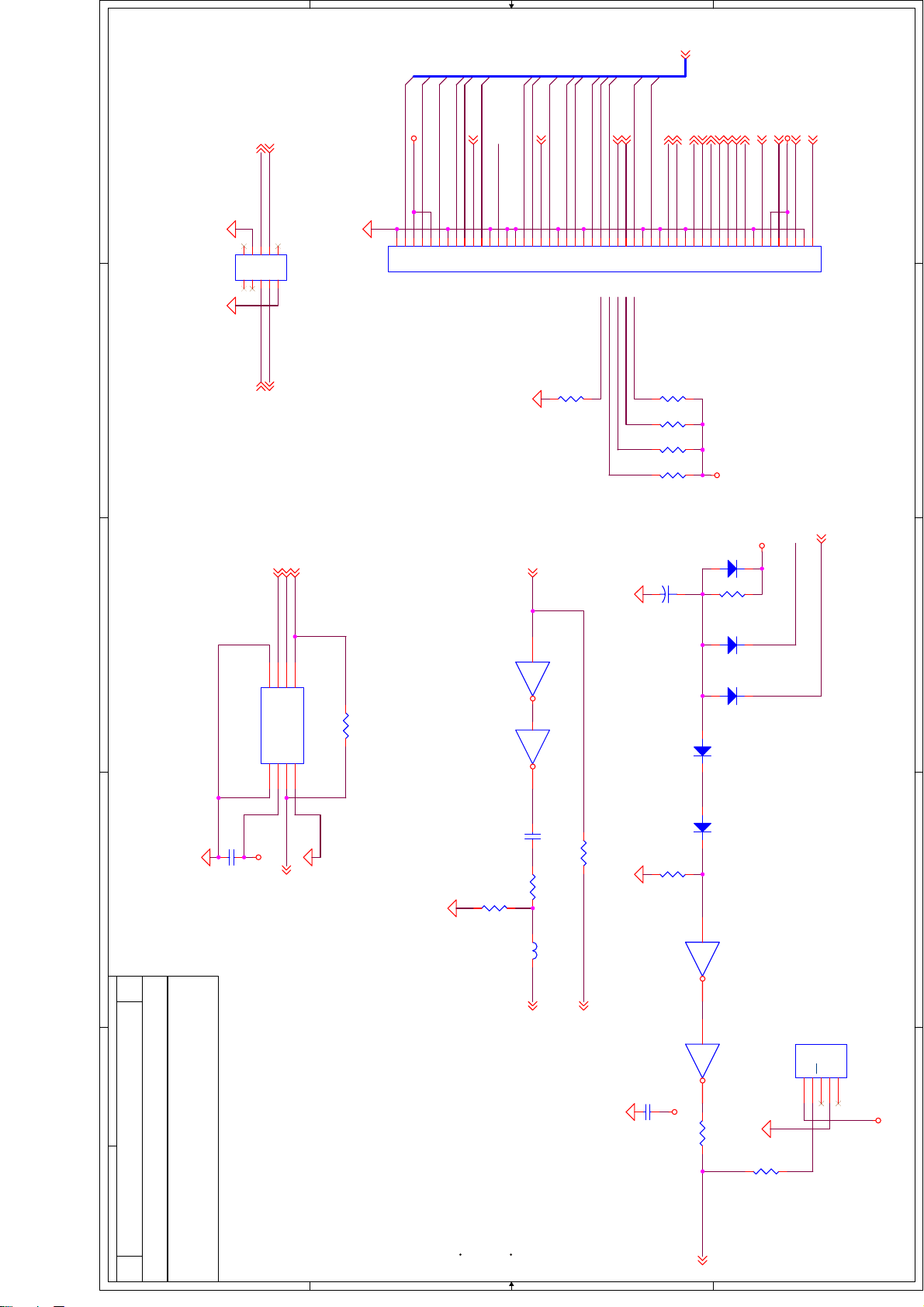

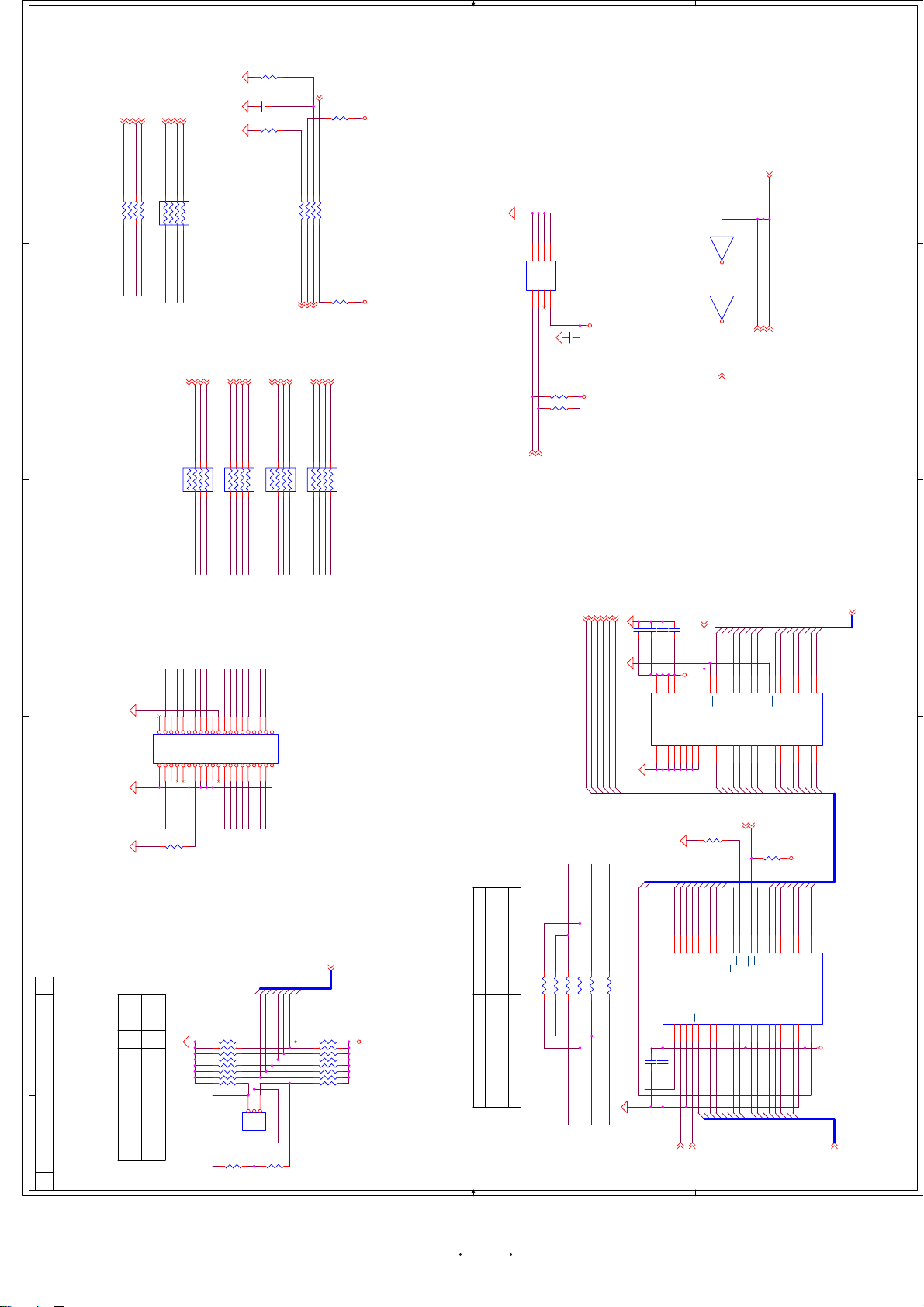

BBK 9915-S Service manual

R

SERVICE MANUAL

bbk9915S

bbk9915S

SCHEMATIC DIAGRAM&PCB SILKSCREEN

SDRAM_CKE

SDRAM__A9

SDRAM__A8

SDRAM__A7

SDRAM__A6

SDRAM__A5

SDRAM__A4

SDRAM__A3

SDRAM__A2

SDRAM__A1

SDRAM__A0

SDRAM_DQ9

SDRAM_DQ8

SDRAM_DQ7

SDRAM_DQ6

SDRAM_DQ5

SDRAM_DQ4

SDRAM_DQ3

SDRAM_DQ2

SDRAM_DQ1

SDRAM_DQ0

SIO_SDA

SIO_SCL

SIO_IRRX

E5 signals named after

master host's

(/RST)

(MUTE)

D D

VREF3,4,5

U1

D16

H20

G20

N20

P20

A16

C15

B16

B17

A18

C20

E18

E17

F17

C19

D19

D18

B20

C18

A20

B18

C17

A17

B19

A19

G19

E20

F20

F19

H17

G18

G17

F18

E19

D20

K20

J19

H19

H18

J17

J18

J20

K17

K18

K19

L17

M19

N18

M18

L20

M17

L19

M20

N19

L18

N17

R19

P19

P18

R20

P17

T20

R18

T19

R17

W17

U14

Y17

W18

V16

V18

Y19

T18

U18

V20

V17

U20

W19

U19

W20

Y18

V19

Y20

R6 *0

IR_IN 13

(/ETHER_IRQ)

E5_SDRAM_A9

E5_SDRAM_A8

E5_SDRAM_A7

E5_SDRAM_A6

E5_SDRAM_A5

E5_SDRAM_A4

E5_SDRAM_A3

E5_SDRAM_A2

E5_SDRAM_A1

E5_SDRAM_A0

E5_SDRAM_DQ9

E5_SDRAM_DQ8

E5_SDRAM_DQ7

E5_SDRAM_DQ6

E5_SDRAM_DQ5

E5_SDRAM_DQ4

E5_SDRAM_DQ3

E5_SDRAM_DQ2

E5_SDRAM_DQ1

E5_SDRAM_DQ0

1 2

E5_SDRAM_CLK#04,5

E5_SDRAM_CLK#14,5

E5_SDRAM_CLKE4,5

E5_SDRAM_CLK04,5

E5_SDRAM_CLK14,5

E5_SDRAM_WE#4,5

E5_SDRAM_A15

E5_SDRAM_A14

E5_SDRAM_A13

E5_SDRAM_A12

E5_SDRAM_A11

E5_SDRAM_A10

E5_SDRAM_DQM3

E5_SDRAM_DQS3

E5_SDRAM_DQ31

E5_SDRAM_DQ30

E5_SDRAM_DQ29

E5_SDRAM_DQ28

E5_SDRAM_DQ27

E5_SDRAM_DQM2

E5_SDRAM_DQ26

E5_SDRAM_DQS2

E5_SDRAM_DQ25

E5_SDRAM_DQ24

E5_SDRAM_DQ23

E5_SDRAM_DQ22

E5_SDRAM_DQ21

E5_SDRAM_DQ20

E5_SDRAM_DQ19

E5_SDRAM_DQM1

E5_SDRAM_DQ18

E5_SDRAM_DQS1

E5_SDRAM_DQ17

E5_SDRAM_DQ16

E5_SDRAM_DQ15

E5_SDRAM_DQ14

E5_SDRAM_DQ13

E5_SDRAM_DQ12

E5_SDRAM_DQ11

E5_SDRAM_DQM0

E5_SDRAM_DQ10

E5_SDRAM_DQS0

E5_IRTX2

E5_IRTX1

E5_UART2_TX

E5_UART2_RX

E5_UART1_TX 6

E5_UART1_RX 6

SCL 7,10,11,12,13

SDA 7,10,11,12,13

R2

*10K

D1

*1N6263

E5_SDRAM_CAS#4,5

E5_SDRAM_RAS#4,5

E5_UART1_RTS 6

E5_UART1_CTS 6

E5_VDDX

5

E5_SDRAM_A[15..0]4,5

E5_SDRAM_DQ[31..0]3

4

3

3

3

3

3

3

3

3

3

2

E5_SPI_MOSI 13

E5_SPI_MISO 13

E5_SPI_CLK 13

VI_VSYNC010

VI_CLK010

VI_D9

C1

A5

VI_VSYNC0

VI_CLK0

PCI_AD10

PCI_AD9

V12

W11

HD10

HD11

VI_D8

VI_D7

VI_D7

VI_D8

VI_D9

PCI_AD13

PCI_AD12

PCI_AD11

V10

Y12

HD12

HD13

VI_D6

VI_D5

C4

B3A2A1

VI_D5

VI_D6

PCI_AD15

PCI_AD14

U10

V11

HD14

HD15

C C

VI_D3

VI_D4

VI_D3

VI_D4

PCI_AD17

PCI_AD16

E5_MA1 6,7

E5_MA2 6,7

VI_D[9..2]10

VI_D2

C3C2D3

VI_D2

PCI_AD19

PCI_AD18

E5_MA3 6,7

E5_MA4 6,7

V18

E5_TRST6

E5_TDO6

E5_TMS6

B6D7B2

TDO

TMS

TRST_L

PCI_AD22

PCI_AD21

PCI_AD20

E5_MA5 6,7

E5_MA22 7

C1 104

E5_TCK6

E5_TDI6

D8

C7

B7

TCK

TDI

PCI_AD25

PCI_AD24

PCI_AD23

E5_MA26

E5_MA25

E5_MA24

E5_MA23

1.8V

/SYS_RST6,7

R24 100

R23 22

W16

A12

CLKX

A7

CLKO

BYPASS_PLL

PCI_RST_L

PCI_AD28

PCI_AD27

PCI_AD26

/E5_CS1 6

/E5_CS0 7

/E5_CS2

A10

B10

CLKI

CLKI

CLKX

PCI_AD31

PCI_AD30

PCI_AD29

/E5_CS4

/E5_CS3

AI_FSYNC12

AI_MCLKO12

AI_SCLK12

R21 22

R22 22

AIMCLKO

AIFSYNC

AISCLK

C12

A13

AI_SCLK

AI_FSYNC

AI_MCLKO

PCI_STOP_L

PCI_TRDY_L

PCI_IRDY_L

W4Y3V5W5Y4V6Y5Y6U6W6V7W7Y8Y7V8W8Y11

/E5_CS5

/WAIT 6

E5_GPIO5 13

(/WAIT)

/DTACK

AI_D012

R19 22

R20 22

AOMCLKO

AI_D1

C13

D12

B12

AI_D0

AI_D1

PCI_FRAME_L

PCI_CBE_L3

PCI_PAR

Y10U8Y9V9U9

/E5_WEL 6,7

E5_GPIO0 13

E5_GPIO4 7,8,10,11

(E5_GPIO5)

(E5_GPIO0)

(E5_GPIO4)

AO_IEC9586

AO_MCLKO12

R18 22

AOIEC

B13

AO_IEC958

AO_MCLKO

PCI_CBE_L1

PCI_CBE_L2

E5_GPIO3 12

E5_GPIO2 6

(E5_GPIO3)

AO_FSYNC12

AO_SCLK12

AO_D312

AO_D012

AO_D112

AO_D212

R11 22

R15 22

R17 22

R16 22

R12 DNS-22

R13 DNS-22

R14 DNS-22

AOFSYNC

AOSCLK

D14

C14

D13

B15

A15

A14

B14

AO_3

AO_0

AO_1

AO_2

AO_D0

AO_D1

AO_D2

AO_D3

AO_SCLK

AO_FSYNC

SDRAM_VREF

SDRAM_CLK_L1

SDRAM_CLK1

SDRAM_CLK_L0

SDRAM_CLK0

SDRAM_WE_L

SDRAM_RAS_L

SDRAM_CAS_L

SDRAM__A15

SDRAM__A14

SDRAM__A13

SDRAM__A12

SDRAM__A11

SDRAM__A10

SDRAM_DQM3

SDRAM_DQS3

SDRAM_DQ31

SDRAM_DQ30

SDRAM_DQ29

SDRAM_DQ28

SDRAM_DQ27

SDRAM_DQ26

SDRAM_DQ25

SDRAM_DQ24

SDRAM_DQM2

SDRAM_DQS2

SDRAM_DQ23

SDRAM_DQ22

SDRAM_DQ21

SDRAM_DQ20

SDRAM_DQ19

SDRAM_DQ18

SDRAM_DQ17

SDRAM_DQ16

SDRAM_DQM1

SDRAM_DQS1

SDRAM_DQ15

SDRAM_DQ14

SDRAM_DQ13

SDRAM_DQ12

SDRAM_DQ11

SDRAM_DQ10

SDRAM_DQM0

SDRAM_DQS0

OE#/SIO_IRTX2

MAddress2/SIO_IRTX1

MAddress26/SIO_SPI_CLK

MAddress5/SIO_SPI_CS3

MAddress22/SIO_SPI_CS2

MAddress23/SIO_SPI_CS1

MAddress24/SIO_SPI_CS0

MAddress1/SIO_SPI_MISO

MAddress25/SIO_SPI_MOSI

MAddress3/SIO_UART1_RTS

WR#/SIO_UART1_CTS

MAddress4/SIO_UART1_TX

CS0#/SIO_UART1_RX

SIO_UART2_TX

SIO_UART2_RX

PCI_CBE_L0

PCI_INTA_L

PCI_REQ_L

PCI_GNT_L

ALE

U13

Y16

Y15

V15

Y13

W10W9U7

E5_ALE 6,7

E5_GPIO1 13

/E5_OE 6,7

MCONFIG1

(E5_GPIO2)

(E5_GPIO1)

/E5_WEH

(DEM/GPO)

C10

C8

AGND1

AGND2

AGND3

GNDX

ATAPI_DATA6

ATAPI_DATA5

ATAPI_DATA4

ATAPI_DATA3

ATAPI_DATA3 7

ATAPI_DATA5 7

ATAPI_DATA6 7

ATAPI_DATA4 7

C4

104

+

C2

47u/16

B B

VO_CLK11

R26 22

H1

A9C9A8

AGND0

VO_CLK

ATAPI_DATA10

ATAPI_DATA9

ATAPI_DATA8

ATAPI_DATA7

ATAPI_DATA8 7

ATAPI_DATA7 7

ATAPI_DATA10 7

ATAPI_DATA9 7

V33

L1

B601

VO_D1311

VO_D1411

VO_D1211

VO_D1511

2 7

3 6

4 5

F4

VO_12

VO_14

VO_13

VO_15

VO_D12

VO_D13

VO_D14

VO_D15

ATAPI_DATA15

ATAPI_DATA14

ATAPI_DATA13

ATAPI_DATA12

ATAPI_DATA11

ATAPI_DATA12 7

ATAPI_DATA11 7

ATAPI_DATA14 7

ATAPI_DATA15 7

ATAPI_DATA13 7

VO_D1011

VO_D1111

VO_D911

3 6

4 5

1 8

RP4 22/RP

E1F3E2D1E3

VO_11

VO_10

VO_9

VO_D9

VO_D10

VO_D11

AtapiAddr2

AtapiAddr3

AtapiAddr4

AtapiAddr2 7

AtapiAddr3 7

AtapiAddr4 7

3.3V

VO_D811

VO_D711

1 8

2 7

G4

F2

VO_8

VO_7

VO_D7

VO_D8

AtapiAddr0

AtapiAddr1

AtapiAddr0 7

AtapiAddr1 7

VO_D311

VO_D611

VO_D411

VO_D511

RP3

22/RP

1 8

2 7

3 6

4 5

G1G2G3

F1

VO_4

VO_3

VO_6

VO_5

VO_D3

VO_D4

VO_D5

VO_D6

ATAPI_DIOW_L

ATAPI_DIOR_L

ATAPI_IORDY

ATAPI_INTRQ

ATAPI_DIOW_L 7

ATAPI_DIOR_L 7

ATAPI_IORDY 7

ATAPI_INTRQ 7

VO_D111

VO_D011

VO_D211

1 8

2 7

3 6

4 5

RP1 22/RP

RP2 22/RP

H2H3H4

J4

VO_0

VO_1

VO_2

VO_D1

VO_D2

ATAPI_DMAACK_L

ATAPI_DMARQ

ATAPI_RESET

ATAPI_RESET 7

ATAPI_DMAACK_L 7

ATAPI_DMARQ 7

MCONFIG0

C6

D2

A6

NC

NCNCVO_D0

MCONFIG0

PCI_AD0

W15

M16Y1U1W1T3W2V3T1W3V2V1U3V4Y2U2T2R2R1P2N3M4N1N2N4P1P3P4R3R4

HD1

HD0

R25 22

HD[15..0]6,7

V25

B4

B5

DMN8600

PCI_AD2

PCI_AD1

W13

W14

HD2

HD3

D6

C5

PCI_AD5

PCI_AD4

PCI_AD3

Y14

V14

HD4

HD5

2.5V

PCI_AD6

W12

U12

HD7

HD6

A3B1A4

NCNCNCNCNCNCNC

PCI_AD8

PCI_AD7

U11

V13

HD8

HD9

A A

E5_DLLGND

C31 27PF

GND_SSTL2

5

CLKX

E5_AGNDGND

103

C45

104

C46

104

C47

103

C48

4

104

C49

103

C50

103

C40

103

C41

3

103

C42

103

C43

103

C44

+

C32

47u/16

+

C33

47u/16

104

C34

104

C35

104

Date: Sheet

C36

104

C37

104

C38

104

C39

C

Title

Size Document Number Rev

DMN8600

2

Y1

13.5MHz

C29

103

C30

104

E5_VDDREF E5_VDDX

E5_AVDD

E5_VCORE

BBK

C5 27PF

CLKI

103

C6

103

C7

103

C8

104

C9

104

C10

GND_SSTL2

C11

104

104

C12

104

C13

104

C14

+

C15

47u/16

103

C24

103

C25

103

C26

103

C27

103

C28

+

C16

47u/16

104

C18

104

C19

104

C20

104

C21

104

C22

104

C23

BIO_PHY_DATA38

BIO_PHY_DATA08

BIO_PHY_DATA68

BIO_PHY_DATA58

BIO_PHY_DATA48

BIO_PHY_DATA18

BIO_PHY_DATA28

BIO_PHY_CTL18

BIO_PHY_CTL08

BIO_PHY_CLK8

BIO_LINK_ON8

BIO_LREQ8

BIO_LPS8

E5_V5BIAS

SSTL2_VDD

E5_VPAD

SSTL2_VDD

E5_VCORE

V33

Caps with smaller capacitance values to be

closer to respective power pins compared to

those of larger values. All should be as

close as possible.

E5_VPAD

V33

VCC

BIO_PHY_DATA78

E5_AVDD

E5_VDLL

E5_VDDX

E5_V5BIAS

General decoupling cap placement:

5V

1.18K/1%

K3

BIO_PHY_DATA7

K2

BIO_PHY_DATA6

K1

BIO_PHY_DATA5

J1

BIO_PHY_DATA4

M2

BIO_PHY_DATA3

M3

BIO_PHY_DATA2

L3

BIO_PHY_DATA1

J2

BIO_PHY_DATA0

L2

BIO_PHY_CTL1

J3

BIO_PHY_CTL0

M1

BIO_LREQ

L4

BIO_LPS

K4

BIO_LINK_ON

L1

BIO_PHY_CLK

E4

VDD_PAD0

K5

VDD_PAD1

L5

VDD_PAD2

T4

VDD_PAD3

T12

VDD_PAD4

T11

VDD_PAD5

E11

VDD_PAD6

E9

VDD_PAD7

D5

VDD_PAD8

D4

VDD_CORE0

J5

VDD_CORE1

M5

VDD_CORE2

U4

VDD_CORE3

T9

VDD_CORE4

T10

VDD_CORE5

E12

VDD_CORE6

E10

VDD_CORE7

J16

VDD_25V0

K16

VDD_25V1

L16

VDD_25V2

C16

VDD_25V3

D17

VDD_25V4

D15

VDD_25V5

U5

5V_BIAS1

U16

VDD_DLL0

U15

VDD_DLL1

D10

AVDD0

B9

AVDD1

D9

AVDD2

B8

AVDD3

A11

VDDX

H8

VSS_PC2_CTR1

H9

VSS_PC2_CTR2

H10

VSS_PC2_CTR3

H11

VSS_PC2_CTR4

H12

VSS_PC2_CTR5

H13

VSS_PC2_CTR6

J8

VSS_PC2_CTR7

J9

VSS_PC2_CTR8

J10

VSS_PC2_CTR9

J11

VSS_PC2_CTR10

J12

VSS_PC2_CTR11

J13

VSS_PC2_CTR12

K8

VSS_PC2_CTR13

K9

VSS_PC2_CTR14

K10

VSS_PC2_CTR15

K11

VSS_PC2_CTR16

K12

VSS_PC2_CTR17

K13

VSS_PC2_CTR18

L8

VSS_PC2_CTR19

L9

VSS_PC2_CTR20

L10

VSS_PC2_CTR21

L11

VSS_PC2_CTR22

L12

VSS_PC2_CTR23

L13

VSS_PC2_CTR24

M8

VSS_PC2_CTR25

M9

VSS_PC2_CTR26

M10

VSS_PC2_CTR27

M11

VSS_PC2_CTR28

M12

VSS_PC2_CTR29

M13

VSS_PC2_CTR30

N8

VSS_PC2_CTR31

N9

VSS_PC2_CTR32

N10

VSS_PC2_CTR33

N11

VSS_PC2_CTR34

N12

VSS_PC2_CTR35

N13

VSS_PC2_CTR36

U17

GND_DLL0

T17

GND_DLL1

R27

E5_VDDREF

D11

C11

B11

VDD_REF

R_REF

VSS_REF

ATAPI_DATA1

ATAPI_DATA0

ATAPI_DATA0 7

ATAPI_DATA1 7

ATAPI_DATA2

ATAPI_DATA2 7

1

213Tuesday, August 12, 2003

of

0.0

E5_V5BIAS

E5_VDDREF

C3

47u/16

E5_VDDX

+

E5_AVDD

SSTL2_VDD

27

E5_VCORE

E5_UART2_TX

E5_UART2_RX

1

1

TP2

TP3

/WAIT

E5_GPIO5

R10 10K

1

TP1

E5_GPIO3

E5_GPIO4

R9 10K

R8 1K

/E5_CS2

E5_GPIO2

R5 10K

R7 10K

/E5_CS1

R4 10K

/E5_CS0

R3 10K

MCONFIG1

R1 10K

V33

1

A A

B B

C C

D D

5

5

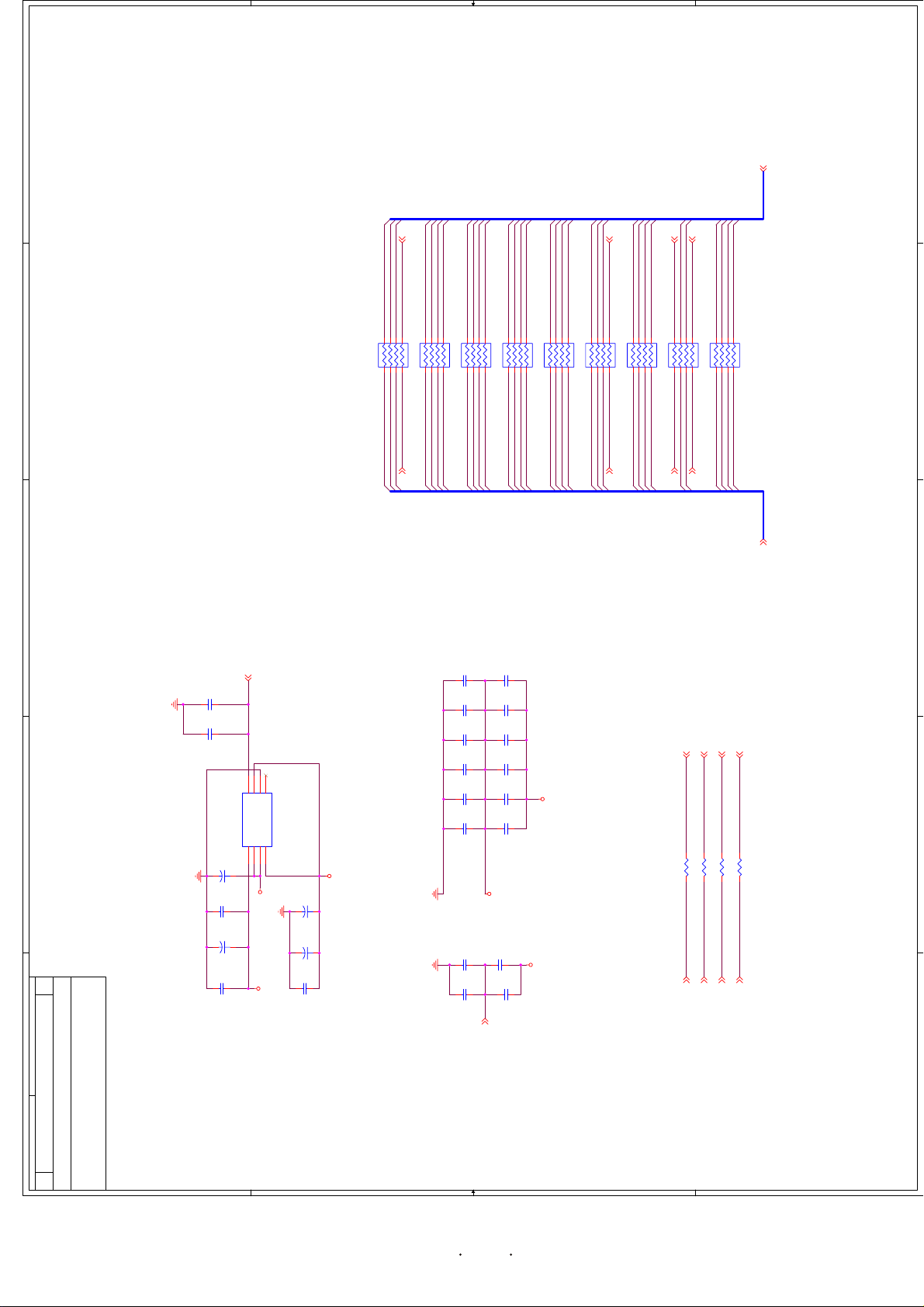

E5_SDRAM_DQ[31..0] 2

E5_SDRAM_DQM3 2 SDRAM_DQM34,5

E5_SDRAM_DQ16

E5_SDRAM_DQ19

E5_SDRAM_DQ17

E5_SDRAM_DQ20

E5_SDRAM_DQ31 SDRAM_DQ31

E5_SDRAM_DQ25 SDRAM_DQ25

The VTT side of the terminaton resistors should be placed

on a wide VTT island on the surface layer. The island is

located at each end of the bus, so it does not interfere

with the signal routing.

RP13 56/RP

4

182736

45

SDRAM_DQ30E5_SDRAM_DQ30

45

SDRAM_DQ17

SDRAM_DQ20

RP12 56/RP

182736

SDRAM_DQ16

SDRAM_DQ19

E5_SDRAM_DQ14

E5_SDRAM_DQ13

E5_SDRAM_DQ11

RP11 56/RP

182736

45

SDRAM_DQ14

SDRAM_DQ13

SDRAM_DQ11

SDRAM_DQ12E5_SDRAM_DQ12

E5_SDRAM_DQ0

E5_SDRAM_DQ1

E5_SDRAM_DQ2

E5_SDRAM_DQ3

RP10 56/RP

182736

45

SDRAM_DQ0

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

E5_SDRAM_DQ4

E5_SDRAM_DQ6

E5_SDRAM_DQ5

E5_SDRAM_DQ7

1 8

2 7

3 6

4 5

RP9 56/RP

SDRAM_DQ4

SDRAM_DQ6

SDRAM_DQ5

SDRAM_DQ7

E5_SDRAM_DQ15

E5_SDRAM_DQ9

E5_SDRAM_DQ10

1 8

2 7

3 6

4 5

RP8 56/RP

SDRAM_DQM04,5E5_SDRAM_DQM0 2

SDRAM_DQ15

SDRAM_DQ9

SDRAM_DQ10

E5_SDRAM_DQ22

E5_SDRAM_DQ29

2 7

3 6

4 5

SDRAM_DQ29

SDRAM_DQ22

SDRAM_DQ21E5_SDRAM_DQ21

E5_SDRAM_DQ23

1 8

3 6

4 5

RP7 56/RP

SDRAM_DQM24,5E5_SDRAM_DQM2 2

SDRAM_DQ23

SDRAM_DQ18E5_SDRAM_DQ18

E5_SDRAM_DQM1 2

E5_SDRAM_DQ8

1 8

2 7

RP6 56/RP

SDRAM_DQM14,5

SDRAM_DQ8

E5_SDRAM_DQ28

E5_SDRAM_DQ26

E5_SDRAM_DQ27

E5_SDRAM_DQ24

1 8

2 7

3 6

4 5

RP5 56/RP

SDRAM_DQ28

SDRAM_DQ26

SDRAM_DQ27

SDRAM_DQ24

4

SDRAM_DQ[31..0]4,5

VREF should be routed over a

reference plane and isolated, and possibly

shielded with both SSTL2_VDD and SSTL2_GND

VREF needs to be decoupled

to both SSTL2_VDD and SSTL2_GND with balanced

decoupling capacitors.

3

3

VREF2,4,5

C51

104

C59

104

C74

104

C75

103

123

4 5

GND_SSTL2

2

LP2995

VREF VDDQ

GND

VSENSE

AVIN

PVIN

NC

U2

VTT

678

C67

220u/10

47u/16

C68

C69

104

VTT

+

+

Date: Sheet

C

Size Document Number Rev

Title

TERM AT E5

+

220u/10

C70

SSTL2_VDD

C72

104

+

47u/16

C71

BBK

104

V25_D

C73

104

103

103

104

104

GND_SSTL2

GND_SSTL2

104

103

C52

104

C60

C53

103

C61

C54

103

C62

SSTL2_VDD

C55

104

C63

C56

104

C64

E5_SDRAM_DQS3 2

R31 51

E5_SDRAM_DQS0 2

E5_SDRAM_DQS1 2

E5_SDRAM_DQS2 2

R29 51

R30 51

R28 51

2

VTT

VTT

SDRAM_DQS04,5

SDRAM_DQS24,5

SDRAM_DQS14,5

SDRAM_DQS34,5

SSTL2_VDD

C58

104

C65

C57

103

C66

VREF 2,4,5

1

313Tuesday, August 12, 2003

of

0.0

1

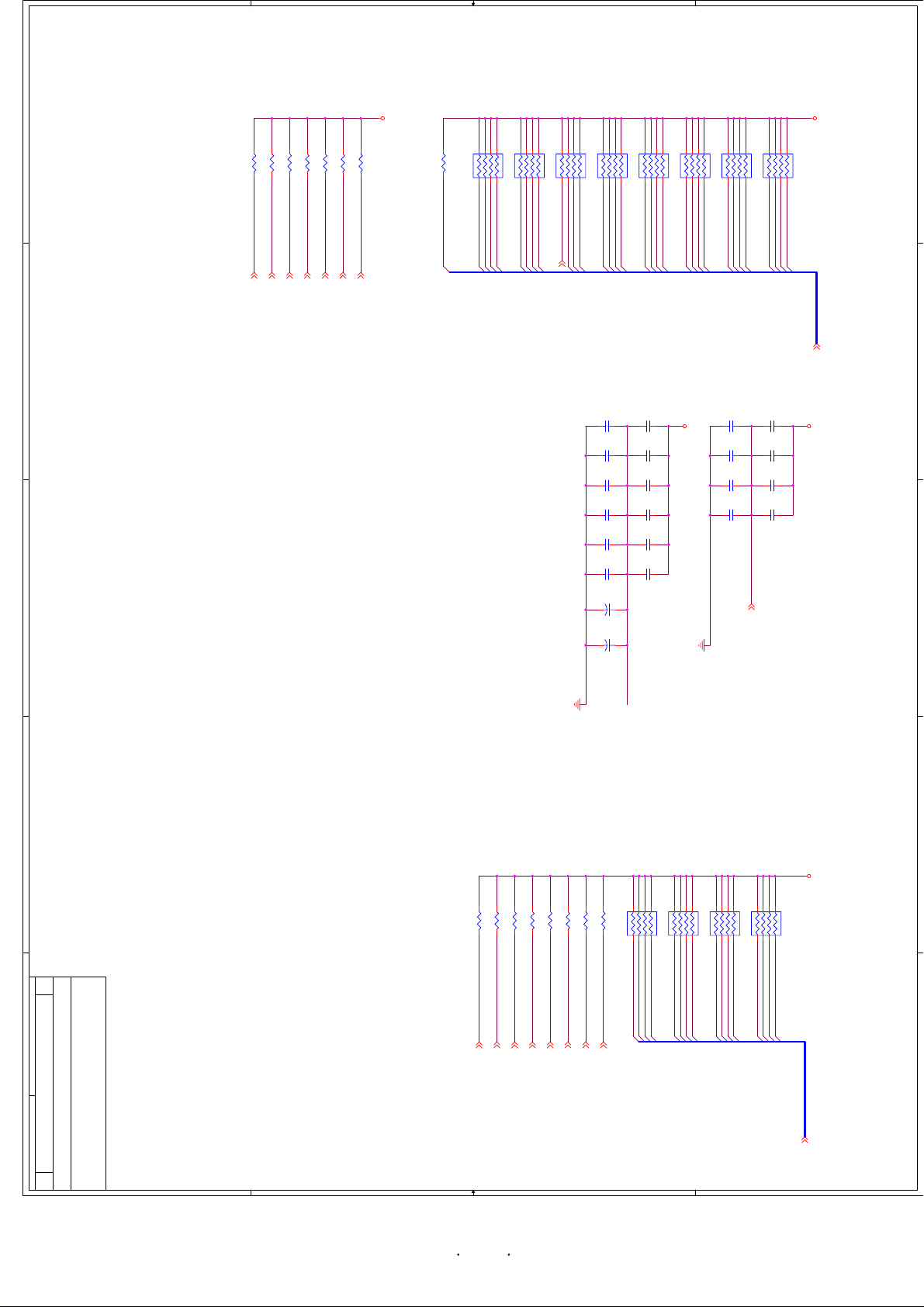

28

A A

B B

C C

D D

5

R46

56

SDRAM_DQM33,5

R43

R44

R45

51

51

56

56

SDRAM_DQS33,5

SDRAM_DQS23,5

SDRAM_DQM03,5

SDRAM_DQM13,5

VTT

R4051R4151R42

SDRAM_DQS03,5

SDRAM_DQS13,5

R205 56

SDRAM_DQ17

2 7

3 6

4 5

SDRAM_DQ30

SDRAM_DQ31

1 8

RP25 56/RP

SDRAM_DQ29

SDRAM_DQ28

1 8

2 7

3 6

4 5

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ27

RP24 56/RP

2 7

3 6

4 5

SDRAM_DQ18

SDRAM_DQM23,5

SDRAM_DQ23

1 8

4 5

RP23 56/RP

SDRAM_DQ21

SDRAM_DQ22

1 8

2 7

3 6

RP22 56/RP

SDRAM_DQ16

SDRAM_DQ19

SDRAM_DQ20

182736

45

SDRAM_DQ15

SDRAM_DQ14

SDRAM_DQ13

SDRAM_DQ12

RP20 56/RP

182736

45

SDRAM_DQ10

SDRAM_DQ8

SDRAM_DQ9

4 5

RP18 56/RP

SDRAM_DQ11

1 8

2 7

3 6

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ4

SDRAM_DQ7

RP16 56/RP

4 5

SDRAM_DQ3

1 8

2 7

3 6

RP14 56/RP

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ0

VTT

decoupling capacitors.

VREF needs to be decoupled

to both SSTL2_VDD and GND_SSTL2 with balanced

5

SDRAM_DQ[31..0]3,5

4

located at each end of the bus, so it does not interfere

with the signal routing.

The VTT side of the terminaton resistors should be placed

on a wide VTT island on the surface layer. The island is

SSTL2_VDD

C80

C92

104

104

103

103

104

C84

104

C85

104

C93

C86

103

C94

C87

103

C95

C88

104

C96

104

104

104

C81

104

103

C82

103

103

C83

103

SSTL2_VDD VTT

C76

C77

C78

C79

4

3

2

C

Date: Sheet

Title

Size Document Number Rev

TERM AT DDR & VREF/VTT

C89

104

C97

104

3

47u/16

47u/16

GND_SSTL2

+

C90

+

C91

VREF 2,3,5

GND_SSTL2

VTT

2

1 8

2 7

3 6

182736

45

E5_SDRAM_A14

E5_SDRAM_A8

E5_SDRAM_A11

E5_SDRAM_A9

RP19 56/RP

4 5

E5_SDRAM_A6

E5_SDRAM_A7

R39

R37

R38

51

51

51

BBK

E5_SDRAM_CAS#2,5

E5_SDRAM_CLKE2,5

E5_SDRAM_RAS#2,5

R34

R35

R36

51

51

E5_SDRAM_CLK12,5

E5_SDRAM_WE#2,5

R3251R33

51

51

E5_SDRAM_CLK02,5

E5_SDRAM_CLK#02,5

E5_SDRAM_CLK#12,5

RP21 56/RP

182736

45

E5_SDRAM_A15

E5_SDRAM_A12

E5_SDRAM_A13

E5_SDRAM_A10

RP17 56/RP

E5_SDRAM_A4

E5_SDRAM_A5

1 8

2 7

3 6

4 5

RP15 56/RP

E5_SDRAM_A0

E5_SDRAM_A1

E5_SDRAM_A2

E5_SDRAM_A3

1

413Tuesday, August 12, 2003

of

0.0

29

E5_SDRAM_A[15..0]2,5

1

A A

SSTL2_VDD SSTL2_VDD

3 9 15 55 61 1 18 33

C100

104

C101

104

B B

C C

D D

E5_SDRAM_A[15..0]2,4 E5_SDRAM_A[15..0]2,4

5

4

104

104

104

104

104

104

103

103

103

103

47u/16

C102

C103

C104

C105

C106

C107

C108

C109

C110

C111

+

C112

C98 47u/16

+

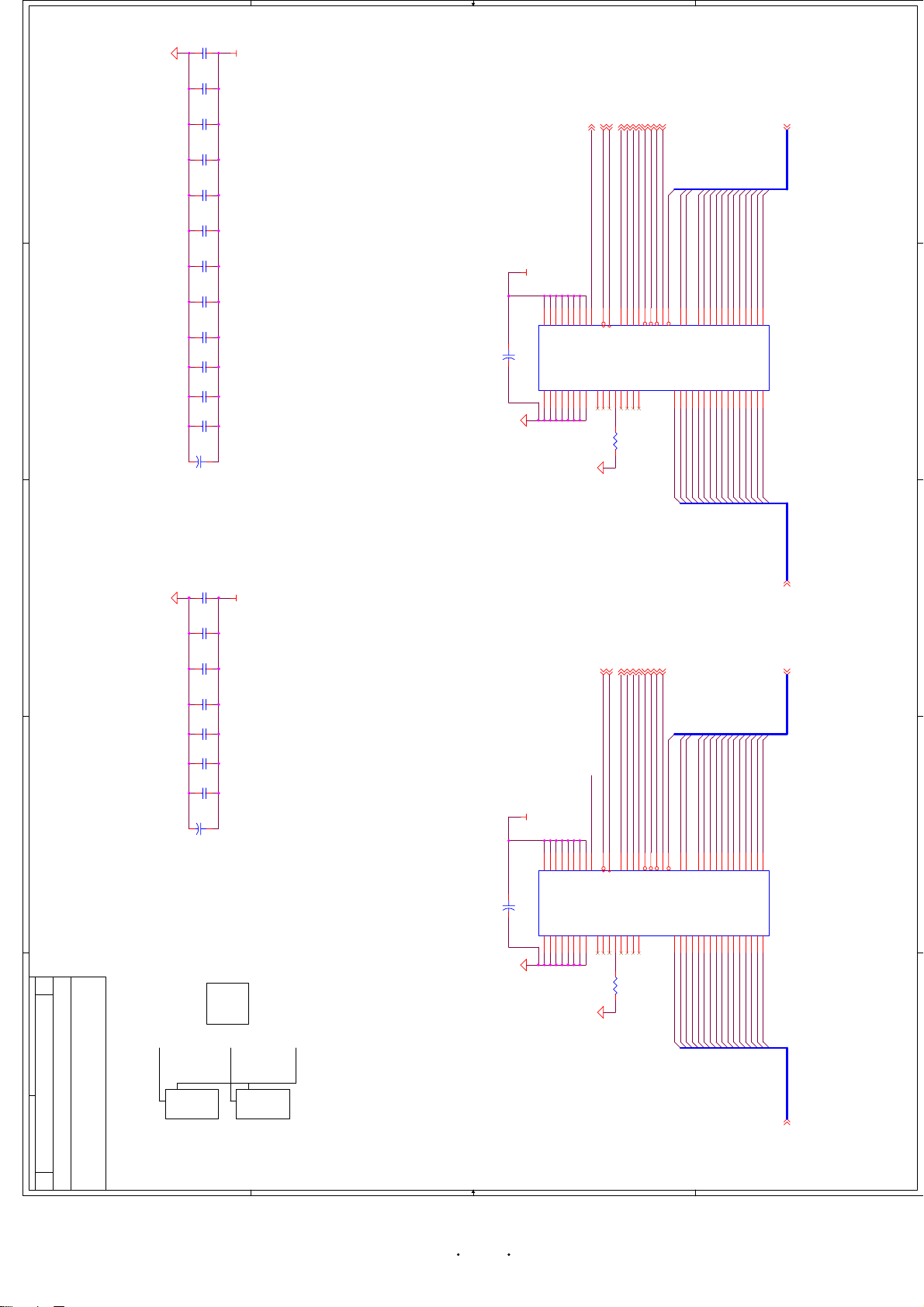

8MX16 DDR

VCCQ

VCCQ

GNDQ

GNDQ

64

155561

VCCQ

GNDQ

9

VCCQ

GNDQ

3

VCCQ

GNDQ

33

VCC

VCC

VCC

GND

GND

GND

3448666125258

VREF

SDRAM_DQM1 3,4 SDRAM_DQM3 3,4

SDRAM_DQM0 3,4

SDRAM_DQS1 3,4 SDRAM_DQS3 3,4

SDRAM_DQS0 3,4 SDRAM_DQS2 3,4

VREF 2,3,4

E5_SDRAM_CLK0 2,4

E5_SDRAM_CLK#0 2,4

46118

49

CLK

CLK#

NC

53

R47 10K

UDQS

E5_SDRAM_CLKE 2,4

E5_SDRAM_RAS# 2,4

E5_SDRAM_CAS# 2,4

E5_SDRAM_WE# 2,4

E5_SDRAM_A6

E5_SDRAM_A9

E5_SDRAM_A7

E5_SDRAM_A4

E5_SDRAM_A8

E5_SDRAM_A10

D9D7D6D8D5D4D3D2D1

SDRAM_DQ7

SDRAM_DQ5

SDRAM_DQ10

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ6

SDRAM_DQ4

E5_SDRAM_A2

E5_SDRAM_A0

E5_SDRAM_A3

E5_SDRAM_A1

293031323536373839402841262724442322212047

U3

A0A1A2A3A4A5A6A7A8A9A10/AP

D0

2

SDRAM_DQ1

SDRAM_DQ0

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ[31..0]3,4

E5_SDRAM_A12

E5_SDRAM_A13 SDRAM_DQ30

E5_SDRAM_A15

E5_SDRAM_A11

165145

CAS#

WE#

LDM

UDM

LDQS

NCNCNCNCNCNCNC

14171925424350

Option for 256Mb Option for 256Mb

A11

BA0

BA1

CS#

CKE

RAS#

D15

D14

D13

D12

D11

D10

65636260595756131154108754

SDRAM_DQ14

SDRAM_DQ12

SDRAM_DQ13

SDRAM_DQ11

SDRAM_DQ15

5

4

3

2

C

Date: Sheet

1

Title

Size Document Number Rev

2 (8M BY 16) DDR SDRAM

C118

104

C119

104

C120

104

C121

103

C122

103

C123

103

C124

103

+

C125

47u/16

BBK

LAYOUT

NOTE:

PLACEMENT

C99 47u/16

+

SSTL2_VDDSSTL2_VDD

8MX16 DDR

VCCQ

GNDQ

64

VCCQ

GNDQ

155561

VCCQ

GNDQ

9

VCCQ

GNDQ

3

VCCQ

GNDQ

VCC

GND

33

VCC

GND

VREF

49

VCC

VREF

GND

3448666125258

GND_SSTL2GND_SSTL2

E5

SDRAM_CLK0

SDRAM_CLK1

SDRAM_A15

SDRAM_DQM2 3,4

E5_SDRAM_CLK1 2,4

E5_SDRAM_CLK#1 2,4

46118

CLK

CLK#

NC

53

R48 10K

UDQS

165145

LDQS

E5_SDRAM_RAS# 2,4

E5_SDRAM_CAS# 2,4

E5_SDRAM_WE# 2,4

CKE

RAS#

CAS#

WE#

LDM

UDM

NCNCNCNCNCNCNC

14171925424350

E5_SDRAM_CLKE 2,4

E5_SDRAM_A10

E5_SDRAM_A12

E5_SDRAM_A11

E5_SDRAM_A7

E5_SDRAM_A13

E5_SDRAM_A15

CS#

E5_SDRAM_A8

E5_SDRAM_A9

A11

BA0

BA1

D15

D14

D13

D12

D11

D10

D9D7D6D8D5D4D3D2D1

65636260595756131154108754

SDRAM_DQ31

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ24

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ23

SDRAM_DQ27

E5_SDRAM_A4

E5_SDRAM_A6

E5_SDRAM_A5

E5_SDRAM_A2

E5_SDRAM_A3

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21E5_SDRAM_A5

SDRAM_DQ18

SDRAM_DQ22

E5_SDRAM_A0

E5_SDRAM_A1

293031323536373839402841262724442322212047

U4

A0A1A2A3A4A5A6A7A8A9A10/AP

D0

M2M1

2

SDRAM_DQ17

SDRAM_DQ16

SDRAM_DQ[31..0]3,4

3

2

1

513Tuesday, August 12, 2003

of

0.0

U22

M1

U25

M2

30404040

A A

2

E5_UART1_RX2 E5_UART1_RTS 2

E5_UART1_TX2

B B

C C

/ETHER_IRQ

,7

HD[15..0]

D D

5

UART SERIAL IO

E5_UART1_CTS 2

13579

+++++

+++++

246810

E5_GPIO22

F_Y_IN13

F_Y_IN

J2

F_CVBS_IN13

F_CVBS_IN

DNS CON5X2

4

V33

HD4

HD6

CON50/SMT/TH/50

50

HD3

HD9

50 pins header for JTAG

debuging

HD2

/RST_SW

HD1

HD0

E5_MA1 2,7

User can put a 6 pins 50mil

header without putting the

HD14

HD12

HD7

E5_TRST

HD11

E5_ALE 2,7

E5_TDO

E5_TCK

HD8

E5_GPIO2 2

E5_TMS

E5_TDI

HD15

10K

10K

10K

10K

/WAIT 2

+

C126

22u/16

E5_TCK 2

R52

R53

R54

R55

E5_MA4 2,7

E5_MA2 2,7

E5_TDI 2

E5_TRST 2

V33

IN4148

1 2

10K

PDI

/E5_WEL 2,7

E5_TDO 2

D2

R50

HD13

HD5

HD10

/E5_OE 2,7

R58

10K

AO_IEC9582 SPDIF_OUT 13

V33

E5_MA3 2,7

/E5_CS1 2

E5_TMS 2

Connector

VCC

/SYS_RST 2,7

E5_MA5 2,7

J1

12345678910111213141516171819202122232425262728293031323334353637383940414243444546474849

E-Link III

/RST_HOST_LED13

/RST_SW

/RST_HOST_LED

5

4

22K

IN4148

IN4148

R56

VCC

1 2

D3

1 2

1 2

D5

1 2

D6

1 2

U6A

74AHCT14

PDO

3 4

U6B

74AHCT14

R51

0

IN4148

D4

IN4148

Package: SOT-23 5L

*V6300F

GND

VDD

RES

NC

NC

12345

RESET CIRCUITRY

U5

3

123

4 5

In1SWIn2

NC NC

VCC

VCC

Out

678

U7

R204

*0

Gnd

F_Y_IN/F_CVBS_IN 10

GND

MM1225XF

C129

104

2

B

Title

Size Document Number Rev

Date: Sheet

FP, RST, IR, AV IO/ELink-3 CON, UART

1

BBK

120

R60

104

330

0

5 6

9 8

U6C

74AHCT14

U6D

74AHCT14

C128

R59

L2

R57

33

OPTICAL 13

C127

104

3

2

VCC

1

R49

613Tuesday, August 12, 2003

of

0.0

31

/SYS_RST2,7

*0

A A

R86

680

B B

ATAPI_RESET2

C C

D D

C137

RP30 33/RP

ATAPI_DATA10 2

ATAPI_DATA11 2

182736

HD_AT10

HD_AT11

ATAPI_DATA8 2

ATAPI_DATA9 2

45

HD_AT8

HD_AT9

22PF

10K

RP29 33/RP

R87

ATAPI_DATA6 2

ATAPI_DATA7 2

45

HD_AT7

HD_AT6

ATAPI_DATA4 2

ATAPI_DATA5 2

182736

HD_AT5

HD_AT4

RP28 33/RP

IORDY

DMARQ

R84 82

R83 82

ATAPI_IORDY2

ATAPI_DMARQ2

INT_ATA

R82 82

ATAPI_INTRQ2

ATAPI_DATA3 2

45

HD_AT3

R81 0

RSTATA

ATAPI_DATA2 2

HD_AT2

5

4

ATAPI_DMAACK_L 2

R101 33

DMACK

ATAPI_DIOR_L 2

R100 33

DIOR

ATAPI_DIOW_L 2

R99 33

DIOW

AtapiAddr4 2

R98 33

CS3FX

AtapiAddr3 2

4 5

CS1FX

AtapiAddr2 2

AtapiAddr0 2

AtapiAddr1 2

1 8

2 7

3 6

RP31 33/RP

ATA_A2

ATA_A0

ATA_A1

ATAPI_DATA15 2

ATAPI_DATA14 2

ATAPI_DATA12 2

ATAPI_DATA13 2

182736

45

HD_AT15

HD_AT14

HD_AT13

HD_AT12

4.7K

10K

ATAPI_DATA0 2

ATAPI_DATA1 2

182736

HD_AT0

HD_AT1

RP27 33/RP

VCC

R71

VCC

R72

DEDICATED ATAPI INTERFACE

4 5

DNS AT24C16

GNDSDA

SCL

WP

678

SCL 2,10,11,12,13

SDA 2,10,11,12,13

5

E5_GPIO42,8,10,11

Select the source

of /RST

11 10

U6E

/RST_AUDIO 12,13

13 12

74AHCT14

U6F

74AHCT14

/RST_7302 2,8,10,11

/RST_PHY 2,8,10,11

/RST_7115 2,8,10,11

123

U11

A0A1A2

VCC

V33

104

C136

R67

VCC

4.7K

R68

4.7K

BOARD REGISTERS

4

3

2

Date: Sheet

1

C

Title

Size Document Number Rev

FLASH, BREG, ATA, IDC

HEADER 20X2

37 38

39 40

0

BBK

HD[1:0]

HD[7]

01

11

1

10

0 Normal Mode (Jumper 1-2)

00

1

0HD[2] 128Mb DDR SDRAM

Nanya

256Mb DDR SDRAM

ESMT - M13S128168A-6T

Samsung - K4H281638D-TCB3

Micron - MT46V8M16-55

Debuge Mode (Jumper 2-3)

CS1FX

35 36

CS3FX

HD[15..0]2,6

E5_MA3 2,6

E5_MA22 2

E5_MA4 2,6

E5_MA1 2,6

E5_MA2 2,6

E5_MA5 2,6

HD_AT0

17 18

HD_AT15

HD_AT1

13 14

15 16

HD_AT14

HD_AT4

HD_AT3

HD_AT2

78

910

11 12

HD_AT12

HD_AT11

HD_AT13

HD_AT7

HD_AT5

RSTATA

HD_AT6

J3

12

34

56

HD_AT9

HD_AT8

HD_AT10

HD7

HD3

HD4

HD5

HD6

HD1

HD2

HD0

R73 DNS-100KR89 100K

R74 100K

R75 DNS-100K

R76 DNS-100K

R77 DNS-100K

R78 DNS-100K

R79 DNS-100K

R80 100K

HD[15..0]2,6

HOST Read

V33

2MB

8MB

4MB

R64,R65,R66 R69,R70

R69,R70

R69

R64,R65,R66

R64,R65,R66,R70

Size Stuff Not Stuff

R70 DNS-0

R69 0

BA20

BA21

R66 DNS-0

R65 DNS-0

RY/BY/A19

NC/A20/A20

BA4

BA22

BA5

BA22

R64 DNS-0

A19/A19/A21

BA3

BA2

R63 0

WP#/ACC/SYS_RST

DMARQ

DIOW

DMACK

INT_ATA

ATA_A1

DIOR

IORDY

ATA_A0

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

R97

CAB_SEL

R90 DNS100K

R91 100K

R92 100K

R93 DNS-100K

R94 DNS-100K

R95 DNS-100K

R96 100K

KEYWAY (NO PIN)

ATA_A2

104

C135

104

C133

104

VCC

74LVC16373

GND

45

BA1

BA1

BA17

MX29LV160

C134

104

E5_ALE 2,6

C130

104

C131

183142

7

VCC

VCC

VCC

GND

GND

GND

A1

A0

25

C132

104

HD14

HD15

V33

2A6

2A7

2A8

2OE

2LE

GND

GND

GND

GND

BA2

CE

BA1

2B6

2B7

2B8

BA21

BA20

R62

0

BA8

BA18

BA7

BA4

BA6

BA19

BA3

BA5

RY/BY/A19

A18

A17A7A6A5A4A3A2

VSS

OE

D2D9D1D8D0

HD2

HD8

HD9

HD1

HD0

HD12

HD13

HD11

2A3

2A4

2A5

2B3

2B4

2B5

BA19

BA17

BA18

/SYS_RST2,6

ACC

WP#/ACC

RY/BY/A19

RST

ACC

WP/ACC

VCC

D11D3D10

HD3

HD11

HD10

HD10

HD9

2A1

2A2

2B1

2B2

BA15

BA16

/E5_WEL2,6

NC/A20/A20

WE

D4

HD4

HD8

1LE

1A8

1OE

1B8

BA14

10K

NC/A20/A20

A19/A19/A21

BA9

101112131415161718192021222324

A19/A19/A21

HD12

HD5

HD13

HD7

3714836353332302927262425

BA13

BA10

HD6

HD2

HD1

HD4

HD6

HD3

HD0

HD5

47464443414038

U9

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1B1

1B2

1B3

1B4

1B5

1B6

1B7

235689111213141617192022234101521283439

BA7

BA6

BA8

BA12

BA11

BA9

BA[22..1]

V33

R61

BA13BA10

BA12

BA16

BA15

BA14

BA11

123456789

U10

A15

A14

A13

A12

A11

A10A9A8

BYTE/VIO

VSS

D15D7D14D6D13D5D12

A16

4847464544434241403938373635343332313029282726

V33

BA17

HD7

HD15

HD14

3

FLASH MEMORY(2 or 4 or 8 Mb)

2

1

713Tuesday, August 12, 2003

of

0.0

R88 *0

JP1

DNS HEADER 3X1

123

R85 *0

32

/E5_CS0 2

/E5_OE 2,6

HD[15..0] 2,6

Loading...

Loading...