Page 1

SERVICE MANUAL

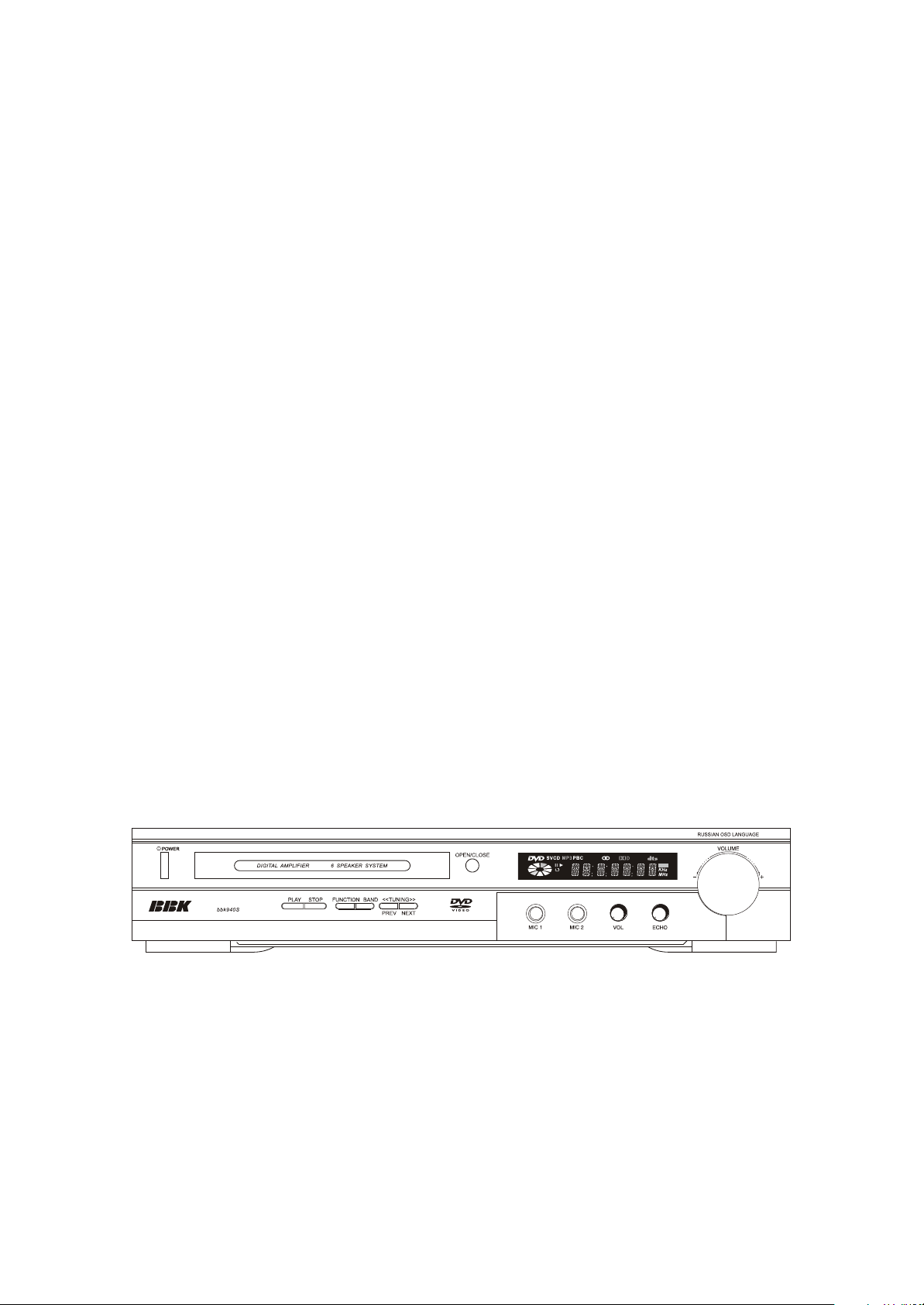

bbk940S

ALL FM

ST.

TUNED

AM

3D

MEM

Page 2

CONTENTS

1. SAFETY PRICAUTIONS

2. PREVENTION OF ELECTRO STATIC DISCHARGE(ESD)TO ELECTROSTATICALLY

SENSITIVE(ES)DEVICES

3. CONTROL BUTTON LOCATIONS AND EXPLANATIONS

4. PREVERTION OF STATIC ELECTRICITY DISCHARGE

5. ASSEMBLING AND DISASSEMBLING THE MECHANISM UNIT

5.1 OPTICAL PICKUP UNIT EXPLOSED VIEW AND PART LIST

5.2 BRACKET EXPLOSED VIEW AND PART LIST

5.3 MISCELLANEOUS

6. ELECTRICAL CONFIRMATION

6.1 VIDEO OUTPUT (LUMINANCE SIGNAL) CONFIRMATION

6.2 VIDEO OUTPUT(CHROMINANCE SIGNAL) CONFIRMATION

1

1

2

4

5

5

7

8

9

9

10

7. MPEG BOARD CHECK WAVEFORM

8. IC BLOCK DIAGRAM & DESCRIPTION

8.1 MT1336 12

8.2 MT1369

8.3 U214 HY29F800 31

8.4 U203 SDRAM-HY57V1610D

8.5 LX1722

8.6 SI4558DY

9. SCHEMATIC & PCB WIRING DIAGRAM

10. SPARE PARTS LIST 65

11

12

20

34

35

39

43

Page 3

1.1 GENERAL GUIDELINES

1. SAFETY PREAUTIONS

2.PREVENTION OF ELECTRO STATIC DISCHARGE(ESD)TO

ELECTROSTATICALLY SENSITIVE(ES)DEVICES

1

1. When servicing, observe the original lead dress. if a short circuit is found, replace all parts which have

been overheated or damaged by the short circuit.

2. After servicing, see to it that all the protective devices such as insulation barrier, insulation papers

shields are properly installed.

3. After servicing, make the following leakage current checks to prevent the customer from being exposed

to shock hazards.

Some semiconductor(solid state)devices can be damaged easily by static electricity. Such components

commonly are called Electrostatically Sensitive(ES)Devices. Examples of typical ES devices are integrated

circuits and some field-effect transistors and semiconductor chip components. The following techniques

should be used to help reduce the incidence of component damage caused by electro static discharge(ESD).

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain

off any ESD on your body by touching a known earth ground. Alternatively, obtain and wear a commercially

availabel discharging ESD wrist strap, which should be removed for potential shock reasons prior to

applying power to the unit under test.

2. After removing an electrical assembly equipped with ES devices,place the assembly on a conductive

surface such as alminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder ES devices.

4. Use only an anti-static solder removal device. Some solder removal devices not classified as anti-static

(ESD protected)can generate electrical charge sufficient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate electrical charges sufficient to damage ES

devices.

6. Do not remove a replacement ES device from its protective package until immediately before you are

ready to install it. (Most replacement ES devices are packaged with leads electrically shorted together by

conductive foam, alminum foil or comparable conductive material).

7. Immediately before removing the protective material from the leads of a replacement ES device, touch

the protective material to the chassis or circuit assembly into which the device will be installed.

Caution

Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion

such as the brushing together of your clothes fabric or the lifting of your foot from a carpeted floor can

generate static electricity(ESD).

notice (1885x323x2 tiff)

Page 4

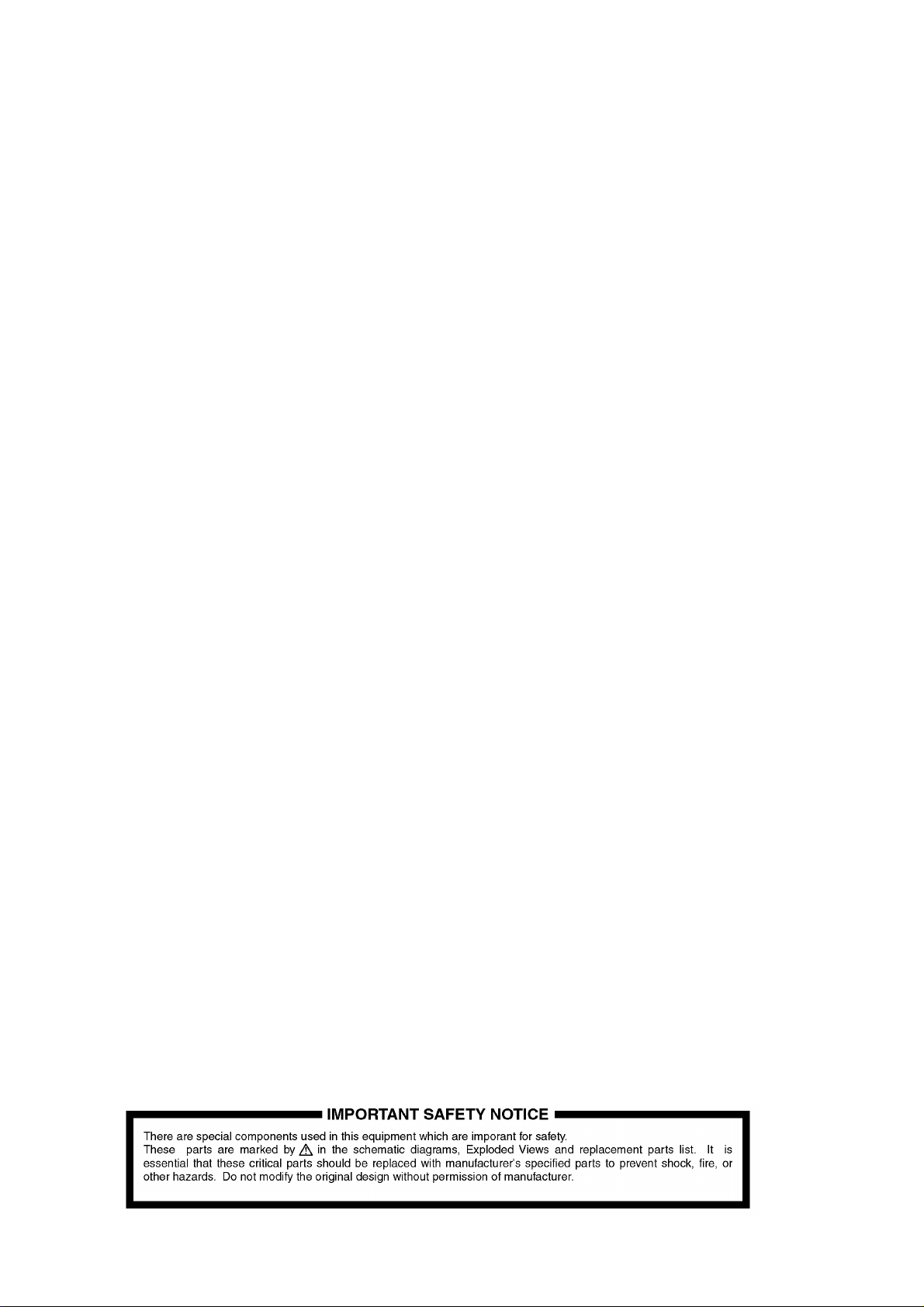

3.Control Button Locations and Explanations

2

Front Panel Illustration

POWER switch

2

Disc tray

2

7 8 9 10 11

6

6

7

PLAY button

STOP button

3

12 13 14 15

ALL FM

4

ST.

TUNED

AM

11

3D

MEM

DVD MODE: NEXT button

5

TUNER MODE: TUNING button

12

MIC 1 jack

3

OPEN/CLOSE button

4

VFD display window

5

VOLUME knob

8

FUNCTION button

9

DVD MODE: PAUSE button

TUNER MODE: BAND button

10

DVD MODE PREV button

TUNER MODE TUNING button

13

MIC 2 jack

14

MIC VOLUME knob

15

ECHO adjustment knob

Page 5

Control Button Locations and Explanations (Continued)

3

Remote Control Illustration

STANDBY

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

AUDIO

1 2

5

9 0 +10

TITLE

SETUP

PLAY PAUSE STOP

SLOW REPEAT

SF

SLEEP

SAVE

MAN/AUTO

BAND BASS VOL

32

RETURN button

Back to the previous menu.

33

MENU button

Display the disc menu, PBC ON/OFF button.

34

ZOOM button

Zoom in/out the playing frame.

35

OSD button

Display the disc information.

36

GOTO button

Play from the desired point.

37

ANGLE button

Camera angles switch, MP3/JPEG playback modes switch.

38

FUNCTION button

DISC/RADIO/AUX IN switch.

39

EJECT button

Open/Close the disc tray.

ANGLE FUNCTION

SUBTITLE

6 7 8

P/NL/R

ZOOM

SELECT

A-B

PSM

EQ

PRESET

TUNING

TREBLE

3

EJECT

4

GOTO

OSD

MENU

RETURN

MAIN

VOL

MUTE

SPEAKERS

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

STANDBY button

Enter or exit the standby mode.

2

AUDIO button

Change the audio language.

3

SUBTITLE button

Change subtitle languages/Switch JPEG display modes.

4

NUMBERED buttons

5

L/R button

Switch audio channel.

6

P/N button

Switch the TV system between PAL, NTSC and AUTO.

7

TITLE button

DVD titles.

8

DIRECTION ARROWS

UP/DOWN/LEFT/RIGHT DIRECTION ARROW.

9

SELECT button

10

SETUP button

Function setup.

11

PLAY button

Normal playback.

12

PAUSE button

Pause playback.

13

SLOW button

Slow playback.

14

SF button

Adjust sound field effects.

15

REPEAT button

Repeat playback.

16

SLEEP button

Sleep timer.

17

EQ button

Adjust EQ effects.

18

SAVE button

Stations saving button, up to 20 FM/AM stations can

be saved respectively.

19

TUNING +/- buttons

Tuning up/down stations.

FWD/REV button

Fast forward/backward playback.

20

MAN/AUTO button

Manual/automatic tuning switch.

21

BAND button

FM/AM switch.

22

BASS +/- button

Increase/decrease bass.

23

TREBLE +/- button

Increase/decrease treble.

24

VOL +/- button

Increase/decrease power amplifier's channel volume.

25

SPEAKERS button

Select power amplifier's channel volume.

26

PRESET +/- button

Select the preset channels.

PREVIOUS/NEXT button

Select previous/next chapter or track when playing.

27

MUTE button

Turn off/on audio outputs

28

27

MAIN VOL button

Increase/decrease the master volume.

29

PSM button

Power Spectrum Meter on/off.

2730

A-B button

Repeat the selected section A-B.

31

STOP button

Stop playback.

Page 6

The laser diode in the traverse unit (optical pickup)may brake down due to static electricity of clothes or human

body. Use due caution to electrostatic breakdown when servicing and handling the laser diode.

Some devices such as the DVD player use the optical pickup(laser diode)and the optical pickup will be damaged

by static electricity in the working environment.Proceed servicing works under the working environment where

1. Put a conductive material(sheet)or iron sheet on the area where the optical pickup is placed,and ground the

3. The flexible cable may be cut off if an excessive force is applied to it.Use caution when handling the cable.

4

4.PREVENTION OF STATIC ELECTRICITY DISCHARGE

4.1.Grounding for electrostatic breakdown prevention

grounding works is completed.

4.1.1. Worktable grounding

sheet.

4.1.2.Human body grounding

1 Use the anti-static wrist strap to discharge the static electricity from your body.

safety_3 (1577x409x2 tiff)

4.1.3.Handling of optical pickup

1. To keep the good quality of the optical pickup maintenance parts during transportation and before

installation, the both ends of the laser diode are short-circuited.After replacing the parts with new ones,

remove the short circuit according to the correct procedure. (See this Technical Guide).

2. Do not use a tester to check the laser diode for the optical pickup .Failure to do so willdamage the laser

diode due to the power supply in the tester.

4.2. Handling precautions for Traverse Unit (Optical Pickup)

1. Do not give a considerable shock to the traverse unit(optical pickup)as it has an extremely high-precise

structure.

2. When replacing the optical pickup, install the flexible cable and cut is short land with a nipper. See the

optical pickup replacement procedure in this Technical Guide. Before replacing the traverse unit, remove

the short pin for preventingstatic electricity and install a new unit.Connect the connector as short times as

possible.

4. The half-fixed resistor for laser power adjustment cannot be adjusted. Do not turn the resistor.

Page 7

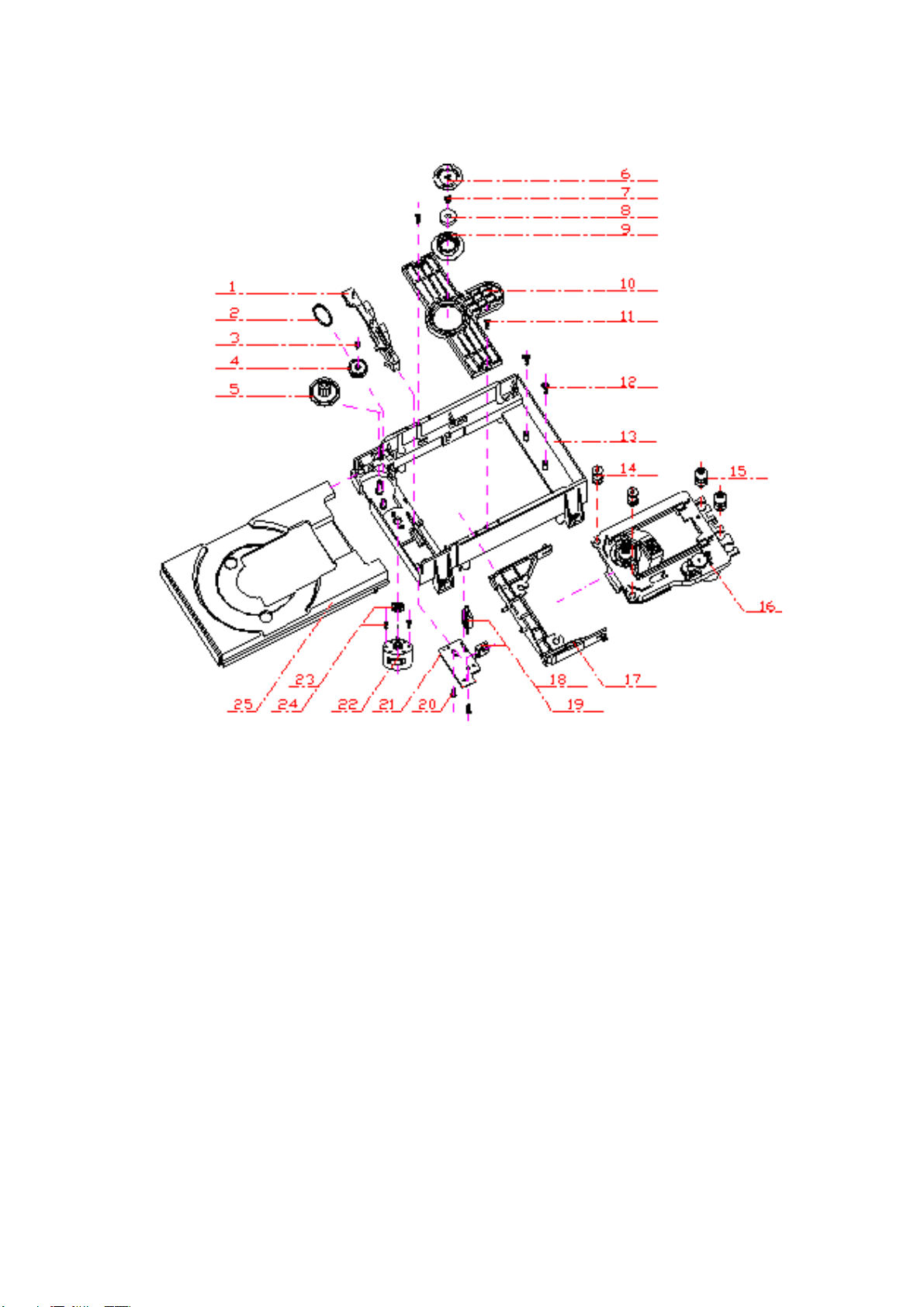

5.1 Optical pickup Unit Explosed View and Part List

5. Assembling and disassembling the mechanism unit

5

Pic (1)

Page 8

Materials to Pic (1)

6

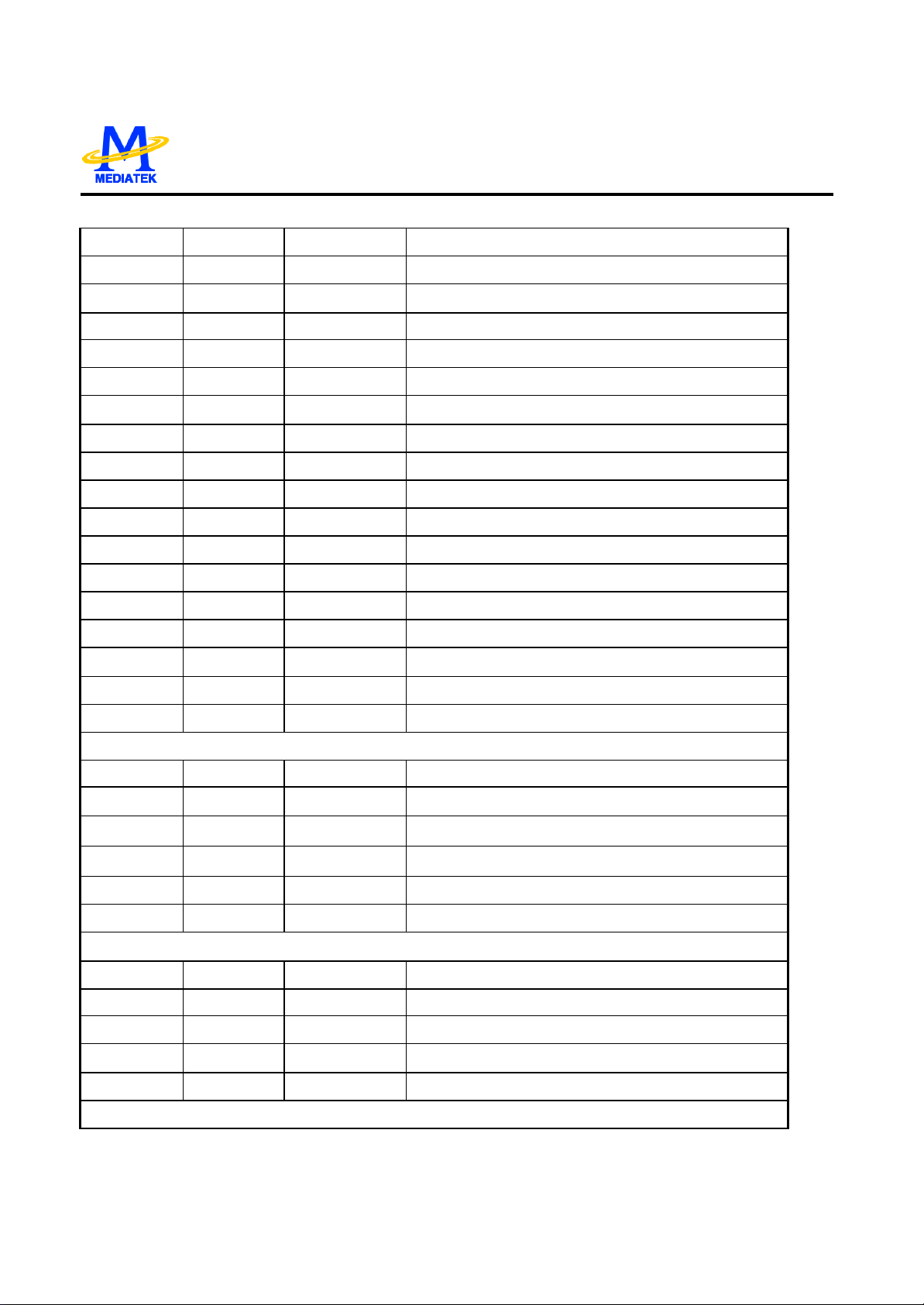

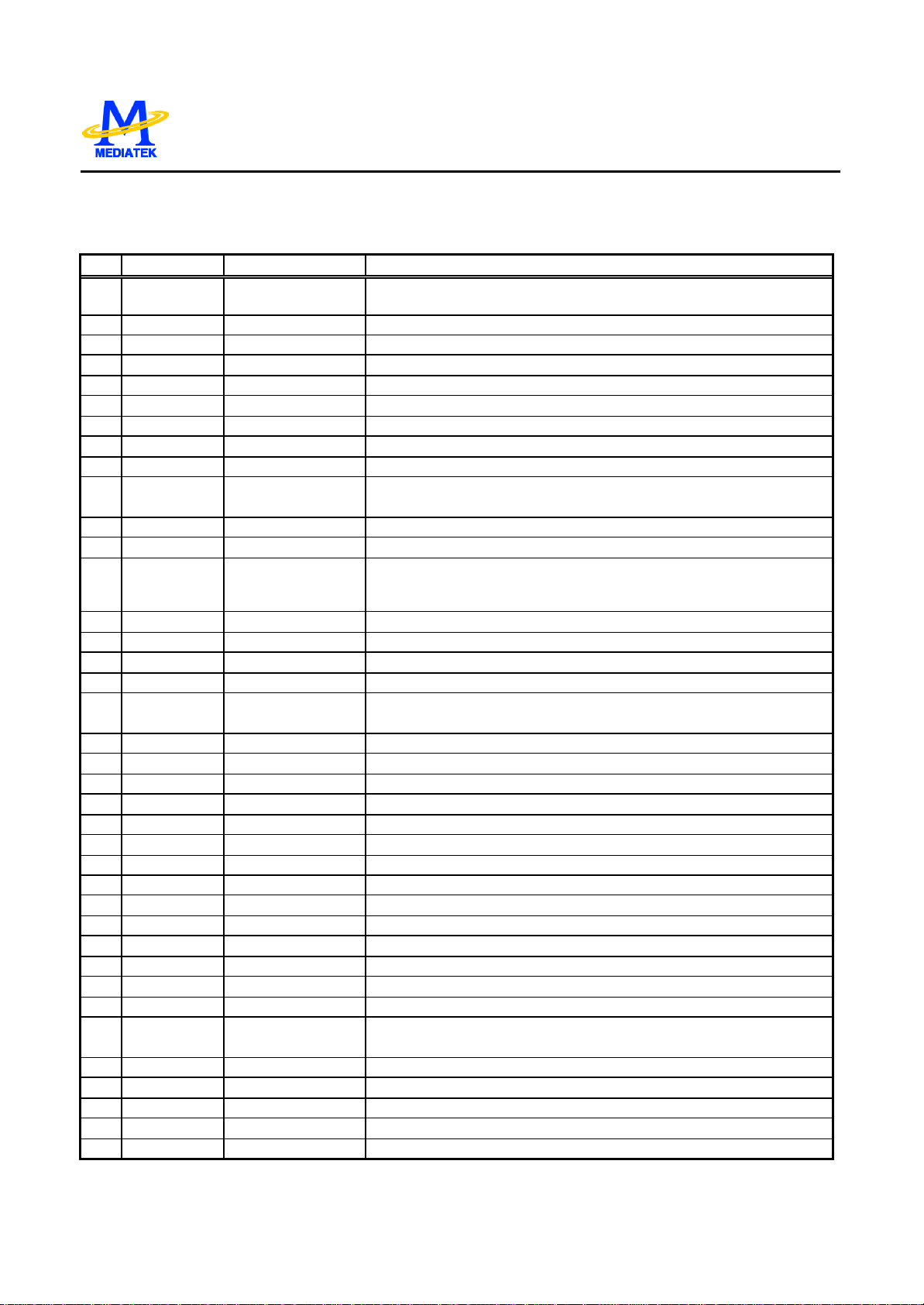

No. PARTS CODE PARTS NAME Q ty

14692200 SF-HD60 1

1

1EA0311A06300 ASSY, CHASSIS, COMPLETE 1

2

Or

3

4

5

6

7

8

9

10

11

21

Or

31

32

1EA0M10A15500 ASSY, MOTOR, SLED 1

1EA0M10A15501 ASSY, MOTOR, SLED 1

1EA2451A24700 HOLDER, SHAFT 3

1EA2511A29100 GEAR, RACK 1

1EA2511A29200 GEAR, DRIVE 1

1EA2511A29300 GEAR, MIDDLE, A 1

1EA2511A29400 GEAR, MIDDLE, B 1

1EA2744A03000 SHAFT, SLIDE 1

1EA2744A03100 SHAFT, SLIDE, SUB 1

1EA2812A15300 SPRING, COMP, TYOUSEI 3

1EA2812A15400 SPRING, COMP, RACK 1

1EA0B10B20100 ASSY, PWB 1

1EA0B10B20200 ASSY, PWB 1

SEXEA25700--- SPECIAL SCREW BIN+-M2X11 3

SEXEA25900--- SPECIAL SCREW M1.7X2.2 2

33

34

35

Note : This parts list is not for service parts supply.

SFBPN204R0SE- SCR S-TPG PAN 2X4 2

SFSFN266R0SE- SCR S-TPG FLT 2.6X6 1

SWXEA15400--- SPECIAL WASHER 1.8X4 X0.25 2

Page 9

5.2 Bracket Explosed View and Part List

7

Pic (2)

Materials to Pic(2)

1.bracket 14. front silicon rubber

2.belt 15. Back silicon rubber

3.screw 16. Pick-up

4.belt wheel 17. Pick-up

5.gearwheel 18. switch

6.iron chip 19. Five-pin flat plug

7. Immobility mechanism equipment 20. screw

8. Magnet 21. PCB

9. Platen 22. motor

10. Bridge bracket 23. Motor wheel

11. screw 24. screw

12. screw 25.tray

13. Big bracket

Before going process with disassembly and installation, please carefully both

peruse the chart and confirm the materials.

Page 10

5.3 MISCELLANEOUS

8

5.3.1 Protection of the LD(Laser diode)

Short the parts of LD circuit pattern by soldering.

5.3.2 Cautions on assembly and adjustment

Make sure that the workbenches,jigs,tips,tips of soldering irons and measuring instruments are

grounded,and that personnel wear wrist straps for ground.

Open the LD short lands quickly with a soldering iron after a circuit is connected.

Keep the power source of the pick-up protected from internal and external sources of electrical

noise.

Refrain from operation and storage in atmospheres containing corrosive gases (such as H2S,SO2,

NO2 and Cl2)or toxic gases or in locations containing substances(especially from the organic silicon,cyan,

formalin and phenol groups)which emit toxic gases.It is particularly important to ensure that none of the

above substances are present inside the unit.Otherwise,the motor may no longer run.

Page 11

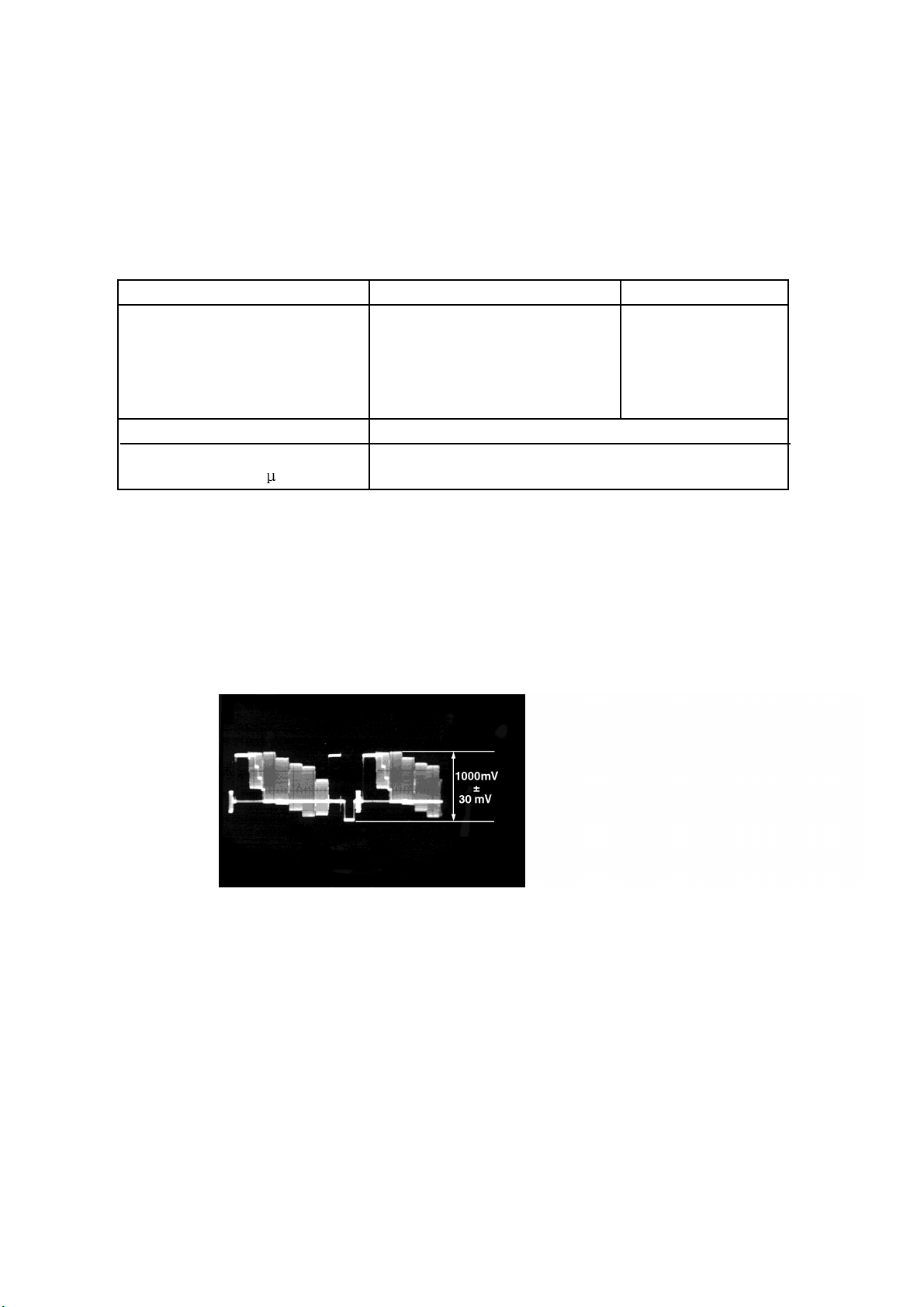

6.1. Video Output (Luminance Signal) Confirmation

6.Electrical Confirmation

9

DO this confirmation after replacing a P.C.B.

Measurement point

Video output terminal

Measuring equipment,tools

200mV/dir,10 sec/dir

Purpose:To maintain video signal output compatibility.

1.Connect the oscilloscope to the video output terminal and terminate at 75 ohms.

2.Confirm that luminance signal(Y+S)level is 1000mVp-p±30mV

PLAY(Title 46):DVDT-S15

PLAY(Title 12):DVDT-S01

Mode Disc

Color bar 75%

Confirmation value

1000mVp-p±30mV

DVDT-S15

or

DVDT-S01

Page 12

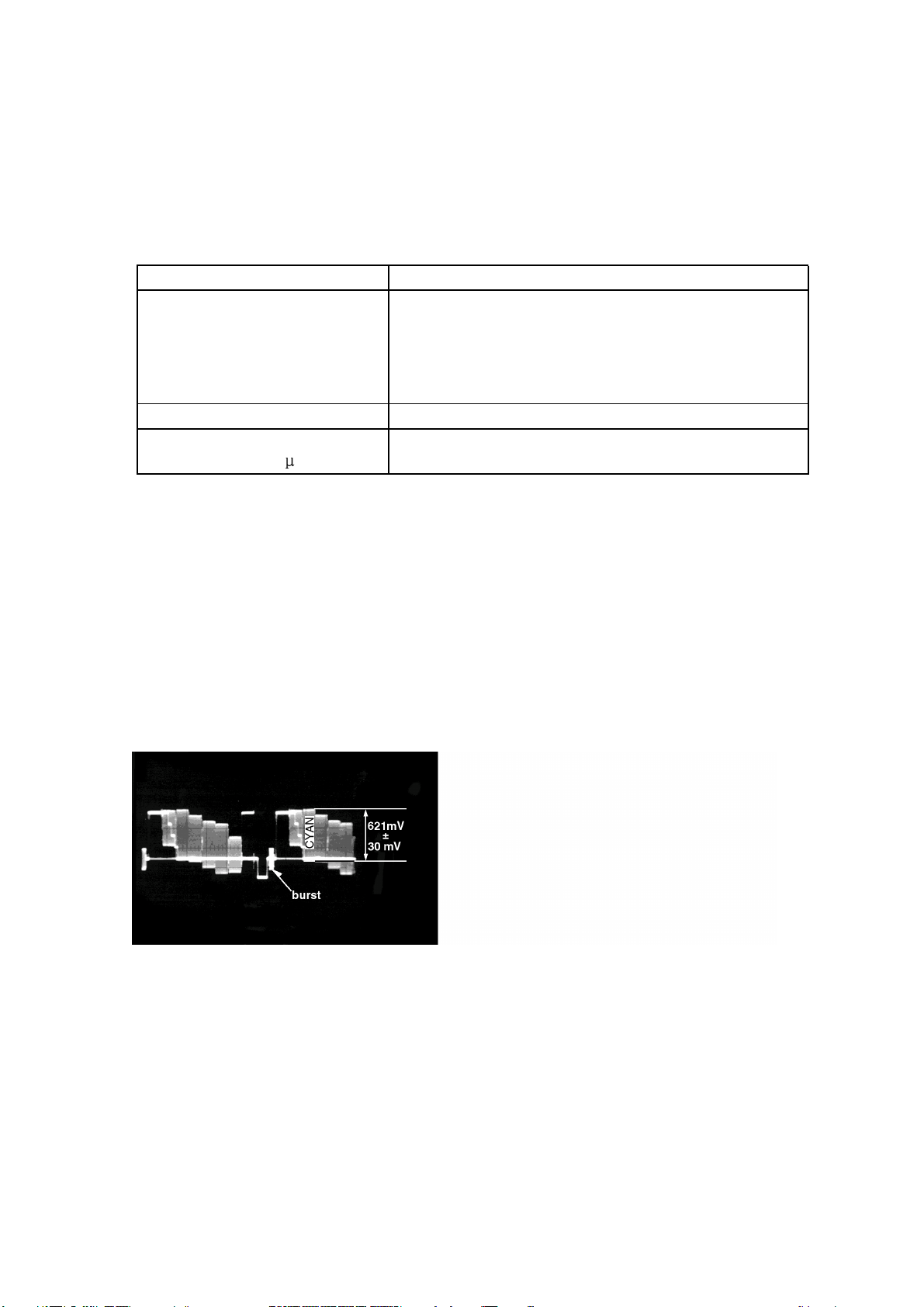

Do the confirmation after replacing P.C.B.

Screwdriver,Oscilloscope

6.2 Video Output(Chrominance Signal) Confirmation

10

Measurement point

Video output terminal

Measuring equipment,tools Confirmation value

200mV/dir,10 sec/dir

Purpose:To maintain video signal output compatibility.

1.Connect the oscilloscope to the video output terminal and terminate at 75 ohme.

2.Confirm that the chrominance signal(C)level is 621 mVp-p±30mV

PLAY(Title 46):DVDT-S15

PLAY(Title 12):DVDT-S01

Mode Disc

Color bar 75%

621mVp-p±30mV

DVDT-S15

or

DVDT-S01

Page 13

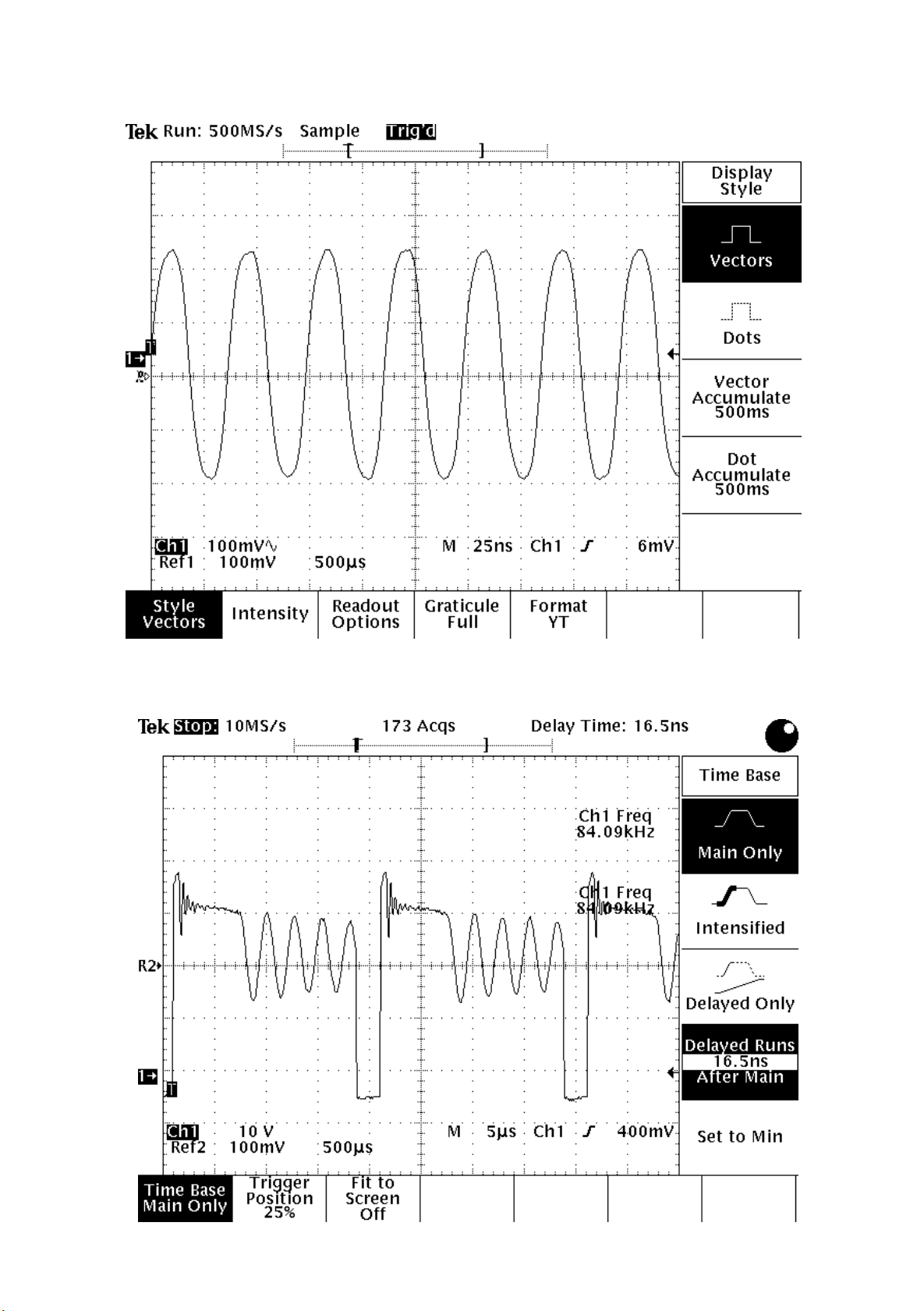

7.MPEG BOARD CHECK WAVEFORM

7.1 27MHz WAVEFORM

7.2 IC5L0380R PIN.2 WAVEFORM DIAGRAM

11

Page 14

8.1 MT1336

8. IC BLOCK DIAGRAM & DESCRIPTION

12

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1336

GENERAL DESCRIPTION

MT1336 is a high performance CMOS analog front-end IC for both CD_ROM driver up to 48XS and

DVD-ROM driver up to 16XS. It also supports DVD- RAM read up to 4XS Version 2. It contains servo amplifiers

to generate focusing error, 3-beam tracking error, 1 beam radial push-pull signal, RF level and SBAD for servo

functions. It also includes DPD tracking error signal for DVD_ROM application. For DVD- RAM disks, there are

also Differential Push-Pull (DPP) method for generating tracking signal and Differential Astigmatic Detection

(DAD) for processing focusing signal. Programmable equalizer and AGC circuits are also incorporated in this

chip to optimize read channel performance. In addition, this chip has dual automatic laser power control circuits

for DVD- ROM (DVD-RAM) and CD -ROM seperately and reference voltage generators to reduce external

components. Programmable functions are implemented by the access of internal register through bi-directional

serial port to configure modes selection.

FEATURES

n RF equalizer with programmable

13dB.

n MT1336 supports at least eight different kinds of pick-up heads with versatile input configuration for

both RF input stages and servo signal blocks.

n Versatile on -line AGC.

n 3 beams tracking error signal generator for CD_ROM application.

n One beam differential phase tracking error (DPD) generator for DVD_ROM application.

n Differential push pull tracki ng error (DPP) generator for DVD_RAM application.

n Focusing error signal generator for CD-ROM, DVD-ROM and DVD-RAM (DAD method).

n RF level signal generator.

n Sub-beam added signal for 3 beams CD_ROM.

n One beam push-pull signal generator for central servo application.

n High speed RF envelop detection circuit with bandwidth up to 400KHz for CD-ROM.

n Defect and Blank detection circuits.

from 3MHz to 70 MHz and programmable boost from 3dB to

f

c

n Dual automatic laser power control circuits with programmable level of LD monitor voltage.

n Vref=1.4V voltage and V2ref=2.8V voltage generators.

n V20=2.0V voltage for pick-up head reference.

n Bi-directional serial port to access internal registers.

Page 15

MT1336

13

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

DVDA

CDA

DVDB

CDB

DVDC

CDC

DVDD

CDD

DVDRFIN

DVDRFIP

DPFN

DPFO

DPDMUTE

CDFOP

CDFON

RFGC

RFGCU

RFGCI

AGC1

AGC2

AGC3

RFSUBO

WOBSO

V20

V2REFO

VREFO

MC

TPI

TNI

MA

MB

MD

OSP

OSN

ATTENUATOR

INPUT MUX

AGC

AGC

SA

SB

SC

SD

IR

VGA

VGA EQ

ENVELOP

ENVELOP

DETECTOR

DETECTOR

DPD

SBAD

TE

PCS

DVD

APC

RFOP

RFON

LRFRP

DEFECT

HRFRP

CRTP

CRTPLP

CSO

LVL

TEO

FEO

REFCOS

HALLCOS

COSPHI

REFSIN

HALLSIN

SINPHI

MDI2

LDO2

RF

LEVEL

FE

CD

APC

MDI1

LDO1

CENTRAL

SERVO

UDGATE

WOBBLE

DET

REF and 2VREF

REF and 2VREF

Voltage Generator

Voltage Generator

SERIAL

PORT

IDGATE

VFO13

SDATA

SLCK

SDEN

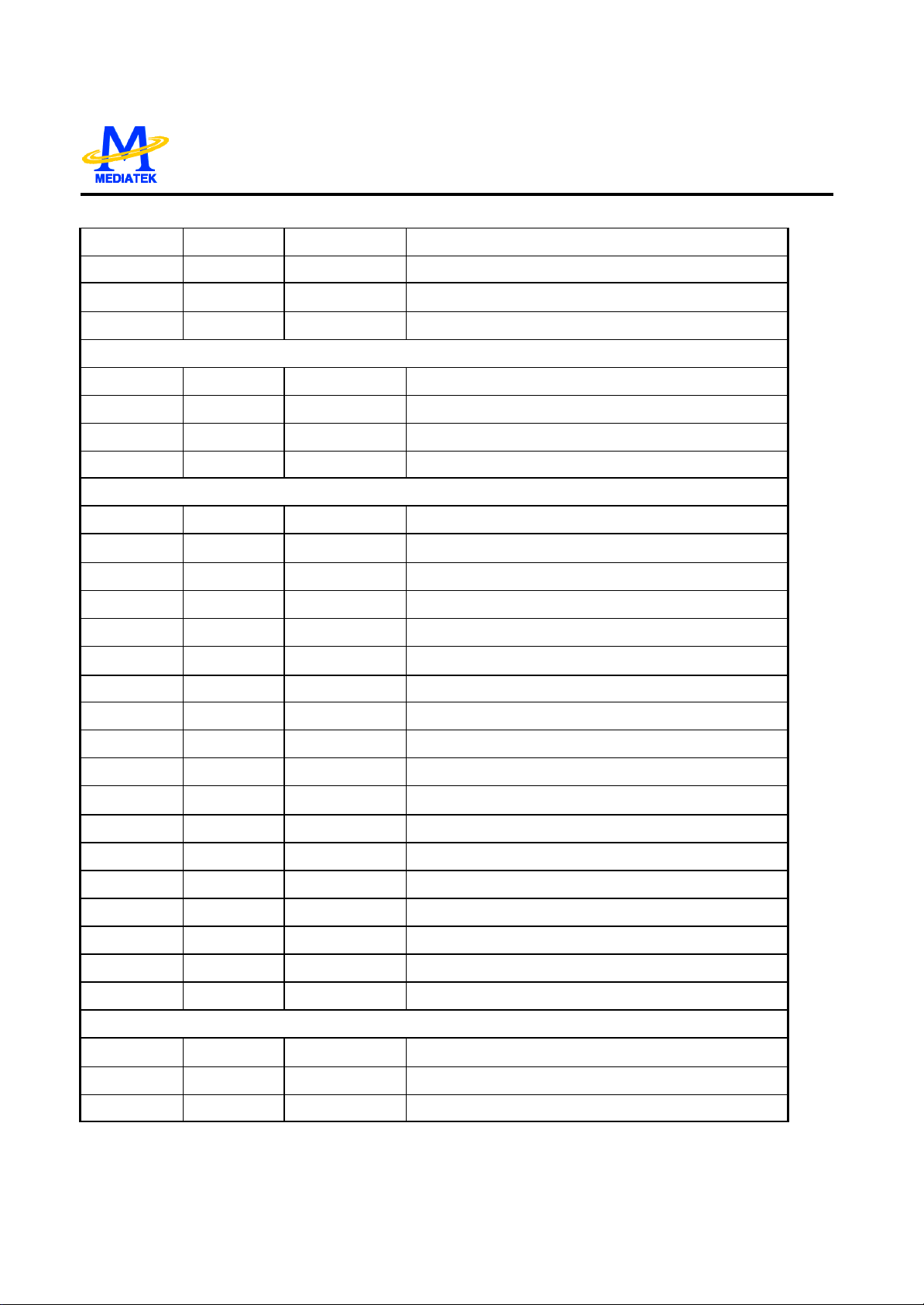

MT1336 FUNCTION BLOCKS DIAGRAM

Page 16

14

MT1336

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

WGND

WOBSO

WVDD

AGNDX

AGNDX

AVDDO

RFOP

RFON

AGNDO

TM1

TM2

TM3

AGNDT

TM4

AVDDT

V2REFO

VREFO

V20

FEO

LVL

CSO

TEO

VDDP

DEFECT

LRFRP

HRFRP

CRTP

CRTPLP

TRLPA

TRLP

HTRC

GNDP

DPFN

DPFO

AGNDX

AGNDX

AGNDX

VDD

VFO13

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

RFSUBO

LDO2

LDO1

127

126

125

128

3940414243

MDI1

124

WAVDD

MDI2

123

AGC1

AGC2

AGC3

121

120

119

122

MT1336

DVD-ROM

DVD_RAM

454647

44

48

WAGND

TNI

SGND

118

117

116

With

Read

495051

525453

CDFOP

SVDD

TPI

CDFON

115

114

113

112

111

555657585960616263

SASBMC

IR

AVDDSCSD

110

109

108

MD

AGND

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

MB

MA

DVDA

DVDB

DVDC

DVDD

DVDRFIP

DVDRFIN

CDA

CDB

CDC

CDD

OSN

OSP

RFGC

RFGCU

RFGCI

CEQP

CEQN

AGNDX

AGNDX

MON

MOP

SW1

SW2

SWO

SINPHI

REFSIN

HALLSIN

AGNDM

REFCOS

HALLCOS

COSPHI

AVDDM

AGNDX

AVDDF

VCON

AGNDF

IO0

GND

UDGATE

HDGATE

IO4

IO1

IO5

IO7

IO8

IO9

IO6

IO3

IO2

IOB

IOA

MT1336 PIN ASSIGNMENT

SCLK

VDDS

XCK16M

RST

SDEN

GNDS

SDATA

AGNDP

AGNDX

AVDDP

DPDMUTE

Page 17

15

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1336

MT1336 PIN DESCRIPTIONS

Pin Numbers Symbol Type Description

LQFP128

RF Flag Interface

23 DEFECT Digital Output Flag of bad data output status

RF SIO interface

56 SCLK Digital Input RF serial clock input

58 SDEN Digital Input RF serial data enable

59 SDATA Digital IO RF serial data IO

60 RST Digital input Reset (active high)

55 XCK16M Digital Input 16.9MHz for verification

RF SERVO interface

40 UDGATE Digital Input Con trol signal for DVD-RAM

41 IDGATE Digital Input Control signal for DVD -RAM

38 VFO13 Digital Input DVD -RAM Header signal

RF

100 DVDA Analog input AC coupled DVD RF signal input A

99 DVDB Analog Input AC coupled DVD RF signal input B

98 DVDC Analog Input AC coupled DVD RF signal input C

97 DVDD Analog Input AC coupled DVD RF signal input D

95 DVDRFIN Analog Input AC coupled DVD RF signal input RFIN

96 DVDRFIP Analog Input AC coupled DVD RF signal input RFIP

94 CDA Analog Input AC coupled CD RF signal input A

93 CDB Analog Input AC coupled CD RF signal input B

92 CDC Analog Input AC coupled CD RF signal input C

91 CDD Analog Input AC coupled CD RF signal input D

90 OSN Analog RF Offset cancellation capacitor connecting

89 OSP Analog RF Offset cancellation capacitor connecting

85 CEQP Analog RF Offset cancellation capacitor connecting

84 CEQN Analog RF Offset cancellation capacitor connecting

88 RFGC Analog RF AGC loop capacitor connecting for DVD -ROM

Page 18

16

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

87 RFGCU Analog RF AGC loop capacitor connecting for DVD -RAM

86 RFGCI Analog RF AGC loop capacitor connecting for DVD -RAM

101 MA Analog Input DC coupled DVD -RAM main-beam RF signal input A

102 MB Analog Input DC coupled DVD-RAM main-beam RF signal input B

103 MC Analog Input DC coupled DVD-RAM main-beam RF signal input C

104 MD Analog Input DC coupled DVD-RAM main-beam RF signal input D

105 SA Analog Input DC coupled DVD -RAM sub-beam RF signal input A

106 SB Analog Input DC coupled DVD -RAM sub-beam RF signal input B

110 SC Analog Input DC coupled DVD -RAM sub-beam RF signal input C

111 SD Analog Input DC coupled DVD -RAM sub-beam RF signal input D

108 IR Analog External current bias resistor (R=20K)

119 AGC1 Analog Wobble AGC loop1 capacitor

121 AGC2 Analog Wobble AGC loop2 capacitor

122 AGC3 Analog Wobble AGC loop3 capacitor

MT1336

127 RFSUBO Analog output Header push-pull RF output signal

1 WOBSO Digital output Wobble signal output

6 RFOP Analog output RF positive output

7 RFON Analog output RF negative output

TRACKING ERROR

32 DPFN Analog DPD amplifier negative input

33 DPFO Analog DPD amplifier output

61 DPDMUTE Digital input DPD mute control input

116 TNI Analog Input 3 beam satellite PD signal negative input

115 TPI Analog Input 3 beam satellite PD signal positive input

21 TEO Analog Output Tracking error output

FOCUSING ERROR & RF LEVEL & CENTRAL SERVO SIGNAL

112 CDFOP Analog Input CD focusing error positive input

113 CDFON Analog Input CD focusing error negative input

18 FEO Analog Output Focusing error output

19 LVL Analog Output RF level output

20 CSO Analog output Central servo signal output

ALPC

Page 19

17

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1336

124 MDI1

125 LDO1 Analog Ou tput Laser driver output

123 MDI2

126 LDO2 Analog Output Laser driver output

RF RIPPLE

26 CRTP Analog RF top envelop filter capacitor connecting

27 CRTPLP Analog Defect level filter capacitor connecting

25 HRFRP Analog output High frequency RF ripple output or Blank detector’s output

24 LRFRP Analog output Low frequency RF ripple output

POWER

67, 69 AVDD Power Master PLL Filter power

65, 73 AGND GND GND for Master PLL Filter

64 AVDD Power DPD Power

62 AGND GND DPD GND

109 AVDD Power RF path Power

107 AGND GND RF path GND

Analog Input

Analog Input

Laser power monitor input

Laser power monitor input

114 SVDD Power Servo Power

117 SGND GND Servo GND

2,120 WAVDD Power Wobble Power

128,118 WAGND GND Wobble GND

5 AVDDO Power Power for RF output

8 AGNDO GND GND for RF output

14 AVDDT Power Power for Trimming PAD

12 AGNDT GND GND for Trimming PAD

22 VDDP Power Peak Detection Power

31 GNDP GND Peak Detection GND

37,54 VDD Power Serial I/O Power

39,57 GND GND Serial I/O GND

REFERENCE VOLTAGE

16 VREFO Analog output Reference voltage 1.4V

15 V2REFO Analog output Reference voltage 2.8V

17 V20 Analog Output Reference voltage 2.0V

Page 20

18

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

ALPC TRIMMING

9 TM1 Analog input Trimming pin for ALPC1

10 TM2 Analog input Trimming pin for ALPC1

11 TM3 Analog input Trimming pin for ALPC2

13 TM4 Analog input Trimming pin for ALPC2

HIGH SPEED TRACK COUNTING

29 TRLP Analog Low-pass filter capacitor connecting

28 TRLPA Analog Low-pass filter capacitor connecting

30 HTRC Digital output High speed track counting digital output

PCS

74 HALLSIN Analog input Negative input of amplifier for hall sensor signal

75 REFSIN Analog input Positive input of amplifier for hall sensor signal

76 SINPHI Analog output Amplifier output for hall sensor signal

MT1336

71 HALLCOS Analog input Negative input of amplifier for hall sensor signal

72 REFCOS Analog input Positive input of amplifier for hall sensor signal

70 COSPHI Analog output Amplifier output for hall sensor signal

FOR MONITOR ONLY

81

80

66 VCON Analog output

77 SWO Analog output Output from mux of SW1 & SW2

78 SW2 Analog input External input for servo input select

79 SW1 Analog input External input for servo input select

FOR SERIAL I/O

42

43 IO1

44 IO2

45 IO3

46 IO4

MON Analog output

MOP Analog output

IO0

47 IO5

Page 21

19

PRELIMINARY, SUBJ ECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

48 IO6

49 IO7

50 IO8

51 IO9

52 IOA

53 IOB

MT1336

Page 22

8.2 MT1369

20

Specifications are subject to change without notice

F

EATURES

n Super Integration DVD player single chip

§

§

§

§

§

§

§

n Speed Performance on Servo and Decoding

§

§

§

n Channel Data Processor

§

§

§

§

§

n Servo Control and Spindle Motor Control

§

§

§

§

§

§

n Host Micro controller

Servo controller and data channel processing

MPEG-1/MPEG-2/JPEG video decoding

AC-3/DTS/DVD-Audio/MP3 audio decoding

Unified track buffer and A/V decoding buffer

Video processing for scaling and video quality

enhancement

OSD & Sub-picture decoding

Built-in clock generator

DVD-ROM up to 8XS

CD-ROM up to 24XS

Built-in a frequency programmable clock to µP

and RSPC Decoder to optimize the performance

over power

Provides interface with analog front -end

processor

Analog data slicer for small jitter capability

Built-in high performance data PLL for channel

data demodulation

EFM/EFM+ data demodulation

Enhanced channel data frame sync protection &

DVD-ROM sector sync protection

Programmable frequency error gain and phase

error gain of spindle PLL to control spindle motor

on CLV and CAV mode

Provide a varipitch speed control for CLV and CAV

mode

Built-in ADCs and DACs for digital servo control

Provide 2 general PWM

Tray control can be PWM output or digital output

Built-in DSP for digital servo control

DVD Player Combo Chip

§

Built-in 8032 micro controller

§

Built-in internal 373 and 8-bit programmable

lower address port

§

256-bytes on-chip RAM

§

Up to 1M bytes FLASH -programming interface

§

Supports 5/3.3-Volt. FLASH interface

§

Supports power-down mode

§

Supports additional serial port

n DVD-ROM/CD-ROM Decoding Logic

§

Supports CD-ROM Mode 1, CD-ROM XA Mode 2

Form 1, CD-ROM XA Mode 2 Form 2, and CD -DA

formats

§

High-speed ECC logic capable of correcting one

error per each P -codeword or Q-codeword

§

Automatic sector Mode and Form detection

§

Automatic sector Header verification

§

8-bit counter for decode completion check

§

Programmable descrambling and error

correction schemes

§

Automatically repeated error corrections

§

8-bit C2 Pointer counter

§

Decoder Error Notification Interrupt that signals

various decoder errors

§

Provide error correction acceleration

n Buffer Memory Controller

§

Supports 16Mb/32Mb/64M b SDRAM

§

Supports 16-bit/32-bit SDRAM data bus interface

§

Build in a DRAM interface programmable clock to

optimize the DRAM performance

§

Provide the self-refresh mode SDRAM

§

Programmable DRAM access cycle and refresh

cycle timings

§

Block-based sector addressing

§

Programmable buffering counter for buffer status

tracking

§

Maximum DRAM speed is 133MHz

§

Support 5/3.3-Volt. DRAM Interface

MT1369

Page 23

MT1369

21

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

n Video Decode

§

Decodes MPEG1 video and MPEG2 main level,

main profile video (720/480 and 720x576)

§

Maximum input bit -rate of 15Mbits/sec

§

Smooth digest view function with I, P and B

picture decoding

§

Baseline, extended-sequential and progressive

JPEG image decoding

§

RLE and non-RLE BMP image decoding

§

Support CD-G titles

n Video/SPU/HLI Processor

§

Arbitrary ratio vertical/horizontal scaling of video,

from 0.25X to 256X

§

256/16/4/2-color bitmap format OSD,

§

256/16 color RLC format OSD

§

Automatic scrolling of OSD image

§

Warp mode of OSD can reduce memory required

§

Dual Sub-picture decoder

§

Provides 4-color/32x32-pixel hardware cursor

§

Fade-in, Fade out, and Wipe functions as

specified in the DVD-Audio Specification and

other slide show transition effects

- MLP decoding for DVD-Audio

- MPEG-1 layer 1/layer 2 audio decoding

- MPEG-2 layer1/layer2 2 -channel audio decoding

- Dolby Pro Logic decoding

§

Up to 6 channel linear PCM output for DVD Audio

/ DVD Video

§

Downmix function

§

Support IEC 60958/61937 output

- PCM / bit stream / mute mode

- Custom IEC latency up to 2 frames

§

Pink noise and white noise generator

§

Karaoke functions

- Microphone echo with adjustable echo level,

echo -depth and delay length

- Microphone tone control with three custom

second-order IIR filter

- Vocal mute/vocal assistant

- Key shift up to +/- 8 keys controlled by 1/2 key

§

Channel equalizer

§

3D surround processing include virtual surround

and speaker separation

§

Power-down control

n Audio Processing

§

Decoder format supports:

- Dolby Digital (AC-3) decoding

- DTS decoding

n Outline

§

208-pin LQFP package

§

3.3/2.5-Volt. Dual operating voltages

Page 24

MT1369

22

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

P

IN DEFINITIONS

Pin Symbol Type Description

1 IREF Analog Input Current reference input. It generate reference current for data PLL.

Connect an external 100K resistor to this pin and PLLVSS.

2 PLLVSS Ground Ground for data PLL and related analog circuitry

3 LPIOP Analog Output Positive output of the low pass filter

4 LPION Analog Output Negative output of the low pass filter

5 LPFON Analog output Negative output of loop filter amplifier

6 LPFIP Analog Input Positive input of loop filter amplifier

7 LPFIN Analog Input Negative input of loop filter amplifier

8 LPFOP Analog Output Positive output of loop filter amplifier

9 JITFO Analog Output RF jitter meter output

10 JITFN Analog Input Negative input of the operation amplifier for RF jigger meter

11 PLLVDD3 Power Power for data PLL and related analog circuitry

12 FOO Analog Output Focus servo output. PDM output of focus servo compensator

13 TRO Analog Output Tracking servo output. PDM output of tracking servo compensator

14 TROPENPWM Analog Output Tray open output, controlled by microcontroller.

This is PWM output for TRWMEN

TRWMEN

27hRW2

=0

=1 or is digital output for

27hRW2

15 PWMOUT2 Analog Output The general PWM output

16 DVDD2 Power 2.5V power

17 DMO Analog Output Disk motor control output. PWM output

18 FMO Analog Output Feed motor control. PWM output

19 FG Input, Pull Up Motor Hall sensor input

20 DVSS Ground Ground

21 HIGHA0 Inout, Pull Up Microcontroller address 8

22 HIGHA1 Inout, Pull Up Microcontroller address 9

23 HIGHA2 Inout, Pull Up Microcontroller address 10

24 HIGHA3 Inout, Pull Up Microcontroller address 11

25 HIGHA4 Inout, Pull Up Microcontroller address 12

26 HIGHA5 Inout, Pull Up Microcontroller address 13

27 DVSS Ground Ground

28 HIGHA6 Inout, Pull Up Microcontroller address 14

29 HIGHA7 Inout, Pull Up Microcontroller address 15

30 AD7 Inout Microcontroller address/data 7

31 AD6 Inout Microcontroller address/data 6

32 AD5 Inout Microcontroller address/data 5

33 AD4 Inout Microcontroller address/data 4

34 DVDD3 Power 3.3V power

35 AD3 Inout Microcontroller address/data 3

36 AD2 Inout Microcontroller address/data 2

37 AD1 Inout Microcontroller address/data 1

38 AD0 Inout Microcontroller address/data 0

39 IOA0 Inout, Pull Up Microcontroller address 0 / GPIO0

40 IOA1 Inout, Pull Up Microcontroller address 1 / GPIO1

41 DVDD2 Power 2.5V power

Page 25

MT1369

23

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Symbol Type Description

42 IOA2 Inout, Pull Up Microcontroller address 2 / GPIO2

43 IOA3 Inout, Pull Up Microcontroller address 3 / GPIO3

44 IOA4 Inout, Pull Up Microcontroller address 4 / GPIO4

45 IOA5 Inout, Pull Up Microcontroller address 5 / GPIO5

46 IOA6 Inout, Pull Up Microcontroller address 6 / GPIO6

47 IOA7 Inout, Pull Up Microcontroller address 7 / GPIO7

48 A16 Output Flash address 16

49 A17 Output Flash address 17

50 IOA18 Inout Flash address 18 / GPIO10

51 IOA19 Inout Flash address 19 / GPIO11

52 DMVSS Ground Ground for DRAM clock circuitry

53 DMVDD3 Power Power for DRAM clock circuitry

54 ALE Inout, Pull Up Microcontroller address latch enable

55 IOOE# Inout Flash output enable, active low / GPIO1 3

56 IOWR# Inout Flash write enable, active low / GPIO17

57 IOCS# Inout, Pull Up Flash chip select, active low / GPIO18

58 DVSS Ground Ground

59 UP1_2 Inout, Pull Up Microcontroller port 1-2

60 UP1_3 Inout, Pull Up Microcontroller port 1-3

61 UP1_4 Inout, Pull Up Microcontroller port 1-4

62 UP1_5 Inout, Pull Up Microcontroller port 1-5

63 UP1_6 Inout, Pull Up Microcontroller port 1-6

64 DVDD3 Power 3.3V power

65 UP1_7 Inout, Pull Up Microcontroller port 1-7

66 UP3_0 Inout, Pull Up Microcontroller port 3-0

67 UP3_1 Inout, Pull Up Microcontroller port 3-1

68 INT0# Inout, Pull Up Microcontroller interrupt 0, active low

69 IR Input IR control signal input

70 DVDD2 Power 2.5V power

71 UP3_4 Inout Microcontroller port 3-4

72 UP3_5 Inout Microcontroller port 3-5

73 UWR# Inout, Pull Up Microcontroller write strobe, active low

74 URD# Inout, Pull Up Microcontroller read strobe, active low

75 XTALI Input Crystal input, 27MHz

76 XTALO Output Crystal output

77 DVSS Ground Ground

78 RD7 Inout DRAM data 7

79 RD6 Inout DRAM data 6

80 RD5 Inout DRAM data 5

81 RD4 Inout DRAM data 4

82 DVDD2 Power 2.5V power

83 RD3 Inout DRAM data 3

84 RD2 Inout DRAM data 2

85 RD1 Inout DRAM data 1

86 RD0 Inout DRAM data 0

Page 26

MT1369

24

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Symbol Type Description

87 RWE# Output DRAM write enable, active low

88 CAS# Output DRAM column address strobe, active low

89 RAS# Output DRAM row address strobe, active low

90 RCS# Output DRAM chip select, active low

91 BA0 Output DRAM bank address 0

92 DVDD3 Power 3.3V power

93 RD15 Inout, Pull Up/Down DRAM data 15

94 RD14 Inout, Pull Up/Down DRAM data 14

95 RD13 Inout, Pull Up/Down DRAM data 13

96 RD12 Inout, Pull Up/Down DRAM data 12

97 DVSS Ground Ground

98 RD11 Inout, Pull Up/Down DRAM data 11

99 RD10 Inout, Pull Up/Down DRAM data 10

100 RD9 Inout, Pull Up/Down DRAM data 9

101 RD8 Inout, Pull Up/Down DRAM data 8

102 VPVDD3 Power Power for varipitch VCO circuitry

103 VCOCIN Analog Input Connect capacitor for compensator loop filter

104 VPVSS Ground Ground for varipitch VCO circuitry

105 DVSS Ground Ground

106 CLK Output DRAM clock

107 CLE Output DRAM clock enable

108 RA11 Output DRAM address bit 11 or audio serial data 3 (channel 7/8)

109 RA9 Output DRAM address 9

110 RA8 Output DRAM address 8

111 DVDD2 Power 2.5V power

112 RA7 Output DRAM address 7

113 RA6 Output DRAM address 6

114 RA5 Output DRAM address 5

115 RA4 Output DRAM address 4

116 DVSS Ground Ground

117 DQM1 Output Mask for DRAM input/output byte 1

118 DQM0 Output Mask for DRAM input/output byte 0

119 BA1 Output DRAM bank address 0

120 RA10 Output DRAM address10

121 DVDD2 Power 2.5V power

122 RA0 Output DRAM address 0

123 RA1 Output DRAM address 1

124 RA2 Output DRAM address 2

125 RA3 Output DRAM address 3

126 DVSS Ground Ground

127 RD31 Inout, Pull Up/Down DRAM data 31

128 RD30 Inout, Pull Up/Down DRAM data 30

129 RD29 Inout, Pull Up/Down DRAM data 29

130 RD28 Inout, Pull Up/Down DRAM data 28

131 DVDD3 Power 3.3V power

Page 27

MT1369

25

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Symbol Type Description

132 RD27 Inout, Pull Up/Down DRAM data 27

133 RD26 Inout, Pull Up/Down DRAM data 26

134 RD25 Inout, Pull Up/Down DRAM data 25

135 RD24 Inout, Pull Up/Down DRAM data 24

136 DVSS Ground Ground

137 DQM3 Output Mask for DRAM input/output byte 3

138 DQM2 Output Mask for DRAM input/output byte 2

139 RD23 Inout, Pull Up/Down DRAM data 23

140 RD22 Inout, Pull Up/Down DRAM data 22

141 DVDD2 Power 2.5V power

142 RD21 Inout, Pull Up/Down DRAM data 21

143 RD20 Inout, Pull Up/Down DRAM data 20

144 RD19 Inout, Pull Up/Down DRAM data 19

145 RD18 Inout, Pull Up/Down DRAM data 18

146 DVSS Ground Ground

147 RD17 Inout, Pull Up/Down DRAM data 17

148 RD16 Inout, Pull Up/Down DRAM data 16

149 ABCK Output Audio bit clock

150 ALRCK Inout, Pull Down (1) Audio left/right channel clock

(2) Trap value in power-on reset.

1:use external 373, 0:use internal 373

151 DVDD3 Power 3.3V power

152 ASDATA0 Inout, Pull Down Audio serial data 0 (left/right channel)

153 ASDATA1 Inout, Pull Down Audio serial data 1 (surround left/surround right channel)

154 ASDATA2 Inout, Pull Down Audio serial data 2 (center/LFE channel)

155 ACLK Inout Audio DAC master clock (384/256 audio sample frequency)

156 APVDD3 Power Power for audio clock circuitry

157 APVSS Ground Ground f or audio clock circuitry

158 SPDIF Output SPDIF output

159 MC_DAT Input Microphone serial input

160 BLANK# Inout Video blank area, active low / GPIO14

161 VSYN Inout Vertical sync / GPIO16

162 HSYN Inout Horizontal sync / GPIO15

163 DVSS Ground Ground

164 YUV0 Output Video data output bit 0

165 YUV1 Output Video data output bit 1

166 YUV2 Output Video data output bit 2

167 YUV3 Output Video data output bit 3

168 YUV4 Output Video data output bit 4

169 DVDD2 Power 2.5V power

170 YUV5 Output Video data output bit 5

171 YUV6 Output Video data output bit 6

172 YUV7 Output Video data output bit 7

173 ICE Input, Pull Down Microcontroller ICE mode enable

174 PRST Input, Pull Down Power on reset input, active high

175 DVSS Ground Ground

Page 28

MT1369

26

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Symbol Type Description

176 VFO13 Output The 1st, 3rd VFO pulse output of DVD-RAM ID header

177 IDGATE Output DVD -RAM ID header detect signal output

178 DVDD3 Power 3.3V power

179 UDGATE Output DVD -RAM recording data gate signal output

180 WOBSI Input Wobble signal input

181 SDATA Output RF serial data output

182 SDEN Output RF serial data latch enable

183 SLCK Output RF serial clock output

184 BDO Input, Pull Down Flag of defect data status input

185 DVDD3 Power 3.3V power

186 PDMVDD3 Power Power for PDM circuitry

187 PWMVREF Analog Input A reference voltage input for PWM circuitry. A typical value of 2.8 v

188 PWM2VREF Analog Input A reference voltage input for PWM circuitry. A typical value of 1.4 v

189 PDMVSS Ground Ground for PDM circuitry

190 ADCVSS Ground Ground for ADC circuitry

191 ADIN Analog Input General A/D input

192 RFSUBI Analog Input RF subtraction signal input terminal

193 TEZISLV Analog Input Tracking error zero crossing low pass input

194 TEI Analog Input Tracking error input

195 CSO Analog Input Central servo input

196 FEI Analog Input Focus error input

197 RFLEVEL Analog Input Sub beam add input or RFRP low pass input

198 RFRP_DC Analog Input RF ripple detect input

199 RFRP_AC Analog Input RF ripple detect input (through AC coupling)

200 RFRPSLV Analog Input RFRP slice level input

201 HRFZC Analog Input High frequency RF ripple zero crossing

202 ADCVDD3 Power Power for ADC circuitry

203 RFDTSLVP Analog Output Positive RF data slicer level output

204 SCON Analog Output Negative analog slicer current output

205 SCOP Analog Output Positive analog slicer current output

206 RFDTSLVN Analog Output Negative RF data slicer level output

207 RFIN Analog Input Negative input of RF differential signal

208 RFIP Analog Input Positive input of RF differential signal

Page 29

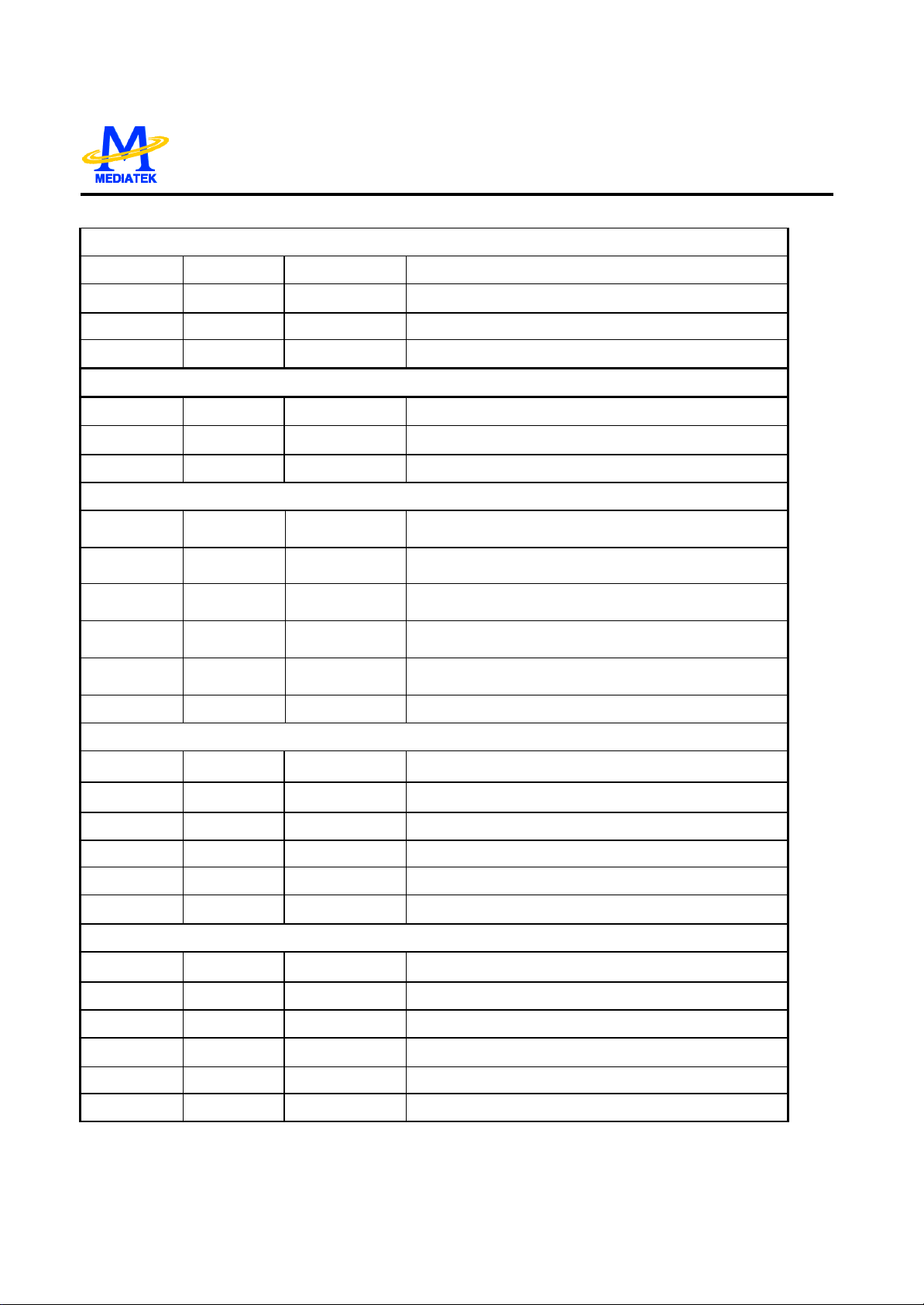

MT1369

27

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

IREF

PLLVSS

LPIOP

LPION

LPFON

LPFIP

LPFIN

LPFOP

JITFO

JITFN

PLLVDD3

FOO

TRO

TROPENPWM

PWMOUT2

DVDD2

DMO

FMO

DVSS

HIGHA0

HIGHA1

HIGHA2

HIGHA3

HIGHA4

HIGHA5

DVSS

HIGHA6

HIGHA7

AD7

AD6

AD5

AD4

DVDD3

AD3

AD2

AD1

AD0

IOA0

IOA1

DVDD2

IOA2

IOA3

IOA4

IOA5

IOA6

IOA7

A16

A17

IOA18

IOA19

IPVSS

RFRP_AC

RFRPSLV

RFRP_DC

FEI

RFLEVEL

HRFZC

RFIP

208

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

FG

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53IPVDD3

207

54

206

55

205

56

RFDTSLVP

SCON

203

204

58

57

202

59

201

60

200

61

ADCVDD3

SCOP

RFIN

RFDTSLVN

199

62

198

63

197

64

196

65

CSO

195

66

ADIN

191

PDMVSS

ADCVSS

189

190

PWMVREF

PDMVDD3

PWM2VREF

186

187

188

TEI

194

RFSUBI

TEZISLV

192

193

DVD Player Combo Chip

75

74

73

72

71

70

69

68

67

SDATA

DVDD3

BDO

SDEN

SLCK

181

182

183

184

185

MT1369

80

79

78

77

76

UDGATE

WOBSI

179

180

82

81

DVDD3

IDGATE

177

178

84

83

VFO13

DVSS

175

176

86

85

PRST

174

87

ICE

173

88

YUV7

172

89

YUV6

171

90

YUV5

170

91

DVDD2

YUV4

168

169

93

92

YUV3

167

94

YUV2

166

95

YUV1

165

96

YUV0

164

97

DVSS

163

98

HSYN

162

99

VSYN

161

100

MC_DAT

BLANK#

159

160

102

101

APVSS

SPDIF

157

158

104

103

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

APVDD3

ACLK

ASDATA2

ASDATA1

ASDATA0

DVDD3

ALRCK

ABCK

RD16

RD17

DVSS

RD18

RD19

RD20

RD21

DVDD2

RD22

RD23

DQM2

DQM3

DVSS

RD24

RD25

RD26

RD27

DVDD3

RD28

RD29

RD30

RD31

DVSS

RA3

RA2

RA1

RA0

DVDD2

RA10

BA1

DQM0

DQM1

DVSS

RA4

RA5

RA6

RA7

DVDD2

RA8

RA9

RA11

CKE

CLK

DVSS

ALE

IOOE#

IOCS#

IOWR#

DVSS

UP1_2

UP1_3

UP1_4

UP1_5

UP1_6

UP1_7

DVDD3

UP3_0

UP3_1

INT0#

IR

UP3_4

DVDD2

UP3_5

URD#

UWR#

XTALI

DVSS

XTALO

RD7

RD6

RD5

RD4

RD3

DVDD2

RD2

RD1

RD0

CAS#

RWE#

RAS#

RCS#

BA0

RD15

DVDD3

RD14

RD13

RD12

DVSS

RD11

RD10

RD9

RD8

VCOCIN

VPVDD3

VPVSS

Page 30

MT1369

28

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

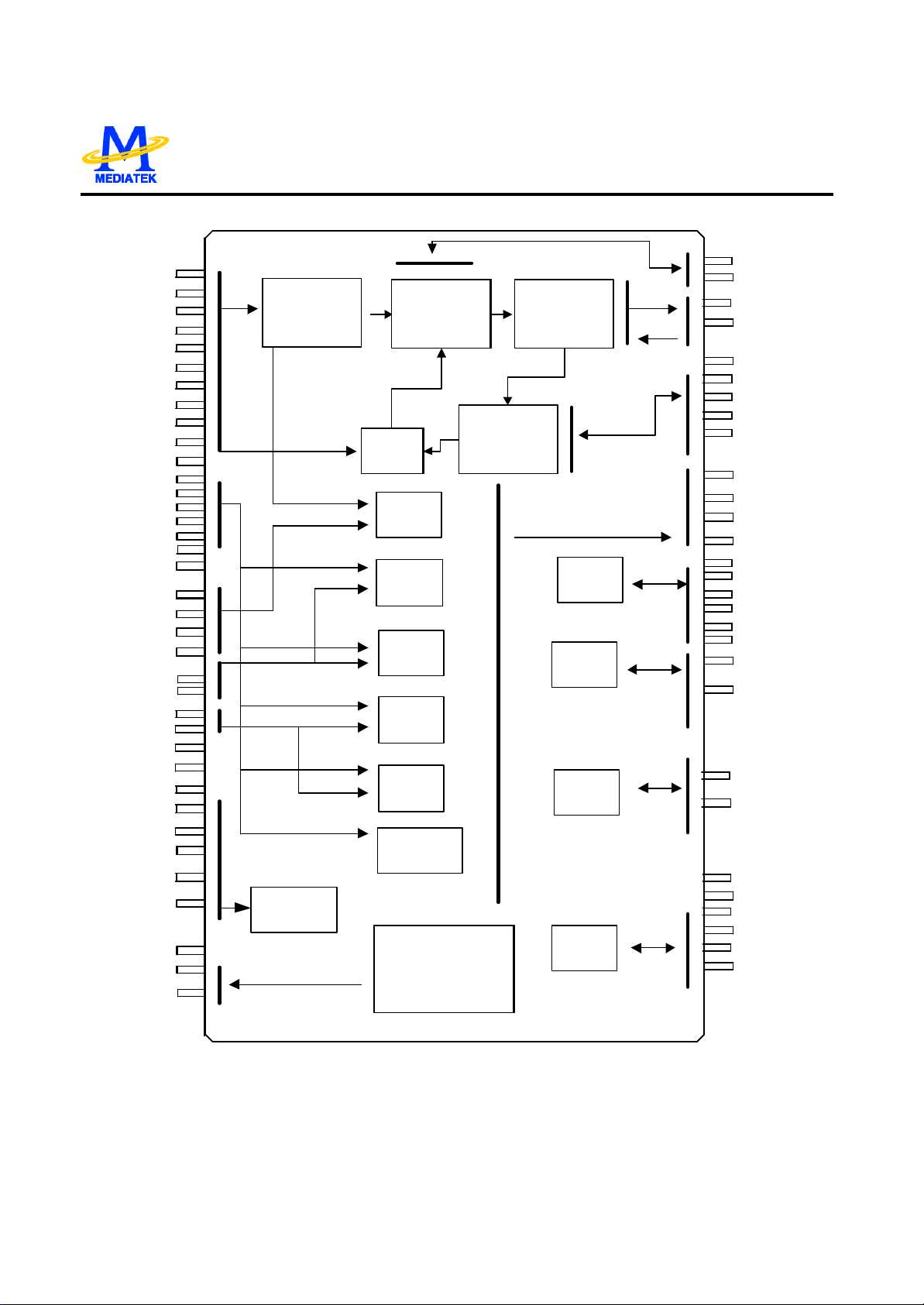

F

UNCTIONAL BLOCK

IR/

VFD

Servo

IO

Servo

DSP

Playback

Controller

System

Controller

DVD module

Analog

Front end

DRAM

Interface

Spindle

Controller

DPU

Processor

Audio

Channel

Decode

Debug

Port

Audio

Output

CSS/

CPPM

System

Parser

Decoder

Microphone

Input

TV encoder

Video

Output

Video

Servo Controller

The servo control is accomplished through the servo DSP (Servo Digital Signal Processor) and its accessory I/O circuits. This servo

DSP is capable of performing complex operations and also provides a friendly interface for the system controller. By issuing type

1 and type 2 commands from the system controller, the servo DSP can accomplish various complicated servo control functions,

such as tracking, seeking and MT1336 chip register programming. As for the servo I/O circuits, it provides interface between the

input servo signals and the Servo DSP. It has built-in ADCs to digitize the servo control signal and DACs to provide signals for the

actuator and sledge motor. It also has a serial interface to communicate with the MT1336 chip.

Analog Front End

The analog front end contains a data slicer circuit and a data PLL circuit. The RF analog signal from MT1336 is quantized by

the data slicer to form the EFM/EFM+ bit stream, from which the channel bit clock is extracted by the data PLL.The

EFM/EFM+bit stream and bit clock are then output to DPU for channel bit processing.

DPU

Data path unit (DPU) provides protection on data with lost synchron ization patterns and demodulates EFM/EFM+ bit stream into

the channel raw data that will be corrected by the decoder. The synchronization protection makes data after the synchronization

pattern to be extracted even if the synchronization pattern is not found.

Spindle Controller

DRAM Flash

Audio DAC

SPDIF

MIC

Page 31

MT1369

29

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

The spindle controller is used to control disc spindle motor. It includes a varipitch CLV clock generator, a CLV/CAV controller,

and a PWM generator. The varipitch CLV clock enerator generates a reference colck for the speed of operation. The CLV/CAV

controller changes the mode and speed of operation according to servo register setting. The PWM generator generates

pulse-width-modulated signal to drive disc spindle motor driver.

CSS/CPPM

The CSS/CPPM module provides functions necessary for decoding discs conforming to CSS/CPPM specification.

System Parser

The system parser is used to help the system controller to decode DVD/SVCD/VCD bitstream just after the channel decoder

performing error correction. Acting as a DMA master, it moves bitstream data from RSPC buffer to video, audio, or sub -picture

buffer according to system controller request. It also decrypts the scramble data of the CSS/CPPM sectors. Another function of

system parser is providing system controller/DSP a DRAM memory copy controller to enhance system controller/DSP performance.

Video Decoder

The primary function of MT1369 is to support MPEG1 and MPEG2 video decoding. The video decode engine comprises of

variable length decoder (VLD), inverse transformer (IT), motion compensator (MC), and block reconstructor (BR). The video

decode engine decodes the variable length encoded symbols in MPEG bitstream and performs inverse scan, inverse

quantization, mismatch control and inverse discrete cosine transform onto the variable length decoded data. The motion

compensator fetches prediction data from reference picture buffer according to motion vectors and motion prediciton mode for P

and B pictures. Finally, the block reconstructor combines both the results of inverse transformer and motion compensator to derive

the reconstructed image macroblock and write back to picture buffer.

The video decode engine can also support JPEG and BMP file decoding by common image compression hardware kernels.

Video Output

The Video Output unit contains Video Processor, SPU, OSD, Cursor, TV encoder units, it performs

§ Reading decoded video from DRAM buffer

§ Scaling the image

§ Gamma/Brightness/Hue/Saturation adjustment and edge enhancement

§ Reading and decoding SPU and OSD data from DRAM buffer

§ Generating hardware cursor image

§ Merging the video data, SPU, OSD and cursor

Video Processor

The Video Processor unit controls the transfer of video data stored in the DRAM to an internal or external TV encoder. It uses

FIFOs to buffer outgoing luminance and chrominance data, and performs YUV420 to YUV422 conversion and arbitrary

vertical/horizontal decimation/interpolation, from 1/4x to 256x. With this arbitrary ratio scaling capability, the Video Processor

can perform arbitrary image conversion, such as PAL to NTSC, NTSC to PAL, MPEG1 to MPEG2, Letterbox, Pan-Scan

conversion or zoom in, zoom out. It is also capible of interlace to progressive conversion.

The Video Processor unit performs the following functions:

§ Requests and receives the decoded picture data from the picture buffer in external DRAM for display

§

Resample vertical data to create 4:2:2 sample format

§ Optionally performs vertical/horizontal resampling of both luminance and chrominance data

§ Performs optional Gamma correction, luminance/chrominance adjustment, and edge enhancement

The Video Processor unit contains two 2 -tap vertical filters for luminance and chrominance . These filters are used to

interpolate and reposition luminance and chrominance line to improve picture quality. These filters are capble of generating

up to eight, unique subline value between two consecutive scan lines. The generation of lines depends on the ratio between

the height of the source image and the target image. In applications where DRAM bandwidth are critical the filters can be

configured as simple line-repeating to reduce the DRAM bandwidth required.

Page 32

MT1369

30

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

The Video Processor unit integrates two separate horizontal postprocessing filter, a simple 2-tap linear horizontal filter and

an 8-tap programmable filter. These filters are provided for scaling images horizontally along the scan line. These two filters

is capable of generating up to eight, unique subpixel values between two consecutive pixels on a scan line. The generation

of pixels depends on the ratio between the width of the source image and the target image.

SPU

This is a hardware sub-picture decoder. It decodes the compressed SPU image bitstream and CHG_COLCON commands

according to SPU header information previously decoded by system controller. The SPU module also allows two SPU

objects to be displayed at the same time. SPU image is blended with main video stream.

OSD

The OSD module can operate with 2/4/16/256-color bitmap format (1/2/4/8 bits), and 16/256 color RLC format, all have 16

levels of transparency. In addition, it accepts an special WARP mode, which inserts one programmable RLC code in the

bitmap to reduce the image size stored in DRAM. It also features automatic shadow/outline generation in 2-color mode, 2

Hilight areas, 1 ChangeColor area and 1 OSDVoid area. One OSD area can occupy the full or a partial screen, or multiple

OSDs can occur in a screen at the same time, only if they don't occupy the same horizontal line. The output image is

blended with the video-SPU mixed stream.

Cursor

A hardware cursor genera tor is integrated in Video Output Unit. The cursor image is a 32x32 4-color bitmap image, each

colors are programmable. Cursor can be enlarged by 2 in both vertical and horizontal directions. Cursor image is multiplexed

with video-SPU-OSD mixed stream.

Audio Interface

Audio interface consists of Audio Output Interface and Microphone Input Interface.

Audio Output Interface

The MT1369 can support up to 8 channel audio outputs. The output formats can be 16, 24, or 32-bit frames. Left alignment,

right alignment, or I2S formats are all supported.

With built-in PLL, MT1369 can provide the audio clock (ACLK) for external audio DAC at 384Fs, where Fs is usually 32KHz,

44.1KHz, 48KHz, 96KHz, or 192KHz. ACLK can also be programmed to be from outside MT1369. When ACLK is input to

MT1369, the frequency could be 128*n Fs, where n is from 1 to 7.

Audio raw (encoded) data or cooked (decoded) data can be output on a single line using S/PDIF interface. The output slew

rate and driving force of this pad are programmable.

Microphone Input Interface

The MT1369 provides a microphone input interface. Two independent microphones’ data could be input to the MT1369.

There are two independent digital volume control for these two input channels. The input data formats can also be left

alignment, right alignment, or I2S formats.

System Controller

MT1369 uses an embedded Turbo-8032 as System Controller and provide ICE interface to increase the feasibility of F/W

development. Also, MT1369 includes an build-in internal 373 to latch l ower byte address from 8032 Port 0 and provide a

glue-logic free solution. MT1369 supports up to 1M X 8 bits Flash ROM to store 8032 code, H/W related data, User data, etc. F/W

upgrade can be achieved either by debug interface or by disk.

Page 33

KEY FEATURES

IC BLOCK DIAGRAM & DESCRIPTION

31

8.3 U214 HY29F800

n 5 Volt Read, Program, and Erase

– Minimizes system-level power requirements

n High Performance

– Access times as fast as 55 ns

n Low Power Consumption

– 20 mA typical active read current in byte

mode, 28 mA typical in word mode

– 35 mA typical program/erase current

– 5 µA maximum CMOS standby current

n Compatible with JEDEC Standards

– Package, pinout and command-set

compatible with the single-supply Flash

device standard

– Provides superior inadvertent write

protection

n Sector Erase Architecture

– Boot sector architecture with top and

bottom boot block options available

– One 16 Kbyte, two 8 Kbyte, one 32 Kbyte

and fifteen 64 Kbyte sectors in byte mode

– One 8 Kword, two 4 Kword, one 16 Kword

and fifteen 32 Kword sectors in word mode

– A command can erase any combination of

sectors

– Supports full chip erase

n Erase Suspend/Resume

– Temporarily suspends a sector erase

operation to allow data to be read from, or

programmed into, any sector not being

erased

n Sector Protection

– Any combination of sectors may be

locked to prevent program or erase

operations within those sectors

n Temporary Sector Unprotect

– Allows changes in locked sectors

(requires high voltage on RESET# pin)

n Internal Erase Algorithm

– Automatically erases a sector, any

combination of sectors, or the entire chip

n Internal Programming Algorithm

– Automatically programs and verifies data

at a specified address

n Fast Program and Erase Times

– Byte programming time: 7 µs typical

– Sector erase time: 1.0 sec typical

– Chip erase time: 19 sec typical

n Data# Polling and Toggle Status Bits

– Provide software confirmation of

completion of program or erase

operations

n Ready/Busy# Output (RY/BY#)

– Provides hardware confirmation of

completion of program and erase

operations

n Minimum 100,000 Program/Erase Cycles

n Space Efficient Packaging

– Available in industry-standard 44-pin

PSOP and 48-pin TSOP and reverse

TSOP packages

19

A[18:0]

CE#

OE#

WE#

RESET#

BYTE#

8

DQ[7:0]

7

DQ[14:8]

DQ[15]/A-1

RY/BY#

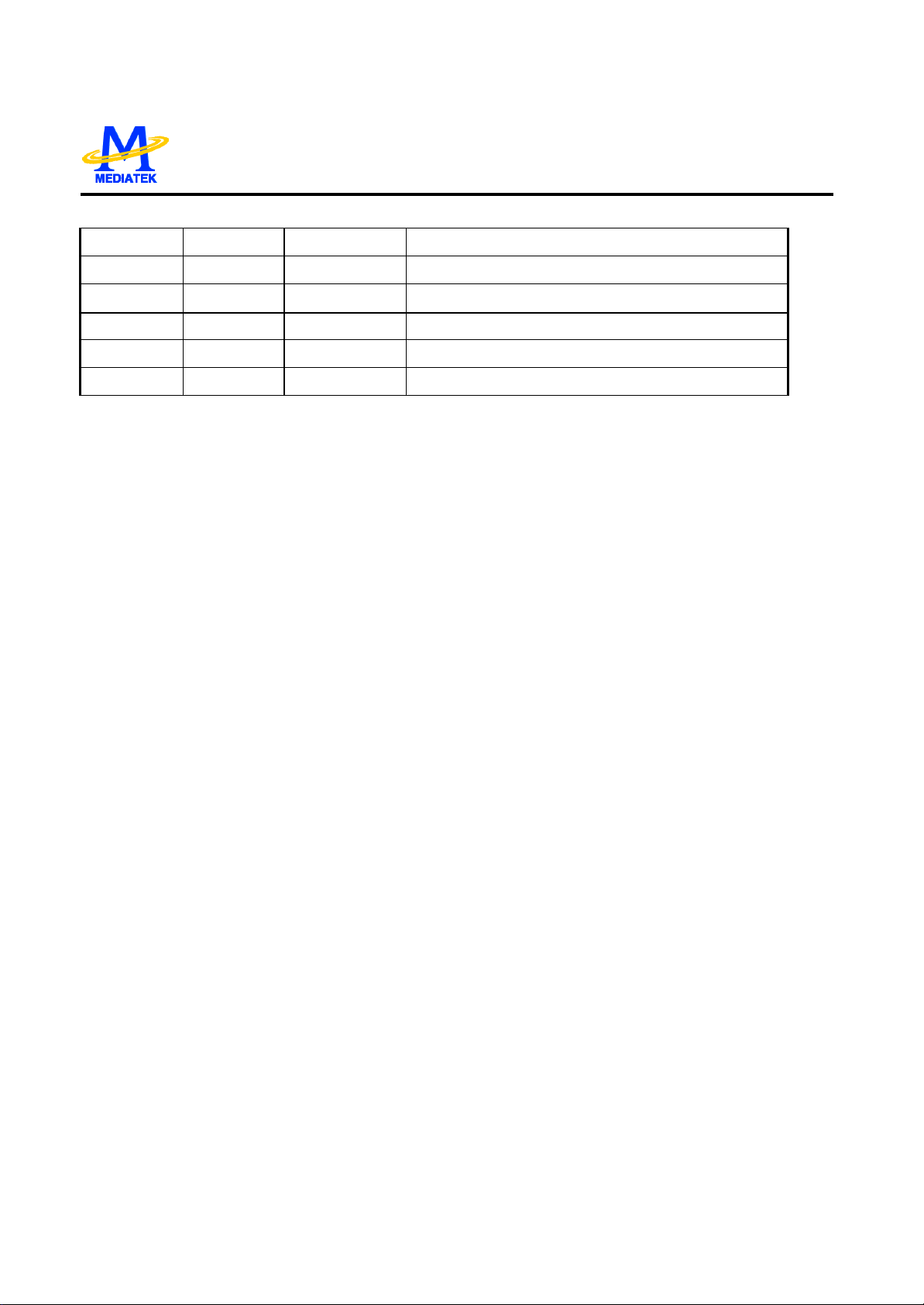

Page 34

BLOCK DIAGRAM

IC BLOCK DIAGRAM & DESCRIPTION

32

DQ[15:0]

A[18:0], A-1

DQ[15:0]

WE#

CE#

OE#

BYTE#

RESET#

RY/BY#

STATE

CONTROL

COMMAND

REGISTER

PROGRAM

VOLTAGE

GENERATOR

VCC DETECTOR TIMER

ERASE VOLTAGE

GENERATOR AND

SECTOR SWITCHES

A[18:0], A-1

I/O CONTROL

Y-DECODER

X-DECODER

ADDRESS LATCH

I/O BUFFERS

DATA LATCH

Y-GATING

8 Mb FLASH

MEMORY

ARRAY

Page 35

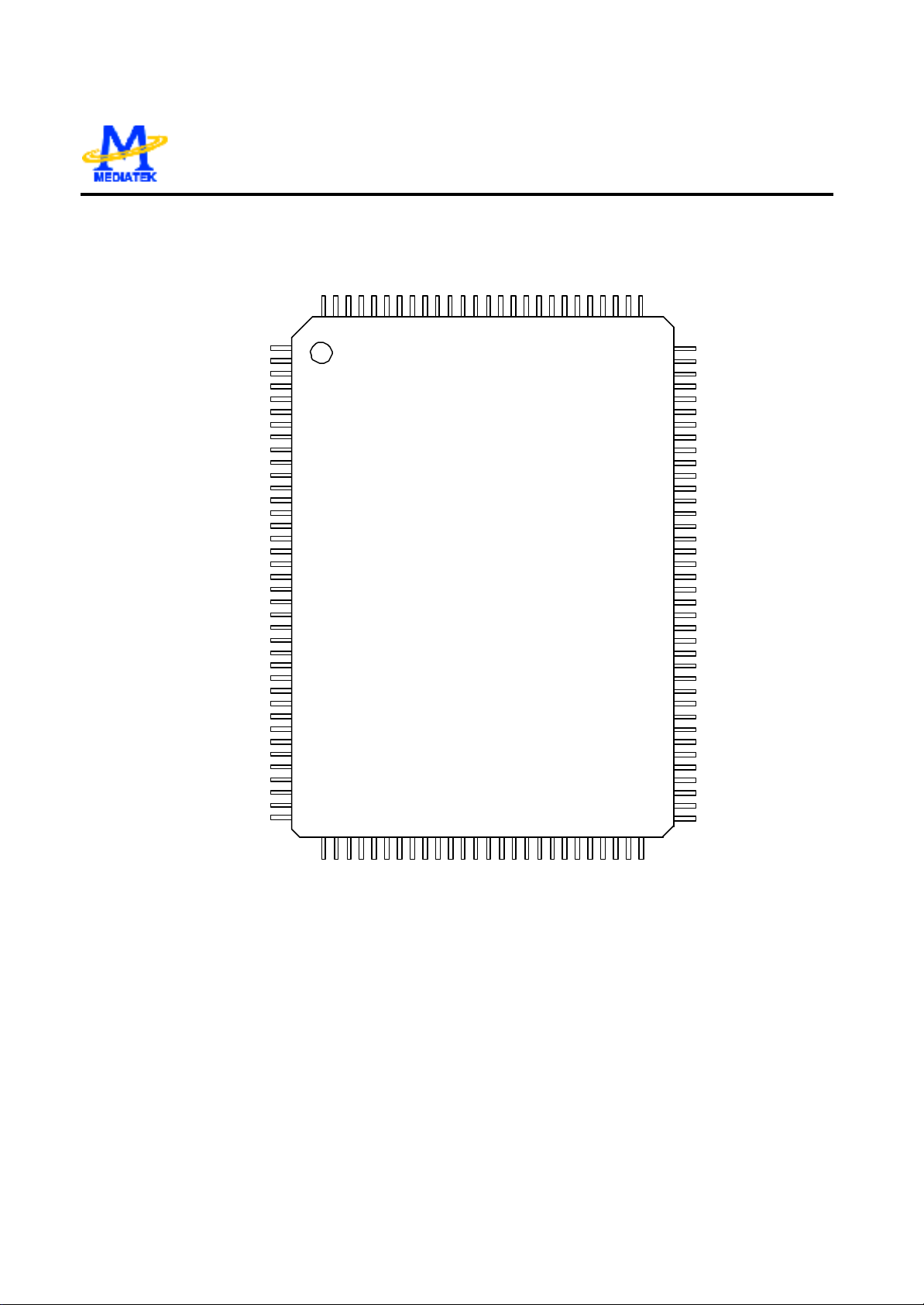

PIN CONFIGURATIONS

IC BLOCK DIAGRAM & DESCRIPTION

33

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1910

A0

CE#1112

V

SS

OE#1314

DQ0

DQ81516

DQ1

DQ91718

DQ2

DQ101920

DQ3

DQ112122

1

2

3

4

5

6

7

8

PSOP44

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

RESET#

WE#

A8

A9

A10

A11

A12

A13

A14

A15

A16

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

A15

A14

A13

A12

A11

A10

A9

A8

NC

NC910

WE#

RESET#1112

NC

NC1314

RY/BY#

A181516

A17

A71718

A6

A51920

A4

A32122

A2

A12324

A16

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

A16

1

2

3

4

5

6

7

8

Standard

TSOP48

1

2

3

4

5

6

7

8

9

Reverse

TSOP48

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

A15

A14

A13

A12

A11

A10

A9

A8

NC

NC

WE#

RESET#

NC

NC

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

Page 36

DESCRIPTION

IC BLOCK DIAGRAM & DESCRIPTION

8.4 U203 SDRAM-HY57V1610D

2 Banks x 512k x 16 Bit Synchronous DRAM

34

THE Hynix HY57V161610D is a 16,777,216-bits CMOS Synchronous DRAM, ideally suited for the Mobile applications

which require low power consumption and industrial temperature range. HY57V161610D is organized as 2banks of

524,288x16.

HY57V161610D is offering fully synchronous operation referenced to a positive edge clock. All inputs and outputs are

synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

Programmable options include the length of pipeline (Read latency of 1,2 or 3), the number of consecutive read or

write cycles initiated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count

sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate

command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipeline

design is not restricted by a `2N` rule.)

FEATURES

• Single 3.0V to 3.6V power supply

• All device pins are compatible with LVTTL interface

• JEDEC standard 400mil 50pin TSOP-II with 0.8mm

of pin pitch

• All inputs and outputs referenced to positive edge of

system clock

• Data mask function by UDQM/LDQM

• Internal two banks operation

Note1)

ORDERING INFORMATION

Part No. Clock Frequency Organization Interface Package

HY57V161610DTC-55I 183MHz

HY57V161610DTC-6I 166MHz

HY57V161610DTC-7I 143MHz

HY57V161610DTC-10I 100MHz

• Auto refresh and self refresh

• 4096 refresh cycles / 64ms

• Programmable Burst Length and Burst Type

- 1, 2, 4, 8 and Full Page for Sequence Burst

- 1, 2, 4 and 8 for Interleave Burst

• Programmable CAS Latency ; 1, 2, 3 Clocks

2Banks x 512Kbits x 16 LVTTL

400mil

50pin TSOP II

This document is a general product description and is subject to chage without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. No patent licenses are implied

Rev. 0.2/Aug.01

Page 37

AudioMAX™ LX1721 / 1722

p

8.5 LX1722

35

LINFINITY DIVISION

DESCRIPTION

DESCRIPTION

The LX1721/1722 is a monolithic high

performance Class-D stereo controller IC

designed for high efficiency or space

constrained audio requirements such as

portable or battery operated products,

automotive amplifiers, and multi-channel

multimedia computer and video game

applications. This high frequency, full

audio bandwidth switching power

amplifier controller offers dramatically

improved performance over Linfinity’s

revious generation amplifier products.

Enhancements include higher output

power, better SNR, lower noise floor, and

reduced THD. Combined with output

power MOSFET’s and an output filter, the

LX1721/1722 is a complete Class-D audio

solution.

IMPORTANT: For the most current data, consult MICROSEMI’s website: http://www.microsemi.com

Channel

Channel 2

Channel 3

7V - 25V

1

IN +

IN -

LX1722

Stereo

IN +

IN -

CLOCK

LX1711

Mono

IN +

IN -

FETs

FETs

FETs

DESCRIPTIONDESCRIPTION

A complete audio amplifier module is

available to quickly evaluate the LX1721

or LX1722 stereo controller. Simply

connect the amplifier to the power source,

audio signal, and speakers. Reference

designs support a variety of requirements

including multi channel systems,

subwoofers, satellite / subwoofer combinations and various speaker loads (2Ω,

4Ω, 8Ω). The versatile amplifier solution

can easily be adjusted for frequency

response, optimized for efficiency and

performance, or designed to minimize

PCB area and component count. The

LX1721/1722 is available in a space

saving 44-pin QSOP package.

(Continued Next Page)

PRODUCT HIGHLIGHT

PRODUCT HIGHLIGHT

PRODUCT HIGHLIGHTPRODUCT HIGHLIGHT

Output Power vs. Supply Voltage

Left

Right

2Ω, 4Ω, 8Ω

Subwoofer

1kHz, 4Ω, THD+N=1%

Class-D Stereo Power Amplifier Controller

2.1 Audio Amplifier

Configuration

KEY FEATURES

KEY FEATURES

KEY FEATURES KEY FEATURES

! Integrated Switching Class-D

Stereo Controller IC

! Full 20Hz-20kHz Audio

Bandwidth

! High Fidelity (LX1721) Or

High Power (LX1722)

Versions Available

! Single Supply Operation

! THD+N <0.06% Typical

(1Wrms, 1kHz, 4Ω)

! Maximum Efficiency 80%-

85%

! Output Power >60Wrms per

Channel (LX1722, 4Ω, 1%

THD+N)

! PSRR –70dB Typical

! Differential Input To Minimize

Noise Effects

! Supports Multi-Channel

Systems

! Complete LXE1721or

LXE1722 Amplifier Evaluation

Module Available

! 44-Pin QSOP Package

APPLICATIONS

APPLICATIONS

APPLICATIONS APPLICATIONS

! Multimedia Speakers

! Surround Sound Game

Systems

! Notebook Computers

! Desktop Computers

! Automotive Amplifiers And

Head units

! Battery Operated Equipment

(Megaphone, Public Address

System)

! Portable Audio (Boom Box)

! Wireless Speakers

! High Power Subwoofer

! Automotive Audio Systems

! Home Theatre

Page 38

AudioMAX™ LX1721 / 1722

36

LINFINITY DIVISION

THERMAL DATA

THERMAL DATA

DB

44-PIN QSSOP PACKAGE

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θ

Junction Temperature Calculation: TJ = TA + (P

numbers are guidelines for the thermal performance of the device/pc-board

The θ

JA

system. All of the above assume no ambient airflow.

THERMAL DATATHERMAL DATA

x θ

D

DESCRIPTION

DESCRIPTION (CONTINUTED)

The stereo output controller is available in either an

LX1722 high power version (>65Wrms, 4Ω) with a supply

voltage range of 7V-25V or an LX1721 high fidelity

version (better SNR performance) with a supply voltage

range of 7V-15V. The current rating of the external

MOSFET’s, the available supply voltage, and speaker load

primarily limits the maximum output power. The amplifier

provides high fidelity performance and is designed to

operate over the full 20Hz to 20kHz audio band. Signal

distortion measurements yield

DESCRIPTION DESCRIPTION

Class-D Stereo Power Amplifier Controller

θJA 50°°°°C/W

θθ

).

JA

THD+N levels of 0.06%(1kHz, 1Wrms). Efficiency is

greater than 80% typical, which eliminates the need for

heatsinks in most applications. The AudioMAX™ solution

requires a single supply voltage, simplifying input power

requirements where a dual supply may not be available. To

minimize potential environmental noise issues and ease the

integration of the amplifier into a variety of applications,

features such as a balanced/differential audio input and a high

power supply rejection ratio help reduce the effects of noise

from the audio signal or power supply.

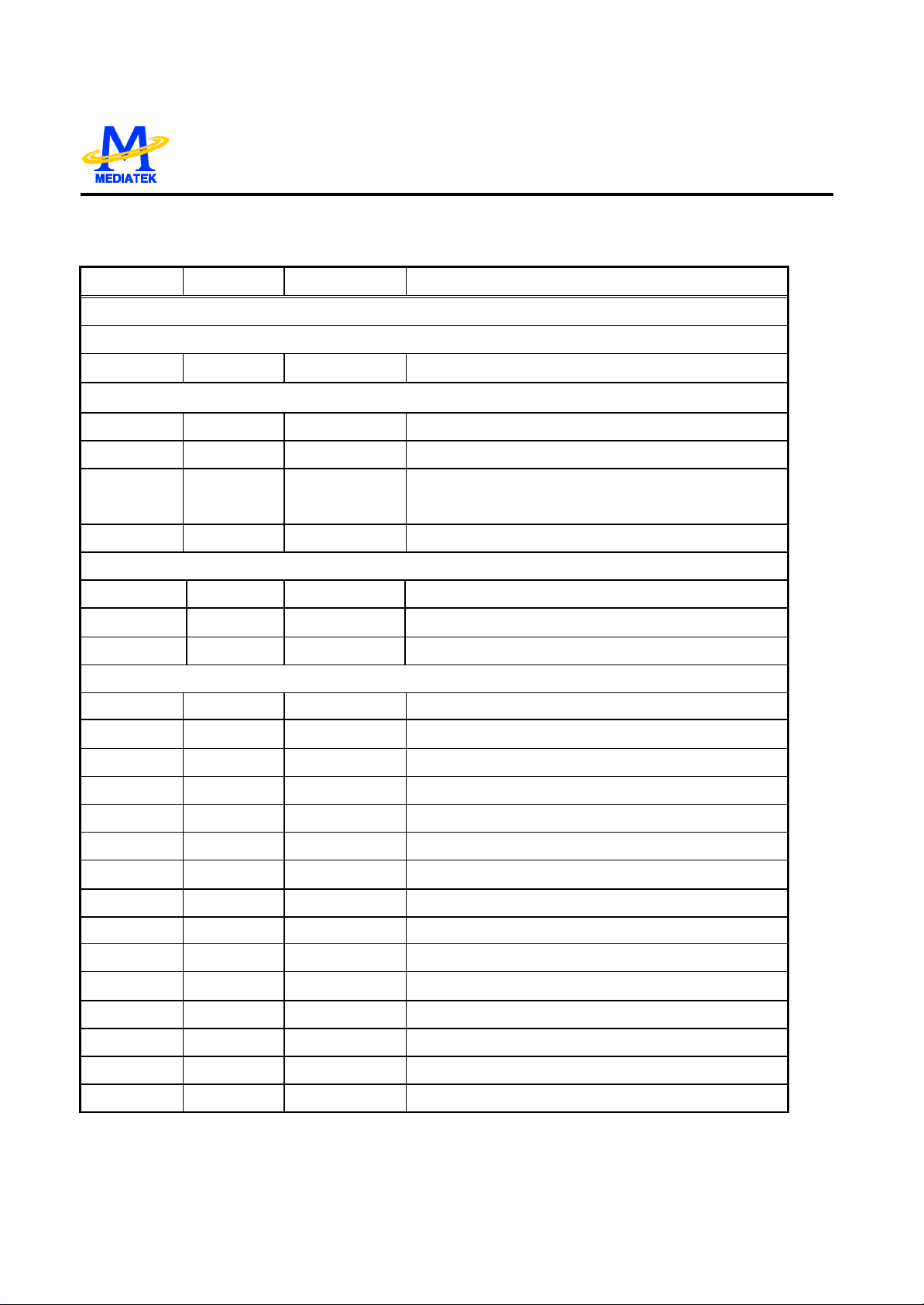

PACKAGE PIN OUT

PACKAGE PIN OUT

PACKAGE PIN OUT PACKAGE PIN OUT

LFAOUT

CPWM

RPWM

LMUTE

LEAOUT

LEAIN

VREF

CLOCK

GND

LIN+

LAMPOUT

RIN+

RIN-

RAMPOUT

SLEEP

STATUS

RMUTE

REAIN

REAOUT

RFAOUT

1

V25

LIN-

22

DB PACKAGE

(Top View)

LFBK-

44

LFBK+

LISN

VDD

CN

PVDD

PGND

LN+

LP+

LP-

LN-

RN-

RP-

RP+

RN+

PGND

CP

PVDD

NC

RISN

RFBK+

RFBK-

23

Page 39

AudioMAX™ LX1721 / 1722

37

LINFINITY DIVISION

FUNCTIONAL PIN

FUNCTIONAL PIN DESCRIPTION

PIN NAME DESCRIPTION PIN NAME DESCRIPTION

LFAOUT

CPWM

RPWM

LMUTE

LEAOUT

LEAIN

VREF

CLOCK

GND

V25

LIN+

LIN-

LAMPOUT

RIN+

RIN-

RAMPOUT

SLEEP

STATUS

RMUTE

REAIN

REAOUT

RFAOUT

Left Feedback Amplifier Output

PWM Capacitor Connection

PWM Resistor Connection

Left Mute Input (Active High)

Left Error Amplifier Output

Left Inverting Input of Error Amplifier

5V Reference

Input / Output Clock for Synch Operation

Low Current Ground

2.5V Reference

Left Positive Audio Input

Left Negative Audio Input

Left Input Amplifier Output

Right Positive Audio Input

Right Negative Audio Input

Right Input Amplifier Output

Sleep Input (active low)

UVLO Indicator (Open Collector Output)

Right Mute Input (Active High)

Right Inverting Input of Error Amplifier

Right Error Amplifier Output

Right Feedback Amplifier Output

FUNCTIONAL PIN FUNCTIONAL PIN

Class-D Stereo Power Amplifier Controller

DESCRIPTION

DESCRIPTIONDESCRIPTION

LFBKLFBK+

LISN

VDD

CN

PVDD

PGND

LN+

LP+

LP-

LN-

RN-

RP-

RP+

RN+

PGND

CP

PVDD

NC

RISN

RFBK+

RFBK-

Left Feedback Amplifier Inverting Input

Left Feedback Amplifier Non-Inverting

Input

Left Current Limit Sense Input

Analog Supply Voltage

Supply Decoupling for NFET Drivers

Output Driver Supply Voltage

Output Driver High Current Ground

Left Drive for NFET on Positive Half of

Bridge

Left Drive for PFET on Positive Half of

Bridge

Left Drive for PFET on Negative Half of

Bridge

Left Drive for NFET on Negative Half of

Bridge

Right Drive for NFET on Negative Half of

Bridge

Right Drive for PFET on Negative Half of

Bridge

Right Drive for PFET on Positive Half of

Bridge

Right Drive for NFET on Positive Half of

Bridge

Output Driver High Current Ground

Supply Decoupling for PFET Drivers

Output Driver Supply Voltage

No Connect

Right Current Limit Sense Input

Left Feedback Amplifier Non-Inverting

Input

Right Feedback Amplifier Inverting Input

ABSOLUTE MAXIMUM RAT

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (PVDD, VDD).............................................................................................................................. -0.3V to 30V

SLEEP

, STATUS, R/LFBK+, R/LFBK-................................................................................................. -0.3V to VDD +0.3V

ABSOLUTE MAXIMUM RATABSOLUTE MAXIMUM RAT

R/LISN......................................................................................................................................... PVDD –2 to PVDD to +0.3V

RPWM, CPWM, R/LMUTE....................................................................................................................-0.3V to VREF +0.3V

R/LIN+, R/LIN-, R/LAMPOUT ..............................................................................................................-0.3V to VREF +0.3V

R/LEAIN, R/LEAOUT, R/LFAOUT......................................................................................................-0.3V to VREF + 0.3V

CLOCK........................................................................................................................................................ -0.3V to CN +0.3V