Page 1

INSTRUCTION MANUA L

FOR

BE1-11

Protection Systems

Modbus™ Communication Protocol

Publication: 9424200774

Revision: B Aug-14

Page 2

Page 3

9424200774 Rev B i

Caution

Note

Preface

This instruction manual provides information about the BE1-11 Protection Systems with the Modbus™

protocol. To accomplish this, the following information is provided:

• General information

• Register table

Conventions Used in this Ma nua l

Important safety and procedural information is emphasized and presented in this manual through

warning, caution, and note boxes. Each type is illustrated and defined as follows.

Warning!

Warning boxes call attention to conditions or actions that may cause

personal injury or death.

Caution boxes call attention to operating conditions that may lead to

equipment or property damage.

Note boxes emphasize important information pertaining to installation

or operation.

BE1-11g Preface

Page 4

ii 9424200774 Rev B

Basler Electric does not assume any responsibility to compliance or noncompliance with national code, local code,

For terms of service relating to this product and software, see the Commercial Terms of Products and Services

document available at www.basler.com/terms.

This publication contains confidential information of Basler Electric Company, an Illinois corporation. It is loaned for

and options are subject to modification without notice. Over time, improvements and revisions may be made to this

manual.

The English-language version of this manual serves as the only approved manual version.

12570 State Route 143

Highland IL 62249-1074 USA

www.basler.com

info@basler.com

Tel: +1 618.654.2341

Fax: +1 618.654.2351

© 2014 by Basler Electric

All rights reserved

First printing: April 2014

Warning!

READ THIS MANUAL. Read this manual before installing, operating, or maintaining the BE1-11. Note

all warnings, cautions, and notes in this manual as well as on the product. Keep this manual with the

product for reference. Only qualified personnel should install, operate, or service this system. Failure to

follow warning and cautionary labels may result in personal injury or property damage. Exercise

caution at all times.

or any other applicable code. This manual serves as reference material that must be well understood prior to

installation, operation, or maintenance.

confidential use, subject to return on request, and with the mutual understanding that it will not be used in any

manner detrimental to the interests of Basler Electric Company and used strictly for the purpose intended.

It is not the intention of this manual to cover all details and variations in equipment, nor does this manual prov ide

data for every possible contingency regarding installation or operation. The availability and design of all features

publication. Before performing any of the following procedures, contact Basler Electric for the latest revision of this

Preface BE1-11

Page 5

9424200774 Rev B iii

Contents

General Information .................................................................................................................................... 1

Message Structure .................................................................................................................................... 1

Device Address Field ............................................................................................................................. 1

Function Code Field ............................................................................................................................... 1

Data Block Field ..................................................................................................................................... 2

Error Check Field ................................................................................................................................... 2

Modbus™ Modes of Operation .................................................................................................................. 2

Modbus™ Over Serial Line ........................................................................................................................ 2

Message Structure ................................................................................................................................. 2

Message Framing and Timing Considerations ...................................................................................... 3

Modbus™ on TCP/IP .................................................................................................................................. 3

Application Data Unit ............................................................................................................................. 3

MBAP Header Description ..................................................................................................................... 4

Error Handling and Exception Responses ................................................................................................ 4

BE1-11 Modbus™ via Ether net .................................................................................................................. 5

Communications Hardware Requirements................................................................................................ 5

Modbus™ Over RS-485 Communication Requirements ........................................................................ 5

Modbus™ Over Ethernet TCP/IP Communication Requirements .......................................................... 5

Detailed Message Query and Response for RTU Transmission Mode .................................................... 5

Read Holding Registers ......................................................................................................................... 5

Return Query Data ................................................................................................................................. 6

Restart Communications Option ............................................................................................................ 6

Listen Only Mode ................................................................................................................................... 6

Preset Multiple Registers ....................................................................................................................... 7

Preset Single Register ........................................................................................................................... 8

Data Formats ............................................................................................................................................. 8

Floating Point Data Format (Float) ........................................................................................................ 9

Long Integer Data Format (Uint32, Int32, and IP Address) ................................................................... 9

Integer Data Format (Uint16 and Int16) or Bit-Mapped Variables in Uint16 Format ............................. 9

Short Integer Data Format/Byte Character Data Format (Uint8 and Int8) ........................................... 10

String Data Format (String) .................................................................................................................. 10

CRC Error Check ................................................................................................................................. 11

Reading Fault Record Data ................................................................................................................. 11

Contiguous Poll Block Registers .......................................................................................................... 11

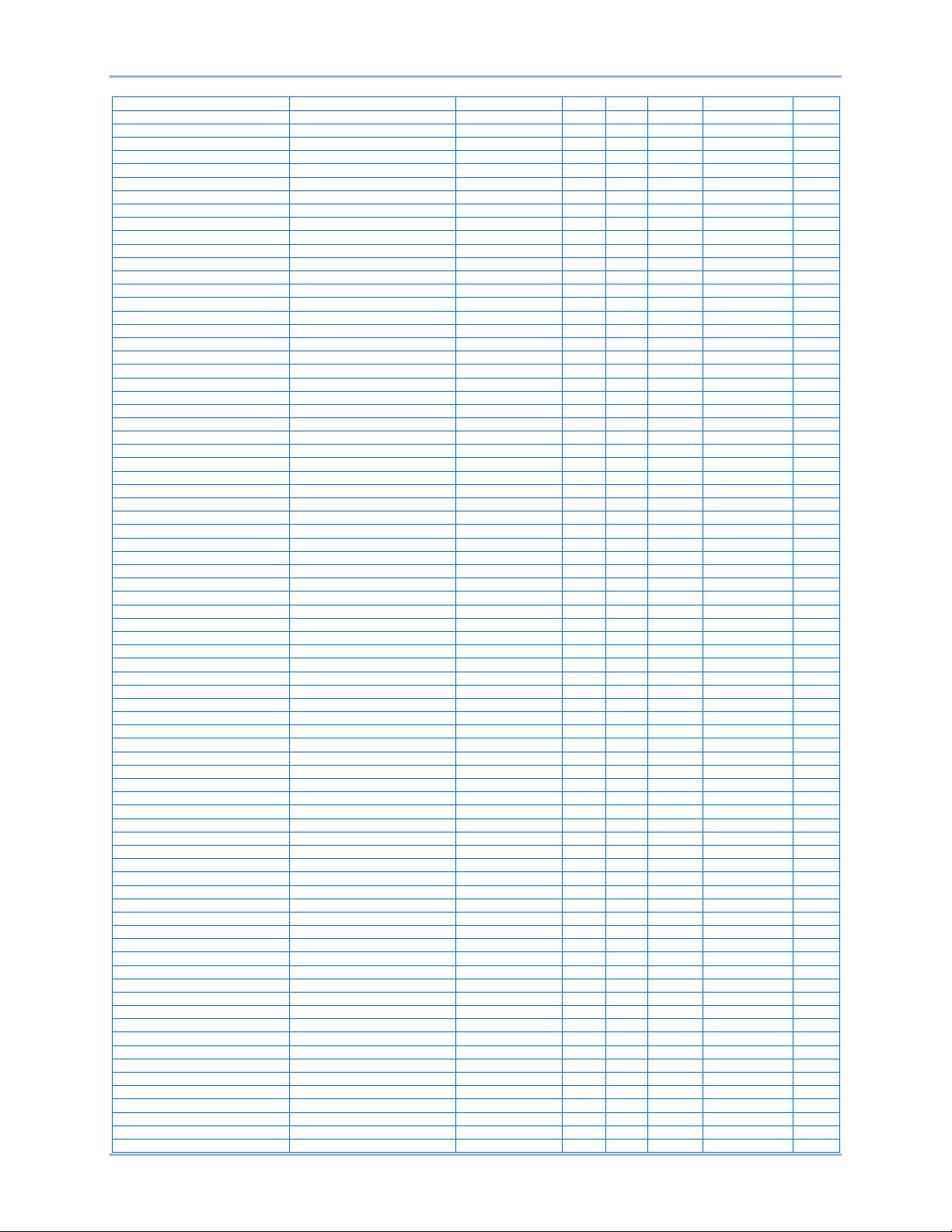

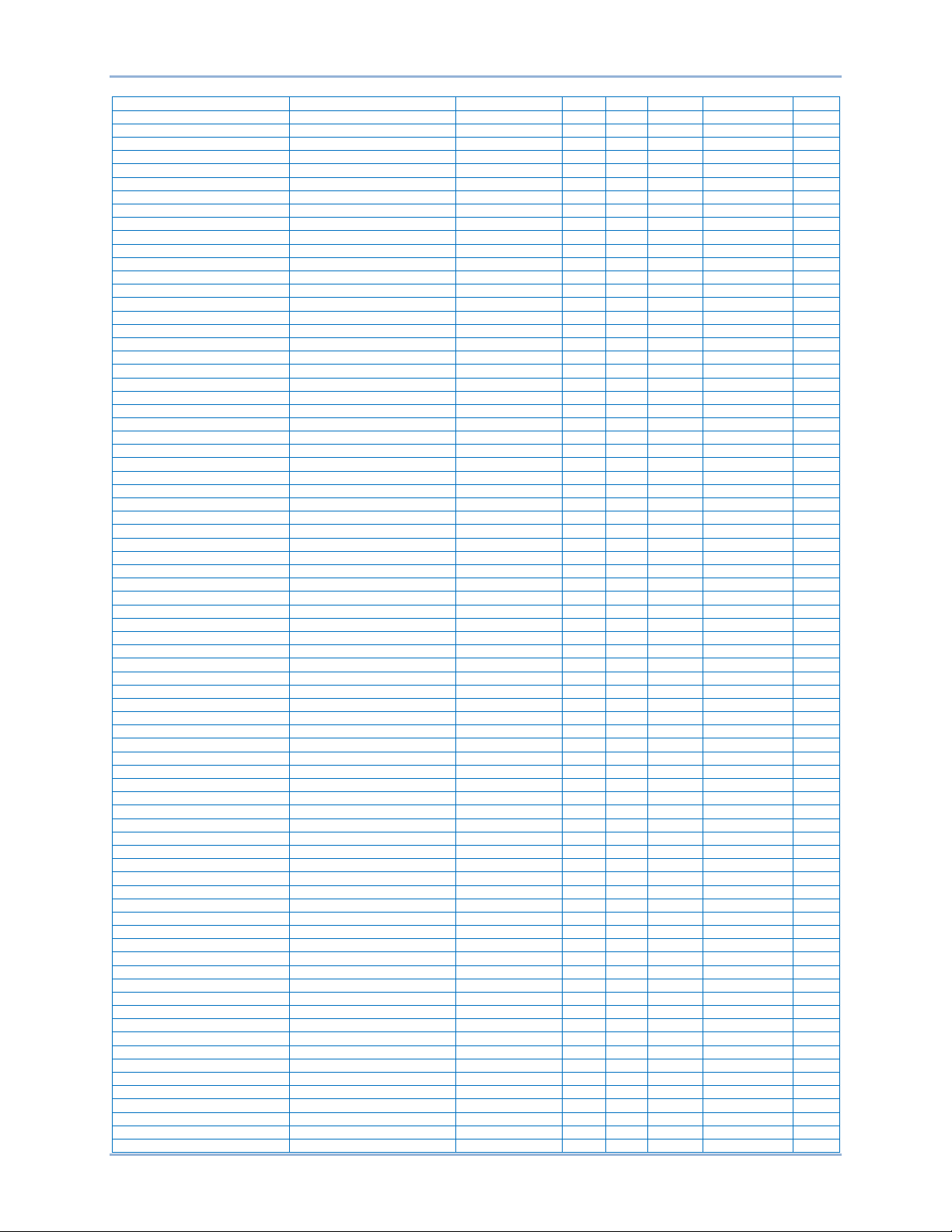

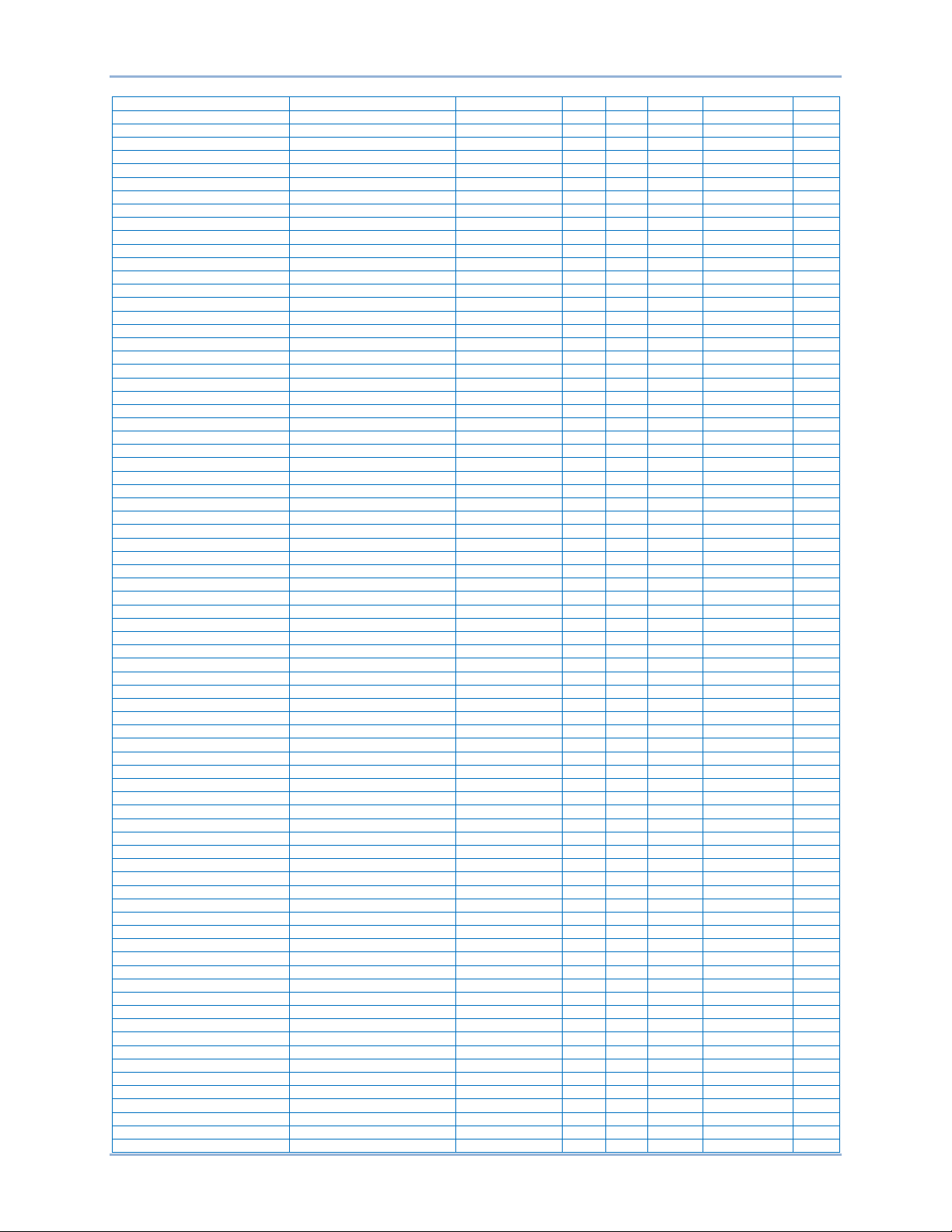

Register Table ........................................................................................................................................... 13

Conventions ............................................................................................................................................. 13

Register Table ......................................................................................................................................... 13

General ................................................................................................................................................ 13

SBO Select .......................................................................................................................................... 14

SBO Operate ....................................................................................................................................... 14

Direct Operate ...................................................................................................................................... 15

Binary Points ........................................................................................................................................ 15

Reporting ............................................................................................................................................. 31

Power Quality ....................................................................................................................................... 31

Fault Record ........................................................................................................................................ 32

Relay Settings ...................................................................................................................................... 33

Reporting Setup ................................................................................................................................... 35

Power Quality Setup ............................................................................................................................ 35

Demand Setup ..................................................................................................................................... 35

Fault Record Setup .............................................................................................................................. 35

Poll Block Settings ............................................................................................................................... 35

Metering ............................................................................................................................................... 39

Demand Data ....................................................................................................................................... 42

Global Settings ..................................................................................................................................... 44

BE1-11 Contents

Page 6

iv 9424200774 Rev B

Protection Settings ............................................................................................................................... 56

User Labels ........................................................................................................................................ 152

Alarms and Targets Reporting .............................................................................................................. 155

Revision History ...................................................................................................................................... 177

Contents BE1-11

Page 7

9424200774 Rev B 1

General Information

This document describes the Modbus™ communications protocol employed by BE1-11 Protection

Systems and how to exchange information with these protection systems over a Modbus network. The

BE1-11 communicates by emulating a subset of the Modicon 984 Programmable Controller.

Modbus communications use a master-slave technique in which only the master can initiate a transaction.

This transaction is called a query. When appropriate, a slave (BE1-11) responds to the query. When a

Modbus master communicates with a slave, information is provided or requested by the master.

Information residing in the BE1-11 is grouped categorically as follows:

• Global Parameters

• Control Parameters (Select Before Operate)

• Setting Parameters

• Report Parameters

• Metering Parameters

All supported data can be read as specified in the register table. Abbreviations are used in the register

table to indicate the register type. Register types are:

• Read/Write = RW

• Read Only = R

Select Before Operate (SBO) functions are used to change active settings groups and control outputs.

There are four settings groups in the BE1-11, one of which may be selected as active using SBO

commands.

When a slave receives a query, the slave responds by either supplying the requested data to the master

or performing the requested action. A slave device never initiates communications on the Modbus

network and will always generate a response to the query unless certain error conditions occur. The

BE1-11 is designed to communicate on the Modbus network only as a slave device.

Message Structure

Device Address Field

The device address field contains the unique Modbus address of the slave being queried. The addressed

slave repeats the address in the device address field of the response message. This field is 1 byte.

Modbus protocol limits a device address from 1 - 247. The address is user-selectable at insta llati on and

can be altered during real-time operation.

Function Code Field

The function code field in the query message defines the action to be taken by the addressed slave. This

field is echoed in the response message and is altered by setting the most significant bit (MSB) of the

field to 1 if the response is an error response. This field is 1 byte in length.

The BE1-11 maps all available data into the Modicon 984 holding register address space and supports

the following function codes:

• Function 03 (03 hex) - read holding registers

• Function 06 (06 hex) - preset single register

• Function 08 (08 hex), subfunction 00 - diagnostics: return query data

• Function 08 (08 hex), subfunction 01 - diagnostics: restart communications option

• Function 08 (08 hex), subfunction 04 - diagnostics: force listen only mode

• Function 16 (10 hex) - preset multiple registers

BE1-11 General Information

Page 8

2 9424200774 Rev B

PDU

ADU

Function code

Data

Additional address

Error Check

Data Block Field

The query data block contains additional information needed by the slave to perform the requested

function. The response data block contains data collected by the slave for the queried function. An error

response will substitute an exception response code for the data block. The length of this field varies with

each query. See the paragraphs on Register Definitions in this manual for interpretation of data.

Error Check Field

The error check field provides a method for the slave to validate the integrity of the query message

contents and allows the master to confirm the validity of response message contents. This field is 2 bytes.

Modbus™ Modes of Operati on

A standard Modbus network offers the remote terminal unit (RTU) transmission mode for communication.

BE1-11 Protection Syst ems support the Modbus/TCP or RS-485 modes depending on communication

options for the protection system. For example, the Modbus/TCP mode is employed when Ethernet

Protocol Option “2” (Modbus/TCP with BEST net™Plus) or Ethernet Protocol Option “4” (Modbus/TCP and

DNP3 with BESTnetPlus) is ordered. See the style chart in the Introduction chapter of the appropriate

instruction manual for the BE1-11. The BE1-11 also supports the Modbus over RS-485 protocol when the

BE1-11 is ordered with the RS-485 Port Protocol Option “M”. The BE1-11 supports Modbus/TCP and RS485 at the same time. These two optional modes of operation are described below.

A master can query slaves individually or universally. A universal ("broadcast") query, when allowed,

evokes no response from any slave device. If a query to an individual slave device requests actions

unable to be performed by the slave, the slave response message contains an exception response code

defining the error detected. Exception response codes are quite often enhanced by the information found

in the "Error Details" block of holding registers.

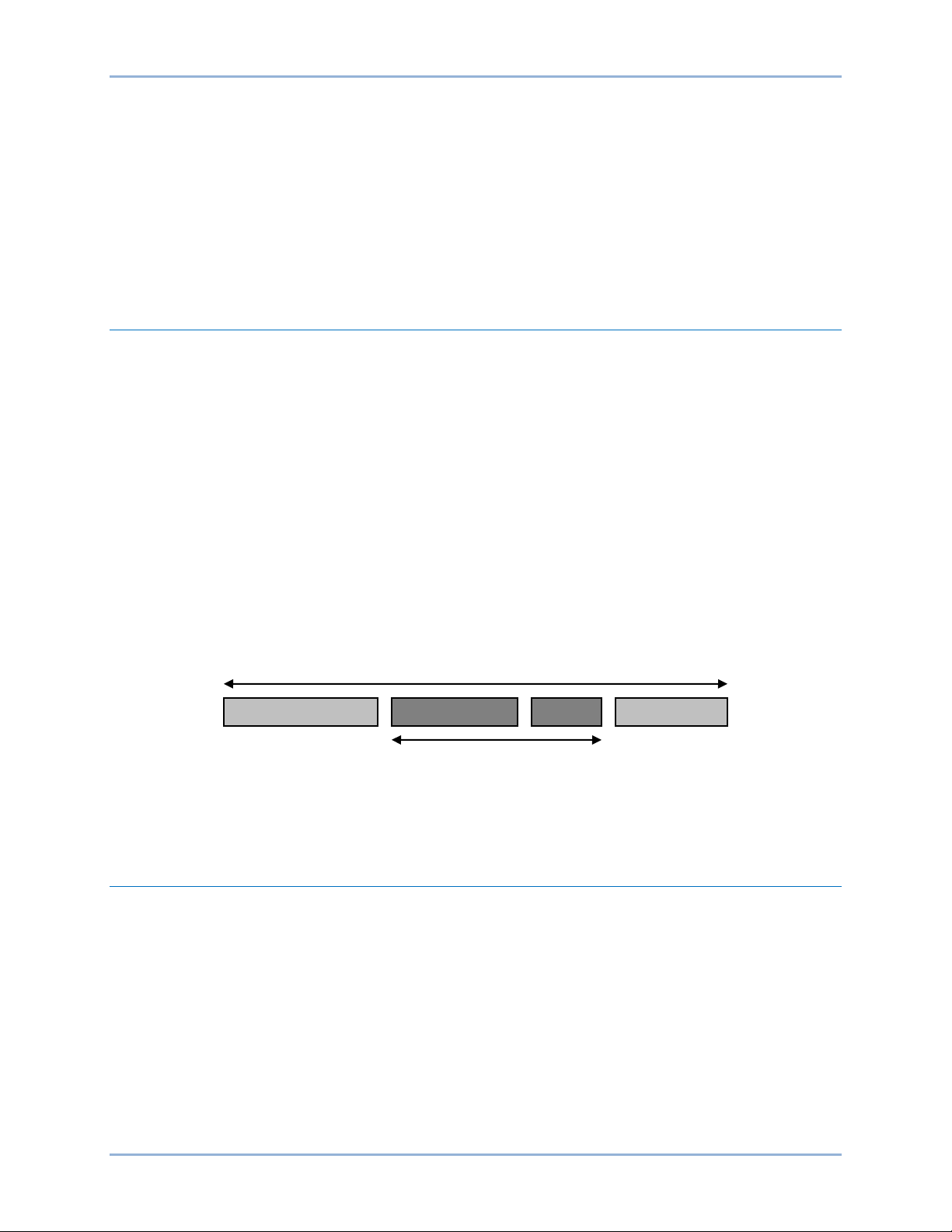

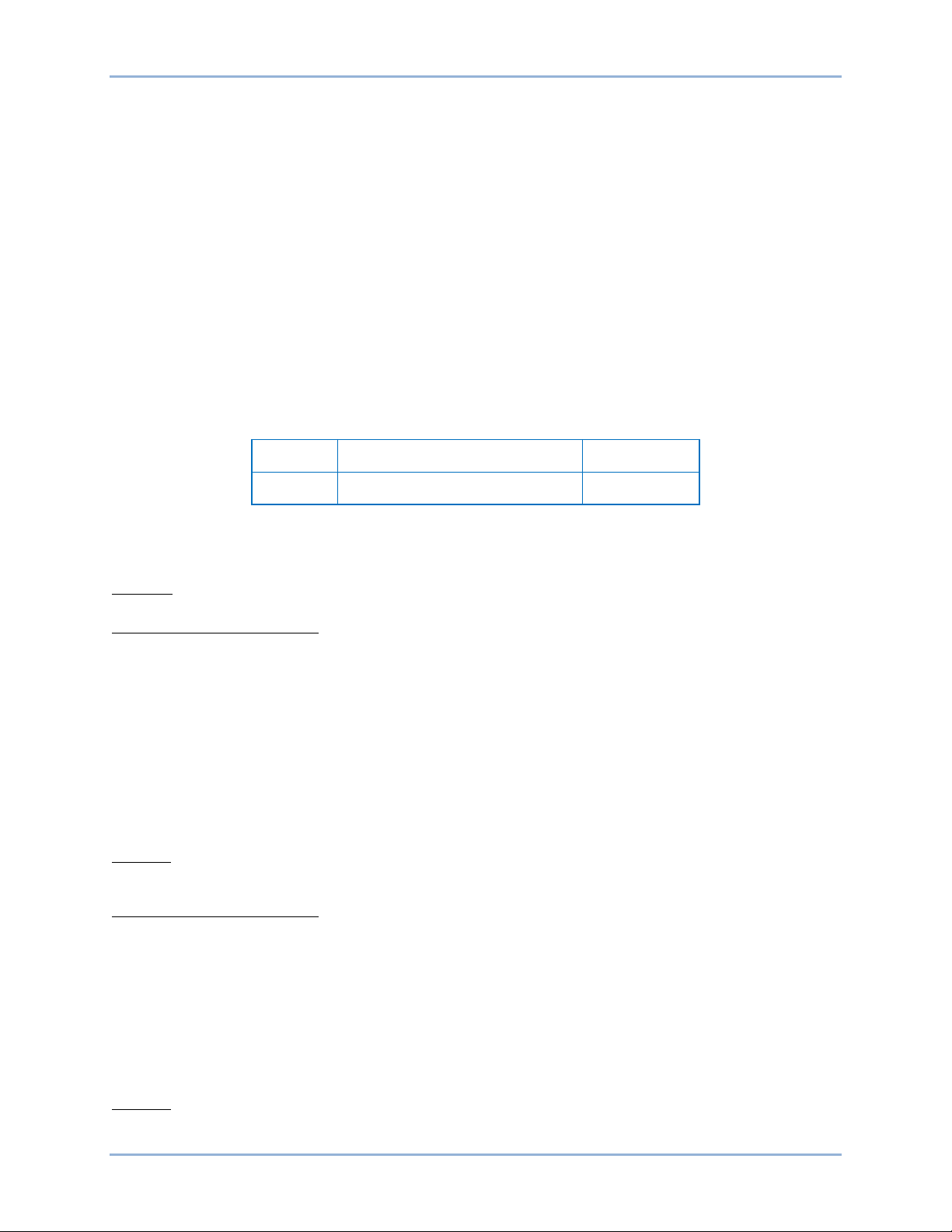

The Modbus protocol defines a simple Protocol Data Unit (PDU) independent of the underlying

communication layers. The mapping of the Modbus protocol on specific buses or networks can introduce

some additional fields on the Application Data Unit (ADU). See Figure 1.

Figure 1. General Modbus Frame

The client that initiates a Modbus transaction builds the Modbus Application Data Unit. The function code

indicates to the server which kind of action to perform.

Modbus™ Over Serial Line

Message Structure

Master initiated queries and BE1-11 responses share the same message structure. Each message is

comprised of four message fields. They are:

• Device Address (1 byte)

• Function Code (1 byte)

• Data Block (n bytes)

• Error Check field (2 bytes)

Each 8-bit byte in a message contains two 4-bit hexadecimal characters. The message is transmitted in a

continuous stream with the LSB of each byte of data transmitted first. Transmission of each 8-bit data

byte occurs with one start bit and either one or two stop bits. Parity checking is performed, when enabled,

and can be either odd or even. The transmission baud rate is user-selectable, and can be set at

General Information BE1-11

Page 9

9424200774 Rev B 3

PDU

Modbus TCP/IP ADU

Function code

Data

MBAP Header

installation and altered during real-time operation. The BE1-11 Modbus supports baud rates up to

115200. The factory default baud rate is 19200.

The BE1-11 supports RS-485 compatible serial interfaces. This interface is accessible from the rear panel

of the BE1-11. The RS-485 interface is configured for Modbus communication when Option “M” is

ordered.

Message Framing and Timing Considerations

When receiving a message via the RS-485 communication port, the BE1-11 requires an inter-by te lat enc y

of 3.5 character times before considering the message complete.

Once a valid query is received, the BE1-11 waits a specified amount of time before responding. This time

delay is set on the Miscellaneous Modbus Settings screen under Communications in BESTCO M SPlus®.

This parameter contains a value from 10 - 10,000 milliseconds. The default value is 10 milliseconds.

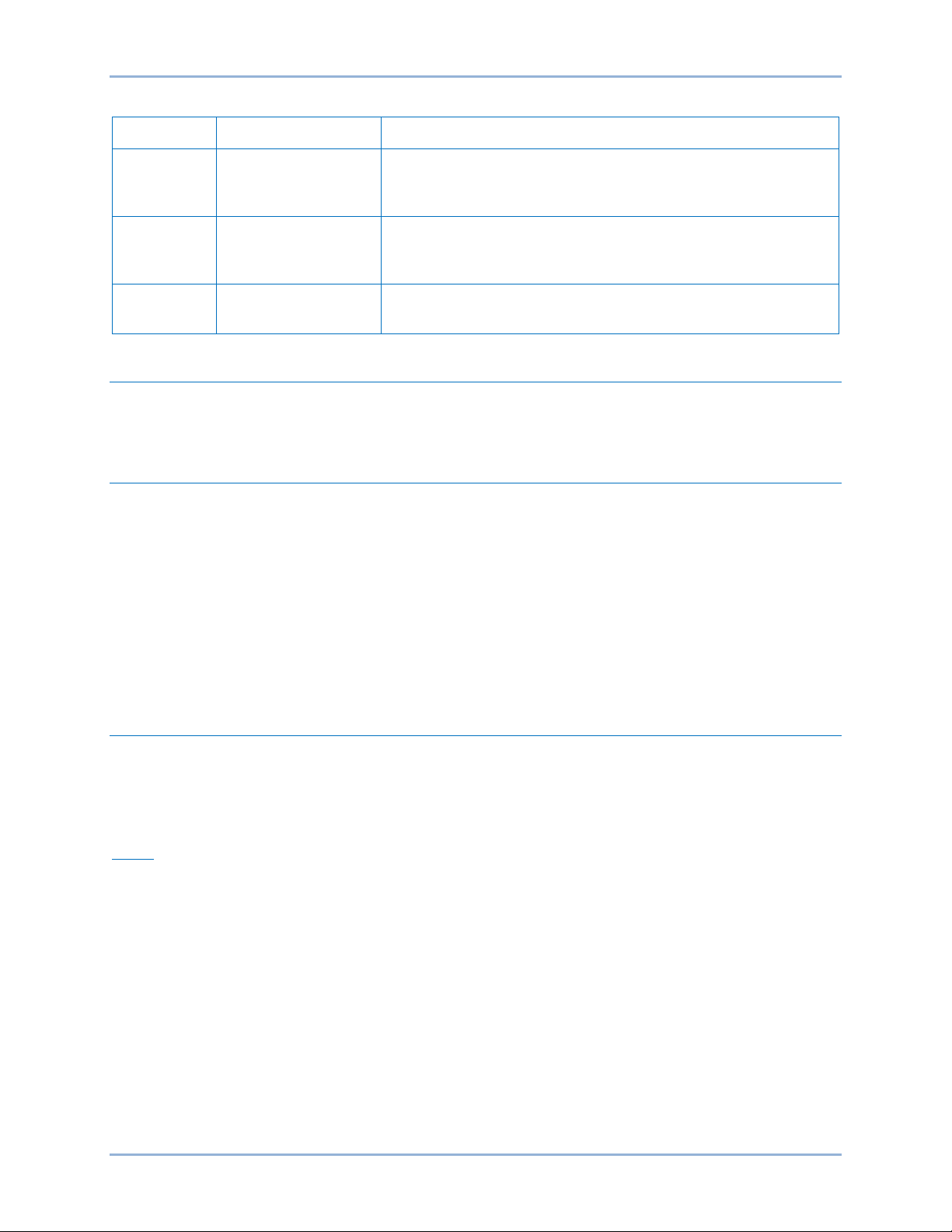

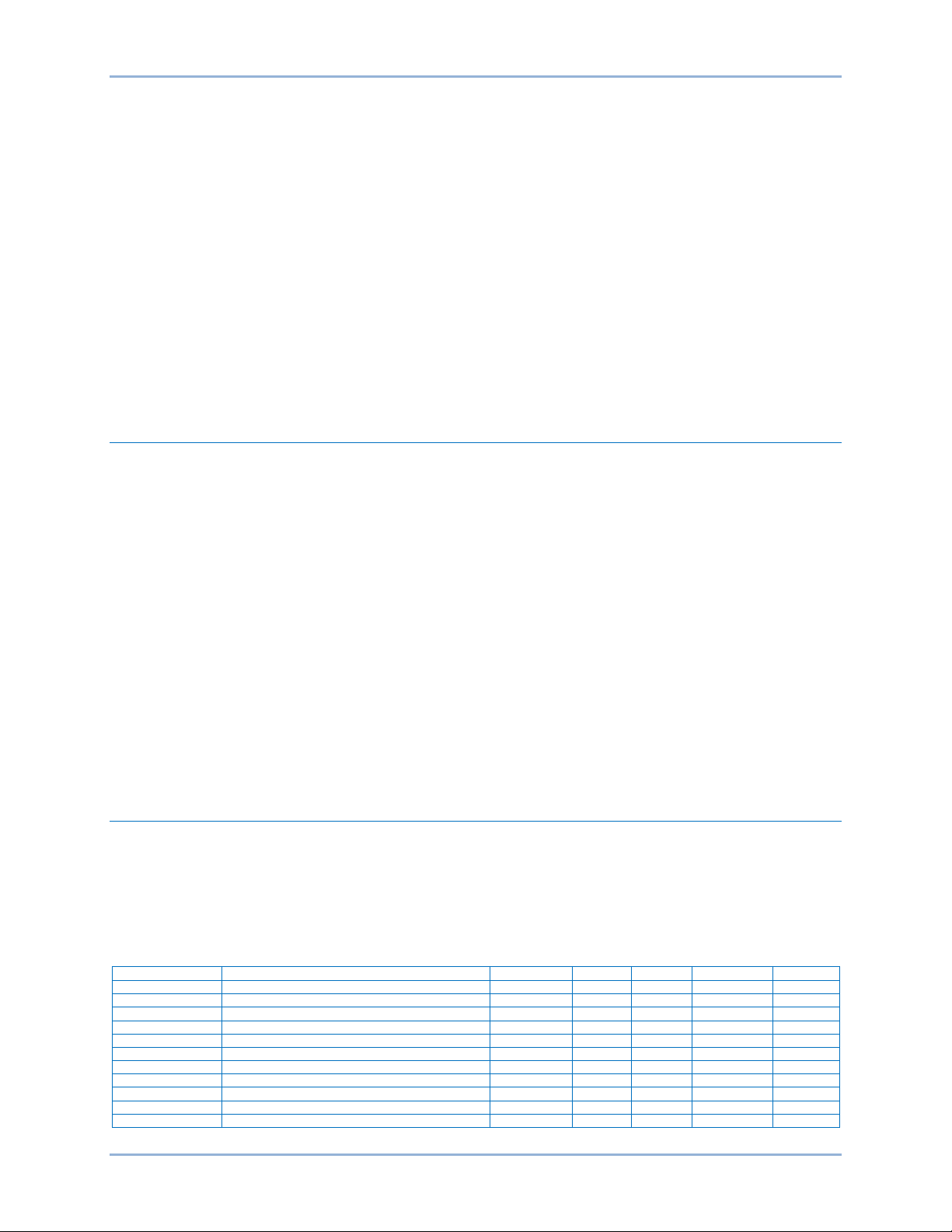

Table 1 provides the response message transmission time (in seconds) and 3.5 character times (in

milliseconds) for various message lengths and baud rates.

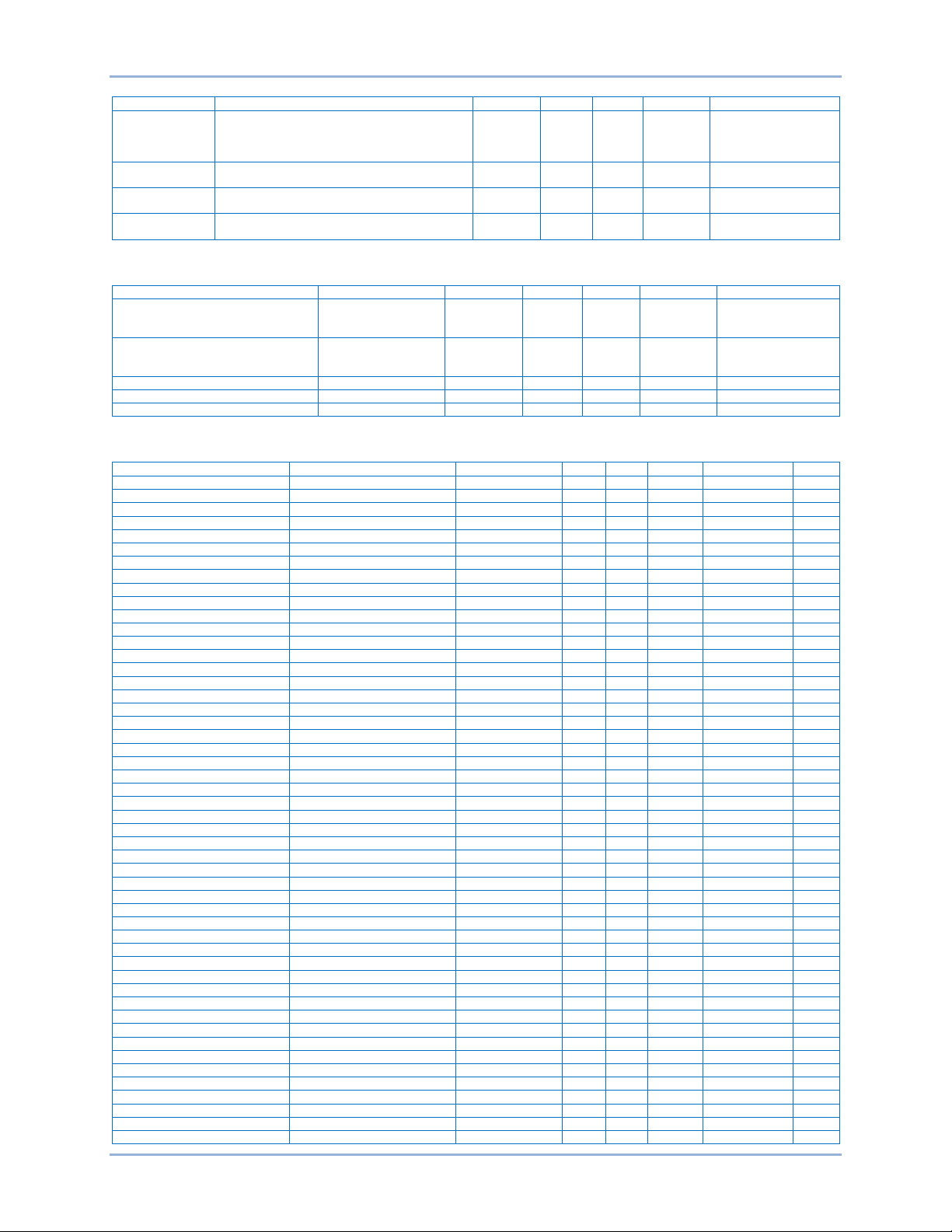

Table 1. Timing Considerations

Message Tx Time (s)

Baud Rate 3.5 Character Time (ms)

2400 16.04 0.59 1.17

4800 8.021 0.29 0.59

9600 4.0104 0.15 0.29

19200 2.0052 0.07 0.15

128 Bytes 256 Bytes

Modbus™ on TCP/IP

Application Data Unit

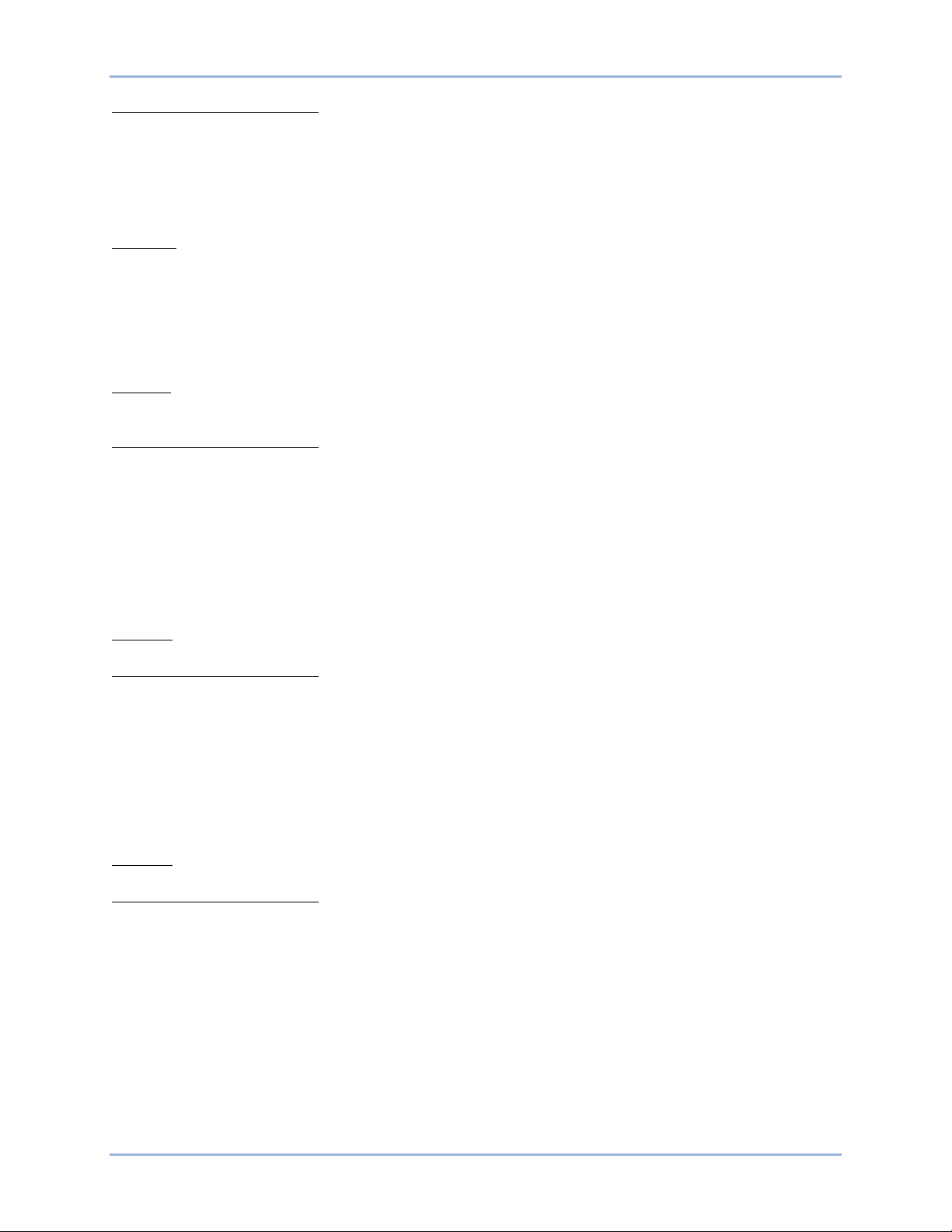

The following describes the encapsulation of a Modbus request or response when it is carried on a

Modbus TCP/IP network. See Figure 2.

Figure 2. Modbus Request/Response Over TCP/IP

A dedicated header is used on TCP/IP to identify the Modbus Application Data Unit. It is called the MBAP

header (Modbus Application Protocol header).

This header provides some differences compared to the Modbus RTU application data unit used on a

serial line:

• The Modbus ‘slave addr ess’ field usually use d on Modbus Serial Line is replaced by a s i ngle byte

• All Modbus requests an d responses are d esigned in s uch a way that the rec ipient can ver ify that

BE1-11 General Information

‘Unit Identifier’ wit hin the MBAP header. Th e ‘Unit Identifier’ is us ed to communicate via dev ices

such as bridges, routers, and gateways that use a single IP address to support multiple

independent Modbus end units.

a message is finished. For func tio n codes wher e the M odbus PDU h as a fix ed len gth, the fu nc tio n

code alone is suff icient. For function c odes carrying a var iable amount of data in the request or

response, the data field includes a byte count.

Page 10

4 9424200774 Rev B

• When Modbus is carr ied over TCP, additional len gth in for mat ion is c ar rie d i n th e MB AP hea der to

allow the recipient to recognize message boundaries even if the message has been split into

multiple packets for transm ission. The existence of explic it and implicit length rules and us e of a

CRC-32 error check code (on Ethernet) results in an infinitesimal chance of undetected corruption

to a request or response message.

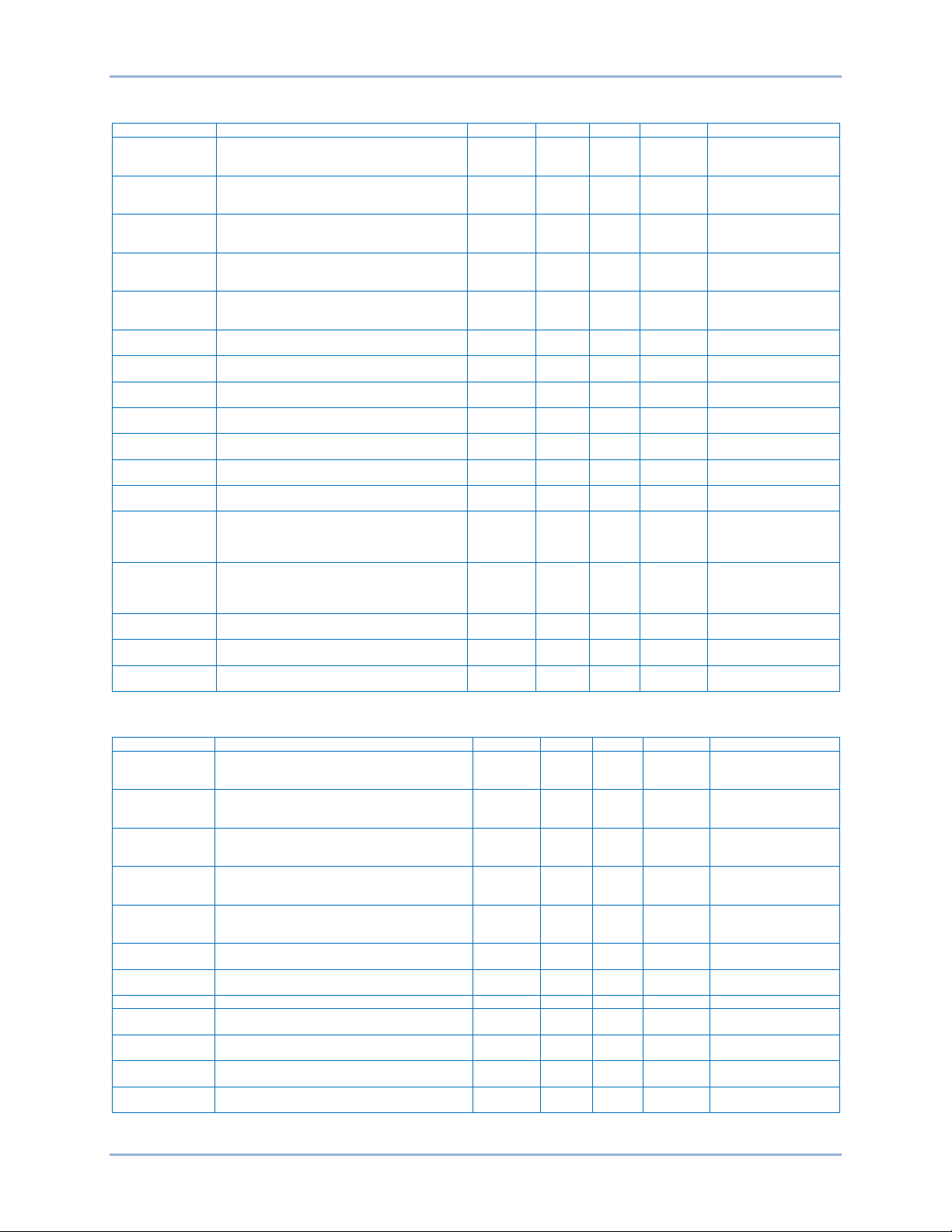

MBAP Header Description

The MBAP Header contains the fields listed in Table 2.

Table 2. MBAP Header Fields

Fields Length Description Client Server

Transaction

Identifier

Protocol

Identifier

Length 2 Bytes Number of following bytes.

Unit Identifier 1 Byte

The header is 7 bytes long:

• Transaction Identifier – Used for transacti on pairing, the Modbus serv er copies in the response

the transaction identifier of the request.

• Protocol Identifier – Used for intra-system multi plexing. The Modbus protocol is identified by the

value 0.

• Length – A byte count of the following fields, including the Unit Identifier and data fields.

• Unit Identifier – Used for intr a-system routing purpose. It is typic ally used to communicat e to a

Modbus or a Modbus serial line slav e through a gateway between an Ethernet TCP/I P network

and a Modbus serial line. This field is set by the Modbus Client in the request and must be

returned with the same value in the response by the server.

2 Bytes

2 Bytes 0 = Modbus protocol.

Identification of a Modbus

request/response transaction.

Identification of a remote slave

connected on a serial line or on

other buses.

Initialized by

the client.

Initialized by

the client.

Initialized by

the client

(request).

Initialized by

the client.

Recopied by the

server from the

received request.

Recopied by the

server from the

received request.

Initialized by the

server (response).

Recopied by the

server from the

received request.

Note: All Modbus/TCP ADU are sent via TCP on registered port 502.

Error Handling and Exception Responses

Any query received that contains a non-existent device address, a framing error, or CRC error is ignored.

No response is transmitted. Queries addressed to the BE1-11 with an unsupported function or illegal

values in the data block result in an error response message with an exception response code. The

exception response codes supported by the BE1-11 are provided in Table 3.

General Information BE1-11

Page 11

9424200774 Rev B 5

Table 3. Supported Exception Response Codes

Code Name Description

01 Illegal Function

02 Illegal Data Address

03 Illegal Data Value

The query Function/Subfunction Code is unsupported; query

read of more than 125 registers; query preset of more than 100

registers.

A register referenced in the data block does not support queried

read/write; query preset of a subset of a numerical register

group.

A preset register data block contains an incorrect number of

bytes or one or more data values out of range.

BE1-11 Modbus™ via Ethernet

Modbus can communicate through Ethernet if the IP address of the BE1-11 is configured as described in

the Communication chapter of the appropriate BE1-11 instruction ma nua l.

Communications Hardware Requirements

Modbus™ Over RS-485 Communication Requirements

The BE1-11 optional RS-485 physical interface is three positions of a terminal strip with locations for

Send/Receive A (A), Send/Receive B (B) and Signal Ground (C). Refer to the instruction manuals for the

BE1-11 protection systems for further details.

Modbus™ Over Ethernet TCP/IP Communication Requirements

The BE1-11 Ethernet port (RJ-45 or fiber optic) is used with the Ethernet option. The protection system

supports 10/100BASE-T using Cat 5 / Cat 5e shielded twisted pair on the RJ-45 port or 100MB/s on the

fiber optic port. Refer to the appropriate instruction manual for the BE1-11 for further details.

Detailed Message Query and Res pons e f or RTU Transmission Mode

A detailed description of BE1-11 supported mes s age queri es and respons es is pr ov ided in the follow in g

paragraphs.

Read Holding Registers

Query

This query message requests a register or block of registers to be read. The data block contains the starting

register addres s and the quant ity of regist ers to be rea d. A register address of N wi ll read holding register

N+1. If the query is a broadcast (device address = 0), no response message is returned.

Device Address

Function Code = 03 (hex)

Starting Address Hi

Starting Address Lo

No. of Registers Hi

No. of Registers Lo

CRC Hi error check

CRC Lo error check

The number of registers cannot exceed 125 without causing an error response with the exception code

for an illegal function.

BE1-11 General Information

Page 12

6 9424200774 Rev B

Response

The response message contains the data queried. The data block contains the block length in bytes

followed by the data (one Data Hi byte and one Data Lo byte) for each requested register.

Reading an unassigned holding register returns a value of zero.

Device Address

Function Code = 03 (hex)

Byte Count

Data Hi (For each requested register, there is one Data Hi and one Data Lo.)

Data Lo

.

.

Data Hi

Data Lo

CRC Hi error check

CRC Lo error check

Return Query Data

This query contains data to be returned (looped back) in the response. The response and query

messages should be identical. If the query is a broadcast (device address = 0), no response message is

returned.

Device Address

Function Code = 08 (hex)

Subfunction Hi = 00 (hex)

Subfunction Lo = 00 (hex)

Data Hi = xx (don't care)

Data Lo = xx (don't care)

CRC Hi error check

CRC Lo error check

Restart Communications Option

This query causes the remote communications function of the BE1-11 to restart, terminating an active

listen only mode of operation. No effect is made upon primary BE1-11 operations. Only the remote

communications function is affected. If the query is a broadcast (device address = 0), no response

message is returned.

If the BE1-11 receives this query while in the listen only mode, no response message is generated.

Otherwise, a response message identical to the query message is transmitted prior to the

communications restart.

Device Address

Function Code = 08 (hex)

Subfunction Hi = 00 (hex)

Subfunction Lo = 01 (hex)

Data Hi = xx (don't care)

Data Lo = xx (don't care)

CRC Hi error check

CRC Lo error check

Listen Only Mode

This query forces the addressed BE1-11 to the listen only mode for Modbus communications, isolating it

from other devices on the network. No responses are returned.

General Information BE1-11

Page 13

9424200774 Rev B 7

While in the listen only mode, the BE1-11 continues to monitor all queries. The BE1-11 does not respond

to any other query until the listen only mode is removed. All write requests with a query to Preset Multiple

Registers (Function Code = 16) are also ignored. When the BE1-11 receives the restart communications

query, the listen only mode is removed.

Device Address

Function Code = 08 (hex)

Subfunction Hi = 00 (hex)

Subfunction Lo = 04 (hex)

Data Hi = xx (don't care)

Data Lo = xx (don't care)

CRC Hi error check

CRC Lo error check

Preset Multiple Registers

A preset multiple registers query could address multiple registers in one slave or multiple slaves. If the

query is a broadcast (device address = 0), no response message is returned.

Query

A Preset Multiple Register query message requests a register or block of registers to be written. The data

block contains the starting address and the quantity of registers to be written, followed by the Data Block

byte count and data. The BE1-11 will perform the write when the device address in query is a broadcast

address or the same as the BE1-11 Modbus Unit ID (device address).

A register address of N will write Holding Register N+1.

Data will cease to be written if any of the following exceptions occur.

• Queries to write to Read Only r egisters result i n an err or res ponse with Ex cepti on Code of “I llegal

Data Address”.

• Queries attempting to write more than 100 registers cause an error response with Exception

Code “Illegal Function”.

• An incorrect Byte Count will result in an error response with Exception Code of “Illegal Data

Value”.

• There are several instances of registers that are grouped together to collectively represent a

single numerical BE1-11 d ata value (i.e. - floati ng point data, 32-bit integer data, and strings). A

query to write a subset o f such a register group will result in an error response with Except ion

Code “Illegal Data Address”.

• A query to write a not allo wed value (out of rang e) to a register resul ts in an error response w ith

Exception Code of “Illegal Data Value” .

Device Address

Function Code = 10 (hex)

Starting Address Hi

Starting Address Lo

No. of Registers Hi

No. of Registers Lo

Byte Count

Data Hi

Data Lo

.

.

Data Hi

Data Lo

CRC Hi error check

CRC Lo error check

BE1-11 General Information

Page 14

8 9424200774 Rev B

Response

The response message echoes the starting address and the number of registers. There is no response

message when the query is a broadcast (device address = 0).

Device Address

Function Code = 10 (hex)

Starting Address Hi

Starting Address Lo

No. of Registers Hi

No. of Registers Lo

CRC Hi Error Check

CRC Lo Error Check

Preset Single Register

A Preset Single Register query message requests a single register to be written. If the query is a

broadcast (device address = 0), no response message is returned.

Note: Only data types INT16, INT8, UINT16, UINT8, and String (not longer than 2 bytes), can be preset

by this function.

Query

Data will cease to be written if any of the following exceptions occur.

• Queries to write to Read Only r egisters result i n an err or res ponse with Ex cepti on Code of “I llegal

Data Address”.

• A query to write a disallow ed value (out of range) to a register results in an error response with

Exception Code of “Illegal Data Value” .

Device Address

Function Code = 06 (hex)

Address Hi

Address Lo

Data Hi

Data Lo

CRC Hi error check

CRC Lo error check

Response

The response message echoes the Query message after the register has been altered.

Data Formats

BE1-11 Protection Systems support the following data types:

● Data types mapped to 2 registers

○ Unsigned Integer 32 (Uint32)

○ Signed Integer 32 (Int32)

○ Floating Point (Float)

○ IP Address (IP Address )

○ Strings maximum 4 characters long (String)

● Data types mapped to 1 register

○ Unsigned Integer 1 6 (Uint16) (If this type is mapped to section Binar y Points, then 1 regist er

contains up to 16 b it-mapped variables as listed in the Regis ter Table chapter under Binary

Points.)

○ Signed Integer 16 (Int16)

○ Unsigned Integer 8 (Uint8)

General Information BE1-11

Page 15

9424200774 Rev B 9

Sign

Exponent + 127

Mantissa

○ Signed Integer 8 (Int8)

○ Strings maximum 2 characters long (String)

● Data types mapped to more than 2 registers

○ Strings longer than 4 characters (String)

Floating Point Data Format (Float)

The Modbus floating point data format uses two consecutive holding registers to represent a data value.

The first register contains the low-order 16 bits of the following 32-bit format:

• MSB is the sign bit for the floating-point value (0 = positive).

• The next 8 bits are the exponent biased by 127 decimal.

• The 23 LSBs comprise the normalized mantissa. The most-significant bit of the mantissa is

always assumed to be 1 and is not explicitly stored, yielding an effective precision of 24 bits.

The value of the floating-point number is obtained by multiplying the binary mantissa times two raised to

the power of the unbiased exponent. The assumed bit of the binary mantissa has the value of 1.0, with

the remaining 23 bits providing a fractional value. Table 4 shows the floating-point format.

Table 4. Floating Point Format

1 Bit 8 Bits 23 Bits

The floating-point format allows for values ranging from approximately 8.43X10

–37

to 3.38X1038. A floatingpoint value of all zeroes is the value zero. A floating-point value of all ones (not a number) signifies a

value currently not applicable or disabled.

Example: The value 95,800 represented in floating-point format is hexadecimal 47BB1C00. This number

will read from two consecutive holding registers as follows:

Holding Regi ste r Value

K (Hi Byte) hex 1C

K (Lo Byte) hex 00

K+1 (Hi Byte) hex 47

K+1 (Lo Byte) hex BB

The same byte alignments are required to write.

Long Integer Data Format (Uint32, Int32, and IP Address)

The Modbus long integer data format uses two consecutive holding registers to represent a 32-bit data

value. The first register contains the low-order 16 bits and the second register contains the high-order 16

bits.

Example: The value 95,800 represented in long integer format is hexadecimal 0x00017638. This number

will read from two consecutive holding registers as follows:

Holding Regi ste r Value

K (Hi Byte) hex 76

K (Lo Byte) hex 38

K+1 (Hi Byte) hex 00

K+1 (Lo Byte) hex 01

The same byte alignments are required to write.

Integer Data Format (Uint16 and Int16) or Bit-Mapped Variables in Uint16 Format

The Modbus integer data format uses a single holding register to represent a 16-bit data value.

Example: The value 4660 represented in integer format is hexadecimal 0x1234. This number will read from

a holding register as follows:

BE1-11 General Information

Page 16

10 9424200774 Rev B

Holding Regi ste r Value

K (Hi Byte) hex 12

K (Lo Byte) hex 34

The same byte alignments are required to write.

If Uint16 Data Format is listed in the Binary Points Section only, then each register contains up to 16 bit-

mapped variables as listed in the Register Table chapter under Binary Points.

Example: Register 900 occupies 16 rows in the Register Table where each row gives the name of specific

bit-mapped data such as 900-0 indicates bit 0 of register 900 is mapped to 60FL/60FL ALARM, bit 1 is

mapped to 27P/BLOCK, and so forth until 900-15 is mapped to 27P-2/BLOCK.

Short Integer Data Format/Byte Character Data Format (Uint8 and Int8)

The Modbus short integer data format uses a single holding register to represent an 8-bit data value. The

holding register high byte will always be zero.

Example: The value 132 repres ented in short i nteger format is hex adecimal 0x84. This number w ill read

from a holding register as follows:

Holding Regi ste r Value

K (Hi Byte) hex 00

K (Lo Byte) hex 84

The same byte alignments are required to write.

String Data Format (String)

The Modbus string data format uses one or more holding registers to represent a sequence, or string, of

character values. If the string contains a single character, the holding register high byte will contain the

ASCII character code and the low byte will be zero.

Example: The string “PASSWORD” represented in string format will read as follows:

Holding Register Value

K (Hi Byte) ‘P’

K (Lo Byte) ‘A’

K+1 (Hi Byte) ‘S’

K+1 (Lo Byte) ‘S’

K+2 (Hi Byte) ‘W’

K+2 (Lo Byte) ‘O’

K+3 (Hi Byte) ‘R’

K+3 (Lo Byte) ‘D’

Example: If the above string is changed to “P”, the new string will read as follows:

Holding Regi ste r Value

K (Hi Byte) ‘P’

K (Lo Byte) hex 00

K+1 (Hi Byte) hex 00

K+1 (Lo Byte) hex 00

K+2 (Hi Byte) hex 00

K+2 (Lo Byte) hex 00

K+3 (Hi Byte) hex 00

K+3 (Lo Byte) hex 00

The same byte alignments are required to write.

General Information BE1-11

Page 17

9424200774 Rev B 11

CRC Error Check

This field contains a 2-byte CRC value for transmission error detection. The master first calculates the

CRC and appends it to the query message. The BE1-11 Protection System recalculates the CRC value

for the received query and performs a comparison to the query CRC value to determine if a transmission

error has occurred. If so, no response message is generated. If no transmission error has occurred, the

slave calculates a new CRC value for the response message and appends it to the message for

transmission.

The CRC calculation is performed using all bytes of the device address, function code, and data block

fields. A 16-bit CRC register is initialized to all 1's. Then each 8-bit byte of the message is used in the

following algorithm:

First, exclusive-OR the message byte with the low-order byte of the CRC register. The result, stored in

the CRC register, will then be right-shifted eight times. The CRC register MSB is zero-filled with each

shift. After each shift, the CRC register LSB is examined. If the LSB is a 1, the CRC register is exclusiveORed with the fixed polynomial value A001 (hex) prior to the next shift. Once all bytes of the message

have undergone the above algorithm, the CRC register will contain the message CRC value to be placed

in the error check field.

Reading Fault Record Data

Fault record data is obtained by reading registers from the session fault record. The fault record to be

reported is selected by writing the fault number to register “Fault Report Selection”. See Fault Record

Setup in the Register Table chapter. The selected fault may be from 1 to 255. Entering a value of –1, will

select the most recent fault record.

Contiguous Poll Block Registers

The user may allocate up to 125 holding registers to the Contiguous Poll Block (9875-9999). This

allocation allows dispersed registers that are frequently read to be polled via a single read query. Mapping

can be done via BESTCOMSPlus or via Modbus registers in the Poll Block Settings session. A register is

assigned to a position in the Poll Block by writing its address value into the corresponding position in the

Contiguous Poll Block Assignments registers (9676-9800) in the Poll Block Settings session. Unassigned

position(s) must be mapped to Modbus Dummy Data register (9874), which always returns a value of 0.

Once assignments are made, the values of the assigned registers may be read by polling the Contiguous

Poll Block. For example, if you wanted to continuously monitor VA Primary (10100), IA Pri m ar y (10124),

IA Angle (10126), and Total PF (10192) Holding Registers, you would first configure the Contiguous Poll

Block Registers by writing the desired register address values 10100, 10101, 10124, 10125, 10126,

10127, 10192, and 10193 into the Contiguous Poll Block Assignment registers 9676 thru 9683,

respectively. You may now begin monitoring the specified registers by reading the first 8 locations in the

Contiguous Poll Block; ie, reading registers 9875/9876 for VA Primary (as specified in its corresponding

assignment registers 9676/9677), reading registers 9876/9877 for IA Primary (as specified in its

corresponding assignment registers 9678/9679), reading registers 9879/9880 for IA Angle (as specified in

its corresponding assignment registers 9680/9681), and reading registers 9881/9882 for Total PF (as

specified in its corresponding assignment registers 9682/9683).

BE1-11 General Information

Page 18

12 9424200774 Rev B

General Information BE1-11

Page 19

9424200774 Rev B 13

Name

Description

Register

Type

Bytes

Writable

Range

System Data

Default Graphics Module Version

1

String

13 R 0 - 13

System Data

Alternate Graphics Module Version

8

String

13 R 0 - 13

System Data

Model Number

15

String

64 R 0 - 64

Reserved

47-110

System Data

Boot Version Information

111

String

64 R 0 - 64

Reserved

143-206

System Data

Firmware Part Number

207

String

64 R 0 - 64

Unit Info

Style Number

239

String

32 R 0 - 32

Unit Info

Model Number

255

String

64 R 0 - 64

Unit Info

App Part Number

287

String

64 R 0 - 64

Unit Info

Serial Number

319

String

32 R 0 - 32

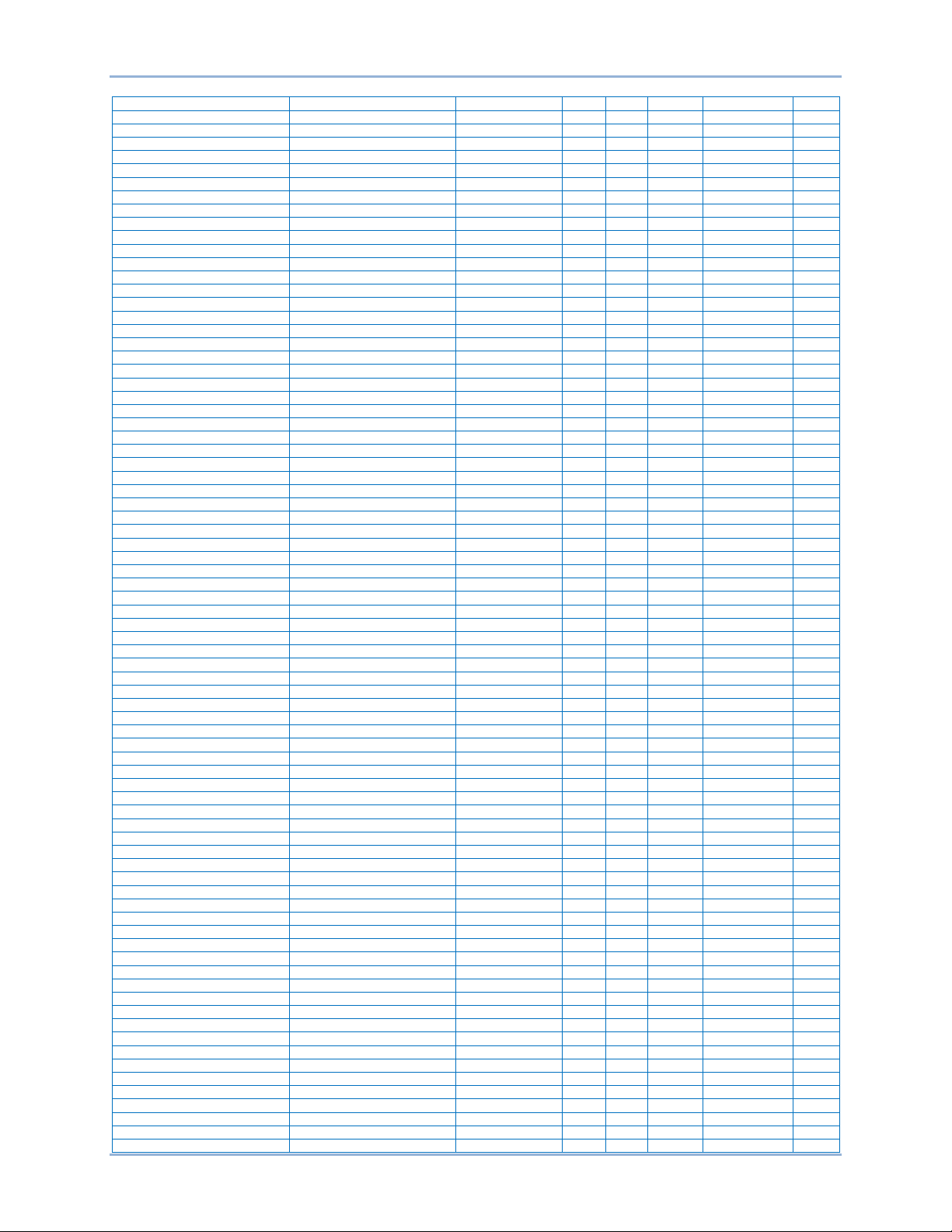

Register Table

Parameters are mapped into the holding register address space in blocks according to access type.

Registers 9875 through 9999 are reserved for user configurable polling block, and register 9874 is

reserved for system use only. By default, all registers in the polling block are mapped to register 9874

when their value is zero. Use BESTCOMSPlus® to map desired data to poll block registers to be read by

one Modbus™ read request.

Any holding register not listed in the register table is an unassigned holding register. Reading or writing to

unassigned holding registers is not allowed and error code “Illegal Data Address” will be reported.

Reading/Writing any data (variable) as its complete (atomic) value is the only legal operation. Partially

requested data will return an error. For example, request for reading/writing of/to only register 620 will

return an error because this register is part of data Settings Group-Direct Operate that is mapped to 2

registers. Reading of register 620 is correct only if reading/writing of both 620 and 621 are requested in

the same query.

Conventions

The Type column uses the following abbreviations:

• String - ASCII string

• Float - Floating point

• Int32 - Integer (32-bit integ er )

• Int16 - Integer (16-bit int eg er)

• Int8 - Integer (8-bit integer)

• Uint32 - Unsigned Integer (32-bit integer)

• Uint16 - Unsigned Integer (16-bit integer)

• Uint8 - Unsigned Integer (8-bit integer)

• IP Address - IP Address

The Style column uses the following abbreviations:

• F - Feeder Protection System

• G - Generator Protection System

• I - Intertie Protection System

• M - Motor Protection System

• T - Transformer Protection System

Register Table

The register table on the following pages contains the following groups:

General, SBO Select, SBO Operate, Direct Operate, Binary Points, Reporting, Power Quality, Fault

Record, Relay Settings, Reporting Setup, Power Quality Setup, Demand Setup, Fault Record Setup, Poll

Block Settings, Metering, Deman d Data, Global Settings, Protection Settings, and User Labels.

General

BE1-11 Register Table

Page 20

14 9424200774 Rev B

Name

Description

Register

Type

Bytes

Writable

Range

43-1

Select

600

Uint32

4

R W

Set=1

Pulse=3

43-2

Select

602

Uint32

4

R W

Set=1

Pulse=3

43-3

Select

604

Uint32

4

R W

Set=1

Pulse=3

43-4

Select

606

Uint32

4

R W

Set=1

Pulse=3

43-5

Select

608

Uint32

4

R W

Set=1

Pulse=3

101

Select

610

Uint32

4

R W

Trip=1

Close=2

Local Contacts

Contact Output 1 Override State Select

612

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 2 Override State Select

613

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 3 Override State Select

614

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 4 Override State Select

615

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 5 Override State Select

616

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output A Override State Select

617

Uint8 1 R W

Off=0

On=1

Settings Group

Select

618

Int32 4 R W

Settings Group 0=0

Settings Group 3=3

Settings Group

Direct Operate

620

Int32 4 R W

Settings Group 0=0

Settings Group 3=3

Local Contacts

Contact Output 6 Override State Select

622

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 7 Override State Select

623

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 8 Override State Select

624

Uint8 1 R W

Off=0

On=1

Name

Description

Register

Type

Bytes

Writable

Range

43-1

Operate

700

Uint32

4

R W

Set=1

Pulse=3

43-2

Operate

702

Uint32

4

R W

Set=1

Pulse=3

43-3

Operate

704

Uint32

4

R W

Set=1

Pulse=3

43-4

Operate

706

Uint32

4

R W

Set=1

Pulse=3

43-5

Operate

708

Uint32

4

R W

Set=1

Pulse=3

101

Operate

710

Uint32

4

R W

Trip=1

Close=2

Local Contacts

Contact Output 1 Override State Operate

712

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 2 Override State Operate

713

Uint8 1 R W

Off=0 On=1

Local Contacts

Contact Output 3 Override State Operate

714

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 4 Override State Operate

715

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 5 Override State Operate

716

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output A Override State Operate

717

Uint8 1 R W

Off=0

On=1

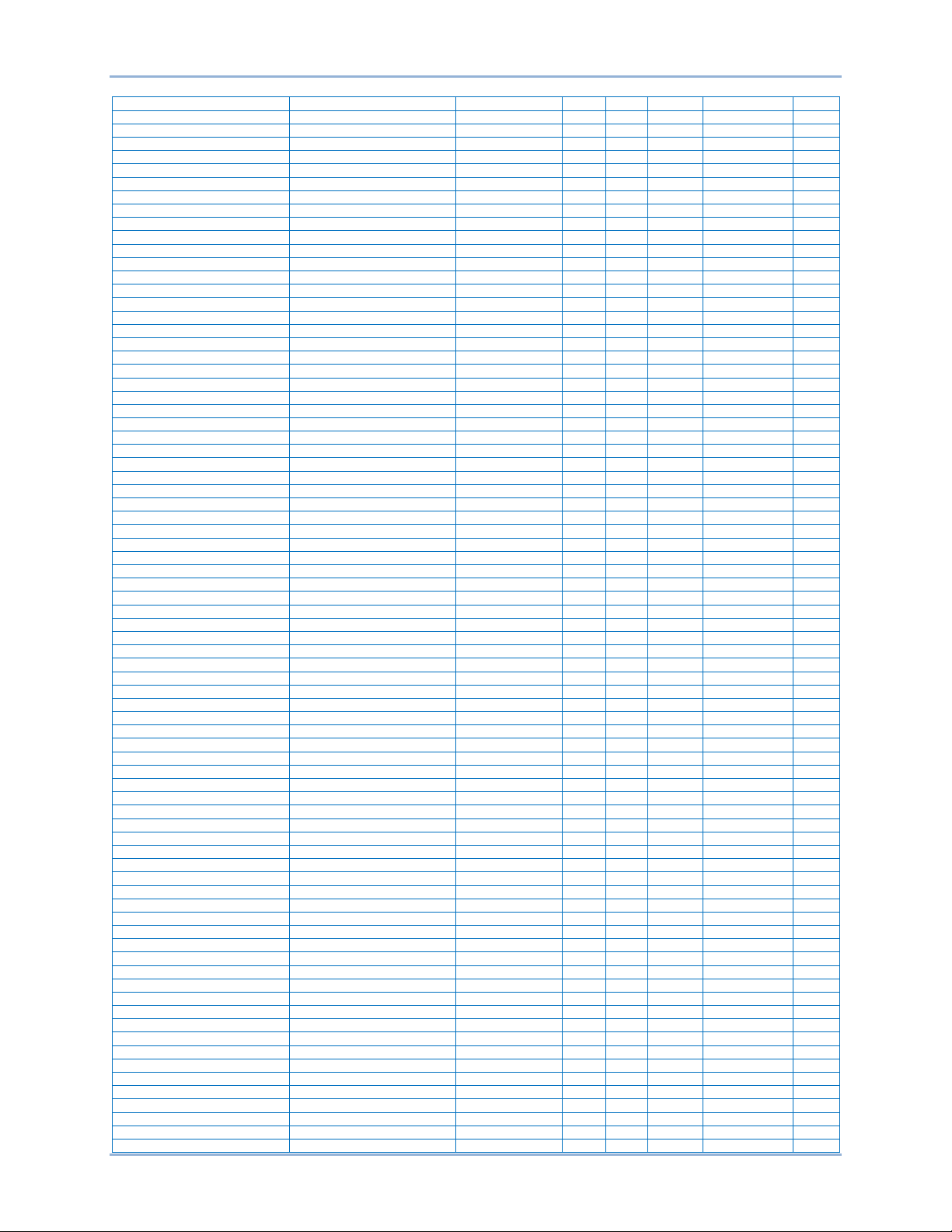

SBO Select

Reset=2

Reset=2

Reset=2

Reset=2

Reset=2

SBO Operate

Settings Group 1=1

Settings Group 2=2

Settings Group 1=1

Settings Group 2=2

Reset=2

Reset=2

Reset=2

Reset=2

Reset=2

Register Table BE1-11

Page 21

9424200774 Rev B 15

Name

Description

Register

Type

Bytes

Writable

Range

Settings Group

Operate

718

Int32 4 R W

Settings Group 0=0

Settings Group 3=3

Local Contacts

Contact Output 6 Override State Operate

720

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 7 Override State Operate

721

Uint8 1 R W

Off=0

On=1

Local Contacts

Contact Output 8 Override State Operate

722

Uint8 1 R W

Off=0

On=1

Name

Description

Register

Type

Bytes

Writable

Range

101

Untag

800

Uint32

4

R W

Disable Tag=0

Blocking Tag=2

101

Tag

802

Uint32

4

R W

Disable Tag=0

Blocking Tag=2

Demand Meter Circuit 1

Reset Demands

804

Uint32

4

R W

Operate=1

Current Demand Circuit 2

Reset Demands

806

Uint32

4

R W

Operate=1

G Current Demand Circuit 2

Reset Demands

808

Uint32

4

R W

Operate=1

Name

Description

Register

Type

Bytes

Writable

Range

Style

60FL

60FL Alarm

900 bit 0

Uint16

2 R True=1 False=0

FGIMT

24

Block

900 bit 1

Uint16

2 R True=1 False=0

GIT

24

Pickup

900 bit 2

Uint16

2 R True=1 False=0

GIT

24

Trip

900 bit 3

Uint16

2 R True=1 False=0

GIT

24

Target

900 bit 4

Uint16

2 R True=1 False=0

GIT

24

Alarm

900 bit 5

Uint16

2 R True=1 False=0

GIT

25

Block

900 bit 6

Uint16

2 R True=1 False=0

FGI

25

Status

900 bit 7

Uint16

2 R True=1 False=0

FGI

25

VM1 Status

900 bit 8

Uint16

2 R True=1 False=0

FGI

27P-1

Block

900 bit 9

Uint16

2 R True=1 False=0

FGIMT

27P-1

Pickup

900 bit 10

Uint16

2 R True=1 False=0

FGIMT

27P-1

Trip

900 bit 11

Uint16

2 R True=1 False=0

FGIMT

27P-1

Target A

900 bit 12

Uint16

2 R True=1 False=0

FGIMT

27P-1

Target B

900 bit 13

Uint16

2 R True=1 False=0

FGIMT

27P-1

Target C

900 bit 14

Uint16

2 R True=1 False=0

FGIMT

27P-2

Block

900 bit 15

Uint16

2 R True=1 False=0

FGIMT

27P-2

Pickup

901 bit 0

Uint16

2 R True=1 False=0

FGIMT

27P-2

Trip

901 bit 1

Uint16

2 R True=1 False=0

FGIMT

27P-2

Target A

901 bit 2

Uint16

2 R True=1 False=0

FGIMT

27P-2

Target B

901 bit 3

Uint16

2 R True=1 False=0

FGIMT

27P-2

Target C

901 bit 4

Uint16

2 R True=1 False=0

FGIMT

27P-3

Block

901 bit 5

Uint16

2 R True=1 False=0

FGIMT

27P-3

Pickup

901 bit 6

Uint16

2 R True=1 False=0

FGIMT

27P-3

Trip

901 bit 7

Uint16

2 R True=1 False=0

FGIMT

27P-3

Target A

901 bit 8

Uint16

2 R True=1 False=0

FGIMT

27P-3

Target B

901 bit 9

Uint16

2 R True=1 False=0

FGIMT

27P-3

Target C

901 bit 10

Uint16

2 R True=1 False=0

FGIMT

27P-4

Block

901 bit 11

Uint16

2 R True=1 False=0

FGIMT

27P-4

Pickup

901 bit 12

Uint16

2 R True=1 False=0

FGIMT

27P-4

Trip

901 bit 13

Uint16

2 R True=1 False=0

FGIMT

27P-4

Target A

901 bit 14

Uint16

2 R True=1 False=0

FGIMT

27P-4

Target B

901 bit 15

Uint16

2 R True=1 False=0

FGIMT

27P-4

Target C

902 bit 0

Uint16

2 R True=1 False=0

FGIMT

27P-5

Block

902 bit 1

Uint16

2 R True=1 False=0

FGIT

27P-5

Pickup

902 bit 2

Uint16

2 R True=1 False=0

FGIT

27P-5

Trip

902 bit 3

Uint16

2 R True=1 False=0

FGIT

27P-5

Target A

902 bit 4

Uint16

2 R True=1 False=0

FGIT

27P-5

Target B

902 bit 5

Uint16

2 R True=1 False=0

FGIT

27P-5

Target C

902 bit 6

Uint16

2 R True=1 False=0

FGIT

27X-1

Block

902 bit 7

Uint16

2 R True=1 False=0

FGIT

27X-1

Pickup

902 bit 8

Uint16

2 R True=1 False=0

FGIT

27X-1

Trip

902 bit 9

Uint16

2 R True=1 False=0

FGIT

27X-1

Target 3V0

902 bit 10

Uint16

2 R True=1 False=0

FGIT

27X-1

Target V2

902 bit 11

Uint16

2 R True=1 False=0

FGIT

27X-1

Target AUX

902 bit 12

Uint16

2 R True=1 False=0

FGIT

27X-1

Target 3RD

902 bit 13

Uint16

2 R True=1 False=0

FGIT

27X-1

Target V1

902 bit 14

Uint16

2 R True=1 False=0

FGIT

27X-2

Block

902 bit 15

Uint16

2 R True=1 False=0

FGIT

27X-2

Pickup

903 bit 0

Uint16

2 R True=1 False=0

FGIT

27X-2

Trip

903 bit 1

Uint16

2 R True=1 False=0

FGIT

Settings Group 1=1

Settings Group 2=2

Direct Operate

Info Tag=1

Info Tag=1

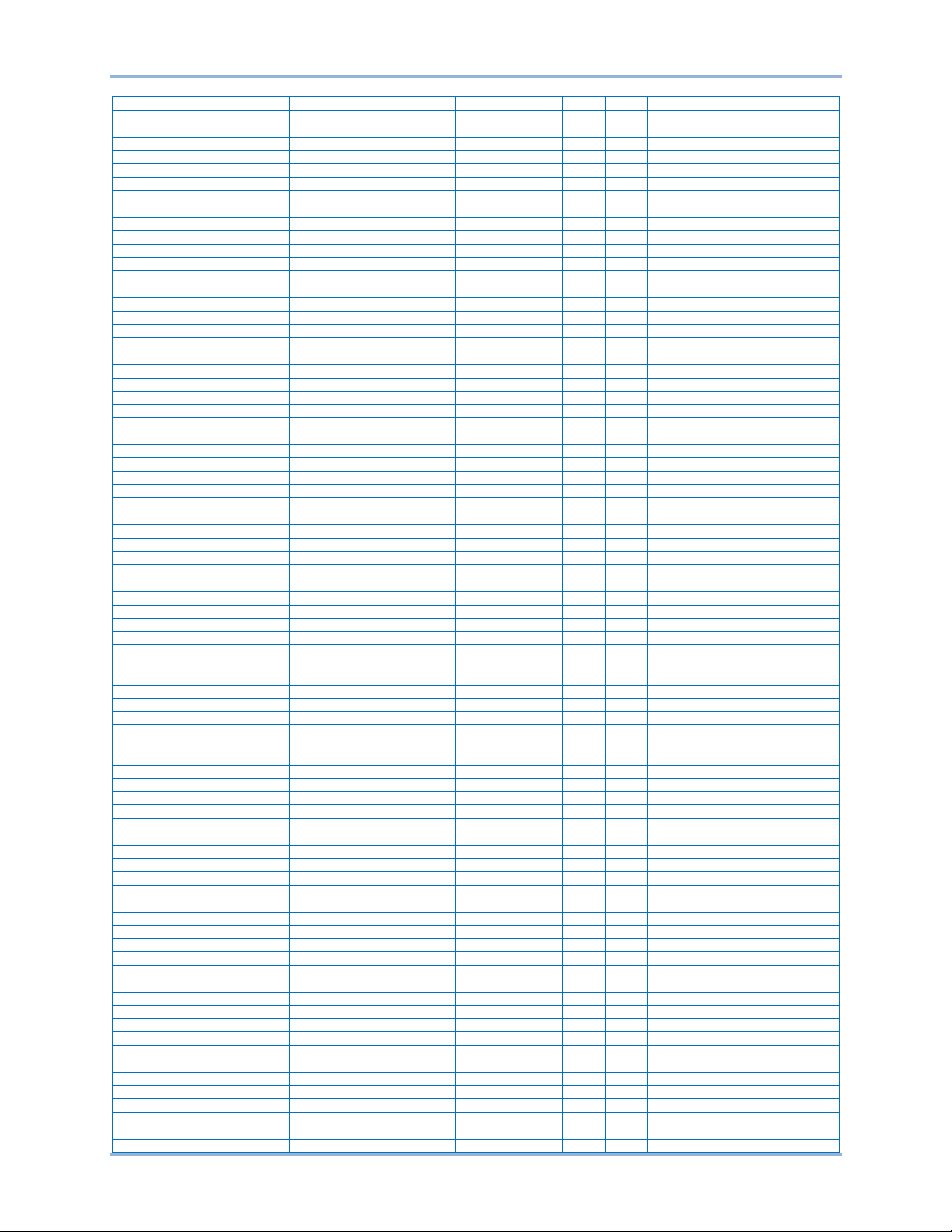

Binary Points

BE1-11 Register Table

Page 22

16 9424200774 Rev B

Name

Description

Register

Type

Bytes

Writable

Range

Style

27X-2

Target 3V0

903 bit 2

Uint16

2 R True=1 False=0

FGIT

27X-2

Target V2

903 bit 3

Uint16

2 R True=1 False=0

FGIT

27X-2

Target AUX

903 bit 4

Uint16

2 R True=1 False=0

FGIT

27X-2

Target 3RD

903 bit 5

Uint16

2 R True=1 False=0

FGIT

27X-2

Target V1

903 bit 6

Uint16

2 R True=1 False=0

FGIT

27X-3

Block

903 bit 7

Uint16

2 R True=1 False=0

FGIT

27X-3

Pickup

903 bit 8

Uint16

2 R True=1 False=0

FGIT

27X-3

Trip

903 bit 9

Uint16

2 R True=1 False=0

FGIT

27X-3

Target 3V0

903 bit 10

Uint16

2 R True=1 False=0

FGIT

27X-3

Target V2

903 bit 11

Uint16

2 R True=1 False=0

FGIT

27X-3

Target AUX

903 bit 12

Uint16

2 R True=1 False=0

FGIT

27X-3

Target 3RD

903 bit 13

Uint16

2 R True=1 False=0

FGIT

27X-3

Target V1

903 bit 14

Uint16

2 R True=1 False=0

FGIT

27X-4

Block

903 bit 15

Uint16

2 R True=1 False=0

FGIT

27X-4

Pickup

904 bit 0

Uint16

2 R True=1 False=0

FGIT

27X-4

Trip

904 bit 1

Uint16

2 R True=1 False=0

FGIT

27X-4

Target 3V0

904 bit 2

Uint16

2 R True=1 False=0

FGIT

27X-4

Target V2

904 bit 3

Uint16

2 R True=1 False=0

FGIT

27X-4

Target AUX

904 bit 4

Uint16

2 R True=1 False=0

FGIT

27X-4

Target 3RD

904 bit 5

Uint16

2 R True=1 False=0

FGIT

27X-4

Target V1

904 bit 6

Uint16

2 R True=1 False=0

FGIT

59P-1

Block

904 bit 7

Uint16

2 R True=1 False=0

FGIMT

59P-1

Pickup

904 bit 8

Uint16

2 R True=1 False=0

FGIMT

59P-1

Trip

904 bit 9

Uint16

2 R True=1 False=0

FGIMT

59P-1

Target A

904 bit 10

Uint16

2 R True=1 False=0

FGIMT

59P-1

Target B

904 bit 11

Uint16

2 R True=1 False=0

FGIMT

59P-1

Target C

904 bit 12

Uint16

2 R True=1 False=0

FGIMT

59P-2

Block

904 bit 13

Uint16

2 R True=1 False=0

FGIMT

59P-2

Pickup

904 bit 14

Uint16

2 R True=1 False=0

FGIMT

59P-2

Trip

904 bit 15

Uint16

2 R True=1 False=0

FGIMT

59P-2

Target A

905 bit 0

Uint16

2 R True=1 False=0

FGIMT

59P-2

Target B

905 bit 1

Uint16

2 R True=1 False=0

FGIMT

59P-2

Target C

905 bit 2

Uint16

2 R True=1 False=0

FGIMT

59P-3

Block

905 bit 3

Uint16

2 R True=1 False=0

FGIT

59P-3

Pickup

905 bit 4

Uint16

2 R True=1 False=0

FGIT

59P-3

Trip

905 bit 5

Uint16

2 R True=1 False=0

FGIT

59P-3

Target A

905 bit 6

Uint16

2 R True=1 False=0

FGIT

59P-3

Target B

905 bit 7

Uint16

2 R True=1 False=0

FGIT

59P-3

Target C

905 bit 8

Uint16

2 R True=1 False=0

FGIT

59P-4

Block

905 bit 9

Uint16

2 R True=1 False=0

FGIT

59P-4

PICKUP

905 bit 10

Uint16

2 R True=1 False=0

FGIT

59P-4

Trip

905 bit 11

Uint16

2 R True=1 False=0

FGIT

59P-4

Target A

905 bit 12

Uint16

2 R True=1 False=0

FGIT

59P-4

Target B

905 bit 13

Uint16

2 R True=1 False=0

FGIT

59P-4

Target C

905 bit 14

Uint16

2 R True=1 False=0

FGIT

59X-1

Block

905 bit 15

Uint16

2 R True=1 False=0

FGIMT

59X-1

Pickup

906 bit 0

Uint16

2 R True=1 False=0

FGIMT

59X-1

Trip

906 bit 1

Uint16

2 R True=1 False=0

FGIMT

59X-1

Target 3V0

906 bit 2

Uint16

2 R True=1 False=0

FGIMT

59X-1

Target V2

906 bit 3

Uint16

2 R True=1 False=0

FGIMT

59X-1

Target AUX

906 bit 4

Uint16

2 R True=1 False=0

FGIMT

59X-1

Target 3RD

906 bit 5

Uint16

2 R True=1 False=0

FGIMT

59X-1

Target V1

906 bit 6

Uint16

2 R True=1 False=0

FGIMT

59X-2

Block

906 bit 7

Uint16

2 R True=1 False=0

FGIMT

59X-2

Pickup

906 bit 8

Uint16

2 R True=1 False=0

FGIMT

59X-2

Trip

906 bit 9

Uint16

2 R True=1 False=0

FGIMT

59X-2

Target 3V0

906 bit 10

Uint16

2 R True=1 False=0

FGIMT

59X-2

Target V2

906 bit 11

Uint16

2 R True=1 False=0

FGIMT

59X-2

Target AUX

906 bit 12

Uint16

2 R True=1 False=0

FGIMT

59X-2

Target 3RD

906 bit 13

Uint16

2 R True=1 False=0

FGIMT

59X-2

Target V1

906 bit 14

Uint16

2 R True=1 False=0

FGIMT

59X-3

BLOCK

906 bit 15

Uint16

2 R True=1 False=0

FGIT

59X-3

PICKUP

907 bit 0

Uint16

2 R True=1 False=0

FGIT

59X-3

TRIP

907 bit 1

Uint16

2 R True=1 False=0

FGIT

59X-3

Target 3V0

907 bit 2

Uint16

2 R True=1 False=0

FGIT

59X-3

Target V2

907 bit 3

Uint16

2 R True=1 False=0

FGIT

59X-3

Target AUX

907 bit 4

Uint16

2 R True=1 False=0

FGIT

59X-3

Target 3RD

907 bit 5

Uint16

2 R True=1 False=0

FGIT

59X-3

Target V1

907 bit 6

Uint16

2 R True=1 False=0

FGIT

59X-4

Block

907 bit 7

Uint16

2 R True=1 False=0

FGIT

59X-4

Pickup

907 bit 8

Uint16

2 R True=1 False=0

FGIT

59X-4

Trip

907 bit 9

Uint16

2 R True=1 False=0

FGIT

59X-4

Target 3V0

907 bit 10

Uint16

2 R True=1 False=0

FGIT

59X-4

Target V2

907 bit 11

Uint16

2 R True=1 False=0

FGIT

59X-4

Target AUX

907 bit 12

Uint16

2 R True=1 False=0

FGIT

59X-4

Target 3RD

907 bit 13

Uint16

2 R True=1 False=0

FGIT

59X-4

Target V1

907 bit 14

Uint16

2 R True=1 False=0

FGIT

50-1

Block

907 bit 15

Uint16

2 R True=1 False=0

FGIMT

Register Table BE1-11

Page 23

9424200774 Rev B 17

Name

Description

Register

Type

Bytes

Writable

Range

Style

50-1

Pickup

908 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-1

Trip

908 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-1

Target A

908 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-1

Target B

908 bit 3

Uint16

2 R True=1 False=0

FGIMT

50-1

Target C

908 bit 4

Uint16

2 R True=1 False=0

FGIMT

50-1

Target Negative Sequence

908 bit 5

Uint16

2 R True=1 False=0

FGIMT

50-1

Target Residual

908 bit 6

Uint16

2 R True=1 False=0

FGIMT

50-1

Target Independent Ground

908 bit 7

Uint16

2 R True=1 False=0

FGIMT

50-1

67 Target A

908 bit 8

Uint16

2 R True=1 False=0

FGIT

50-1

67 Target B

908 bit 9

Uint16

2 R True=1 False=0

FGIT

50-1

67 Target C

908 bit 10

Uint16

2 R True=1 False=0

FGIT

50-1

67 Target Negative Sequence

908 bit 11

Uint16

2 R True=1 False=0

FGIT

50-1

67 Target Residual

908 bit 12

Uint16

2 R True=1 False=0

FGIT

50-1

67 Target Independent Gr ou nd

908 bit 13

Uint16

2 R True=1 False=0

FGIT

50-2

Block

908 bit 14

Uint16

2 R True=1 False=0

FGIMT

50-2

Pickup

908 bit 15

Uint16

2 R True=1 False=0

FGIMT

50-2

Trip

909 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-2

Target A

909 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-2

Target B

909 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-2

Target C

909 bit 3

Uint16

2 R True=1 False=0

FGIMT

50-2

Target Negative Sequence

909 bit 4

Uint16

2 R True=1 False=0

FGIMT

50-2

Target Residual

909 bit 5

Uint16

2 R True=1 False=0

FGIMT

50-2

Target Independent Ground

909 bit 6

Uint16

2 R True=1 False=0

FGIMT

50-2

67 Target A

909 bit 7

Uint16

2 R True=1 False=0

FGIT

50-2

67 Target B

909 bit 8

Uint16

2 R True=1 False=0

FGIT

50-2

67 Target C

909 bit 9

Uint16

2 R True=1 False=0

FGIT

50-2

67 Target Negative Sequence

909 bit 10

Uint16

2 R True=1 False=0

FGIT

50-2

67 Target Residual

909 bit 11

Uint16

2 R True=1 False=0

FGIT

50-2

67 Target Independent Gr ou nd

909 bit 12

Uint16

2 R True=1 False=0

FGIT

50-3

Block

909 bit 13

Uint16

2 R True=1 False=0

FGIMT

50-3

Pickup

909 bit 14

Uint16

2 R True=1 False=0

FGIMT

50-3

Trip

909 bit 15

Uint16

2 R True=1 False=0

FGIMT

50-3

Target A

910 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-3

Target B

910 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-3

Target C

910 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-3

Target Negative Sequence

910 bit 3

Uint16

2 R True=1 False=0

FGIMT

50-3

Target Residual

910 bit 4

Uint16

2 R True=1 False=0

FGIMT

50-3

Target Independent Ground

910 bit 5

Uint16

2 R True=1 False=0

FGIMT

50-3

67 Target A

910 bit 6

Uint16

2 R True=1 False=0

FGIT

50-3

67 Target B

910 bit 7

Uint16

2 R True=1 False=0

FGIT

50-3

67 Target C

910 bit 8

Uint16

2 R True=1 False=0

FGIT

50-3

67 Target Negative Sequence

910 bit 9

Uint16

2 R True=1 False=0

FGIT

50-3

67 Target Residual

910 bit 10

Uint16

2 R True=1 False=0

FGIT

50-3

67 Target Independent Gr ou nd

910 bit 11

Uint16

2 R True=1 False=0

FGIT

50-4

Block

910 bit 12

Uint16

2 R True=1 False=0

FGIMT

50-4

Pickup

910 bit 13

Uint16

2 R True=1 False=0

FGIMT

50-4

Trip

910 bit 14

Uint16

2 R True=1 False=0

FGIMT

50-4

Target A

910 bit 15

Uint16

2 R True=1 False=0

FGIMT

50-4

Target B

911 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-4

Target C

911 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-4

Target Negative Sequence

911 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-4

Target Residual

911 bit 3

Uint16

2 R True=1 False=0

FGIMT

50-4

Target Independent Ground

911 bit 4

Uint16

2 R True=1 False=0

FGIMT

50-4

67 Target A

911 bit 5

Uint16

2 R True=1 False=0

FGIT

50-4

67 Target B

911 bit 6

Uint16

2 R True=1 False=0

FGIT

50-4

67 Target C

911 bit 7

Uint16

2 R True=1 False=0

FGIT

50-4

67 Target Negative Sequence

911 bit 8

Uint16

2 R True=1 False=0

FGIT

50-4

67 Target Residual

911 bit 9

Uint16

2 R True=1 False=0

FGIT

50-4

67 Target Independent Gr ou nd

911 bit 10

Uint16

2 R True=1 False=0

FGIT

50-5

Block

911 bit 11

Uint16

2 R True=1 False=0

FGIMT

50-5

Pickup

911 bit 12

Uint16

2 R True=1 False=0

FGIMT

50-5

Trip

911 bit 13

Uint16

2 R True=1 False=0

FGIMT

50-5

Target A

911 bit 14

Uint16

2 R True=1 False=0

FGIMT

50-5

Target B

911 bit 15

Uint16

2 R True=1 False=0

FGIMT

50-5

Target C

912 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-5

Target Negative Sequence

912 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-5

Target Residual

912 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-5

Target Independent Ground

912 bit 3

Uint16

2 R True=1 False=0

FGIMT

50-5

67 Target A

912 bit 4

Uint16

2 R True=1 False=0

FGIT

50-5

67 Target B

912 bit 5

Uint16

2 R True=1 False=0

FGIT

50-5

67 Target C

912 bit 6

Uint16

2 R True=1 False=0

FGIT

50-5

67 Target Negative Sequence

912 bit 7

Uint16

2 R True=1 False=0

FGIT

50-5

67 Target Residual

912 bit 8

Uint16

2 R True=1 False=0

FGIT

50-5

67 Target Independent Gr ou nd

912 bit 9

Uint16

2 R True=1 False=0

FGIT

50-6

Block

912 bit 10

Uint16

2 R True=1 False=0

FGIMT

50-6

Pickup

912 bit 11

Uint16

2 R True=1 False=0

FGIMT

50-6

Trip

912 bit 12

Uint16

2 R True=1 False=0

FGIMT

50-6

Target A

912 bit 13

Uint16

2 R True=1 False=0

FGIMT

BE1-11 Register Table

Page 24

18 9424200774 Rev B

Name

Description

Register

Type

Bytes

Writable

Range

Style

50-6

Target B

912 bit 14

Uint16

2 R True=1 False=0

FGIMT

50-6

Target C

912 bit 15

Uint16

2 R True=1 False=0

FGIMT

50-6

Target Negative Sequence

913 bit 0

Uint16

2 R True=1 False=0

FGIMT

50-6

Target Residual

913 bit 1

Uint16

2 R True=1 False=0

FGIMT

50-6

Target Independent Ground

913 bit 2

Uint16

2 R True=1 False=0

FGIMT

50-6

67 Target A

913 bit 3

Uint16

2 R True=1 False=0

FGIT

50-6

67 Target B

913 bit 4

Uint16

2 R True=1 False=0

FGIT

50-6

67 Target C

913 bit 5

Uint16

2 R True=1 False=0

FGIT

50-6

67 Target Negative Sequence

913 bit 6

Uint16

2 R True=1 False=0

FGIT

50-6

67 Target Residual

913 bit 7

Uint16

2 R True=1 False=0

FGIT

50-6

67 Target Independent Gr ou nd

913 bit 8

Uint16

2 R True=1 False=0

FGIT

51-1

Block

913 bit 9

Uint16

2 R True=1 False=0

FGIMT

51-1

Pickup

913 bit 10

Uint16

2 R True=1 False=0

FGIMT

51-1

Trip

913 bit 11

Uint16

2 R True=1 False=0

FGIMT

51-1

Target A

913 bit 12

Uint16

2 R True=1 False=0

FGIMT

51-1

Target B

913 bit 13

Uint16

2 R True=1 False=0

FGIMT

51-1

Target C

913 bit 14

Uint16

2 R True=1 False=0

FGIMT

51-1

Target Negative Sequence

913 bit 15

Uint16

2 R True=1 False=0

FGIMT

51-1

Target Residual

914 bit 0

Uint16

2 R True=1 False=0

FGIMT

51-1

Target Independent Ground

914 bit 1

Uint16

2 R True=1 False=0

FGIMT

51-1

67 Target A

914 bit 2

Uint16

2 R True=1 False=0

FGIT

51-1

67 Target B

914 bit 3

Uint16

2 R True=1 False=0

FGIT

51-1

67 Target C

914 bit 4

Uint16

2 R True=1 False=0

FGIT

51-1

67 Target NEG SEQ

914 bit 5

Uint16

2 R True=1 False=0

FGIT

51-1

67 Target Residual

914 bit 6

Uint16

2 R True=1 False=0

FGIT

51-1

67 Target Independent Gr ou nd

914 bit 7

Uint16

2 R True=1 False=0

FGIT

51-2

Block

914 bit 8

Uint16

2 R True=1 False=0

FGIMT

51-2

Pickup

914 bit 9

Uint16

2 R True=1 False=0

FGIMT

51-2

Trip

914 bit 10

Uint16

2 R True=1 False=0

FGIMT

51-2

Target A

914 bit 11

Uint16

2 R True=1 False=0

FGIMT

51-2

Target B

914 bit 12

Uint16

2 R True=1 False=0

FGIMT

51-2

Target C

914 bit 13

Uint16

2 R True=1 False=0

FGIMT

51-2

Target Negative Sequence

914 bit 14

Uint16

2 R True=1 False=0

FGIMT

51-2

Target Residual

914 bit 15

Uint16

2 R True=1 False=0

FGIMT

51-2

Target Independent Ground

915 bit 0

Uint16

2 R True=1 False=0

FGIMT

51-2

67 Target A

915 bit 1

Uint16

2 R True=1 False=0

FGIT

51-2

67 Target B

915 bit 2

Uint16

2 R True=1 False=0

FGIT

51-2

67 Target C

915 bit 3

Uint16

2 R True=1 False=0

FGIT

51-2

67 Target NEG SEQ

915 bit 4

Uint16

2 R True=1 False=0

FGIT

51-2

67 Target Residual

915 bit 5

Uint16

2 R True=1 False=0

FGIT

51-2

67 Target Independent Gr ou nd

915 bit 6

Uint16

2 R True=1 False=0

FGIT

51-3

Block

915 bit 7

Uint16

2 R True=1 False=0

FGIMT

51-3

Pickup

915 bit 8

Uint16

2 R True=1 False=0

FGIMT

51-3

Trip

915 bit 9

Uint16

2 R True=1 False=0

FGIMT

51-3

Target A

915 bit 10

Uint16

2 R True=1 False=0

FGIMT

51-3

Target B

915 bit 11

Uint16

2 R True=1 False=0

FGIMT

51-3

Target C

915 bit 12

Uint16

2 R True=1 False=0

FGIMT

51-3

Target Negative Sequence

915 bit 13

Uint16

2 R True=1 False=0

FGIMT

51-3

Target Residual

915 bit 14

Uint16

2 R True=1 False=0

FGIMT

51-3

Target Independent Ground

915 bit 15

Uint16

2 R True=1 False=0

FGIMT

51-3

67 Target A

916 bit 0

Uint16

2 R True=1 False=0

FGIT

51-3

67 Target B

916 bit 1

Uint16

2 R True=1 False=0

FGIT

51-3

67 Target C

916 bit 2

Uint16

2 R True=1 False=0

FGIT

51-3

67 Target Negative Sequence

916 bit 3

Uint16

2 R True=1 False=0

FGIT

51-3

67 Target Residual

916 bit 4

Uint16

2 R True=1 False=0

FGIT

51-3

67 Target Independent Gr ou nd

916 bit 5

Uint16

2 R True=1 False=0

FGIT

51-4

Block

916 bit 6

Uint16

2 R True=1 False=0

FGIMT

51-4

Pickup

916 bit 7

Uint16

2 R True=1 False=0

FGIMT

51-4

Trip

916 bit 8

Uint16

2 R True=1 False=0

FGIMT

51-4

Target A

916 bit 9

Uint16

2 R True=1 False=0

FGIMT

51-4

Target B

916 bit 10

Uint16

2 R True=1 False=0

FGIMT

51-4

Target C

916 bit 11

Uint16

2 R True=1 False=0

FGIMT

51-4

Target Negative Sequence

916 bit 12

Uint16

2 R True=1 False=0

FGIMT

51-4

Target Residual

916 bit 13

Uint16

2 R True=1 False=0

FGIMT

51-4

Target Independent Ground

916 bit 14

Uint16

2 R True=1 False=0

FGIMT

51-4

67 Target A

916 bit 15

Uint16

2 R True=1 False=0

FGIT

51-4

67 Target B

917 bit 0

Uint16

2 R True=1 False=0

FGIT

51-4

67 Target C

917 bit 1

Uint16

2 R True=1 False=0

FGIT

51-4

67 Target Negative Sequence

917 bit 2

Uint16

2 R True=1 False=0

FGIT

51-4

67 Target Residual

917 bit 3

Uint16

2 R True=1 False=0

FGIT

51-4

67 Target Independent Gr ou nd

917 bit 4

Uint16

2 R True=1 False=0

FGIT

51-5

Block

917 bit 5

Uint16

2 R True=1 False=0

FGIMT

51-5

Pickup

917 bit 6

Uint16

2 R True=1 False=0

FGIMT

51-5

Trip

917 bit 7

Uint16

2 R True=1 False=0

FGIMT

51-5

Target A

917 bit 8

Uint16

2 R True=1 False=0

FGIMT

51-5