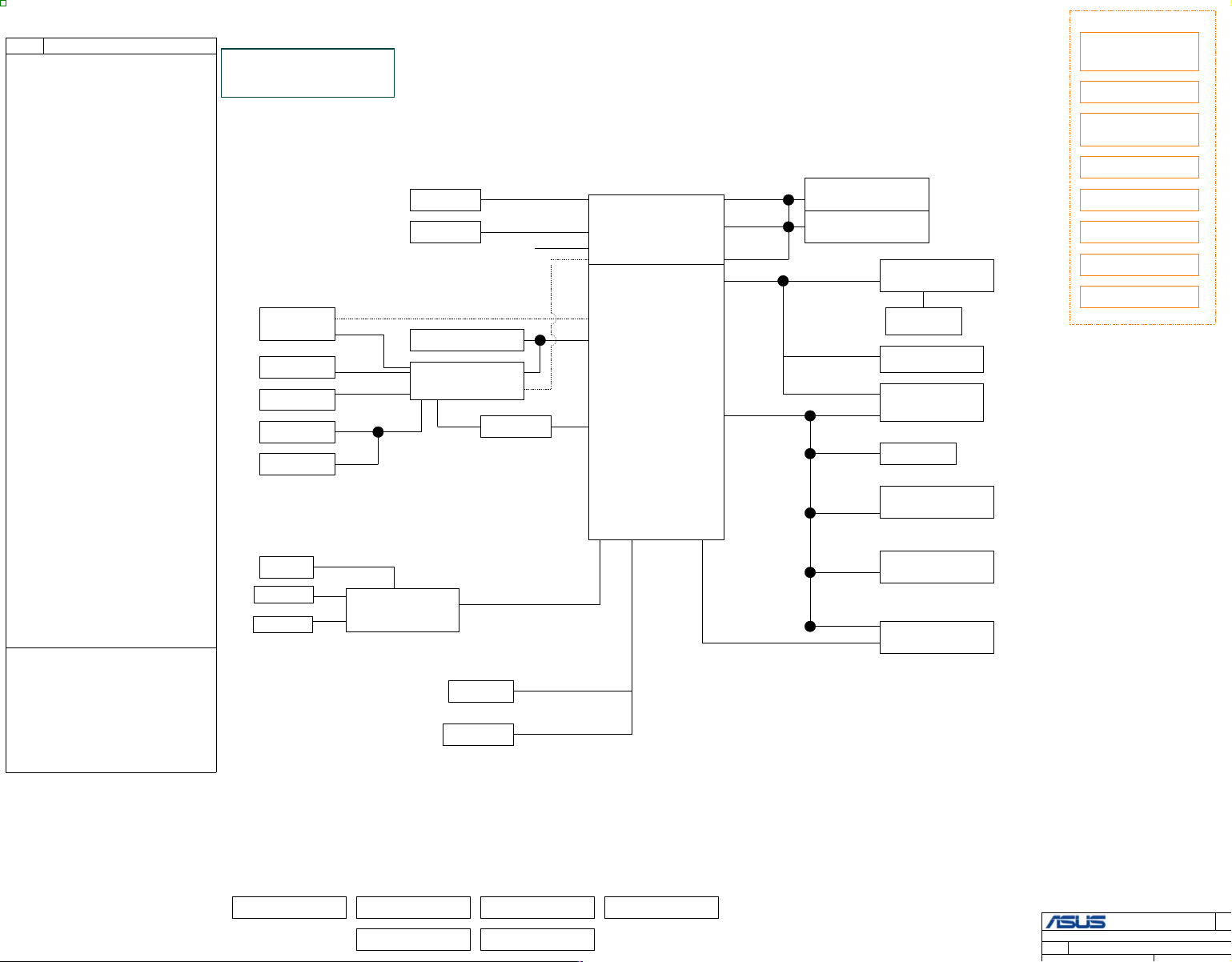

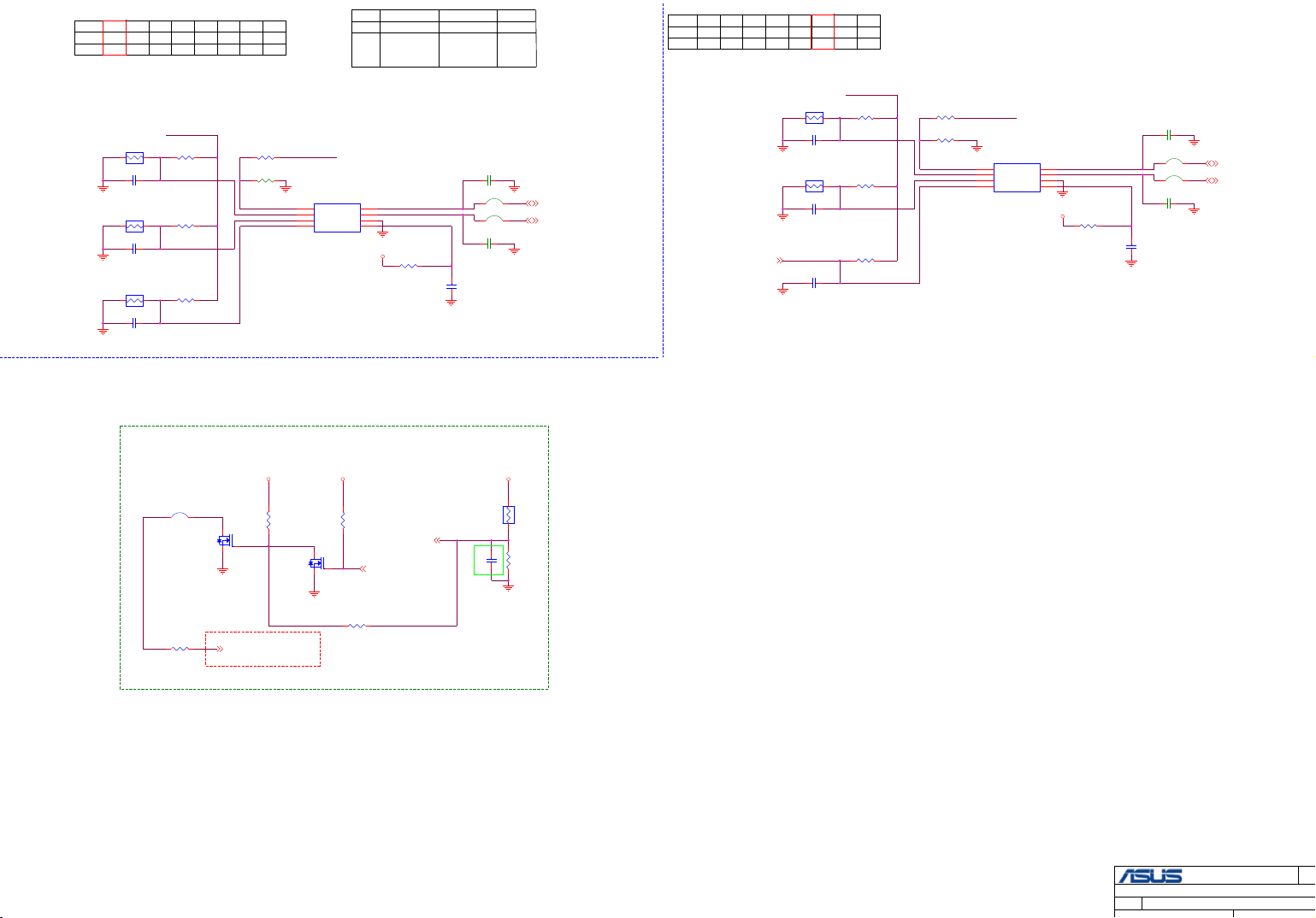

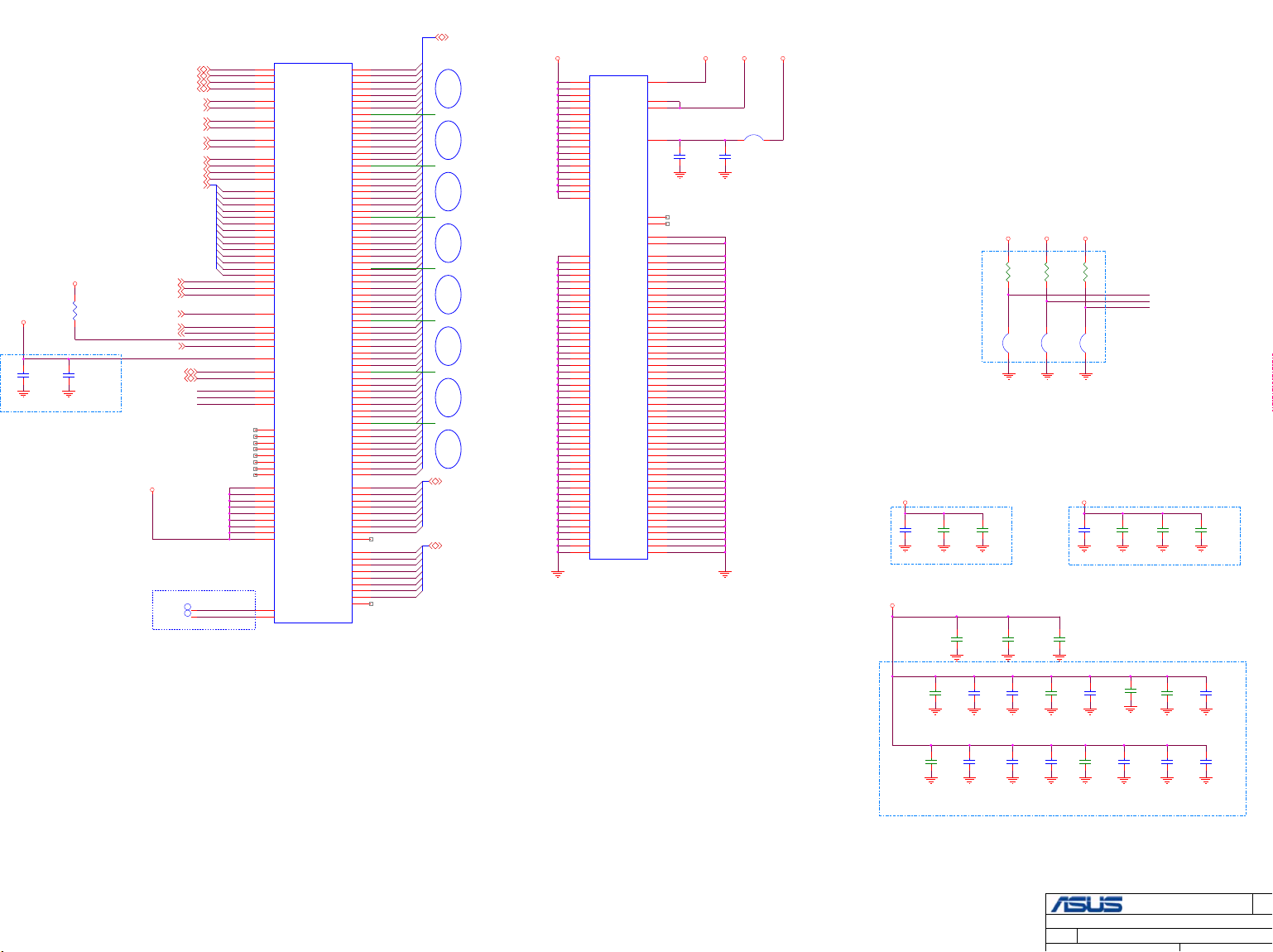

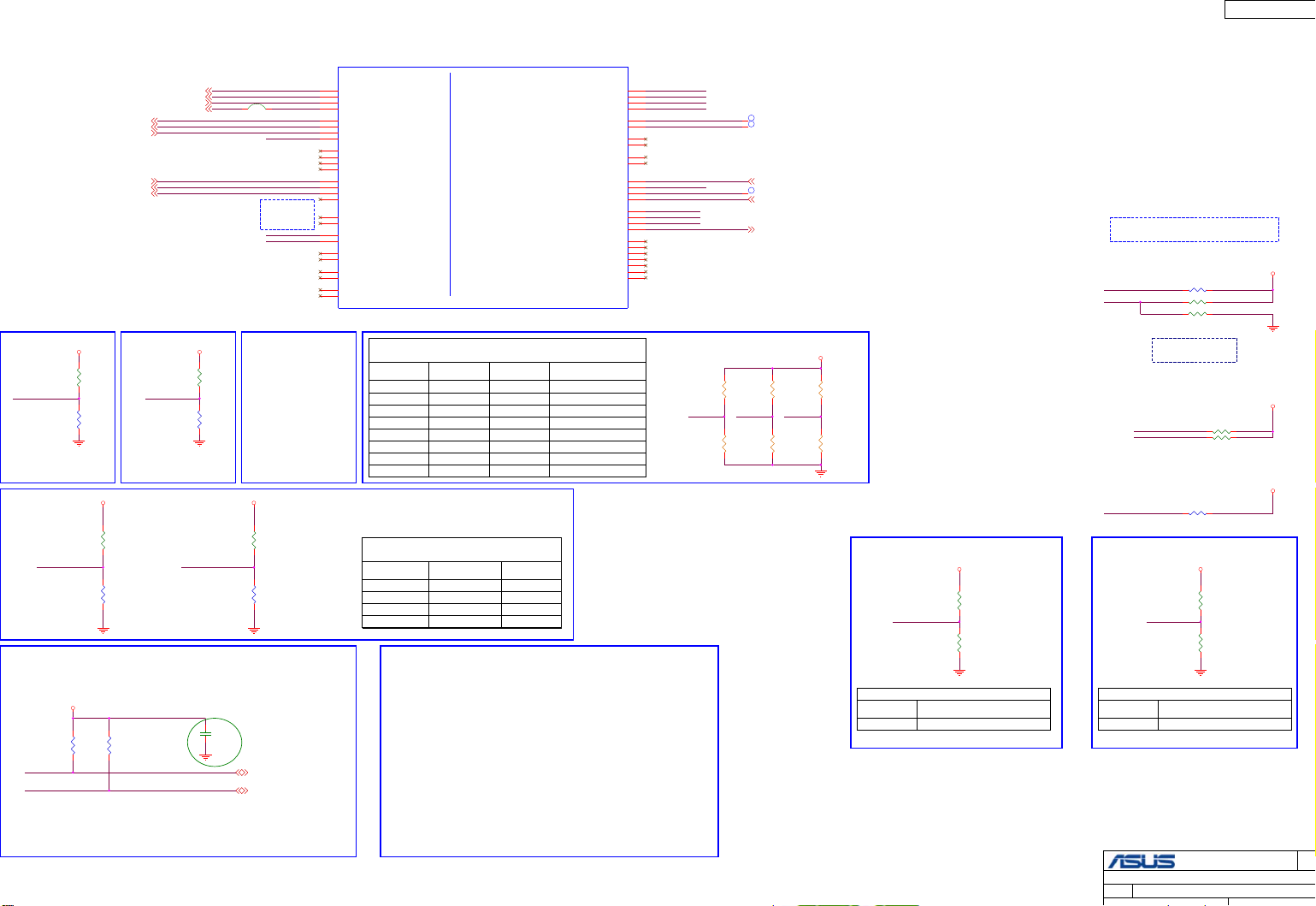

Asus X407UAR,X407UBR,X407UFR Schematic

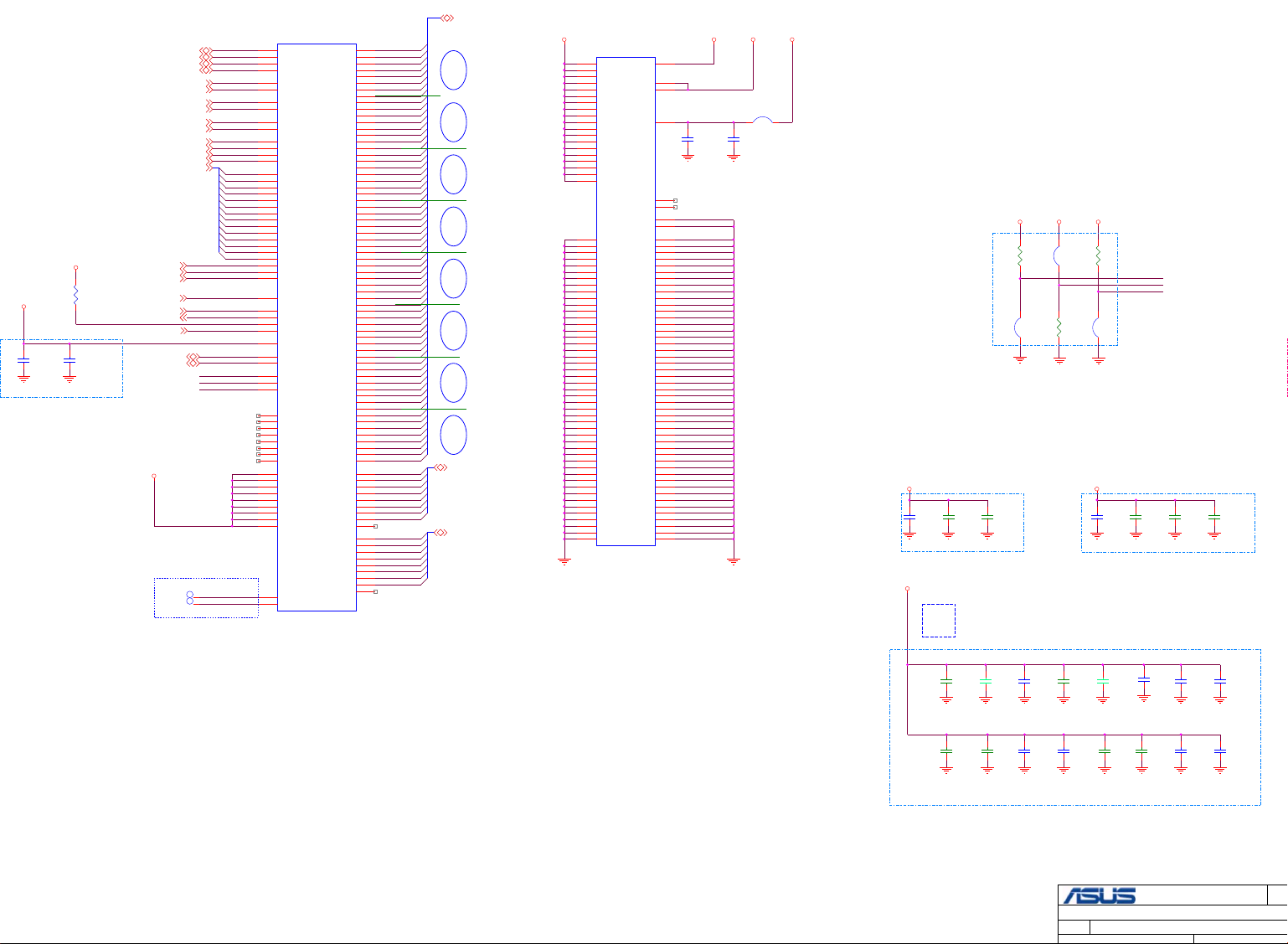

SYSTEM PAGE REF.

PAGE

001_Block Diagram

002_System Setting

003_CPU_DISPLAY

004_CPU_DDR4

005_CPU_LPC,SPI,SMB,CLINK

006_CPU_POEWR

008_CPU_MISC,JTAG

009_CPU_CFG,RSVD

010_CPU_POWER_CAP

016_DDR4_SO-DIMM_A_REV

017_DDR4_SO-DIMM_B_STD

018_DDR4_CA_DQ_VOLTAGE

019_DDR4

020_CPU_PCH_CSI2,EMMC

021_CPU_PCH_CGPIO, LPIO, MISC

022_CPU_PCH_AUDIO,SDIO,SDXC

023_CPU_PCH_PCIE,USB,SATA

024_CPU_PCH_CLOCK SIGNALS,RTC

025_CPU_PCH_SYS_POWER

026_CPU_PCH_POEWR,GND

027_CPU_PCH_POEWR,GND

028_PCH-SPI ROM,OTH /DEBUG PORT

029_Silego_Green_CLK_Gen

030_KBC_IT8995E/CX

031_KBC_KB,TP

032_RST_Reset Circuit

036_AUD-ALC3251

037_AUD-HEADPHONE JACK

038_AUD_SPEAKER

042_CardReader Connector

045_eDP Connector

048_HDMI-type D

050_FAN & SENSOR

051_NGFF(KEY-M)_SSD

052_USB 3.0 + 2.0 CONN

053_NGFF(KEY-E)_WLAN

057_DSG_Discharge

058_PRO_Protect

059_Power & WIFI & CAP LED&LID

060_DC_DC & BAT IN

064_

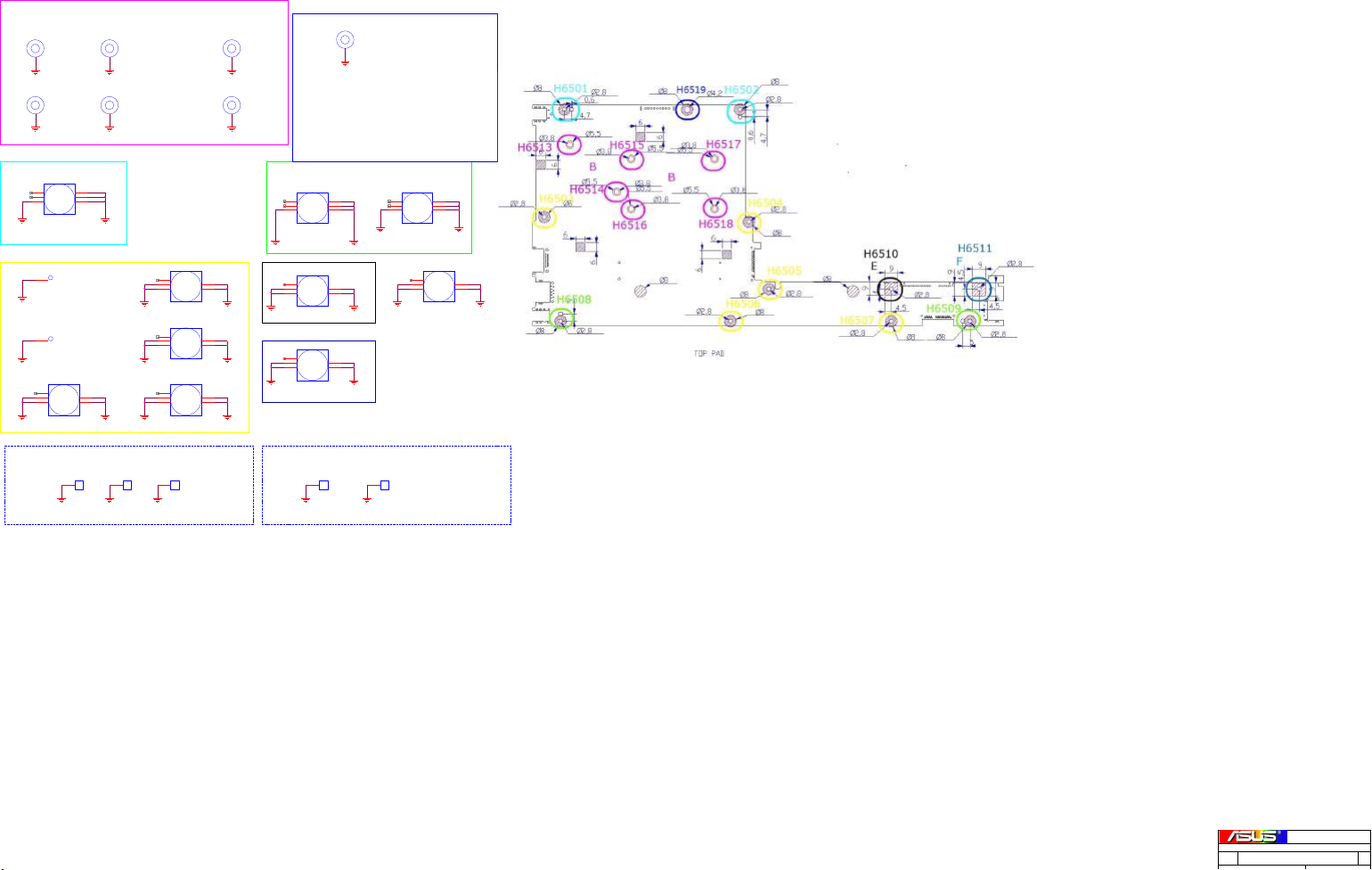

065_ME_Conn & Skew Hole

066_

067_

068_HDD COnnector

069_EMI

070_VGA_nVIDIA_N16V/S_PCIE

071_VGA_nVIDIA_N16V/S_FB-IF

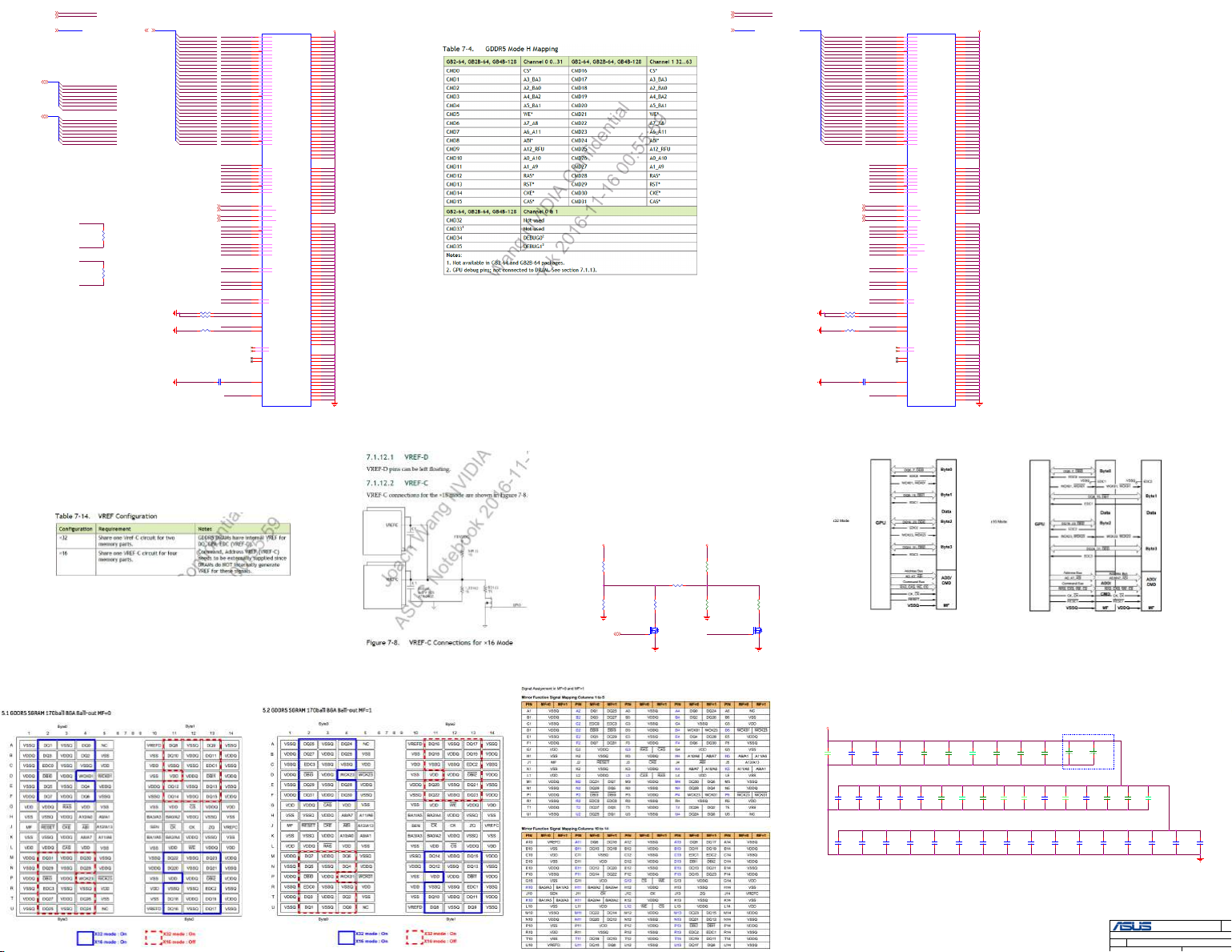

072_VGA_nVIDIA_N16V/S_FB-DDR3

073_VGA_nVIDIA_N16V/S_VDD

074_VGA_nVIDIA_N16V/S_DISPLAY

075_VGA_nVIDIA_N16V/S_ROM,XTAL

076_VGA_nVIDIA_N16V/S_GPIO

077_VGA_nVIDIA_N16V/S_POWER

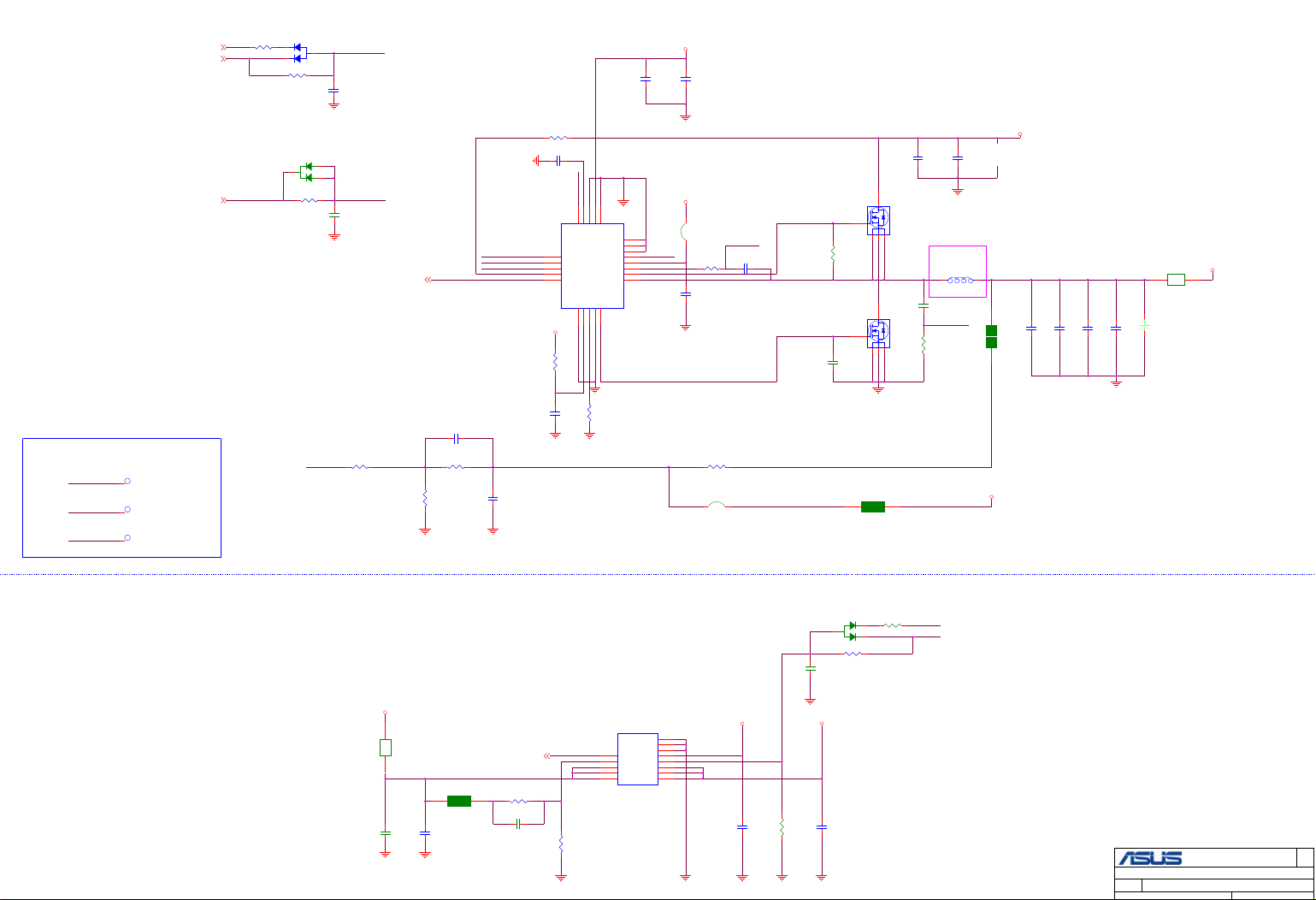

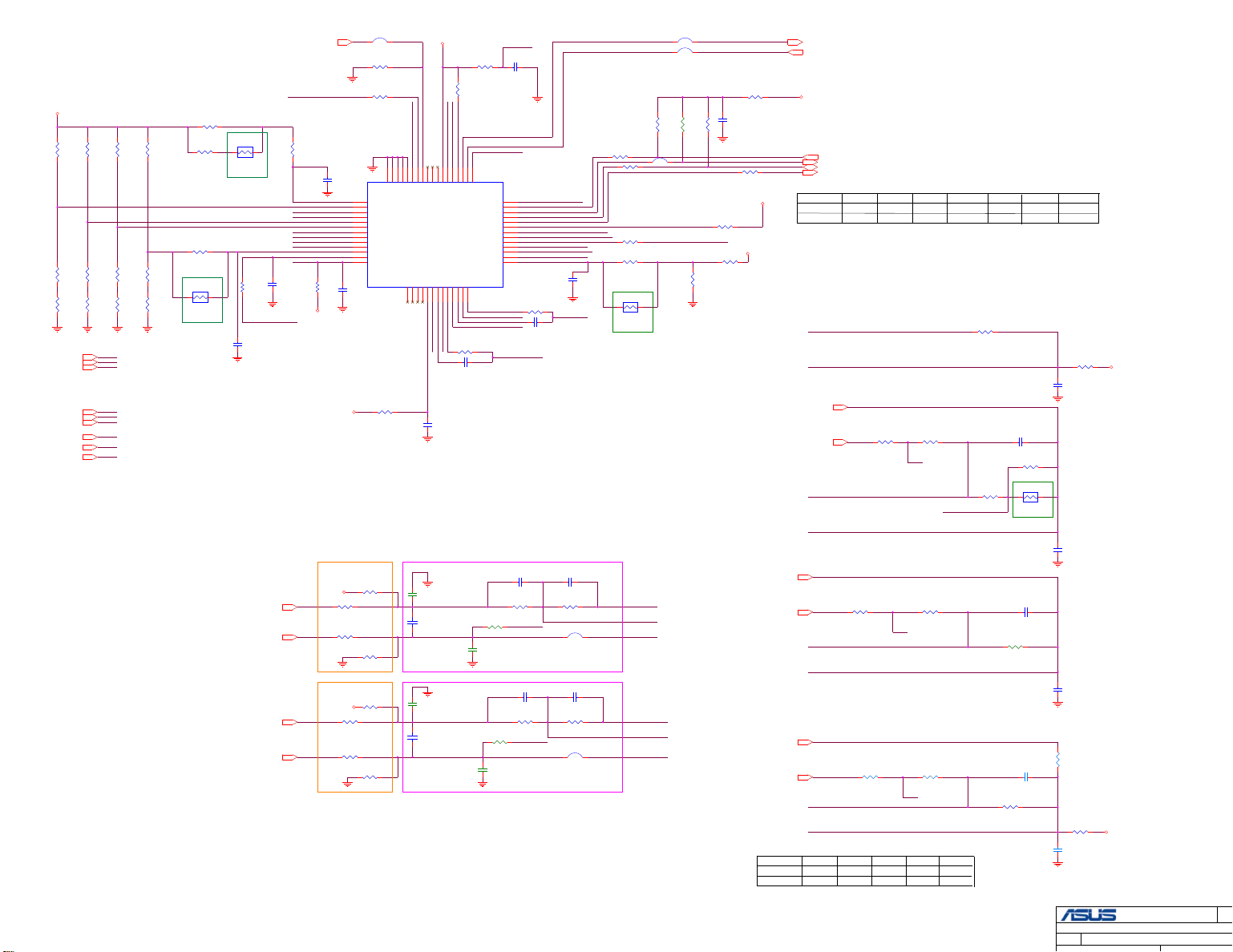

080_PW_IMVP8 (1) (RT3601BCGQW)

081_PW_IMVP8 (2) (RT3601BCGQW)

083_PW_+1.0VSUS / +1.8VSUS

084_PW_+1.2VS

086_PW_1.35V/+0.675VS (UP9011Q)

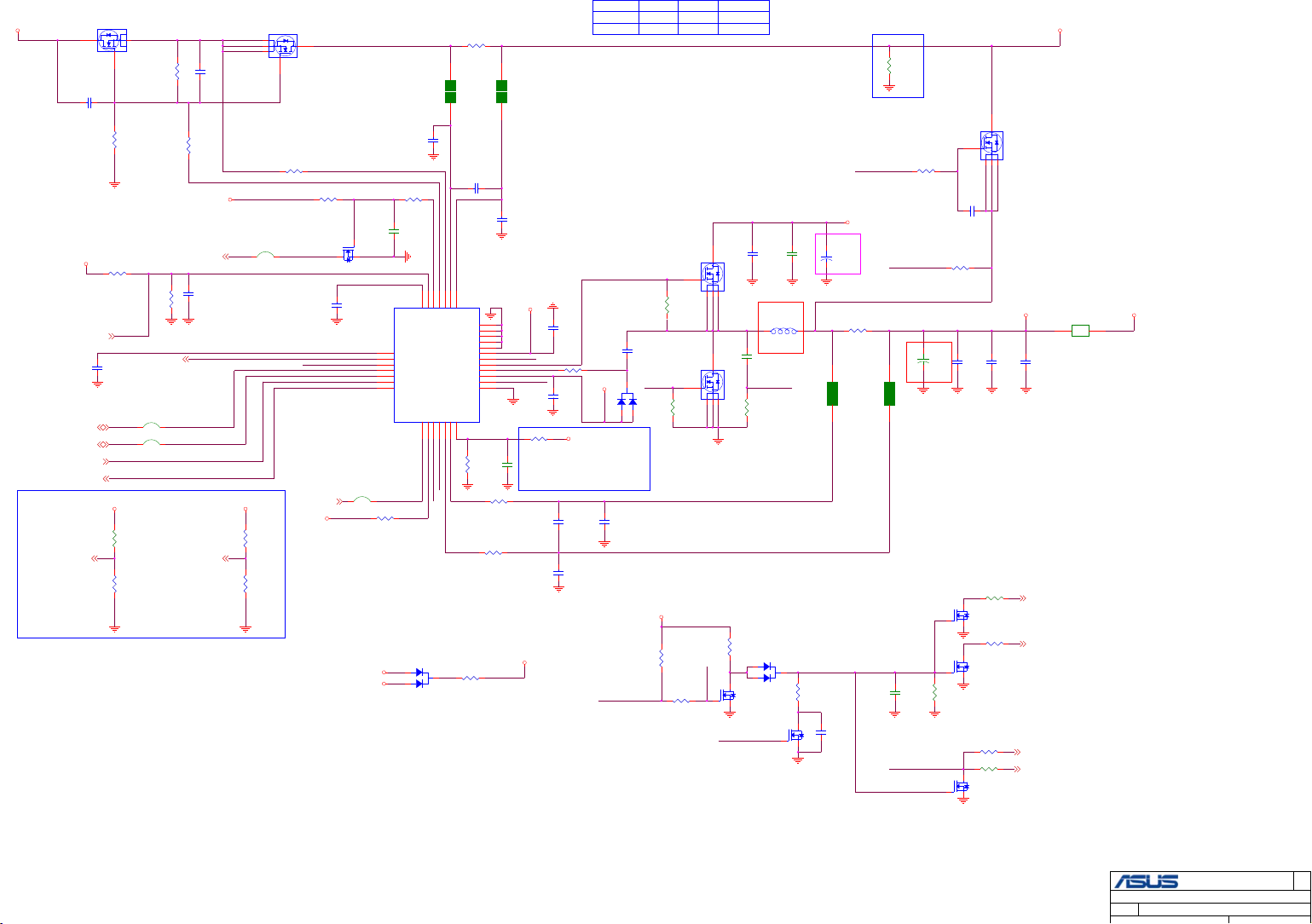

087_PW_+3VADSW/+5VSUS (RT8249C)

088_PW_LOAD SWITCH

089.PW_CHARGER(BQ24780)

090_PW_PROTECTION

091_PW_DGPU_2PHASE(RT8815A)

Content

X407UAR/UBR/UFR SCHEMATIC Revision 1.0

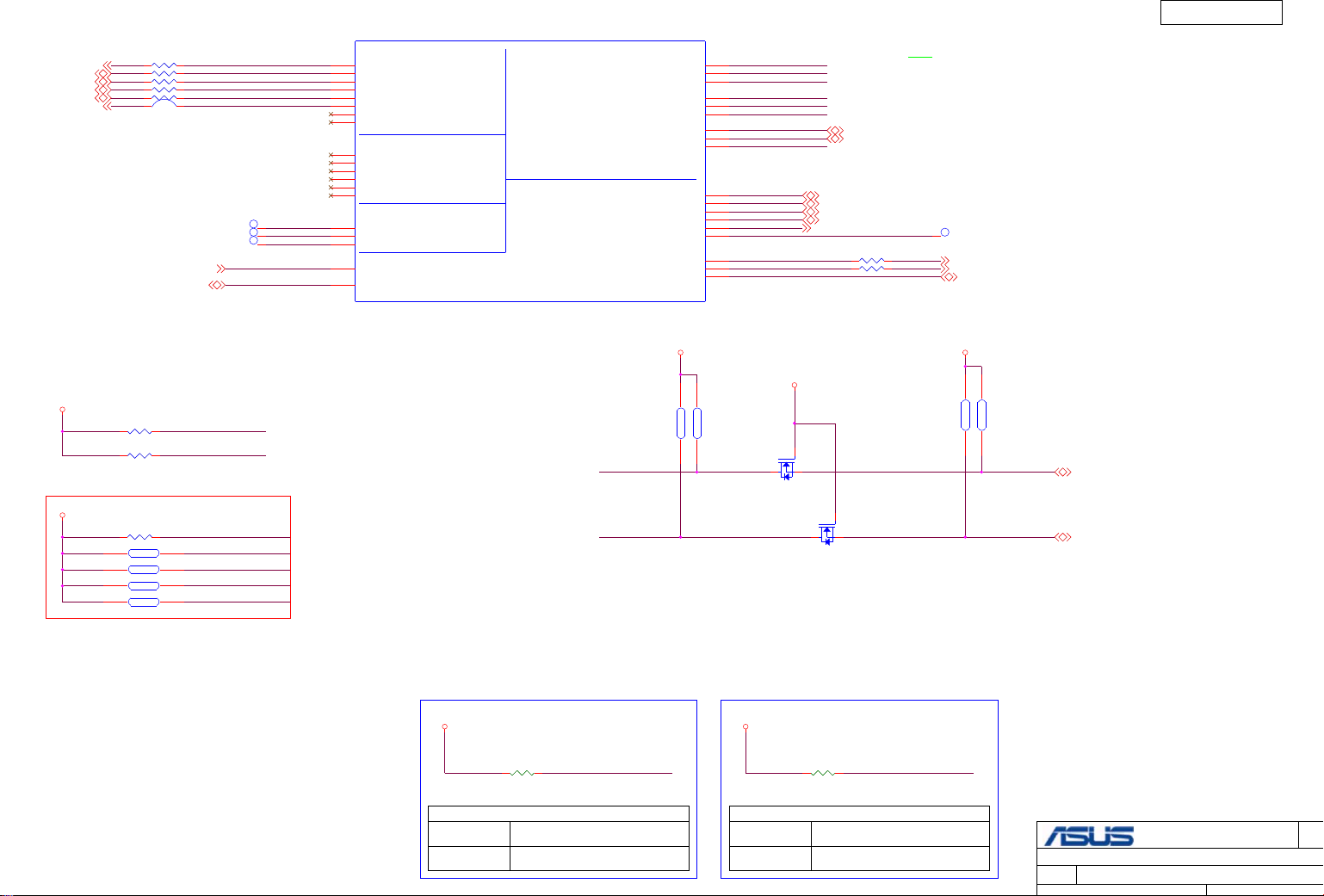

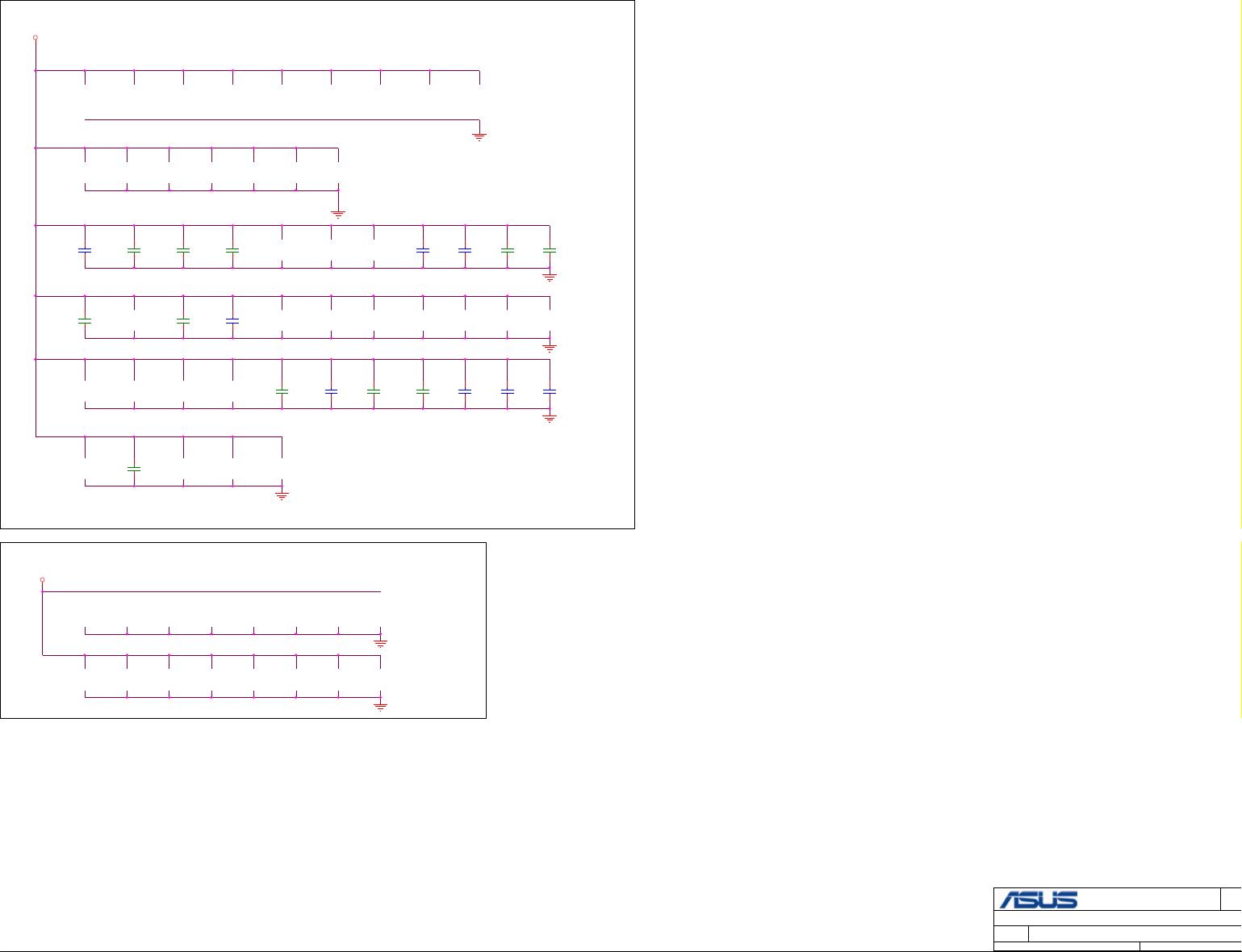

BLOCK DIAGRAM

(UAR:UMA)(45W) (Power BOM)

(UBR:DGPU = Nvidia N16V-GMR1, MX110)(65W) (Power BOM)

(UFR:DGPU = Nvidia N16S-GTR, MX130)(65W) (Power BOM)

Touchpad

Page 31

Keyboard

Page 31

Charger

Page 88

CPU

Thermal Sensor

Page 50

DIMM

Thermal Sensor

Page 14

INT. AMIC

Audio Jack

Page 37

Speaker L/R

I2C

SMB0

SMB1

Audio Codec

eDP Panel

HDMI type A

Debug Conn.

SPI

ALC3251

Page 36Page 38

Non Connected Standby

Page 45

Page 48

EC

IT8995E

Page 68

NGFF SSD

Page 51

DDI_2

SPI ROM

W25Q64FVSSIQ

HDD

eDP

DDI_2

DDI_1

SML1

I2C1

LPC

Page 28

Page 30

SPI

Page 28

HDA

SATA_0

Gen3

SATA_2

CPU

Kabylake R- U42

Page 3~9

PCH

8th Generation

Intel Processor Families

I/O for U/Y Platforms

MCP

Page 20~28

Azalia

SATA

Gen2

DDR4

2133MHz

DDR4

2133MHz

SMB

PCIE

USB 2.0

USB 3.0

DDR4 so-dimm

DDR4 so-dimm

PCIE_1~4

PCIE_9/10/11/12

PCIE_6

USB 2.0_8

USB 2.0_6

USB 2.0_2

USB 2.0_4

USB 2.0_1

USB 3.0_1

Page 13~15, 19

Nvidia

MX110/MX130

N16V-GMR1/N16S-GTR

VRAM x32

gDDR5 2GB

NGFF SSD

Page 51

WLAN + BT

Page 53

CMOS Camera

Page 45

USB 2.0 Standard Conn.

1 port

Page 52

Card Reader

Page 42

USB 3.0 Standard Conn.

1 ports

Page 52

Page 70~ 79

Power

+VCCGT

+VCCCORE

+VCCST

+1.0VSUS / +1.8VSUS

+0.95VSG

+VCCPRIM_CORE

+1.2V / +VTT / +2.5V

+3VADSW/+5VSUS

Load Switch

Charger

+VDDC

+VCCSA

Page 80 & 81

Page 83

Page 84

Page 86

Page 87

Page 88

Page 89

Page 91

CPU XDP

Page 7

Discharge Circuit

Reset Circuit

Page 57

Page 32

DC & BATT. Conn.

Skew Holes

Page 60

Page 65

PWM Fan

Page 50

BOM

Title :

Size

Custom

Date: Sheet

Wednesday, March 07, 2018

Block Diagram

Dept.:

Project Name

X407UA/UV

ASUSTeK COMPUTER INC.

Engineer:

Brian Chen

1

Rev

R1.0

102

of

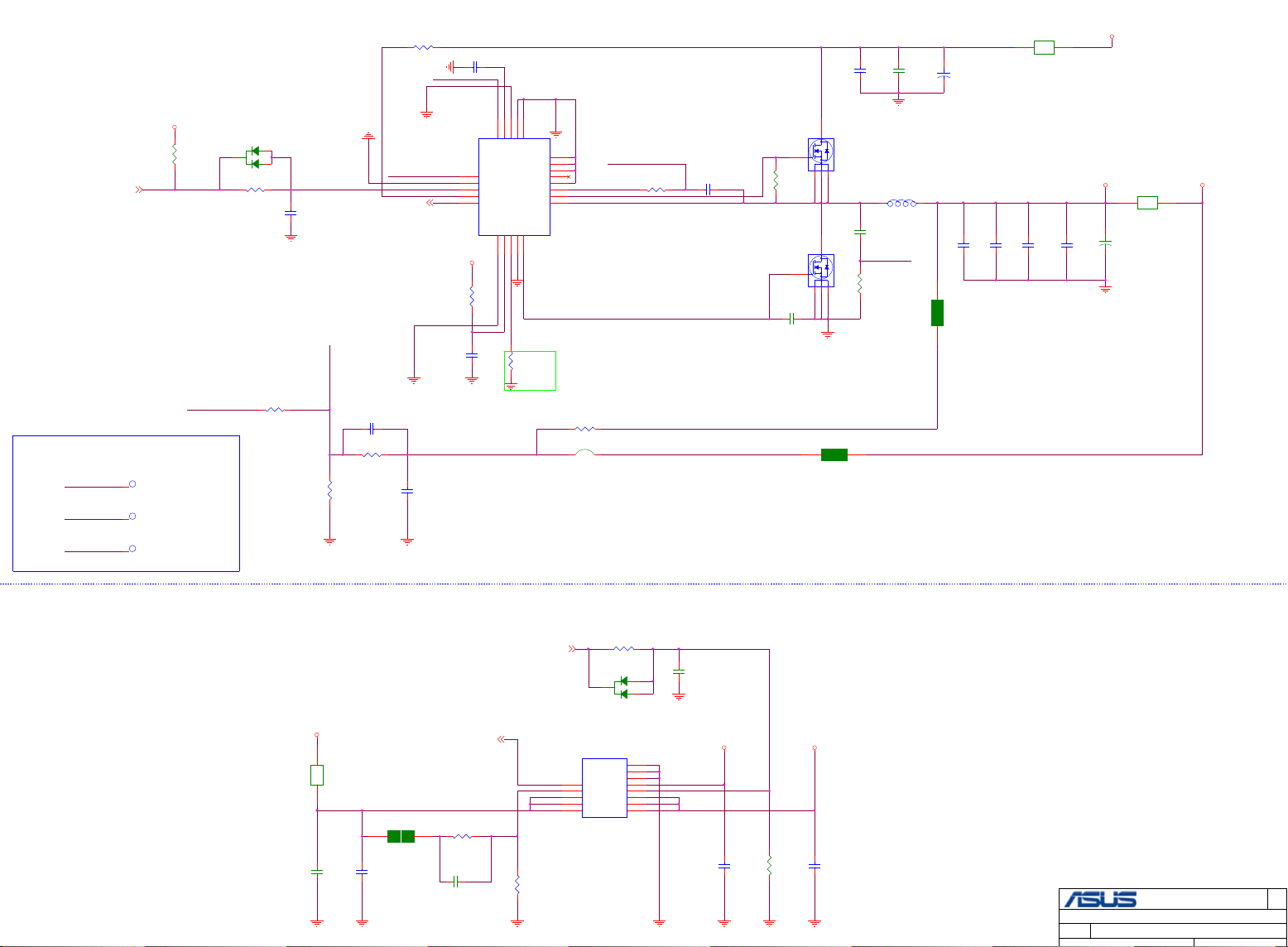

+3VSUS

PR8318

100KOhm

@

VSUS_ON31,58,84,89

PT830* 請放置 PU8302旁;並請放置Trace 上!

PT8303

P_1.0VSUS_HG_30

P_1.0VSUS_LX_30

P_1.0VSUS_LG_30

1

NB_TPC20T

PT8301

1

NB_TPC20T

PT8302

1

NB_TPC20T

12

P_1.0VSUS_LX_30

@

PD8301

BAT54CW

1

3

2

12

PR8303

30KOhm

PR8306

178KOhm

PR8306 close to PU8302

12

PC8313

0.1UF/25V

12

VFB=0.75V

GND GND

P_1.0VSUS_FB_10

12

PR8311

10KOhm

GND

1.0VSUS_PWRGD59

820PF/50V

PC8315

PR8309

3.48KOhm

12

f=420kHz

PR8304

620KOhm

1 2

P_1.0VSUS_FB_10

P_1.0VSUS_LDO_EN_10

P_1.0VSUS_EN_10

P_1.0VSUS_TON_10

GND

12

12

PC8301

0.1UF/25V

GND

P_1.0VSUS_VSENS_10

PU8302

GND

RT8248AGQW

+5VSUS_PWR

PR8321

2.2Ohm

5%

P_1.0VSUS_VSENS_10

P_1.0VSUS_VIN_S

PC8304

0.033UF/16V

12

VDDQ

6

FB

7

S3

8

S5

9

TON

10

PGOOD

VID12VDD13CS14PGND15LGATE

nbs_r0603_h24_000s

1 2

nbs_c0603_h37_000s

12

PC8307

1UF/25V

GND

1

2

3

4

5

GND1

GND4

VTTREF

VTTSNS

VTTGND

GND3

GND2

VTT

VLDOIN

BOOT

UGATE

PHASE

11

GND

P_1.0VSUS_CS_10

P_1.0VSUS_VDDP_30

12

RLIMIT = ILIMIT x RDS(ON) ×10 / 5μA

PR8310

OCP=14~16A

200KOhm

+1.0VSUS (RT8248AGQW)

23

22

21

20

19

18

17

P_1.0VSUS_BST_30

16

P_1.0VSUS_HG_30

P_1.0VSUS_LX_30

20160530 modify

PR8313

10Ohm

PSL8303

0402

@

12

21

P_1.0VSUS_BST_R_30

nbs_r0603_h24_000s

P_1.0VSUS_LG_30

P_1.0VSUS_LOSENS_10

P_1.0VSUS_RESENS_10

PR8315

0Ohm

1 2

5%

PC8302

0.1UF/25V

1 2

nbs_c0603_h37_000s

PR8302

10KOhm

@

1 2

PC8310

2200PF/50V

@

2

c0805,nb_c0805_h57_hdi

22UF/6.3V

PC8303

12

AC_BAT_SYS

+1.0VO

c0805,nb_c0805_h57_hdi

22UF/6.3V

12

+

6mm

Imax=7.45A

PJP8303

3MM_OPEN_5MIL

112

560UF/2.5V

PCE8302

@

+1.0VSUS

@

2

PJP8301

1MM_OPEN_5MIL

112

12

12

12

PCI8301

10UF/25V

nbs_c0805_h57_000s

GND

5

PQH8301

PEA16BA

D

4

G S

123

5

D

4

G S

123

@

12

GND

PSP8301

SHORT_PAD

@

PQL8302

12

PEA16BA

12

12

[HF]CYNTEC/PEUB063T-1R0MS

2 1

7x7x3mm

PC8317

1000PF/50V

nbs_c0603_h37_000s

P_1.0VSUS_SNB_S

PR8320

1Ohm

nbs_r1206_h30_000s

PL8302

1UH

Irat=12A

5%

PCI8303

10UF/25V

@

nbs_c0805_h57_000s

@

@

+

PCE8301

68UF/25V

h=6mm

480mil

c0805,nb_c0805_h57_hdi

c0805,nb_c0805_h57_hdi

22UF/6.3V

22UF/6.3V

PC8305

PCO8306

12

SHORT_PAD

@

12

PSP8302

PC8320

12

12

Imax=1A

+1.8VSUS

1

1

2

2

12

PJP8302

1MM_OPEN_5MIL

@

PC8311

10UF/6.3V

@

+1.8VSUSO

12

PC8309

10UF/6.3V

PSP8303

@

SHORT_PAD

1.8VSUS_PWRGD59

PR8314

12.7KOHM

1 2

12

PC8319

1000PF/50V

3A LDO REF=0.8V

+1.8VSUS [For PCH]

PU8301

APL5930CQBI-TRG

1

POK

2

FB

3

VOUT1

4

VOUT2

5

VOUT36VIN1

PR8312 0Ohm

PD8302

BAT54CW

3

13

GND3

12

GND2

11

GND1

10

VCNTL

9

EN

8

VIN3

7

VIN2

12

12

PC8318

@

1

2

0.1UF/16V

@

GND

+5VSUS

12

PC8316

1UF/16V

+3VA_DSW

12

12

PC8314

PR8307

10UF/6.3V

10KOhm

@

<Variant Name>

Title :

Size

C

Date: Sheet

Wednesday, March 07, 2018

Project Name

X540UVK

PW_+1.0VSUS / +1.8VSUS

Dept.:

NB Power Team

Engineer:

Andy

Rev

R0.1

102

of

84

VSUS_ON31,58,84,89

1.8VSUS_PWRGD

P_1.8VSUS_FB_10 P_1.8VSUS_EN_10

@

12

12

PR8308

10KOhm

BOM

Project Name

X540UVK

Title :

Size

A3

Date: Sheet

Wednesday, March 07, 2018

PW_+1.2VS

Dept.:

NB Power Team

Engineer:

Andy

85

of

Rev

R1.0

102

BOM

Project Name

X540UVK

Title :

Size

Custom

Date: Sheet

Wednesday, March 07, 2018

POWER_+VGFX_CORE

Dept.:

NB Power Team

Engineer:

Andy

86

of

Rev

R1.0

102

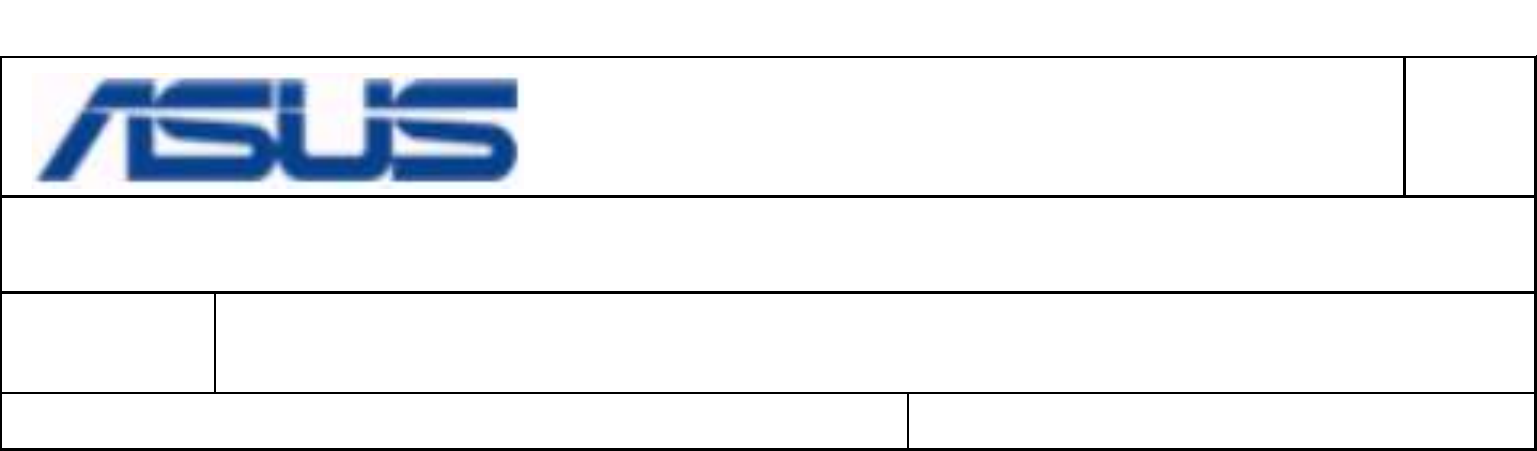

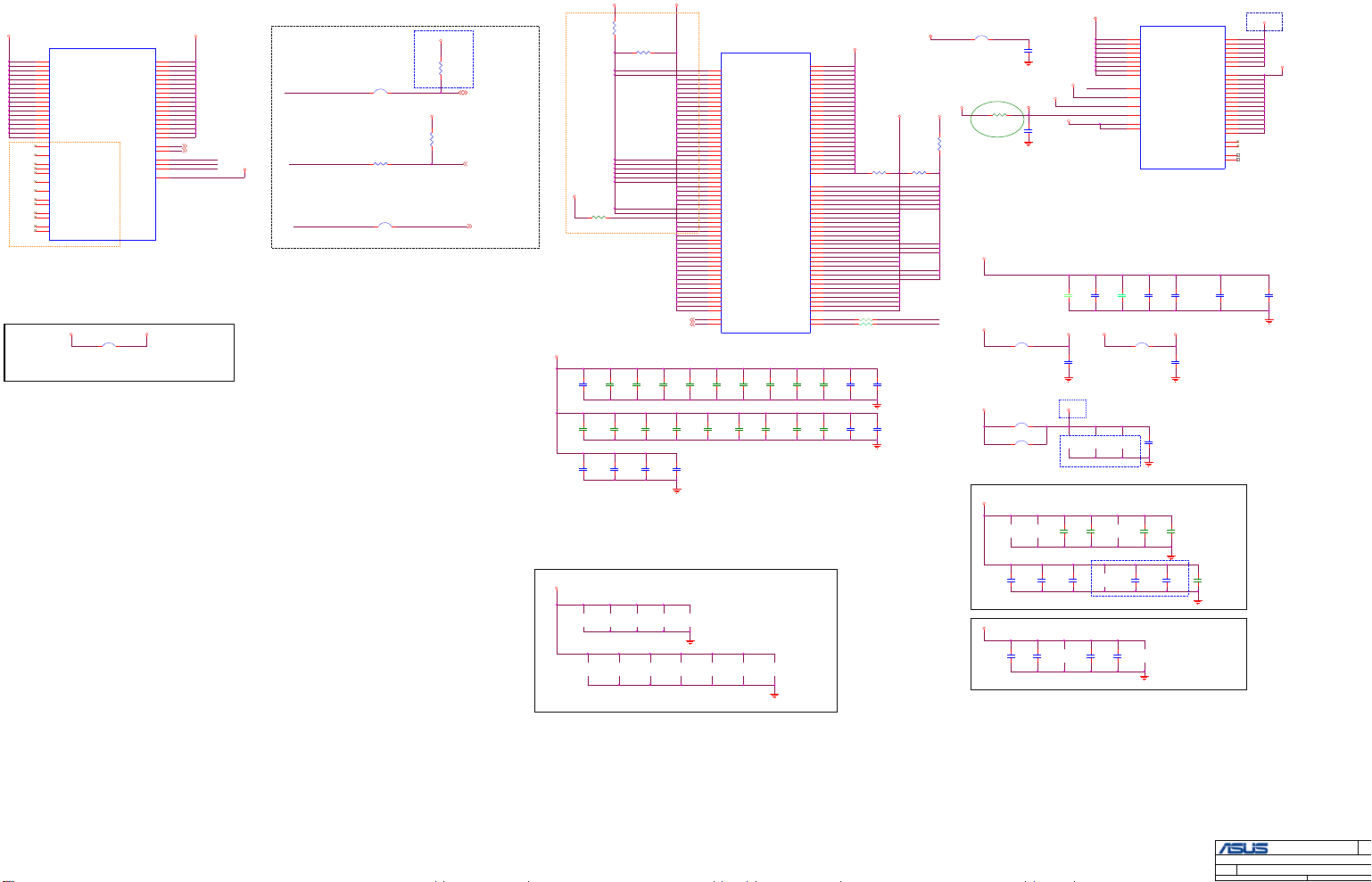

TOP VGA NUTTOP CPU NUT

www.teknisi-indonesia.com

H6515

CT189B180D150

GND GND

H6516

CT189B180D150

GND GND

H6501

1

NP_NC1

2

NP_NC2

3

GND2

2D_D110N_DO122X98N

GND GND

1

GND

20171013 Brian

H6503 change to s11705

for 螺絲孔徑2.8mm to 2.3mm.

1

20171013 Brian

H6505 change to s08180

GND GND GND

for 螺絲孔徑2.8mm to 2.3mm.

1

2

3

GND GND

H6517

CT189B180D150

H6518

CT189B180D150

6

GND5

5

GND4

4

GND3

H6503

C315D91

H6505

C315D91

H6507

NP_NC

5

GND1

GND4

4

GND2

GND3

C315D110N

H6504

1

NP_NC

2

5

GND1

GND4

3

4

GND2

GND3

C315D110N

GND GND

H6506

1

NP_NC

2

5

GND1

GND4

3

4

GND2

GND3

C315D110N

H6526

1

NP_NC

2

5

GND1

GND4

3

4

GND2

GND3

C315D110N

GND GND

H6513

CT189B180D150

GND

H6514

CT189B180D150

GND

20180117 Brian

Add H6526 for EMI DIMM-door.

BAT NUT

H6519

CT236CB195D165

nbs_nut_1p_418

13020-03890000

GND

20170814 Brian

H6519 footprint from nbs_nut_1p_414(TOP上件)

to nbs_nut_1p_418(BOT上件).

20171013 Brian

H6519 change 13020-03890000 to 13020-04030000

for 螺絲孔徑2.8mm to 2.3mm.

20171025 Brian

H6519 change to 13020-03890000.

H6508

1

6

NP_NC1

GND5

2

5

NP_NC2

GND4

3

4

GND2

GND3

2D_D110N_D122X98N

GND GND

H6510

1

NP_NC

2

5

GND1

GND4

3

4

GND2

GND3

ST354CB315D110N

GND GND

H6511

1

NP_NC

2

5

GND1

GND4

3

4

GND2

GND3

RT591X571CB315D110N

GND GND

H6509

1

6

NP_NC1

GND5

2

5

NP_NC2

GND4

3

4

GND2

GND3

2D_D110N_D122X98N

GND GND

H6520

1

NP_NC

2

GND1

GND4

3

GND2

GND3

C197D110N

GND GND

5

4

TOP GASKET (6*6)

1

SMD98X118

H6523

H6522

1

1

1

SMD98X118

H6521

1

1

SMD98X118

GND GND GND GND GND

TOP/BOT VRAM GASKET (3*2)

H6524

1

SMD118X118

1

1

SMD118X118

H6525

1

<Variant Name>

ASUSTeK COMPUTER INC. NB4

Size Project Name

D

Date: Sheet

Title :

Engineer:

X507UA/UV

65_ME_Conn & Skew Hole

Bull Tsai

66 102Wednesday, March 07, 2018

Rev

R1.0

of

PT860* 請放置 PU8600旁;並請放置Trace 上!

PT8601

1

P_1V2_HG_30

NB_TPC20T

PT8602

1

P_1V2_LX_30

NB_TPC20T

PT8603

1

P_1V2_LG_30

NB_TPC20T

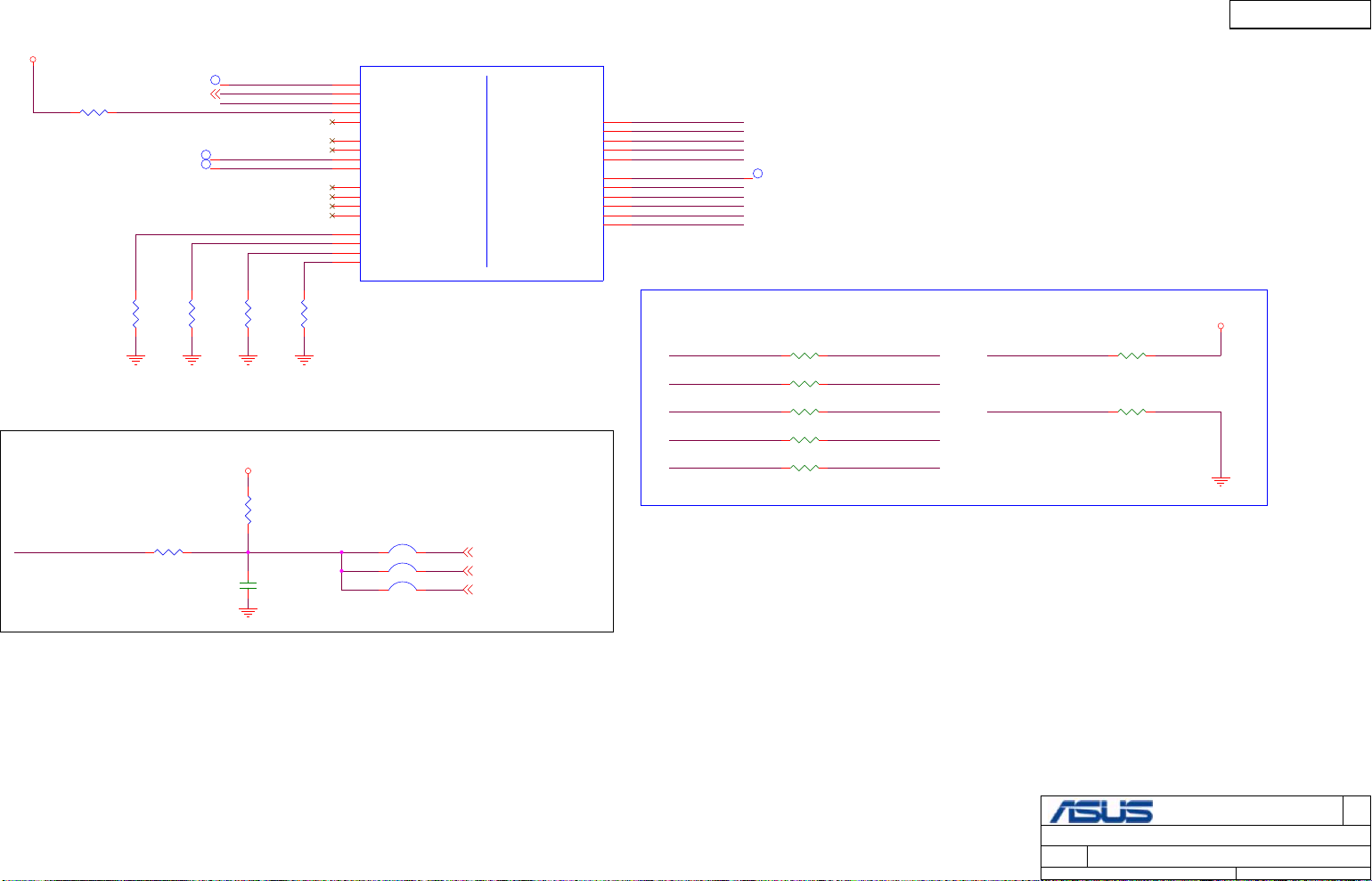

+1.2V / +VTT / +2.5V[For Memory]

PD8600

PR8630

BAT54AW

0Ohm

PM_SUSC#26,31

1.2V_ON31

DDR_PG_CTRL5

12

1

2

1 2

PR8613

10KOhm

3

PD8601

BAT54CW

PR8616

0Ohm

3

P_1V2_EN_10

12

PC8613

0.22UF/10V

f=420kHz

PR8607

620KOhm

2

1

12

@

P_1V2_LDO_EN_10

12

PC8614

0.1UF/25V

@

1 2

GND

PU8600

RT8248AGQW

P_1V2_FB_10

P_1V2_LDO_EN_10

P_1V2_EN_10

1.2V_PWRGD59

P_1V2_TON_10

PC8615

0.1UF/25V

10

AC_BAT_SYS

12

P_1V2_VSENS_10

P_1V2_VTTREF_10

GND

1

2

3

4

5

GND1

VDDQ

GND4

VTTREF

VTTSNS

VTTGND

GND3

FB

S3

S5

TON

PGOOD

VID12VDD13CS14PGND15LGATE

11

VLDOIN

GND2

VTT

BOOT

UGATE

PHASE

6

7

8

9

+5VSUS

12

PR8601

2.2Ohm

P_1V2_LX_30

PR8621

178KOhm

VFB=0.75V

12

P_1V2_FB_10

PC8612

820PF/50V

12

PR8611

6.2KOhm

12

PR8612

10KOhm

P_1V2_VSENS_10

12

GND GND

nbs_r0603_h24_000s

PC8602

1UF/25V

nbs_c0603_h37_000s

12

PC8611

0.1UF/25V

P_1V2_CS_10

P_1V2_LG_30

P_1V2_VDD_30

5%

GND GND

12

12

PR8603

402KOhm

GND

GND

+VTT

12

12

PC8601

PC8600

10UF/6.3V

nbs_c0805_h37_000s

23

22

21

20

19

+VTT

18

P_1V2_LDOIN_30

17

P_1V2_BST_30

16

P_1V2_HG_30

P_1V2_LX_30

RLIMIT = ILIMIT x RDS(ON) ×10 / 5μA

OCP=13A

10UF/6.3V

nbs_c0805_h37_000s

+1.2V

@

21

PSL8601

0603

nbs_r0603_h24_000s

1 2

12

PC8604

1UF/25V

nbs_c0603_h37_000s

GND

PR8606

0Ohm

PR8609

10Ohm

PSL8602

@

0402

P_1V2_BST_R_30

PC8603

5%

0.1UF/25V

1 2

nbs_c0603_h37_000s

12

21

P_1V2_LOSENS_10

AC_BAT_SYS

12

12

PCI8601

PCI8603

10UF/25V

10UF/25V

GND

20160316

PL8600

1UH

Irat=12A

2 1

7x7x3mm

[HE]CYNTEC/PEUB063T-1R0MS

12

PC8609

1000PF/50V

nbs_c0603_h37_000s

@

P_1V2_SNB_S

12

PR8608

5%

1Ohm

nbs_r1206_h30_000s

@

N/A

nbs_c0805_h57_000s

P_1V2_VO_S

12

+1.2V

h=6mm

Imax= 10.06A

OCP= 13A

+1.2V

PJP8601

12

c0805,nb_c0805_h57_hdi

22UF/6.3V

12

PC8610

112

2

@

3MM_SHORT_PIN

@

+

PCE8601

330UF/2V

480mil

c0805,nb_c0805_h57_hdi

c0805,nb_c0805_h57_hdi

22UF/6.3V

PCO8606

SHORT_PAD

12

12

PSP8600

@

PC8605

22UF/6.3V

12

c0805,nb_c0805_h57_hdi

22UF/6.3V

PC8607

nbs_c0805_h57_000s

5

PQH8601

QM1830M3

D

4

G S

123

12

PR8604

10KOhm

@

5

PQL8602

QM1830M3

D

4

G S

123

12

PC8608

1000PF/50V

@

PSP8601

@

SHORT_PAD

1 2

Imax= 3A

OCP= 4.5A

+2.5V

2

PJP8602

2

1MM_SHORT_PIN

1

1

12

PC8619

10UF/6.3V

@

nbs_c0805_h57_000s

@

+2.5VO

12

PC8616

10UF/6.3V

nbs_c0805_h57_000s

PSP8602

@

SHORT_PAD

12

3A LDO REF=0.8V

2.5V_PWRGD59

PR8623

21.5KOhm

1 2

PC8606

1000PF/50V

+2.5V

PU8601

APL5930CQBI-TRG

1

POK

2

2.5V_PWRGD

P_2.5V_FB_10 P_2.5V_RCEN_10

@

12

12

PR8602

10KOhm

3

4

5

FB

VOUT1

VOUT2

VOUT36VIN1

PD8602

@

PR8615

BAT54AW

0Ohm @

1

3

12

PR8614

PC8620

10KOhm

0.1UF/25V

@

13

GND3

12

GND2

11

GND1

10

VCNTL

9

EN

8

VIN3

7

VIN2

+5VSUS

12

PC8617

1UF/16V

+3VA_DSW

12

12

PC8618

PR8622

10UF/6.3V

10KOhm

@

12

PM_SUSC#

2

1.2V_ON

12

<Core Design>

Title :

Size

A2

Date: Sheet

Wednesday, March 07, 2018

PW_+1.2V/+VTT/+2.5V

Dept.:

NB Power team

Project Name

X540UVK

Engineer:

Andy

Rev

R0.1

102

of

87

+3VA_DSW / +5VSUS [System Power]

www.teknisi-indonesia.com

AC_BAT_SYS

+5VSUS

+5VSUS_PWR

21

0603

PSL8705 is close to PJP8702 0511

PSL8705 @

Imax =9.81A

PJP8702

@

3MM_SHORT_PIN

112

2

PC8723

22UF/6.3V

@

PJP8701

1MM_OPEN_5MIL

112

2

12

PCE8703

220UF/6.3V

V-Chip

h=4.5mm

20160415_Modify 20170517_Modify

@

P_5VSUS_VIN_S

12

PR8701

6.49KOhm

PL8702

3.3UH

Irat=6.5A

7x7x3mm

PC8715

150PF/50V

@

12

PCI8701

10UF/25V

nbs_c0805_h57_000s

PQH8701

QM1830M3

21

PQL8702

QM1830M3

P_5VSUS_FB_10

5

D

4

GS

123

5

D

4

GS

123

1 2

P_5VSUS_LG_30

PC8716

@

2200PF/50V

PCE8702

68UF/25V

h=6mm

[HF]CYNTEC/PEUB063T-3R3MS

+5VSUSO

12

+

P_5VSUS_VSENS_10

PC8709

0.1UF/25V

12

+

SHORT_PAD

12

PSP8705

@

12

12

PR8703

10KOhm

12

+5VSUS IOCP=9.2A

PR8702

1 2

30KOHM

PR8706

1 2

30KOHM

+3VA_DSW IOCP=9.2A

P_5VSUS_HG_30

P_5VSUS_LX_30

P_5VSUS_CS_10

P_5VSUS_FB_10

+3VAO

P_3VADSW_FB_10

P_3VADSW_CS_10

3VADSW_ON31

5VSUS_ON31,58

12

PC8702

4.7UF/6.3V

+3VAO

P_3VADSW_VIN_S

5

D

123

5

D

123

PQH8704

PQL8703

12

QM1830M3

QM1830M3

PT8713

1

P_3VADSW_HG_30

PT8714

1

P_3VADSW_LX_30

PT8715

1

P_3VADSW_LG_30

12

PCI8705

10UF/25V

nbs_c0603_h39_000s

[HF]CYNTEC/PEUB063T-3R3MS

PL8701

3.3UH

Irat=6.5A

7x7x3mm

12

PR8727

680KOhm

P_3VADSW_FBMLCC_10

PC8708

0.01UF/50V

PJP8703

1MM_OPEN_5MIL

112

PCI8707

10UF/25V

21

12

@

2

20160401 Modify

12

12

12

PC8706

0.1UF/25V

P_5VSUS_BST_R

12

PR8705

5%

0Ohm

nbs_r0603_h24_000s

P_5VSUS_HG_30

P_5VSUS_LX_30

P_12VSUS_SKIPSEL_20

P_5VSUS_EN_10

P_5VSUS_BST_30

PU8701

RT8249CGQW

16

17

18

19

20

21

EN1

UG1

GND122GND223GND3

1

CS1

2

FB1

3

LDO3

4

FB2

5

CS2

EN27PGOOD8PHASE29BOOT210UG2

6

P_3VADSW_EN_10

PSL8702

SHORT_LAND

0402

PSL8703

SHORT_LAND

0402

PSL8704

SHORT_LAND

0603

BOOT1

LG1

PHASE1

SKIPSEL

BYP1

LDO5

VIN

LG2

P_3VADSW_HG_30

P_3VADSW_LX_30

P_3VADSW_BST_30

PR8708

5%

0Ohm

nbs_r0603_h24_000s

1 2

P_3VADSW_BST_R

12

PC8714

0.1UF/25V

3VA_DSW_PWRGD 26,31,59

@

21

P_3VADSW_EN_10

@

21

P_5VSUS_EN_10

@

21

15

14

13

12

11

+3VA

P_5VSUS_LG_30

+5VSUSO

+5VAO

P_3VADSW_LG_30

12

PC8705

4.7UF/6.3V

P_3VADSW_HG_30

P_3VADSW_LX_30

P_3VADSW_LG_30

AC_BAT_SYS

P_3VADSW_FB_10

1 2

PC8703

2200PF/50V

4

4

@

G S

G S

PT8716

PT8717

PT8718

Close to PU8701

+3VADSWO

PC8707

390PF/50V

SHORT_PAD

12

PSP8706

@

P_3VADSW_VSENS_10

12

PC8721

PR8704

150PF/50V

6.8KOhm

@

12

PR8707

10KOhm

1

1

1

AC_BAT_SYS

P_5VSUS_HG_30

P_5VSUS_LX_30

P_5VSUS_LG_30

12

PCO8711

22UF/6.3V

12

PC8710

0.1UF/25V

Imax = 9.5A

PJP8704

@

3MM_SHORT_PIN

112

2

12

12

PC8725

22UF/6.3V

PC8726

22UF/6.3V

+3VA_DSW

12

PC8727

22UF/6.3V

@

PSL8701

+12VSUS

12

@

21

0603

P_12VSUS_CP4_20 P_12VSUS_CP3_20

12

PC8724

0.1UF/25V

nbs_c0603_h37_000s

P_12VSUS_CP1_20P_3VADSW_LG_30 +5VSUSO

PC8718

0.1UF/25V

12

P_12VSUS_CP2_20

PC8701

0.1UF/25V

請 check 整份線路 +12VSUS total 並聯對地電阻不得小於10kOhm

6

5

BAT54SDW

PD8701

Adaptor Mode (IMVP8)

CS S4

1

1

1

1

1

1

TPC28T

TPC28T

TPC28T

S3

-

1

-

1

-

1

-

1

-

1

-

1

0

-

PT8708

1

@

+3VADSWO

PT8701

+3VA_DSW

PT8706

1

@

PT8702

1

@

+5VSUS

PT8709

+5VAO

1

2

34

12

PC8722

0.1UF/25V

nbs_c0603_h37_000s

PS_ON 1

3VADSW_ON

3VSUS_ON

5VSUS_ON

1.35V_ON

SUSC_EC#

SUSB_EC#

PT8704

+12VSUS

PT8712

GND

PT8703

GND GND

S5 S5 with USB Charger+S0

DS3

-

-

1

-

1

-

0

-

1

-

0

-

0

-

0

TPC28T

1

@

+3VAO

TPC28T

1

@

+3VA

TPC28T

1

@

GND+5VSUSO

TPC28T

1

@

TPC28T

1

@

1

-

1

0

-

-

1

0

-

-

0

-

PT8705

PT8707

PT8711

PT8710

TPC28T

TPC28T

TPC28T

TPC28T

0

1

@

1

@

1

@

1

@

3VADSW_ON

3VSUS_ON

1.35V_ON

SUSC_EC#

SUSB_EC#

BOM

Title :

Size

Custom

Date: Sheet

Wednesday, March 07, 2018

Battery Mode (IMVP8)

1

PS_ON

1

1

1

1

1

1

PW_+3VA_DSW/+5VSUS

Dept.:

NB Power Team

CS

S3

-

-

-

-5VSUS_ON

-

-

-

Project Name

X540UVK

-

-

-

-

-

-

DS3

1

1

0

110

0

0

Engineer:

S5 S5 with USB Charger+S0

S4

0

0

0

0

0

0

0

0

0

0

0

0

0

Andy

88

1-

0

0

1

0

0

0

Rev

R0.1

102

of

2016/11/18 X542UA_R1.0 #84, Modify to GDDR5

FBA_CLK072

FBA_CLK0#72

FBA_CMD[0:15]72

FBA_DBI[7..0]72

FBA_EDC[7..0]72

FBA Partition Memory (1 of 2)

FBA_D[0:63]72

FBA_D[0:63]

20161215 Byte SWAP

20161216 bitd SWAP

FBA_D7

FBA_D6

FBA_D5

FBA_D4

FBA_D3

FBA_D2

FBA_D1

FBA_D0

FBA_D15

FBA_D14

FBA_D13

FBA_D12

FBA_D11

GND

GND

MF=0 non-Mirror

FBA_D10

FBA_D9

FBA_D8

FBA_D23

FBA_D22

FBA_D21

FBA_D20

FBA_D19

FBA_D18

FBA_D17

FBA_D16

FBA_D31

FBA_D30

FBA_D29

FBA_D28

FBA_D27

FBA_D26

FBA_D25

FBA_D24

FBA_WCK2372

FBA_WCK23#72

FBA_WCK0172

FBA_WCK01#72

R7202 121Ohm1% /VGA

R7203 1KOhm/VGA

R7204 1KOhm/VGA

20161215 SWAP

20161215 SWAP

1 2

1 2

12

FBA_DBI0

FBA_DBI1

FBA_DBI2

FBA_DBI3

FBA_DBI4

FBA_DBI5

FBA_DBI6

FBA_DBI7

FBA_EDC0

FBA_EDC1

FBA_EDC2

FBA_EDC3

FBA_EDC4

FBA_EDC5

FBA_EDC6

FBA_EDC7

FBA_CLK0

R7239

80.6Ohm

/VGA

1%

1 2

FBA_CLK0#

FBA_CLK1

R7240

80.6Ohm

/VGA

1%

1 2

FBA_CLK1#

X507 remove C7202/C7203

GND

C7204 820PF/50V

MF=0 non-Mirror

U7201

M2

DQ7/DQ31

M4

FBA_D5

DQ6/DQ30

N2

FBA_D0

DQ5/DQ29

N4

FBA_D2

DQ4/DQ28

T2

FBA_D4

DQ3/DQ27

T4

FBA_D7

DQ2/DQ26

U2

FBA_D3

DQ1/DQ25

U4

FBA_D6

DQ0/DQ24

M13

FBA_D1

DQ15/DQ23

M11

FBA_D12

DQ14/DQ22

N13

FBA_D8

DQ13/DQ21

N11

FBA_D15

DQ12/DQ20

T13

FBA_D9

DQ11/DQ19

T11

FBA_D13

DQ10/DQ18

U13

FBA_D14

DQ9/DQ17

U11

FBA_D11

DQ8/DQ16

F13

FBA_D10

DQ23/DQ15

F11

FBA_D18

DQ22/DQ14

E13

FBA_D20

DQ21/DQ13

E11

FBA_D19

DQ20/DQ12

B13

FBA_D23

DQ19/DQ11

B11

FBA_D16

DQ18/DQ10

A13

FBA_D21

DQ17/DQ9

A11

FBA_D17

DQ16/DQ8

F2

FBA_D22

DQ31/DQ7

F4

FBA_D24

DQ30/DQ6

E2

FBA_D26

DQ29/DQ5

E4

FBA_D27

DQ28/DQ4

B2

FBA_D25

DQ27/DQ3

B4

FBA_D31

DQ26/DQ2

A2

FBA_D30

DQ25/DQ1

A4

FBA_D28

DQ24/DQ0

FBA_D29

J5

A12/A13

K4

FBA_CMD9

A0/A10/A8/A7

K5

FBA_CMD6

A1/A9/A11/A6

K10

FBA_CMD7

A3/BA3/A5/BA1

K11

FBA_CMD4

A2/BA0/A4/BA2

H10

FBA_CMD3

A5/BA1/A3/BA3

H11

FBA_CMD1

A4/BA2/A2/BA0

H5

FBA_CMD2

A6/A11/A1/A9

H4

FBA_CMD11

A7/A8/A0/A10

FBA_CMD10

D4

WCK23/WCK01

D5

WCK23#/WCK01#

P4

WCK01/WCK23

P5

WCK01#/WCK23#

R2

EDC0/EDC3

R13

FBA_EDC0

EDC1/EDC2

C13

FBA_EDC1

EDC2/EDC1

C2

FBA_EDC2

EDC3/EDC0

FBA_EDC3

P2

DBI0#/DBI3#

P13

FBA_DBI0

DBI1#/DBI2#

D13

FBA_DBI1

DBI2#/DBI1#

D2

FBA_DBI2

DBI3#/DBI0#

FBA_DBI3

G3

CAS#/RAS#

L3

FBA_CMD12

RAS#/CAS#

FBA_CMD15

J3

CKE#

J11

FBA_CMD14

CK#

J12

FBA_CLK0#

CK

FBA_CLK0

G12

WE#/CS#

L12

FBA_CMD0

CS#/WE#

FBA_CMD5

J13

ZQ

J10

FBA_ZQ1

SEN

FBA_SEN1

J2

RESET#

J1

FBA_CMD13

MF

FBA_MF1

A5

Vpp/NC

U5

Vpp/NC1

A10

VREFD1

U10

VREFD2

1 2

J14

VREFC

FBA_VREFC0

/VGA

J4

ABI#

FBA_CMD8

K4G41325FE-HC28

/VGA

+FBVDDQ

B1

VDDQ1

B3

VDDQ2

B12

VDDQ3

B14

VDDQ4

D1

VDDQ5

D3

VDDQ6

D12

VDDQ7

D14

VDDQ8

E5

VDDQ9

E10

VDDQ10

F1

VDDQ11

F3

VDDQ12

F12

VDDQ13

F14

VDDQ14

G2

VDDQ15

G13

VDDQ16

H3

VDDQ17

H12

VDDQ18

K3

VDDQ19

K12

VDDQ20

L2

VDDQ21

L13

VDDQ22

M1

VDDQ23

M3

VDDQ24

M12

VDDQ25

M14

VDDQ26

N5

VDDQ27

N10

VDDQ28

P1

VDDQ29

P3

VDDQ30

P12

VDDQ31

P14

VDDQ32

T1

VDDQ33

T3

VDDQ34

T12

VDDQ35

T14

VDDQ36

C5

VDD1

C10

VDD2

D11

VDD3

G1

VDD4

G4

VDD5

G11

VDD6

G14

VDD7

L1

VDD8

L4

VDD9

L11

VDD10

L14

VDD11

P11

VDD12

R5

VDD13

R10

VDD14

A1

VSSQ1

A3

VSSQ2

A12

VSSQ3

A14

VSSQ4

C1

VSSQ5

C3

VSSQ6

C4

VSSQ7

C11

VSSQ8

C12

VSSQ9

C14

VSSQ10

E1

VSSQ11

E3

VSSQ12

E12

VSSQ13

E14

VSSQ14

F5

VSSQ15

F10

VSSQ16

H2

VSSQ17

H13

VSSQ18

K2

VSSQ19

K13

VSSQ20

M5

VSSQ21

M10

VSSQ22

N1

VSSQ23

N3

VSSQ24

N12

VSSQ25

N14

VSSQ26

R1

VSSQ27

R3

VSSQ28

R4

VSSQ29

R11

VSSQ30

R12

VSSQ31

R14

VSSQ32

U1

VSSQ33

U3

VSSQ34

U12

VSSQ35

U14

VSSQ36

B5

VSS1

B10

VSS2

D10

VSS3

G5

VSS4

G10

VSS5

H1

VSS6

H14

VSS7

K1

VSS8

K14

VSS9

L5

VSS10

L10

VSS11

P10

VSS12

T5

VSS13

T10

VSS14

GND

GDDR5 X32

FBA_CLK172

FBA_CLK1#72

FBA_CMD[16:31]72

20161214 SWAP

20161214 SWAP

FBA_D[0:63]

GND

GND

MF=0 non-Mirror

FBA_D63

FBA_D62

FBA_D61

FBA_D60

FBA_D59

FBA_D58

FBA_D57

FBA_D56

FBA_D55

FBA_D54

FBA_D53

FBA_D52

FBA_D51

FBA_D50

FBA_D49

FBA_D48

FBA_D47

FBA_D46

FBA_D45

FBA_D44

FBA_D43

FBA_D42

FBA_D41

FBA_D40

FBA_D39

FBA_D38

FBA_D37

FBA_D36

FBA_D35

FBA_D34

FBA_D33

FBA_D32

FBA_WCK4572

FBA_WCK45#72

FBA_WCK6772

FBA_WCK67#72

R7207 121Ohm1% /VGA

R7205 1KOhm/VGA

R7206 1KOhm/VGA

1 2

1 2

12

X507 remove C7206/C7207

GND

C7205 820PF/50V

FBA_D56

FBA_D58

FBA_D59

FBA_D57

FBA_D60

FBA_D63

FBA_D61

FBA_D62

FBA_D54

FBA_D55

FBA_D52

FBA_D53

FBA_D48

FBA_D51

FBA_D49

FBA_D50

FBA_D46

FBA_D40

FBA_D45

FBA_D41

FBA_D47

FBA_D42

FBA_D44

FBA_D43

FBA_D33

FBA_D35

FBA_D32

FBA_D37

FBA_D39

FBA_D36

FBA_D34

FBA_D38

FBA_CMD25

FBA_CMD22

FBA_CMD23

FBA_CMD20

FBA_CMD19

FBA_CMD17

FBA_CMD18

FBA_CMD27

FBA_CMD26

FBA_EDC7

FBA_EDC6

FBA_EDC5

FBA_EDC4

FBA_DBI7

FBA_DBI6

FBA_DBI5

FBA_DBI4

FBA_CMD28

FBA_CMD31

FBA_CMD30

FBA_CLK1#

FBA_CLK1

FBA_CMD16

FBA_CMD21

FBA_ZQ3

FBA_SEN3

FBA_CMD29

FBA_MF3

1 2

FBA_VREFC1

/VGA

FBA_CMD24

FBA Partition Memory (2 of 2)

MF=0 non-Mirror

U7203

M2

M4

N2

N4

T2

T4

U2

U4

M13

M11

N13

N11

T13

T11

U13

U11

F13

F11

E13

E11

B13

B11

A13

A11

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

J10

J2

J1

A5

U5

A10

U10

J14

J4

DQ7/DQ31

DQ6/DQ30

DQ5/DQ29

DQ4/DQ28

DQ3/DQ27

DQ2/DQ26

DQ1/DQ25

DQ0/DQ24

DQ15/DQ23

DQ14/DQ22

DQ13/DQ21

DQ12/DQ20

DQ11/DQ19

DQ10/DQ18

DQ9/DQ17

DQ8/DQ16

DQ23/DQ15

DQ22/DQ14

DQ21/DQ13

DQ20/DQ12

DQ19/DQ11

DQ18/DQ10

DQ17/DQ9

DQ16/DQ8

DQ31/DQ7

DQ30/DQ6

DQ29/DQ5

DQ28/DQ4

DQ27/DQ3

DQ26/DQ2

DQ25/DQ1

DQ24/DQ0

A12/A13

A0/A10/A8/A7

A1/A9/A11/A6

A3/BA3/A5/BA1

A2/BA0/A4/BA2

A5/BA1/A3/BA3

A4/BA2/A2/BA0

A6/A11/A1/A9

A7/A8/A0/A10

WCK23/WCK01

WCK23#/WCK01#

WCK01/WCK23

WCK01#/WCK23#

EDC0/EDC3

EDC1/EDC2

EDC2/EDC1

EDC3/EDC0

DBI0#/DBI3#

DBI1#/DBI2#

DBI2#/DBI1#

DBI3#/DBI0#

CAS#/RAS#

RAS#/CAS#

CKE#

CK#

CK

WE#/CS#

CS#/WE#

ZQ

SEN

RESET#

MF

Vpp/NC

Vpp/NC1

VREFD1

VREFD2

VREFC

ABI#

K4G41325FE-HC28

/VGA

B1

VDDQ1

B3

VDDQ2

B12

VDDQ3

B14

VDDQ4

D1

VDDQ5

D3

VDDQ6

D12

VDDQ7

D14

VDDQ8

E5

VDDQ9

E10

VDDQ10

F1

VDDQ11

F3

VDDQ12

F12

VDDQ13

F14

VDDQ14

G2

VDDQ15

G13

VDDQ16

H3

VDDQ17

H12

VDDQ18

K3

VDDQ19

K12

VDDQ20

L2

VDDQ21

L13

VDDQ22

M1

VDDQ23

M3

VDDQ24

M12

VDDQ25

M14

VDDQ26

N5

VDDQ27

N10

VDDQ28

P1

VDDQ29

P3

VDDQ30

P12

VDDQ31

P14

VDDQ32

T1

VDDQ33

T3

VDDQ34

T12

VDDQ35

T14

VDDQ36

C5

VDD1

C10

VDD2

D11

VDD3

G1

VDD4

G4

VDD5

G11

VDD6

G14

VDD7

L1

VDD8

L4

VDD9

L11

VDD10

L14

VDD11

P11

VDD12

R5

VDD13

R10

VDD14

A1

VSSQ1

A3

VSSQ2

A12

VSSQ3

A14

VSSQ4

C1

VSSQ5

C3

VSSQ6

C4

VSSQ7

C11

VSSQ8

C12

VSSQ9

C14

VSSQ10

E1

VSSQ11

E3

VSSQ12

E12

VSSQ13

E14

VSSQ14

F5

VSSQ15

F10

VSSQ16

H2

VSSQ17

H13

VSSQ18

K2

VSSQ19

K13

VSSQ20

M5

VSSQ21

M10

VSSQ22

N1

VSSQ23

N3

VSSQ24

N12

VSSQ25

N14

VSSQ26

R1

VSSQ27

R3

VSSQ28

R4

VSSQ29

R11

VSSQ30

R12

VSSQ31

R14

VSSQ32

U1

VSSQ33

U3

VSSQ34

U12

VSSQ35

U14

VSSQ36

B5

VSS1

B10

VSS2

D10

VSS3

G5

VSS4

G10

VSS5

H1

VSS6

H14

VSS7

K1

VSS8

K14

VSS9

L5

VSS10

L10

VSS11

P10

VSS12

T5

VSS13

T10

VSS14

+FBVDDQ

GND

+FBVDDQ

R7235

549Ohm

/VGA

1 2

FBA_VREFC0

R7236

1.33KOhm

/VGA

1 2

GND

MEM_VREF_CTL77

2

GND

1 2

R7238 0Ohm

/VGA

R7237

931Ohm

/VGA

1 2

61

Q7201A

UM6K1N

/VGA

+FBVDDQ

R7220

549Ohm

@/VGA

1 2

FBA_VREFC1

MEM_VREF_CTL

R7222

931Ohm

@/VGA

1 2

34

Q7201B

5

UM6K1N

/VGA

GND

+FBVDDQ

12

12

C7225

10UF/6.3V

0603

@/VGA

12

C7235

4.7UF/6.3V

0603

/VGA

12

C7251

0.1UF/10V

/VGA

12

12

C7226

10UF/6.3V

/VGA

C7228

C7227

10UF/6.3V

10UF/6.3V

/VGA

/VGA

12

12

12

12

C7237

C7236

C7238

10UF/6.3V

4.7UF/6.3V

1UF/6.3V

/VGA

/VGA

/VGA

12

12

12

C7252

1UF/6.3V

C7254

C7253

2.2UF/6.3V

1UF/6.3V

/VGA

/VGA

/VGA

12

12

12

C7229

10UF/6.3V

@/VGA

12

C7239

C7240

1UF/6.3V

4.7UF/6.3V

/VGA

/VGA

12

C7255

2.2UF/6.3V

/VGA

12

C7231

C7230

10UF/6.3V

@/VGA

C7232

10UF/6.3V

10UF/6.3V

@/VGA

@/VGA

12

12

12

C7241

C7242

C7243

1UF/6.3V

1UF/6.3V

1UF/6.3V

/@VGA

@/VGA

@/VGA

12

12

12

C7256

C7257

1UF/6.3V

C7258

2.2UF/6.3V

2.2UF/6.3V

/VGA

/VGA

LD R1.2 [chip]

Add Ce7201/02

12

12

12

C7233

10UF/6.3V

@/VGA

12

12

C7244

1UF/6.3V

@/VGA

12

C7259

2.2UF/6.3V

/VGA

/VGA

12

+

+

CE7201

C7234

10UF/6.3V

@/VGA

C7245

4.7UF/6.3V

/VGA

CE7202

470uF/2V

470uF/2V

@/VGA

@/VGA

12

12

C7247

C7248

4.7UF/6.3V

1UF/6.3V

/VGA

@/VGA

12

C7261

C7262

1UF/6.3V

1UF/6.3V

/VGA

/VGA

<Variant Name>

Title :

Size

Custom

Date: Sheet

Wednesday, March 07, 2018

12

12

C7249

C7250

1UF/6.3V

1UF/6.3V

@/VGA

/@VGA

12

12

C7263

1UF/6.3V

/VGA

DDR3L

Dept.:

NB2_RD1_EE1

C7264

1UF/6.3V

/VGA

Project Name

X407UA/UV

12

Engineer:

12

C7266

C7265

1UF/6.3V

0.1UF/10V

/VGA

/VGA

GND

Rev

R2.0

Brian Chen

102

of

73

12

C7246

1UF/6.3V

@/VGA

12

12

C7260

2.2UF/6.3V

/VGA

R7221

1.33KOhm

@/VGA

1 2

GND

A/D_DOCK_IN

P_CHG_CMPOUT_1091

A/D_MAX_POWER31 MB_MAX_POWER31

200mil

PC8905

1000PF/50V

1 2

A/D_DOCK_IN

AD : 17.8V

P_CHG_ACDET_1091

PC8917

47PF/50V

SMB0_DAT31,61

SMB0_CLK31,61

P_CHG_CMPIN_1091

PQ8901

QM3056M6AC

D

3

12

2

12

1 2

PR8929

127KOhm

12

1 2

1

G S

P_CHG_ACMOS_G_20

PR8905

1MOhm

P_IMVP8_PSYS_INFO81

PR8909

100KOhm

@

PR8916

0Ohm

5%

PR8924

20KOhm

PSL8901 @

0402

0402

PSL8903 @

P_CHG_ACMOS_S_20

12

PR8937

4.7MOhm

12

P_CHG_REGN_20

AC_IN_OC#31,77

12

1 2

21

21

12

PC8922

0.047UF/50V

nbs_c0603_h37_000s

PR8934

4.02KOHM

PC8912

0.1UF/25V

10m 5m

4

G S

123

4

G S

123

PR8908

10KOhm

@

>=120W

AC_BAT_SYS

5

PQH8901

QM1830M3

D

5

PQL8901

QM1830M3

D

nbs_c0603_h37_000s

nbs_r1206_h30_000s

5%

PR8920

150KOHM

1 2

61

PQ8908A

2

EM6K1-G-T2R

NEW_PWRLIMIT#_CPU

AC_OK

12

PCI8901

10UF/25V

nbs_c0805_h57_000s

PL8901

3.3UH

Irat=6.5A

2 1

[HE]CYNTEC/PEUB063T-3R3MS

12

PC8925

1000PF/50V

P_CHG_SNB_20

12

PR8910

@

1Ohm

PD8902

BAT54CW

2

3

1

PR8913

1MOhm

5

200mil

12

PCI8902

10UF/25V

@

nbs_c0805_h57_000s

@

P_PL_AC_THROTTLE_10

1 2

EM6K1-G-T2R

34

PQ8905B

12

+

PCE8901

68UF/25V

h=6mm

P_CHG_RSENS_SHAPE

1 2

SHORT_PAD

12

PSP8901

@

12

PC8908

270PF/50V

for shipping mode

P_CHG_BATDRV_20

AC_BAT_SYS

PR8926

10mOHM

nbs_r0612_h28_000s

PC8914

2200PF/50V

@

12

PR8940

20KOhm

@

P_CHG_BATSRC_20

SHORT_PAD

12

PSP8902

@

12

P_PL_AC_THROTTLE_GPU_10

PR8923

4.02KOHM

1 2

12

h=6mm

PR8922

1MOhm

@

P_CHG_BATDRV_G_20

1 2

PC8918

0.01UF/50V

PR8906

10OHM

nbs_r0603_h39_000s

1 2

PC8906

12

+

PCE8904

68UF/25V

@

34

PQ8904B

5

EM6K1-G-T2R

34

PQ8908B

5

EM6K1-G-T2R

1 2

VGA_ALERT_P# ---> GPIO9

dGPU_PD# ---> GPIO12

PR8904 0Ohm

61

2

4

G S

10UF/25V

1 2

1 2

1 2

1 2

PR8925

@

0Ohm

PQ8904A

EM6K1-G-T2R

123

240mil

PR8935

0Ohm

@

PR8942

100Ohm

5

D

240mil

12

QM0930M3

PQ8903

10UF/25V

PC8916

12

PWRLIMIT_EC# 31

PWRLIMIT#_CPU 9

VGA_ALERT_P# 77

dGPU_PD# 77

PC8924

AC_BAT_SYS

10UF/25V

PJP8901

3MM_OPEN_5MIL

2

112

BAT_CONBAT

@

<=40W <=120W

PR8938

P_CHG_LX_30

12

nbs_c0603_h37_000s

3

1

12

PC8901

0.1UF/25V

P_CHG_PROCHOT#_10

25m

EPC NB G

PR8927

10KOhm

@

1 2

PC8928

0.047UF/50V

P_CHG_LG_30

PD8901

BAT54CW

2

1 2

+5VS_PWR

PR8917

150KOHM

1 2

PR8901

0Ohm

1 2

PQ8902

QM0930M3

3

D

5

2

1

GS

4

PR8936

4.02KOHM

PSL8902

2 1

0402

@

P_CHG_ACDET_10

+3VACC+3VACC

12

PR8914

100KOhm

PR8903

93.1KOhm

1 2

P_CHG_PATH_19V_SHAPE

12

PR8911

1 2

100KOhm

61

PQ8905A

12

PC8907

47PF/50V

P_CHG_IDCHG_10

P_CHG_PMON_10

P_CHG_PROCHOT#_10

P_CHG_SDA_5

P_CHG_SCL_5

BAT1_IN_OC#31

+3VSUS

PR8828 SET

x : 0V =>0 OHM

30W: 0.4V =>14k

40W: 0.8V =>32k

45W: 1.2V =>57.6k

65W: 1.6V =>93.1k

75W: 2.0V =>150k

90W: 2.4V =>270k

120W: 2.8V =>560k

x : 3.3V =>@

2

EM6K1-G-T2R

P_CHG_IADP_10

PSL8904

0402

A/D_DOCK_IN

AC_OK

21

1 2

10KOhm

BAT

SN2867RUYR

@

PR8933

PC8909

0.1UF/25V

PR8928

1 2

1KOhm

12

PC8910

0.1UF/25V

@

PU8901

8

IDCHG

9

PMON

10

PROCHOT#

11

SDA

12

SCL

13

CMPIN

14

CMPOUT

PD8903

BAT54CW

2

1

12

P_CHG_ACDRV_20

P_CHG_ACOK_10

3

4

5

6

7

IADP

ACOK

ACDET

ACDRV

CMSRC

BATPRES#16TB_STAT#17BATSRC18BATDRV19SRN20SRP21ILIM

15

P_CHG_BATDRV_20

P_CHG_TB_STAT#_10

P_CHG_BATPRES#_10

P_CHG_BATSRC_20

3

1 2

12

PSP8903

SHORT_PAD

@

P_CHG_ACN_10

P_CHG_CMSRC_20

P_CHG_ACP_10

1

2

ACP

ACN

GND6

GND5

GND4

GND3

GND2

PHASE

HIDRV

BTST

REGN

LODRV

GND1

12

P_CHG_SRN_10

P_CHG_SRP_10

PR8932

10Ohm 5%

nbs_r1206_h28_000s

1 2

PR8938

10mOHM

nbs_r0612_h28_000s

PC8903

0.1UF/25V

1 2

33

32

31

30

29

28

VCC

27

26

25

24

23

22

P_CHG_ILIM_10

PR8919

100KOhm

nbs_r0603_h39_000s

1 2

nbs_r0603_h39_000s

1 2

PJ8803.PJ8804

請從PR8806內側中間拉線。

12

PSP8904

SHORT_PAD

@

12

PC8915

0.1UF/25V

P_CHG_VCC_20

P_CHG_VCC_20

P_CHG_LX_30

P_CHG_HG_30

P_CHG_BST_30

P_CHG_REGN_20

P_CHG_LG_30

1 2

PR8921

180KOhm

12

PC8926

0.1UF/25V

@

I limit : Charge 6 A

DisCharge 24A

PR893110OHM

PR891210OHM

P_CHG_VCC_20

12

PC8921

1UF/25V

nbs_c0603_h37_000s

PR8918

0Ohm

1 2

12

PC8920

2.2UF/16V

+3VA

12

PC8913

0.1UF/25V

12

PC8929

0.1UF/25V

P_CHG_BST_R_30

P_CHG_REGN_20

BOM

Title :

Size

A2

Date: Sheet

Wednesday, March 07, 2018

PW_CHARGER

Dept.:

NB Power Team

Project Name

X540UVK

Engineer:

Andy

Rev

R0.1

102

of

90

Address Selection Table

Address

0x7E 0x7C 0x7A 0x78 0x76 0x74 0x72 0x70

10k 1.5k 2k 3.6k 3.9k 4.3k 5.1k 6k

PR9001

8.2k 6.2k 6.8k 4.7k 3.6k 2.7kOpen 2k

PR9002

Register Address

Address

R/W

W W W

Temp. alert

Function

threshold setting

0x03 0x04 0x050x00 0x01 0x02

R R R

Sensed temp. data

0x06

R

bit 4 = 0

bit 5 = 0

bit 6 = 0

When ALERT#

assert

Address Selection Table

Address

0x7E 0x7C 0x7A 0x78 0x76 0x74 0x72 0x70

10k 1.5k 2k 3.6k 3.9k 4.3k 5.1k 6k

PR9008

PR9009

8.2k 6.2k 6.8k 4.7k 3.6k 2.7kOpen 2k

PTR9000 place near PQ8901

Close to AC FET

PTR9002 place near BAT Connect

105C @ 5k

40C @ 51k

GND

PTR9002 place near PL8901 or PQL8901(CHG page)

105C @ 5k

40C @ 51k

GND

PTR9000

100kOhm

PC9000

0.1UF/25V

PTR9001

100kOhm

PC9001

0.1UF/25V

PTR9002

100kOhm

PC9002

0.1UF/25V

12

12

12

12

12

12

P_TEMPSENS_VCC_30

PR9003

12KOHM

1.0 ~ 3.56V

PR9004

12KOHM

1.0 ~ 3.56V

PR9005

12KOHM

1.0 ~ 3.56V

DC Jack Thermal Latch

PSL9003

SHORT_LAND

0402

P_LATCH_ACDET_10

PR9013

20KOhm

PQ9001B

EM6K1-G-T2R

12

1%

12

1%

12

1%

21

P_LATCH_OUT_10

12

P_TEMPSENS_ADDR_10

P_TEMPSENS_TM3_10

P_TEMPSENS_TM2_10

P_TEMPSENS_TM1_10

34

5

P_LATCH_OUT#_10

GND

P_CHG_ACDET_10 90

PR9001

10KOhm

PR9002

2KOHM

1 2

@

P_CHG_REGN_20

1 2

12

P_TEMPSENS_VCC_30

GNDGND

PR9014

100KOhm

PQ9001A

EM6K1-G-T2R

1

2

3

4

61

GND

PU9000

ALT/ADD

TM3

TM2

TM1

UP1905AMA8

P_CHG_REGN_20

2

ALERT# pull low if sensed temp.

is higher than setting

8

SDA

7

P_TEMPSENS_SDA_30

SCL

6

P_TEMPSENS_SCL_30

GND

5

VCC5

P_TEMPSENS_VCC_30

GND

+5VSUS_PWR

PR9006 2.2Ohm 5%

nbs_r0603_h24_000s

12

PR9017

10KOhm

P_CHG_CMPIN_1090

P_CHG_CMPOUT_10 90

PR9018

1 2

10KOhm

1 2

12

PC9003

1UF/16V

nbs_c0603_h37_000s

GND

PTR9003 place near DC JACK

PC9008

1UF/25V

PC9005

47PF/50V

@

1 2

PSL9001

2 1

0402

PSL9002

@

2 1

0402

@

1 2

PC9004

47PF/50V

@

GND

GND

P_CHG_REGN_20

1 2

12

1 2

GND

PTR9003

100kOhm

PR9022

7.32KOhm

SMB1_DAT 29,31,91

SMB1_CLK 29,31,91

Check 其他頁是否有

pull high 到 3.3V

47KOHM

47KOHM

PTR9004

PC9007

0.1UF/25V

PTR9005

PC9010

0.1UF/25V

PC9012

0.1UF/25V

12

12

12

12

12

P_TEMPSENS_6_VCC_30

PR9007

12KOHM

12

1%

1.0 ~ 3.56V

PR9010

12KOHM

12

1%

1.0 ~ 3.56V

PR9012

12KOHM

12

1%

1.0 ~ 3.56V

PR9008

4.3KOHM

1 2

P_TEMPSENS_6_VCC_30

PR9009

3.6KOhm

1 2

P_TEMPSENS_6_ADDR_10

P_TEMPSENS_6_TM3_10

P_TEMPSENS_6_TM2_10

P_GPU_VRM_TEMP_SENSOR_10

PC9006

47PF/50V

@/VGA

1 2

GND

12

PC9011

1UF/16V

nbs_c0603_h37_000s

GND

PL9001

2 1

0402

PSL9004

2 1

0402

1 2

PC9009

47PF/50V

@/VGA

SMB1_DAT 29,31,91

@/VGA

SMB1_CLK 29,31,91

@/VGA

Check 其他頁是否有

pull high 到 3.3V

GND

GNDGND

PU9001

1

2

3

4

ALT/ADD

TM3

TM2

TM1

UP1905AMA8

8

SDA

7

P_TEMPSENS_6_SDA_30

SCL

6

P_TEMPSENS_6_SCL_30

GND

5

VCC5

P_TEMPSENS_6_VCC_30

GND

+5VSUS

1 2

PR9011 2.2Ohm 5%

nbs_r0603_h24_000s

PTR7807 place near VRAM.

TR7806 place near GPU

105C @ 5k

40C @ 51k

GND

P_GPU_VRM_TEMP_SENSOR_1092

P_GPU_VRM_TEMP_SENSOR_10

105C @ 5k

40C @ 51k

GND

<Variant Name>

Title :

Size

A2

Date: Sheet

Wednesday, March 07, 2018

PW_PROTECTION

Dept.:

NB Power Team

Project Name

X540UVK

Engineer:

Andy

Rev

R0.1

102

of

91

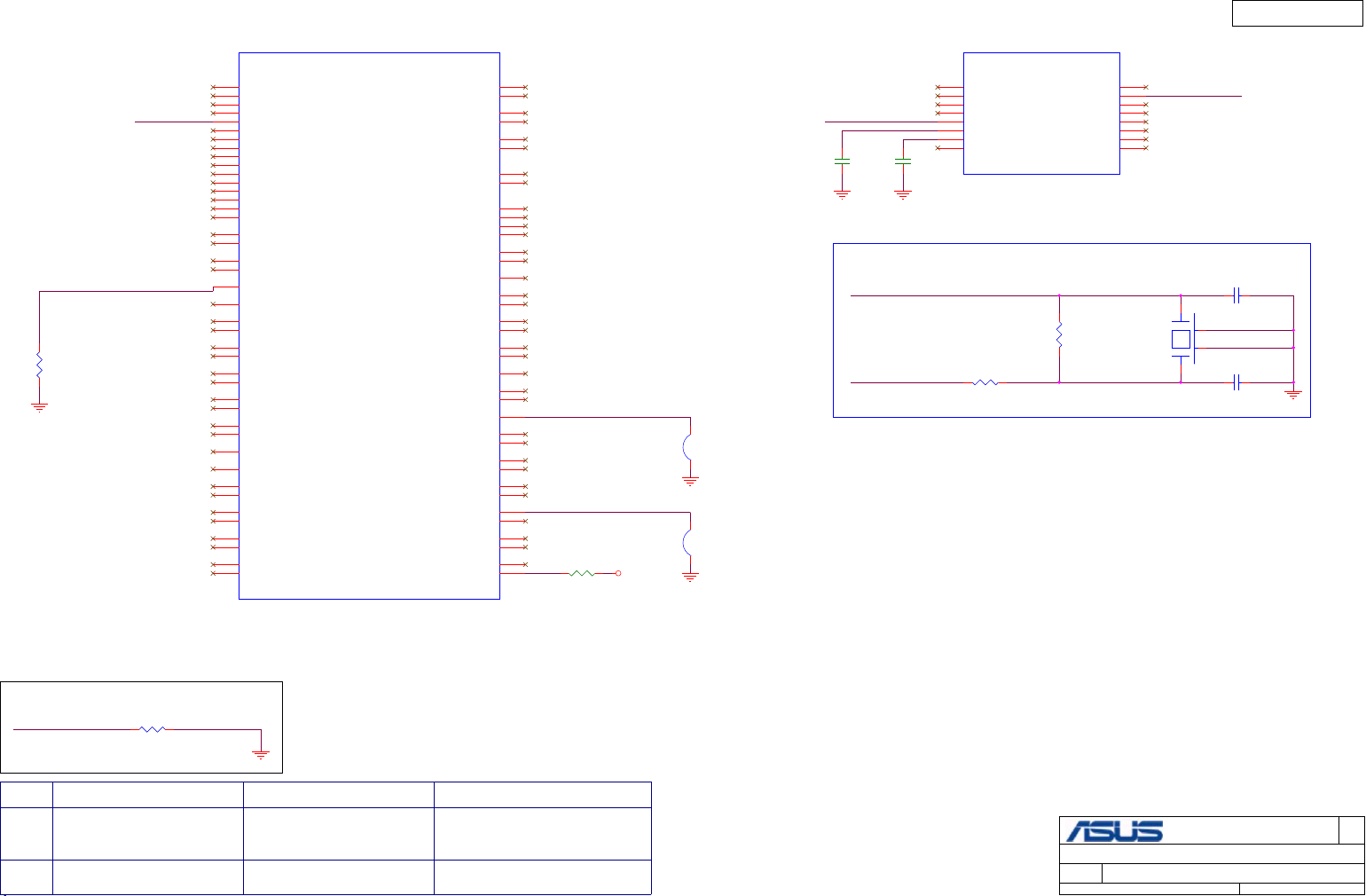

Psys FF=3.2V

www.teknisi-indonesia.com

PR8029

33W - 97.6K / 10G212976214031

45W - 71.5K / 10G212715214030

65W - 49.9K / 10G212499214030

90W - 35.7K / 10G212357214030

120W - 26.7K / 10G212267214031

VREF_0.6V

12

PR8001

12.1KOhm

1%

Frequency=500kHz

12

PR8046

26.1KOhm

1%

12

12

PR8006

18.7KOhm

1%

PR8056

8.25kOhm

1%

PR8018

22KOhm 1%

1 2

1 2

PR8039

30KOHM 1%

Place Close to PL8102

P_IMVP8_CORE_TSEN_R_10

1 2

PR8057

12

12

PR8027

2.61KOHM

1%

12

PR8024

22Ohm

5%

P_IMVP8_CORE1_HG_3082

P_IMVP8_CORE1_LX_3082

P_IMVP8_CORE1_LG_3082

P_IMVP8_GT_HG_3082

P_IMVP8_GT_LX_3082

P_IMVP8_GT_LG_3082

P_IMVP8_CORE_VIN_S82

P_IMVP8_CORE2_PWM_1082

P_IMVP8_CORE_DRVEN_1082

12

12

PR8035

PR8048

11.5KOHM

5.76KOhm

1%

1%

12

12

PR8026

PR8058

49.9Ohm

300Ohm

1%

1%

PR8065

330KOHM

1%

12

PR8033

330KOHM

1%

110KOHM 1%

PTR8002

1 2

100kOhm

1%

Place Close to PQL8102

P_VCCCORE_VCCSENSE_50ohm7

P_VCCCORE_VSSSENSE_50ohm7

P_VCCGT_VCCSENSE_50ohm7

P_VCCGT_VSSSENSE_50ohm7

Skylake IMVP8 Power [For CPU]

PSL8001

PC8026

47PF/50V

PR8060

1 2

0Ohm

PR8042

1 2

0Ohm

+VCCGT

1 2

1 2

0402

PR8029

49.9KOhm

1 2

ADP=65W

PR8020

0Ohm 5%

1 2

1

IMON_MAIN

2

SET1

3

FB_MAIN

4

COMP_MAIN

5

SET2

6

SET3

7

ISEN1N_MAIN

8

ISEN2N_MAIN

9

ISEN2P_MAIN

10

ISEN1P_MAIN

11

TSEN_MAIN

12

VIN

13

VCC

12

PC8065

4.7UF/6.3V

PR8008

1Ohm

nbs_r0603_h24_000s

PR8050

100Ohm

12

PR8059

100Ohm

12

PR8025

100Ohm

1 2

PR8061

0Ohm

PR8044

0Ohm

PR8064

100Ohm

1 2

P_IMVP8_PSYS_INFO90 IMVP8_PWRGD 26,31

P_VCCCORE_VCCSENSE_R_50ohm

12

PR8045

PC8079

1 2

0.01UF/50V

3.6KOhm

1%

P_IMVP8_CORE_IMON_10

P_IMVP8_SET1_10

P_IMVP8_CORE_FB_10

P_IMVP8_CORE_COMP_10

P_IMVP8_SET2_10

P_IMVP8_SET3_10

P_IMVP8_CORE_CSN1_10

P_IMVP8_CORE_CSN2_10

P_IMVP8_CORE_CSP2_10

P_IMVP8_CORE_CSP1_10

P_IMVP8_CORE_TSEN_10

P_IMVP8_VIN_10

P_IMVP8_VCC_20

PR8062

1Ohm

12

+5VSUS_PWR

+5VSUS_PWR

12

1 2

PTRL8002

100kOhm 1%

PR8054

10OHM

12

P_IMVP8_CORE_VIN_S

PC8081

1 2

47PF/50V

Place Close to CPU

+VCCCORE

Place Close to CPU

VREF_0.6V

21

P_IMVP8_PSYS_10

P_IMVP8_CORE_VSN_10

P_IMVP8_CORE_VSEN_10

47

48

49

50

51

52

53

PSYS

GND154GND255GND356GND457GND5

FB_SA

RGND_SA

VSEN_MAIN

RGND_MAIN

BOOT_SA15UGATE_SA16PHASE_SA17LGATE_SA18PVCC19LGATE_MAIN20PHASE_MAIN21UGATE_MAIN22BOOT_MAIN23LGATE_AUXI24PHASE_AUXI25UGATE_AUXI26BOOT_AUXI

14

P_IMVP8_CORE1_LG_30

P_IMVP8_PVCC_20

5%

12

12

PC8053

2.2UF/6.3V

@

PC8023

1 2

1000PF/50V

PC8007

1000PF/50V

12

P_VCCCORE_VSSSENSE_R_50ohm

@

PC8024

1 2

1000PF/50V

P_VCCGT_VCCSENSE_R_50ohm

PC8025

1000PF/50V

12

P_VCCGT_VSSSENSE_R_50ohm

12

PR8030

53.6KOhm

1%

P_IMVP8_SA_CSN_10

P_IMVP8_SA_CSP_10

P_IMVP8_SA_IMON_10

43

44

45

46

IMON_SA

COMP_SA

ISENP_SA

ISENN_SA

VR_READY

VREF06/PSET

PR8037

1Ohm

P_IMVP8_CORE1_BST_30

P_IMVP8_CORE1_LX_30

P_IMVP8_CORE1_HG_30

1 2

PC8030

0.1UF/25V

nbs_c0603_h37_000s

PR8000

3.9Ohm 1%

1 2

IMVP8_PWRGD_L

P_IMVP8_EN_10

P_IMVP8_CORE2_PWM_10

PU8001

40

41EN42

ATK1604ACGQW

DRVEN

PWM_MAIN

VCLK

ALERT#

VDIO

VR_HOT#

IMON_AUXI

ISENP_AUXI

ISENN_AUXI

VSEN_AUXI

COMP_AUXI

RGND_AUXI

FB_AUXI

TSEN_AUXI

P_IMVP8_GT_BST_30

P_IMVP8_GT_LX_30

P_IMVP8_GT_LG_30

12

PR8040

100Ohm

1 2

12

PC8020

1000PF/50V

@

100Ohm

1 2

12

P_IMVP8_VREF_0.6V_S

PC8000

0.47UF/16V

1 2

1 2

PR8031 49.9Ohm

1 2

PR8032 10Ohm

39

38

P_IMVP8_CORE_DRVEN_10

37

P_SVID_CLK_X1

36

P_SVID_ALERT#_X1

35

P_SVID_DATA_X1

34

P_IMVP8_VR_HOT#_10

33

P_IMVP8_GT_IMON_10

32

P_IMVP8_GT_CSP_10

31

P_IMVP8_GT_CSN_10

30

P_IMVP8_GT_VSEN_10 P_VCCGT_VCCSENSE_R_50ohm

29

P_IMVP8_GT_COMP_10

28

P_IMVP8_GT_VSN_10

27

P_IMVP8_GT_FB_10

PR8004

1Ohm

1 2

P_IMVP8_GT_BST_R_30P_IMVP8_GT_HG_30

1 2

PC8010

0.1UF/25V

nbs_c0603_h37_000s

P_IMVP8_CORE1_BST_R_30

PR8043

PC8021

1000PF/50V

@

@

PC8008

220PF/50V

PR8070

10KOhm 1%

+5VSUS_PWR

@

PC8009

220PF/50V

PR8073

10KOhm 1%

+5VSUS_PWR

PC8016

12

82PF/50V

PR8053

54.9KOhm 1%

1 2

12

PSL8006

12

82PF/50V

PR8023

22KOhm 1%

12

1 2

PSL8007

1 2

12

0402

PC8011

0402

12

PC8080

47PF/50V

21

21

1 2

1 2

PR8028

110KOHM 1%

1 2

Place Close to PQL8101

P_IMVP8_CORE_COMP_10P_VCCCORE_VCCSENSE_R_50ohm

P_IMVP8_CORE_FB_10

P_IMVP8_CORE_VSN_10

P_IMVP8_GT_COMP_10

P_IMVP8_GT_FB_10

P_IMVP8_GT_VSN_10

PR8009

0Ohm 5%

PTR8001

100kOhm

1%

Place Close to PU8001

Place Close to PU8001

PR8011

45.3Ohm

P_IMVP8_SVID_VCC_10

12

PR8041

110Ohm

PSL8002

0402

P_IMVP8_GT_TSEN_R_10P_IMVP8_GT_TSEN_10

@

21

174KOhm

PSL8004

21

0402

21

0402

PSL8005

PR8034

1Ohm

nbs_r0603_h24_000s

12

12

12

PR8010

PC8015

0.1UF/25V

100Ohm

nbs_c0603_h37_000s

1 2

PR8074 100Ohm

VREF_0.6V

PR8013

37.4KOhm 1%

1 2

VREF_0.6V

1 2

PR8002

12

PR8019

8.66KOhm

1%

1%

P_IMVP8_CORE_ISEN-_1082

P_IMVP8_CORE_ISEN+_1082

P_IMVP8_CORE_ISEN2-_1082

P_IMVP8_CORE_ISEN2+_1082

5%

12

P_IMVP8_GT_ISEN-_1082

P_IMVP8_GT_ISEN+_1082

U42

U22

ALL_SYSTEM_PWRGD 26,31,59,70

+VCCST

P_SVID_CLK_50OHM_X2 7

P_SVID_ALERT#_50OHM_X2 7

P_SVID_DATA_50OHM_X2 7

IMVP8_VRHOT# 9

Disable SA

Enable SA

PR8063 PR8072 PR8038 PR8052

@@10Kohm

0ohm

P_IMVP8_SA_CSP_10

P_IMVP8_SA_CSN_10

P_IMVP8_GT_CSP_10

P_IMVP8_GT_CSN_10

PR8068

1.1KOhm 1%

1 2

P_IMVP8_CORE_CSP1_10

P_IMVP8_CORE_CSN1_10

PR8069

1.1KOhm 1%

1 2

P_IMVP8_CORE_CSP2_10

P_IMVP8_CORE_CSN2_10

PR8005 PR8075 PR8017

0ohm @ @

PR8067

2KOhm 1%

1 2

/U42

0ohm@ 1Kohm

0ohm

4.7Kohm

PR8055

2KOhm 1%

1 2

P_IMPV8_GT_LX_R_10

PR8016

1.1KOhm 1%

1 2

P_IMPV8_CORE1_LX_R_10

PR8051

1.1KOhm 1%

1 2

P_IMPV8_CORE2_LX_R_10

PR8051 PR8069

1.1Kohm

@

0ohm

2.37Kohm

P_IMVP8_GT_CSP_R_10

/U42

1.1Kohm

@

PR8003 PR8066

1.4Kohm 1.4Kohm

PR8052

0Ohm 5%

1 2

PR8007

2.74KOhm 1%

1 2

1 2

@

PC8002

0.1UF/16V

1 2

PR8014

4.7KOhm 1%

1 2

PTRL8004

1 2

4.7KOhm

3%

Place Close to PL8101

PC8003

0.1UF/16V

1 2

PR8015

590OHM @

1 2

PC8004

0.1UF/16V

1 2

/U42

PR8017

0Ohm /U22

PC8001

@

@

0.1uF/25V

PR8072

1KOhm

1 2

N/A

12

PC8006

0.1UF/25V

12

PC8012

0.1UF/25V

12

PC8018

0.1UF/25V

12

PR8005

/U42

0Ohm

5%

PR8075

/U22

1KOhm

1 2

12

<Variant Name>

+5VSUS_PWR

PC8014

0.1UF/25V

N/A

Title :

Skylake IMVP8

Size

Dept.:

Power team

Custom

Date: Sheet

Wednesday, March 07, 2018

+5VSUS_PWR

Project Name

S430

Engineer:

Rev

R0.9

EE

103

of

81

Title

<Title>

Size Document Number Rev

A

Date: Sheet

<Doc> <RevCode>

, March 07, 2018

2 1Wednesday

of

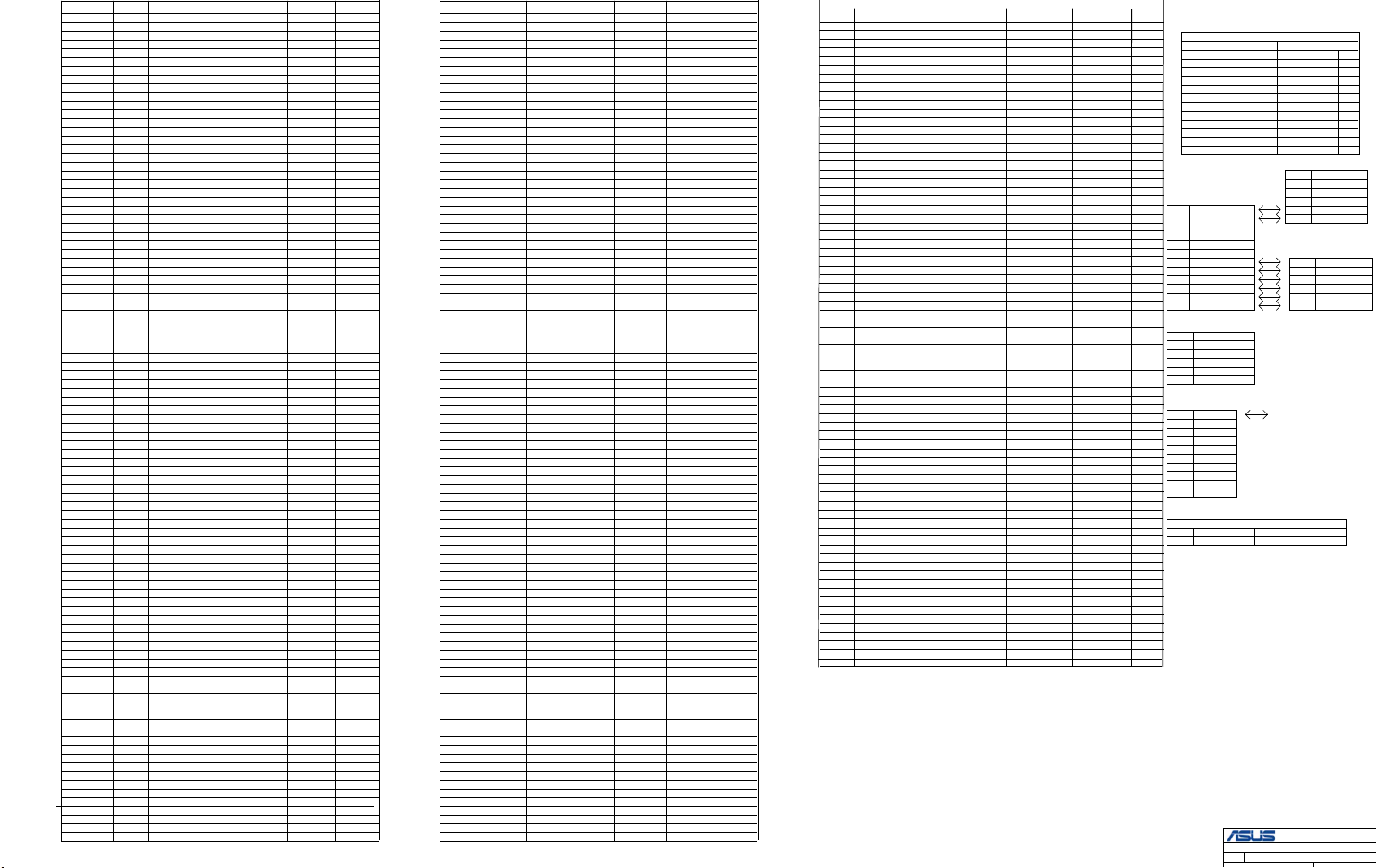

PCH_CPT

GPIO

For 555 N/A

Need Add EC

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For X541UV N/A

For X541UV N/A

For 555 N/A

For X541UV N/A

X541UV Change

For 555 N/A

For 555 N/A

PCH_IBEX GPIO

GPP_A0

GPP_A1

GPP_A2

GPP_A3

GPP_A4

GPP_A5

GPP_A6

GPP_A7

GPP_A8

GPP_A9

GPP_A10

GPP_A11

GPP_A12

GPP_A13

GPP_A14

GPP_A15

GPP_A16

GPP_A17

GPP_A18

GPP_A19

GPP_A20

GPP_A21

GPP_A22

GPP_A23

GPP_B0

GPP_B1

GPP_B2

GPP_B3

GPP_B4

GPP_B5

GPP_B6

GPP_B7

GPP_B8

GPP_B9

GPP_B10

GPP_B11

GPP_B12

GPP_B13

GPP_B14

GPP_B15

GPP_B16

GPP_B17

GPP_B18

GPP_B19

GPP_B20

GPP_B21

GPP_B22

GPP_B23

GPP_C0

GPP_C1

GPP_C2

GPP_C3

GPP_C4

GPP_C5

GPP_C6

GPP_C7

GPP_C8

GPP_C9

GPP_C10

GPP_C11

GPP_C12

GPP_C13

GPP_C14

GPP_C15

GPP_C16

GPP_C17

GPP_C18

GPP_C19

GPP_C20

GPP_C21

GPP_C22

GPP_C23

GPP_D0

GPP_D1

GPP_D2

GPP_D3

GPP_D4

GPP_D5

GPP_D6

GPP_D7

GPP_D8

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D13

GPP_D14

GPP_D15

GPP_D16

GPP_D17

GPP_D18

GPP_D19

GPP_D20

GPP_D21

GPP_D22

Power on

DGPU

GLAN

WLAN

Default States

需確認是否具wake 功能

UART1_RTS#

UART1_CTS#

UART0_CTS#

Signal NameUse As

RC_IN#

Native1

Native1

LPC_AD0

LPC_AD1

Native1

LPC_AD2

Native1

Native1

LPC_AD3

LPC_FRAME#

Native1

INT_SERIRQ

Native1

GPO

N/A

PM_CLKRUN#

Native

CLK_KBCPCI_PCH

Native1

Native

CLK_DEBUG

N/A

GPO

N/A

GPO

SUSWARN#

Native1

PCH_SUS_STAT#

Native1

PCH_SUSACK#

Native1

N/A (SD_1P8_SEL)

GPO

N/A (SD_PWR_EN#)

GPO

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

N/A (VCCPRIM_VID0)

Native

N/A (VCCPRIM_VID1)

Native

GPO

N/A

N/A

GPO

N/A

GPO

CK_REQ_P0#

Native

CK_REQ_P1#

Native

CK_REQ_P2#

Native

CK_REQ_P3#

Native

CK_REQ_P4#

Native

CK_REQ_P5#

Native

Native

MPHY_PWREN (N/A)

Native

PCH_SLP_S0#

Native

PLT_RST#

PCH_GPPB14

GPO

GPO

N/A (GSPI0_CS_R#)

GPO

N/A (GSPI0_CLK_R)

GPO

N/A (GSPI0_MISO_R)

N/A (PCH_GPPB18)

GPO

BT_ON/OFF#

GPO

GPU_EVENT#

GPO

GPI

DGPU_FB_CLAMP_GPIO

GPO

PCH_GPPB22

SML1ALERT#

Native

Native

SMB_CK +3VSUS

Native

SMB_DATA

GPP_C2

GPO

GPO

SML0_CK

GPO

SML0_DATA

GPP_C5

GPO

GPO

SML1_CK

GPO

SML1_DATA

N/A (PCH_GPPC8)

GPO

N/A (PCH_GPPC9)

GPO

N/A (PCH_GPPC10)

GPO

N/A (PCH_GPPC11)

GPO

DIMM_SEL0

GPO

DIMM_SEL1

GPO

DIMM_SEL2

GPO

FP_RST#_GPIO

GPO

AOAC_WLANLED(N/A)

GPO

N/A (ALS_INT#)

Native

I2C1_SDA_TCH_PAD

Native

I2C1_SCL_TCH_PAD

DGPU_PWROK

GPI

GPU_RST#

GPO

GPO

DGPU_PWR_EN# +3VSUS

TPanel_INT#

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

GPIO_SMI_ASM1142(N/A)

GPI

SATA_ODD_PWRGT

GPO

SATA_ODD_DA#

GPI

GPO

N/A

N/A

GPO

PCB_ID0

GPI

DMIC_ID

GPI

TOUCHPAD_ID

GPI

TOUCH_PANEL_ID

GPI

TOUCHPAD_INTR#

GPI

WLAN_LED_R

GPO

SNSR_HUB_PWREN

GPO

FP_INT#

GPI

N/A

GPO

N/A

GPO

GPO

(N/A) DMIC_CLK_PCH

GPO

(N/A) DMIC_DATA_PCH

N/A

GPO

N/A

GPO

Int.& Ext

Pull up / down

EXT PU 10K

EXT PU 10K

EXT PU 8.2K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 20K

EXT PU 10K

EXT PD 10K

EXT PU 150K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 10K

EXT PU 10K

EXT PU 10K

PU 4.7K

PU 4.7K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PD 10K

EXT PD 10K

EXT PD 10K

EXT PD 10K

EXT PU 10K

Power

+3VS

+3VS

+3VS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSG

PU at DGPU

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSG

+3VS

+3VS

+3VS

+3VS

+3VS

PU at EC

For X541UV ADD

For X541UV ADD

PU at DGPU

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 ADD

For 555 ADD

For 555 N/A

PCH_IBEX GPIO

GPP_D23

GPP_E0

GPP_E1

GPP_E2

GPP_E3

GPP_E4

GPP_E5

GPP_E6

GPP_E7

GPP_E8

GPP_E9

GPP_E10

GPP_E11

GPP_E12

GPP_E13

GPP_E14

GPP_E15

GPP_E16

GPP_E17

GPP_E18

GPP_E19

GPP_E20

GPP_E21

GPP_E22

GPP_E23

GPP_F0

GPP_F1

GPP_F2

GPP_F3

GPP_F4

GPP_F5

GPP_F6

GPP_F7

GPP_F8

GPP_F9

GPP_F10

GPP_F11

GPP_F12

GPP_F13

GPP_F14

GPP_F15

GPP_F16

GPP_F17

GPP_F18

GPP_F19

GPP_F20

GPP_F21

GPP_F22

GPP_F23

GPP_G0

GPP_G1

GPP_G2

GPP_G3

GPP_G4

GPP_G5

GPP_G6

GPP_G7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPD8

GPD9

GPD10

GPD11

Use As Signal Name

GPO

N/A

DIRECT_ESATA_DETECT_R#

GPO

SATA_ODD_PRSNT_R#

GPO

MSATA_MPCIE_DET#

GPO

N/A

GPO

SATA0_DEVSLP

GPO

SATA1_PHYSLP_DIRECT

GPO

SATA2_DEVSLP

GPO

N/A

GPO

PCH_SATA_LED#

NATIVE

USB_OC_1_2#_R EXT PU 10K

NATIVE

USB_OC_3_4#

GPI

USB_OC_5_6#

GPI

USB_OC_7_8#

GPI

N/A

GPO

HDMI_HP

NATIVE

EXT_SMI# EXT PU 10K

GPO

EXT_SCI#

GPI

EDP_HPD_CON

NATIVE

DDPB_SCL_PCH

GPO

DDPB_SDA_PCH

GPO

DDPC_SCL_PCH

NATIVE

DDPC_SDA_PCH

NATIVE

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

GPO

N/A

GPO

N/A

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A (SDIO_CMD)

GPO

N/A (SDIO_D0)

GPO

N/A (SDIO_D1)

GPO

N/A (SDIO_D2)

GPO

N/A (SDIO_D3)

GPO

N/A (SDIO_CD#)

GPO

N/A (SDIO_CLK)

GPO

N/A (SDIO_WP)

GPOGPO

PM_BATLOW_R#

Native

ME_AC_PRESENT_PCH

Native

PCH_GPD2#

GPO

PM_PWRBTN#

Native

PM_SUSB#

Native

PM_SUSC#

Native

PM_SLP_A_R#

Native

WLAN_ON#

GPO

NA (SUS_CK)

GPO

PCH_SLP_WLAN# (N/A)

GPO

SLP_S5# (N/A)

GPO

LAN_PWREN (N/A)

GPO

Power on

Default States

Int.& Ext

Power

Pull up / down

EXT PU 10K

+3VS

EXT PU 10K

+3VS

EXT PU 10K

+3VS

EXT PU 10K

+3VS

+3VSUS

EXT PU 10K

+3VSUS

EXT PU 10K

+3VSUS

EXT PU 10K

+3VSUS

EXT PD 100K PD at IC of eDP to VGA

EXT PU 1M

EXT PU 10K

EXT PU 10K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 8.2K

EXT PU 100K

EXT PU 10K

EXT PD 100K

EXT PD 100K PD at EC

EXT PD 1K

PD at HDMI conn

+3VS

+3VS

+3VS

PD at LVDS conn

+3VS

+3VS

+3VS

+3VA_DSW

+3VA_DSW

+3VA_DSW

PD at EC

PU at HDMI conn

PU at HDMI conn

VC lose

EC

IT8995

GPIO

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

For 555 N/A

Pin Name

Config

O

OD

OD

Alt

O

Alt

Alt

O

Alt

I

OD

I

O

O

OD

O

Alt

Alt

O

I

I

Alt

I

I

O

Alt

OD

OD

O

Alt

Alt

O

O

O

O

O

I

OD

OD

O

O

Alt

Alt

Alt

Alt

Alt

O

O

O

I

O

Alt

Alt

Alt

O

O

O

O

O

I

I

I

I

I

I

Alt

Alt

I

O

Alt

O

Alt

I

I

OGPJ7

PWR_LED

CHG_LED#

EC_GPA3

EC_GPA4

FAN0_PWM

KB_LED_PWM

EC_GPA7 (N/A)

LID_SW#

(N/A)

PWR_SW#

PS_ON

A20GATE (N/A)

(N/A)

PM_PWRBTN#

BAT1_IN_OC#

(N/A)

PCH_SLP_S0#

ME_AC_PRESENT

BUF_PLT_RST#

EXT_SCI#

EXT_SMI#

OP_SD#

FAN0_TACH

(N/A)

SUSC_EC#

1.2V_ON

N/A

(N/A)

CAP_LED#

PECI_EC

PCH_SPI_OV

DGPU_LIMIT

PCH_SUSACK#

PWRLIMIT_EC#

(N/A)

PM_CLKRUN#

SMB3_CLK

SMB3_DAT

DPWROK_EC

PM_PWROK

PM_SYSPWROK

LCD_BACKOFF#

PM_SLP_SUS#

3VSUS_PWRGD

ALL_SYSTEM_PWRGD

IMVP8_PWRGD

3VA_DSW_PWRGD

ME_SusPwrDnAck_EC

A/D_MAX_POWER

MB_MAX_POWER

EC_WAKE_SCI

PL_REF_EC

WLAN_PWR_EN

EC_GPJ5

N/A

N/A

GPA0

GPA1

GPA2

GPA3

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPF0

GPF1

GPF2

GPF3

GPF4

GPF5

GPF6

GPF7

GPG0

GPG1

GPG2

GPG6

GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6

GPH7

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

GPI7

GPJ0

GPJ1

GPJ2

GPJ3

GPJ4

GPJ5

GPJ6

*1: EC config GPI; Function output

Signal Name

N/A

N/A

N/A

N/AIBAT_REF_EC

Default status

LOW

HIGH

HIGH

LOW

LOW

LOW

LOW

HIGH

HIGH

HIGH

LOW

HIGH

HIGH

LOW

HIGH

LOW

LOW

LOW

HIGH

LOW

HIGH

HIGH

LOW

HIGH

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

HIGH

HIGH

LOW

HIGH

HIGH

LOW

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

LOW

HIGH

HIGH

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

LOW

HIGH

HIGH

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

HIGH

Ext Pull up / down

EXT 10K PU

EXT 10K PUCHG_FULL_LED#

EXT 10K PU +3VA_EC

EXT 10K PU

EXT 4.7K PUSMB1_DAT

EXT 100K PDPM_SUSC#

EXT 10K PD

EXT 100K PD

EXT 10K PU +3VS

EXT 10K PU +3VS

EXT 10K PU

EXT 10K PU

EXT 10K PDSUSB_EC#

EXT 10K PD

EXT 100K PDPM_SUSB#

EXT 1K PUTHRO_CPU#

EXT 10K PU/ 1M PD5VSUS_ON

EXT 100K PU

EXT 4.7K PU +3VSTP_CLK

EXT 8.2K PU

EXT 10K PDPM_RSMRST#

EXT 10K PD

EXT 100K PD

EXT 10K PD

EXT 10K PU/ 100K PD +3VA_EC

EXT 10K PU +3VS

EXT 10K PU +3VS

EXT 100K PU +3VA_DSW

EXT 0 PD

EXT 100K PU/93.1K PD +3VACC

+VCCSTG

+3VA_EC

+3VA_ECVSUS_ON

+3VA_ECEXT 4.7K PUSMB0_CLK

+3VA_ECEXT 4.7K PUSMB0_DATA

+3VSEXT 4.7K PUTP_DAT

+3VA_ECEXT 100K PU

+3VA_ECEXT 100K PU3VADSW_ON

+3VS

Power

+3VA_EC

+3VA_EC

+3VA_ECEXT 10K PU

+3VAEXT 10K PUAC_IN_OC#

+3VAEXT 10K PU

+3VA

+3VSEXT 10K PU

+3VSEXT 10K PURC_IN#

+3VA_ECEXT 4.7K PUSMB1_CLK