Asus P55T2P4 User Manual

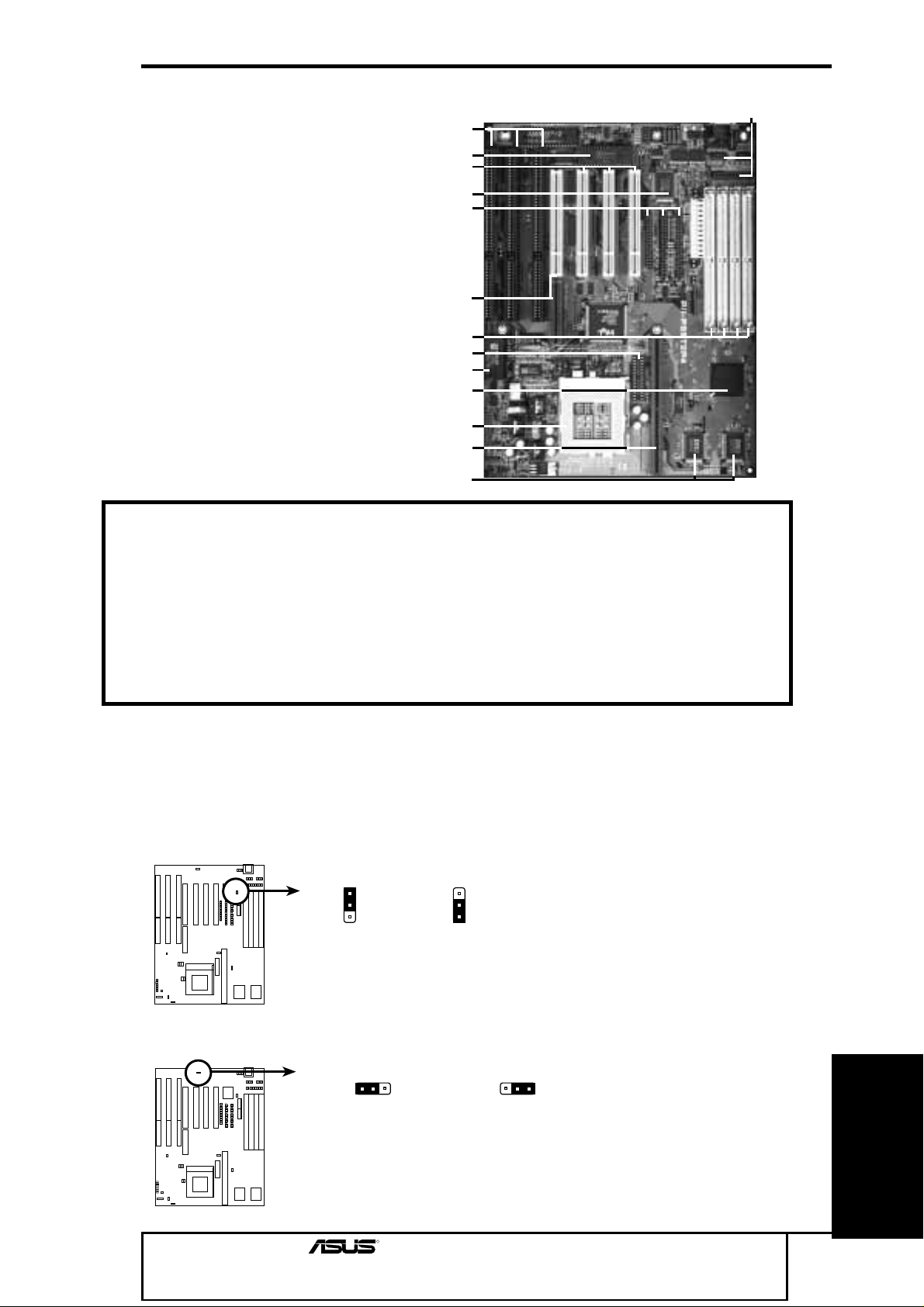

Carte mère ASUS P/I-P55T2P4

NOTE: Consultez cette documentation conjointement avec le manuel de l’utilisateur

Parallèle & série

3 emplacements Bus ISA

BIOS Flash programmable

3 emplacements PCI

Controleur d’E/S 16550 UART1

Connecteur floppy & IDE

MediaBus PCI 4.1 Bus propriétaire ASUS

Emplacements pour SIMM à 72 broches

TAG SRAM améliorable

Horloge à temps réel fonctionnant automatiquement

430HX PCIset d’Intel

Socle 7 de CPU ZIF

Fente d’expansion L2 Cache améliorable

Pipeline L2 Cache extensible à 256/512KB

F026

ATTENTION: Les cartes mère et les pièces de l’ordinateur se composent des chips des circuits

intégrés (IC) extrêmement délicats. Pour protéger la carte mère et les autres pièces contre les

dommages provoqués par l’électricité statique, respectez les précautions suivantes quand vous

travaillez avec votre ordinateur.

1. Débranchez votre ordinateur avant de travailler dans l’intérieur.

2. Tenez les pièces par leurs bords et ne touchez pas les composants électroniques, les fils ou

les circuits.

3. Utilisez un lien mis à terre avant d’utiliser des pièces de l’ordinateur.

4. Quand les pièces ne sont pas liées au système, mettez-les sur un coussinet anti-statique et

mis à terre, ou placez-les sur le sac dans lequel elles sont fournies.

Réglage des Cavaliers

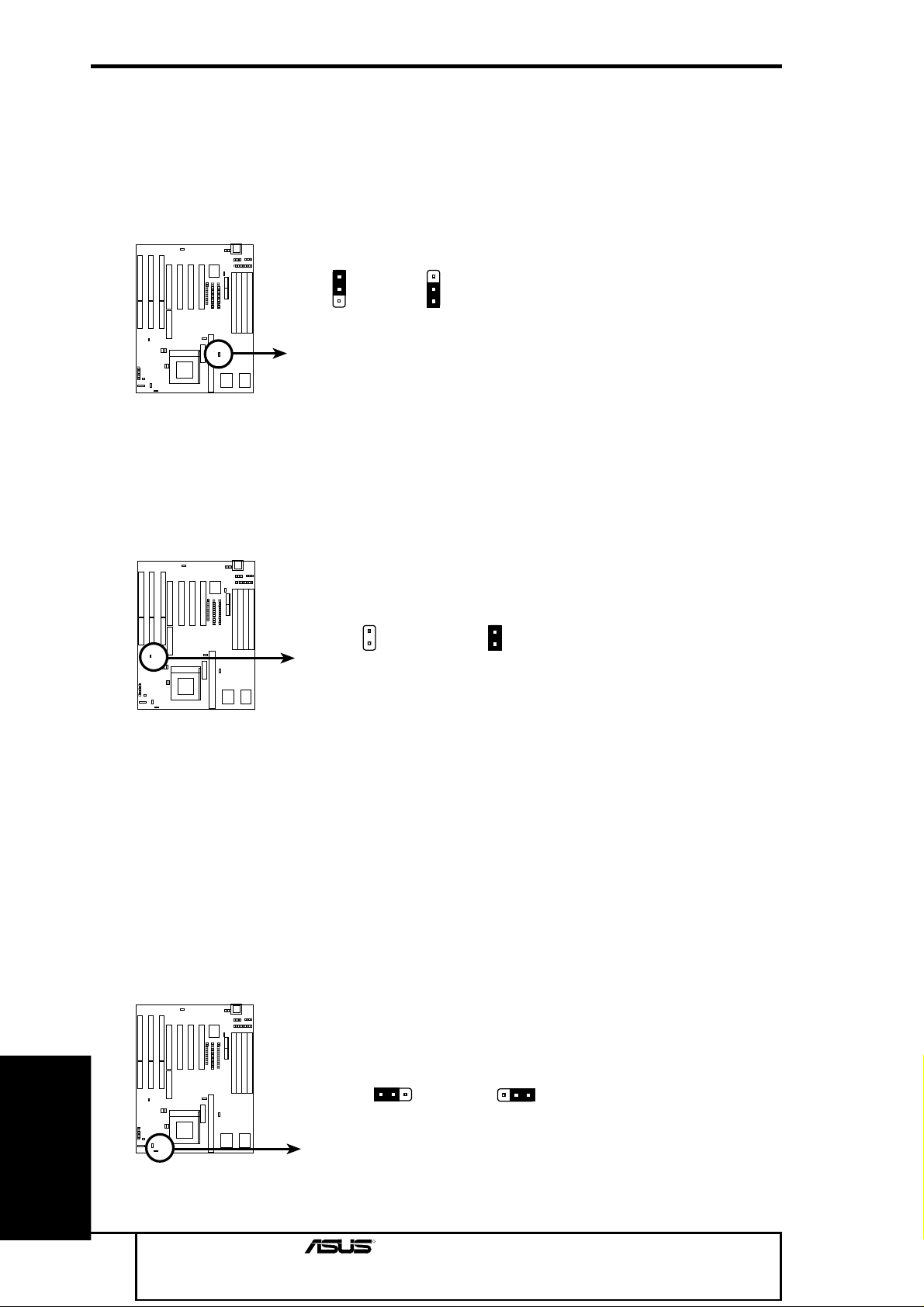

1. Sélection du dispositif d’entrée/sortie multiple à la carte mère (JP1)

Vous pouvez mettre hors fonction sélectivement chaque composant du dispositif d’entrée/

sortie multiple à la carte mère (lecteur floppy, série, parallèle et l’IrDA) par le BIOS (voir

MAQUETTE DES CARACTÉRISTIQUES DU CHIPSET) ou mettre à la fois hors fonction

tous les composants du dispositif d’entrée/sortie multiple avec le cavalier suivant afin d’utiliser

votre propre carte d’entrée/sortie multiple.

JP1

1

2

3

Mis en fonction (défaut) Mis hors fonction

JP1

1

2

3

Réglage du dispositif d’entrée/sortie multiple

(mettre en/hors fonction)

2. Programmation du BIOS Flash (JP2)

Le cavalier JP2 permet de flasher le BIOS en position Mis en fonction.

JP2

123

Mis en fonction

Nom du produit:

JP2

1

23

Mis hors fonction

(défaut)

Programmation de la secteur de démarrage

(mis en/hors fonction)

R

P/I-P55T2P4 Pentium

Révision du manuel: 3.10 Référence prompte pour les utilisateurs français

Date de publication: Janvier 1997

For French Users

Quick Reference

1

Réglage des Cavaliers

3. Réglage de la capacité totale du cache au niveau 2 (JP5)

Ce cavalier règle la capacité totale du cache au niveau 2 qui est présent. Si vous disposez des

chips cache intégrée à la carte mère (pour leur situation, voir “Plan de la carte mère”) ainsi

qu’un emplacement d’extension cache, vous disposez de 256KB. Si vous avez seulement des

chips cache intégrée à la carte mère, vous disposez de 512KB. Un module cache “ASUS” ou

“COAST” peut être utilisé pour passer de 256KB à 512KB. Sans regarder à votre combinaison

de cache, réglez les cavaliers suivants selon la capacité totale du niveau 2 du cache présente

sur la carte mère et installée comme module.

JP5

1

2

3

256KB 512KB

Réglage de la capacité totale du cache au niveau 2

(256KB/512KB)

JP5

1

2

3

4. Horloge temps réel (RTC) RAM (JP7)

Ceci efface les informations entrées par l’utilisateur et sauvegardées au CMOS RAM de

l’horloge à temps réel, comme p.ex. l’information sur le disque dur et les mots de passe. Pour

effacer les données R TC: (1) éteignez le PC, (2) court-circuitez ce cavalier , (3) allumez le PC,

(4) éteignez le PC, (5) enlevez ce cavalier, (6) allumez le PC, (7) appuyez et tenez appuyé la

touche <Delete> (effacement) pendant le démarrage et accédez à la maquette BIOS afin de

rentrer les préférences de l’utilisateur.

JP7 JP7

En opération (défaut) Effacement des données

RTC RAM (en opération/effacement des données)

5-6.Sélections du régulateur de tension à simple/double plan du CPU

Les cavaliers suivants règlent la tension alimentant le CPU. Il faut déterminer si votre CPU

utilise une alimentation simple plan ou une alimentation double plan. Si une alimentation

simple plan est utilisée pour le CPU, les sélections de l’alimentation double plan seront mises

hors fonction automatiquement. Si une alimentation double plan est utilisée pour le CPU, les

sélections de l’alimentation simple plan seront mises hors fonction automatiquement. Il est

possible d’installer simultanément un cavalier à l’alimentation simple plan et un autre cavalier à l’alimentation double plan.

5. Sélections du régulateur de tension à simple plan du CPU (JP17)

Ces cavaliers règlent la tension alimentant le CPU avec une tension simple plan. Les CPU

actuels d’Intel marqués “Pentium” sont dotés seulement d’une alimentation simple plan et

utilisent le voltage Standard de 3,38 (STD) ou le voltage de 3,5 (VRE).

Quick Reference

For French Users

JP17

1

23

STD 3,3V-3,465V (défaut)

Sélection du régulateur de tension (STD/VRE)

JP17

123

VRE 3,4V-3,6V

Nom du produit:

2

Révision du manuel: 3.10 Référence prompte pour les utilisateurs français

R

P/I-P55T2P4 Pentium

Date de publication: Janvier 1997

Réglage des Cavaliers

6. Sélection du régulateur de tension à double plan du CPU (JP20)

Ces cavaliers règlent la tension alimentant le CPU avec une tension double plan.

[1-2]

JP20

2,5 Volts

Sélection de la tension CPU Vcore

[3-4]

JP20

2,7 Volts

[5-6]

JP20

2,8 Volts

(défaut)

[7-8]

JP20

2,9 Volts

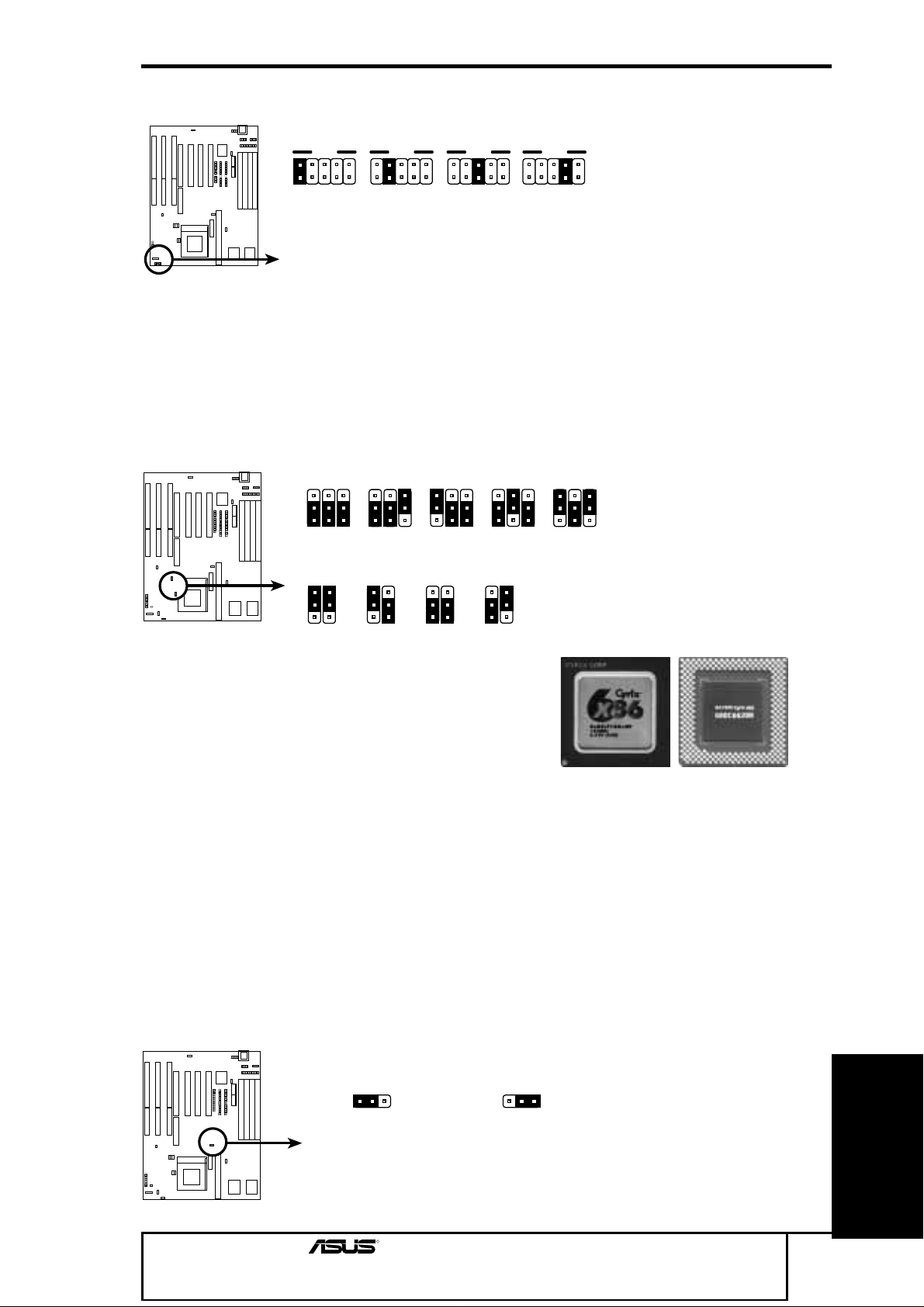

7. Sélection de la fréquence externe (BUS) du CPU (JP8, JP9, JP10)

Ces cavaliers informent la génératrice de l’horloge à quelle fréquence faut-il transmettre à

l’UC. Ceux permettent la sélection de la fréquence externe (ou l’Horloge BUS). L’Horloge

BUS multiplé par le ratio égal en fréquence interne du CPU (la vitesse annoncée par l’U.C.).

8. Ratio de la fréquence du CPU au BUS (JP11, JP12)

Ces cavaliers règlent la proportion de la fréquence entre la fréquence interne du CPU et la

fréquence externe (désignée par l’Horloge BUS). Ceux-ci doivent être réglés conjointement

avec les cavaliers JP8 à JP10 Sélection de la fréquence externe (BUS).

JP9

JP8

JP10

50MHz 55MHz 60MHz

Sélection de la fréquence de l’horloge externe du CPU (BUS)

JP12

JP11

JP9

JP8

JP10

1

2

3

JP12

JP11

JP9

JP8

JP10

1

2

3

JP12

JP11

JP9

JP8

JP10

1

2

3

66MHz

JP12

JP11

JP9

JP8

JP10

1

2

3

75MHz

1

2

3

1

2

3

1,5 x 2,0 x 2,5 x 3,0 x

CPU: Ratio de la fréquence du BUS (1,5x, 2,0x, 2,5x, 3,0x)

1

2

3

1

2

3

1

2

3

Identification du CPU CYRIX

Le CPU Cyrix supporté par la carte mère est marqué Cyrix

6x86 P166+, mais doit être Révision 2,7 ou plus avancé.

Le numéro de série se trouve au dos du CPU; ce numéro

doit être G8DC6620A ou plus avancé.

9. Capacité de la mémoire cache (JP4)

Par défaut, 64MB du RAM n’utilise que la T AG SRAM intégrée à la carte mère qui permet de

faire fonctionner la mémoire cache jusqu’à 64MB. Si vous installez le DRAM au-dessus de

64MB et désirez permettre la capacité de la mémoire cache d’être utilisée avec plus de 64MB,

il faut installer une TAG SRAM supplémentaire ou se servir d’un module cache doté d’une

TAG SRAM étendu (comme p.ex. 256KB ASUS CM1 Rév. 3,0 avec 2 TAG SRAM), mais

pas tous les deux simultanément. Ensuite, il faut régler ce cavalier à 512MB.

ATTENTION: S’il y a des chips cache DRAM (Mcache) sur la carte mère ou sur le module

cache SIMM plutôt que sur les chips SRAM accès pipeline, ce cavalier doit être réglé à

64MB, car un réglage à 512MB rendrait instable le système. Les chips Mcache ne peuvent

permettre d’améliorer la mémoire cache que jusqu’au 64MB. Pour la situation du cache au

niveau 2, voir le “Plan de la carte mère.” En cas le module cache que vous avez installé

préalablement est doté d’une T AG SRAM supplémentaire, n’installez pas un autre TAG SRAM

au socle d’amélioration de TAG SRAM.

JP4

1

23

512MB cacheable

Seulement accès SRAM

Nom du produit:

JP4

123

64MB cacheable (défaut)

Accès SRAM ou MCache

Capacité de la cache (64MB/512MB)

R

P/I-P55T2P4 Pentium

Révision du manuel: 3.10 Référence prompte pour les utilisateurs français

Date de publication: Janvier 1997

For French Users

Quick Reference

3

Loading...

Loading...