5

4

3

2

1

SYSTEM PAGE REF.

PAGE

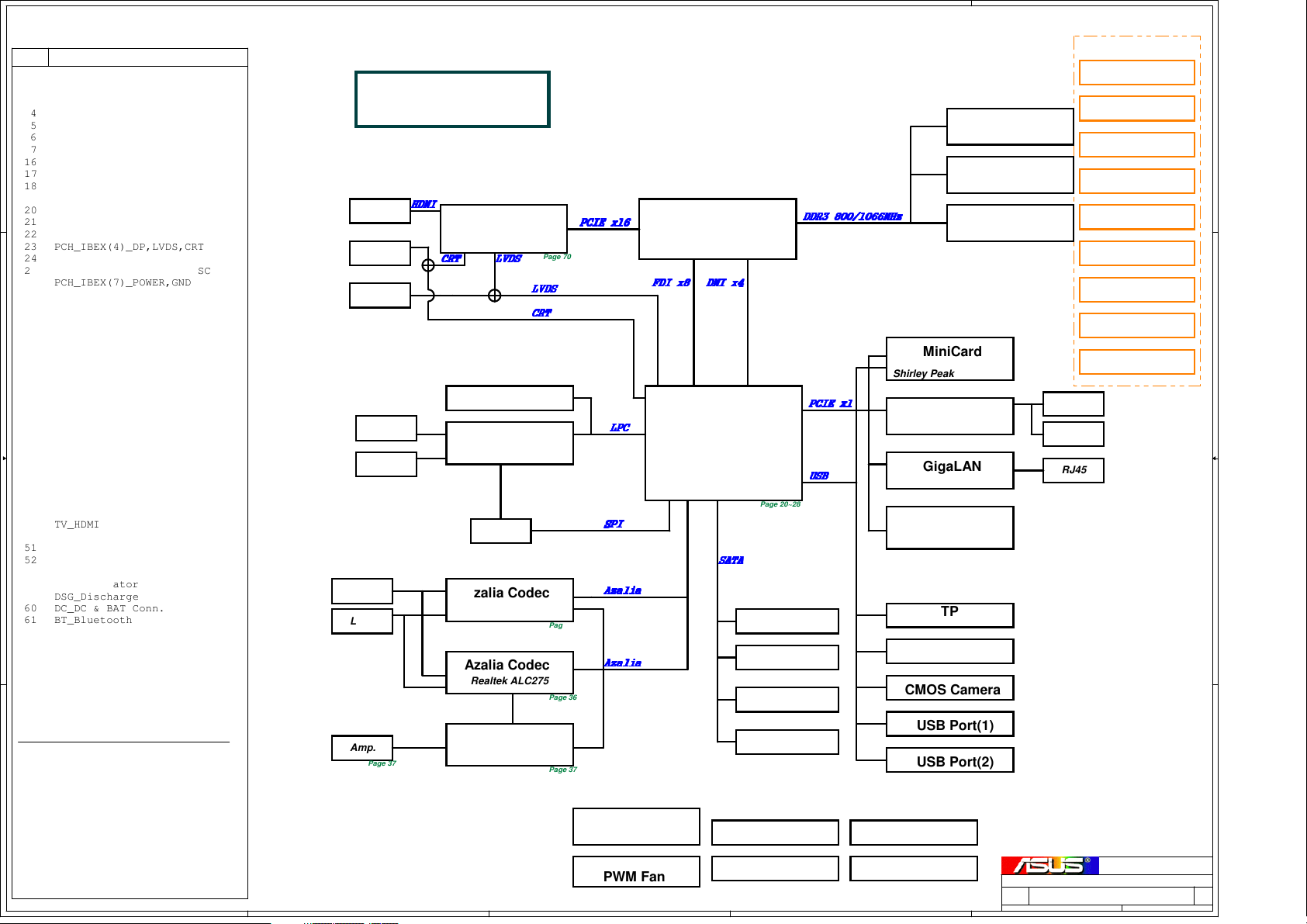

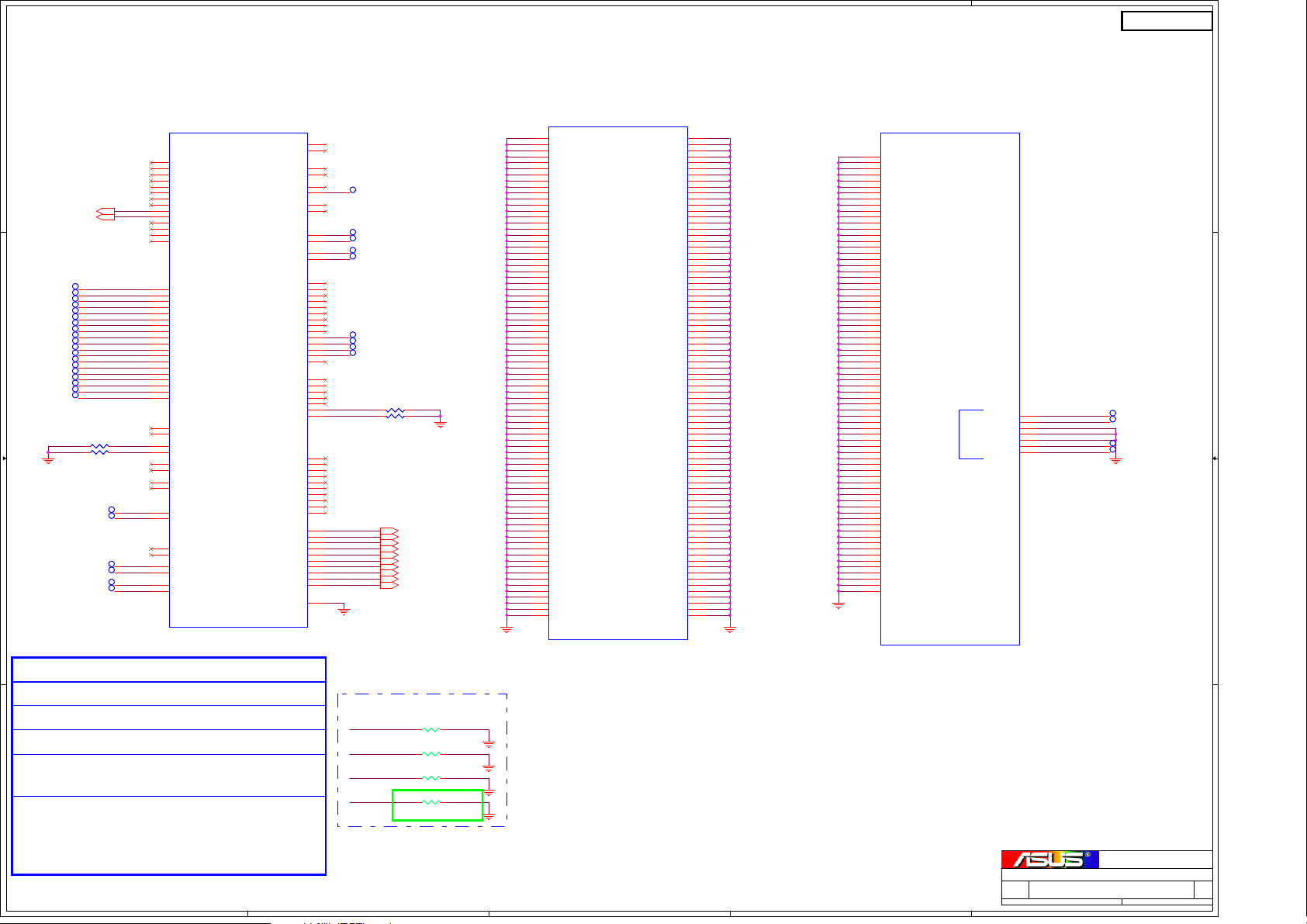

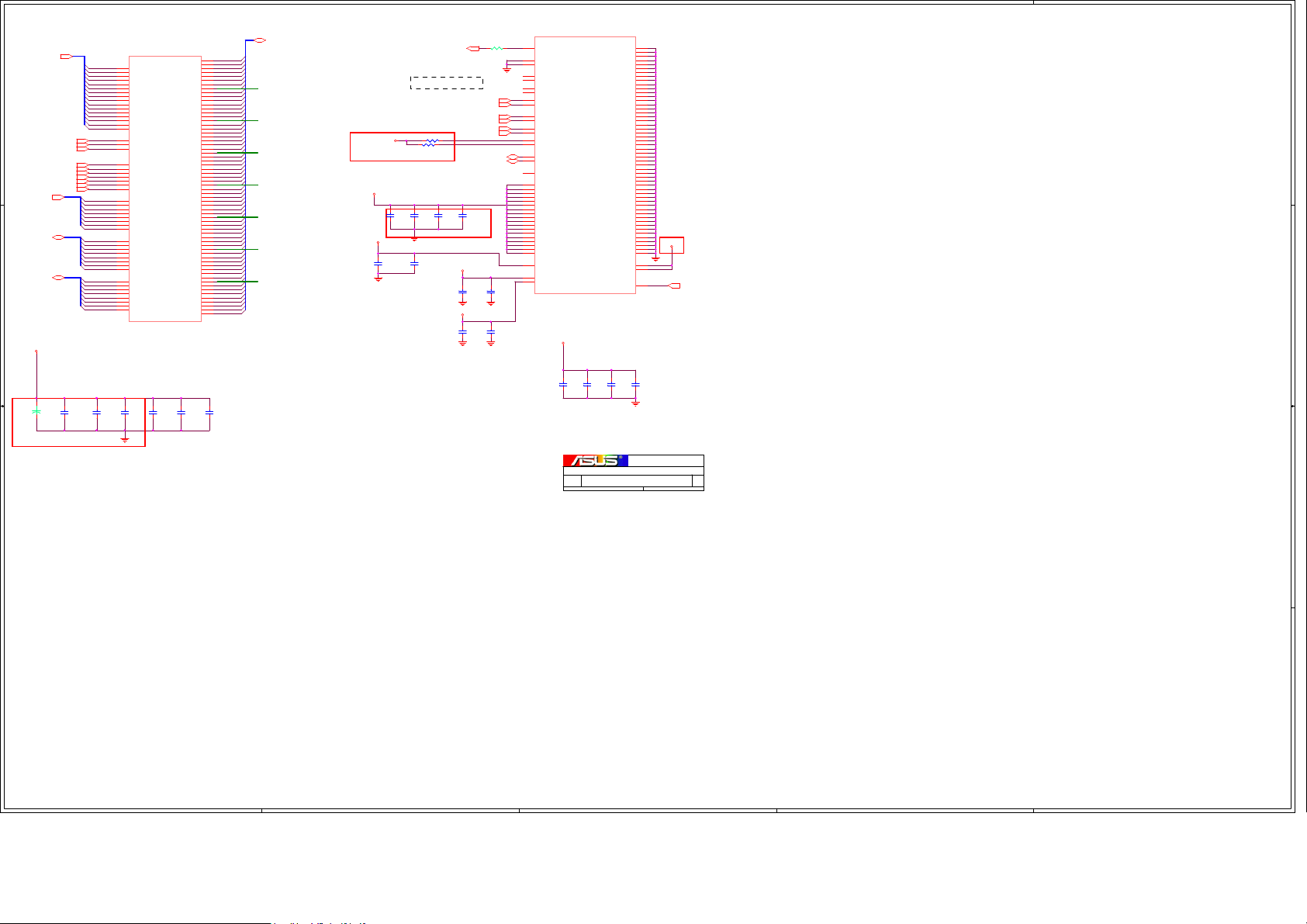

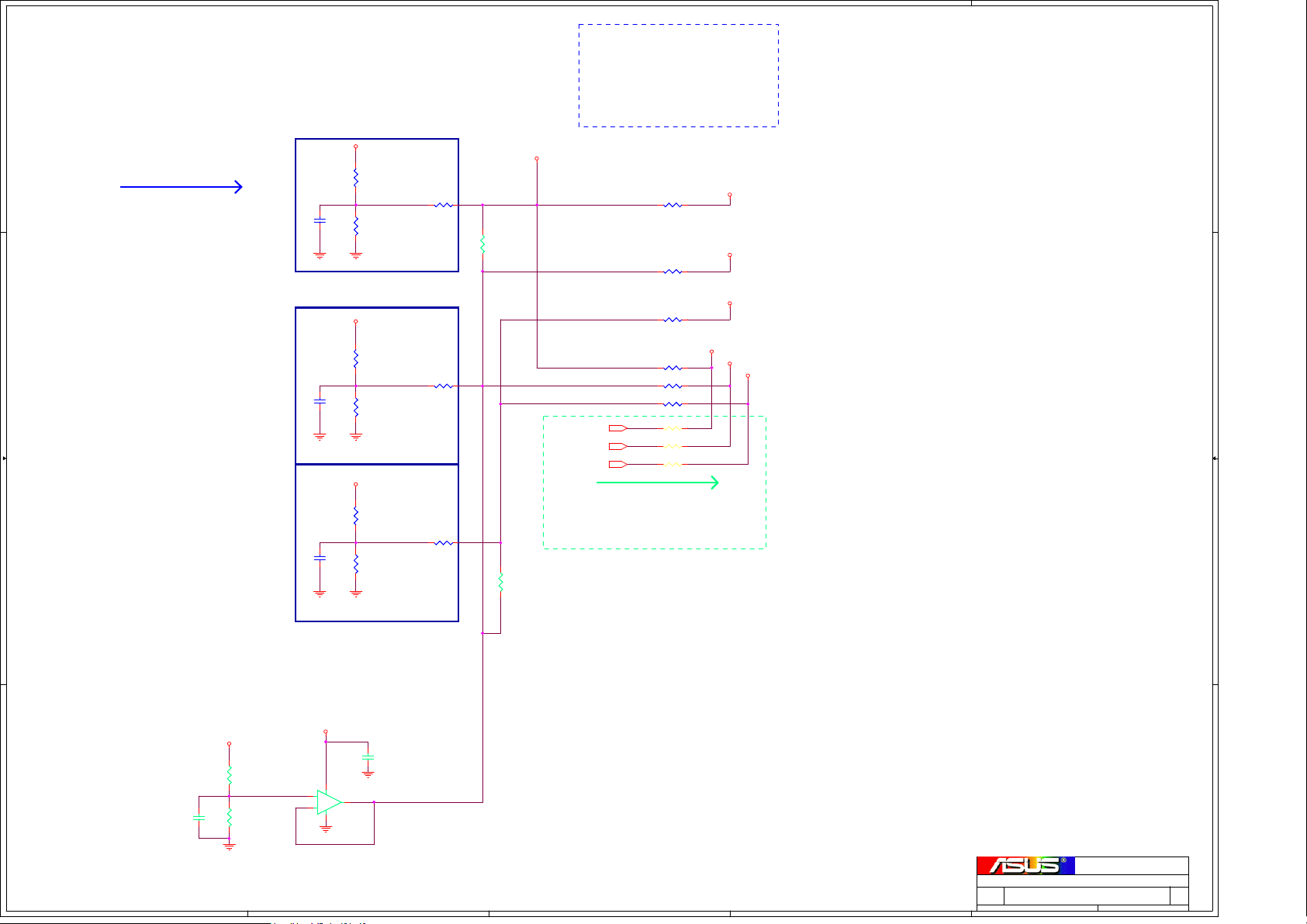

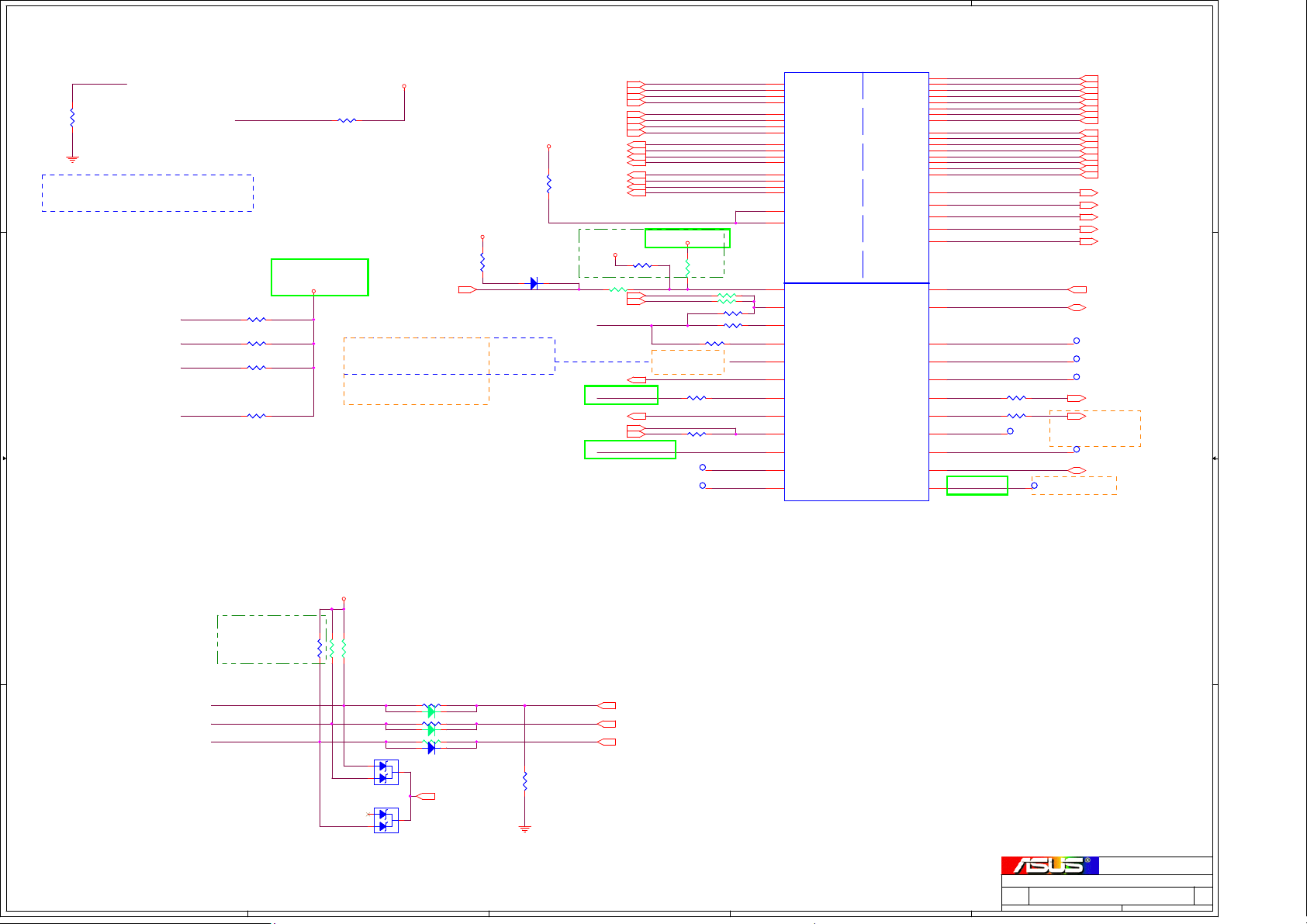

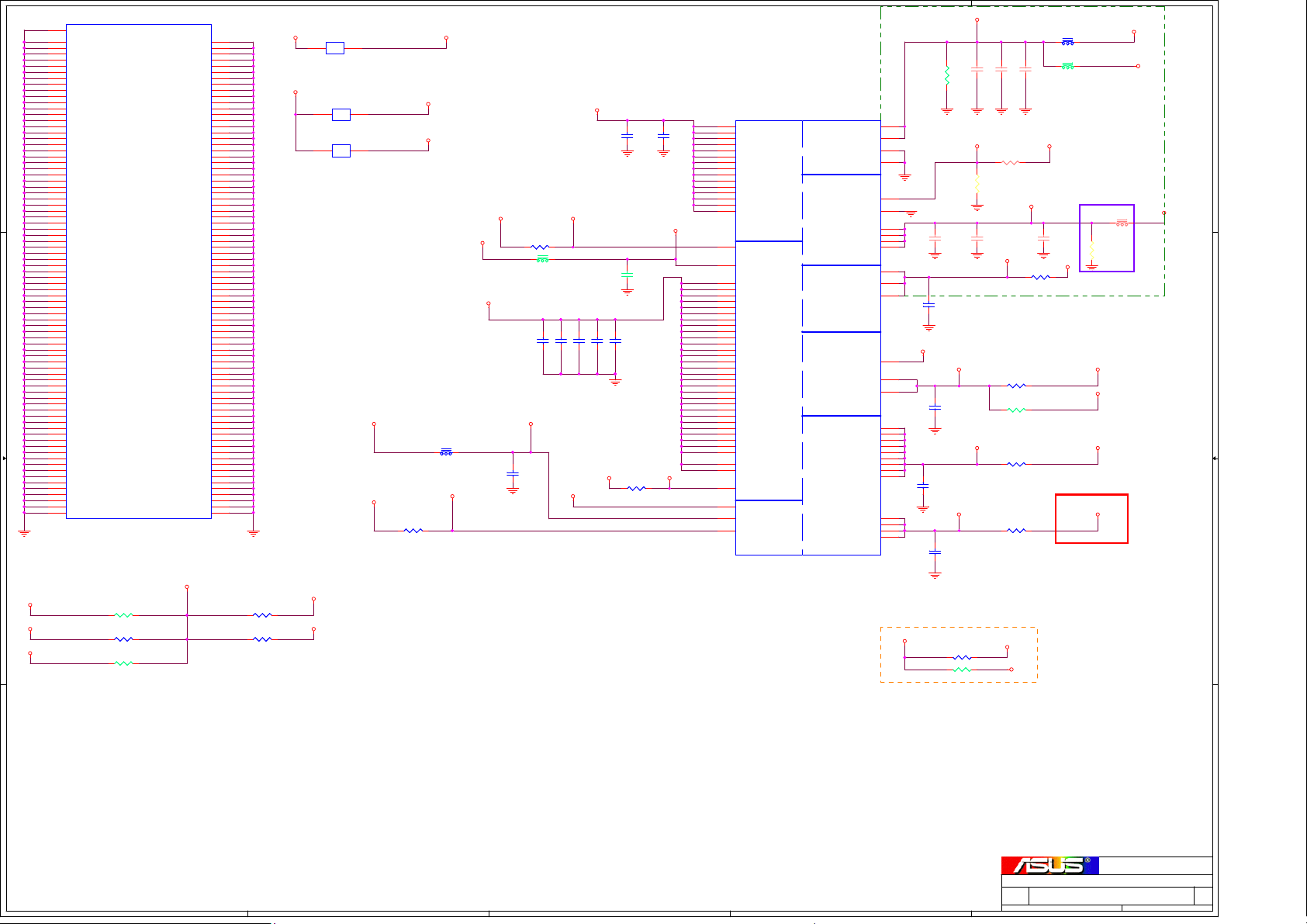

1 Block Diagram

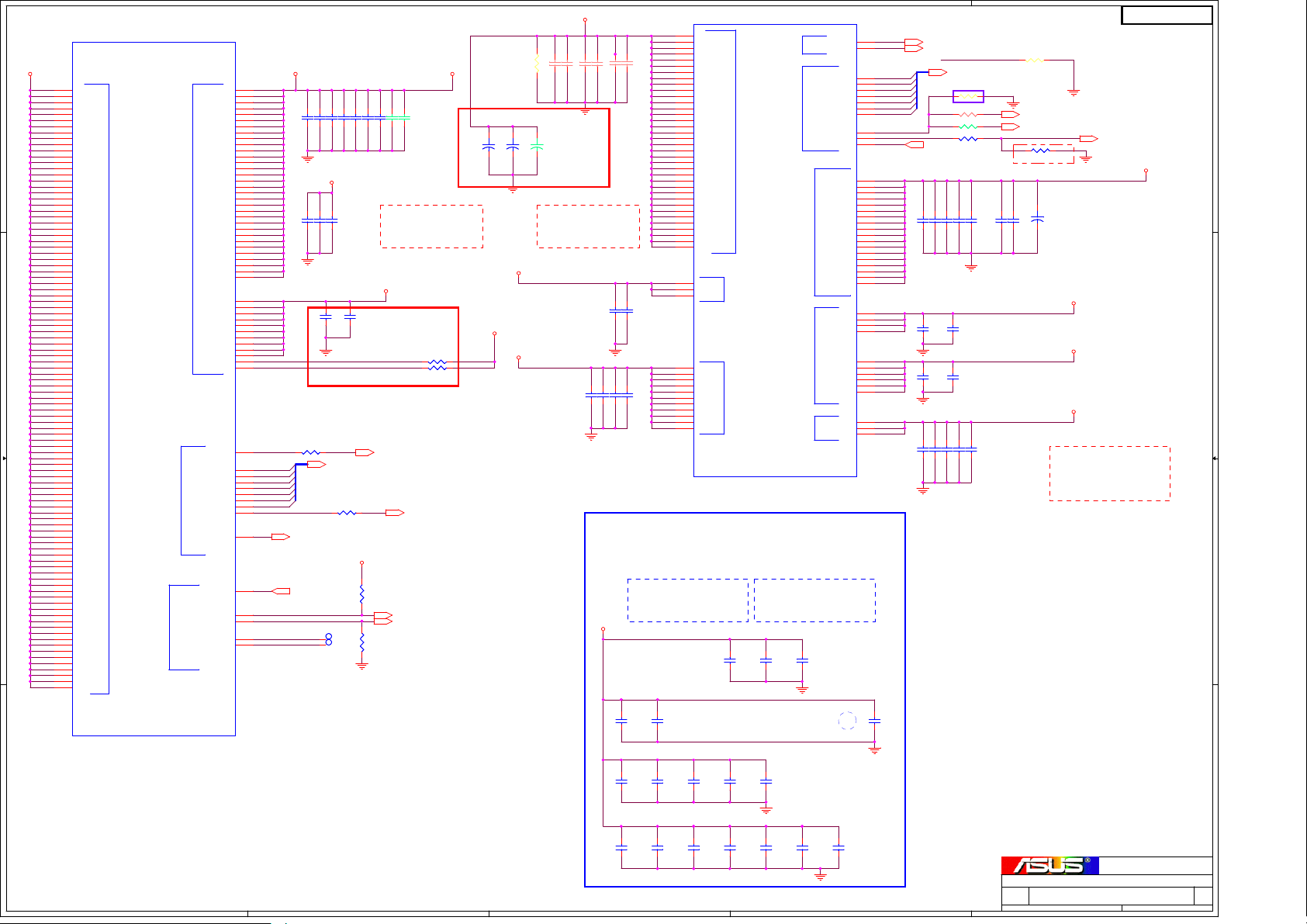

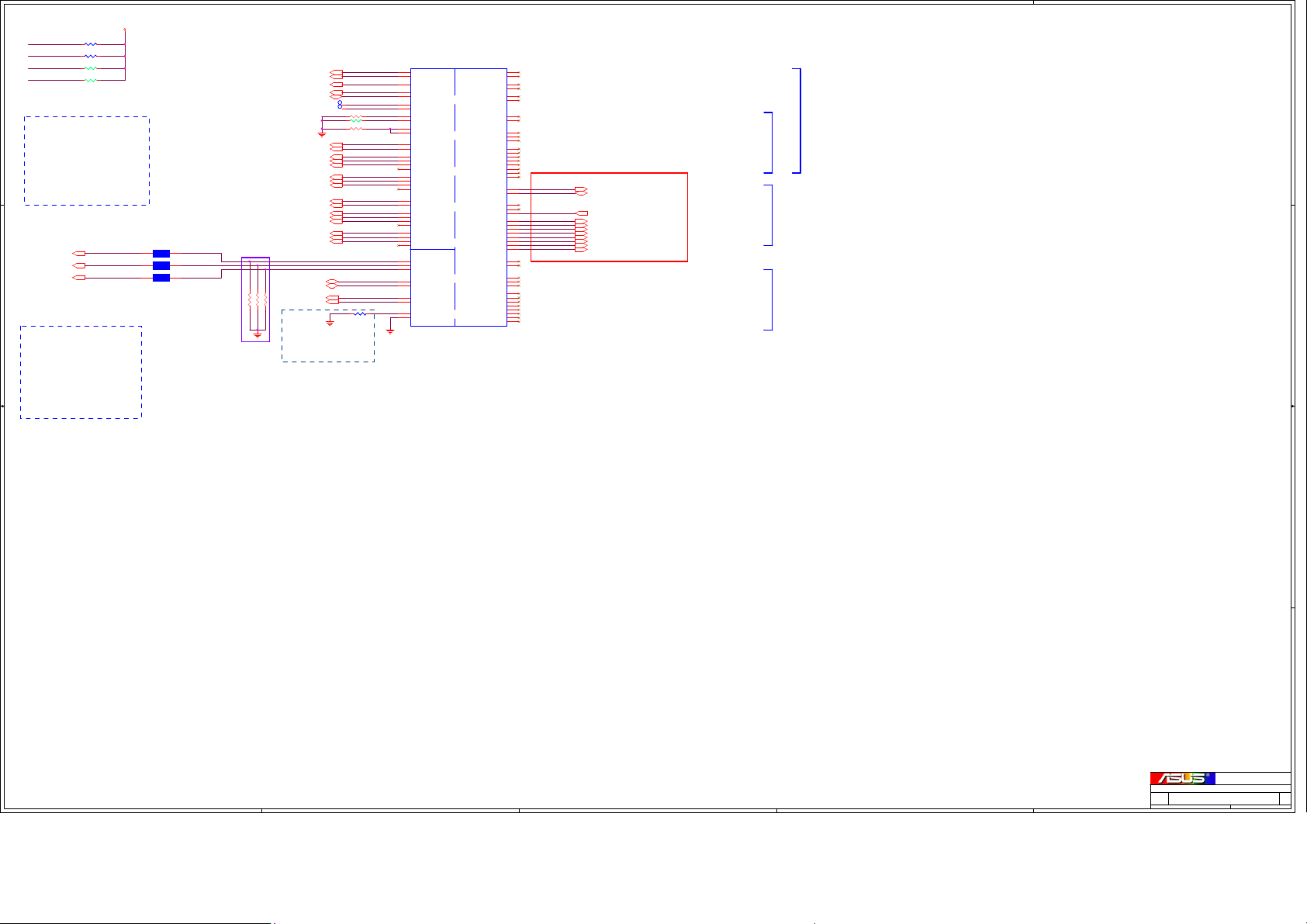

2 System Setting

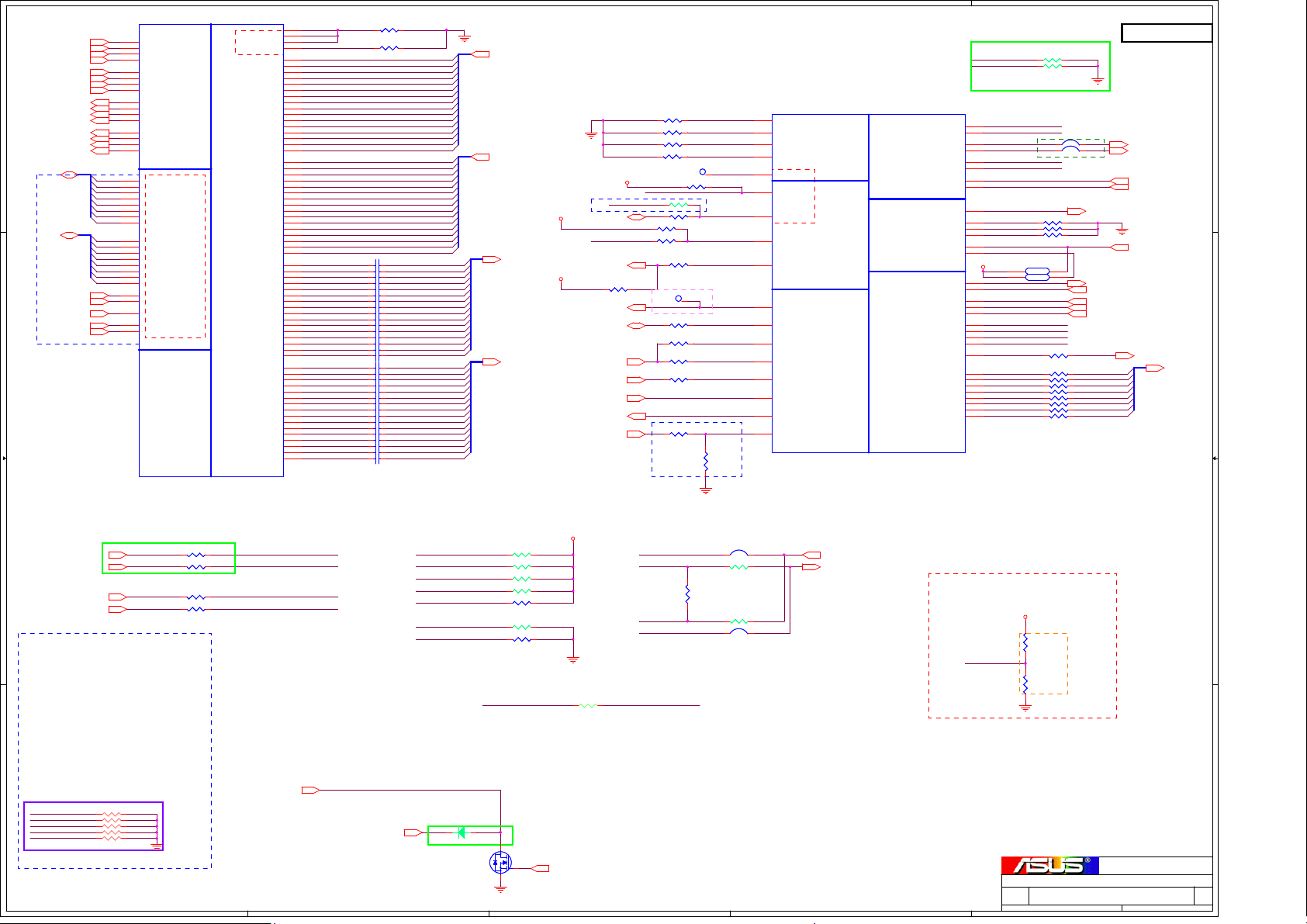

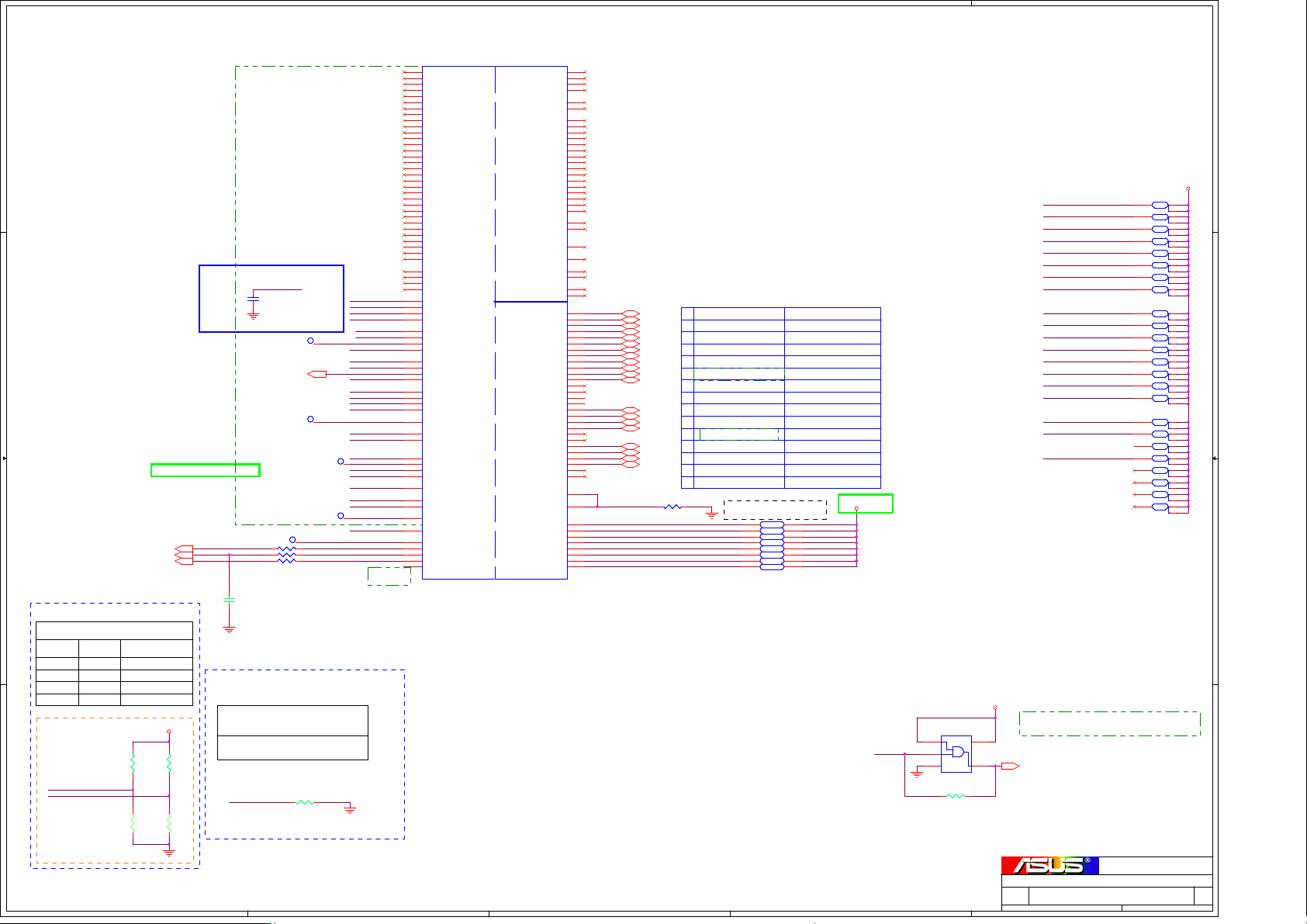

3 CPU(1)_DMI,PEG,FDI,CLK,MISC

4

D D

C C

B B

A A

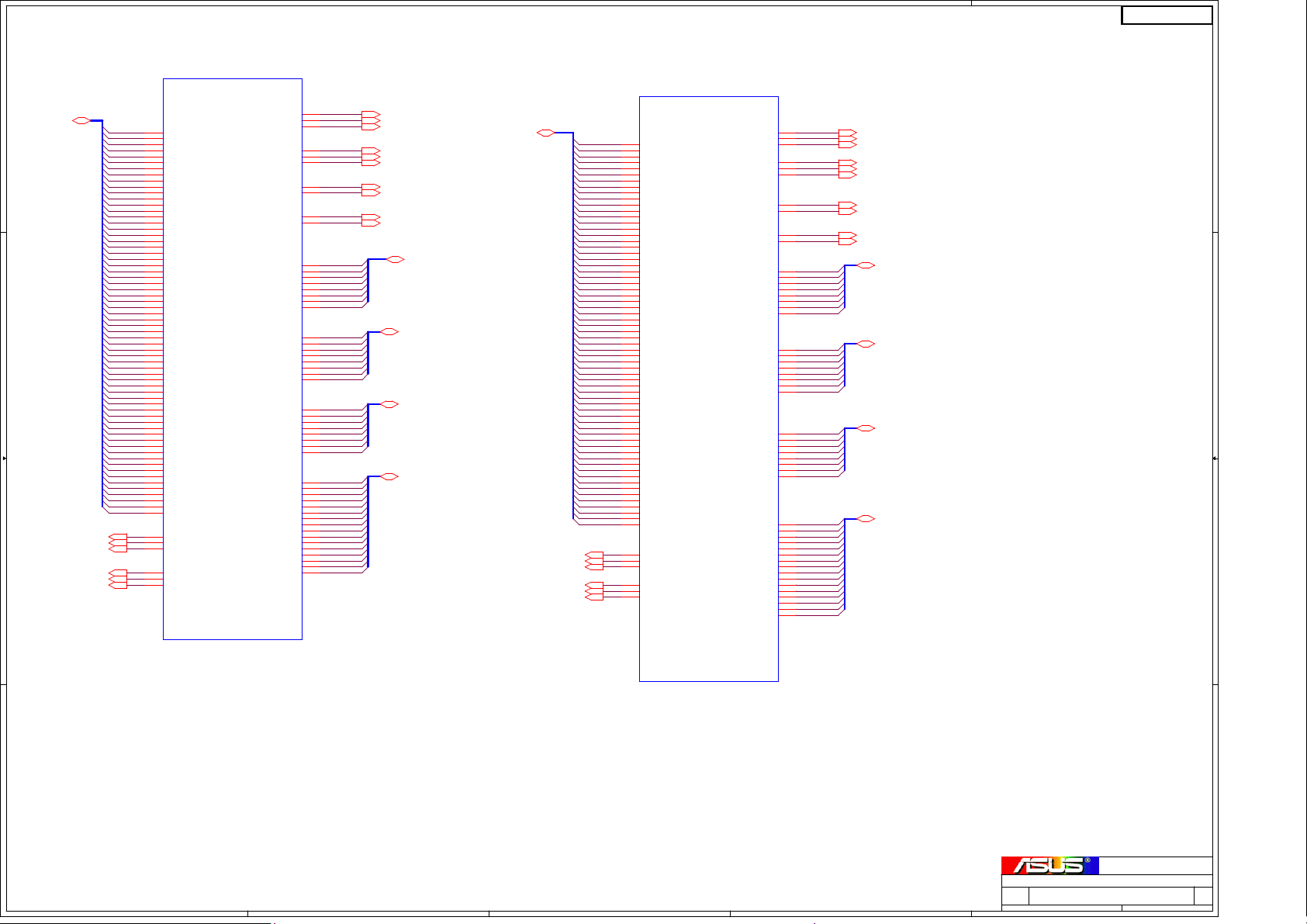

CPU(2)_DDR3

5

CPU(3)_CFG,RSVD,GND

6

CPU(4)_PWR

7

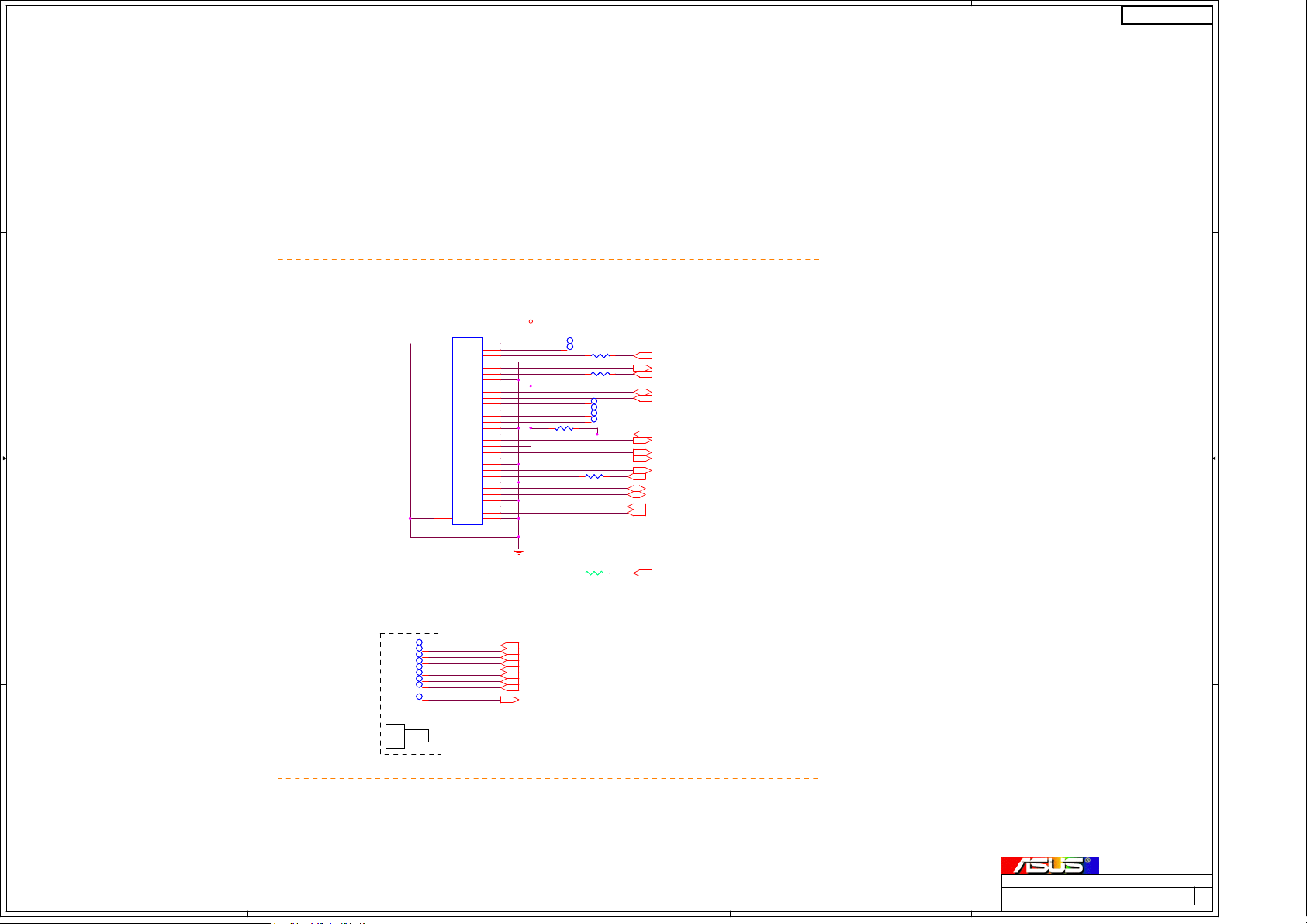

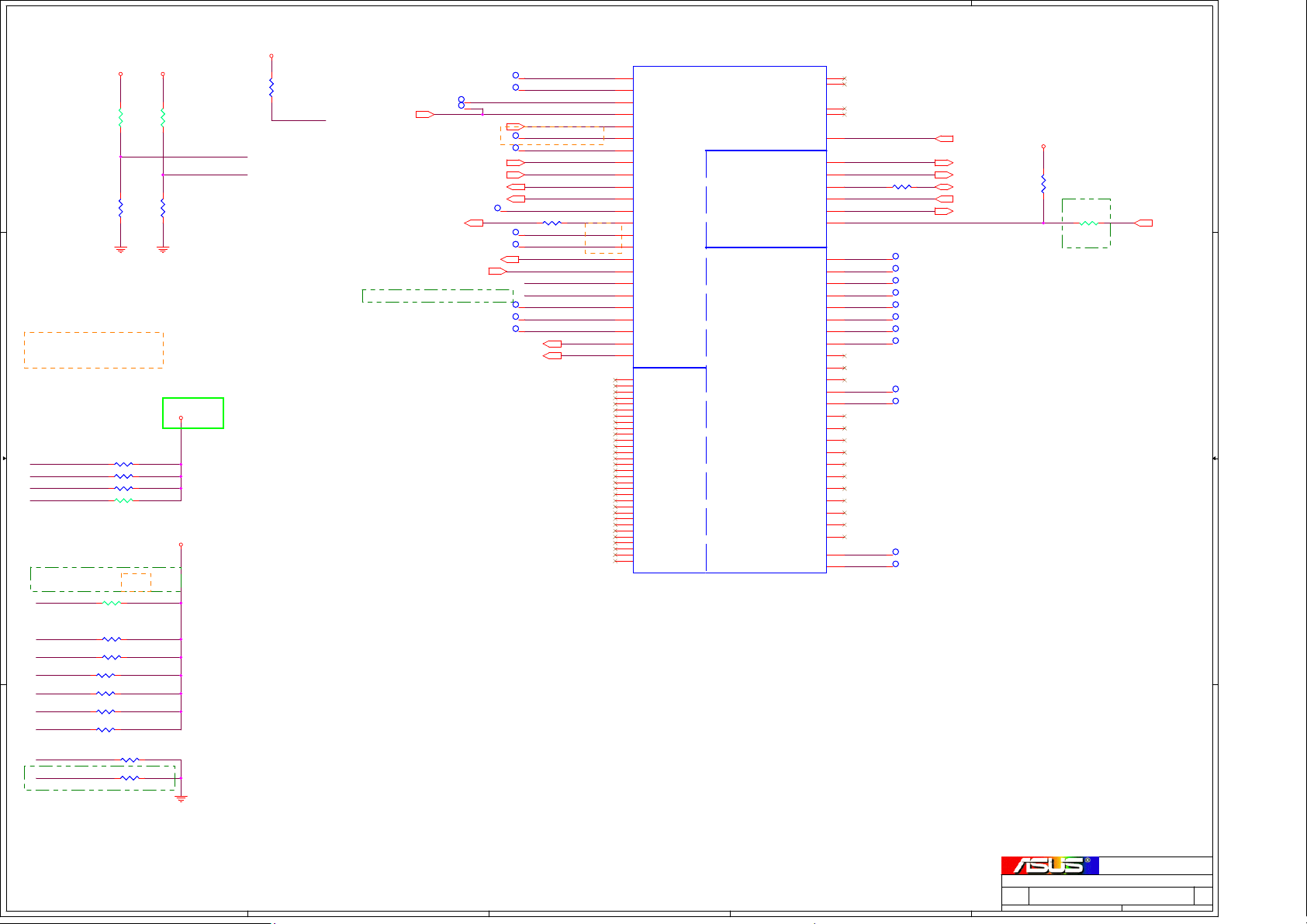

CPU(5)_XDP

16

DDR3 SO-DIMM_0

17

DDR3 SO-DIMM_1

18

DDR3 CA_DQ VOLTAGE

19 VID controller

20

PCH_IBEX(1)SATA,IHDA,RTC,LPC

21

PCH_IBEX(2)_PCIE,CLK,SMB,PEG

22

PCH_IBEX(3)_FDI,DMI,SYS PWR

23

PCH_IBEX(4)_DP,LVDS,CRT

24

PCH_IBEX(5)_PCI,NVRAM,USB

25

PCH_IBEX(6)CPU,GPIO,MISC

PCH_IBEX(7)_POWER,GND

26

27

PCH_IBEX(8)_POWER,GND

28

PCH_SPI ROM,OTH

29

CLK_ICS9LPR362

30

EC_IT8512(1/2)

31

EC_IT8512(2/2)KB, TP

32

RST_Reset Circuit

33

HANKSVILLE

34

LAN_RJ45

36

CODEC-ALC663

37

AUD_Amp & Jack

38

AUD_FM2010

40

CB_R5C833

41

CB_R5C833

42

CB_4in1 CardReader

CB_NewCard

43

BUG_Debug

44

45

CRT_LCD Panel

46

CRT_D-Sub

Display Port

47

48

TV_HDMI

50

FAN_Fan & Sensor

51

XDD_HDD & ODD

USB_USB Port *2

52

MINICARD(WLAN)

53

LED_Indicator

56

DSG_Discharge

57

DC_DC & BAT Conn.

60

BT_Bluetooth

61

TUN_TV Tuner

64

ME_Conn & Skew Hole

65

ESA_ESATA

66

PCH_XDP, ONFI

67

VGA_MXM

70

VGA_LVDS Switch

71

PW_VCORE(MAX17034)

80

PW_SYSTEM(MAX17020)

81

PW_I/O_VTT_CPU&+1.1VM

82

PW_I/O_DDR & VTT& +1.8VS83

PW_I/O_3VM & ME_+VM_PWEGD

84

PW_+VGFX_CORE(MAX17028)

86

PW_CHARGER(MAX17015)

88

PW_DETECT

90

PW_LOAD SWITCH

91

PW_PROTECT

92

PW_SIGNAL93

PW_FLOWCHART

94

Content

5

David Lewis schematic Rev 1.1

BLOCK DIAGRAM

HDMI

HDMI

Page 39

Page 37

4

Page 48

Page 46

Page 45

Page 31

Page 31

HDMIHDMI

nVIDIA N11P-GS1

LVDS

CRT

CRT

CRTCRT

LVDS

LVDSLVDS

Debug Conn.

EC

ITE IT8571

SPI ROM

Azalia Codec

Realtek ALC680

Azalia Codec

Realtek ALC275

TPA3110D2

Page 30

Page 28

Page 70

LVDS

LVDS

LVDSLVDS

CRT

CRT

CRTCRT

PCIE x16

PCIE x16

PCIE x16PCIE x16

Page 44

SPI

SPI

SPISPI

Page 35

Azalia

Azalia

AzaliaAzalia

Page 36

Azalia

Azalia

AzaliaAzalia

Page 36

Page 37

Clock Generator

ICS9LRS3197

PWM Fan

CPU

Arrandale / Clarksfield

DMI x4

DMI x4FDI x8

DMI x4DMI x4

PCH

LPC

LPC

LPCLPC

FDI x8

FDI x8FDI x8

HM55

SATA

SATA

SATASATA

Page 29

3

Discharge Circuit

Page 50

Page 3~6

Page 20~28

ODD

HDD(1)

HDD(2)

ESATA

Reset Circuit

DDR3 800/1066MHz

DDR3 800/1066MHz

DDR3 800/1066MHzDDR3 800/1066MHz

PCIE x1

PCIE x1

PCIE x1PCIE x1

USB

USB

USBUSB

Page 51

Page 51

Page 51

Page 49

Page 57

Page 32

2

HDMI

CRT

LCD Panel

Touchpad

Keyboard

INT. MIC

Page 45

Line In

Amp.

MiniCard

WLAN

Shirley Peak/ Echo Peak

NEC uPD720200

GigaLAN

MiniCard

TV Tuner

TP

Bluetooth

CMOS Camera

USB Port(1)

USB Port(2)

DC & BATT. Conn.

Skew Holes

Page 60

Page 65

DDR3 SO-DIMM

DDR3 SO-DIMM

DDR3 SO-DIMM

Page 16~18

Page 53

USB3.0

Page 54

Page 33

Page 64

Page 61

Page 55

Page 65

Page 49

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

USB3.0

RJ45

Power

VCORE

System

1.5VS & 1.05VS

DDR & VTT

+2.5VS

Charger

Detect

Load Switch

Power Protect

Page 54

Page 54

Page 34

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

David Lewis

David Lewis

David Lewis

1

Page 80

Page 81

Page 82

Page 83

Page 84

Page 86

Page 90

Page 91

Page 92

Block Diagram

Block Diagram

Block Diagram

Daniel Huang

Daniel Huang

Daniel Huang

1 99Wednesday, April 07, 2010

1 99Wednesday, April 07, 2010

1 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

5

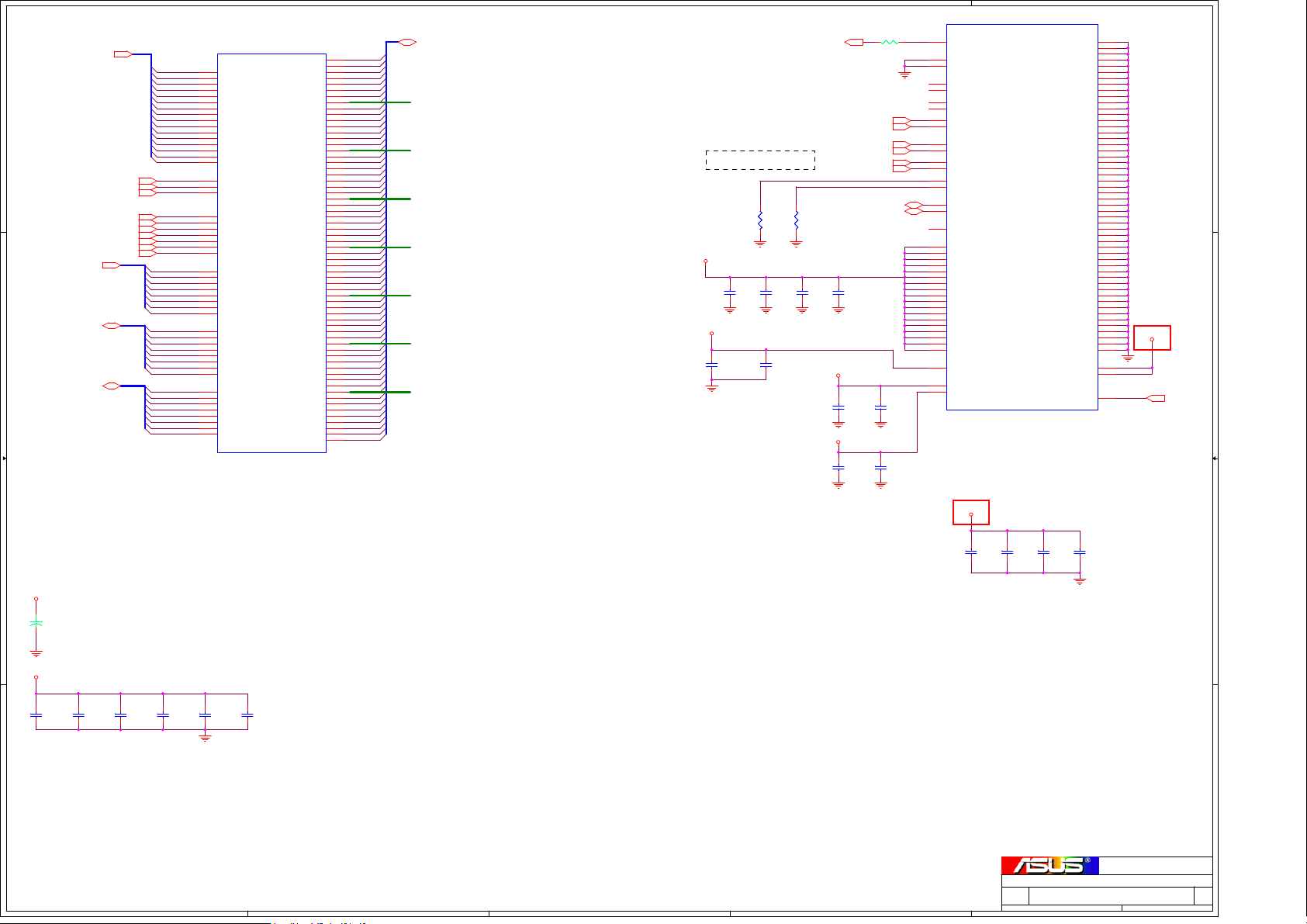

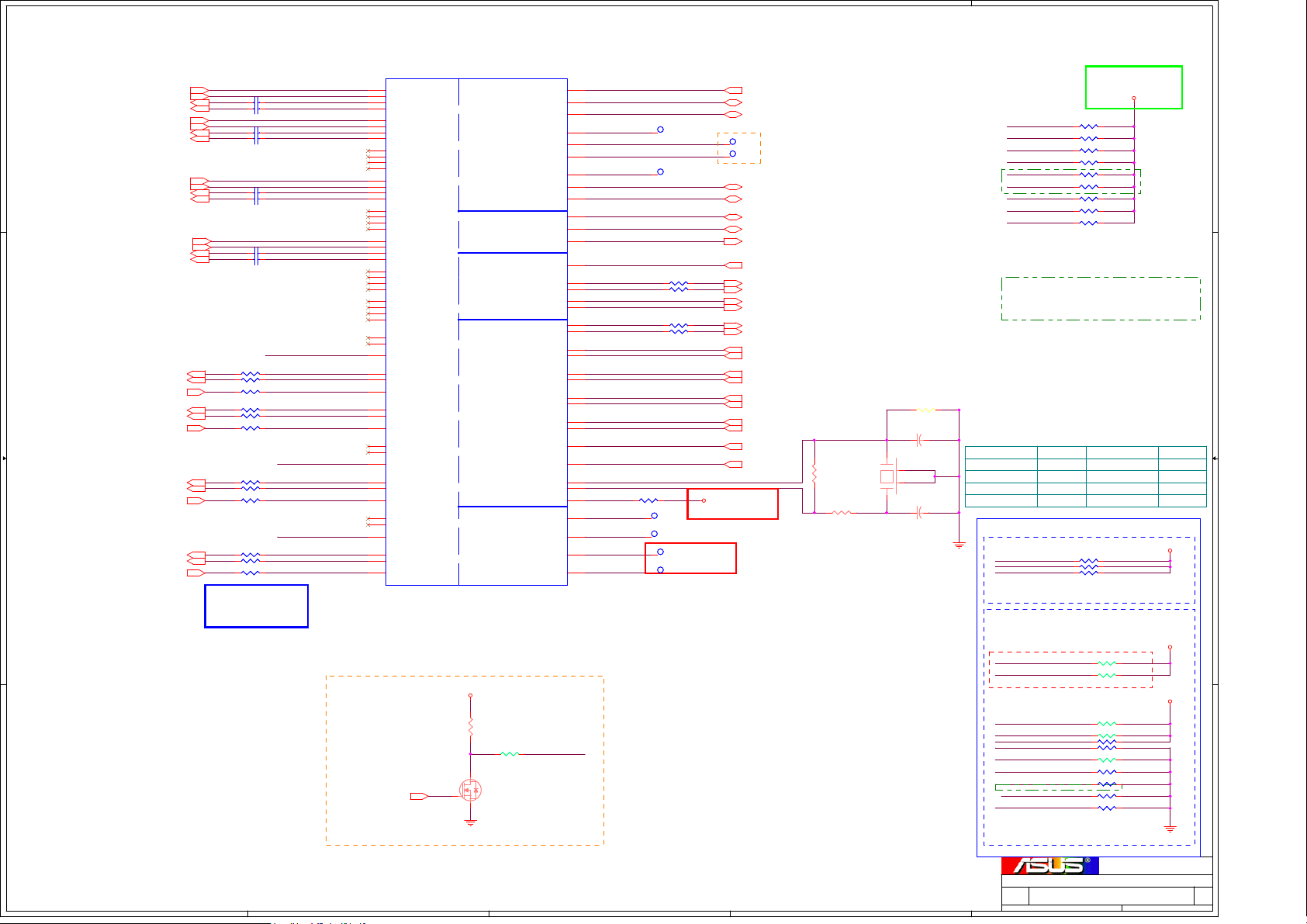

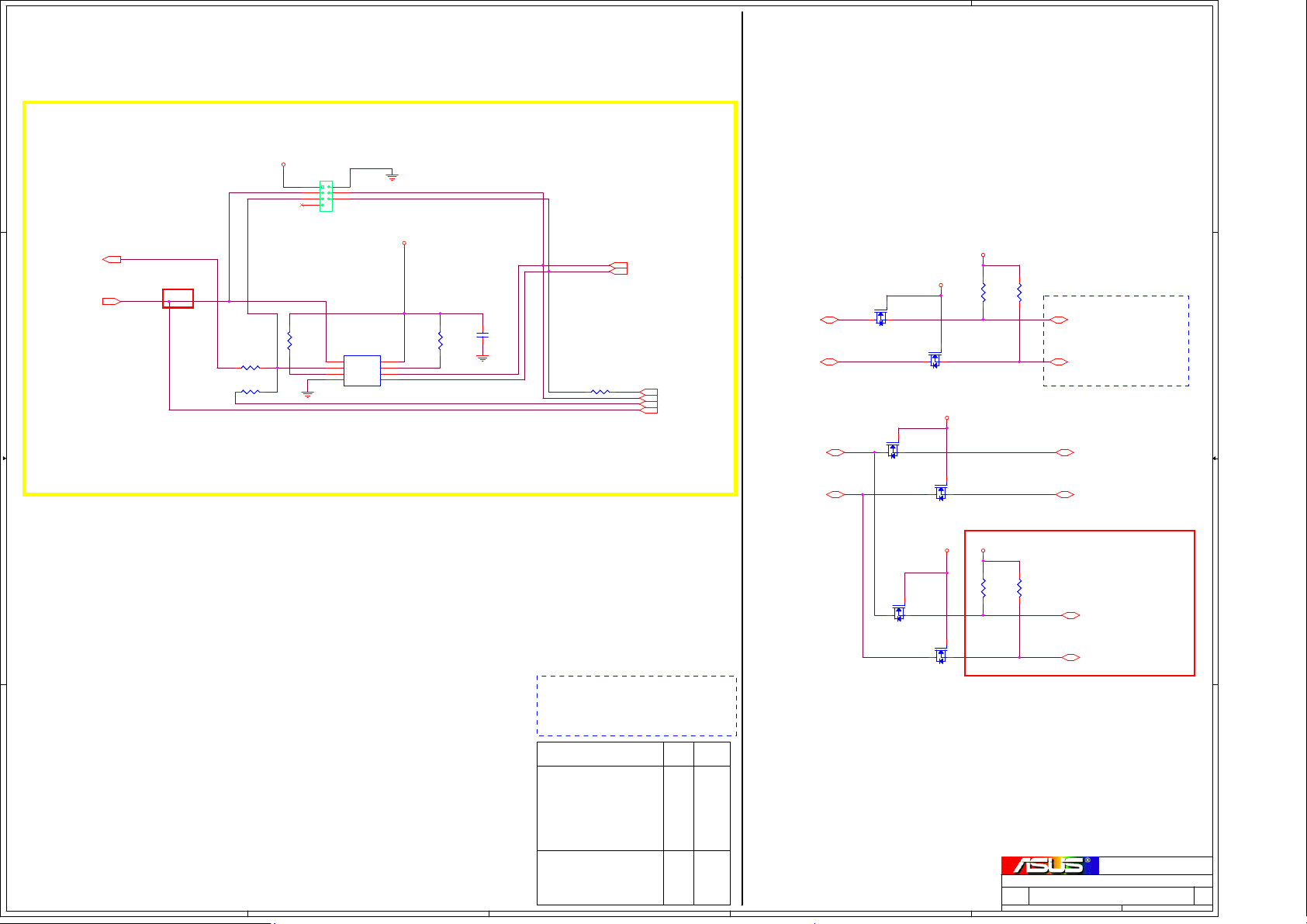

PCH_IBEX

GPIO

D D

C C

B B

A A

PCH_IBEX

GPIO

GPIO 00

GPIO 01

GPIO [2:5]

GPIO 06

GPIO 07

GPIO 08

GPIO 09

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16 +3VS

GPIO 17 +3VSGPI

GPIO 18 +3VS

GPIO 19 +3VS

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24 +3VSUS

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39 +3VS

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

GPIO 47

GPIO 48

GPIO 49

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 59

GPIO 60

GPIO 61

GPIO 62

GPIO 63

GPIO 64

GPIO 65

GPIO 66

GPIO 67

GPIO 72

GPIO 73

GPIO 74

GPIO 75

5

GPI

GPI

GPI

GPI

GPI

GPI

Native

Native

GPI

Native

GPI

Native

GPO

GPI

Native

GPI

Native

GPI

GPO

Native

GPO

Native

Native

GPO

GPO

Native

GPO

Native

GPIO

GPI

GPI

GPO

GPO

GPO

GPI

GPI

Native

Native

Native

Native

Native

Native

Native

GPI CLKREQ_PEG#

GPI

Native

Native

Native

GPO

Native

Native

GPO

GPIO

Native

Native

Native

Native

Native

Native

Native

Native

Native

Native

Native

Native

GPIO

Signal NameUse As Power

NC_TP

NC_TP

-

HPD_INTR#

USB3_SMI#

EXT_SMI#

USB_OC5#

USB_OC6#

EXT_SCI#

NC_TP

NC_TP

USB_OC7#

BT_LED

DGPU_HOLD_RST#

DGPU_PWROK

CLKREQ1_TV#

SATA1GP

CLKREQ2#_WLAN

SATA0GP

WLAN_LED

NC_TP

NC_TP

CLK_REQ3#

CLKREQ4_USB#

NC_TP

WLAN_ON#

- ME_SusPwrDnAck

ME_AC_PRESENT

PM_CLKRUN#

HDA_DOCK_EN#

STP_PCI#

SATA_CLK_REQ#

dGPU_PWR_EN#_GPIO36

DGPU_PRSNT#

PCB_ID0

PCB_ID1

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

CLK_REQ5#

NC_TP

NC_TP

NC_TP

PCH_TEMP_ALERT#GPO

PCI_REQ1#

PCI_GNT1#

dGPU_SELECT#

DGPU_PWM_SELECT#_R

PCI_REQ3#

PCI_GNT3#Native

CLKREQ_GLAN#

BT_ON

SML1_CLK

USB_OC0#

SML0ALERT#

NC_TP

NC_TP

NC_TP

NC_TP

NC_TP

EDID_SELECT#

NC_TP

PM_BATLOW#

CLK_REQ0#

SMLALERT#

SML1_DATA

4

Internal &

External

Pull-up/down

EXT PU

EXT PU

EXT PU

EXT PU

EXT PU (Not used)

EXT PU & INT PU

EXT PU (Not used)

EXT PU (Not used)

EXT PU

-

INT PD

EXT PU (Not used)

EXT PD

EXT PU (Not used)

EXT PD & INT TBD

EXT PD

EXT PU

EXT PD

EXT PU

-

INT PU

-

EXT PU (Not used)

EXT PD

-

-

EXT PU

EXT PU

EXT PU

EXT PU

EXT PD

EXT PU/PD

EXT PD

EXT PD

EXT PD

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU

EXT PU (Not used)

EXT PU (Not used)

EXT PD

EXT PU (Not used)

EXT PU

EXT PU (Not used)

INT PU

EXT PU/PD

EXT PU/PD

EXT PU

INT PU

EXT PD

EXT PU(DIODE)

EXT PU

EXT PU (Not used)

EXT PU

-

-

-

INT TBD

INT TBD

INT TBD

INT TBD

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU

4

+3VS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+5VS

+3VS

+5VS

+3VS

+5VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

EC

IT8512

3

EC GPIO

Use As Signal Name

GPA0

GPA1

GPA2

GPA3

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPB7

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPF0

GPF1

GPF2

GPF3

GPF4

GPF5

GPF6

GPF7

GPG0

GPG1

GPG2

GPG6 GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6 CAP_LED#

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

GPI7

GPJ0

GPJ1

GPJ2

GPJ4

GPJ5 LVDS_GPU_SW

O

PWR_LED#

O

CHG_LED#

CHG_FULL_LED#

LCD_BL_PWM

O

FAN0_PWM

O

KB_LED_PWM

-

BATSEL_0

O

BATSEL_1

O

-

IO

SMB0_CLK

IO

SMB0_DAT

O

A20GATE

O

RCIN#

PM_RSMRST#

O

-

IO

SMB1_CLK

IO

SMB1_DAT

O

PM_PWRBTN#

AC_IN_OC#

I

OP_SD#

O

BAT1_IN_OC#

I

RFON_SW#

I

PWRLIMIT#

I

PM_SUSC#

I

I

BUF_PLT_RST#

O

EXT_SCI#

O

EXT_SMI#

LCD_BACKOFF#

O

FAN0_TACH

I

VSUS_ON

O

EGAD (IT8301 Address/Data connect)

O

EGCS (IT8301 Cycle Start connect)

O

EGCLK (IT8301 Clock connect)

O

PWR_SW#

I

LID_SW#

I

PCH_SPI_OV

O

EXP_GATE#

I

TP_CLK

I

TP_DAT

IO

THRO_CPU

O

-

PM_SUSB#

I

-

IO

PM_CLKRUN#

O

GFX_VR_ON

CHG_EN

O

O

SUSC_EC#

O

SUSB_EC#

O

-

O

-

I

SUS_PWRGD

I

ALL_SYSTEM_PWRGD

I

VRM_PWRGD

I

GFX_VR

I

-

I

-

I

-

O

CPU_VRON

O

PM_PWROK

O

VSET_EC

O

ISET_ECGPJ3

O

-

O

3

2

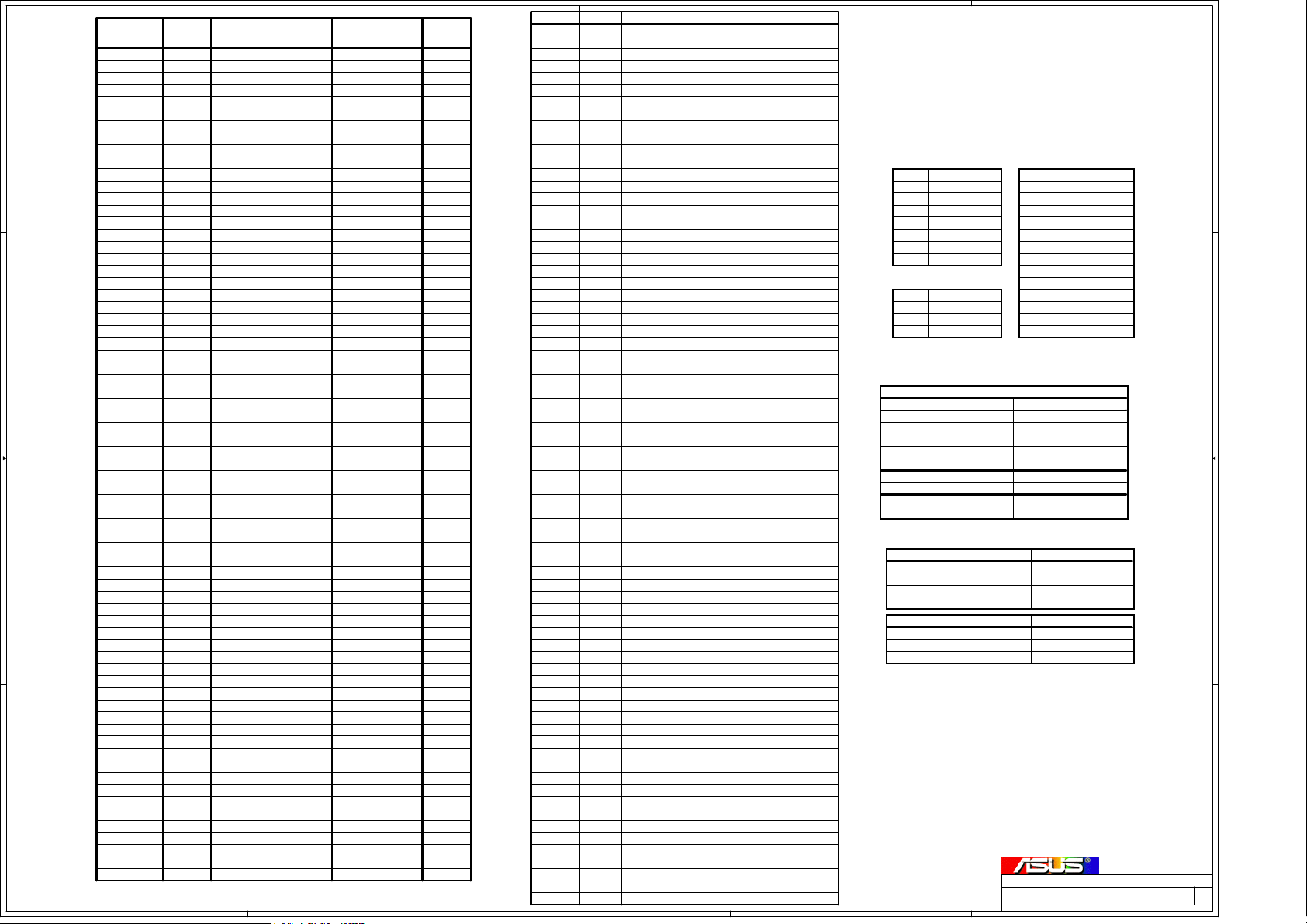

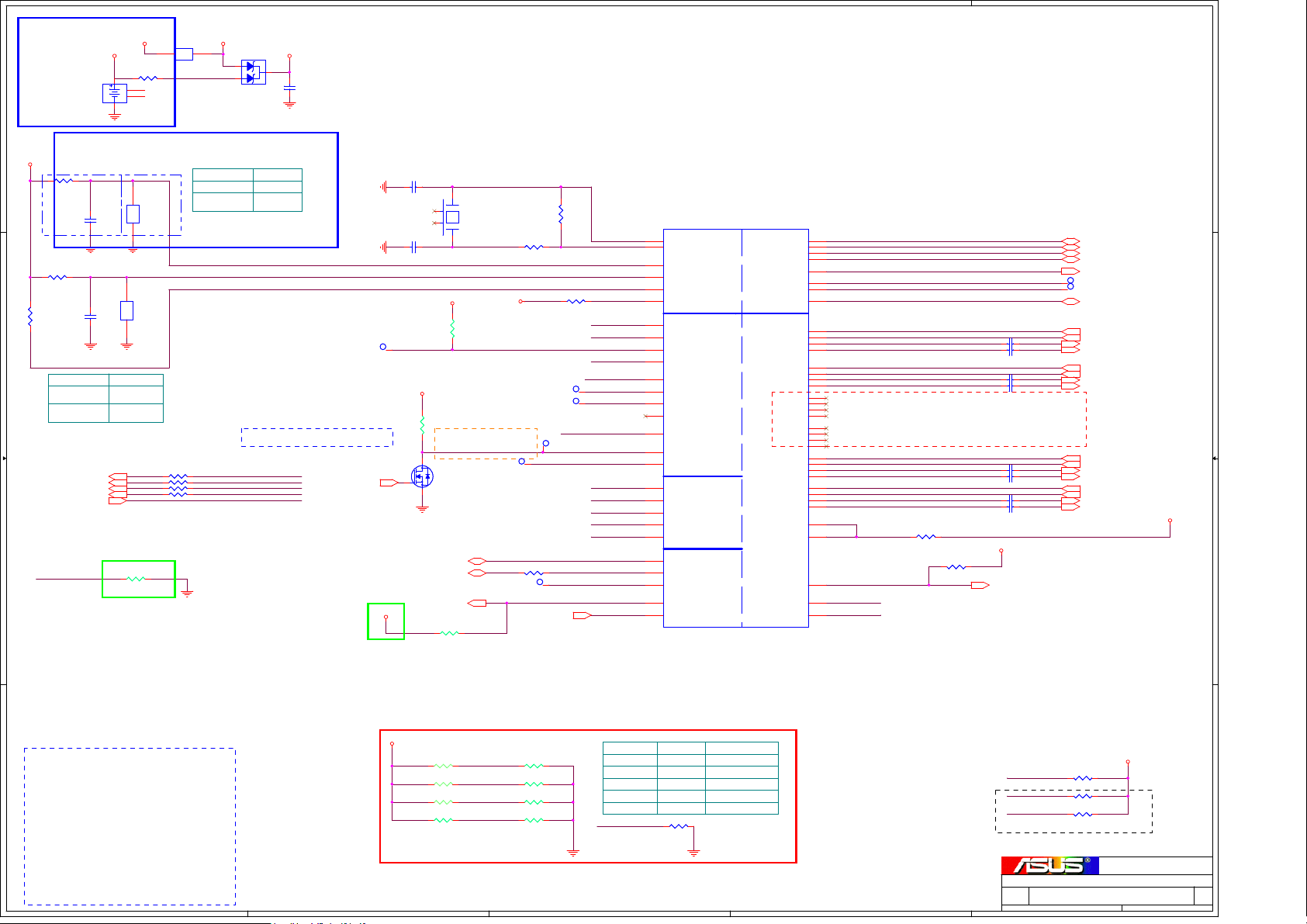

PCIE 1

PCIE 2

Minicard WLAN

PCIE 3

PCIE 4

PCIE 5

PCIE 6

GLAN

PCIE 7

PCIE 8

SATA 0

SATA HDD (1)

SATA1

SATA ODD

SATA4

SATA5

SM_BUS ADDRESS :

PCH Master

SM-Bus Device

Clock Generator(ICS9LRS3197)

SO-DIMM 0 1010000x ( A0 )

SO-DIMM 1

VID Controller(ASM8272)

WiFi/WiMax

EC Master (SMB1)

SM-Bus Device

CPU Thermal Sensor(G781) 1001100x ( 98 )

Device Identification

CPU Thermal Sensor P/N:

06G023048011

1st

S

S

S

Clock Gen P/N:

1st

06G011604010

S

S

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

USB 0 USB Port (1)

USB 1

USB 2

USB 3

USB 4

USB 5

USB 6

USB 7

USB 8

USB 9

USB 10

USB 11

USB 12

USB 13

SM-Bus Address

1101001x ( D2 )

1010001x ( A2 )

0011011x ( 36 )

N/A

SM-Bus Address

component name

G781F

component name

ICS9LRS3197

Size Project Name

Size Project Name

Size Project Name

C

C

C

1

USB Port (3)

USB Port (4)

Card Reader(2.0)

WiFi/WiMax

Camera

Bluetooth

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

David Lewis

David Lewis

David Lewis

1

System Setting

System Setting

System Setting

Daniel Huang

Daniel Huang

Daniel Huang

2 99Wednesday, April 07, 2010

2 99Wednesday, April 07, 2010

2 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

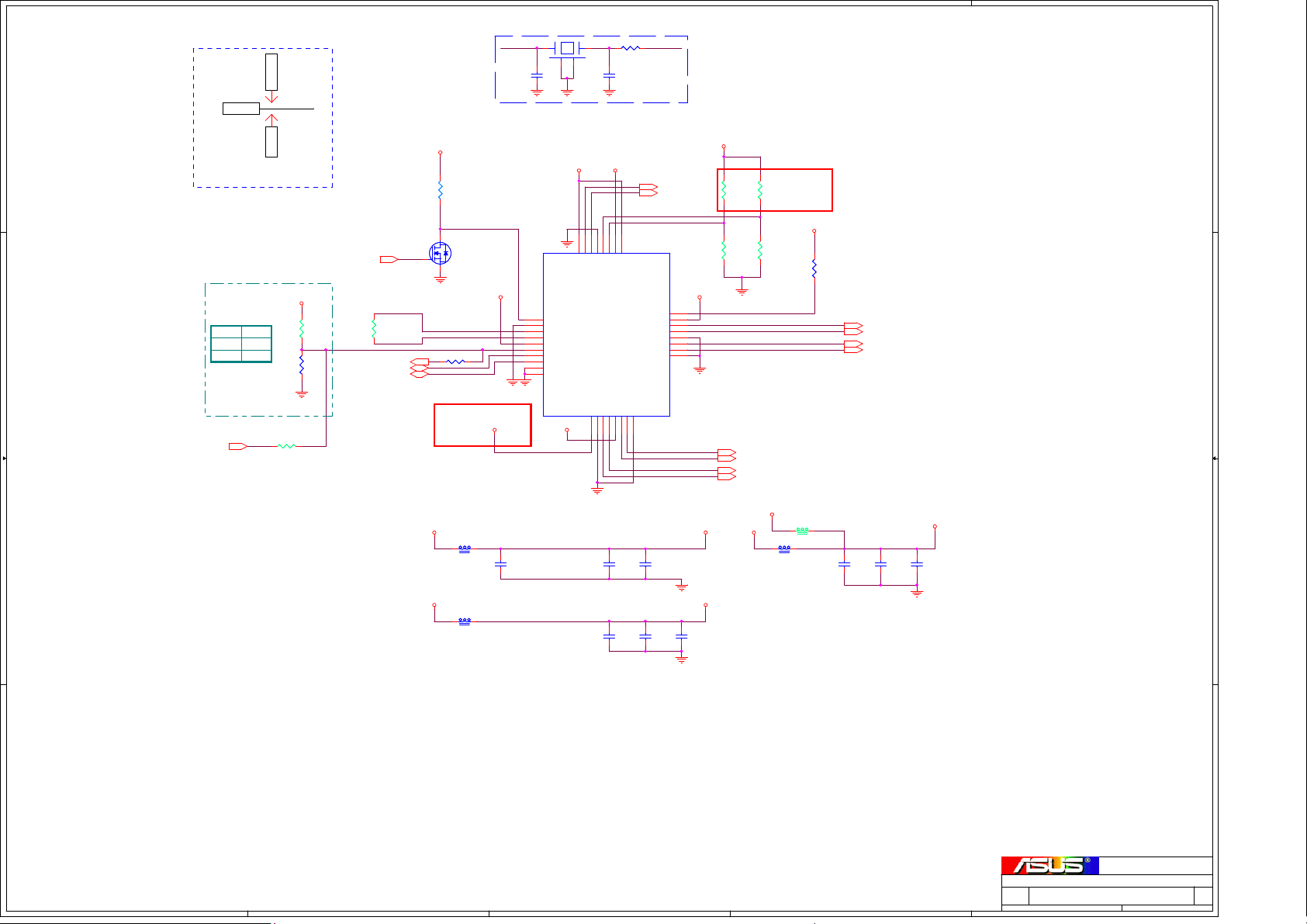

5

U0301A

U0301A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

SOCKET989

SOCKET989

DMI_TXN022

DMI_TXN122

DMI_TXN222

DMI_TXN322

DMI_TXP022

DMI_TXP122

DMI_TXP222

DMI_TXP322

DMI_RXN022

DMI_RXN122

DMI_RXN222

D D

C C

DMI_RXN322

DMI_RXP022

DMI_RXP122

DMI_RXP222

DMI_RXP322

FDI_TXN[7:0]22

FDI_TXP[7:0]22

FDI_FSYNC022

FDI_FSYNC122

FDI_INT22

FDI_LSYNC022

FDI_LSYNC122

For Intel GFX display

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_IRCOMP_R

EXP_RBIAS

PCIENB_RXN0

PCIENB_RXN1

PCIENB_RXN2

PCIENB_RXN3

PCIENB_RXN4

PCIENB_RXN5

PCIENB_RXN6

PCIENB_RXN7

PCIENB_RXN8

PCIENB_RXN9

PCIENB_RXN10

PCIENB_RXN11

PCIENB_RXN12

PCIENB_RXN13

PCIENB_RXN14

PCIENB_RXN15

PCIENB_RXP0

PCIENB_RXP1

PCIENB_RXP2

PCIENB_RXP3

PCIENB_RXP4

PCIENB_RXP5

PCIENB_RXP6

PCIENB_RXP7

PCIENB_RXP8

PCIENB_RXP9

PCIENB_RXP10

PCIENB_RXP11

PCIENB_RXP12

PCIENB_RXP13

PCIENB_RXP14

PCIENB_RXP15

PCIENB_TXN0

PCIENB_TXN1

PCIENB_TXN2

PCIENB_TXN3

PCIENB_TXN4

PCIENB_TXN5

PCIENB_TXN6

PCIENB_TXN7

PCIENB_TXN8

PCIENB_TXN9

PCIENB_TXN10

PCIENB_TXN11

PCIENB_TXN12

PCIENB_TXN13

PCIENB_TXN14

PCIENB_TXN15

PCIENB_TXP0

PCIENB_TXP1

PCIENB_TXP2

PCIENB_TXP3

PCIENB_TXP4

PCIENB_TXP5

PCIENB_TXP6

PCIENB_TXP7

PCIENB_TXP8

PCIENB_TXP9

PCIENB_TXP10

PCIENB_TXP11

PCIENB_TXP12

PCIENB_TXP13

PCIENB_TXP14

PCIENB_TXP15

4

R0301 49.9Ohm1%R0301 49.9Ohm1%

1 2

R0302 750Ohm1%R0302 750Ohm1%

1 2

CX0301 0.1UF/16VCX0301 0.1UF/16V

1 2

CX0302 0.1UF/16VCX0302 0.1UF/16V

1 2

CX0303 0.1UF/16VCX0303 0.1UF/16V

1 2

CX0304 0.1UF/16VCX0304 0.1UF/16V

1 2

CX0305 0.1UF/16VCX0305 0.1UF/16V

1 2

CX0306 0.1UF/16VCX0306 0.1UF/16V

1 2

CX0307 0.1UF/16VCX0307 0.1UF/16V

1 2

CX0308 0.1UF/16VCX0308 0.1UF/16V

1 2

CX0309 0.1UF/16VCX0309 0.1UF/16V

1 2

CX0310 0.1UF/16VCX0310 0.1UF/16V

1 2

CX0311 0.1UF/16VCX0311 0.1UF/16V

1 2

CX0312 0.1UF/16VCX0312 0.1UF/16V

1 2

CX0313 0.1UF/16VCX0313 0.1UF/16V

1 2

CX0314 0.1UF/16VCX0314 0.1UF/16V

1 2

CX0315 0.1UF/16VCX0315 0.1UF/16V

1 2

CX0316 0.1UF/16VCX0316 0.1UF/16V

1 2

CX0317 0.1UF/16VCX0317 0.1UF/16V

1 2

CX0318 0.1UF/16VCX0318 0.1UF/16V

1 2

CX0319 0.1UF/16VCX0319 0.1UF/16V

1 2

CX0320 0.1UF/16VCX0320 0.1UF/16V

1 2

CX0321 0.1UF/16VCX0321 0.1UF/16V

1 2

CX0322 0.1UF/16VCX0322 0.1UF/16V

1 2

CX0323 0.1UF/16VCX0323 0.1UF/16V

1 2

CX0324 0.1UF/16VCX0324 0.1UF/16V

1 2

CX0325 0.1UF/16VCX0325 0.1UF/16V

1 2

CX0326 0.1UF/16VCX0326 0.1UF/16V

1 2

CX0327 0.1UF/16VCX0327 0.1UF/16V

1 2

CX0328 0.1UF/16VCX0328 0.1UF/16V

1 2

CX0329 0.1UF/16VCX0329 0.1UF/16V

1 2

CX0330 0.1UF/16VCX0330 0.1UF/16V

1 2

CX0331 0.1UF/16VCX0331 0.1UF/16V

1 2

CX0332 0.1UF/16VCX0332 0.1UF/16V

1 2

PCIENB_RXN[15:0] 70

R0370,R0371,R0372 near U0301

PCIENB_RXP[15:0] 70

For EC request, to read PECI via EC.

Connection: R0317.2-->Q0301.1-->U3001.118

R0310 don't remove

PCIEG_RXN0

PCIEG_RXN1

PCIEG_RXN2

PCIEG_RXN3

PCIEG_RXN4

PCIEG_RXN5

PCIEG_RXN6

PCIEG_RXN7

PCIEG_RXN8

PCIEG_RXN9

PCIEG_RXN10

PCIEG_RXN11

PCIEG_RXN12

PCIEG_RXN13

PCIEG_RXN14

PCIEG_RXN15

PCIEG_RXP0

PCIEG_RXP1

PCIEG_RXP2

PCIEG_RXP3

PCIEG_RXP4

PCIEG_RXP5

PCIEG_RXP6

PCIEG_RXP7

PCIEG_RXP8

PCIEG_RXP9

PCIEG_RXP10

PCIEG_RXP11

PCIEG_RXP12

PCIEG_RXP13

PCIEG_RXP14

PCIEG_RXP15

PCIEG_RXN[15:0] 70

PCIEG_RXP[15:0] 70

+VTT_CPU

+VTT_CPU

H_THRMTRIP#25,32

H_CPUPWRGD7,25

H_DRAM_PWRGD22

H_VTTPWRGD58

H_PWRGD_XDP7

BUF_PLT_RST#7,24,30,32,33,45,53,54,64,70

3

+VTT_CPU

H_PECI25

H_PROCHOT_S#

R0340

R0340

56OHM

56OHM

H_CPURST#7

PM_SYNC#22

H_CATERR#

THRO_CPU

0Ohm

0Ohm

R0317

@R0317

@

0Ohm

0Ohm

R0308

R0308

R0322 68OHMR0322 68OHM

0Ohm

0Ohm

R0310

R0310

0Ohm

0Ohm

R0311

R0311

12

T0302T0302

0Ohm

0Ohm

R0314

R0314

0Ohm

0Ohm

R0309

R0309

0Ohm

0Ohm

R0315

R0315

0Ohm

0Ohm

R0316

R0316

R0318

R0318

1 2

1.5KOhm 1%

1.5KOhm 1%

R1.0

R030320Ohm 1% R030320Ohm 1%

12

R030420Ohm 1% R030420Ohm 1%

12

R030549.9Ohm 1% R030549.9Ohm 1%

12

R030649.9Ohm 1% R030649.9Ohm 1%

12

T0301T0301

12

12

12

H_PROCHOT_S#_R

12

12

1

12

VCCPWRGOOD_1_R

12

VCCPWRGOOD_0_R

12

VDDPWRGOOD_R

12

PLT_RST#_R

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKTOCC#

1

R030749.9Ohm 1% R030749.9Ohm 1%

12

H_PECI_ISO

H_THRMTRIP#_R

H_CPURST#

PM_SYNC#_R

12

R0319

R0319

750Ohm

750Ohm

1%

1%

2

SKTOCC#:pulled to ground on processor.

may use to determine if CPU is present

U0301B

U0301B

AT23

AT24

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

G16

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

SOCKET989

SOCKET989

MISC THERMAL

MISC THERMAL

DDR3

DDR3

PWR MANAGEMENT

PWR MANAGEMENT

CLOCKS

CLOCKS

MISC

MISC

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

R1.1,item L11

CLKDREF

CLKDREF#

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

+VTT_CPU

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

R0366 1KOhm

R0366 1KOhm

R0367 1KOhm

R0367 1KOhm

Place near R0328,R0329.

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_ITP_BCLK_R

CLK_ITP_BCLK#_R

CLK_EXP_P

CLK_EXP_N

CLKDREF

CLKDREF#

SM_RCOMP0

R0331 100Ohm1%R0331 100Ohm1%

SM_RCOMP1

R0332 24.9Ohm1%R0332 24.9Ohm1%

SM_RCOMP2

R0333 130OHM1%R0333 130OHM1%

PM_EXTTS#1

RN0301A

RN0301A

10KOHM

10KOHM

RN0301B

RN0301B

10KOHM

10KOHM

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

H_DBR#_R

R0336 0OhmR0336 0Ohm

XDP_OBS0_R

RX0337 0OhmRX0337 0Ohm

XDP_OBS1_R

RX0338 0OhmRX0338 0Ohm

XDP_OBS2_R

RX0339 0OhmRX0339 0Ohm

XDP_OBS3_R

RX0340 0OhmRX0340 0Ohm

XDP_OBS4_R

RX0341 0OhmRX0341 0Ohm

XDP_OBS5_R

RX0342 0OhmRX0342 0Ohm

XDP_OBS6_R

RX0343 0OhmRX0343 0Ohm

XDP_OBS7_R

RX0344 0OhmRX0344 0Ohm

@

@

@

@

1 2

1 2

1 2

12

34

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

CLK selection

SL0317

SL0317

21

0402

0402

SL0318

SL0318

21

0402

0402

1

Main Board

CLK_ITP_BCLK 7

CLK_ITP_BCLK# 7

CLK_DREF 21

CLK_DREF# 21

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

120MHz from PCH.

PM_EXTTS#0 14,15,16

Check here

XDP_DBRESET# 7,22

M_DRAMRST# 14,15,16

XDP_PRDY# 7

XDP_PREQ# 7

XDP_TCLK 7

XDP_TMS 7

XDP_TRST# 7

XDP_OBS[7:0] 7

12G011909890

R03911KOhm@R03911KOhm

3

JTAG MAPPING

XDP_TDI_R

XDP_TDO_M

12

XDP_TDI_M

XDP_TDO_R

BUF_PLT_RST#H_CPURST#

0402

0402

R0351 0Ohm

R0351 0Ohm

1 2

@

@

R0353

R0353

0Ohm

0Ohm

R0352 0Ohm@R0352 0Ohm@

1 2

0402

0402

SL0308

SL0308

21

XDP_TDI 7

XDP_TDO 7

DRAMPWROK: (DGU R1.52)

+1.5V

SL0309

SL0309

21

VDDPWRGOOD_R

2

R0320

R0320

1.1KOhm

1.1KOhm

1%

1%

1 2

12

R0321

R0321

3.01KOHM

3.01KOHM

1%

1%

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

Title :

Title :

Title :

Daniel Huang

Daniel Huang

Daniel Huang

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

1

3 99Thursday, April 15, 2010

3 99Thursday, April 15, 2010

3 99Thursday, April 15, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Q0301

Q0301

H2N7002

H2N7002

1

1

1

+VTT_CPU

12

1 2

@

THRO_CPU 30

R1.1,item L8

R03230Ohm R03230Ohm

BCLK_CPU_P_PCH25

B B

BCLK_CPU_N_PCH25

CLK_DMI_PCH21

CLK_DMI#_PCH21

12

R03550Ohm R03550Ohm

12

R03590Ohm R03590Ohm

12

R03560Ohm R03560Ohm

12

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_EXP_P

CLK_EXP_N

FDI disable: (For discrete graphic)

1. NC:

FDI_TX#[0:7],FDI_TX[0:7],FDI_RX#[0:7],FDI_RX[0:7]

VCC_AXGSENSE,VSS_AXGSENSE

2. Pull-down to GND via 1KΩ ± 5% resistor:

FDI_FSYNC[0:1],FDI_LSYNC[0:1],FDI_INT,GFX_IMON

~15mW power saving.(DG R0.8 P.70)

3. Connected to GND:

VCCAXG,

4. Can be connected to GND directly:

DPLL_REF_CLK,DPLL_REF_CLK#

5. Connect to +V1.05S rail:

VCCFDIPLL

A A

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

FDI_INT

AUB Item1

1 2

1 2

1 2

1 2

1 2

R03641KOhm CFD R03641KOhm CFD

R03611KOhm CFD R03611KOhm CFD

R03651KOhm CFD R03651KOhm CFD

R03621KOhm CFD R03621KOhm CFD

R03631KOhm CFD R03631KOhm CFD

5

H_PROCHOT_S#80,85

PWRLIMIT#30,88

4

H_CPURST#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO_R

XDP_TCLK

XDP_TRST#

H_PROCHOT_S#

@

@

12

D0301 RB751V-40

D0301 RB751V-40

R1.1,item L10.

R0313 68OHM@R0313 68OHM@

R0345 51Ohm@R0345 51Ohm@

1 2

R0346 51Ohm@R0346 51Ohm@

1 2

R0347 51Ohm@R0347 51Ohm@

1 2

R0348 51OhmR0348 51Ohm

1 2

R0349 51Ohm@R0349 51Ohm@

1 2

R0350 51OhmR0350 51Ohm

1 2

32

3

3

D

D

G

G

S

S

2

2

5

4

3

2

1

Main Board

U0301C

U0301C

U0301D

U0301D

AA6

SA_CK[0]

M_A_DQ[63:0]15

D D

C C

B B

M_A_DQ0

A10

AM10

AR11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AR14

AP14

AJ10

AL10

AK12

AK11

AL11

AL13

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS015

M_A_BS115

M_A_BS215

M_A_CAS#15

M_A_RAS#15

M_A_WE#15

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 15

M_CLK_DDR#0 15

M_CKE0 15

M_CLK_DDR1 15

M_CLK_DDR#1 15

M_CKE1 15

M_CS#0 15

M_CS#1 15

M_ODT0 15

M_ODT1 15

M_A_DM[7:0] 15

M_A_DQS#[7:0] 15

M_A_DQS[7:0] 15

M_A_A[15:0] 15

M_B_DQ[63:0]14,16

M_B_DQ0

B5

AR10

AT10

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS014,16

M_B_BS114,16

M_B_BS214,16

M_B_CAS#14,16

M_B_RAS#14,16

M_B_WE#14,16

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

M_B_DM0

D4

M_B_DM1

E1

M_B_DM2

H3

M_B_DM3

K1

M_B_DM4

AH1

M_B_DM5

AL2

M_B_DM6

AR4

M_B_DM7

AT8

M_B_DQS#0

D5

M_B_DQS#1

F4

M_B_DQS#2

J4

M_B_DQS#3

L4

M_B_DQS#4

AH2

M_B_DQS#5

AL4

M_B_DQS#6

AR5

M_B_DQS#7

AR8

M_B_DQS0

C5

M_B_DQS1

E3

M_B_DQS2

H4

M_B_DQS3

M5

M_B_DQS4

AG2

M_B_DQS5

AL5

M_B_DQS6

AP5

M_B_DQS7

AR7

M_B_A0

U5

M_B_A1

V2

M_B_A2

T5

M_B_A3

V3

M_B_A4

R1

M_B_A5

T8

M_B_A6

R2

M_B_A7

R6

M_B_A8

R4

M_B_A9

R5

M_B_A10

AB5

M_B_A11

P3

M_B_A12

R3

M_B_A13

AF7

M_B_A14

P5

M_B_A15

N1

M_CLK_DDR2 16

M_CLK_DDR#2 16

M_CKE2 16

M_CLK_DDR3 16

M_CLK_DDR#3 16

M_CKE3 16

M_CS#2 16

M_CS#3 16

M_ODT2 16

M_ODT3 16

M_B_DM[7:0] 14,16

M_B_DQS#[7:0] 14,16

M_B_DQS[7:0] 14,16

M_B_A[15:0] 14,16

SOCKET989

SOCKET989

SOCKET989

SOCKET989

A A

CPU(2)_DDR3

CPU(2)_DDR3

CPU(2)_DDR3

Title :

Title :

Title :

Daniel Huang

Daniel Huang

Daniel Huang

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

1

Rev

Rev

Rev

1.01

1.01

1.01

4 99Thursday, April 15, 2010

4 99Thursday, April 15, 2010

4 99Thursday, April 15, 2010

5

4

3

2

1

Main Board

D D

DIMM0_VREF_DQ18

DIMM1_VREF_DQ18

T0578T0578

T0567T0567

T0566T0566

T0565T0565

T0569T0569

T0568T0568

T0571T0571

T0572T0572

T0574T0574

T0570T0570

C C

B B

T0575T0575

T0573T0573

T0576T0576

T0577T0577

T0592T0592

T0581T0581

T0580T0580

T0579T0579

T0583T0583

10mil trace

10mil trace

CFG0

1

CFG1

1

CFG2

1

CFG3

1

CFG4

1

CFG5

1

CFG6

1

CFG7

1

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

1

CFG16

1

CFG17

1

CFG18

1

H_RSVD17_R

R05010Ohm R05010Ohm

12

H_RSVD18_R

R05020Ohm R05020Ohm

12

T0513T0513

1

T0510T0510

1

T0511T0511

1

T0512T0512

1

T0514T0514

1

T0515T0515

1

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

AC9

AB9

J29

J28

A34

A33

C35

B35

U9

T9

C1

A3

U0301E

U0301E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

SOCKET989

SOCKET989

AJ13

RSVD32

AJ12

RSVD33

AH25

RSVD34

AK26

RSVD35

AL26

RSVD36

AR2

RSVD37

AJ26

RSVD38

AJ27

RSVD39

AP1

RSVD40

AT2

RSVD41

AT3

RSVD42

AR1

RSVD43

AL28

RSVD45

AL29

RSVD46

AP30

RSVD47

AP32

RSVD48

AL27

RSVD49

AT31

RSVD50

AT32

RSVD51

AP33

RSVD52

AR33

RSVD53

AT33

RSVD54

AT34

RSVD55

AP35

RSVD56

AR35

RSVD57

AR32

RSVD58

E15

RSVD59

F15

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD67

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

RESERVED

RESERVED

RSVD64_R

RSVD65_R

SB_CK[2]

SB_CK#[2]

SB_CKE[2]

SB_CS#[2]

SB_ODT[2]

SB_CK[3]

SB_CK#[3]

SB_CKE[3]

SB_CS#[3]

SB_ODT[3]

1

1

1

1

1

1

1

1

1

T0504T0504

T0501T0501

T0506T0506

T0507T0507

T0503T0503

T0508T0508

T0509T0509

T0502T0502

T0505T0505

R0505 0OhmR0505 0Ohm

1 2

R0506 0OhmR0506 0Ohm

1 2

M_CLK_DDR4 14

M_CLK_DDR#4 14

M_CKE4 14

M_CS#4 14

M_ODT4 14

M_CLK_DDR5 14

M_CLK_DDR#5 14

M_CKE5 14

M_CS#5 14

M_ODT5 14

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

AR9

AR6

AR3

AP7

AP4

AP2

AM8

AM5

AM2

AL9

AL6

AL3

AJ8

AJ5

AJ2

AH9

AH6

AH3

AF8

AF4

AF2

U0301H

U0301H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

SOCKET989

SOCKET989

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

U0301I

U0301I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

SOCKET989

SOCKET989

VSS

VSS

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

NCTF

NCTF

TP_MCP_VSS_NCTF2

AT1

AR34

B34

B2

TP_MCP_VSS_NCTF6

B1

TP_MCP_VSS_NCTF7

A35

TP_MCP_VSS_NCTF1

AT35

T0564T0564

1

T0561T0561

1

T0563T0563

1

T0562T0562

1

CFG strapping information:

CFG[1:0]: PCI Express Port Bifurcation:(Clarksfield Only)

- 11 = 1 x 16 PEG (Default)

- 10 = 2 x 8 PEG

CFG[3]: PCIE Static Numbering Lane Reversal.(Auburndale Only)

- 1:Normal Operation (Default)

- 0:Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

CFG[4]: Embedded DisplayPort Detection.(Auburndale Only)

- 1:Disabled - No Physical Display Port attached to Embedded DisplayPort

- 0:Enabled - An external Display Port device is connected to the Embedded Display Port

CFG[7]: Fixed for PCI Express 2.0 jitter specifications.(Clarksfi eld)

Clarksfield (only for early samples pre-ES1) - Connect to GND with 3.01K Ohm /5% resistor

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not impact AUB functionality.

Unmount if Intel has fixed this issue.

A A

Note: (Auburndale)Hardware Straps are sampled on

the asserting edge of VCCPWRGOOD_0 and

VCCPWRGOOD_1 and latched inside the processor.

Note: (Clarksfield)Hardware Straps are sampled

after RSTIN# de-assertion.

5

CFG0

CFG3

CFG4

CFG7

4

@

@

R0535 3.01KOHM

R0535 3.01KOHM

R0536 3.01KOHM

R0536 3.01KOHM

R0537 3.01KOHM

R0537 3.01KOHM

R0538 3.01KOHM

12

1%

1%

@

@

12

1%

1%

@

@

12

1%

1%

@R0538 3.01KOHM

@

12

1%

1%

R1.1,item B1

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

Title :

Title :

Title :

Daniel Huang

Daniel Huang

Daniel Huang

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

1

Rev

Rev

Rev

1.1

1.1

1.1

5 93Thursday, April 15, 2010

5 93Thursday, April 15, 2010

5 93Thursday, April 15, 2010

5

U0301F

U0301F

+VCORE

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

D D

C C

B B

A A

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

SOCKET989

SOCKET989

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

PSI#

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

R0616 0OhmR0616 0Ohm

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

VR_VID0

VR_VID1

VR_VID2

VR_VID3

VR_VID4

VR_VID5

VR_VID6

PM_DPRSLPVR_R

H_VTTVID1 82

1 2

VTT_TEST TBD

AN35

AJ34

AJ35

B15

A15

I_MON 80

VCCSENSE_R

VSSSENSE_R

VTT_SENSE

TP_VSS_SENSE_VTT

12

12

C060110UF/6.3V C060110UF/6.3V

+VTT_CPU

12

12

C068710UF/6.3V C068710UF/6.3V

C061722UF/6.3V C061722UF/6.3V

R0601 0OhmR0601 0Ohm

1

1

12

12

C060610UF/6.3V C060610UF/6.3V

C060210UF/6.3V C060210UF/6.3V

C060410UF/6.3V C060410UF/6.3V

12

C068910UF/6.3V C068910UF/6.3V

C068810UF/6.3V C068810UF/6.3V

C61822UF/ 6.3V C61822UF/6.3V

12

12

VR_VID[0:6] 80

1 2

+VCORE

T0632T0632

T0631T0631

4

C61410UF/6.3V@C61410UF/6.3V

12

12

12

12

12

C061310UF/6.3V C061310UF/6.3V

C060810UF/6.3V C060810UF/6.3V

C061110UF/6.3V C061110UF/6.3V

@

V1.1S_VTT (Arrandale)

V1.05S_VTT (Clarksfield)

7PCS 22UF 0805

8PCS 10UF 0805

+VTT_CPU

PM_PSI# 80

PM_DPRSLPVR 80

R0602

R0602

100Ohm

100Ohm

1%

1%

1 2

VCCSENSE 80

VSSSENSE 80

12

R0603

R0603

100Ohm

100Ohm

1%

1%

+VTT_CPU+VTT_CPUCC

C61510UF/6.3V@C61510UF/6.3V

@

DANIEL 0720

R0620

R0620

R0621

R0621

DANIEL 0720

3

+VGFX_CORE

12

12

12

R06070Ohm

R06070Ohm

C065122UF/6.3V

C065122UF/6.3V

C065022UF/6.3V

C065022UF/6.3V

CFD

CFD

ARD

ARD

ARD

ARD

CE605330UF/2V

CE605330UF/2V

CE606330UF/2V

CE606330UF/2V

CE607330UF/2V

12

ESR=6mOhm/Ir=3A

ESR=6mOhm/Ir=3A

PANASONIC/EEFSX0D331XE

PANASONIC/EEFSX0D331XE

CE607330UF/2V

12

+

+

+

+

@

@

ESR=6mOhm/Ir=3A

ESR=6mOhm/Ir=3A

PANASONIC/EEFSX0D331XE

PANASONIC/EEFSX0D331XE

VCCAXG

2PCS 22UF 0805

2PCS 10UF 0603

ESR=6mOhm/Ir=3A

ESR=6mOhm/Ir=3A

DANIEL 0720

PANASONIC/EEFSX0D331XE

PANASONIC/EEFSX0D331XE

12

+

+

C62010UF/6.3V c0603

C62010UF/6.3V c0603

12

12

C061910UF/6.3V c0603

C061910UF/6.3V c0603

C064922UF/6.3V

C064922UF/6.3V

C064822UF/6.3V

C064822UF/6.3V

ARD

ARD

ARD

ARD

ARD

ARD

ARD

ARD

1 2

1 2

DANIEL 0720

+VTT_CPU

12

12

C065422UF/6.3V C 065422UF/6.3V

C065522UF/6.3V C 065522UF/6.3V

+VTT_CPU

0Ohmr0603_h24

0Ohmr0603_h24

+VTT_CPU

0Ohmr0603_h24

0Ohmr0603_h24

12

12

12

12

12

C065722UF/6.3V C 065722UF/6.3V

C065822UF/6.3V C 065822UF/6.3V12C065622UF/6.3V C 065622UF/6.3V

C065922UF/6.3V C 065922UF/6.3V

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AK21

AK19

AK18

AK16

AH21

AH19

AH18

AH16

AL21

AL19

AL18

AL16

AJ21

AJ19

AJ18

AJ16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

U0301G

U0301G

VCCAXG1

VCCAXG2

VCCAXG3

VCCAXG4

VCCAXG5

VCCAXG6

VCCAXG7

VCCAXG8

VCCAXG9

VCCAXG10

VCCAXG11

VCCAXG12

VCCAXG13

VCCAXG14

VCCAXG15

VCCAXG16

VCCAXG17

VCCAXG18

VCCAXG19

VCCAXG20

VCCAXG21

VCCAXG22

VCCAXG23

VCCAXG24

VCCAXG25

VCCAXG26

VCCAXG27

VCCAXG28

VCCAXG29

VCCAXG30

VCCAXG31

VCCAXG32

VCCAXG33

VCCAXG34

VCCAXG35

VCCAXG36

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

VTT52

VTT53

VTT54

VTT55

VTT56

VTT57

VTT58

SOCKET989

SOCKET989

SENSE

LINES

SENSE

LINES

GRAPHICS

GRAPHICS

GRAPHICS VIDs

GRAPHICS VIDs

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

VCCAXG_SENSE

VSSAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT59

VTT60

VTT61

VTT62

VTT63

VTT64

VTT65

1.1V1.8V

1.1V1.8V

VTT66

VTT67

VTT68

VCCPLL1

VCCPLL2

VCCPLL3

2

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

GVR_VID0

GVR_VID1

GVR_VID2

GVR_VID3

GVR_VID4

GVR_VID5

GVR_VID6

GFX_VRON_EN

GFXVR_DPRSLPVR_R

VCC_AXG_SENSE 86

VSS_AXG_SENSE 86

GVR_PWR_MON

GVR_VID[0:6] 86

R0605@: R8621 does not have 4.7K pull-down.

R0605 4.7KOhm

R0605 4.7KOhm

1 2

R0612 0Ohm

R0612 0Ohm

1 2

R0617 0Ohm@R0617 0Ohm@

1 2

R0604 0OhmR0604 0Ohm

1 2

GVR_PWR_MON 86

12

12

12

C06211UF/ 10V C06211UF/10V

C06221UF/ 10V C06221UF/10V

C06231UF/ 10V C06231UF/10V

12

12

C0626

C0626

C0627

C0627

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

12

12

C066522UF/6.3V C066522UF/6.3V

12

12

12

C06281UF/ 10V C06281UF/10V

C06672.2UF/10V C06672.2UF/10V

C06291UF/ 10V C06291UF/10V

CFD

CFD

ARD

ARD

12

12

C06241UF/ 10V C06241UF/10V

C066422UF/6.3V C066422UF/6.3V

12

12

C06684.7UF/6.3V C06684.7UF/6.3V

R0613 1KOhm

R0613 1KOhm

12

C06251UF/ 10V C06251UF/10V

C068522UF/6.3V C 068522UF/6.3V

C066622UF/6.3V C 066622UF/6.3V

1 2

CFD

CFD

GFX_VR_ON 30,86

GFX_VR 30

R0606

R0606

1 2

10KOhm

10KOhm

12+CE0604330UF/2V

+

12

C068622UF/6.3V C 068622UF/6.3V

CE0604330UF/2V

ESR=6mOhm/Ir=3A

ESR=6mOhm/Ir=3A

PANASONIC/EEFSX0D331XE

PANASONIC/EEFSX0D331XE

+VTT_CPU

+VTT_CPU

+1.8VS

VCCPLL

1PCS 2.2UF 0805

2PCS 1.0UF 0805

1PCS 22 UF 0805

1PCS 4.7UF 0603

1

Main Board

GFXVR_DPRSLPVR 86

R0606@:Itel Checklist recommendation

+1.5V

DANIEL 0721

Processor Decoupling

Decoupling guide from Intel

Schematic R0.9: Schematic Checklist R0.7:

+VCORE

VCORE 22uF * 16pcs

10uF * 16pcs

470uF* 6pcs(2 no stuff).

12

12

C0640

C0640

C0641

C0641

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

8/5 delete C0646 (22UF,6.3V) for layout placement.

(+1.8VS,VCCPLL)

12

12

C0670

C0670

10UF/6.3V

10UF/6.3V

12

C0671

C0671

10UF/6.3V

10UF/6.3V

C0669

C0669

10UF/6.3V

10UF/6.3V

VCORE 22uF * 12pcs

12

C0635

C0635

22UF/6.3V

22UF/6.3V

12

C0672

C0672

10UF/6.3V

10UF/6.3V

10uF * 16pcs

470uF* 6pcs(2 no stuff).

12

12

C0636

C0636

C0637

C0637

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

12

C0673

C0673

10UF/6.3V

10UF/6.3V

12

C0647

C0647

22UF/6.3V

22UF/6.3V

12

12

C0677

C0677

10UF/6.3V

10UF/6.3V

5

4

3

C0678

C0678

10UF/6.3V

10UF/6.3V

12

C0679

C0679

10UF/6.3V

10UF/6.3V

12

C0680

C0680

10UF/6.3V

10UF/6.3V

12

C0681

C0681

10UF/6.3V

10UF/6.3V

12

C0682

C0682

10UF/6.3V

10UF/6.3V

12

C0683

C0683

10UF/6.3V

10UF/6.3V

2

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Title :

Title :

Title :

Daniel Huang

Daniel Huang

Daniel Huang

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

1

6 99Thursday, April 15, 2010

6 99Thursday, April 15, 2010

6 99Thursday, April 15, 2010

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

Main Board

D D

CPU XDP connector

+VTT_CPU

J0701

J0701

31

1

SIDE1

32

SIDE2

FPC_CON_30P

FPC_CON_30P

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

C C

R1.3,item L21

1

1

CPUPWRGD_XDP

HBPM3#

HBPM2#

HBPM1#

HBPM0#

XDP_RST#_R

T0720T0720

T0721T0721

1 2

1 2

1

1

1

1

R071151Ohm R071151Ohm

12

1 2

T0716T0716

T0717T0717

T0718T0718

T0719T0719

R07090Ohm R07090Ohm

R07081KOhm R07081KOhm

R07071KOhm R07071KOhm

H_PWRGD_XDP 3

XDP_TRST# 3

H_CPUPWRGD 3,25

XDP_PREQ# 3

XDP_PRDY# 3

XDP_TDO 3

XDP_TDI 3

XDP_TMS 3

XDP_TCLK 3

XDP_DBRESET# 3,22

H_CPURST# 3

SMB_DAT_S 14, 15,16,28,29,53

SMB_CLK_S 14,15,16,28,29,53

CLK_ITP_BCLK# 3

CLK_ITP_BCLK 3

(45)

(54)

(39)

( 3)

( 5)

(52)

(56)

(58)

(57)

(48)

(46)

(42)

(40)

(44) +VTT_CPU

B B

T0722T0722

1

T0723T0723

1

T0724T0724

1

T0725T0725

1

T0726T0726

1

T0727T0727

1

T0728T0728

1

T0729T0729

1

T0730T0730

1

FFC

J0701

path

Put these test point near J0701.

Put it away from the FFC path.

A A

5

4

XDP_RST#_R

R0715 0Ohm @R0715 0Ohm @

XDP_OBS0 3

XDP_OBS1 3

XDP_OBS2 3

XDP_OBS3 3

XDP_OBS4 3

XDP_OBS5 3

XDP_OBS6 3

XDP_OBS7 3

PM_PWRBTN#_R 22

1 2

BUF_PLT_RST# 3,24,30,32,33,45,53,54,64,70

3

Title :

Title :

Title :

CPU(5)_XDP

CPU(5)_XDP

CPU(5)_XDP

James1_Wu

James1_Wu

Engineer:

Engineer:

M60J

M60J

M60J

1

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

James1_Wu

7 99Thursday, April 15, 2010

7 99Thursday, April 15, 2010

7 99Thursday, April 15, 2010

Rev

Rev

Rev

2.02

2.02

2.02

5

D D

C C

4

3

2

1

B B

A A

NB_****

NB_****

NB_****

Title :

Title :

Title :

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

1

Daniel Huang

Daniel Huang

Daniel Huang

8 99Wednesday, April 07, 2010

8 99Wednesday, April 07, 2010

8 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

Daniel Huang

Daniel Huang

1

Daniel Huang

9 99Wednesday, April 07, 2010

9 99Wednesday, April 07, 2010

9 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

Daniel Huang

Daniel Huang

1

Daniel Huang

10 99Wednesday, April 07, 2010

10 99Wednesday, April 07, 2010

10 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

Daniel Huang

Daniel Huang

1

Daniel Huang

11 99Wednesday, April 07, 2010

11 99Wednesday, April 07, 2010

11 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

Daniel Huang

Daniel Huang

1

Daniel Huang

12 99Wednesday, April 07, 2010

12 99Wednesday, April 07, 2010

12 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

Daniel Huang

Daniel Huang

1

Daniel Huang

13 99Wednesday, April 07, 2010

13 99Wednesday, April 07, 2010

13 99Wednesday, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

David Lewis

David Lewis

David Lewis

5

M_B_DQ[6 3:0] 4,16

J1401A

M_B_A[15 :0]4,16

D D

M_B_BS04,16

M_B_BS14,16

M_B_BS24,16

M_B_CAS #4,16

M_CLK_D DR#45

M_CLK_D DR#55

M_CLK_D DR45

M_CLK_D DR55

M_CKE45

M_CKE55

M_B_DM[7:0]4,16

M_B_DQS [7:0]4,16

M_B_DQS #[7:0]4,16

C C

+1.5V

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS 0

M_B_DQS 1

M_B_DQS 2

M_B_DQS 3

M_B_DQS 4

M_B_DQS 5

M_B_DQS 6

M_B_DQS 7

M_B_DQS #0

M_B_DQS #1

M_B_DQS #2

M_B_DQS #3

M_B_DQS #4

M_B_DQS #5

M_B_DQS #6

M_B_DQS #7

J1401A

98

97

96

95

92

91

90

86

89