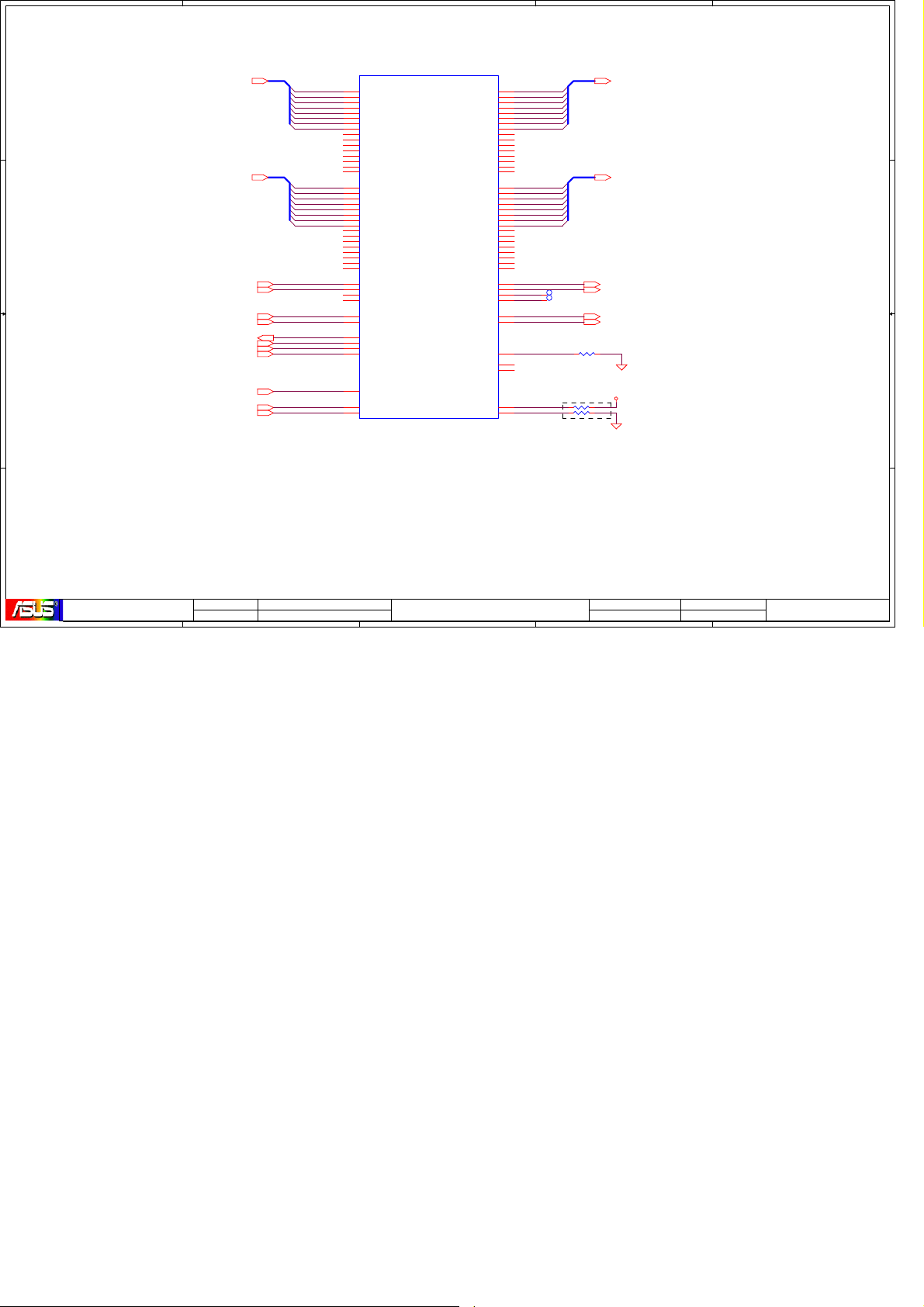

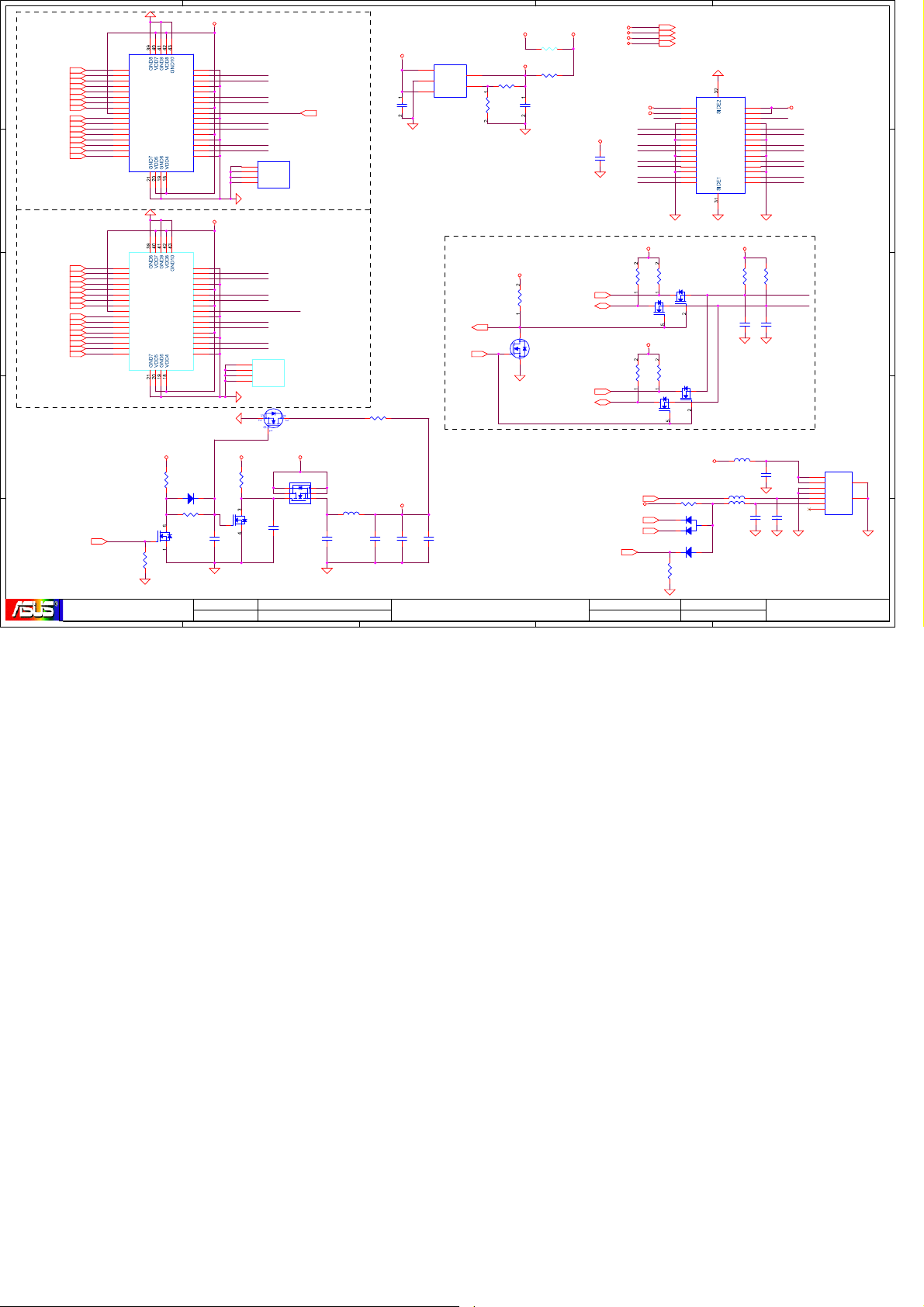

Asus A8M, A8T Schematic

A

B

A8T/M SCHEMATIC R2.1

C

D

E

1 1

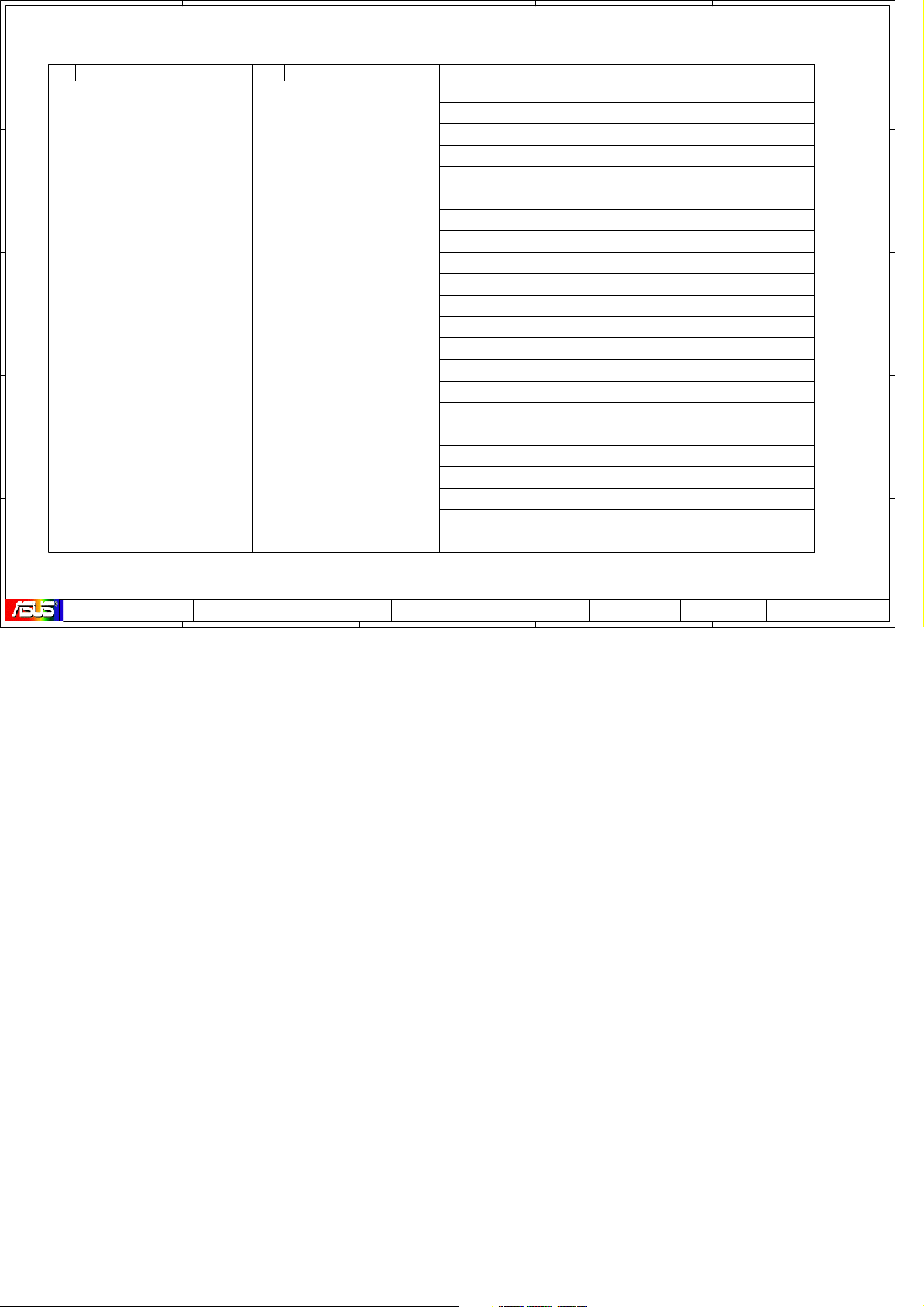

PAGE

SYSTEM PAGE REF.

4

AMD S1 CPU--HT

5

AMD S1 CPU--CNTL

AMD S1 CPU--DDR2

6

7

AMD S1 CPU--PWR/GND

8

DDR2 SO-DIMM_0

DDR2 SO-DIMM_1

9

DDR2 ADDRESS TERMIN ATION

10

C51M--HT TO CPU

2 2

3 3

4 4

5 5

11

C51M--HT TO MCP

12

C51M--PCI-E

13

C51M--CRT & LVDS

14

15

C51M--PWR/GND

VGA CONN

16

17

LVDS & INVERTER CON N

CRT & TV_OUT

18

MCP51--HT

19

20

MCP51--PCI

21

MCP51--IDE

22

MCP51--USB & HDA & GPIO

23

MCP51--PWR/GND

24

HDD & CD-ROM CONN

25

USB PORTS

26

SUPER I/O LPC47N217

27

BIOS & FIR

28

KBC 38857

29

SM BUS & POWER PORT

30

PCI-E--MINI CARD

PCI-E--NEW CARD

31

32

PCI--LAN RTL8110CL

RJ45 & RJ11

33

34

PCI--1394,CardReade r R5C832

35

PCI--4 IN1 CON

AUDIO CODEC ALC660

36

37

AUDIO AMP G1420

38

MDC,B/T,TPM & DISCH G,HOLE

39

DVI CONN

40

ACIN, BAT, FAN, I/O PORT

41

SW & LED & TP

42

POWER-ON SEQUENCE

HISTORY

43

I/O PORT44

Content

PAGE

POWER PAGE REF.

61 POWER_VCORE

62 POWER_SYSTEM

63 POWER_I/O_1.2VO & 1.0VO

64 POWER_I/O_LDO

65 POWER_I/O_DDR2

66 POWER_VGA_CORE(E mpty)

67 POWER_LOAD_SYSTE M

68 POWER_CHARGER

69 POWER_PIC

70 POWER_PROTECT

71 POWER_SWITCH_+5V LCM

72 POWER_DIAGRAM

Content

<Core Design>

PROJECT:

A

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

1 55

B

DESCRIPTION:

PAGE REF.

C

RELEASE DATE :

D

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

Albert Su

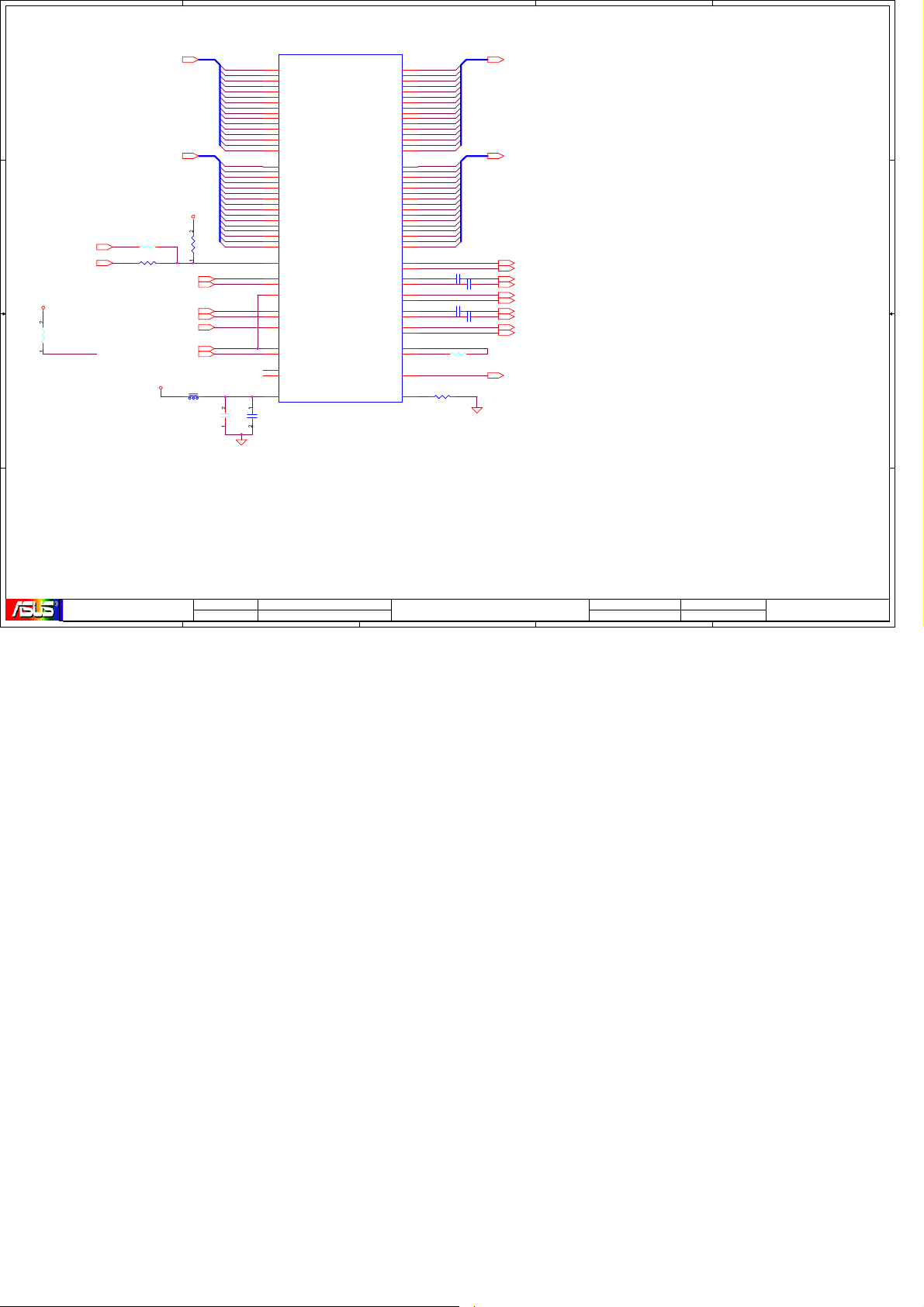

A

B

C

D

E

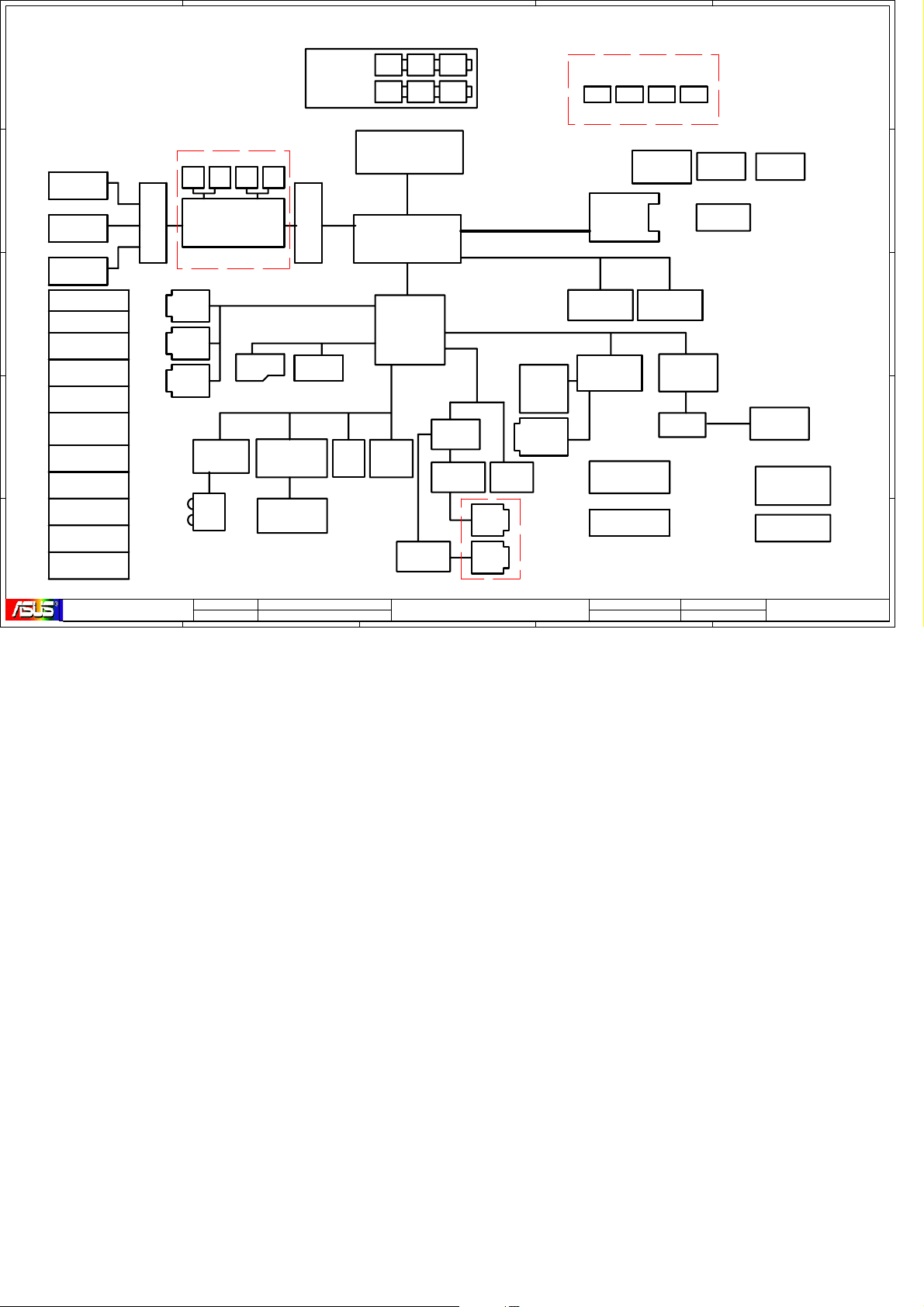

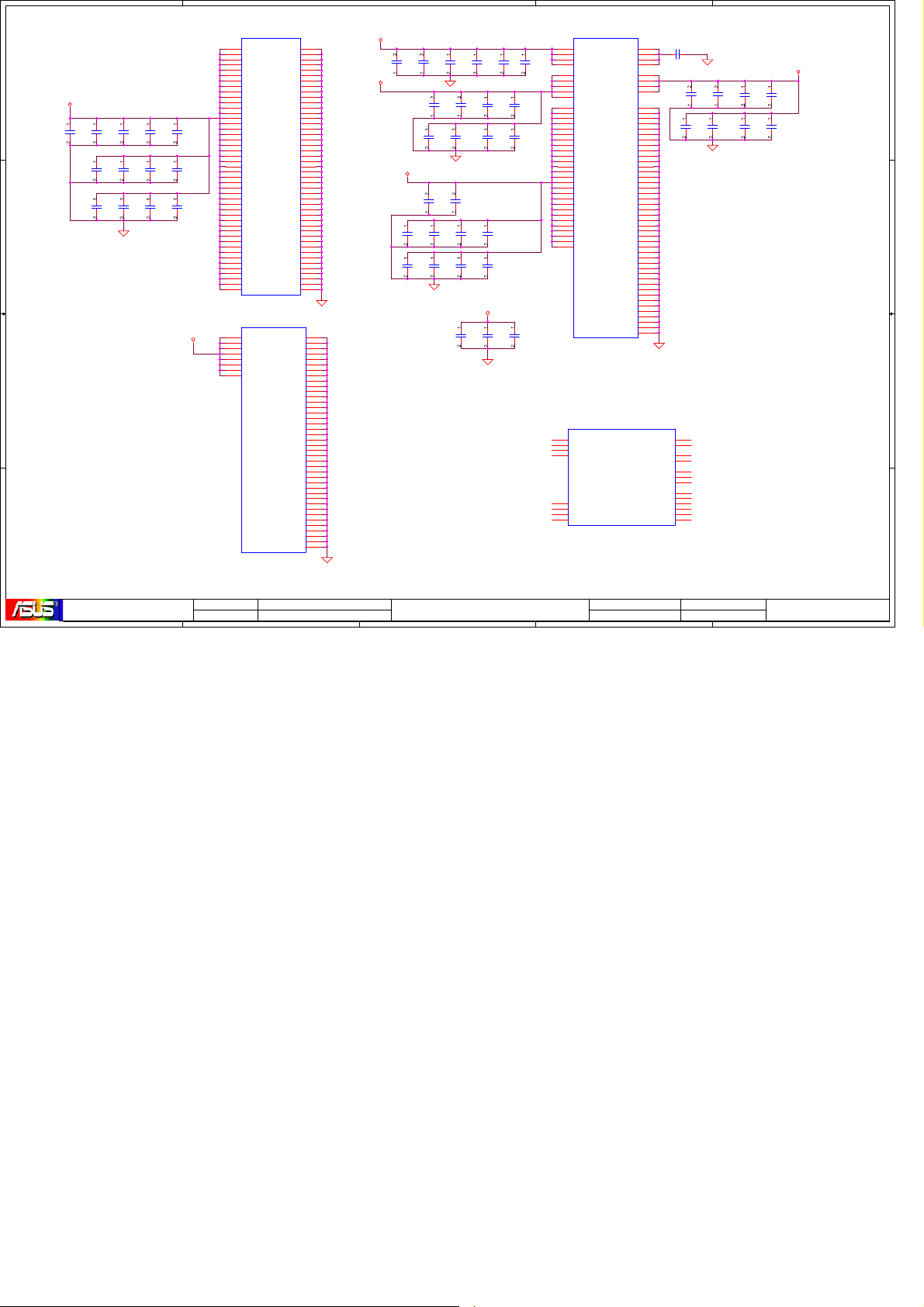

A8T/M AMD S1/C51MV BLOCK DIAGRAM

1 1

BATTERY

TYPE

IO PORT

3S2P

1394 USB MIC LINE_IN

AMD

638

4,5,6,7

HT X16

C51MV

HT X8

MCP51

19,20,2 1,22,23

27

MIC AMP

LM358

DESCRIPTION:

DDR2 SDRAM 53 3/667MHz

PCI EXPRESS X 1

PCI_BUS

ACZ

Codec

ADI1986A

36

AUDIO AMP

G1420

37

C

MDC

CON

37

LINE

OU

T

40

MIC_IN

40

BLOCK DAIGRAM

3.3V, 33MHz

4 IN 1

CARD

READER

35

1394

SLOT

38

40

MINI CARD

CARDBUS

RICOH

R5C832

VGA

CON

A8T

16

USB x5

B/T

Camera

LFB LFB LFB LFB

Nvidia

G7x series

VGA BAORD

25

38

ODD

(Secondary)

38

SUPER I/O

47N217

FIR

REVISION

2.1

KEYBOARD

CONTROLLER

26

M38857

INTERNAL

KEYBOARD

DATE:

SHEET OF

PCI-E

x16

VGA

CON

16 11,12,1 3,14,15

USB2.0

PATA BUS

HDD

(Primary)

2424

LPC, 33MHz

TPM

28

38

3027

Friday, July 21, 2006

2 55

B

FWH

BIOS

LVDS & INV

CON

2 2

3 3

4 4

5 5

<Core Design>

17

CRT & TV

CON

18

DVI Dual

CH.

39

VCORE

SYSTEM

1.2VO & 1.0VO

I/O LDO

+1.8V & +0.9V

LOAD SYSTEM

CHARGER

PIC

PROTECT

SWITCH 5VLCM

DIAGRAM

PROJECT:

A

61

62

63

64

65

67

68

69

70

71

72

POWER

SEQENCE

DDR2 533/667

SODIMM X2

+1.8V

+0.9V

8,9

30

34

SW & LED &

TOUCHPAD

CON

AC & BAT CON

FAN CTRL

RELEASE DATE :

D

42

....

NEW

CARD

LAN 1G

RTL8110SBL

LAN IO

41

40

40,44

RESET SM_BUS

42 29

DDR

CAP/RES

10

31

32

RJ11,RJ45

33

CON

33

DCIN

RTC

FAN CON.

H/W MONITOR

THERMAL

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

40

70

Albert Su

A

B

C

D

E

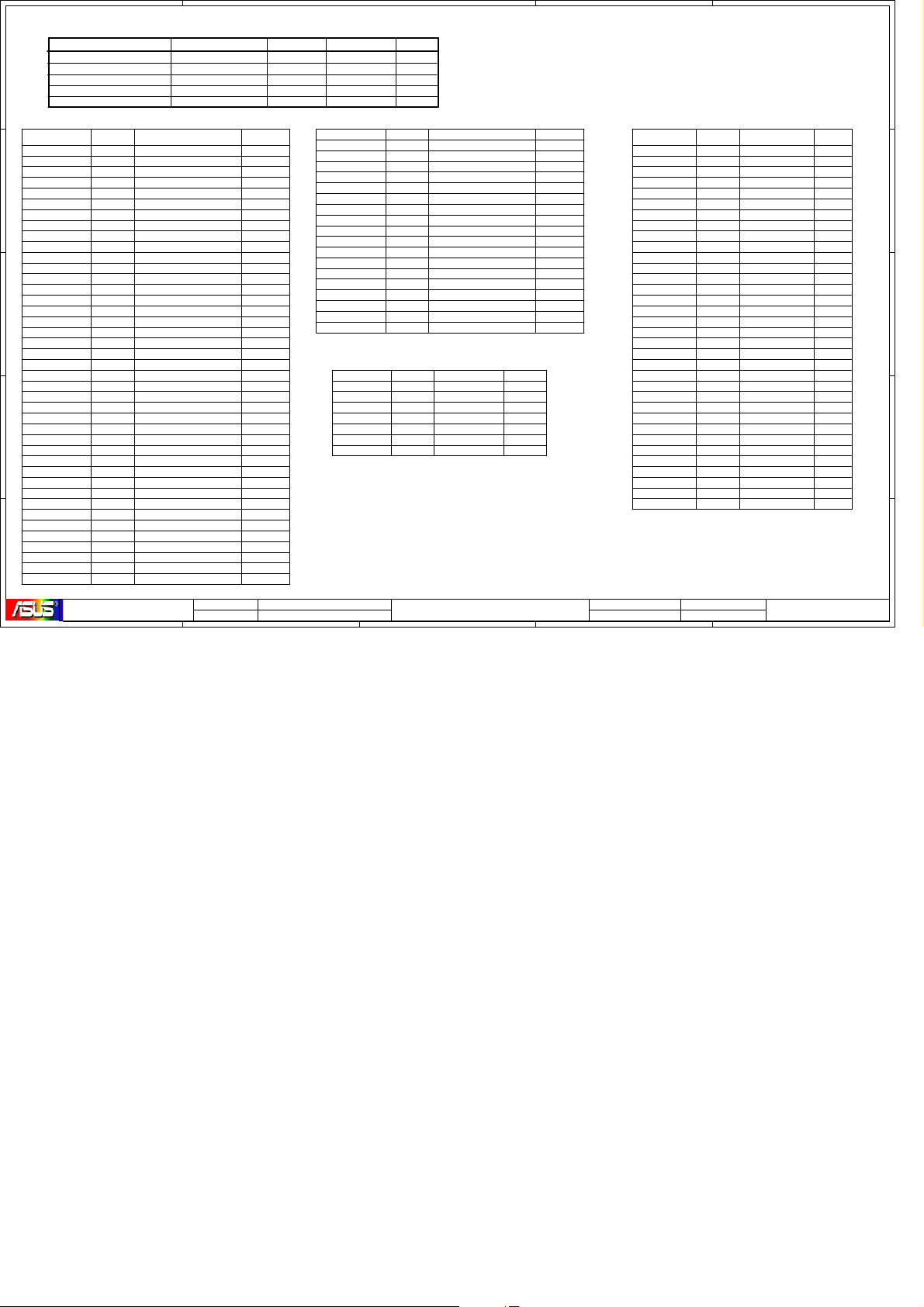

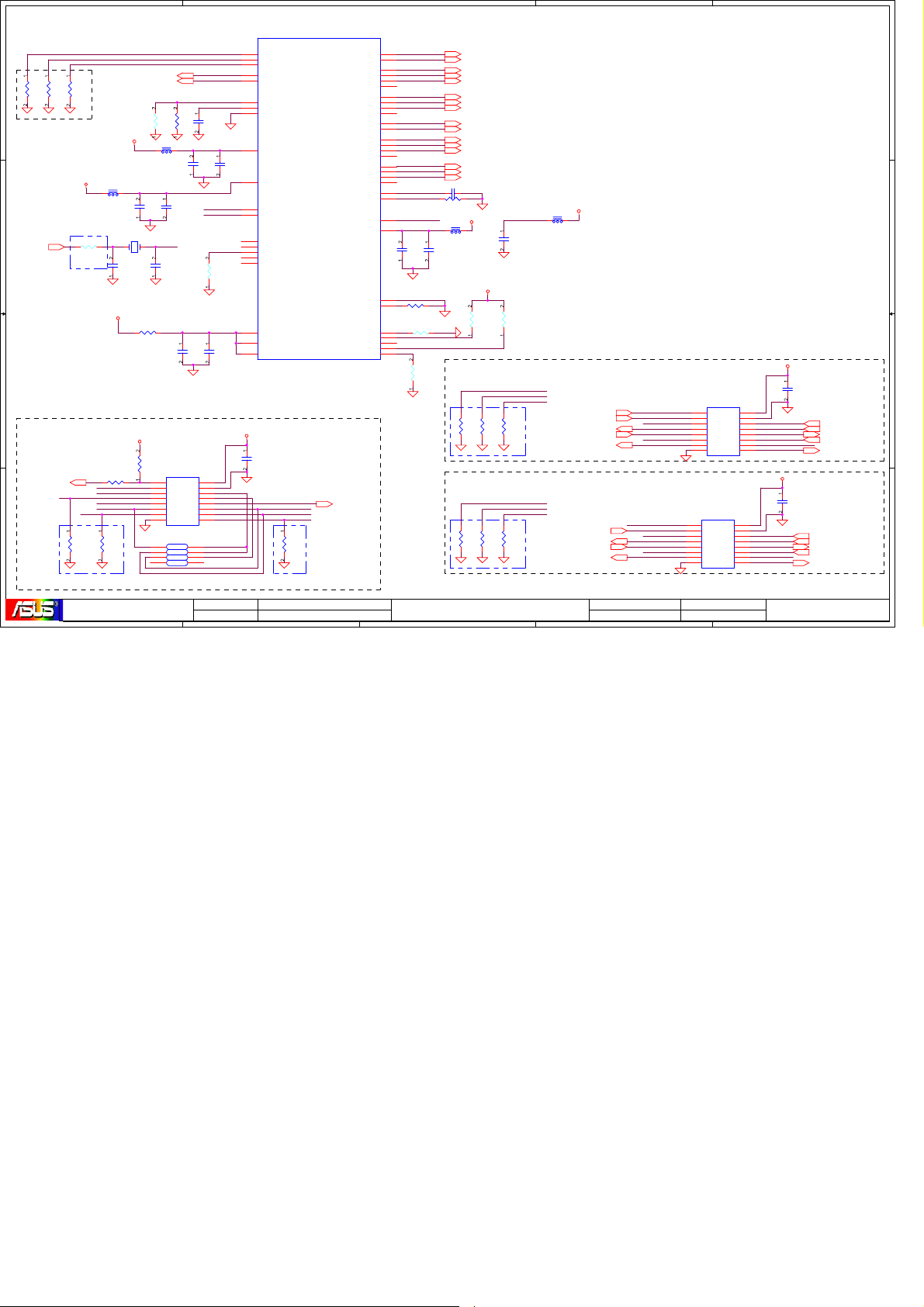

PCI Device

Chipset (Host to PCI)

1 1

2 2

3 3

4 4

5 5

<Core Design>

LAN -- Realtek

1394

4 IN 1

MCP51_GPIO

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9 CR_V

GPIO_10

GPIO_[11:16]

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_42

GPIO_43

GPIO_44

GPIO_45

GPIO_46

PROJECT:

Signal Name

Use As

GPI

GPI

GPI

GPO

GPO

GPO

GPO

GPO

GPI

GPI

GPI

GPO

GPO OP_SD#

GPO

GPI VGA_DETE

GPO

GPI

GPO

A

IDSEL#

(AD30 internal)

AD17

AD16

PCB_ID2

KB_SCI#

PWRLMT#

SUS_STAT#

802_LED_EN#

MCP_TV_EN

CB_SD#

CR_VID0

ID1

(CR_VID2)

(CPU_VID[0:5])

(LID#)

BATT_TALARM#

USB_OC#1

1 Hz

IGP_DDC_SELECT +3VSUS

ACZ_SDIN0_AUD

ACZ_SDIN1_MDC

CHG_FULL_OC

SMB_MEM_SCL +3VSUS

SMB_MEM_SDA

SMB_CLK_SB

SMB_DAT_SB

(SMB_ALERT#)

PCI_PME#

SIO_SMI#

EXTSMI#_3A

(RI#)

SUS_CLK

WLAN_ON#

MXM_PWR_ON

CT#

BACK_OFF#

VGA_PWRGD

PM_CLKRUN#

PCI_PERR#

ACZ_SYNC

ACZ_SDOUT

BT_ON/OFF#

A8T

REVISION

2.1

REQ/GNT#

n/a

1 C

0

0

Power

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

Friday, July 21, 2006

DATE:

SHEET OF

B

Interrupts

A

B

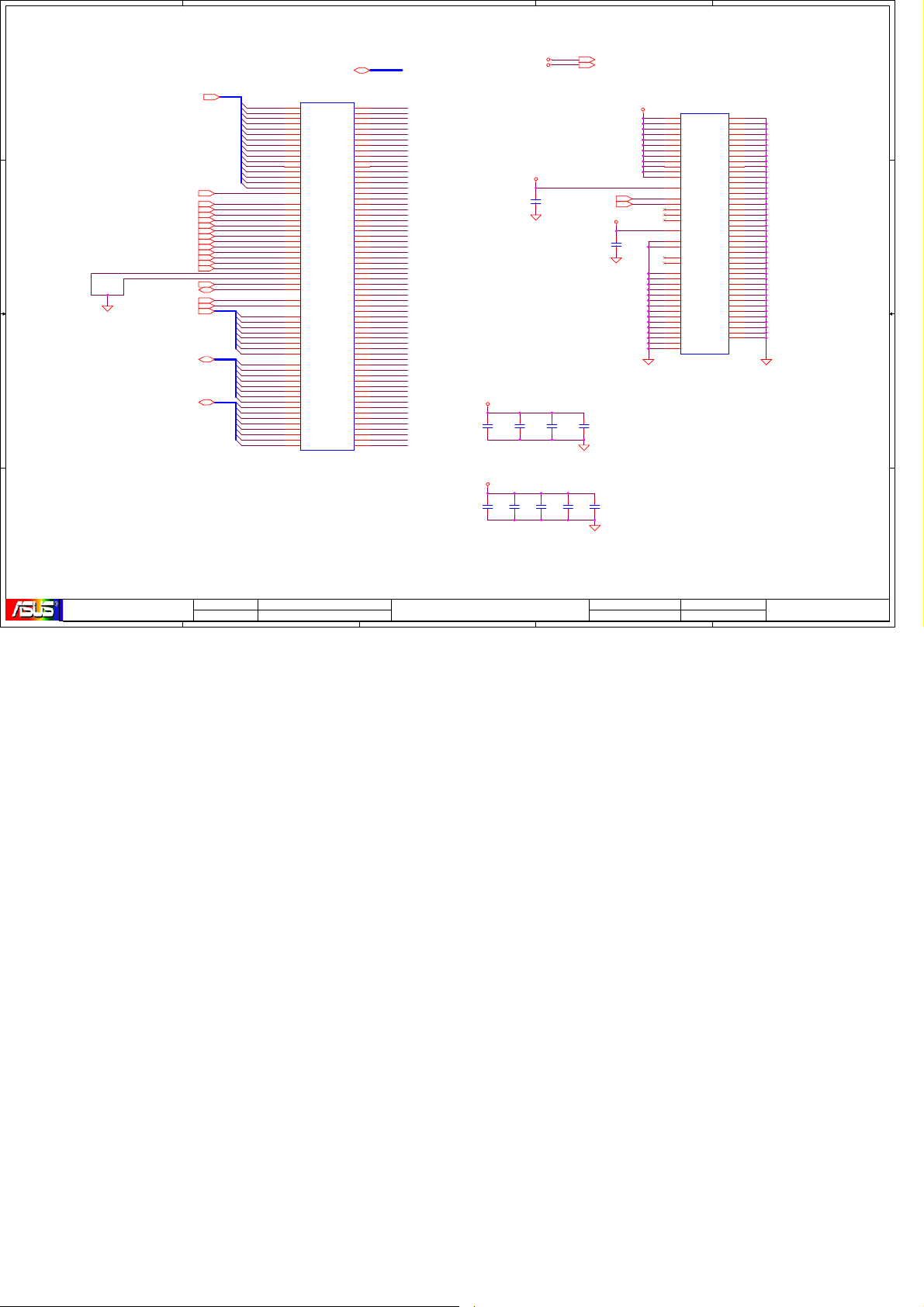

MCP51_GPIO Use As Signal Name Power

GPIO_47

GPIO_48

GPIO_49

GPIO_50

GPIO_51

GPIO_52

GPIO_53

GPIO_54

GPIO_55

GPIO_56

GPIO_57

GPIO_58

GPIO_59

GPIO_60

GPIO_61

GPIO_62

GPIO_63

GPIO_64

47N217_GPIO USE_AS SIGNAL_NAME

GPIO10

GPIO[11:12]

GPIO[13:14]

GPIO23 +3VS

GPIO46

GPIO47

3 55

PC/PCI

GPI

GPO

GPO

GPO

GPO

GPI +3VS

GPI

GPO

GPI

GPO

GPI

GPO

GPI

GPI

DESCRIPTION:

SM_BUS ADDRESS :

ST

LOAD_TE

FWH_WP#

LCD_VDD_EN_GM

LCD_BACKEN_GM

EDID_CLK_C51M

EDID_DATA_C51M

GPU_ON

HA20GATE

KBDCPURST

SATA_LED#

CPU_THERMTRIP#

PM_THERM#

PCB_ID0

PCB_ID1

IGP_SELECT

(CABLE_DET_P)

(CABLE_DET_S

SCHEMATICS REF.

C

)

Power

+3VS

+3VS

+3VS

+3VSGPIO[40:45] GPI

+3VS

+3VS

Thermal MAX6657 = 1001100x ( 98h )

DDR_SODIMM0 = 1010000x ( A0h )

DDR_SODIMM1 = 1010001x ( A2h )

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

M38857_GPIO USE_AS SIGNAL_NAME

P23

P22

P21 GPO

P20

P42

P43

P44 KBCPURST_3Q

P45

P46 KBSCI_3Q

P47 PM_CLKRUN#

P50

P51

P52

P53

P54

P55

P56

P57

P67

P66

P65

P64

P63

P62

P61

P60

P76 GPIO

P77

P27

P26

P25 CAP_LED#

P24

P40 KBC_EXTSMI

P41

RELEASE DATE :

D

GPO

MSK_INSTKEY#

GPO BAT_LEARN

GPO KBCRSM

GPO

WATCHDOG

GPI

SWDJ_EN

GPO

GPO

KBC_GA20

GPO

GPI

GPI

BAT_LLOW#_OC

FAN1_TACH

GPI

GPO

KBDDT0

GPO

KBDDT1

GPI

LID_KBC#

GPI

BAT_IN_OC#

GPO

FAN1_DC

ADJ_BL

GPO

NEWCARD_OFF#

GPI

GPI

PANLOCK_#

MARATHON_#

GPI

ACIN_OC#

GPI

NEWCARD_DET#

GPI

WIRELESS_#

GPI

GPI

INTERNET_#

GPI

BLUETOOTH_#

SMD_BAT

SMC_BAT

GPIO

GPO

SCR_LED# +3V

NUM_LED#

GPO

GPO

GPO

SET_PCIRSTNS#

GPO

PANLOCK_LED

GPO

Power

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

Albert Su

5

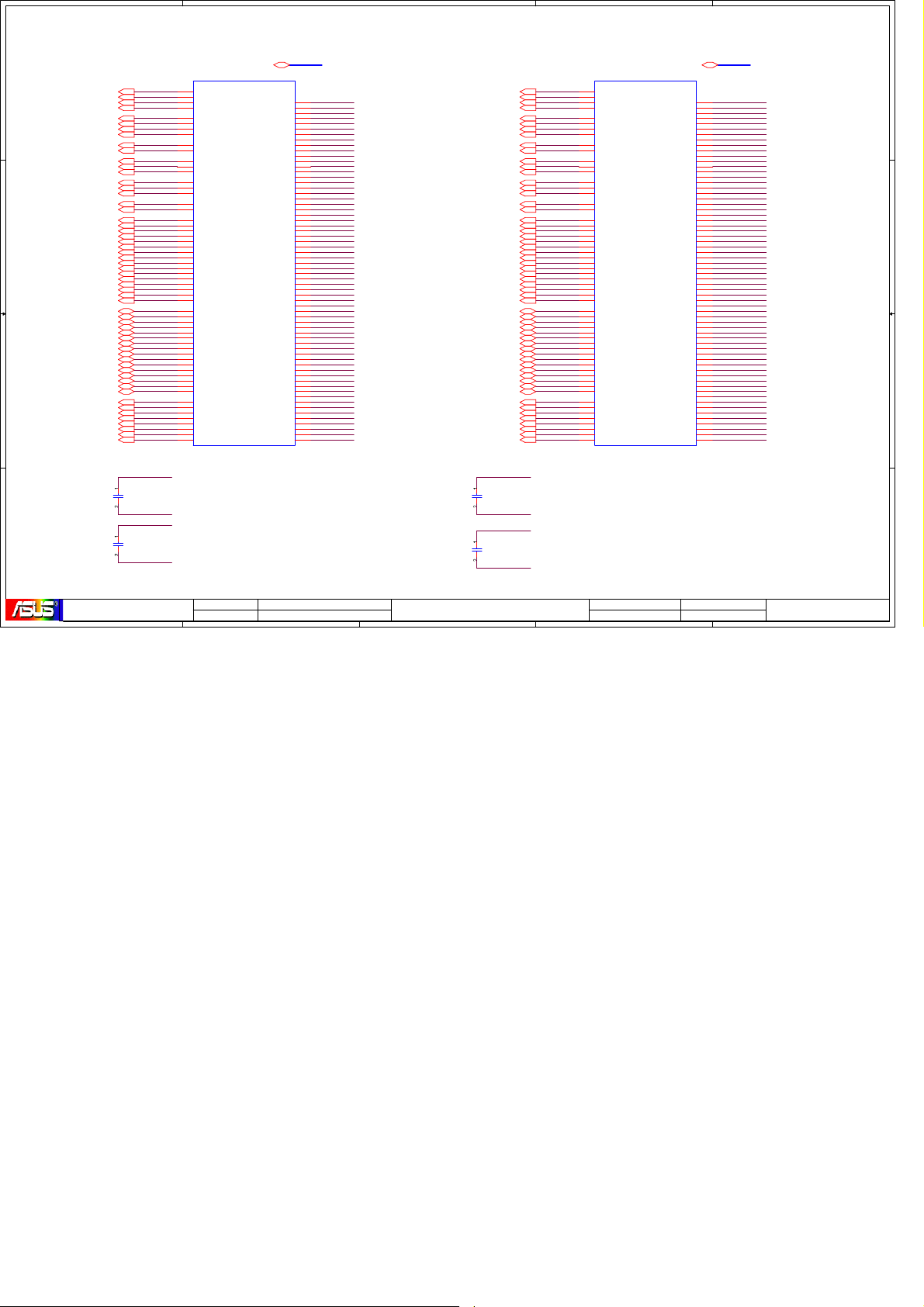

D D

+1.2VS_HT

C C

B B

R772

49.9Ohm

R773

49.9Ohm

HT_TXCTL

HT_TXCTL#

HTCPU_TXDP[0..15]11

HTCPU_TXDN[0..15]11

4

U1A

HT_TXCTL

HT_TXCTL#

J5

K5

J3

J2

P3

P4

N1

P1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

SOCKET638

L0_CLKIN_H1

L0_

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

HTCPU_TXCLK111

HTCPU_TXCLK1#11

HTCPU_TXCLK011

HTCPU_TXCLK0#11

HTCPU_TXCTL11

HTCPU_TXCTL#11

HTCPU_TXDP15

HTCPU_TXDN15

HTCPU_TXDP14

HTCPU_TXDN14

HTCPU_TXDP13

HTCPU_TXDN13

HTCPU_TXDP12

HTCPU_TXDN12

HTCPU_TXDP11

HTCPU_TXDN11

HTCPU_TXDP10

HTCPU_TXDN10

HTCPU_TXDP9

HTCPU_TXDN9

HTCPU_TXDP8

HTCPU_TXDN8

HTCPU_TXDP7

HTCPU_TXDN7

HTCPU_TXDP6

HTCPU_TXDN6

HTCPU_TXDP5

HTCPU_TXDN5

HTCPU_TXDP4

HTCPU_TXDN4

HTCPU_TXDP3

HTCPU_TXDN3

HTCPU_TXDP2

HTCPU_TXDN2

HTCPU_TXDP1

HTCPU_TXDN1

HTCPU_TXDP0

HTCPU_TXDN0

CLKIN_L1

3

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

HYPERTRA NSPORT

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

2

Y4

Y3

Y1

W1

T5

R5

R2

R3

HTCPU_RXDP15

T4

HTCPU_RXDN15

T3

HTCPU_RXDP14

V5

HTCPU_RXDN14

U5

HTCPU_RXDP13

V4

HTCPU_RXDN13

V3

HTCPU_RXDP12

Y5

HTCPU_RXDN12

W5

HTCPU_RXDP11

AB5

HTCPU_RXDN11

AA5

HTCPU_RXDP10

AB4

HTCPU_RXDN10

AB3

HTCPU_RXDP9

AD5

HTCPU_RXDN9

AC5

HTCPU_RXDP8

AD4

HTCPU_RXDN8

AD3

HTCPU_RXDP7

T1

HTCPU_RXDN7

R1

HTCPU_RXDP6

U2

HTCPU_RXDN6

U3

HTCPU_RXDP5

V1

HTCPU_RXDN5

U1

HTCPU_RXDP4

W2

HTCPU_RXDN4

W3

HTCPU_RXDP3

AA2

HTCPU_RXDN3

AA3

HTCPU_RXDP2

AB1

HTCPU_RXDN2

AA1

HTCPU_RXDP1

AC2

HTCPU_RXDN1

AC3

HTCPU_RXDP0

AD1

HTCPU_RXDN0

AC1

HTCPU_RXCLK1 11

HTCPU_RXCLK1# 11

HTCPU_RXCLK0 11

HTCPU_RXCLK0# 11

T221

1

T222

1

HTCPU_RXCTL 11

HTCPU_RXCTL# 11

HTCPU_RXDP[0..15] 11

HTCPU_RXDN[0..15] 11

1

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

4 55

4

DESCRIPTION:

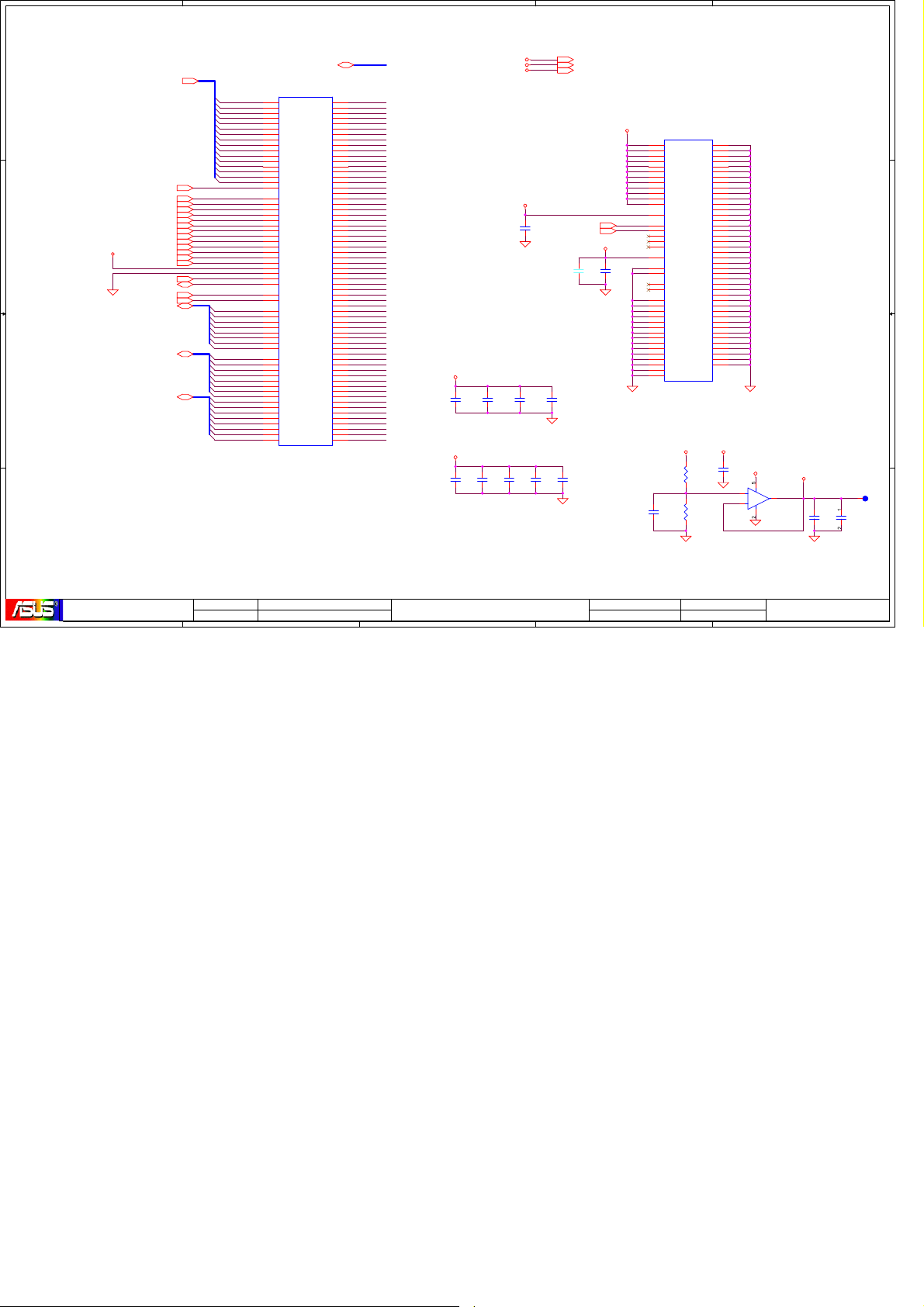

S1 CPU HT

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

+2.5VS

L100

180NH

+

CE7

100UF/6.3V

CLK_CPU11

D D

CLK_CPU#11

+1.8V

R779

2KOhm

C C

R783

2KOhm

0.1UF/16V

C704 3900PF/50V

C705 3900PF/50V

R < 600 mils from CPU

AC caps < 1250 mils

CPU_MVREF

C706

C707

1000PF/50V

12

12

+1.8V

Place near CPU socket

+2.5VS +1.8V

B B

HTCPU_RST#11

HTCPU_PWRGD11

HTCPU_STP#11

A A

PWRGD22,70

<Core Design>

RN34A

1 2

1KOhm

RN34B

3 4

1KOhm

RN34C

5 6

1KOhm

RN34D

7 8

1KOhm

+5VO

R21

1KOhm

Q2A

UM6K1N

2

PROJECT:

5

1 2

3 4

5 6

Q2B

UM6K1N

A8T

21

C701

4.7UF/6.3V

1 2

R774 169Ohm

+1.8V

CPU_VDD_FB61

CPU_VDD_FB#61

U52A

VCC

GND

74LVC07AD

U52B

VCC

GND

74LVC07AD

U52C

VCC

GND

74LVC07AD

5

VDDA

C702

0.22UF/6.3V

3300PF/25V

CPU_PWRGD

CPU_STP#

CPU_RST#

1 2

R775 1KOhm

300Ohm

1 2

T7128

R777

T223

T225

T226

T227

T228

VTT_SENSE

T7131

1

CPU_MVREF

39.2Ohm

1 2

R781

1 2

R784 39.2Ohm

1 2

R785 510Ohm

1 2

R787 510Ohm

1 2

R788 300Ohm

1 2

R789 300Ohm

T231

T233

T235

T236

T238

H_THERMDC

H_THERMDA

Q3A

UM6K1N

2

REVISION

2.1

C703

CLKIN

CLKIN#

1

1

1

1

1

1

MEM_ZN

MEM_ZP

1

1

1

1

1

1 2

3 4

5 6

7 8

Q3B

UM6K1N

5

AE10

AF10

300Ohm

300Ohm

300Ohm

300Ohm

AC6

AF4

AF5

AF9

AD9

AC9

AA9

E10

Y10

W17

H10

AA7

AC8

AA6

AB6

F8

F9

A9

A8

A7

F10

B7

F6

E6

E9

E8

G9

C2

D7

E7

F7

C7

C3

W7

W8

Y6

CPU_RST#

CPU_PWRGD

CPU_STP#

4

U1D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

THERMTRIP_L

SID

PROCHOT_L

TDI

TRST_L

MISC

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

SOCKET638

RN35A

RN35B

RN35C

RN35D

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

R1.1

Friday, July 21, 2006

DATE:

SHEET OF

5 55

4

3

T224

T229

T7129

1

T7130

1

+1.2VS_HT

1 2

R786 80.6Ohm

< 1" from CPU

80 ohm diff impedence

T230

T232

T234

+1.8V

For future processors

1 2

R793 300Ohm

1 2

R798 51Ohm

1 2

R799 51Ohm

+3VSUS

U52D

VCC

9 8

GND

74LVC07AD

DESCRIPTION:

CPU_VID[0..5] 61

CPU_PSI# 61

+1.8V

+VCORE

11 10

S1 CPU CNTL

3

U52E

VCC

GND

74LVC07AD

H_THERMDA

H_THERMDC

H_THRMTRIP#

U52F

VCC

13 12

GND

74LVC07AD

PCIRST_NEWC#20,31

CPU_VID5

A5

VID5

CPU_VID4

C6

VID4

CPU_VID3

A6

VID3

CPU_VID2

A4

VID2

CPU_VID1

C5

VID1

CPU_VID0

B5

VID0

H_THRMTRIP#

AF6

H_PROCHOT#

AC7

1

AE9

TDO

1

G10

CPU_VDDIO_FB

W9

Y9

A3

HT_REF1

1 2

P6

HT_REF0

R780 44.2Ohm

1 2

R6

R782 44.2Ohm

FBCLKOUT

C9

FBCLKOUT#

C8

1

AE7

1

AD7

1

AE8

1 2

AB8

R790 300Ohm

1

AF7

T237

J7

H8

AF8

1 2

AE6

R791 300Ohm

K8

C4

CPU_VID1

CPU_VDD_FB

CPU_VDD_FB#

AMD circuit is 51 ohm

nVIDIA circuit is 10 ohm

+3VSUS

C1

0.1UF/16V

2

R19 200

U2

VCC

DXP

DXN

OVERT#

Q1

PMBS3904

+1.8VS

Q109

PMBS3904

MAX6657MSA

+1.8VS

R22

10KOhm

R792

10KOhm

SCLK

ALERT#

Q102

2N7002

+3VS

8

7

SDA

6

5

GND

+3VS

R20

C13

10K

0.1U

C34 1000P

H_PROCHOT# PROCHOT#

RELEASE DATE :

1

2

3

4

+1.8V

R23

300Ohm

+1.8V

R794

300Ohm

2

PM_THRM#

R27

4.7KOhm

R797

1 2

0Ohm

+3VS

OTP_RESET# 42

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

R795

4.7KOhm

SCL_3S 16,29

SDA_3S 16,29

PM_THRM# 22

CPU_THRMTRIP# 19

PROCHOT# 28

PWRLMT# 22,68,71

1

R2.1

Albert Su

5

4

3

2

1

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

M_B_DQ[0..63]

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

M_A_DQ[0..63]8

A8T

AA16

AB19

AB20

AD23

AC23

AB16

AC24

Y16

E16

F16

V19

J22

V22

T19

V20

U19

U20

U21

T20

K22

R20

T22

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

W12

W13

Y15

W15

G22

G21

C22

C21

G16

G15

G13

H13

Y13

Y19

F24

E19

C15

E12

U1B

MA0_CLK_H2

MA0

_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

SOCKET638

REVISION

2.1

MEMORY

INTERFACE

D D

C C

B B

A A

<Core Design>

M_CLK_DDR18

M_CLK_DDR#18

M_CLK_DDR08

M_CLK_DDR#08

M_A_CS#38,10

M_A_CS#28,10

M_A_CS#18,10

M_A_CS#08,10

M_ODT18,10

M_ODT08,10

M_A_CAS#8,10

M_A_WE#8,10

M_A_RAS#8,10

M_A_BS#28,10

M_A_BS#18,10

M_A_BS#08,10

M_CKE18,10

M_CKE08,10

M_A_A158,10

M_A_A148,10

M_A_A138,10

M_A_A128,10

M_A_A118,10

M_A_A108,10

M_A_A98,10

M_A_A88,10

M_A_A78,10

M_A_A68,10

M_A_A58,10

M_A_A48,10

M_A_A38,10

M_A_A28,10

M_A_A18,10

M_A_A08,10

M_A_DQS78

M_A_DQS#78

M_A_DQS68

M_A_DQS#68

M_A_DQS58

M_A_DQS#58

M_A_DQS48

M_A_DQS#48

M_A_DQS38

M_A_DQS#38

M_A_DQS28

M_A_DQS#28

M_A_DQS18

M_A_DQS#18

M_A_DQS08

M_A_DQS#08

M_A_DM78

M_A_DM68

M_A_DM58

M_A_DM48

M_A_DM38

M_A_DM28

M_A_DM18

M_A_DM08

C133

1.5PF/50V

C134

1.5PF/50V

<1200 mil from CPU

PROJECT:

5

M_CLK_DDR1

M_CLK_DDR#1

M_CLK_DDR0

M_CLK_DDR#0

M_A_DQ[0..63]

M_A_DQ63

AA12

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

DATE:

SHEET OF

4

M_A_DQ62

AB12

M_A_DQ61

AA14

M_A_DQ60

AB14

M_A_DQ59

W11

M_A_DQ58

Y12

M_A_DQ57

AD13

M_A_DQ56

AB13

M_A_DQ55

AD15

M_A_DQ54

AB15

M_A_DQ53

AB17

M_A_DQ52

Y17

M_A_DQ51

Y14

M_A_DQ50

W14

M_A_DQ49

W16

M_A_DQ48

AD17

M_A_DQ47

Y18

M_A_DQ46

AD19

M_A_DQ45

AD21

M_A_DQ44

AB21

M_A_DQ43

AB18

M_A_DQ42

AA18

M_A_DQ41

AA20

M_A_DQ40

Y20

M_A_DQ39

AA22

M_A_DQ38

Y22

M_A_DQ37

W21

M_A_DQ36

W22

M_A_DQ35

AA21

M_A_DQ34

AB22

M_A_DQ33

AB24

M_A_DQ32

Y24

M_A_DQ31

H22

M_A_DQ30

H20

M_A_DQ29

E22

M_A_DQ28

E21

M_A_DQ27

J19

M_A_DQ26

H24

M_A_DQ25

F22

M_A_DQ24

F20

M_A_DQ23

C23

M_A_DQ22

B22

M_A_DQ21

F18

M_A_DQ20

E18

M_A_DQ19

E20

M_A_DQ18

D22

M_A_DQ17

C19

M_A_DQ16

G18

M_A_DQ15

G17

M_A_DQ14

C17

M_A_DQ13

F14

M_A_DQ12

E14

M_A_DQ11

H17

M_A_DQ10

E17

M_A_DQ9

E15

M_A_DQ8

H15

M_A_DQ7

E13

M_A_DQ6

C13

M_A_DQ5

H12

M_A_DQ4

H11

M_A_DQ3

G14

M_A_DQ2

H14

M_A_DQ1

F12

M_A_DQ0

G12

Friday, July 21, 2006

6 55

DESCRIPTION:

M_CLK_DDR39

M_CLK_DDR#39

M_CLK_DDR29

M_CLK_DDR#29

M_B_CS#39,10

M_B_CS#29,10

M_B_CS#19,10

M_B_CS#09,10

M_ODT39,10

M_ODT29,10

M_B_CAS#9,10

M_B_WE#9,10

M_B_RAS#9,10

M_B_BS#29,10

M_B_BS#19,10

M_B_BS#09,10

M_CKE39,10

M_CKE29,10

M_B_A159,10

M_B_A149,10

M_B_A139,10

M_B_A129,10

M_B_A119,10

M_B_A109,10

M_B_A99,10

M_B_A89,10

M_B_A79,10

M_B_A69,10

M_B_A59,10

M_B_A49,10

M_B_A39,10

M_B_A29,10

M_B_A19,10

M_B_A09,10

M_B_DQS79

M_B_DQS#79

M_B_DQS69

M_B_DQS#69

M_B_DQS59

M_B_DQS#59

M_B_DQS49

M_B_DQS#49

M_B_DQS39

M_B_DQS#39

M_B_DQS29

M_B_DQS#29

M_B_DQS19

M_B_DQS#19

M_B_DQS09

M_B_DQS#09

M_B_DM79

M_B_DM69

M_B_DM59

M_B_DM49

M_B_DM39

M_B_DM29

M_B_DM19

M_B_DM09

M_CLK_DDR3

C756

1.5PF/50V

M_CLK_DDR#3

M_CLK_DDR2

C757

1.5PF/50V

M_CLK_DDR#2

<1200 mil from CPU

S1 CPU MEM

3

U1C

AF18

MB0_CLK_H2

AF17

MB0

_CLK_L2

A17

MB0_CLK_H1

A18

MB0_CLK_L1

Y26

MB0_CS_L3

J24

MB0_CS_L2

W24

MB0_CS_L1

U23

MB0_CS_L0

W23

MB0_ODT1

W26

MB0_ODT0

V26

MB_CAS_L

U22

MB_WE_L

U24

MB_RAS_L

K26

MB_BANK2

T26

MB_BANK1

U26

MB_BANK0

H26

MB_CKE1

J23

MB_CKE0

J25

MB_ADD15

J26

MB_ADD14

W25

MB_ADD13

L23

MB_ADD12

L25

MB_ADD11

U25

MB_ADD10

L24

MB_ADD9

M26

MB_ADD8

L26

MB_ADD7

N23

MB_ADD6

N24

MB_ADD5

N25

MB_ADD4

N26

MB_ADD3

P24

MB_ADD2

P26

MB_ADD1

T24

MB_ADD0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MB_DQS_L2

D16

MB_DQS_H1

C16

MB_DQS_L1

C12

MB_DQS_H0

B12

MB_DQS_L0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

SOCKET638

RELEASE DATE :

2

MEMORY

INTERFACE

M_B_DQ[0..63]9

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

5

4

3

2

1

U1F

AC4

VDD1

AD2

2

VDD

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

D D

C C

B B

A A

+VCORE

C727

C728

22UF/6.3V

22UF/6.3V

C737

22UF/6.3V

C740

180PF/50V

Place under socket on bottom side

C729

22UF/6.3V

C738

22UF/6.3V

C7114

0.22UF/6.3V

C730

22UF/6.3V

C741

22UF/6.3V

C739

0.22UF/6.3V

C731

22UF/6.3V

C732

22UF/6.3V

C6

0.01UF/25V

+VCORE

K6

K10

K12

K14

L11

L13

M2

M6

M8

M10

N7

N9

N11

P8

P10

R4

R7

R9

R11

T10

T12

T14

U7

U9

U11

U13

V6

V8

V10

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

L4

L7

L9

T2

T6

T8

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

SOCKET638

U1G

VDD47

48

VDD

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

SOCKET638

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

VDD

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

M17

VSS91

N4

VSS92

N8

VSS93

N10

VSS94

N16

VSS95

N18

VSS96

P2

VSS97

P7

VSS98

P9

VSS99

P11

VSS100

P17

VSS101

R8

VSS102

R10

VSS103

R16

VSS104

R18

VSS105

VDD

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS130

VSS131

VSS132

VSS133

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+1.2VS_HT

C709

4.7UF/6.3V

+0.9V

Place close to socket

+1.8V

C746

0.22UF/6.3V

C2

0.01UF/25V

Place close to socket

C711

C710

0.22UF/6.3V

4.7UF/6.3V

C720

C719

4.7UF/6.3V

4.7UF/6.3V

C734

C733

1000PF/50V

1000PF/50V

Place close to socket

C743

C745

4.7UF/6.3V

4.7UF/6.3V

C747

C748

0.22UF/6.3V

0.22UF/6.3V

C750

C3

180PF/50V

0.01UF/25V

C752

22UF/6.3V

Place under socket on bottom side

C712

0.22UF/6.3V

C721

0.22UF/6.3V

C735

180PF/50V

C749

0.22UF/6.3V

C751

180PF/50V

+1.8V

22UF/6.3V

C753

C713

180PF/50V

C722

0.22UF/6.3V

C736

180PF/50V

C755

0.22UF/6.3V

C714

180PF/50V

U1H

D4

D3

D2

D1

D10

C10

B10

AD10

W10

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

SOCKET638

U1E

P20

RSVD_MA0_CLK_H3

P19

RSVD_MA0_CLK_L3

N20

RSVD_MA0_CLK_H0

N19

RSVD_MA0_CLK_L0

R26

RSVD_MB0_CLK_H3

R25

RSVD_MB0_CLK_L3

P22

RSVD_MB0_CLK_H0

R22

RSVD_MB0_CLK_L0

SOCKET638

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VTT8

VTT7

VTT6

VTT5

VTT9

VDDIO23

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO24

VDDIO25

VDDIO26

VDDIO27

I O

POWER

VLDT_B4

VLDT_B3

VLDT_B2

VLDT_B1

VTT4

VTT3

VTT2

VTT1

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

RSVD_MA_RESET_L

RSVD_MB_RESET_L

RSVD_VDDNB_FB_H

RSVD_VDDNB_FB_L

RSVD_CORE_TYPE

MISC

INTERNAL

AE5

AE4

AE3

AE2

AC10

AB10

AA10

A10

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

RSVD_VIDSTRB1

RSVD_VIDSTRB0

FREE5

FREE6

FREE4

FREE1

FREE2

FREE3

12

C708 4 .7UF/6.3V

C715

4.7UF/6.3V

C723

1000PF/50V

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

C716

4.7UF/6.3V

C724

1000PF/50V

C717

0.22UF/6.3V

C725

180PF/50V

C718

0.22UF/6.3V

C726

180PF/50V

+0.9V

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

7 55

4

DESCRIPTION:

S1 CPU PWR/GND

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

+1.8V

C137

0.1U

C141

1U/6.3V

C142

1U/6.3V

+3VS

+3VS

C135

0.1U

C138

0.1U

C143

1U/6.3V

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ[0..63]

M_A_DQ9

5

DQ0

M_A_DQ13

7

DQ1

M_A_DQ15

17

DQ2

M_A_DQ11

19

DQ3

M_A_DQ8

4

DQ4

M_A_DQ12

6

DQ5

M_A_DQ10

14

DQ6

M_A_DQ14

16

DQ7

M_A_DQ30

23

DQ8

M_A_DQ27

25

DQ9

M_A_DQ25

35

M_A_DQ29

37

M_A_DQ24

20

M_A_DQ28

22

M_A_DQ26

36

M_A_DQ31

38

M_A_DQ51

43

M_A_DQ50

45

M_A_DQ54

55

M_A_DQ49

57

M_A_DQ55

44

M_A_DQ48

46

M_A_DQ52

56

M_A_DQ53

58

M_A_DQ57

61

M_A_DQ56

63

M_A_DQ60

73

M_A_DQ61

75

M_A_DQ58

62

M_A_DQ59

64

M_A_DQ62

74

M_A_DQ63

76

M_A_DQ6

123

M_A_DQ7

125

M_A_DQ2

135

M_A_DQ3

137

M_A_DQ4

124

M_A_DQ5

126

M_A_DQ1

134

M_A_DQ0

136

M_A_DQ42

141

M_A_DQ47

143

M_A_DQ44

151

M_A_DQ40

153

M_A_DQ46

140

M_A_DQ43

142

M_A_DQ45

152

M_A_DQ41

154

M_A_DQ21

157

M_A_DQ17

159

M_A_DQ20

173

M_A_DQ19

175

M_A_DQ16

158

M_A_DQ22

160

M_A_DQ23

174

M_A_DQ18

176

M_A_DQ38

179

M_A_DQ36

181

M_A_DQ37

189

M_A_DQ32

191

M_A_DQ33

180

M_A_DQ39

182

M_A_DQ35

192

M_A_DQ34

194

Layout Note: Place these Caps near SO DIMM 0

+1.8V

+1.8V

D D

C C

B B

M_A_A[0..15]6,10

M_A_BS#26,10

M_A_BS#06,10

M_A_BS#16,10

M_A_CS#06,10

M_A_CS#16,10

M_CLK_DDR06

M_CLK_DDR#06

M_CLK_DDR16

M_CLK_DDR#16

M_CKE06,10

M_CKE16,10

M_A_CAS#6,10

M_A_RAS#6,10

M_A_WE#6,10

SMB_MEM_SCL9,22

SMB_MEM_SDA9,22

M_ODT06,10

M_ODT16,10

M_A_DM[0..7]6

M_A_DQS[0..7]6

M_A_DQS#[0..7]6

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM1

M_A_DM3

M_A_DM6

M_A_DM7

M_A_DM0

M_A_DM5

M_A_DM2

M_A_DM4

M_A_DQS1

M_A_DQS3

M_A_DQS6

M_A_DQS7

M_A_DQS0

M_A_DQS5

M_A_DQS2

M_A_DQS4

M_A_DQS#1

M_A_DQS#3

M_A_DQS#6

M_A_DQS#7

M_A_DQS#0

M_A_DQS#5

M_A_DQS#2

M_A_DQS#4

CON2A

102

A0

101

A1

100

A2

99

A

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR_DIMM_200P

M_A_DQ[0..63]6

3

+1.8V 5,7,9,10,38,65

+3VS 5, 9,13,14,15,16,17,18,19,20,21,22,23,24,26,27,28,29,30,31,34,36,38,39,41,48,61,70

+1.8V

CON2B

112

VSS16

VDD1

111

VSS17

VDD2

117

VSS18

VDD3

96

VSS19

VDD4

95

VSS20

VDD5

118

VSS21

VDD6

81

VSS22

VDD7

82

VSS23

VDD8

87

VSS24

VDD9

103

VSS25

VDD10

88

VSS26

VDD11

104

VSS27

VDD12

VSS28

199

VSS29

VDDSPD

VSS30

M_A_CS#26,10

M_A_CS#36,10

VTT_REF

C136

0.1U

C139

C140

0.1U

0.1U

C145

C144

1U/6.3V

1U/6.3V

83

120

50

69

163

1

201

202

203

204

47

133

183

77

12

48

184

78

71

72

121

122

196

193

8

DDR_DIMM_200P

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

NP_NC1

NP_NC2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

8 55

4

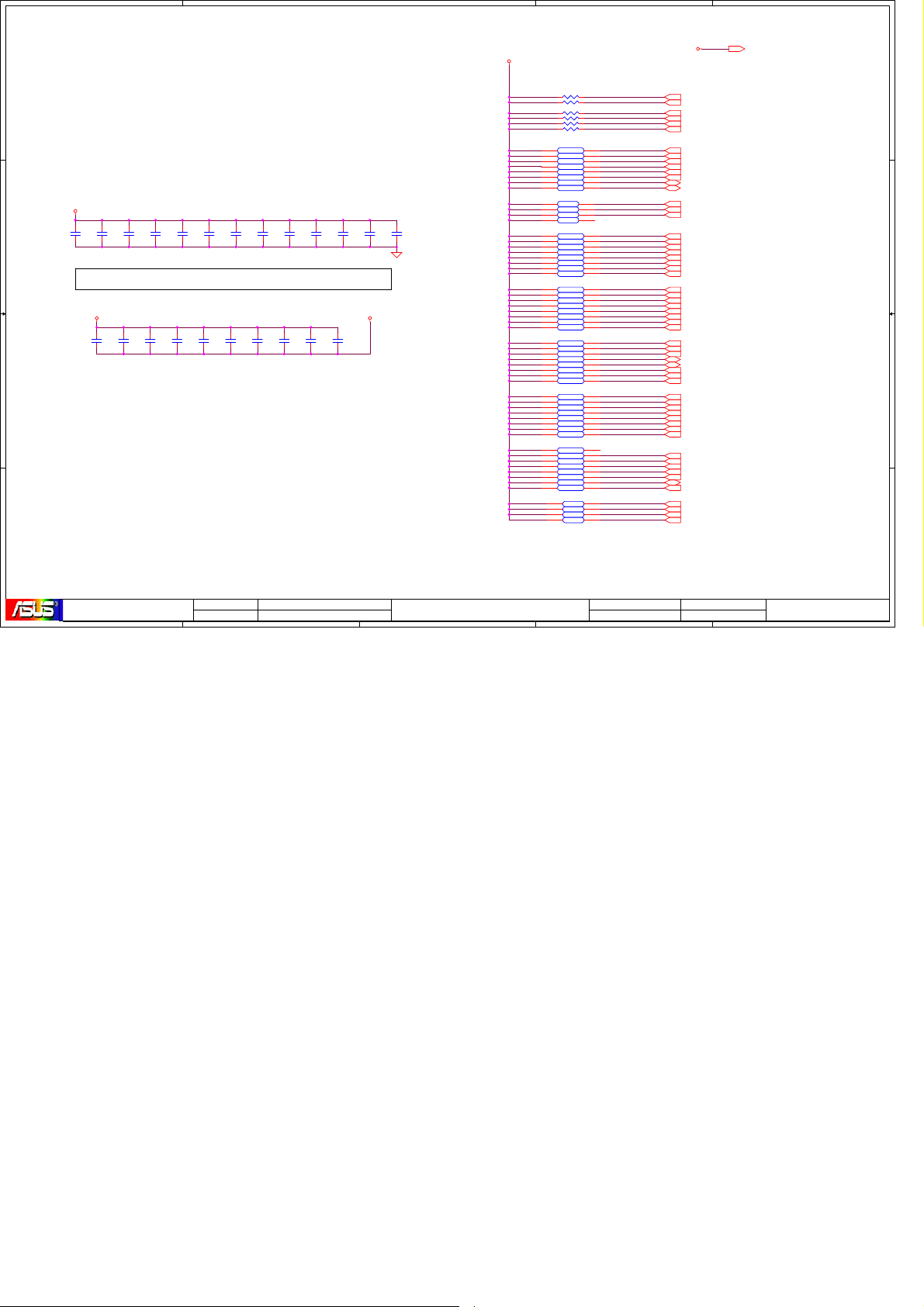

DESCRIPTION:

DDR2 SO-DIMM0

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

C156

1U/6.3V

+1.8V

+3VS

+5V

+3VS

C152

C153

0.1U

0.1U

C157

1U/6.3V

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_B_DQ[0..63]

M_B_DQ43

5

DQ0

M_B_DQ42

7

DQ1

M_B_DQ46

17

DQ2

M_B_DQ47

19

DQ3

M_B_DQ41

4

DQ4

M_B_DQ45

6

DQ5

M_B_DQ44

14

DQ6

M_B_DQ40

16

DQ7

M_B_DQ48

23

DQ8

M_B_DQ53

25

DQ9

M_B_DQ55

35

M_B_DQ54

37

M_B_DQ49

20

M_B_DQ52

22

M_B_DQ51

36

M_B_DQ50

38

M_B_DQ58

43

M_B_DQ63

45

M_B_DQ56

55

M_B_DQ57

57

M_B_DQ62

44

M_B_DQ59

46

M_B_DQ61

56

M_B_DQ60

58

M_B_DQ35

61

M_B_DQ39

63

M_B_DQ37

73

M_B_DQ36

75

M_B_DQ38

62

M_B_DQ34

64

M_B_DQ33

74

M_B_DQ32

76

M_B_DQ30

123

M_B_DQ31

125

M_B_DQ29

135

M_B_DQ24

137

M_B_DQ26

124

M_B_DQ27

126

M_B_DQ25

134

M_B_DQ28

136

M_B_DQ18

141

M_B_DQ22

143

M_B_DQ20

151

M_B_DQ21

153

M_B_DQ19

140

M_B_DQ23

142

M_B_DQ17

152

M_B_DQ16

154

M_B_DQ0

157

M_B_DQ1

159

M_B_DQ7

173

M_B_DQ3

175

M_B_DQ4

158

M_B_DQ5

160

M_B_DQ6

174

M_B_DQ2

176

M_B_DQ9

179

M_B_DQ8

181

M_B_DQ13

189

M_B_DQ12

191

M_B_DQ11

180

M_B_DQ14

182

M_B_DQ15

192

M_B_DQ10

194

Layout Note: Place these Caps near SO DIMM 1

+1.8V

C151

0.1U

+1.8V

C155

1U/6.3V

M_B_DQ[0..63]6

D D

C C

B B

A A

M_B_A[0..15]6,10

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_BS#26,10

M_B_BS#06,10

M_B_BS#16,10

M_B_CS#06,10

M_B_CS#16,10

M_CLK_DDR36

M_CLK_DDR#36

M_CLK_DDR26

M_CLK_DDR#26

M_CKE26,10

+3VS

M_CKE36,10

M_B_CAS#6,10

M_B_RAS#6,10

M_B_WE#6,10

SMB_MEM_SCL8,22

SMB_MEM_SDA8,22

M_ODT26,10

M_ODT36,10

M_B_DM[0..7]6

M_B_DQS[0..7]6

M_B_DQS#[0..7]6

M_B_A15

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM0

M_B_DM1

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS4

M_B_DQS3

M_B_DQS2

M_B_DQS0

M_B_DQS1

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS#4

M_B_DQS#3

M_B_DQS#2

M_B_DQS#0

M_B_DQS#1

CON1A

102

A0

101

A1

100

A2

99

A

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR2_DIMM_200P

3

+1.8V 5,7,8,10,38,65

+3VS 5 ,8,13,14,15,16,17,18,19,20,21,22,23,24,26,27,28,29,30,31,34,36,38,39,41,48,61,70

+5V 16,18,25,28,31,38,40,41

+1.8V

CON1B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

C148

M_B_CS#26,10

M_B_CS#36,10

0.1U

C158

1U/6.3V

VTT_REF

C149

C150

1U/6.3V_*

0.1U

C154

0.1U

C159

1U/6.3V

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

1

VREF

201

GND0

202

GND1

203

NP_NC1

204

NP_NC2

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

DDR2_DIMM_200P

C161

0.01U/X7R

+1.8V

R156

10K_1

R157

10K_1

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

+5V

C160

+5V

V+

+

V-

LMV321IDBVR

VTT_REF

U5

4

C166

1U/6.3V

T21

C758

1000PF/50V

0.1U

1

3

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

9 55

4

DESCRIPTION:

DDR2 SO-DIMM1

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

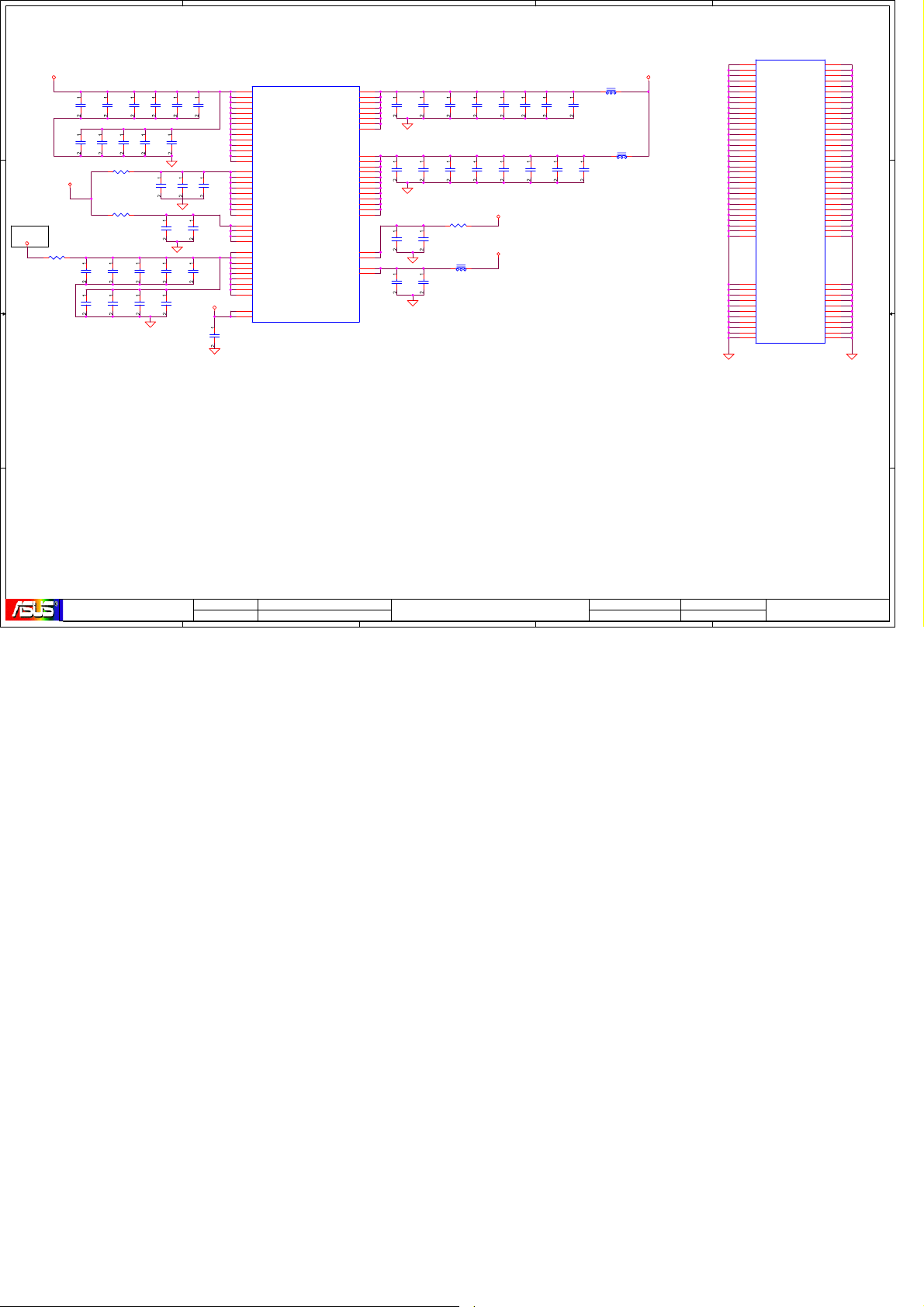

+0.9V

D D

+0.9V

C171

C167

C168

C169

C C

0.1U

0.1U

C170

0.1U

0.1U

C172

0.1U

C173

0.1U

0.1U

C175

C174

0.1U

C176

0.1U

0.1U

C178

C177

0.1U

C179

0.1U

0.1U

Layout note: Place one cap close to every 2 pullup resistors terminated to +0.9V

+0.9V

C180

0.1U

0.1U

B B

0.1U

0.1U

C184

C183

C182

C187

C185

0.1U

C188

0.1U

0.1U

C190

C189

0.1U

0.1U

+1.8V

C191

0.1U

R158 47

R159 47

R168 47

R184 47

R185 47

R187 47

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 2

47OHM

3 4

47OHM

5 6

47OHM

7 8

47OHM

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 16

47

2 15

47

3 14

47

4 13

47

5 12

47

6 11

47

7 10

47

8 9

47

1 2

47OHM

3 4

47OHM

5 6

47OHM

7 8

47OHM

RN10A

RN10B

RN10C

RN10D

RN3A

RN3B

RN3C

RN3D

RN9A

RN9B

RN9C

RN9D

RN9E

RN9F

RN9G

RN9H

RN4A

RN4B

RN4C

RN4D

RN4E

RN4F

RN4G

RN4H

RN7A

RN7B

RN7C

RN7D

RN7E

RN7F

RN7G

RN7H

RN2A

RN2B

RN2C

RN2D

RN2E

RN2F

RN2G

RN2H

RN6A

RN6B

RN6C

RN6D

RN6E

RN6F

RN6G

RN6H

RN5A

RN5B

RN5C

RN5D

RN5E

RN5F

RN5G

RN5H

M_CKE0

M_CKE1

M_A_BS#2

M_A_A4

M_A_A14

M_A_A15

M_ODT3

M_A_CS#3

M_ODT0

M_ODT1

M_A_CS#1

M_A_CS#0

M_A_BS#1

M_A_A13

M_A_A10

M_A_A9

M_A_CS#2

M_A_A12

M_A_A3

M_A_A1

M_A_A5

M_A_A8

M_A_A2

M_A_A0

M_A_A11

M_A_A7

M_A_A6

M_A_BS#0

M_A_WE#

M_B_CS#2

M_CKE2

M_B_BS#2

M_B_A9

M_B_CS#1

M_B_A10

M_B_BS#0

M_B_A14

M_CKE3

M_B_A12

M_B_A15

M_B_A11

M_B_A7

M_B_A5

M_B_A8

M_B_A4

M_B_A3

M_B_A6

M_B_A1

M_B_A0

M_B_A2

M_B_CS#0

M_ODT2

M_B_A13

M_B_CS#3

+0.9V

M_CKE0 6,8

M_CKE1 6,8

M_A_BS#2 6,8

M_A_A4 6,8

M_A_A14 6 ,8

M_A_A15 6 ,8

M_ODT3 6,9

M_A_CS#3 6,8

M_ODT0 6,8

M_ODT1 6,8

M_A_CS#1 6,8

M_A_CS#0 6,8

M_A_CAS# 6,8

M_A_RAS# 6,8

M_A_BS#1 6,8

M_A_A13 6 ,8

M_A_A10 6 ,8

M_A_A9 6,8

M_A_CS#2 6,8

M_A_A12 6 ,8

M_A_A3 6,8

M_A_A1 6,8

M_A_A5 6,8

M_A_A8 6,8

M_A_A2 6,8

M_A_A0 6,8

M_A_A11 6 ,8

M_A_A7 6,8

M_A_A6 6,8

M_A_BS#0 6,8

M_A_WE# 6,8

M_B_CS#2 6,9

M_CKE2 6,9

M_B_BS#2 6,9

M_B_A9 6,9

M_B_CS#1 6,9

M_B_CAS# 6,9

M_B_WE# 6,9

M_B_A10 6 ,9

M_B_BS#0 6,9

M_B_A14 6 ,9

M_CKE3 6,9

M_B_A12 6 ,9

M_B_A15 6 ,9

M_B_A11 6 ,9

M_B_A7 6,9

M_B_A5 6,9

M_B_A8 6,9

M_B_A4 6,9

M_B_A3 6,9

M_B_A6 6,9

M_B_A1 6,9

M_B_A0 6,9

M_B_A2 6,9

M_B_RAS# 6,9

M_B_BS#1 6,9

M_B_CS#0 6,9

M_ODT2 6,9

M_B_A13 6 ,9

M_B_CS#3 6,9

+0.9V 7,48,65

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

10 55

4

DESCRIPTION:

DDR2 ADDRESS TERMINATION

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

C760

0.1UF/16V

U4A

Y23

HT_CPU_RXD0_P

W24

HT_

V24

HT_CPU_RXD2_P

U22

HT_CPU_RXD3_P

R24

HT_CPU_RXD4_P

P24

HT_CPU_RXD5_P

P22

HT_CPU_RXD6_P

N22

HT_CPU_RXD7_P

Y21

HT_CPU_RXD8_P

V21

HT_CPU_RXD9_P

W21

HT_CPU_RXD10_P

T21

HT_CPU_RXD11_P

R18

HT_CPU_RXD12_P

P16

HT_CPU_RXD13_P

N20

HT_CPU_RXD14_P

M17

HT_CPU_RXD15_P

Y22

HT_CPU_RXD0_N

W23

HT_CPU_RXD1_N

V23

HT_CPU_RXD2_N

U21

HT_CPU_RXD3_N

R23

HT_CPU_RXD4_N

P23

HT_CPU_RXD5_N

P21

HT_CPU_RXD6_N

N21

HT_CPU_RXD7_N

Y20

HT_CPU_RXD8_N

W20

HT_CPU_RXD9_N

W22

HT_CPU_RXD10_N

U20

HT_CPU_RXD11_N

R19

HT_CPU_RXD12_N

P17

HT_CPU_RXD13_N

N19

HT_CPU_RXD14_N

N18

HT_CPU_RXD15_N

T23

HT_CPU_RX_CLK0_P

T22

HT_CPU_RX_CLK0_N

R21

HT_CPU_RX_CLK1_P

R20

HT_CPU_RX_CLK1_N

M23

HT_CPU_RXCTL_P

M22

HT_CPU_RXCTL_N

W19

HT_CPU_CAL_1P2V

Y19

HT_CPU_CAL_GND

N16

+1.2V_PLLHTCPU

T13

+1.2V_PLLHTMCP

C51MV

CPU_RXD1_P

HT_CPU_TXD0_P

HT_CPU_TXD1_P

HT_CPU_TXD2_P

HT_CPU_TXD3_P

HT_CPU_TXD4_P

HT_CPU_TXD5_P

HT_CPU_TXD6_P

HT_CPU_TXD7_P

HT_CPU_TXD8_P

HT_CPU_TXD9_P

HT_CPU_TXD10_P

HT_CPU_TXD11_P

HT_CPU_TXD12_P

HT_CPU_TXD13_P

HT_CPU_TXD14_P

HT_CPU_TXD15_P

HT_CPU_TXD0_N

HT_CPU_TXD1_N

HT_CPU_TXD2_N

HT_CPU_TXD3_N

HT_CPU_TXD4_N

HT_CPU_TXD5_N

HT_CPU_TXD6_N

HT_CPU_TXD7_N

HT_CPU_TXD8_N

HT_CPU_TXD9_N

HT_CPU_TXD10_N

HT_CPU_TXD11_N

HT_CPU_TXD12_N

HT_CPU_TXD13_N

HT_CPU_TXD14_N

HT_CPU_TXD15_N

HT_CPU_TX_CLK0_P

HT_CPU_TX_CLK0_N

HT_CPU_TX_CLK1_P

HT_CPU_TX_CLK1_N

HT_CPU_TXCTL_P

HT_CPU_TXCTL_N

CLKOUT_PRI_200MHZ_P

CLKOUT_PRI_200MHZ_N

CLKOUT_SEC_200MHZ_P

CLKOUT_SEC_200MHZ_N

HT_CPU_REQ*

HT_CPU_STOP*

HT_CPU_RESET*

HT_CPU_PWRGD

+2.5V_PLLHTCPU

C23

D23

E22

F23

H22

J21

K21

K23

D21

F19

F21

G20

J19

L17

L20

L18

C24

D24

E23

F24

H23

J22

K22

K24

D22

E20

E21

G19

J18

K17

K19

L19

G23

G24

G22

G21

L23

L24

B24

B23

A22

B21

F18

G18

D20

E19

L16

HTCPU_TXDP0

HTCPU_TXDP1

HTCPU_TXDP2

HTCPU_TXDP3

HTCPU_TXDP4

HTCPU_TXDP5

HTCPU_TXDP6

HTCPU_TXDP7

HTCPU_TXDP8

HTCPU_TXDP9

HTCPU_TXDP10

HTCPU_TXDP11

HTCPU_TXDP12

HTCPU_TXDP13

HTCPU_TXDP14

HTCPU_TXDP15

HTCPU_TXDN0

HTCPU_TXDN1

HTCPU_TXDN2

HTCPU_TXDN3

HTCPU_TXDN4

HTCPU_TXDN5

HTCPU_TXDN6

HTCPU_TXDN7

HTCPU_TXDN8

HTCPU_TXDN9

HTCPU_TXDN10

HTCPU_TXDN11

HTCPU_TXDN12

HTCPU_TXDN13

HTCPU_TXDN14

HTCPU_TXDN15

Int. PU

HTCPU_REQ#

1.5" ~ 7"

+2.5VS_PLLHT

C761

1UF/10V

T239

1

T240

1

1 2

R802 22kOhm_*

C762

0.1UF/16V

HTCPU_TXCLK0 4

HTCPU_TXCLK0# 4

HTCPU_TXCLK1 4

HTCPU_TXCLK1# 4

HTCPU_TXCTL 4

HTCPU_TXCTL# 4

CLK_CPU 5

CLK_CPU# 5

+2.5VS

HTCPU_STP# 5

HTCPU_RST# 5

HTCPU_PWRGD 5

L102

21

120Ohm/100Mhz

HTCPU_TXDP[0..15] 4

HTCPU_TXDN[0..15] 4

+2.5VS+1.2VS

breakout: 5/5

normal: 5/10

HTCPU_RXDP[0..15]4

D D

HTCPU_RXDN[0..15]4

C C

HTCPU_RXCLK04

HTCPU_RXCLK0#4

HTCPU_RXCLK14

HTCPU_RXCLK1#4

HTCPU_RXCTL4

HTCPU_RXCTL#4

+1.2VS_HT

R800 150Ohm

R801 150Ohm

B B

120Ohm/100Mhz

< 500 mil; 5/10

1 2

1 2

L101

21

HTCPU_RXDP0

HTCPU_RXDP1

HTCPU_RXDP2

HTCPU_RXDP3

HTCPU_RXDP4

HTCPU_RXDP5

HTCPU_RXDP6

HTCPU_RXDP7

HTCPU_RXDP8

HTCPU_RXDP9

HTCPU_RXDP10

HTCPU_RXDP11

HTCPU_RXDP12

HTCPU_RXDP13

HTCPU_RXDP14

HTCPU_RXDP15

HTCPU_RXDN0

HTCPU_RXDN1

HTCPU_RXDN2

HTCPU_RXDN3

HTCPU_RXDN4

HTCPU_RXDN5

HTCPU_RXDN6

HTCPU_RXDN7

HTCPU_RXDN8

HTCPU_RXDN9

HTCPU_RXDN10

HTCPU_RXDN11

HTCPU_RXDN12

HTCPU_RXDN13

HTCPU_RXDN14

HTCPU_RXDN15

HTCPUCA_1P2V

HTCPUCA_GND

+1.2VS_PLLHT

C759

1UF/10V

Near BGA

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

11 55

4

DESCRIPTION:

C51M HT

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

breakout: 5/5

normal: 5/10

HTMCP_RXDP[0..7]19

HTMCP_RXDN[0..7]19

HTMCP_RXCLK019

HTMCP_RXCLK0#19 HTMCP_TXCLK0# 19

HTMCP_RXCTL19

HTMCP_RXCTL#19

HTMCP_REQ#19

HTMCP_STP#19

HTMCP_RST#19

HTMCP_PWRGD19

CLK_25M19

CLK_NBHT19

CLK_NBHT#19

1.5" ~ 7"

HTMCP_RXDP0

HTMCP_RXDP1

HTMCP_RXDP2

HTMCP_RXDP3

HTMCP_RXDP4

HTMCP_RXDP5

HTMCP_RXDP6

HTMCP_RXDP7

HTMCP_RXDN0

HTMCP_RXDN1

HTMCP_RXDN2

HTMCP_RXDN3

HTMCP_RXDN4

HTMCP_RXDN5

HTMCP_RXDN6

HTMCP_RXDN7

D D

C C

B B

OD

OD1.5" ~ 7"

AD6

HT_MCP_RXD0_P

AC7

HT_

AA8

HT_MCP_RXD2_P

AA9

HT_MCP_RXD3_P

AD10

HT_MCP_RXD4_P

AD11

HT_MCP_RXD5_P

AC12

HT_MCP_RXD6_P

AC13

HT_MCP_RXD7_P

AA6

HT_MCP_RXD8_P

W7

HT_MCP_RXD9_P

Y8

HT_MCP_RXD10_P

V9

HT_MCP_RXD11_P

Y10

HT_MCP_RXD12_P

AA11

HT_MCP_RXD13_P

V11

HT_MCP_RXD14_P

W12

HT_MCP_RXD15_P

AC6

HT_MCP_RXD0_N

AB7

HT_MCP_RXD1_N

AB8

HT_MCP_RXD2_N

AB9

HT_MCP_RXD3_N

AC10

HT_MCP_RXD4_N

AC11

HT_MCP_RXD5_N

AB12

HT_MCP_RXD6_N

AB13

HT_MCP_RXD7_N

Y6

HT_MCP_RXD8_N

Y7

HT_MCP_RXD9_N

AA7

HT_MCP_RXD10_N

W9

HT_MCP_RXD11_N

W10

HT_MCP_RXD12_N

Y12

HT_MCP_RXD13_N

W11

HT_MCP_RXD14_N

V13

HT_MCP_RXD15_N

AD9

HT_MCP_RX_CLK0_P

AC9

HT_MCP_RX_CLK0_N

U10

HT_MCP_RX_CLK1_P

T10

HT_MCP_RX_CLK1_N

AD14

HT_MCP_RXCTL_P

AC14

HT_MCP_RXCTL_N

AB5

HT_MCP_REQ*

AA5

HT_MCP_STOP*

AC5

HT_MCP_RESET*

AD5

HT_MCP_PWRGD

AC4

CLKIN_25MHZ

Y5

CLKIN_200MHZ_P

W5

CLKIN_200MHZ_N

U4B

MCP_RXD1_P

C51MV

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL_P

HT_MCP_TXCTL_N

CLKOUT_CTERM_GND

SCLKIN_MCLKOUT_200MHZ_P

SCLKIN_MCLKOUT_200MHZ_N

HT_MCP_CAL_1P2V

HT_MCP_CAL_GND

HTMCP_TXDP0

AC24

HTMCP_TXDP1

AD23

HTMCP_TXDP2

AC22

HTMCP_TXDP3

AC20

HTMCP_TXDP4

AB18

HTMCP_TXDP5

AA17

HTMCP_TXDP6

AB16

HTMCP_TXDP7

AC16

AB21

AB20

AB19

W18

W15

AA15

Y14

W13

HTMCP_TXDN0

AC23

HTMCP_TXDN1

AD22

HTMCP_TXDN2

AC21

HTMCP_TXDN3

AD20

HTMCP_TXDN4

AC18

HTMCP_TXDN5

AB17

HTMCP_TXDN6

AB15

HTMCP_TXDN7

AD16

AB22

AA20

AA19

V17

V15

Y15

W14

Y13

AC19

AD19

Y17

W17

AC15

AD15

CLKOUT_CTERM_GND

B22

A20

B20

HTMCPCA_1P2V

AB23

HTMCPCA_GND

AB24

T241

1

T242

1

< 500 mil; 5/5/10

R806 150Ohm

R807 150Ohm

1 2

R805 2.37KOhm

1 2

1 2

HTMCP_TXDP[0..7] 19

HTMCP_TXDN[0..7] 19

HTMCP_TXCLK0 19

HTMCP_TXCTL 19

HTMCP_TXCTL# 19

+1.2VS

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

12 55

4

DESCRIPTION:

C51M HT TO MCP

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

4

3

2

1

C768

0.1UF/16V

U4C

J8

PE0_RX0_P

J6

PE0

K9

PE0_RX2_P

L6

PE0_RX3_P

L7

PE0_RX4_P

M9

PE0_RX5_P

N8

PE0_RX6_P

N6

PE0_RX7_P

R6

PE0_RX8_P

P3

PE0_RX9_P

R8

PE0_RX10_P

U6

PE0_RX11_P

T8

PE0_RX12_P

U7

PE0_RX13_P

V4

PE0_RX14_P

Y3

PE0_RX15_P

J7

PE0_RX0_N

J5

PE0_RX1_N

J9

PE0_RX2_N

L5

PE0_RX3_N

L8

PE0_RX4_N

M8

PE0_RX5_N

N7

PE0_RX6_N

N5

PE0_RX7_N

R5

PE0_RX8_N

P4

PE0_RX9_N

R7

PE0_RX10_N

U5

PE0_RX11_N

T9

PE0_RX12_N

U8

PE0_RX13_N

V3

PE0_RX14_N

AA3

PE0_RX15_N

D1

PE0_PRSNT*

G6

PE1_RX_P

H6

PE1_RX_N

E2

PE1_PRSNT*

J4

PE2_RX_P

K3

PE2_RX_N

E3

PE2_PRSNT*

D3

PE1_CLKREQ*/CLK

E4

PE2_CLKREQ*/DATA

AC3

PE_REFCLKIN_P

AB3

PE_REFCLKIN_N

T11

+1.2V_PLLPE

C51MV

_RX1_P

PE0_TX0_P

PE0_TX1_P

PE0_TX2_P

PE0_TX3_P

PE0_TX4_P

PE0_TX5_P

PE0_TX6_P

PE0_TX7_P

PE0_TX8_P

PE0_TX9_P

PE0_TX10_P

PE0_TX11_P

PE0_TX12_P

PE0_TX13_P

PE0_TX14_P

PE0_TX15_P

PE0_TX0_N

PE0_TX1_N

PE0_TX2_N

PE0_TX3_N

PE0_TX4_N

PE0_TX5_N

PE0_TX6_N

PE0_TX7_N

PE0_TX8_N

PE0_TX9_N

PE0_TX10_N

PE0_TX11_N

PE0_TX12_N

PE0_TX13_N

PE0_TX14_N

PE0_TX15_N

PE0_REFCLK_P

PE0_REFCLK_N

PE1_TX_P

PE1_TX_N

PE1_REFCLK_P

PE1_REFCLK_N

PE2_TX_P

PE2_TX_N

PE2_REFCLK_P

PE2_REFCLK_N

PE_TSTCLK_P

PE_TSTCLK_N

PE_RESET*

PE_CTERM_GND

EXP_TXP15

L1

EXP_TXP14

L3

EXP_TXP13

L4

EXP_TXP12

M4

EXP_TXP11

P1

EXP_TXP10

R1

EXP_TXP9

R3

EXP_TXP8

R4

EXP_TXP7

U4

EXP_TXP6

V1

EXP_TXP5

W1

EXP_TXP4

W3

EXP_TXP3

AA1

EXP_TXP2

AB1

EXP_TXP1

AC1

EXP_TXP0

AD2

EXP_TXN15

L2

EXP_TXN14

M2

EXP_TXN13

M3

EXP_TXN12

N3

EXP_TXN11

P2

EXP_TXN10

R2

EXP_TXN9

T2

EXP_TXN8

T3

EXP_TXN7

U3

EXP_TXN6

V2

EXP_TXN5

W2

EXP_TXN4

Y2

EXP_TXN3

AA2

EXP_TXN2

AB2

EXP_TXN1

AC2

EXP_TXN0

AD3

K1

K2

PCIE_TXP1

G4

PCIE_TXN1

G5

G2

G3

PCIE_TXP2

H4

PCIE_TXN2

J3

H2

H3

F1

F2

G1

D2

R810 2.37KOhm

C763

C765

1 2

R809 100Ohm_*

1 2

0.1UF/10V

12

12

C764 0 .1UF/10V

0.1UF/10V

12

12

C766 0 .1UF/10V

EXP_TXP[0..15] 16

EXP_TXN[0..15] 16

CLK_PCIE_VGA 16

CLK_PCIE_VGA# 16

PCIE_TXP1_MINICARD 30

PCIE_TXN1_MINICARD 30

CLK_PCIE_MINICARD 30

CLK_PCIE_MINICARD# 30

PCIE_TXP2_NEWCARD 31

PCIE_TXN2_NEWCARD 31

CLK_PCIE_NEWCARD 31

CLK_PCIE_NEWCARD# 31

PE_RST# 16,30

EXP_RXP[0..15]16

D D

EXP_RXN[0..15]16

C C

B B

VGA_DETECT#16,20

+3VS

R7133

10KOhm_*

PRSNT_NEWCARD#

GPU_ON16,20

1 2

R7141 0Ohm_*

1 2

R7140 0Ohm

PCIE_RXP1_MINICARD30

PCIE_RXN1_MINICARD30

PCIE_RXP2_NEWCARD31

PCIE_RXN2_NEWCARD31

PRSNT_NEWCARD#31

CLK_REQ_MINICARD#30

CLK_REQ_NEWCARD#31

+1.2VS

120Ohm/100Mhz

EXP_RXP15

EXP_RXP14

EXP_RXP13

EXP_RXP12

EXP_RXP11

EXP_RXP10

EXP_RXP9

EXP_RXP8

EXP_RXP7

EXP_RXP6

EXP_RXP5

EXP_RXP4

EXP_RXP3

EXP_RXP2

EXP_RXP1

EXP_RXP0

EXP_RXN15

EXP_RXN14

EXP_RXN13

EXP_RXN12

EXP_RXN11

EXP_RXN10

EXP_RXN9

EXP_RXN8

EXP_RXN7

EXP_RXN6

+3VS

EXP_RXN5

EXP_RXN4

EXP_RXN3

EXP_RXN2

EXP_RXN1

R808

EXP_RXN0

10KOhm

L103

+1.2VS_PLLPE

21

C767

1UF/16V_*

A A

<Core Design>

PROJECT:

5

A8T

REVISION

2.1

Friday, July 21, 2006

DATE:

SHEET OF

13 55

4

DESCRIPTION:

C51M PCI-E

3

RELEASE DATE :

2

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

Albert Su

5

DAC_R_C51M

DAC_G_C51M

124Ohm

L104

21

C774

0.1UF/16V

U53

S

IA0

IA1

YA

IB0

IB1

YB

GND YC

PI5C3257QE

10KOhm

10KOhm

10KOhm

10KOhm

R817

C769

0.01UF/25V

+3VS_DAC

C770

4.7UF/6.3V

+1.2VS_PLLGCI

C780

0.1UF/16V

16

VCC

15

E#

14

ID0

13

ID1

12

YD

11

IC0

10

IC1

RN36A

RN36B

RN36C

RN36D

REVISION

DAC_B_C51M

DAC_RSET

DAC_VREF

10 mA

C771

0.1UF/16V

20 mA

X1

X2

R819

22KOhm_*

C781

0.1UF/16V

LOAD_VIDEO

LOAD_VGA

2.1

DAC_HSYNC_C51M18

R814

R813

D D

150Ohm

150Ohm

R815

150Ohm

Place near C51M

+2.5VS

C C

27MREF16

B B

C51MV TV/CRT

SELECT

A A

1 2

0Ohm_*

MCP_TV_EN22

R31

150Ohm

Place near switch

<Core Design>

PROJECT:

DAC_VSYNC_C51M18

R816

124Ohm_*

+3VS

120Ohm/100Mhz

L105

120Ohm/100Mhz

R51

X1 X2

R1.1

+1.2VS

R827 0Ohm

1 2

DAC_R_NB

TVDAC_C_NB

DAC_R_C51M

DAC_G_NB

TVDAC_Y_NB

DAC_G_C51M

R32

150Ohm

R1.1 R1.1

5

21

C773

4.7UF/6.3V

X6

1 2

27Mhz

C778

18PF/50V

1 2

R823 0Ohm

+3VS

+2.5VS_PLLGPU

C779

18PF/50V

R826

22KOhm

1

2

3

4

5

6

7

8 9

Place near connector

1 2

3 4

5 6

7 8

A8T

4

U4D

A5

DAC_RED

B6

DAC

_GREEN

A6

DAC_BLUE

B7

DAC_HSYNC

C7

DAC_VSYNC

D8

DAC_RSET

D9

DAC_VREF

C8

DAC_IDUMP

A9

+3.3V_DAC

H13

+2.5V_PLLGPU

C9

XTAL_IN

B9

XTAL_OUT

F12

NC1/DDC_CLK

E11

NC2/DDC_DATA

E17

NC3/HPDET

F17

NC4/EE_CLK

G17

NC5/EE_DATA

R9

+1.2V_PLLGPU

P9

+1.2V_PLLCORE

H16

+1.2V_PLLIFP

C51MV

+5VS

C7110

0.1UF/16V

DAC_B_NB

TVDAC_CVBS_NB

DAC_B_C51M