Page 1

ARCAM

AVR600 Service manual issue 1.2

UA

Page 2

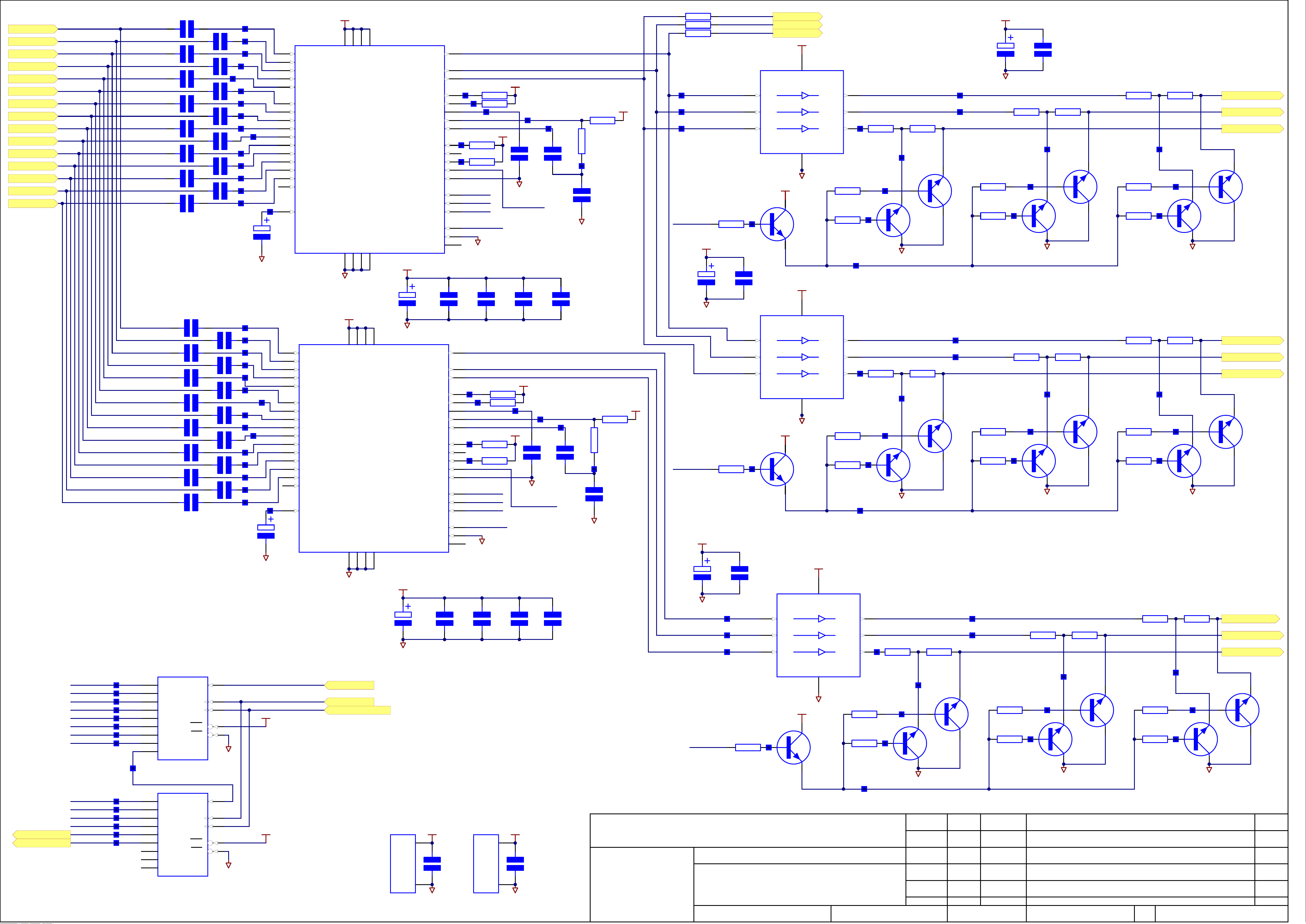

L123AY– Connection board and PSU

This PCB provides the power for the unit through CON203:

+5V_STBY – 5V standby supply L118 RS232, L126 display (on in standby)

+3V3 PW338 – L122 PW338 supply (on in standby)

1V8D – L122 PW338 supply (on in standby)

+5V_1 – general 5V supply

+6V_1 – L156 DSP, L126 Display & L119 NET supply

+40V_VFD – L126 Display

+15V – linear +15V supply

-15V – linear -15V supply

LK100 or the thermal switch from the power amp transformer is required to

pass the live mains. SW101 switches between 230V & 115V.

R101 & R102 are NTC parts to prevent inrush currents when the power amp

is turned on.

CON202 takes the Clk PSU sync signal from L121, Relay SW from L122 (to

turn on the main supplies) and /AC present back to L122. /AC present is

generated from the standby transformer secondaries with D200.D210 &

TR200. This will prevent the unit from starting if it is not low.

The standby transformer is rectified with DBR200 (GBU4K) to give

UNREG_PW338 which is used for the 1V8D (REG206 – LM2670),

3V3_PW338 (REG201 – LM2670). The 12V for the relays to switch the

secondaries are also generated from REG207 (LM7812) which is then

regulated down to give +5V_STBY REG200 (LM7805).

When the signal Relay SW is taken high by the PW338, the secondaries of

the system & power amp transformer are switched in (RLY101 & RLY102).

This enables +15V, -15V (REG204 & REG205) & +5V_1 & +6V_1 (REG202 &

REG203).

Page 3

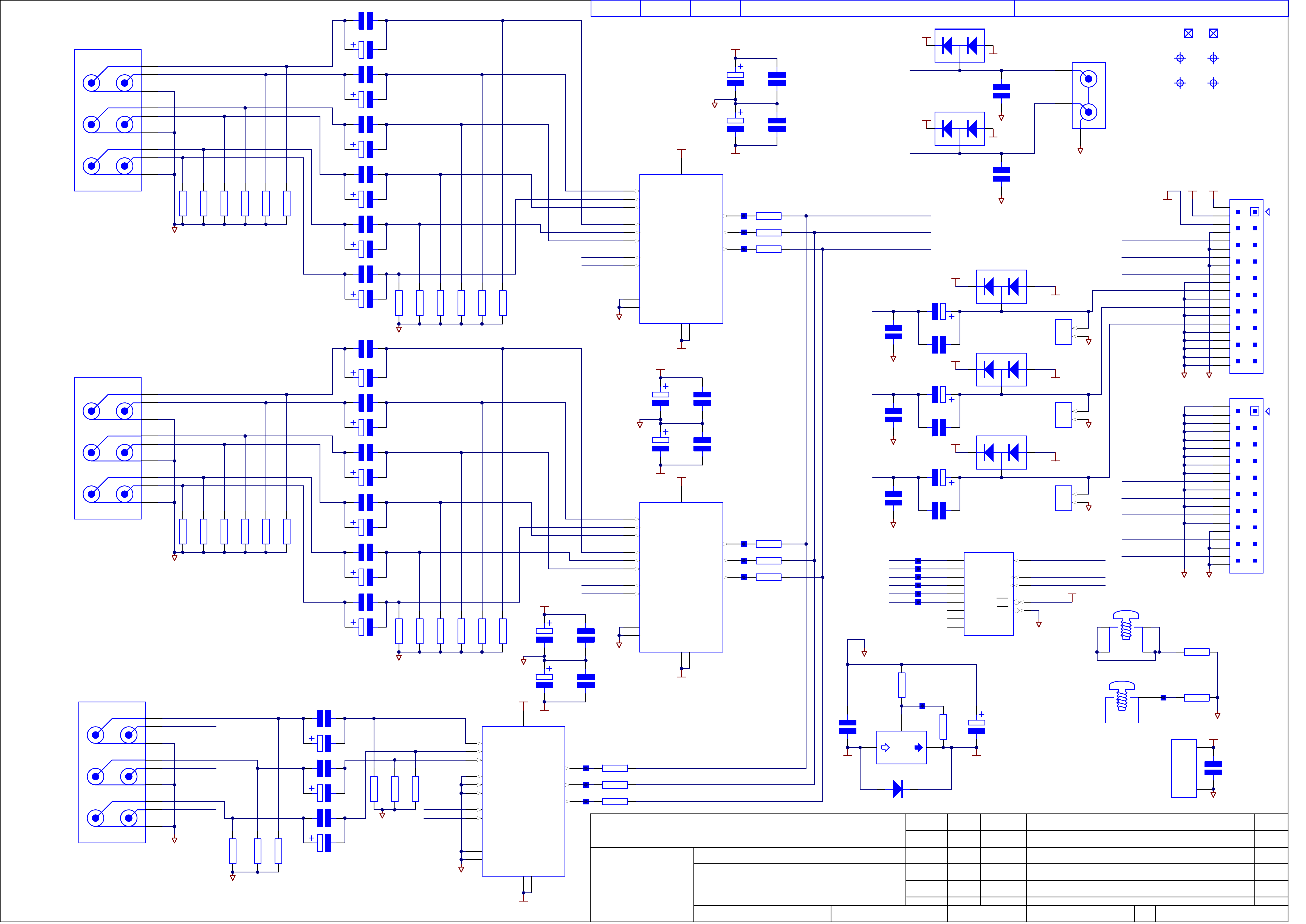

L113AY Component Input – Output board

This PCB selects between one of five component video inputs & also provides

the output connector for Zone 3 audio.

IC100, IC101 & IC104 (LT1675CGN video buffers) require +5V & -5V. The

+5V comes direct from L123 & -5V is generated locally from the -15V supply

(from L123).

Selection of the five inputs is via IC102 (74HCT595D serial to parallel

converter, controlled via SPI Clk, Data & Vcomp latch) and IC100, IC101,

IC104. IC102 generates a /ENx signal which tri-states the output when high

and enables the output when low. When low the input is selected with the

SELx signal, high for input1, low for input2.

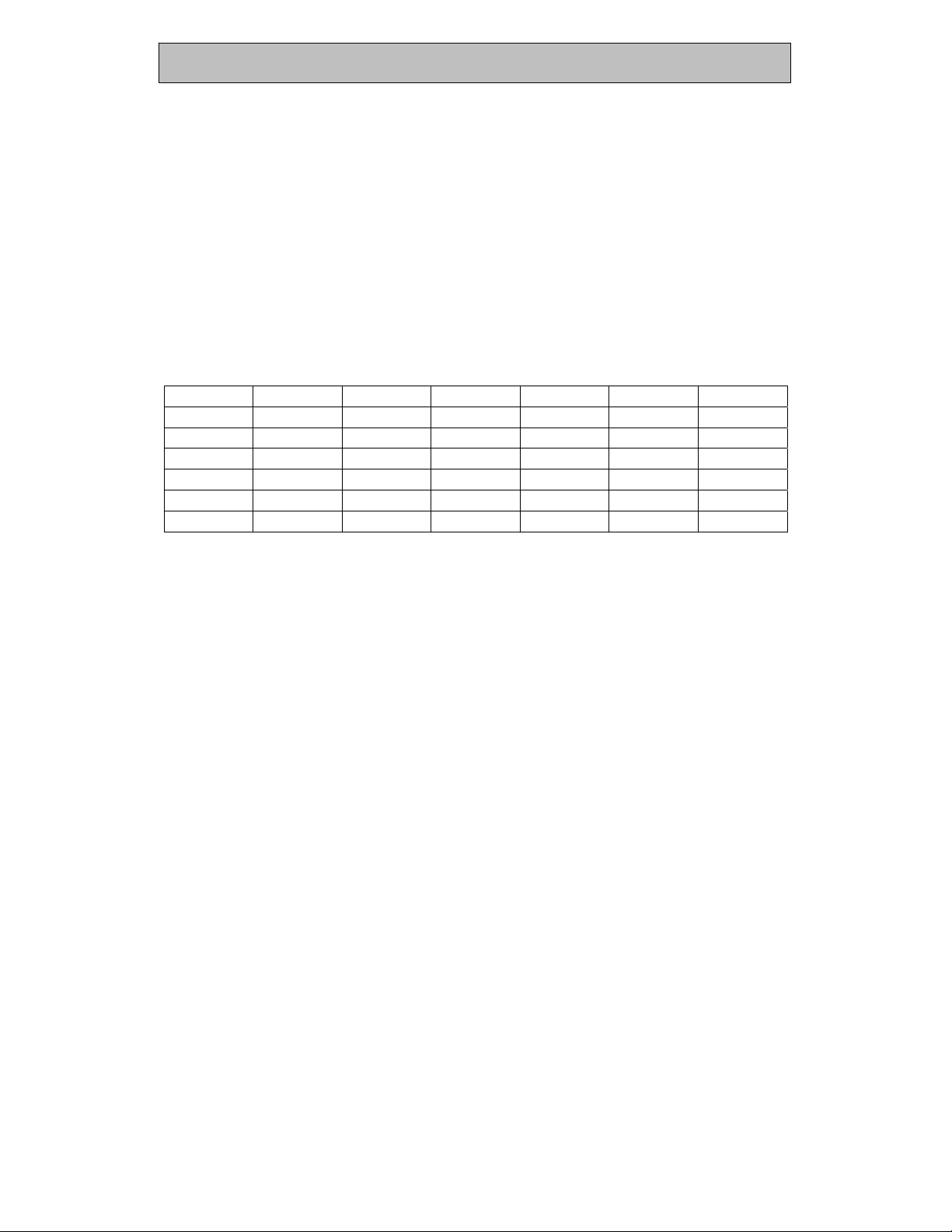

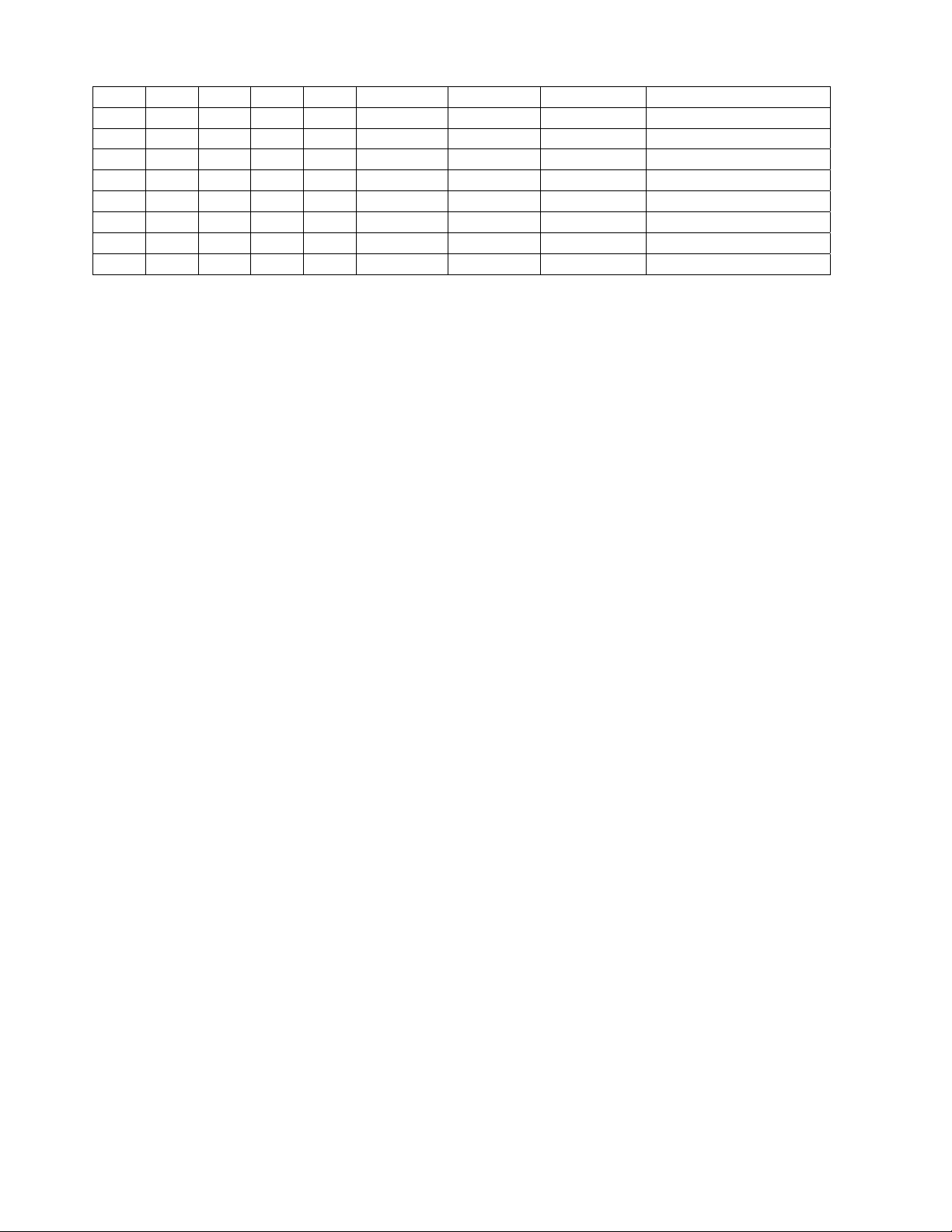

Truth table:

EN0 SEL0 EN1 SEL1 EN2 SEL2

0 0 1 X 1 x SAT

0 1 1 X 1 x AV

1 x 0 0 1 x VCR

1 x 0 1 1 x DVD

1 x 1 x 0 1 PVR

1 x 1 x 1 x BLANK*

*When component input is not used, BLANK should be selected.

SKT101 provides zone 3 audio output.

Page 4

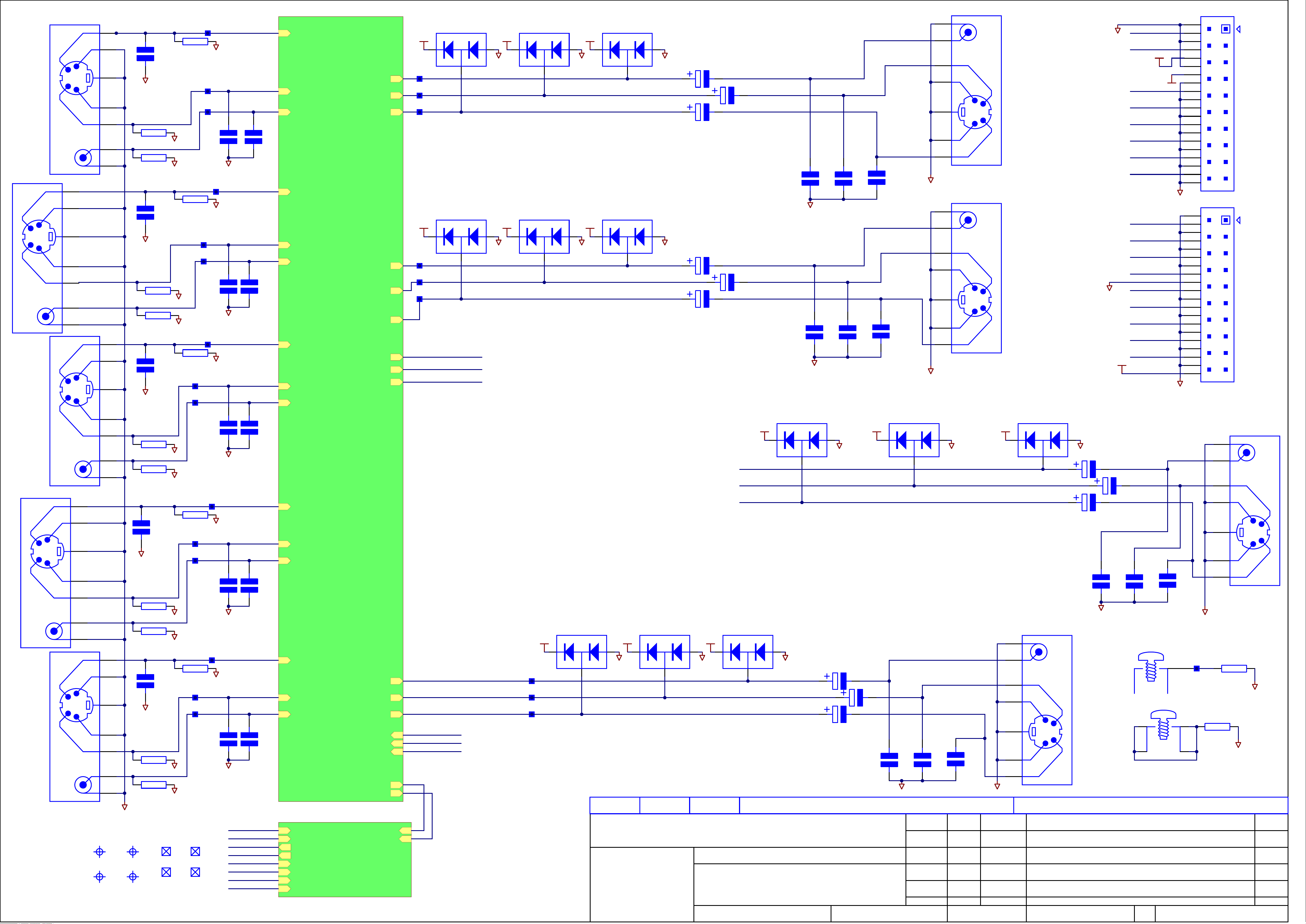

L114AY – Video input – output

This PCB selects between one of five s-video & composite video inputs for the

main input & zone 2 video. It also controls the volume control for Zone 2 & 3.

The main input video is selected using IC200 (LA73031V video mux) under

the control of IC205 & IC208 (74HC595 serial to parallel converters, controlled

by SPI Clk, Data & Vid IO Mux Latch). Inputs are selected using INSEL1,

INSEL2, INSEL3 (Z2 INSEL1, Z2INSEL2, Z2INSEL3 for Zone 2 via IC203 –

LA73031V video mux).

As there is only one sync separator within each LA73031V, it is necessary to

select if this is used for S-video or composite (this means that once composite

video is selected as the source, it is not possible to autodetect S-video) SYNC CTL selects, low = Svideo, high = composite.

There are two buffered (IC201 & IC202 – BA7623F video buffers) tape

outputs, VCR & PVR which can be muted with VCR Mute & PVR Mute

respectively through a transistor network. Each output is muted when that

input is selected to prevent feedback, otherwise the output is a copy of the

composite or S-video signal going to the main zone.

Zone 2 video is buffered through IC204 (BA7623F video buffer) and can also

be mute, if required using the signal Z2Vid Mute & a transistor network.

When S-video or composite inputs are not used, V MUX STBY should be

asserted high. Note: this will disable both the main Zone & Zone 2 S-video &

composite muxes.

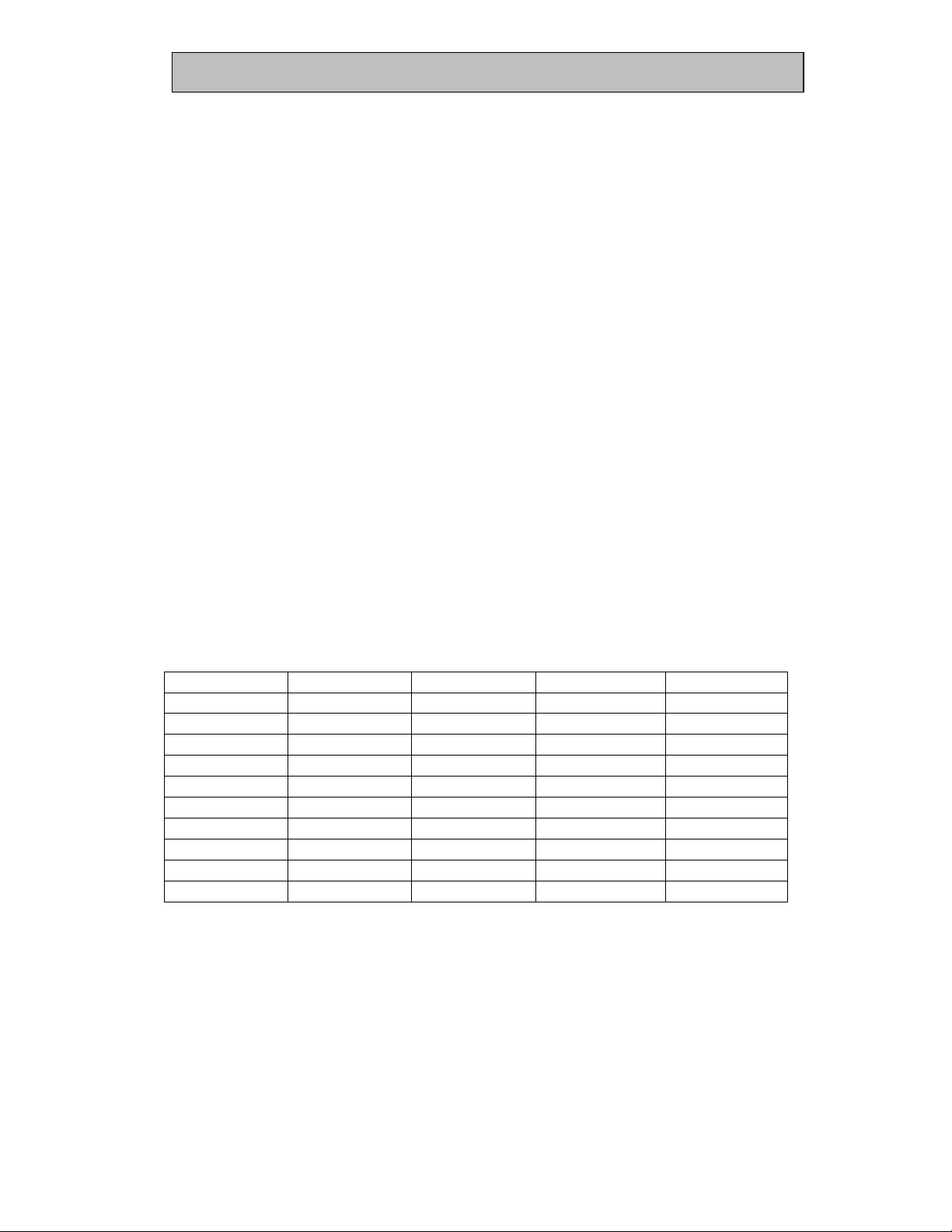

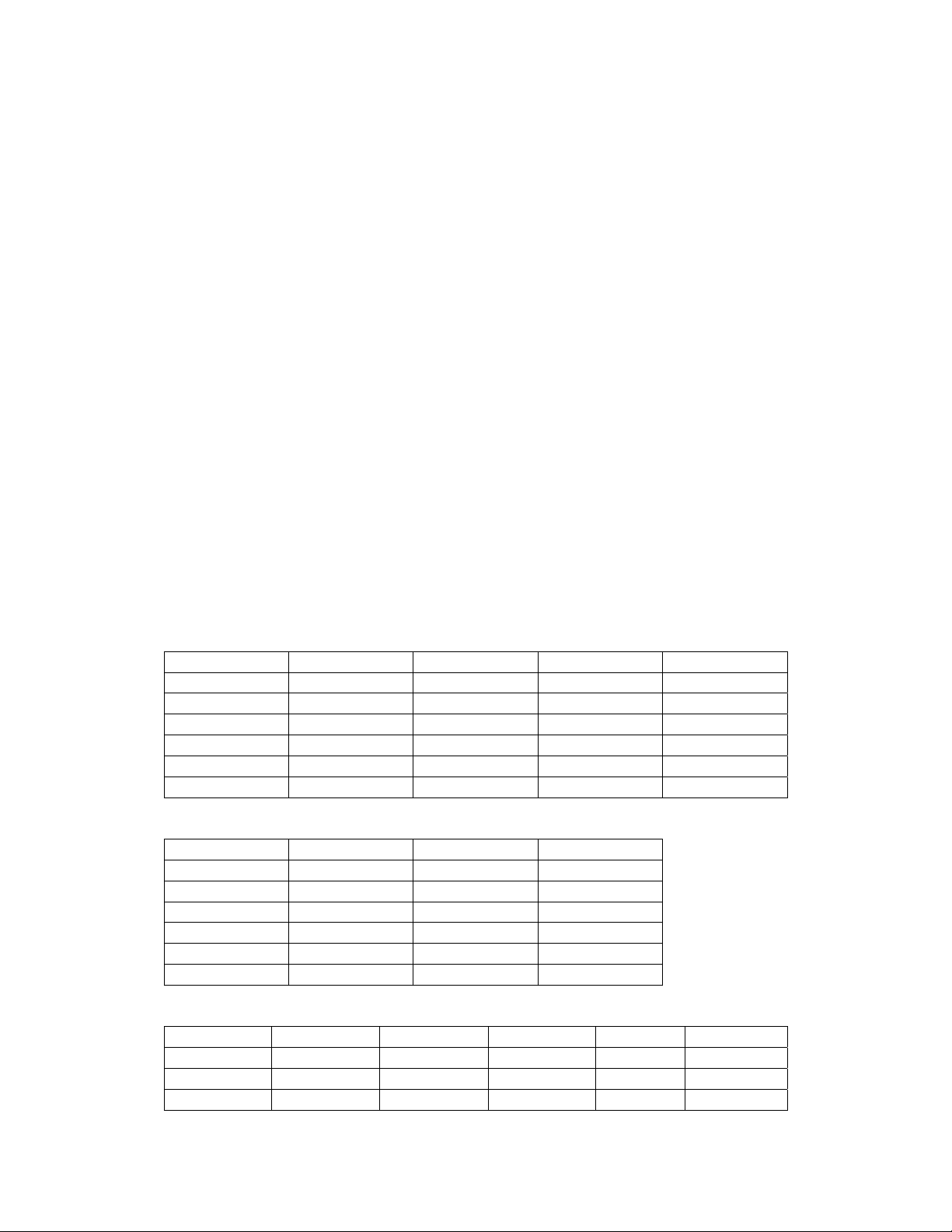

Video Input Truth table:

(Z2)INSEL1 (Z2)INSEL2 (Z2)INSEL3 (Z2)SYNCCTL

0 0 0 1 AV comp

0 0 1 1 SAT comp

0 1 0 1 DVD comp

0 1 1 1 PVR comp

1 0 0 1 VCR comp

0 0 0 0 AV S-vid

0 0 1 0 SAT S-vid

0 1 0 0 DVD S-vid

0 1 1 0 PVR S-vid

1 0 0 0 VCR S-vid

Volume control for Zone 2 & 3 uses IC300 & IC301 (BD3812F volume

controls) via a two-wire interface (Zone SPI Clk & Zone SPI Data). IC300 has

address D2, D1=1, IC301 has address D2, D1=0. The volume controls can

be muted from IC208 (Serial to parallel converter) using Z2 vol mute or Z3 vol

mute. The outputs are also relay controlled for powerup/down with Z2 Mute &

Z3 Mute directly from the PW338 using RLY300 & RLY301 as shunt relays.

The +7VA & -7VA required for the BD3812F volume controls is derived using

REG300 (LM1117) & REG301 (LM337LZ) from the +15V & -15V from L123.

Page 5

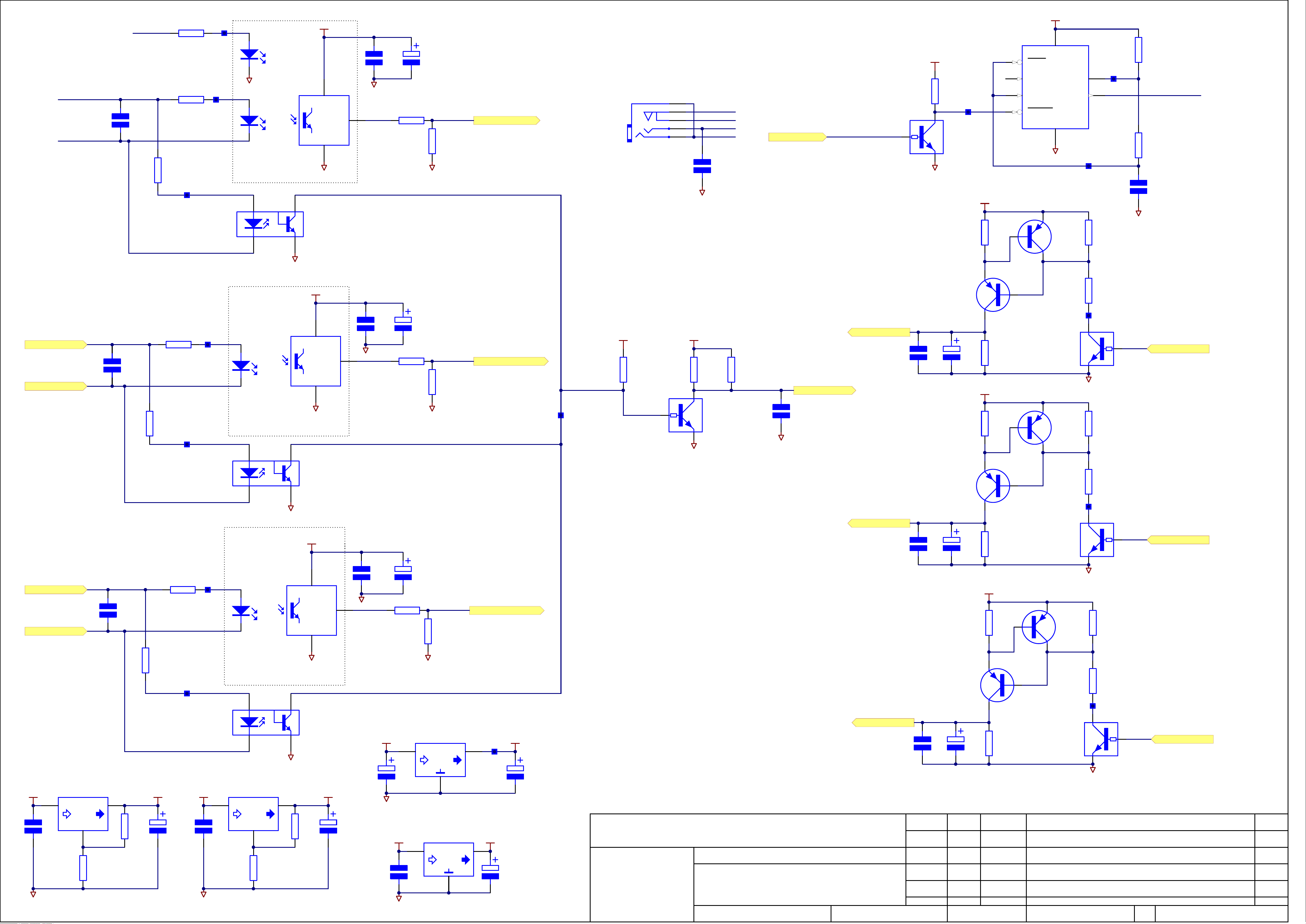

L115AY Digital Input – Output board

This PCB selects on of 8 external digital inputs or one of two internal digital

inputs & generates BClk, WClk & MClk for the DSP (see L156) & DAC (see

L117). It also generates the clocks for the ADC (see L116) when the unit is in

ADC mode.

The CD, AV & DVD inputs use coaxial connector SKT100 and feed into IC200

& IC201 (DS9637ACM buffers). The Tape, SAT, VCR & PVR inputs use

optical connectors RX100, RX101, RX102, RX103. The outputs are padded

down to give 3v3 outputs. There is also the Aux input which can be selected

(see L117), the Net input (see L119) and the HDMI SPDIF (see L122).

One of these inputs is then selected using IC202 & IC203 (74HC151 8-1 mux)

under the control of IC204 (74HC595D serial to parallel converter) controlled

by AN SPI Clk, AN SPI Data & Dig Mux Latch.

The selected input is fed to IC100 (WM8805 SPDIF Rx/Tx) which is controlled

from the PW338 via AN SCL, AN SDA & SPDIF /RESET. IC100 generates

8805MClk, 8805BClk & 8805WClk. Also, SPDIF Out which is a de-jittered

SPDIF stream which is then buffered by IC103 part A, B, C & D (parts E & F

are unused) to give both the optical output (TXC100) & 75ohmcoaxial output

(SKT101).

The selected input is also fed to IC205 part A (74HC123D monostable, part B

unused) which gives a high output from pin 13 (SPDIF_PRESENT to the

PW338) if an SPDIF signal is present.

BClk=64* WClk

MClk=128*WClk (192kHz/176.4kHz), 256*WClk (96kHz/88.2kHz), 512*WClk

(48kHz/44.1kHz) – this clock is used by the PSU to synchronise the switchers.

IC105 (XC95C36 Xilinx) generates a pre-delayed SPDIF stream from the

HDMI clocks (only MClk & WClk used) as the HDMI SPDIF is turned off

during HD audio transfer & the WM8805 does not have a zero delay PLL.

IC104 (74HCT157 Quad 2-1 mux) can also be used to re-direct the clocks

from the HDMI into the system.

IC100 (WM8805) can also operate in master mode to generate clocks for the

ADC when processing an analogue input.

3V3D is generated locally on the PCB from 5V_1 using REG200 (LM1117).

Page 6

L116AY Analogue input board

This PCB selects the analogue input for the main zone & Zone 2/3 and also

digitises the analogue input for processing by the DSP / transmission over

SPDIF.

One of seven phono inputs (Tape, CD, AV, DVD, SAT, VCR, PVR), Aux

(external) input (see L127), AM/FM & DAB(internal)/Sirius(external) inputs

(see L118), Net (internal) input (see L119) and Phono (see L117).

The input for the main zone is selected using IC200, IC208, IC205, IC209

(74HC4051D 8-1 mux) under the control of IC101 & IC102 (74HC595 serial to

parallel converter), controlled by AN SPI Data, AN SPI Clk & A In Mux Latch.

The muxes operate on the virtual earth of IC203 part A (left channel) & IC206

part A (right channel), both NJM2114 op amps, inverting the signal. Part B of

these two op amps re-invert the signal (correct phase) and this output is used

by the ADC & the direct path – Main L & Main R.

IC202 (NJM2114 op amp) inverts the original output of the mux (correct

phase) to provide the three tape outputs, Tape Out, PVR Out & VCR Out.

Each of these has individual mutes – IC201, IC204, IC207 (DG413DY

analogue mux) which mutes the output if that input is selected to prevent

feedback. Otherwise, the output is the selected input. The signals for these

mutes, /Tape Mute, /PVR Mute, /VCR Mute come from IC102 (74HC595

serial – parallel converter).

Selection of the Zone 2 input is very similar, using IC300, IC303, IC302,

IC304 (74HC4051 8-1 muxes) and IC301 (NJM2114 op amp).

The Main L & Main R are connected to input AIN1A/AIN1B of IC100 (CS5345

ADC). Aux L & Aux R are also connected to AIN4A/AIN4B as this is

configurable as the MIC input and can provide power from pin25 of IC100.

the ADC is controlled from the PW338 via AN SCL & AN SDA. ADC/RESET

also comes from IC102, so the ADC can be held in reset when not being

used.

The ADC always operates in slave mode and will sample at the rate dictated

by the incoming clocks from L115 (buffered on L122). ADC Data is sent to

L115 so that it can be transmitted by the SPDIF transmitter and selected for

input to the DSP.

+12VA (REG301 LM7812) & -12VA (REG304 LM7912) for the local op amps

are derived from +15V & -15V from L123.

+5VA (used by the ADC) is derived from the +12VA with REG302 (LM1117).

+3V3D (used by the ADC) is derived from the +12VA with REG300 (LM1117).

+3V3A (REG303 LM1117) & -3V3A (REG305 LM337LZ) for the muxes are

derived from +5VA & -12VA.

Page 7

Truth table

ADC

/RST

x x x x x x x x x x 1 1 1 0 0 0 Z2 CD

x x x x x x x x x x 1 1 1 0 0 1 Z2 AV

x x x x x x x x x x 1 1 1 0 1 0 Z2 SAT

x x x x x x x x x x 1 1 1 0 1 1 Z2 DVD

x x x x x x x x x x 1 1 1 1 0 0 Z2 VCR

x x x x x x x x x x 1 1 1 1 0 1 Z2 PVR

x x x x x x x x x x 1 1 1 1 1 0 Z2 TAPE

x x x x x x x x x x 0 0 0 1 1 1 Z2 Phono

x x x x x x x x x x 0 0 1 1 1 1 Z2 Aux

x x x x x x x x x x 0 1 0 1 1 1 Z2 GND

x x x x x x x x x x 0 1 1 1 1 1 Z2 AM/FM

x x x x x x x x x x 1 0 0 1 1 1 Z2 DAB/Sirius

x x x x x x x x x x 1 0 1 1 1 1 Z2 Net

x x x x x x x x x x 1 1 0 1 1 1 Z2 Spare

x x x x x x x x x x 1 1 1 1 1 1 Z2 GND

x x x x 1 1 1 0 0 0 x x x x x x Main CD

x x x x 1 1 1 0 0 1 x x x x x x Main AV

x x x x 1 1 1 0 1 0 x x x x x x Main SAT

x x x x 1 1 1 0 1 1 x x x x x x Main DVD

x x x x 1 1 1 1 0 0 x x x x x x Main VCR

x x x x 1 1 1 1 0 1 x x x x x x Main PVR

x x x x 1 1 1 1 1 0 x x x x x x Main Tape

x x x x 0 0 0 1 1 1 x x x x x x Main Phono

x x x x 0 0 1 1 1 1 x x x x x x Main Aux

x x x x 0 1 0 1 1 1 x x x x x x Main GND

x x x x 0 1 1 1 1 1 x x x x x x Main AM/FM

x x x x 1 0 0 1 1 1 x x x x x x Main DAB/Sirius

x x x x 1 0 1 1 1 1 x x x x x x Main Net

x x x x 1 1 0 1 1 1 x x x x x x Main Spare

x x x x 1 1 1 1 1 1 x x x x x x Main GND

x 1 1 0 x x x x x x x x x x x x Tape out mute

x 1 0 1 x x x x x x x x x x x x PVR out mute

x 0 1 1 x x x x x x x x x x x x VCR out mute

x 1 1 1 x x x x x x x x x x x x No loop mute

0 x x x x x x x x x x x x x x x ADC reset

1 x x x x x x x x x x x x x x x ADC running

VCR PVR TAPE 5 4 3 2 1 0 5 4 3 2 1 0

MUTE Main Asel Z2 Asel

Page 8

L117AY Analogue output

This PCB converts the digital audio from the DSP (see L156) to analogue

audio. It also configures the use of channels 6 & 7, has the headphone amp,

has the RIAA equaliser for the Phono input and handles the multi-channel

analogue input.

The phono amplifier is a standard RIAA response and is intended for use with

MM cartridges, 5mV (check this!) output. C128 & C129 are important to

prevent the DC offset of IC100 (NJM2114 op amp) from causing problems.

IC101 forms the basis of the headphone amplifier. The output of this section

goes to L127.

IC300 (CS4385 8-channel DAC) takes multichannel data (Data LR, Data

CSw, Data SlSr, Data SblSbr) from the DSP (L156) in addition to clocks (DAC

MClk, DAC BClk, DAC WClk) from L115 (buffered on L122). Control of the

DAC is via AN SDA, AN SCL (from the PW338) and DAC /RESET (from

IC212).

The balanced outputs from the DAC are filtered by IC400, IC401, IC402,

IC403 (NJM2114 op amps). All channels are identical except for the

subwoofer, which has 10dB (check this!) gain.

Left & right inputs to IC204 (CS3318 volume control) are multiplexed between

the filtered DAC output, the Main L & Main R direct analogue inputs (from

L116) and the left & right multichannel inputs (SKT200) with IC200

(74HC4052 dual 4-1 mux). This mux operates on the virtual earth of IC201

(NJM2114 op amp) and also provides the signals Mux L & Mux R.

The centre input to IC204 (CS3318 volume control) is multiplexed between

the filtered DAC output and the centre multichannel inputs (SKT200) with

IC203 (74HC4053 triple 2-1 mux). This mux operates on the virtual earth of

IC205 part A (NJM2114 op amp).

Subwoofer, surround left & surround right inputs to IC204 (CS3318 volume

control) are multiplexed between the filtered DAC output and the subwoofer,

surround left & surround right multichannel inputs (SKT200) with IC214

(74HC4053 triple 2-1 mux). This mux operates on the virtual earth of IC201

(NJM2114 op amp) part A (subwoofer) & IC207 (NJM2114 op amp - Surround

left & surround right).

IC213 selects between the filtered DAC output of surround back left / right,

surround back right / left multichannel inputs, Z2 L / Z2R and Mux L / Mux R.

This allows the use of channels 6 & 7 as either surround back left/right in the

main zone, or powered Zone 2 outputs, or bi-amped left/right in the main

zone. This mux operates on the virtual earth of IC209 (NJM2114 op amp).

IC204 (CS3318 volume control) is controlled by AN SCL, AN SDA (from the

PW338) and VOL /RESET & VOL /MUTE from IC212.

Page 9

Truth table

Sel0 Sel1 Sel2 Sel3 Sel4 Vol /RST Vol /Mute DAC /RST

0 0 0 0 0 1 1 1 DAC output

1 0 x x x 1 1 1 L/R analogue direct

0 1 1 1 0 1 1 1 MCH output

x x x 0 1 1 1 1 Sb=Zone 2

x x x 1 1 1 1 1 Sb=L/R

x x x x x 0 x x Volume control reset

x x x x x 1 0 x Volume control mute

x x x x x x x 0 DAC reset

The output of the volume control is buffered through IC202, IC206, IC208,

IC210 to remove any DC offset before going to CON100 (connection to the

power amp) and SKT100 & SKT100 phono outputs sockets. Shunt relay

muting is provided for power on/off, controlled from the PW338 (Main mute &

Sblr/Sbr mute).

Page 10

L118AY – IR – Trig – DAB/FM - RS232

This PCB handles the following functions:

RS232 communication with the PW338

iPod RS232 control (compatible with rLead & rDock)

Sirius satellite radio (US)

Z1, Z2, Z3 12V triggers

DAB

AM/FM

Z1, Z2, Z3 IR inputs.

CON102 & IC102 (MAX3232 RS232 converter, part1) provide the RS232

communication with the PW338 – used for RS232 control or updating. Note,

the signals RS232 Tx & RS232 Rx are labelled relative to the PW338, so

RS232 Tx is the Tx FROM the PW338.

CON105 & IC102 (MAX3232 RS232 converter, part2) provide the iPod RS232

communication. Pin 9 of CON105 (/iPod Present to PW338) is taken low

when an rLead is connected. Note, the signals iPod Tx & iPod Rx are

labelled relative to the UART (IC403, L122), so iPod Tx is the Tx FROM the

UART.

SKT101 provides the Sirius RS232 communication. Note, the signals Sirius

Tx 232 & Sirius Rx 232 are labelled relative to the UART (IC403, L122), so

Sirius Tx 232 is the Tx FROM the UART.

SKT101 also provides the +5V for the Sirius Home Connect module, so the

module does not require external power. This power comes from the +5V_1

(L123) and is connected to pins 1 & 2 of SKT101 as power & host presence.

Analogue audio also passes through this socket, so this is the only connection

to the Sirius module.

There are three triggers, Zone1 , Zone 2, Zone 3. These give a 12V 100mA

output when activated from IC101 (74HC595 serial to parallel converter). The

signals Z1 Trig, Z2 Trig & Z3 Trig are active high.

DAB uses the Gyrosignal 1122 module. As this module is normally controlled

via RS232, a CPLD, IC100 (XC95C36 Xilinx) is used to provide I2C control

from the PW338 (DAB SCL & DAB SDA). Due to an issue with the

Gyrosignal implementation of I2C within their CPLD, IC103 (SN74HC1GU04

single inverter) is required to invert the DAB SCL signal. The DAB module

gives an analogue output which is buffered through a ground balancing circuit

(IC301 NJM2114 op amp) – this section is also used for the Sirius analogue

output. DAB /RESET comes from IC101 (74HC595).

AM/FM uses the ALPS module. Different modules are fitted depending on

region – Europe (with RDS), US (no RDS), Japan (different FM range).

Control is direct from the PW338, FM CE, SPI Data, SPI Clk. Also, /RDS On

from IC101 (74HC595) is used to turn off the RDS chip in EU modules when

the AM band is used (the RDS chip running on AM interferes with AM

performance). RDS Int & Data come from the Alps module to the PW338 for

Page 11

EU FM transmissions carrying RDS data. VSM goes to an ADC on the

PW338 and provides a signal strength indication. The AM/FM module gives

an analogue output which is buffered through a ground balancing circuit

(IC302 NJM2114 op amp).

IR from the front panel comes onto this board from L126 and goes through a

re-modulator circuit (IC200 LMC555) as it has been demodulated on the front

panel. This signal, Z1 remod, goes through SKT200 such that inserting a plug

into SKT200 will stop this signal (to prevent conflicting signals if a Zone 1

external IR sensor is used) from going to LED200 and then being

demodulated by RX200.

Zone 2 (SKT102) & Zone 3 (SKT103) IR inputs drive LED201 & LED202

which are demodulated by RX201 & RX202.

Zone 1, Zone 2 & Zone 3 are also multiplexed together to give IR Out through

TR207 & SKT104.

The ground balancing circuit uses +5V_1 from L123 and generates -5V from

IC303 (SP6661EN charge pump). The AM/FM module uses +9V_FM,

generated with REG202 (LM317) from +15V (from L123). +12V_IR is

generated from +15V (L123) using REG200 (LM7812) and runs the IR output

& 12V triggers. +5V_STBY (L123) generates +3V3_STBY with REG201

(LM1117) – used by IC102 (MAX3232) so the RS232 comms are still

available in standby. +3V3_D is generated from +5V_1 (L123) with REG203

and is used by the DAB module.

Page 12

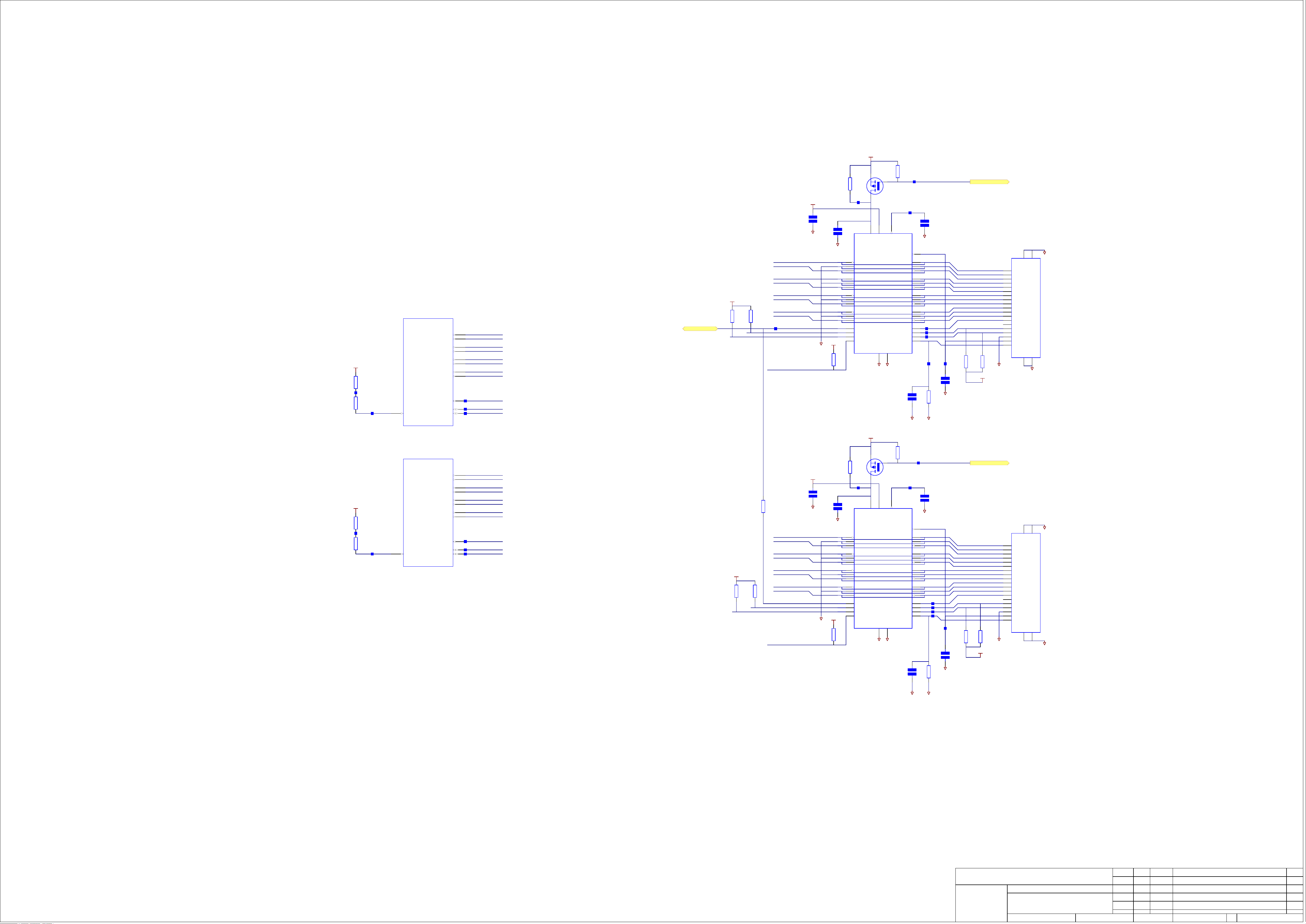

L119AY NETWORK

This PCB handles the network connectivity & USB support. Telnet control

(Ethernet to RS232 tunnelling) is also handled by this PCB.

IC102 (DM850 audio processor) does not have any internal boot code, upon

being powered, it starts the BFL (First level bootloader) from the FLASH

memory IC202 (S29GL064A90TFIR30). This then executes the BSL (second

level bootloader) which brings up the network support. The second level

bootloader then executes the application. The BFL should never need to be

updated and as such will not be included in the standard upgrading

application.

The FLASH memory is also used to store settings, such as the Arcam specific

Cardea keys & MAC address. Note: if the FLASH device is ever changed, it

is essential that the original MAC address be programmed into the unit so that

the user does not lose and internet radio stations/favourites groups.

The device also uses SDRAM (not until the BSL executes) – IC200

(IC42S16800-6T(G)).

Wifi connectivity is via an Edom module and plugs into CON300. Note: this

module is specific to this unit and cannot be substituted, spares must come

from Arcam.

Wired Ethernet uses IC400 (DM9161A MAC), L401 (TS6121C magnetics).

The Ethernet connector (CON400) does not have any link or act LEDs as

these were thought to be potentially annoying in an AV environment.

In addition to the SPDIF audio output, there analogue audio is generated from

NET MClk, NET BClk, NET WClk & NET Data0 using IC501 (CS4345 DAC).

IC500 (LM358AM op amp) buffers & filters the output of the DAC. The output

can then be muted under control of the DM850 (/MUTE) and then ground

balanced with IC502 (NJM2114 op amp).

The DM850 uses two switching regulators for generating the +3V3D

(REG600) and 1V8 (REG601). IC601 (SP6661 charge pump) generates the 5V used by the ground balancing circuit – IC601 has a 4V7 zener regulator

circuit supplying it.

Page 13

L121AY – Connection board

This PCB provides the connections between all the daughter cards, plus the

main PCB (L122).

IC300 & IC301 (74HC244 buffers) take the clock signals (WClk, BClk & MClk)

from L115 & DSP WClk Out & DSPBClk Out from L156 and buffer them to the

ADC, DSP & DAC.

IC303 (74HC4040 divider) divides the MClk down to provide Clk PSU to sync

the switchers on L123.

Page 14

L122AY Main Board

This is the main PCB with the PW338 handling the control of the entire unit,

as well as video processing. HDMI Rx & Tx functions are performed on this

PCB as well as video encoding & decoding.

IC200 is main PW338 micro/video processor. On sheet 4 the microprocessor

interface is shown. The PW338 has no internal boot code, so relies on code

in IC401 (39VF3201 FLASH) to run. IC401 is required to be pre-programmed

with at least boot code. If this part requires replacement, it *must* be

programmed with at least the boot code. If the FLASH is programmed with

the boot code, upon starting up, the PW338 will send out a boot loader

message on the RS232 port0 (sheet 3) at 115.2k baud, 8bits, no parity. If

there is a problem with the DDR memory (IC600 & IC601 sheet 6) there will

be a message sent along with the boot loader message. /AC present (low)

and Poweron_reset (high) from IC402 (LM809M-2.93 – resets the micro if

3V3_PW338 drops below 2.93V) are also required for the PW338 to start.

IC400 (74HC4040 divider) pre-divides the wordclock so the PW338 (EXINT0)

can measure the sampling frequency of incoming digital audio sources. RDS

Int (from L119) is connected to EXINT1 as the RDS data is streamed out of

the ALPS AM/FM module regardless of the readiness of the PW338.

IC403 is a quad UART to provide RS232 communication with the network

(L119), the Sirius satellite radio (L118) & iPod (L118). All signal labels are

with respect to the PW338.

Sheet 7 shows most of the connections to the daughter PCBs as well as the

I2C control busses:

EDID – used for the EDID dual port EEPROM (IC909, sheet 9)

AN – Analogue control bus, L116 Analogue input & L117 Analogue output

HDMI_Config – SiI9135 & SiI9134 x 2 & ADV7310 (sheet 5)

DAB – DAB module (L118) & system EEPROM (IC706 sheet 7)

3 x 74HC595 (IC701, IC703 & IC704) provide additional control output

signals.

The remaining control signals are on sheet 2. This sheet also shows the

interface between the SiI9135 HDMI receiver (IC201) and the PW338. The

audio outpus of IC201 go through L121 (Connection PCB) to L115 (Digital

IO).

Sheet 3 shows the analogue video inputs. There are separate inputs for

composite, S-video & component. The Y signal also is taken to a Sync input

on the PW338.

Sheet 5 is the video output port. The digital video port of the PW338 is

connected to the ADV7310 (IC501), SiI9134 (IC502) & SiI9134 (IC503). The

ADV7310 converts the digital video to analogue video outputs for component,

S-video & composite (depending on the resolution – up to 1080i for

component, 480i/576i only for composite & s-video). The two SiI9134 parts

convert the video data to HDMI serial data. While it is possible to have all

Page 15

video outputs active, resolution & copy protection limits apply. Also, when

displaying 408i/576i the colour space requirements of the ADV7310 &

SiI9134s are incompatible, so if an HDMI display is connected the analogue

outputs are muted.

The PW338 can only output one clock pulse per pixel, so for 480i & 576i

resolutions, a video clock doubler is required (IC504 ICS2402MLF) to convert

the 13.5MHz pixel clock (Display Clk) to 27MHz (Display Clk2) under the

control of Vid_Clk_Sw.

The output of the ADV73120 is filtered by IC500 (ADA4410). Also, the Svideo signals are recombined to form the composite output signal (Cvid out).

The outputs of this part are series terminated with 75ohms before going to

L133 (component IO) & L114 (video IO) via L121 (connection PCB).

Sheet 9 shows the 5 HDMI inputs.

The serial data differential pairs are multiplexed with IC901 & IC903

(PI3HDMI413). The DDC lines are multiplexed with IC907 & IC910

(DG408LDY) for connection with the dual port EEPROM (IC909) and the

HDMI receiver (IC201).

The CEC line is multiplexed with IC911 (DG408DLY)

The +5V line is multiplexed with IC912 (DG408DLY)

Hotplug out is controlled by IC900, IC904 & IC906 (74HCT08 AND gate)

which give individual hotplug control & also global control with PW338

hotplug.

All these multiplexes must operate together for an HDMI input to be correctly

selected.

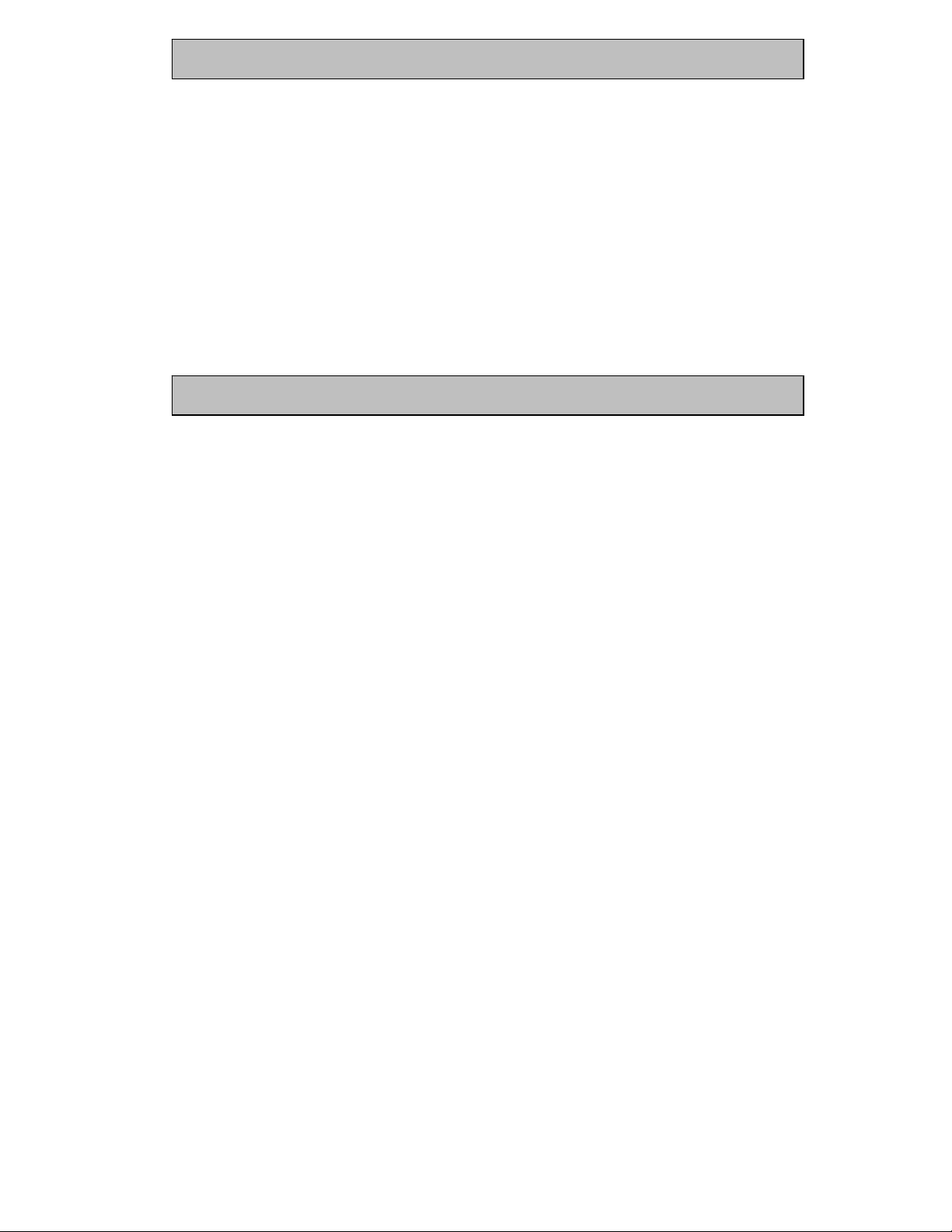

TMDS Mux

Sel3 Sel2 Sel1 Sel0

0 0 0 0 SAT

0 0 0 1 AV

0 0 1 0 DVD

0 1 1 1 PVR

1 0 1 1 VCR

1 1 1 1 Blank

DDC/CEC/+5V Mux

Sel2 Sel1 Sel0

0 0 0 Blank

0 0 1 AV

0 1 0 SAT

1 1 1 DVD

0 1 1 VCR

1 1 1 PVR

Hotplug Mux

SelPVR SelVCR SelDVD SelSAT SelAV

0 0 0 0 0 Blank

0 0 0 0 1 AV

0 0 0 1 0 SAT

Page 16

0 0 1 0 0 DVD

0 1 0 0 0 VCR

1 0 0 0 0 PVR

Sheet 10 shows the ESD protection devices (IC1000 & IC1004 CM2020) for

the two HDMI outputs. There is also provision for turning off the 5V signal to

the display device through FETs M1000 & M1001.

The two 120 way connectors on sheet 11 show all the connections between

the L122 PCB and L122.

Page 17

L124AY – Speaker board

This conducts the output signals from the power amplifiers on both L125 and

L129 to the speaker terminal blocks LS100 – LS103 inclusive, via 4 double

pole relays RLY100 – RLY103. The 24V dc supply from the relays is fed from

L129 via CON101 pin 18, returning to ground via pin 17. The relay switching

transistors are TR100 – TR 103 and the logic level signals to control these

also enter via CON101 pins 19 and 20. Note that the SBL and SBR channels

are switched independently from the other 5 channels, as these can be reassigned in software to support zone 2 in stereo if required.

Zobel networks, comprising 1 uH air cored chokes in parallel with 4R7 2 Watt

resistors, are in series with all outputs to isolate the power amplifiers from

capacitive cable loads which might otherwise provoke instability.

L125AY – Power amp upper

This contains all the power amplifier electronics for the Centre (C), Left

Surround (LS) and Right Surround (RS) channels. It also contains the power

supplies for all 7 channels, which are fed directly from the secondaries of the

power transformer L951TX as raw AC, via CON106, to the bridge rectifiers

DBR201 and DBR202 and two reservoir capacitor banks, C206/7 plus

C210/213 for Vcc/Vee, and C214/5 plus C220/1 for +Vlo and –Vlo.

The power amplifier design is Class G, which is why two sets of power rails

are employed; Vcc and Vee are approximately +/- 59V off load and +Vlo and

– Vlo are approximately +/- 30V off load.

The rectified and smoothed power rails are fed to the lower power amp PCB

L129, along with an AC power feed for checking the mains is present, via

CON100.

CON103 is used to bring in the C, LS and RS line level input signals from the

rest of the AVR via L129. It also imports +/-12V supplies for the front stage

op-amps and +5V for the top heatsink temperature sensor IC400. Outputs

comprise this sensor’s signal and two DC offset protection lines (ERR_POS

and ERR_NEG), which are returned to the system microprocessor via L129.

CON105 carries the C, LS and RS outputs to the Speaker PCB L124. It also

carries the speaker ground returns for all 7 channels back to the star ground

point on L125.

All 7 power amplifiers are identical, except for the Centre channel where only

one half of its set of the various dual driver ICs is used.

Each power amplifier is topologically split into two halves – the input stage IC,

LM4702 high voltage driver IC and DC servo IC comprise the driver stage

(e.g. U_driver_C); the power transistors plus their drivers and protection

circuitry comprise the output stage (e.g. U_PA_C), as shown in the L125

block diagram.

Page 18

Additionally the 3 power amplifier channels in L125 share a common pair of

power MOSFET lifters (the part of the block diagram shown as U_Lifter_C)

which control the amount of output voltage fed to the collectors of the power

transistors in the 3 power amplifiers.

The Centre channel Driver Stage

converter IC700B (one half of an NJM2114) which rejects common mode

noise on the input when grounded to AGND_FF via the handbag link

CON700. Its output feeds one half of the stereo high voltage driver IC

(LM4702C - IC701) via the low pass network R706 and C704. The LM4702 is

used in a non-inverting configuration and provides all the voltage gain of the

system, set by R713 and R704. Pins 11 and 12 of IC701 feed the inputs of the

negative and positive halves of the Output Stage. The dominant pole

compensation is set by C705, C713/R714 provides some second order

feedback in the audio band to provide a higher open loop gain at high audio

frequencies and thus reduce hf distortion. R715 and R716 (without TR700

which is a “no fit”) provide some extra voltage to IC701’s negative supply at

high negative output voltages via a bootstrap arrangement in the output stage

to prevent premature clipping of the negative half of the output. Note that the

heatsink of IC701 is connected to its negative rail – this must NOT be

accidentally shorted to ground!

Good power supplying decoupling of IC701 is essential and is provided by

C701, C708, C709, C712 and C714.

Note that the amplifier is DC coupled throughout. IC702B (one half of a

TL072) has a very high input impedance and forms a ground referenced

inverting integrator with R712 and C711; their time constant is approximately

1.5 seconds. Its output is fed back to the positive input IC701 via the

attenuator R711 and R706 to keep the DC output of the amplifier close to

zero. It can also correct moderate DC offsets appearing at the input of

IC700B. Should these become excessive, or should a circuit fault cause

significant DC at the loudspeaker output, then the error voltage at the output

of IC702B will feed through to the system microprocessor via D700 (which

works in conjunction with the similar diodes in the other power amplifier

channels as a wired OR gate) to generate a system shut down signal.

starts with the balanced to unbalanced

NB. R702 will also mute the power amplifier electronically in the absence of

the +/- 12V supply.

The Centre channel Output Stage

classic emitter follower configuration, with enhancements to ensure near class

A operation at power levels of up to about 10 watts. Both the positive and

negative halves are essentially identical.

The pre-driver and driver transistors are connected to the high voltage rails

Vcc and Vee (approx +/-59V). However because this is a Class G design the

output transistors TR406A and TR409A normally run at half these voltages

(+Vlift and –Vlift, approx +/- 30V) connecting to the +Vlo and –Vlo supplies via

Shottky power diodes D100 and D101 shown on the main block diagram.

When the amplifier is required to deliver more than about +/- 25V peak

comprises complementary triples in a

Page 19

(equivalent to about 30Watts rms into 8 ohms) then the lifters (fed from Vcc

and Vee) are progressively powered on to maintain a constant 5V or so

across the collector-emitter junctions of the output transistors.

Note that on L125 the lifter outputs are shared between all three power

amplifiers for reasons of economy and space – whereas the lifters on the

other 4 channels on L129 are only shared between two power amplifiers

each. Since the worst thermal stress on the lifters occurs at output powers

somewhat above 30W rms equivalent into 8 ohms, we do not recommend

testing the amplifier for extended times with continuous signals in the 30 - 50

Watts range with all three channels (C, SL and SR) running simultaneously

and driving into low impedances. This is especially true of square wave

signals! The thermal sensor IC400 is located close to the lifter MOSFETs in

order to monitor this condition.

The power transistors TR406A and TR409A have built in thermal

compensation diodes (TR406B and TR409B) which form part of the biasing

network. The thermal sense biasing transistors TR401 and TR416 are thus

mounted adjacent to (and ideally in intimate contact with) the driver transistors

TR403 and TR414 so that as they warm up the bias remains relatively stable.

(In practice it rises somewhat, but predictably so, as the drivers warm up).

The pre-drivers, TR400 and TR415, are in a DC feedback loop with TR401

and TR416, so no thermal drift in bias occurs from these. Bias is set by

RV400; D403 and R421 ensure that no catastrophic increase in bias will take

place if RV400 fails open circuit.

Optimum bias at quiescent operating temperature is measured across the two

0.1 ohm emitter resistors forming R408 – it is typically 15mV at the pins of

C400. When setting up from cold a good starting point to achieve this is to first

turn RV400 to minimum (i.e. fully anticlockwise) and then slowly turn it up to

6mV.

The transistors TR405A and B and their associated networks provide

comprehensive two slope safe operating area (SOA) protection for the output

devices. When the prescribed combination of voltage and current across

TR406A or TR409A is exceeded, the relevant protection transistor conducts

and shorts out the base drive to the associated pre-driver, thus limiting the

dissipation in the output device. The output of each channel of the LM4702 is

current limited to about 5-10mA so no damage can occur to it under these

conditions. Note that if an output device fails short circuit then the 7 Amp fuse

in its collector will fail – the driver transistors TR403 and TR414 will then try to

take over and so are protected by 1 ohm fusible resistors in their collectors.

Note that the heatsinks of the drivers TR403 and TR414 are “live” – an

accidental short to ground here with a test probe will probably blow the

associated 1 ohm fusible resistor.

Diodes D402 and D405 protect the output transistors from being reverse

biased in the presence of inductive load “spikes”. Diodes D401A/B form part

of a wired OR gate system with the other power amplifier channels on L124

and are used to drive the lifters connected to the collectors of TR406A and

TR409A. R439 and C411 are part of a bootstrap network for the negative rail

of IC701 and its associated pre-driver transistor TR415. R417 and C406 are

Page 20

a Zobel network (sometimes called a Boucherot cell) to help compensate for

inductive loads at high frequencies.

The Class G Lifters

TR602 plus p-channel power MOSFET M601 for the positive half, and TR603,

TR604 and TR605 plus n-channel power MOSFET M603 for the negative half.

They are arranged as CFPs (complementary feedback pairs) rather than plain

emitter (source) followers so that the MOSFETs can be fully turned on without

needing power supplies that exceed Vcc and Vee.

The two halves operate identically – we will examine the positive (top half)

lifter to see how it works. With only small signals coming from the power

amplifier, node PLD_C remains biased at about +20V (via the network R614,

D600, R602., R603, R605) whilst node +VLIFT_C is held at approximately

+30V (i.e. +Vlo less the 0.2V or so dropped across the Shottky power diode

D100). The emitter of TR602 meanwhile is at about +24.5V, so TR602 is

turned hard off. Thus the base of TR600 is connected via R600 to Vcc and the

emitter is at Vcc – 0.6V. Vgs of M601 is thus -0.6V which is well under the

approx -2.5V required to turn on M601.

When the voltage at node PLD_C exceeds approximately +25V this is enough

to turn on TR602. When about 3V is developed across R600 this is enough to

turn on M601 which conducts until the voltage at the emitter of TR602 has

risen enough to stabilise the system. The output voltage then can rapidly track

the input (plus about 5V) as required, reverse biasing the Shottky power diode

D100 and drawing the collector current for TR406A via M600 and the +Vcc

supply. The complementary emitter follower TR600, TR601 ensured the gate

capacitance of the MOSFET can be both charged and discharged very

quickly. C605 provides fast local decoupling to minimise switching transients.

are in two complimentary halves – TR600, TR601 and

Page 21

L129AY – Power Amp lower

This contains the power amplifier electronics for the Left (L), Right (R),

Surround Back Left (SBL) and Surround Back Right (SBR) channels. It also

contains housekeeping logic for the amplifier protection system and power

drive circuits for the protection relays and cooling fans.

The power amplifiers are essentially identical to those in L125, except that the

lifter circuits are only shared between pairs of power amplifiers (L and SBL, R

and SBR respectively) rather than all three channels in L125. They receive

their raw DC power voltages from L125 via CON100. Please refer to the

description of the Centre Channel (C) power amplifier (in L125) for a detailed

understanding of the circuitry of the power amplifiers in L129.

CON102 carries the L, R, SBL and SBR output signals to the speaker board

L124. It also delivers +24V DC power and logic level switching signals to the 4

speaker relays on L124. NB - the ground returns shown on CON102 do not

carry L129’s main speaker currents back to the star point (which is located on

L125) but are merely used for the L, R, SBL and SBR amplifiers’ optional

extra Boucherot networks located on L124.

Note that it is L129 which communicates with the rest of the receiver, via two

ribbon cables connected to CON101 and CON 103. CON 101 receives 7 line

level input signals, and low voltage supplies (+12V, -12V and +5V) from L117.

CON101 also inputs the speaker relay mute signals for L124. CON103

supports temperature and DC offset monitoring for L125 and L129, plus a fan

drive signal, sent to and from the system microprocessor on L122, via L121.

The heatsink temperature monitors on L129 are IC800 and IC900; these are

located between the relevant pairs of lifter power MOSFETs.

TR102 provides nominal +24V power to the output relays on L124, via the

unregulated +30V supply on L125. The 27V zener diode DZ102 prevents

excessive voltage being applied to the relays in the event of high mains

voltages.

REG 101 is not normally used as links CON109 and CON110 are omitted in

production. It provides +5V for the on board logic and temperature sensors if

no +5V line is present (e.g. during development testing).

TR1003A/B and TR1001 together make a fan driver with a DC gain of 10, so it

can be triggered with a 3V3 microprocessor signal. Power comes from the

unregulated +Vlo supply (approx +30V). The fans are two 12V DC units

connected in series fed from CON107 and CON108.

IC1000 is a triple 3-input NAND gate. To switch on (i.e. unmute) the speaker

relays, all 3 inputs on IC1000B (for LSB and RSB channels) and/or IC1000C

(for the other 5 channels) must be high. The 3 inputs come from:

(a) the AC present detector based around TR1002 and IC1000A,

(b) the ERR_NEG and ERR_POS detector, based around TR1004A/B, which

detects excessive DC offsets on any one or more of the 7 power amplifier

channels and (c) the ~MUTE_SB and ~MUTE_REST lines under the control

of the system microprocessor.

Page 22

L126AY – Front Panel

This PCB handles the VFD, keyboard scan, IR reception for the front panel &

power LEDs.

The micro is an Atmel AT91SAM7S32 (IC101) which must be initially

programmed via the Atmel/Segger debugger via CON101. Subsequently, the

micro can be reprogrammed from the PW338 using the Arcam upgrader utility

over RS232. The bootloader should never need to be updated and as such

will not be included in the standard upgrading application.

Communication with the PW338 is via RS232 – IC101 sends information on

keypresses to the PW338 & receives information to display & brightness

commands from the PW338 – FP_TX & FP_RX. Note these signals are

labelled with respect to the PW338.

IC101 uses +3V3_PW338 so is powered in standby. It has an internal 1V8

regulator which generates VDD_OUT (1V8, pin 8) which is decoupled &

powers the core & PLL of IC101 (pins 18, 41 & 48).

The VFD (DISP100) is driven from serial data SIN from IC101

(AT91SAM7S32 micro). The serial data is gated through IC102 (74HC08

quad NAND gate, parts C & D unused) controlled by SIN1_CTL & SIN2_CTL

from IC101 to provide dimming of the display. The output data from IC102 is

clocked into the display with the signal CLK from IC101 and is latched into the

display during the blanking period (LAT & BLK).

The VFD filament drive is synchronous with the display update. Signals

FClock1 & FClock2 are 180deg out of phase and drive IC100 (AD8532 op

amp) to give a 6V oscillating drive to the two ends of the filament (from +6V_1

– L123). The HT is provided direct from L123 (+40V_VFD). +6V_1 &

+40V_VFD are not present in standby.

IR decoding (RX100) is powered by +5V_STBY, allowing IR reception when in

standby. The signal pass through L121 (Connection) to L118 (Trigger) before

going to L122 (Main PCB).

The power LEDs are fitted to a small snap-off PCB that is connected via a 3

wire lead. Green LED when the unit is on, Red when in standby, both during

power on.

Page 23

L127AY Front Input

This PCB handles the auxiliary input & headphone output.

SKT101 carries the headphone output from L117 (Analogue output). There is

also a switch to sense the headphones being inserted. The pullup resistor for

this is on L122, so if L127 PCB is not fitted or the cable not fitted, the unit will

sense the headphones are permanently inserted.

SKT100 is the microphone, auxillary input (to L116 Analogue input) & also

has an optical input for digital sources (Aux SPDIF to L115 Digital input) using

a 3.5mm optical lead.

L156AY – DSP board

This PCB handles the audio decoding of digital inputs & processing of

digitised analogue sources.

IC100 (ADSP-21366 DSP) handles the main decoding, including the new HD

formats. Data is either from I2S Data (SPDIF/ADC data from L115) or MCH

Data0, MCH Data1, MCH Data2, MCH Data3 from L122 (Main PCB). In both

cases, the clocks DSP WClk, DSPBClk & DSP MClk are required.

The code for IC100 is held in IC103 (S29AL016D FLASH). The DSP also

requires SRAM (IC101, IC104 71V424S SRAM). The address/data bus is

multiplexed through IC102 & IC106 (74LVC573 buffers) controlled by ALE.

Additional memory decoding is handled by IC105 (74LVC139 2-4 decoder).

R121 & R103 (0R0) should be fitted to allow the DSP to boot in SPI mode.

R117 (4k7) sets the internal clock multiplier to 16:1 (16*20MHz = 320MHz).

IC201 (ADSP-21367 DSP) handles the post-processing & room EQ. Data is

sent in multichannel format regardless of the input between IC100 & IC201

(DSP2 LR, DSP2 LsRs, DSP2 CSw, DSP2 SblSbr). The data is clocked in

using DSP2 BClk & DSP2 WClk, generated by IC100 & DSP MClk from L121.

Data is then clocked out to the DACs (Data LR, Data SlSr, Data CSw, Data

SblSbr) with clocks DSP BClk Out, DSPWClk Out which are buffered on L121

before going to L117 (Analogue Out).

Communication with the PW338 is via a single SPI bus:

DSP Clk - clock

DSP MISO – data from PW338

DSP MOSI – data to the PW338

DSP1 /CS – select DSP1

DSP2 /CS – select DSP2

DSP1 FLAG0 – signal back to PW338

DSP2 FLAG0 – signal back to the PW338

Note: DSP reset is by asserting both /CS lins low simultaneously (IC107

74LV1G32 single Or gate).

Page 24

Power for the DSPs comes from two regulators 3V3 (REG300), further

regulated to 1V2 (REG301). Both are heatsinked.

Page 25

SAT IN

VCR IN

AV INDVD IN

PVR IN

Pr

Pb

Y

Pr

Pb

Y

Pr

Pb

OUT

Y

SKT100

D

EF

JYE TAI

GOLD

SKT102

D

EF

JYE TAI

GOLD

SKT103

JYE TAI

GOLD

50V

X7R

50V

D3c

ABC

RG B

A2b

X7R

A/D1a

E3c

B2b

50V

X7R

B/E1a

F3c

C2b

50V

C/F1a

VGND

R100

R101

R102

75R

75R

75R

75R

75R

75R

0W063

0W063

0W063

0W063

0W063

0W063

R103

R104

R105

50V

X7R C112

D3c

ABC

RG B

A2b

X7R

50V

X7R

10N

50V

X7R

50V

X7R

A/D1a

E3c

B2b

50V

X7R

B/E1a

F3c

C2b

50V

X7R C128

50V

X7R C131

50V

X7R C133

D

C/F1a

0W063

R121

VGND

D3c

ABC

RG B

A2b

R122

Pr Out

R123

75R

75R

75R

75R

75R

75R

0W063

0W063

0W063

0W063

0W063

0W063

R124

R125

R126

50V

X7R C135

10N

A/D1a

E3c

EF

B2b

Pb Out

50V

X7R C139

10N

B/E1a

C136

2U2

C142

2U2

10N

10N

10N

50V

YK

50V

YK

F3c

C2b

Y Out

50V

X7R C143

10N

C/F1a

R141

R142

R143

C144

2U2

50V

YK

VGND

75R

75R

VGND

75R

0W063

0W063

0W063

C100

10N

C101

2U2

C102

10N

C104

2U2

C105

10N

C106

2U2

C107

10N

C109

2U2

C110

10N

C111

2U2

C113

2U2

50V

YK

C117

10N

C118

2U2

C120

10N

C122

2U2

C124

10N

C126

2U2

C130

2U2

C132

2U2

C134

2U2

50V

YK

R109

VGND

50V

YK

50V

YK

50V

YK

50V

YK

50V

YK

R112

VGND

50V

YK

50V

YK

50V

YK

50V

YK

50V

YK

R130

VGND

R110

47K

47K

47K

0W063

0W063

0W063

R113

R131

R111

/EN2

SEL2

R114

47K

47K

47K

47K

47K

47K

0W063

0W063

0W063

0W063

0W063

0W063

R132

47K

47K

47K

47K

47K

47K

0W063

0W063

0W063

0W063

0W063

0W063

VGND

R115

R133

1

2

3

6

7

8

9

10

4

5

R116

R134

R117

R135

RED1

GREEN1

BLUE1

RED2

GREEN2

BLUE2

ENABLE*

SELECT

GND

GND

+5V_1

C152

100UF

10V

YXF

VGND

+5V_1

16

V+

C154

100UF

10V

YXF

-5V

VOUT_RED

VOUT_GREEN

VOUT_BLUE

V-

V-

11

12

-5V

/EN0

SEL0

/EN1

SEL1

100N

IC104

LT1675CGN

P117

15

P119

14

P120

13

1

2

3

6

7

8

9

10

4

5

RED1

GREEN1

BLUE1

RED2

GREEN2

BLUE2

ENABLE*

SELECT

GND

GND

VGND

+5V_1

VGND

-5V

1

2

3

6

7

8

9

10

C153

100N

16V

X7R

VGND

C155

16V

X7R

R138

R139

R140

68R 0W063

68R 0W063

68R

DRAWING TITLE

4

5

0W063

RED1

GREEN1

BLUE1

RED2

GREEN2

BLUE2

ENABLE*

SELECT

GND

GND

EN0 SEL0 EN1 SEL1 EN2 SEL2

0 0 1 x 1 x SAT

0 1 1 x 1 x

1 x 0 0 1 x VCR

1 x 0 1 1 x DVD

1 x

1 x 1 x 1 x BLANK

1 x 0 1 PVR

Component IO - Mux

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

VGND

+5V_1

16

V+

VOUT_RED

VOUT_GREEN

VOUT_BLUE

V-

V-

11

12

-5V

C148

100UF

10V

YXF

C150

100UF

10V

YXF

C149

100N

16V

X7R

C151

100N

16V

X7R

+5V_1

16

V+

VOUT_RED

VOUT_GREEN

VOUT_BLUE

V-

V-

11

12

-5V

Filename:

Notes:

Contact Engineer:

+5V_1

-5V

IC100

LT1675CGN

P116

15

P105

14

P106

13

IC101

LT1675CGN

P108

15

P109

14

P110

13

AV

Blank AVR600 Component IO PCBL113PBPCB100 1

C140

100UF

10V

YXF

C146

100UF

10V

YXF

0W063

0W063

0W063

0W063

0W063

0W063

R106

R107

R108

68R

68R

68R

R127

R128

R129

68R

68R

68R

C145

100N

16V

X7R

C147

100N

16V

X7R

VGND

C138

1uF

25V

X7R

L113 C1 Component IO_D0.SchDoc

Contact Tel: (01223) 203270 tel NoNick Clarke

+15V

Z3 L

+15V

Z3 R

Pr in

Y in

Pb in

C114

Y Out

VGND

Pb Out

VGND

Pr Out

VGND

/EN0

SEL0

/EN1

SEL1

/EN2

SEL2

REG100 LM337MP

D105

S1D

1A

470UF

C115

10P

50V

NPO

C119

470UF

C121

10P

50V

NPO

C125

470UF

C127

10P

50V

NPO

0W063

R136

360R

0W063

ADJ

ECO 982

C116

100N

16V

X7R

C123

100N

16V

X7R

C129

100N

16V

X7R

P139

P140

P142

P143

P144

P146

P147

ECO No.

D100

BAV99W

D101

BAV99W

+5V_1

25V

YK

+5V_1

25V

YK

+5V_1

25V

YK

15

1

2

3

4

5

6

7

9

0W063

R137

120R

0W063

PK

INITIALS

Printed:

-15V

AGND

-15V

AGND

BAV99W

D102

IC102A

Q0

DS

Q1

SHCP

Q2

Q3

STCP

Q4

Q5

Q6

MR

OE

Q7

Q7'/DO

74HCT595D

C137

470UF

10V

CK

-5V-15V

136mA (1.36W)

24/9/0707_E165

25/10/06

DATE

03/07/2008

C103

100P

50V

NPO

C108

100P

50V

NPO

BAV99W

D103

NF - Fit for AudioControl

BAV99W

D104

NF - Fit for AudioControl

14

11

12

10

13

DGND

75R output R removed,Y Pb Pr corrected

DESCRIPTION OF CHANGE

GOLD

SKT101

3c

2b

JYE TAI

1a

AGND

-5V

CON102

1

2

HARWIN

M20-973

VGND

-5V

CON103

1

2

HARWIN

M20-973

NF - Fit for AudioControl

VGND

-5V

CON104

1

2

HARWIN

M20-973

VGND

SPI Data

SPI Clk

Vcomp latch

+5V_1

FIX100

4

1

FIX101

1

11Sheet of

SPI Clk

SPI Data

Vcomp latch

Y ADV7312

Pb ADV7312

Pr ADV7312

Y in

Pb in

Pr in

Z3 L

Z3 R

1

23

74HCT595D

A3

FID100 FID101

TOOL100 TOOL101

TOOL102 TOOL103

+5V_1

+15V

-15V

10

11

12

13

14

15

16

17

18

19

20

VGND

DGND

10

11

12

13

14

15

16

17

18

19

20

AGNDVGND

R144

0R0

0W063

R145

P148

0R0

0W063

DGND

IC102B

VCC

GND

+5V_1

16

8

DGND

DRAWING NO.

CON100

1

2

3

4

5

6

7

8

9

MOLEX

CON101

1

2

3

4

5

6

7

8

9

MOLEX

C141

100N

16V

X7R

D.0PCB change onlyPK 15/05/0808_E122

C.0Layout change onlyPK 18/01/0808_E011

B.0

A.0.2INITIAL RELEASENC

ISSUE

L113CT

Page 26

JYE TAI

SKT102

JYE TAI

RJ

SKT106

RJ

SKT101

3

1

5

2

4

T

S

SKT104

JYE TAI

3

1

5

RJ

3

1

5

2

4

T

S

3

1

5

2

4

T

S

VGND

0W063

75R

R103

R108

75R

0W063

VGND

0W063

75R

R110

R112

75R

0W063

VGND

0W063

75R

R119

R120

75R

0W063

VGND

C123

10P

50V

NPO

C129

10P

50V

NPO

C132

10P

50V

NPO

C135

10P

50V

NPO

VGND

VGND

VGND

VGND

VGND

VGND

R100

75R

0W063

R109

75R

0W063

R118

75R

0W063

P122

P123

R127

75R

0W063

P131

P132

P100

VGND

P106

P107

C124

10P

50V

NPO

VGND

P111

P114

C130

10P

50V

NPO

P117

VGND

C133

10P

50V

NPO

P130

VGND

VGND

P109

VGND

VGND

AV Y

AV C

AV Cvid

C125

10P

50V

NPO

SAT Y

SAT C

SAT CVid

C131

10P

50V

NPO

DVD Y

DVD C

DVD Cvid

C134

10P

50V

NPO

VCR Y

VCR C

VCR Cvid

Video Mux

L114_C2_Video Mux_D0.SchDoc

AV Y

VCR Cvid out

AV C

AV Cvid

VCR S-vid Cout

VCR S-vid Yout

SAT Y

SAT C

SAT Cvid

PVR Cvid out

PVR S-vid Cout

PVR S-vid Yout

DVD Y

C vid in

S-vid C in

DVD C

S-vid Y in

DVD Cvid

VCR Y

VCR C

VCR Cvid

BAV99W

D100

+5V_1

P103

P104

P105

BAV99W

D103

+5V_1

P113

P115

P116

C vid in

S-vid C in

S-vid Y in

BAV99W

D101

+5V_1

VGND

VCR Cvid out

VCR S-vid Cout

VCR S-vid Yout

BAV99W

D104

+5V_1

VGND

PVR Cvid out

PVR S-vid Cout

PVR S-vid Yout

+5V_1

VGND

+5V_1

VGND

BAV99W

D102

BAV99W

D105

10V

VGND

C101

C104

10V

VGND

C108

C112

470UF

10V

CK

C102 470UF

470UF

10V

CK

470UF

10V

CK

C110

470UF

10V

CK

10V

CK

470UF

10V

CK

+5V_1

C vid out

S-vid C out

S-vid Y out

VGND

BAV99W

D106

C103

10P

50V

NPO

VGND

C107

10P

50V

NPO

VGND

C105

10P

50V

NPO

C109

10P

50V

NPO

+5V_1

C100

10P

50V

NPO

C106

10P

50V

NPO

BAV99W

D107

VGND

VGND

SKT100

S

T

4

2

5

1

3

JYE TAI

RJ

SKT103

S

T

4

2

5

1

3

JYE TAI

RJ

VGND

+5V_1

BAV99W

D108

10V

C115

VGND

C116

C118

AGND

AGND

+5V_1

470UF

10V

CK

470UF

10V

CK

Z2 R

Z2 L

+15V

C vid out

S-vid C out

S-vid Y out

C vid in

S-vid Y in

S-vid C in

Vid IO Mux Latch

SPI Data

SPI Clk

Z3 L

Z3 R

Zone SPI Clk

Zone SPI data

Z2 /Mute

Z3 /Mute

470UF

10V

CK

-15V

VGND

DGND

CON100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

MOLEX

CON101

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

MOLEX

SKT105

S

T

4

2

5

1

JYE TAI

RJ

JYE TAI

RJ

2

4

T

S

SKT108

3

1

5

2

4

T

S

VGND

TOOL100 TOOL101

TOOL102 TOOL103

0W063

75R

R128

R129

75R

0W063

VGND

75R

0W063

R137

R138

75R

0W063

VGND

VGND

C138

10P

50V

NPO

VGND

VGND

FID100

FID101

R130

75R

0W063

P139

P140

FID102

FID103

C136

10P

50V

NPO

VGND

P133

VGND

C139

10P

50V

NPO

VGND

C137

10P

50V

NPO

PVR Y

PVR C

PVR Cvid

C140

10P

50V

NPO

Z2 /Mute

Z3 /Mute

Z3 L

Z3 R

Z2 L

Z2 R

Zone SPI data

Zone SPI Clk

PVR Y

Z2 C vid Out

PVR C

PVR Cvid

Z2 S-vid C Out

Z2 S-vid Y Out

Vid IO Mux Latch

SPI Data

SPI Clk

Z2 Vol Mute

Z3 Vol Mute

Zone 2 Volume & PSU

L114_C3_zone_vol_PSU_D0.SchDoc

Z2 /Mute

Z3 /Mute

Z2 Vol Mute

Z3 Vol Mute

Z3 L

Z3 R

Z2 L

Z2 R

Zone SPI data

Zone SPI Clk

Z2 C vid Out

Z2 S-vid C Out

Z2 S-vid Y Out

Vid IO Mux Latch

SPI Data

SPI Clk

+5V_1

P135

P137

P138

BAV99W

D109

BAV99W

D110

+5V_1

VGND

DRAWING TITLE

Video IO - Connectors

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

BAV99W

D111

+5V_1

VGND

Filename:

Notes:

Contact Engineer:

VGND

Blank AVR600 Video IO PCBL114PBPCB100 1

L114_C1_Video IO_D0.SchDoc

10V

C128

C127

C126

470UF

10V

CK

Contact Tel: (01223) 203270 tel NoNick Clarke

470UF

10V

CK

470UF

10V

CK

C119

10P

50V

NPO

VGND

C122

10P

50V

NPO

07_E159

ECO No.

C117

10P

50V

NPO

INITIALS

Printed:

RJ

VGND

25/10/06

DATE

03/07/2008

SKT107

S

T

4

2

5

1

3

JYE TAI

VGND

RJ

DESCRIPTION OF CHANGE

13Sheet of

C113

10P

50V

NPO

C114

10P

50V

NPO

FIX101

1

FIX100

4

1

A3

C111

10P

50V

NPO

VGND

P141

1

23

DRAWING NO.

R111

0R0

0W063

3

JYE TAI

RJ

R113

0R0

0W063

DGND

DGND

D.0PK None to this sheet13/05/0808_E123

C.0PK PCB change only18/12/0708_E012

B.0NC Sync control added, C/S-vid mutes removed11/06/07

A.0.2INITIAL RELEASENC

ISSUE

L114CT

Page 27

AV Cvid

SAT Cvid

DVD Cvid

PVR Cvid

VCR Cvid

AV Y

SAT Y

DVD Y

PVR Y

VCR Y

AV C

SAT C

DVD C

PVR C

VCR C

AV Cvid

SAT Cvid

DVD Cvid

PVR Cvid

VCR Cvid

AV Y

SAT Y

DVD Y

PVR Y

VCR Y

AV C

SAT C

DVD C

PVR C

VCR C

C211

C214

C225

C227

C229

C231

C233

C235

C236

C238

C240

C242

C244

C246

C248

C250

C213

C219

C226

C228

C230

C232

C234

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

C237

C239

C241

C243

C245

C247

C249

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

100N

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

16V

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

P210

P212

P225

P227

P228

P231

P233

P244

P246

P251

P254

P262

P271

P206

P207

P208

P209

P213

P215

P218

P234

VGND

P240

P241

P243

P248

P256

P263

P269

P270

P272

P220

P258

40

42

44

1

3

18

20

22

24

26

8

10

12

14

16

6

15

C205

470UF

10V

CK

40

42

44

18

20

22

24

26

10

12

14

16

15

C212

470UF

10V

CK

CVBS IN1

CVBS IN2

CVBS IN3

CVBS IN4

CVBS IN5

Y IN1

Y IN2

Y IN3

Y IN4

Y IN5

C IN1,Cr IN

C IN2

CIN 3

CIN 4

CIN 5

Cb IN

REG

CVBS IN1

CVBS IN2

1

3

CVBS IN3

CVBS IN4

CVBS IN5

Y IN1

Y IN2

Y IN3

Y IN4

8

Y IN5

C IN1,Cr IN

C IN2

CIN 3

CIN 4

6

CIN 5

Cb IN

REG

+5V_1

41

30

VCC1

GND1

37

27

VGND

+5V_1

41

VCC1

GND1

35

11

VCC2

VCC3

GND2

GND3

32

13

30

35

VCC2

VCC3

GND2

GND3

CVBS OUT,Cb OUT

VCC4

Y OUT

COUT,Cr OUT

VSYNC OUT

VDET OUT

VDET FILT

CSYNC OUT

VDET IN

LPF CTL

V DET CTL

GAIN CTL

YOUT SEL

COMPONENT

INSEL1

INSEL2

INSEL3

STANDBY

TEST MODE CTL

GND4

NC

+5V_1

C221

100UF

25V

YK

11

VGND

CVBS OUT,Cb OUT

VCC4

Y OUT

COUT,Cr OUT

VSYNC OUT

VDET OUT

VDET FILT

CSYNC OUT

VDET IN

LPF CTL

V DET CTL

GAIN CTL

YOUT SEL

COMPONENT

INSEL1

INSEL2

INSEL3

STANDBY

TEST MODE CTL

GND4

NC

IC200

LA73031V

38

29

31

P253

36

43

P298

39

34

33

10K

28

2

7

9

4

17

19

21

23

10K

0W063

0W063

R206

P274

R252

P321

INSEL1

INSEL2

INSEL3

V MUX STBY

25

5

VGND

C218

100N

16V

IC203

LA73031V

38

29

31

P277

36

43

P307

39

34

33

10K

10K

28

2

P288

7

9

P322

4

Z2INSEL1

17

Z2INSEL2

19

Z2INSEL3

21

V MUX STBY

23

25

5

VGND

+5V_1

10K

R200

R250 10K

P214 P216

+5V_1

C200

1uF

25V

X7R

VGND

SYNC CTL

C223

100N

16V

C224

100N

16V

+5V_1

R207 10K

R251

0W063

0W063

+5V_1

R213

R253

10K

P278

VGND

Z2SYNC CTL

0W063

P255

C208

1uF

25V

X7R

P219

C201

220P

50V

NPO

P257

R205

10K

0W063

P226

VGND

C251

100N

16V

C209

220P

50V

NPO

VGND

R204

10K

0W063

C202

470P

50V

NPO

0W063

R211

10K

0W063

R212

10K

0W063

P264

C210

470P

50V

NPO

+5V_1

+5V_1

R249

R248

R247

75R

75R

75R

0W063

0W063

0W063

P200

P201

P202

VCR Mute

+5V_1

VGND

PVR Mute

+5V_1

S-vid C in

S-vid Y in

C vid in

R220

1K0

0W063

C206

47UF

35V

YK

R233

1K0

0W063

2

3

4

P238

C207

22N

50V

X7R

2

3

4

P268

IN1

IN2

IN3

+5V_1

IN1

IN2

IN3

+5V_1

S-vid C in

S-vid Y in

C vid in

+5V_1

5

VCC

GND

1

VGND

VGND

TR206

BC849B

SOT-23

+5V_1

5

VCC

GND

1

VGND

VGND

TR213

BC849B

SOT-23

IC201

BA7623F

OUT1

OUT2

OUT3

R216

220R

0W063

R219

220R

0W063

IC202

BA7623F

OUT1

OUT2

OUT3

R229

220R

0W063

R232

220R

0W063

8

7

6

P221

P239

8

7

6

P247

P273

R209

P237

R225

0W063

P267

39R

0W063

P232

VGND

39R

P261

VGND

R210

36R

0W063

P224

TR205

BC849B

SOT-23

R226

36R

0W063

P252

TR212

BC849B

SOT-23

P211

P217

TR202

BC849B

SOT-23

P242

P245

TR209

BC849B

SOT-23

+5V_1

VGND

R214

220R

0W063

R217

220R

0W063

R227

220R

0W063

R230

220R

0W063

C203

47UF

35V

YK

39R 0W063

R203

0W063

P230

P235

C204

22N

50V

X7R

36R 0W063

R208

0W063

P222

TR203

BC849B

SOT-23

VCR S-vid Yout

VCR S-vid Cout

TR200

BC849B

SOT-23

VGND

39R 0W063

R223

0W063

P265

36R 0W063

R224

0W063

TR207

BC849B

SOT-23

TR210

BC849B

SOT-23

PVR S-vid Yout

PVR

VGND

39R

R201

R215

220R

0W063

R218

220R

0W063

39R

R221

S-vid Cout

R228

220R

0W063

R231

220R

0W063

P236

P266

36R

R202

P223

P229

36R

R222

P250P249

P260P259

VCR Cvid out

VCR S-vid Yout

VCR S-vid Cout

VCR Cvid out

TR201

BC849B

SOT-23

TR204

BC849B

SOT-23

VGND

PVR Cvid out

PVR S-vid Yout

PVR S-vid Cout

PVR Cvid out

TR208

BC849B

SOT-23

TR211

BC849B

SOT-23

VGND

Z2 Vol Mute

Z3 Vol Mute

Pin4 low = Svid/CVBS (high=component)

Pin7 (low = 0dB gain), high = 6dB gain

Pin9 low = Svid, high = CVBS

Pin23 low = on, high = standby

Pin28 (low = LPF off), high = LPF on

IC205A

INSEL1

INSEL2

INSEL3

Z2INSEL1

Z2INSEL2

Z2INSEL3

SYNC CTL

Z2SYNC CTL

V MUX STBY

VCR Mute

PVR Mute

Z2 Vid Mute

Z2 Vol Mute

Z3 Vol Mute

P275

P276

P279

P281

P282

P284

P285

P287

P296

P299

P308

P309

P312

P315

15

1

2

3

4

5

6

7

9

P291

15

1

2

3

4

5

6

7

9

Q0

Q1

SHCP

Q2

Q3

STCP

Q4

Q5

Q6

Q7

Q7'/DO

74HCT595D

IC208A

Q0

Q1

SHCP

Q2

Q3

STCP

Q4

Q5

Q6

Q7

Q7'/DO

74HCT595D

DS

MR

OE

DS

MR

OE

14

11

12

10

13

DGND

14

11

12

10

13

DGND

VGND

SPI Data

SPI Clk

Vid IO Mux Latch

+5V_1

+5V_1

37

27

32

13

VGND

SPI Data

SPI Clk

Vid IO Mux Latch

+5V_1

C222

100UF

25V

YK

VGND

VCC

GND

IC208B

74HCT595D

+5V_1

16

8

DGND

C220

100N

16V

X7R

C252

100N

16V

C253

100N

16V

+5V_1

VCC

GND

IC205B

74HCT595D

16

8

DGND

C254

100N

16V

C217

100N

16V

X7R

C255

100N

16V

Video IO - Video Mux

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

C215

47UF

35V

YK

VGND

P203

P204

P205

Z2 Vid Mute

Filename:

Notes:

Contact Engineer:

C216

22N

50V

X7R

2

3

4

IN1

IN2

IN3

+5V_1

R246

1K0

0W063

L114_C2_Video Mux_D0.SchDoc

P314

+5V_1

5

VCC

GND

1

VGND

TR220

BC849B

SOT-23

IC204

BA7623F

OUT1

OUT2

OUT3

Contact Tel: (01223) 203270 tel NoNick Clarke

8

7

6

R242

220R

0W063

R245

220R

0W063

P316

P286

P280

39R 0W063

R238

P313

0W063

P297

36R 0W063

R239

0W063

P292

TR219

BC849B

SOT-23

P283

TR216

BC849B

SOT-23

R240

220R

0W063

R243

220R

0W063

39R 0W063

R236

P310

VGND

11/06/0707_E159

25/10/06

ECO No. DESCRIPTION OF CHANGE

INITIALS

Printed:

DATE

03/07/2008

P294

VGND

39R

R234

36R 0W063

R237

P290

TR217

BC849B

SOT-23

23Sheet of

Z2 S-vid Y Out

Z2 S-vid C Out

TR214

BC849B

SOT-23

R241

220R

0W063

R244

220R

0W063

A3

P311

DRAWING NO.

36R

R235

P289

P295

VGND

Z2 C vid out

Z2 S-vid Y Out

Z2 S-vid C Out

Z2 C vid out

TR215

BC849B

SOT-23

TR218

BC849B

SOT-23

D.0PK None to this sheet13/05/0808_E123

C.0PK PCB change only18/12/0708_E012

B.0NC Sync control added

A.0.2INITIAL RELEASENC

ISSUE

L114CT

Page 28

+7VA

C300

47UF

35V

YK

C305

100N

100V

X7R

R300

C318

BAV99W

D301

+7VA

-7VA

Z2 L

Z2 R

Zone SPI Clk

Zone SPI data

Z2 Vol Mute

Z2 L

Z2 R

D2, D1 = 1

Zone SPI Clk

Zone SPI Data

Z2 Vol Mute

C303

10UF

SM

+7VA

50V

C304

10UF

50V

SM

P302

1

3

P317

12

8

9

10

IN1

IN2

SEL

CL

DA

MUTE

DGND

11

7

VCC

AGND1

AGND2

2

4

6

AGND

OUT1

OUT2

AGND3

5

VEE

IC300

BD3812F-E2

14

13

C307

47UF

35V

YK

P300

P301

C319

100N

100V

X7R

47R

0W125

R301

47R

0W125

AGND

100UF

25V

YK

C301

100UF

25V

YK

AGND

AGND

RLY300B

NEC

+7VA

RLY300A

NEC

BAV99W

D300

AGND

-7VA

AGND

C306

100P

50V

NPO

C302

100P

50V

NPO

GOLD

3c

2b

SKT300

JYE TAI

1a

AGND

Z2 L

Z2 R

Zone SPI Clk

Zone SPI Data

D2, D1 = 0

C310

10UF

SM

-7VA

50V

C311

10UF

50V

SM

P318

1

3

P320

12

8

9

10

DGND -7VA

AGND

+7VA

C308

47UF

35V

YK

7

AGND

IN1

IN2

VCC

OUT1

OUT2

SEL

CL

DA

MUTE

C320

100N

100V

X7R

IC301

BD3812F-E2

14

13

P319

P303

R302

47R

0W125

R303

47R

0W125

C309

100UF

25V

YK