12-Bit, 41 MSPS

AIN

ENCODE

V

REF

DV

CC

AV

CC

AD9042

ADC

V

OFFSET

6

DAC

TH2

A1

TH1

+2.4V

REFERENCE

INTERNAL

TIMING

D11D10D9D8 D7 D6 D5 D4 D3 D2D1D0

MSB LSB

TH3 A2

ADC

DIGITAL ERROR CORRECTION LOGIC

7

ENCODE

GND

3

4

5

6

7

1

2

10

11

8

9

40 39 3841424344 36 35 3437

29

30

31

32

33

27

28

25

26

23

24

121314 15 16 17 18 192021 22

PIN 1

TOP VIEW

(Not to Scale)

AV

CC

AV

CC

AV

CC

AV

CC

AV

CC

D8

D7

D6

D5

D4

D3

D2

AD9042

DV

CC

DV

CC

ENCODE

ENCODE

GND

GND

AIN

NC = NO CONNECT

V

OFFSET

V

REF

C1

AV

CC

D1

D0 (LSB)

GND

NC

D11 (MSB)

GND

GND

GND

GND

D10

GND

GND

GND

GND

GND

D9

DV

CC

DV

CC

DV

CC

DV

CC

GND

a

FEATURES

41 MSPS Minimum Sample Rate

80 dB Spurious-Free Dynamic Range

595 mW Power Dissipation

Single +5 V Supply

On-Chip T/H and Reference

Twos Complement Output Format

CMOS-Compatible Output Levels

APPLICATIONS

Cellular/PCS Base Stations

GPS Anti-Jamming Receivers

Communications Receivers

Spectrum Analyzers

Electro-Optics

Medical Imaging

ATE

PRODUCT DESCRIPTION

The AD9042 is a high speed, high performance, low power,

monolithic 12-bit analog-to-digital converter. All necessary

functions, including track-and-hold (T/H) and reference are

included on chip to provide a complete conversion solution.

The AD9042 runs off of a single +5 V supply and provides

CMOS-compatible digital outputs at 41 MSPS.

Designed specifically to address the needs of wideband,

multichannel receivers, the AD9042 maintains 80 dB

spurious-free dynamic range (SFDR) over a bandwidth of

20 MHz. Noise performance is also exceptional; typical

signal-to-noise ratio is 68 dB.

The AD9042 is built on Analog Devices’ high speed complementary bipolar process (XFCB) and uses an innovative multipass

architecture. Units are packaged in a 28-pin DIP; this custom

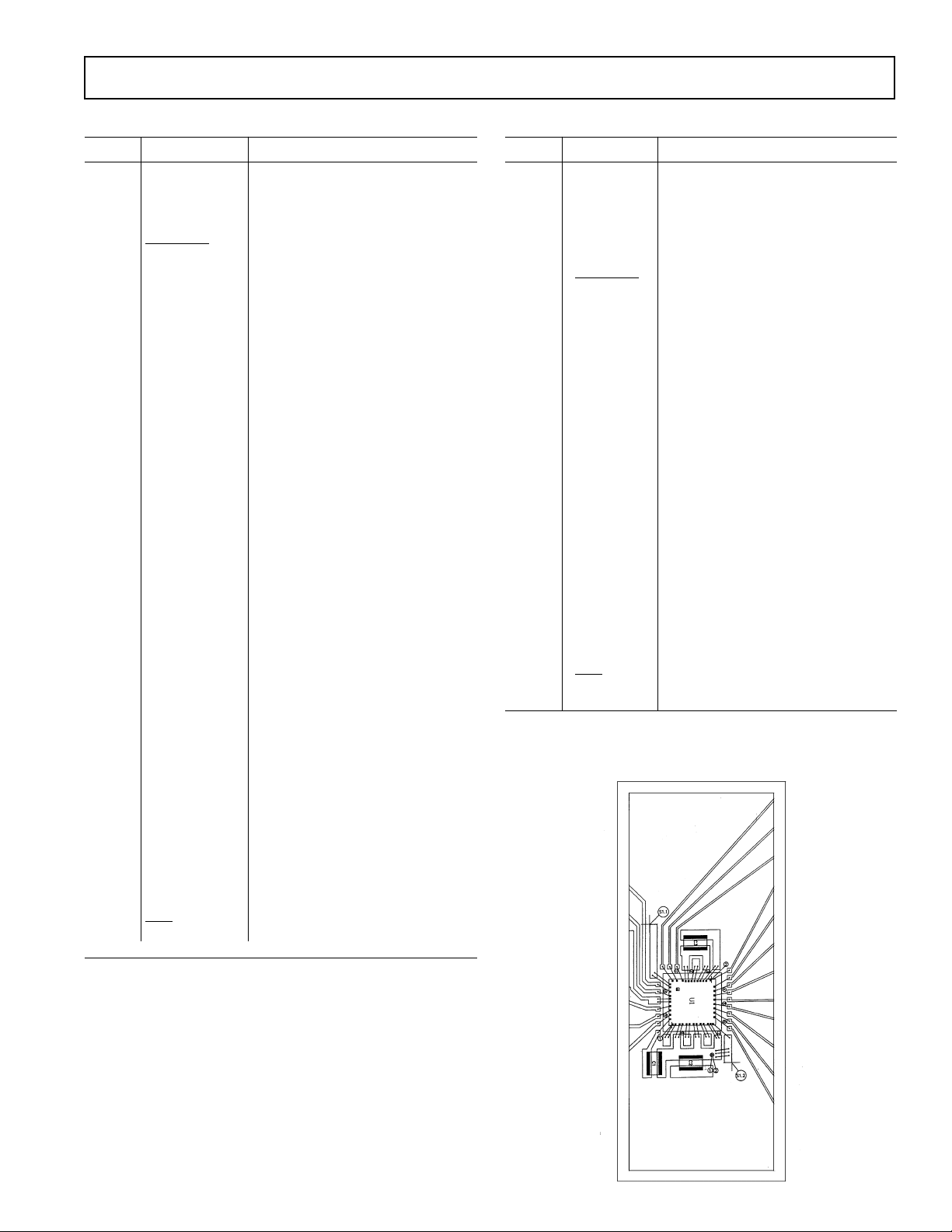

AD9042AD PIN DESIGNATIONS

Monolithic A/D Converter

AD9042

FUNCTIONAL BLOCK DIAGRAM

cofired ceramic package forms a multilayer substrate to which

internal bypass capacitors and the 9042 die are attached and a

44-pin TQFP low profile surface mount package. The AD9042

industrial grade is specified from –40°C to +85°C. However,

the AD9042 was designed to perform over the full military

temperature range (–55°C to +125°C); consult factory for

military grade product options.

PRODUCT HIGHLIGHTS

1. Guaranteed sample rate is 41 MSPS.

2. Dynamic performance specified over entire Nyquist band;

spurious signals typ. 80 dBc for –1 dBFS input signals.

3. Low power dissipation: 595 mW off a single +5V supply.

4. Reference and track-and-hold included on chip.

5. Packaged in 28-pin ceramic DIP and 44-pin TQFP.

AD9042AST PIN DESIGNATIONS

1

GND

2

DV

CC

GND

3

ENCODE

4

5

ENCODE

GND

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

GND

V

OFFSET

V

GND

AV

GND

AV

AD9042

6

TOP VIEW

(Not to Scale)

7

8

AIN

9

10

REF

11

12

CC

13

14

CC

NC = NO CONNECT

28

D11 (MSB)

D10

27

26

D9

D8

25

D7

24

23

D6

D5

22

D4

21

20

D3

19

D2

18

D1

17

D0 (LSB)

16

NC

15

NC

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD9042–SPECIFICA TIONS

DC SPECIFICATIONS

(AVCC = DVCC = +5 V; V

tied to V

REF

through 50 Ω; T

OFFSET

= –408C, T

MIN

= +858C)

MAX

Test AD9042AST Test AD9042AD

Parameter Temp Level Min Typ Max Level Min Typ Max Units

RESOLUTION 12 12 Bits

DC ACCURACY

No Missing Codes Full VI Guaranteed VI Guaranteed

Offset Error Full VI –10 ±3 +10 VI –10 ± 3 +10 mV

Offset Tempco Full V 25 V 25 ppm/°C

Gain Error Full VI –6.5 0 +6.5 VI –6.5 0 +6.5 % FS

Gain Tempco Full V –50 V –50 ppm/°C

REFERENCE OUT (V

REF

2

)

+25°C V 2.4 V 2.4 V

ANALOG INPUT (AIN)

Input Voltage Range V

±0.500 V

REF

Input Resistance Full IV 200 250 300 IV 200 250 300 Ω

Input Capacitance +25°C V 5.5 V 7 pF

ENCODE INPUT

Logic Compatibility

3

4

TTL /CMOS TTL /CMOS

Logic “1” Voltage Full VI 2.0 5.0 VI 2.0 5.0 V

Logic “0” Voltage Full VI 0 0.8 VI 0 0.8 V

Logic “1” Current (V

Logic “0” Current (V

= 5 V) Full VI 450 625 800 VI 450 625 800 µA

INH

= 0 V) Full VI –400 –300 –200 VI –400 –300 –200 µA

INL

Input Capacitance +25°C V 2 V 2.5 pF

1

±0.500 V

REF

DIGITAL OUTPUTS

Logic Compatibility CMOS CMOS

Logic “1” Voltage (IOH = 10 µA) +25°C I 3.5 4.2 I 3.5 4.2 V

Full IV 3.5 IV 3.5 V

Logic “0” Voltage (I

= 10 µA) +25°C I 0.75 0.80 I 0.75 0.80 V

OL

Full IV 0.85 IV 0.85 V

Output Coding Twos Complement Twos Complement

POWER SUPPLY

AV

Supply Voltage Full VI 5.0 VI 5.0 V

CC

I (AV

DV

I (DV

I

) Current Full V 109 V 109 mA

CC

Supply Voltage Full VI 5.0 VI 5.0 V

CC

) Current Full V 10 V 10 mA

CC

(Total) Supply Current Full VI 119 147 VI 119 147 mA

CC

Power Dissipation Full VI 595 735 VI 595 735 mW

Power Supply Rejection +25°C I –20 ±1 +20 I –20 ±1 +20 mV/V

(PSRR) Full V ±5V ±5 mV/V

NOTES

1

C1 (Pin 10 on AD9042AST only) tied to GND through 0.01 µF capacitor.

2

V

is normally tied to V

REF

3

ENCODE driven by single-ended source; ENCODE bypassed to ground through 0.01 µF capacitor.

4

ENCODE may also be driven differentially in conjunction with ENCODE; see “Encoding the AD9042” for details.

Specifications subject to change without notice.

through 50 Ω. If V

OFFSET

is used to provide dc offset to other circuits, it should first be buffered.

REF

(AVCC = DVCC = +5 V; ENCODE & ENCODE = 41 MSPS;

SWITCHING SPECIFICATIONS

V

REF

tied to V

through 50 Ω; T

OFFSET

= –408C, T

MIN

= +858C)

MAX

1

Test AD9042AST Test AD9042AD

Parameter (Conditions) Temp Level Min Typ Max Level Min Typ Max Units

Maximum Conversion Rate Full VI 41 VI 41 MSPS

Minimum Conversion Rate Full IV 5 IV 5 MSPS

Aperture Delay (t

) +25°C V –250 V –250 ps

A

Aperture Uncertainty (Jitter) +25°C V 0.7 V 0.7 ps rms

ENCODE Pulse Width High +25°CIV10 IV10 ns

ENCODE Pulse Width Low +25°CIV10 IV10 ns

Output Delay (tOD) Full IV 5 9 14 IV 5 9 14 ns

NOTE

1

C1 (Pin 10 on AD9042AST only) tied to GND through 0.01 µF capacitor.

–2–

REV. A

(AVCC = DVCC = +5 V; ENCODE & ENCODE = 41 MSPS;

AC SPECIFICATIONS

1

V

REF

tied to V

through 50 Ω; T

OFFSET

= –408C, T

MIN

= +858C)

MAX

2

AD9042

Test AD9042AST Test AD9042AD

Parameter (Conditions) Temp Level Min Typ Max Level Min Typ Max Units

3

SNR

Analog Input 1.2 MHz +25°CV 68 I 65 68 dB

@ –1 dBFS Full V 67.5 V 67.5 dB

9.6 MHz +25°C V 67.5 I 64.5 67.5 dB

Full V 67 V 67 dB

19.5 MHz +25°C I 64 67 I 64 67 dB

Full V 66.5 V 66.5 dB

SINAD

4

Analog Input 1.2 MHz +25°C V 67.5 I 64 67.5 dB

@ –1 dBFS Full V 67 V 67 dB

9.6 MHz +25°C V 67.5 I 64 67.5 dB

Full V 67 V 67 dB

19.5 MHz +25°C I 64 67 I 64 67 dB

Full V 66.5 V 66.5 dB

Worst Spur

5

Analog Input 1.2 MHz +25°C V 80 I 74 80 dBc

@ –1 dBFS Full V 78 V 78 dBc

9.6 MHz +25°C V 80 I 74 80 dBc

Full V 78 V 78 dBc

19.5 MHz +25°C I 73 80 I 73 80 dBc

Full V 78 V 78 dBc

Small Signal SFDR (w/Dither)

6

Analog Input @1.2 MHz Full V 90 V 90 dBFS

9.6 MHz Full V 90 V 90 dBFS

19.5 MHz Full V 90 V 90 dBFS

Two-Tone IMD Rejection

7

F1, F2 @ –7 dBFS Full V 80 V 80 dBc

Two-Tone SFDR (w/Dither)

8

Full V 90 V 90 dBFS

Thermal Noise +25°C V 0.33 V 0.33 LSB rms

Differential Nonlinearity +25°C I –1.0 ± 0.3 +1.0 I –1.0 ± 0.3 +1.0 LSB

(ENCODE = 20 MSPS) Full V ±0.4 VI –1.0 +1.25 LSB

Integral Nonlinearity

(ENCODE = 20 MSPS) Full V ±0.75 V ±0.75 LSB

Analog Input Bandwidth +25°C V 100 V 100 MHz

Transient Response +25°CV 10 V 10 ns

Overvoltage Recovery Time +25°CV 25 V 25 ns

NOTES

1

All ac specifications tested by driving ENCODE and ENCODE differentially; see “ENCODING the AD9042” for details.

2

C1 (Pin 10 on AD9042AST only) tied to GND through 0.01 µF capacitor.

3

Analog input signal power at –1 dBFS; signal-to-noise ratio (SNR) is the ratio of signal level to total noise (first five harmonics removed).

4

Analog input signal power at –1 dBFS; signal-to-noise and distortion (SINAD ) is the ratio of signal level to total noise + harmonics.

5

Analog input signal power at –1 dBFS; worst spur is the ratio of the signal level to worst spur, usually limited by harmonics.

6

Analog input signal power swept from –20 dBFS to –95 dBFS; dither power = –32.5 dBm; dither circuit used on input signal (see “Overcoming Static Nonlinearities

with Dither”); SFDR is ratio of converter full scale to worst spur.

7

Tones at –7 dBFS (F1 = 15.3 MHz, F2 = 19.5 MHz); two tone intermodulation distortion (IMD) rejection is ratio of either tone to worst third order intermod product.

8

Both input tones swept from –20 to –95 dBFS; Dither power = –32.5 dBm; dither circuit used on input signal (see “Overcoming Static Nonlinearities with Dither);

two tone spurious-free dynamic range (SFDR) is the ratio of converter full scale to worst spur.

Specifications subject to change without notice.

REV. A

–3–

AD9042

WARNING!

ESD SENSITIVE DEVICE

WAFER TEST LIMITS

1

(AVCC = DVCC = +5 V; ENCODE = 10.3 MSPS unless otherwise noted)

Parameter Temp Min Max Units

AD9042CHIPS

POWER SUPPLY

ICC Supply Current +25°C 90 147 mA

ENCODE Input

Logic “1” Current +25°C 450 800 µA

Logic “0” Current +25°C –400 –200 µA

DC ACCURACY

Offset Error +25°C–88 mV

Gain Error +25°C –6 6 % FS

No Missing Codes +25°C Guaranteed

Differential Nonlinearity @ 5.3 MSPS +25°C –0.995 LSB

NOTES

1

Electrical test is performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after

packaging is not guaranteed for standard product dice.

2

Die substrate is connected to 0 V.

ABSOLUTE MAXIMUM RATINGS

Parameter Min Max Units

1

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

ELECTRICAL

AV

Voltage 0 7 V

CC

DV

Voltage 0 7 V

CC

Analog Input Voltage 0.5 4.5 V

Analog Input Current 20 mA

Digital Input Voltage (ENCODE) 0 AV

ENCODE,

ENCODE Differential

CC

Voltage 4 V

Digital Output Current –40 40 mA

ENVIRONMENTAL

2

V

II – 100% production tested at +25°C, and sample tested at

specified temperatures. AC testing done on sample

basis.

III – Sample tested only.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C;

sample tested at temperature extremes.

Operating Temperature Range

(Ambient) –40 +85 °C

Maximum Junction Temperature

AD9042AD +175 °C

AD9042AST +150 °C

Lead Temperature (Soldering, 10 sec) +300 °C

Storage Temperature Range (Ambient) –65 +150 °C

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability is not necessarily implied. Exposure to absolute maximum rating

conditions for an extended period of time may affect device reliability.

2

Typical thermal impedances for “D” package (custom ceramic 28-pin DIP):

θJC = 14°C/W; θJA = 34°C/W. For “ST” package (44-pin TQFP) ; θJA = 55°C/W.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9042AST –40°C to +85°C (Ambient) 44-Pin TQFP (Thin Quad Plastic Flatpack) ST-44

AD9042AD –40°C to +85°C (Ambient) 28-Pin 600 Mil Hermetic Ceramic DIP (DH-28) DH-28

AD9042CHIPS –40°C to +85°C (Ambient) Unpackaged Die

AD9042ST/PCB Evaluation Board with AD9042AST

AD9042D/PCB Evaluation Board with AD9042AD

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9042 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. A

AD9042

AD9042AST PIN DESCRIPTIONS

Pin No. Name Function

1, 2 DV

CC

+5 V Power Supply (Digital).

Powers output stage only.

3 ENCODE Encode input. Data conversion

initiated on rising edge.

4

ENCODE Complement of ENCODE. Drive

differentially with ENCODE or

bypass to Ground for single-ended

clock mode.

5, 6 GND Ground.

7 AIN Analog Input.

8V

OFFSET

Voltage Offset Input. Sets mid-

point of analog input range.

Normally tied to V

through

REF

50 Ω resistor.

9V

REF

Internal Voltage Reference.

Nominally +2.4 V; normally tied

to V

through 50 Ω resistor.

OFFSET

Bypass to Ground with 0.1 µF +

0.01 µF microwave chip cap.

10 C1 Internal Bias Point. Bypass to

ground with 0.01 µF cap.

11, 12 AV

CC

+5 V Power Supply (Analog).

13, 14 GND Ground.

15, 16 AV

CC

+5 V Power Supply (Analog).

17, 18 GND Ground.

19, 20 AV

CC

+5 V Power Supply (Analog).

21 GND Ground.

22 GND Ground.

23 NC No Connects.

24 GND Ground.

25 D0 (LSB) Digital Output Bit

(Least Significant Bit)

26–33 D1–D8 Digital Output Bits

34, 35 GND Ground.

36, 37 DV

CC

+5 V Power Supply (Digital).

Powers output stage only.

38, 39 GND Ground.

40, 41 DV

CC

+5 V Power Supply (Digital).

Powers Output Stage only.

42, 43 D9–D10 Digital Output Bits.

44

D11 (MSB)

1

Digital Output Bit

(Most Significant Bit).

NOTE

1

Output coded as twos complement.

AD9042AD PIN DESCRIPTIONS

Pin No. Name Function

1 GND Ground.

2DV

CC

+5 V Power Supply (Digital).

Powers output stage only.

3 GND Ground.

4 ENCODE Encode input. Data conversion

initiated on rising edge.

5

ENCODE Complement of ENCODE. Drive

differentially with ENCODE or

bypass to Ground for single-ended

clock mode.

6, 7 GND Ground.

8 AIN Analog Input.

9V

OFFSET

Voltage Offset Input. Sets mid-

point of analog input range.

Normally tied to V

through

REF

50 Ω resistor.

10 V

REF

Internal Voltage Reference.

Nominally +2.4 V; normally tied

to V

through 50 Ω resistor.

OFFSET

Bypass to Ground with 0.1 µF cap.

11 GND Ground.

12 AV

CC

+5 V Power Supply (Analog).

13 GND Ground.

14 AV

CC

+5 V Power Supply (Analog).

15, 16 NC No Connects.

17 D0 (LSB) Digital Output Bit.

(Least Significant Bit).

18–27 D1–D10 Digital Output Bits.

28

D11 (MSB)1Digital Output Bit

(Most Significant Bit).

NOTE

1

Output coded as twos complement.

AD9042 CUSTOM 28-PIN DIP PACKAGE

REV. A

–5–

AD9042

DIE LAYOUT AND MECHANICAL INFORMATION

Die Dimensions . . . . . . . . . . . . . . . . 155 × 168 × 21 (±1) mils

Pad Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 × 4 mils

Metalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Aluminum

Backing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . None

Substrate Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND

Transistor Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2,605

Passivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Oxynitride

Die Attach . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Silver Filled

Bond Wire . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Gold

DIE LAYOUT W/PAD LABELS

DEFINITION OF SPECIFICATIONS

Analog Bandwidth

The analog input frequency at which the spectral power of the

fundamental frequency (as determined by the FFT analysis) is

reduced by 3 dB.

Aperture Delay

The delay between the 50% point of the rising edge of the

ENCODE command and the instant at which the analog input

is sampled.

Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

Differential Nonlinearity

The deviation of any code from an ideal 1 LSB step.

Encode Pulse Width/Duty Cycle

Pulse width high is the minimum amount of time that the

ENCODE pulse should be left in logic “1” state to achieve

rated performance; pulse width low is the minimum time

ENCODE pulse should be left in low state. At a given clock

rate, these specs define an acceptable Encode duty cycle.

Harmonic Distortion

The ratio of the rms signal amplitude to the rms value of the

worst harmonic component, reported in dBc.

Integral Nonlinearity

The deviation of the transfer function from a reference line

measured in fractions of 1 LSB using a “best straight line”

determined by a least square curve fit.

Minimum Conversion Rate

The encode rate at which the SNR of the lowest analog signal

frequency drops by no more than 3 dB below the guaranteed

limit.

Maximum Conversion Rate

The encode rate at which parametric testing is performed.

Output Propagation Delay

The delay between the 50% point of the rising edge of ENCODE

command and the time when all output data bits are within

valid logic levels.

Overvoltage Recovery Time

The amount of time required for the converter to recover to

0.02% accuracy after an analog input signal 150% of full scale is

reduced to midscale.

Power Supply Rejection Ratio

The ratio of a change in input offset voltage to a change in

power supply voltage.

Signal-to-Noise-and-Distortion (SINAD)

The ratio of the rms signal amplitude (set at 1dB below full

scale) to the rms value of the sum of all other spectral

components, including harmonics but excluding dc.

Signal-to-Noise Ratio (without Harmonics)

The ratio of the rms signal amplitude (set at 1 dB below full

scale) to the rms value of the sum of all other spectral

components, excluding the first five harmonics and dc.

Spurious-Free Dynamic Range

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component. The peak spurious

component may or may not be a harmonic. May be reported in

dBc (i.e., degrades as signal levels is lowered), or in dBFS

(always related back to converter full scale).

Transient Response

The time required for the converter to achieve 0.02%

accuracy when a one-half full-scale step function is applied to

the analog input.

Two-Tone Intermodulation Distortion Rejection

The ratio of the rms value of either input tone to the rms

value of the worst third order intermodulation product;

reported in dBc.

Two-Tone SFDR

The ratio of the rms value of either input tone to the rms value

of the peak spurious component. The peak spurious component

may or may not be an IMD product. May be reported in dBc

(i.e., degrades as signal levels is lowered), or in dBFS (always

related back to converter full scale).

–6–

REV. A

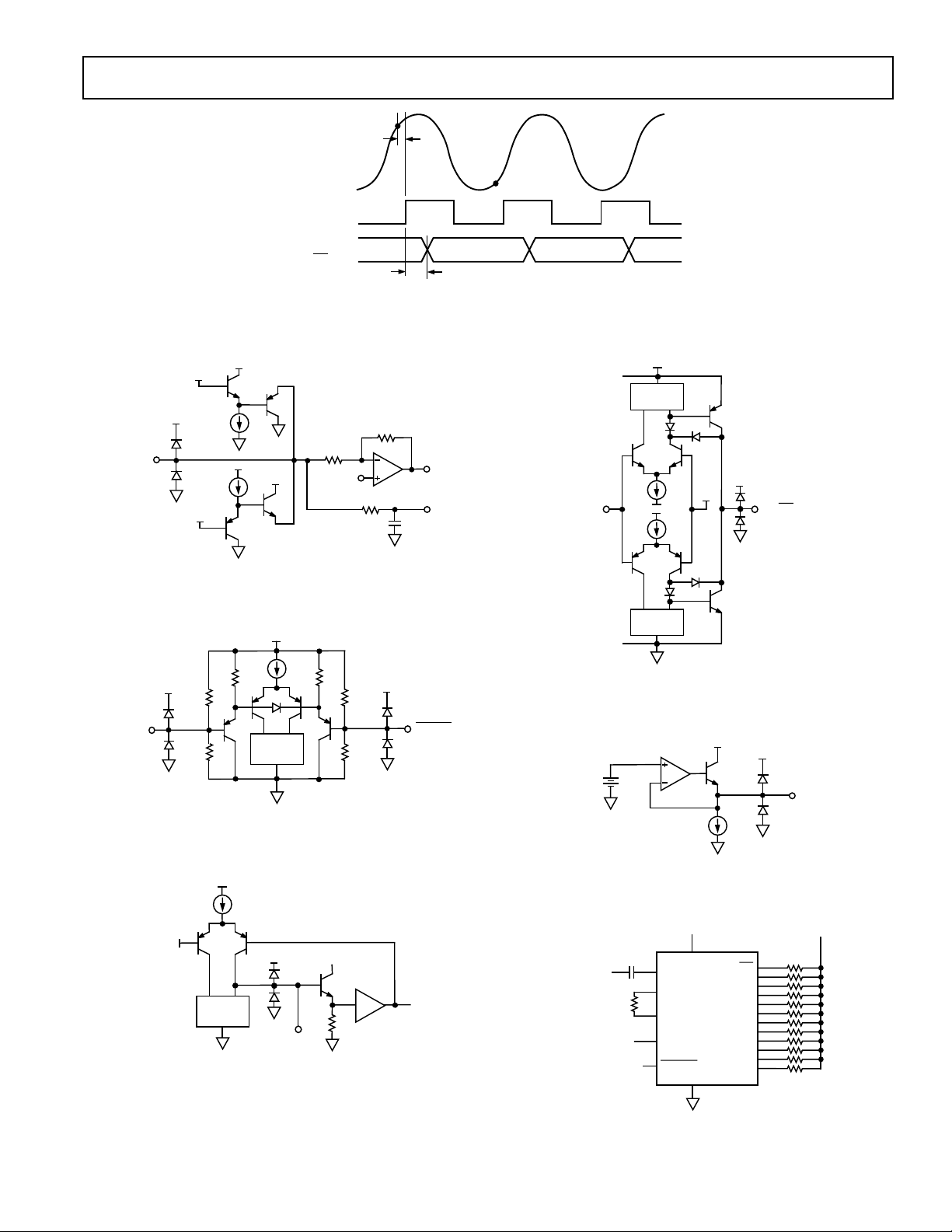

N

DIGITAL

OUTPUTS

(D11–D0)

N – 1N – 2

t

A

= –250 PS TYP

N + 1

t

OD

= 9ns TYP

ANALOG

INPUT

(AIN)

ENCODE

INPUTS

(ENCODE)

N

Figure 1. Timing Diagram

V

REF

AV

CC

0.5mA

2.4V

AV

CC

Equivalent Circuits–AD9042

ENCODE

AIN

AV

250µA

250µA

CC

AV

V

CC

AV

+3.5V

CC

+1.5V

Figure 2. Analog Input Stage

AV

CC

AV

CC

R1

17kΩ

8kΩ

R2

TIMING

CIRCUITS

250Ω

OFFSET

200Ω

R1

17kΩ

R2

8kΩ

250Ω

AV

CC

6pF

ENCODE

DV

CC

CURRENT

MIRROR

DV

CC

REF

D0–D11

CURRENT

MIRROR

V

Figure 5. Digital Output Stage

REV. A

REV. A

Figure 3. Encode Inputs

AV

CC

V

REF

CURRENT

MIRROR

*

AD9042AST ONLY

INTERNAL NODE ON AD9042AD

Figure 4. Compensation Pin, C1

AV

CC

C1

(PIN 10

Figure 6. 2.4 V Reference

+5V

AIN

V

OFFSET

V

REF

ENCODE

ENCODE

2,12,14

28

D11

D0

17

1,3,6,7,11,13

PIN BYPASSED TO GND

REF

AV

CC

SINEWAVE

*

)

–7–

–7–

TTL CLOCK OSC.

NOTE: ALL +5V SUPPLY PINS & V

WITH A 0.1µF CAPACITOR. PINS 15,16 ARE NOT CONNECTED.

Figure 7. AD9042AD Burn-In Diagram

200kHz

49.9Ω

0.1µF

NC

8

9

10

4

5

+5V

10kΩ

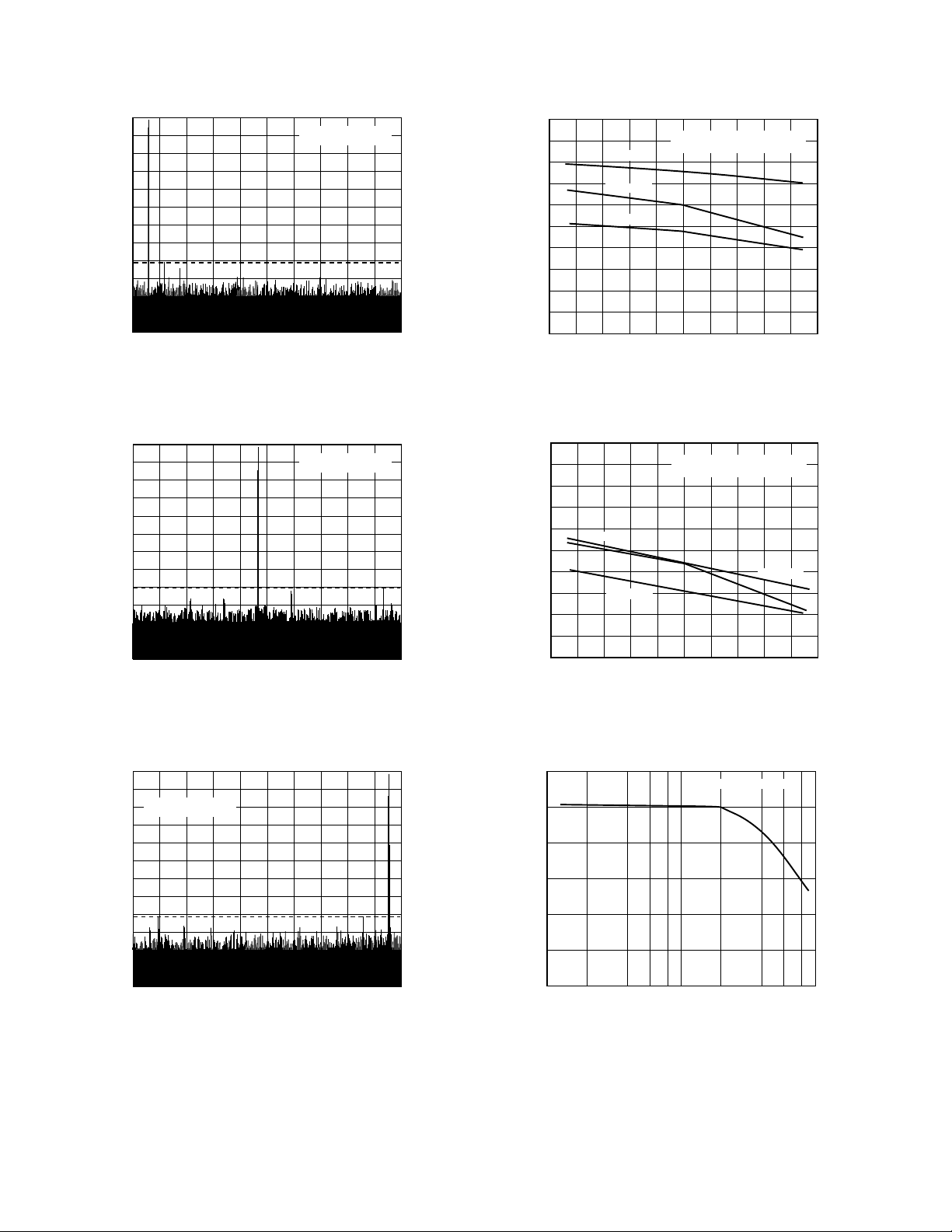

AD9042–Typical Performance Characteristics

ANALOG INPUT FREQUENCY – MHz

0202

WORST CASE HARMONIC – dBc

4 6 8 1012141618

81

79

78

77

80

ENCODE = 41 MSPS

TEMP = –40°C, +25°C, & +85°C

T = +25°C

T = –40°C

T = +85°C

ANALOG INPUT FREQUENCY – MHz

0202

SNR – dB

4 6 8 1012141618

70

68

67

66

69

ENCODE = 41 MSPS

TEMP = –40°C, +25°C, & +85°C

T = +25°C

T = –40°C

T = +85°C

ANALOG INPUT FREQUENCY – MHz

90

80

30

1 10010

WORST HARMONIC – dBc

60

50

40

70

2 4 20 40

ENCODE = 41 MSPS

0

–20

–40

–60

2 3 4 5 6 7 8 9

–80

–100

POWER RELATIVE TO ADC FULL SCALE – dB

–120

dc 20.54.1

8.2 12.3 16.4

FREQUENCY – MHz

Figure 8. Single Tone at 1.2 MHz

0

–20

–40

–60

4

88 5 3 7 6

–80

ENCODE = 41 MSPS

AIN = 1.2MHz

ENCODE = 41 MSPS

AIN = 9.6MHz

Figure 11. Harmonics vs. AIN

2

–100

POWER RELATIVE TO ADC FULL SCALE – dB

–120

dc 20.54.1

8.2 12.3 16.4

FREQUENCY – MHz

Figure 9. Single Tone at 9.6 MHz

0

ENCODE = 41 MSPS

–20

AIN = 19.5MHz

–40

–60

2468 9753

–80

–100

POWER RELATIVE TO ADC FULL SCALE – dB

–120

dc 20.54.1

Figure 10. Single Tone at 19.5 MHz

8.2 12.3 16.4

FREQUENCY – MHz

–8–

Figure 12. Noise vs. AIN

Figure 13. Harmonics vs. AIN

REV. A

Loading...

Loading...