Analog Devices AD73322L a Datasheet

Low Cost, Low Power CMOS

General-Purpose Dual Analog Front End

FEATURES

Two 16-bit A/D converters

Two 16-bit D/A converters

Programmable input/output sample rates

78 dB ADC SNR

78 dB DAC SNR

64 kHz maximum sample rate

−90 dB crosstalk

Low group delay (25 µs typ per ADC channel, 50 µs typ per

DAC channel)

Programmable input/output gain

Flexible serial port allows up to 4 dual codecs to be

connected in cascade, giving 8 I/O channels

Single-supply operation (2.7 V to 3.3 V)

50 mW typ power consumption at 3.0 V

Temperature range: −40°C to +105°C

On-chip reference

28-lead SOIC, TSSOP, and 44-lead LQFP packages

APPLICATIONS

General-purpose analog I/O

Speech processing

Cordless and personal communications

Te le p ho ny

Active control of sound and vibration

Data communications

Wireless local loop

GENERAL DESCRIPTION

The AD73322L is a dual front-end processor for generalpurpose applications, including speech and telephony. It

features two 16-bit A/D conversion channels and two 16-bit

D/A conversion channels. Each channel provides 78 dB signalto-noise ratio over a voice-band signal bandwidth. It also

features an input-to-output gain network in both the analog

and digital domains. This is featured on both codecs and can

be used for impedance matching or scaling when interfacing to

subscriber line interface circuits (SLICs).

The AD73322L is particularly suitable for a variety of applications in the speech and telephony area, including low bit rate,

high quality compression, speech enhancement, recognition,

and synthesis. The low group delay characteristic of the part

makes it suitable for single or multichannel active control

applications.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

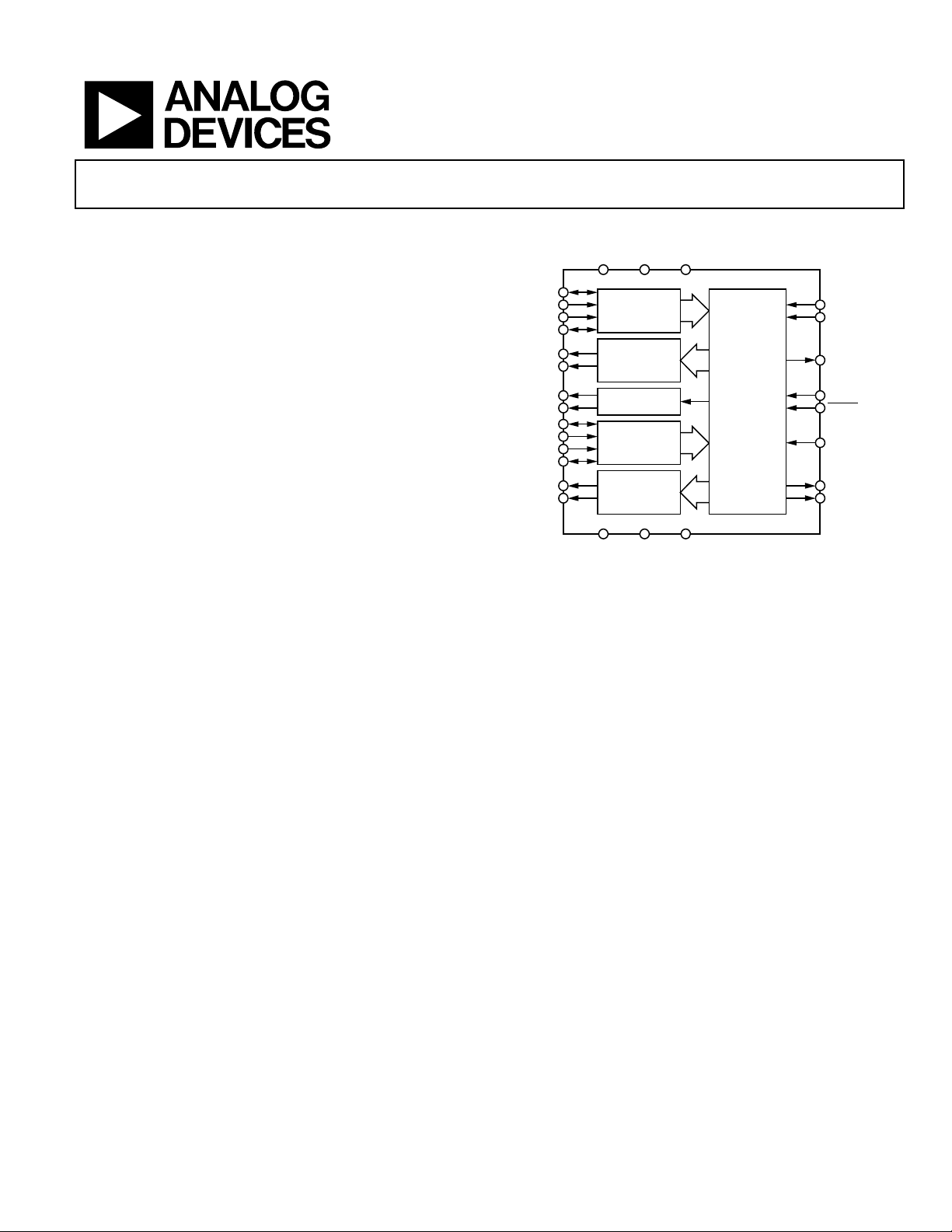

AD73322L

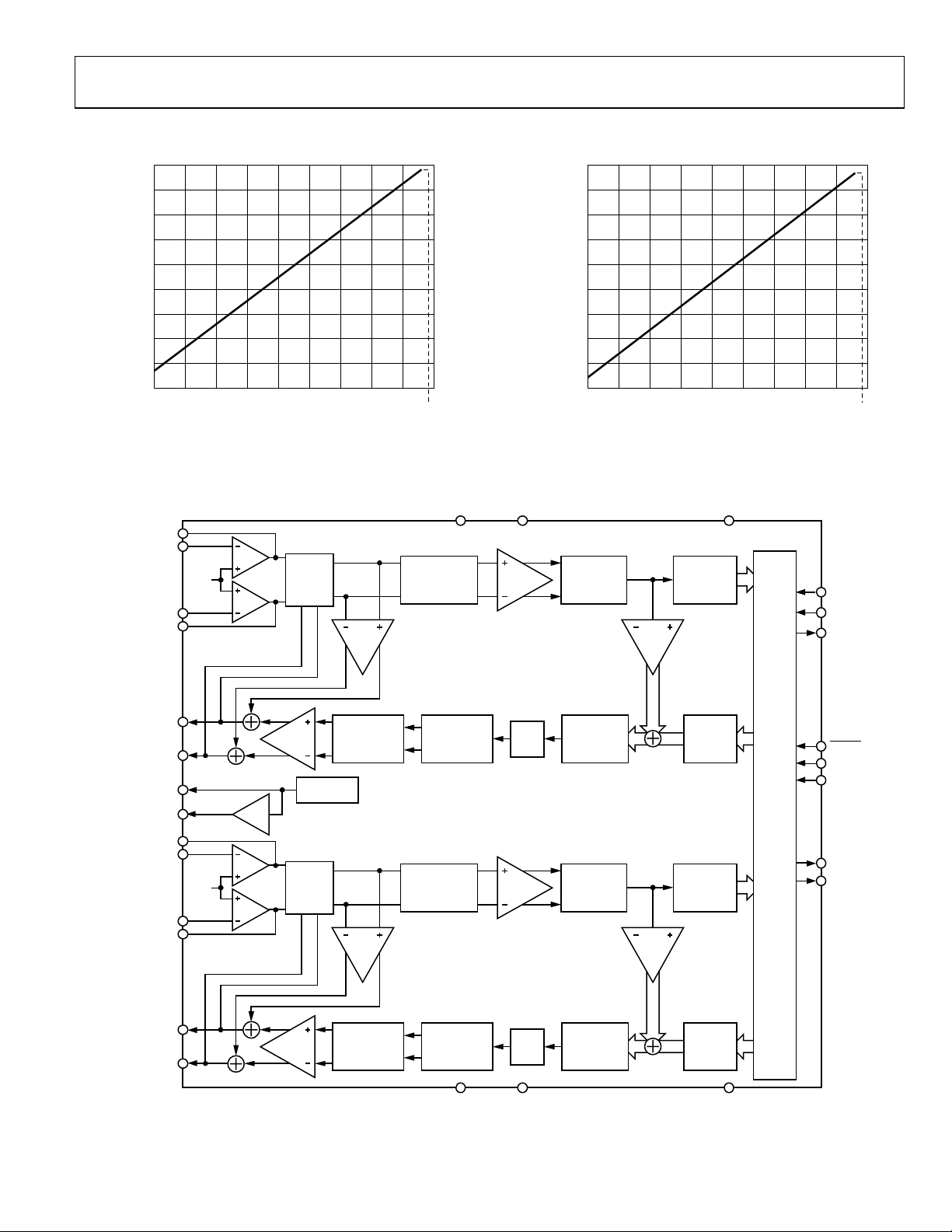

FUNCTIONAL BLOCK DIAGRAM

AVDD1 AVDD2 DVDD

VFBP1

VINP1

VINN1

VFBN1

VOUTP1

VOUTN1

REFOUT

REFCAP

VFBP2

VINP2

VINN2

VFBN2

VOUTP2

VOUTN2

ADC CHANNEL 1

DAC CHANNEL 1

REFERENCE

ADC CHANNEL 2

DAC CHANNEL 2

AGND1 AGND2 DGND

Figure 1.

The A/D and D/A conversion channels feature programmable

input/output gains with ranges of 38 dB and 21 dB, respectively.

An on-chip reference voltage allows single-supply operation.

The sampling rate of the codecs is programmable with four

separate settings offering 64 kHz, 32 kHz, 16 kHz, and 8 kHz

sampling rates (from a master clock of 16.384 MHz).

A serial port (SPORT) allows easy interfacing of single or

cascaded devices to industry-standard DSP engines. The

SPORT transfer rate is programmable to allow interfacing to

both fast and slow DSP engines.

The AD73322L is available in 28-lead SOIC, 28-lead TSSOP,

and 44-lead LQFP packages.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD73322L

SPORT

SDI

SDIFS

SCLK

SE

RESET

MCLK

SDOFS

SDO

00691-001

AD73322L

TABLE OF CONTENTS

Specifications..................................................................................... 4

Sample Rate Divider................................................................... 19

Current Summary......................................................................... 6

Signal Ranges ................................................................................ 7

Timing Characteristics ................................................................ 7

Timing Diagrams.......................................................................... 8

Absolute Maximum Ratings............................................................ 9

ESD Caution.................................................................................. 9

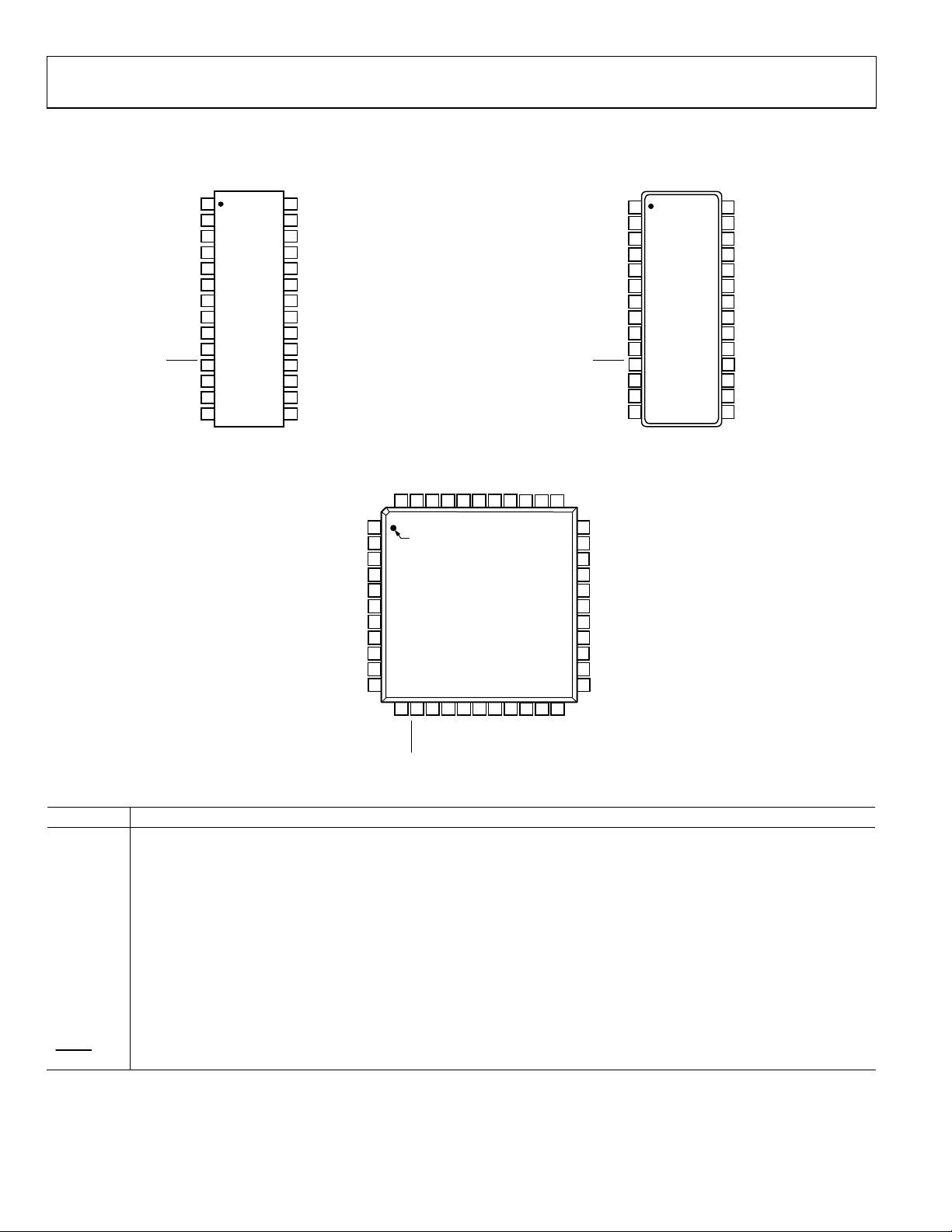

Pin Configurations and Function Descriptions .........................10

Te r mi n ol o g y .................................................................................... 12

Abbreviations .............................................................................. 12

Typical Performance Characteristics and Functional Block

Diagram

Functional Descriptions ................................................................ 14

........................................................................................... 13

Encoder Channels ...................................................................... 14

Programmable Gain Amplifier................................................. 14

ADC ............................................................................................. 14

Analog Sigma-Delta Modulator ............................................... 14

Decimation Filter........................................................................ 15

ADC Coding ............................................................................... 15

Decoder Channel........................................................................ 16

DAC Coding................................................................................ 16

Interpolation Filter ..................................................................... 16

Analog Smoothing Filter and PGA.......................................... 16

Differential Output Amplifiers................................................. 16

Volt a ge R e fere n ce ....................................................................... 16

Analog and Digital Gain Taps................................................... 17

Digital Gain Tap.......................................................................... 18

Serial Port (SPORT)................................................................... 18

SPORT Overview........................................................................ 18

SPORT Register Maps................................................................ 19

Master Clock Divider ................................................................. 19

Serial Clock Rate Divider .......................................................... 19

DAC Advance Register .............................................................. 20

Control Register A ..................................................................... 21

Control Register B...................................................................... 21

Control Register C...................................................................... 21

Control Register D ..................................................................... 22

Control Register E...................................................................... 22

Control Register F...................................................................... 22

Control Register G ..................................................................... 23

Control Register H..................................................................... 23

Operation......................................................................................... 24

Resetting the AD73322L ........................................................... 24

Power Management ................................................................... 24

Operating Modes........................................................................ 24

Program (Control) Mode.......................................................... 24

Data Mode................................................................................... 25

Mixed Program/Data Mode...................................................... 25

Digital Loop-Back Mode ........................................................... 25

SPORT Loop-Back Mode.......................................................... 25

Analog Loop-Back Mode .......................................................... 26

Interfacing ....................................................................................... 27

Cascade Operation..................................................................... 27

Performance .................................................................................... 29

Encoder Section.......................................................................... 29

Encoder Group Delay ................................................................ 30

Decoder Section ......................................................................... 30

On-Chip Filtering....................................................................... 31

Decoder Group Delay................................................................ 31

Design Considerations................................................................... 32

Analog Inputs ............................................................................. 32

Interfacing to an Electret Microphone .................................... 34

Rev. A | Page 2 of 48

AD73322L

Analog Output.............................................................................34

Mixed-Mode Operation.............................................................37

Differential-to-Single-Ended Output.......................................35

Digital Interfacing.......................................................................35

Cascade Operation......................................................................35

Grounding and Layout...............................................................36

DSP Programming Considerations ..............................................37

DSP SPORT Configuration .......................................................37

DSP SPORT Interrupts...............................................................37

DSP Software Considerations When Interfacing to the

AD73322L

Operating Mode ..........................................................................37

....................................................................................37

REVISION HISTORY

12/04—Rev. 0 to Rev. A

Updated Format.................................................................. Universal

Updated Outline Dimensions........................................................46

Changes to Ordering Guide...........................................................47

4/01—Revision 0: Initial Version

Interrupts .....................................................................................37

Initialization.................................................................................38

Running the AD73322L with ADCs or DACs in Power-Down

.......................................................................................................38

DAC Timing Control Example .....................................................40

Configuring an AD73322L to Operate in Data Mode...............41

Configuring an AD73322L to Operate in Mixed Mode ............43

Outline Dimensions........................................................................46

Ordering Guide...........................................................................47

Rev. A | Page 3 of 48

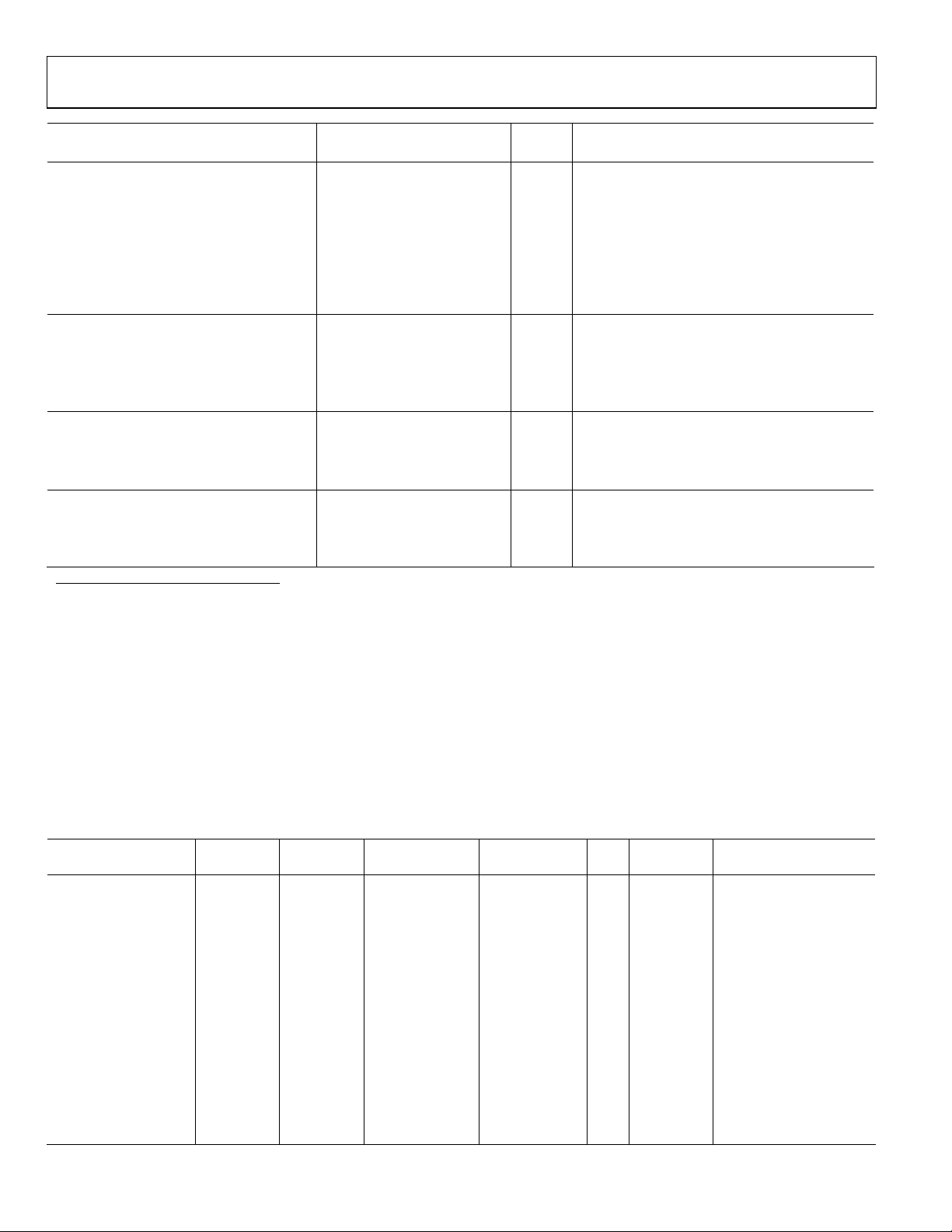

AD73322L

SPECIFICATIONS

AVDD = 3 V ± 10%; DVDD = 3 V ± 10%; DGND = AGND = 0 V, f

unless otherwise noted.

Operating temperature range as follows: A grade, T

= −40°C, T

MIN

Table 1.

A and Y Versions

Parameter Min Typ Max Unit Test Conditions/Comments

REFERENCE

REFCAP

Absolute Voltage, VREFCAP 1.08 1.2 1.32 V

REFCAP TC 50 ppm/°C 0.1 µF capacitor required from REFCAP to AGND2

REFOUT

Typical Output Impedance 130 Ω

Absolute Voltage, V

REFOUT

1.08 1.2 1.32 V Unloaded

Minimum Load Resistance 1 kΩ

Maximum Load Capacitance 100 pF

INPUT AMPLIFIER

Offset ±1.0 mV

Maximum Output Swing 1.578 V Max output swing = (1.578/1.2) × VREFCAP

Feedback Resistance 50 kΩ fC = 32 kHz

Feedback Capacitance 100 pF

ANALOG GAIN TAP

Gain at Maximum Setting +1

Gain at Minimum Setting −1

Gain Resolution 5 Bits Gain step size = 0.0625

Gain Accuracy ±1.0 % Output unloaded

Settling Time 1.0 µs

Delay 0.5 µs

ADC SPECIFICATIONS DAC unloaded

Maximum Input Range at VIN

1, 2

1.578 V p-p Measured differentially

−2.85 dBm Max input = (1.578/1.2) × VREFCAP

Nominal Reference Level at VIN 1.0954 V p-p Measured differentially

(0 dBm0) −6.02 dBm

Absolute Gain

PGA = 0 dB −2.0 −0.7 +0.5 dB 1.0 kHz, 0 dBm0

Gain Tracking Error ±0.1 dB 1.0 kHz, +3 dBm0 to −50 dBm0

Signal-to-Noise and Distortion Refer to Figure 9

PGA = 0 dB 70 78 dB 300 Hz to 3400 Hz; f

79 dB 300 Hz to 3400 Hz; f

77.5 dB 0 Hz to f

Total Harmonic Distortion

PGA = 0 dB −86 −75 dB 300 Hz to 3400 Hz; f

Intermodulation Distortion −61 dB PGA = 0 dB

Idle Channel Noise Crosstalk −72 dBm0 PGA = 0 dB

ADC-to-DAC −107 dB ADC input signal level: 1.0 kHz, 0 dBm0

DAC input at idle

ADC-to-ADC −92 dB ADC1 input signal level: 1.0 kHz, 0 dBm0

ADC2 input at idle; input amplifiers bypassed

−93 dB Input amplifiers included in input channel

DC Offset −20 0 +20 mV PGA = 0 dB

Power Supply Rejection Ratio −65 dB

= 16.384 MHz, f

DMCLK

= +85°C; Y grade, T

MAX

= 8 kHz; TA = T

SAMP

= −40°C, T

MIN

MAX

to T

MIN

= +105°C.

MAX

,

Tap gain change of −FS to +FS

= 8 kHz, PUIA = 0

SAMP

= 8 kHz, PUIA = 1

SAMP

/2; f

SAMP

= 8 kHz

= 8 kHz

SAMP

SAMP

Input signal level at AVDD and DVDD pins:

1.0 kHz, 100 mV p-p sine wave

Rev. A | Page 4 of 48

AD73322L

A and Y Versions

Parameter Min Typ Max Unit Test Conditions/Comments

Group Delay

Input Resistance at PGA

DIGITAL GAIN TAP

Gain at Maximum Setting 1

Gain at Minimum Setting −1

Gain Resolution 16 Bits Tested to 5 MSB of settings

Delay 25 µs Includes DAC delay

Settling Time 100 µs

DAC SPECIFICATIONS DAC unloaded

Maximum Voltage Output Swing

Single-Ended 1.578 V p-p PGA = 6 dB

−2.85 dBm Max output = (1.578/1.2) × VREFCAP

Differential 3.156 V p-p PGA = 6 dB

3.17 dBm Max output = 2 × (1.578/1.2) × VREFCAP

Nominal Voltage Output Swing (0 dBm0)

Single-Ended 1.0954 V p-p PGA = 6 dB

−6.02 dBm

Differential 2.1909 V p-p PGA = 6 dB

0 dBm

Output Bias Voltage 1.2 V REFOUT unloaded

Absolute Gain −1.75 −0.6 +0.75 dB 1.0 kHz, 0 dBm0; unloaded

Gain Tracking Error ±0.1 dB 1.0 kHz, +3 dBm0 to −50 dBm0

Signal-to-Noise and Distortion at 0 dBm0 Refer to Figure 10

PGA = 0 dB 72 78.5 dB 300 Hz to 3400 Hz; f

Total Harmonic Distortion at 0 dBm0

PGA = 0 dB −89 −75 dB 300 Hz to 3400 Hz; f

Intermodulation Distortion −77 dB PGA = 0 dB

Idle Channel Noise Crosstalk −81 dBm0 PGA = 0 dB

DAC-to-ADC −73 dB

−74 dB Input amplifiers included in input channel

DAC-to-DAC −102 dB

Power Supply Rejection −65 dB

Group Delay

50 µs

Output DC Offset

Minimum Load Resistance, R

Single-Ended

Differential 150 Ω

Maximum Load Capacitance, C

Single-Ended 500 pF

Differential 100 pF

FREQUENCY RESPONSE

(ADC and DAC)8 Typical Output

Frequency (Normalized to FS)

0 0 dB

0.03125 −0.1 dB

3, 4

1, 3, 5

25 µs

20 kΩ Input amplifiers bypassed

Tap gain change from −FS to +FS; includes

DAC settling time

1

SAMP

SAMP

= 8 kHz

= 8 kHz

ADC input signal level: AGND;

DAC output signal level: 1.0 kHz, 0 dBm0

Input amplifiers bypassed

DAC1 output signal level: AGND; DAC2

Output signal level: 1.0 kHz, 0 dBm0

Input signal level at AVDD and DVDD pins:

1.0 kHz, 100 mV p-p sine wave

3, 4

1, 6

1, 7

3

L

1, 7

L

25 µs Interpolator bypassed

−50 +5 +60 mV

150 Ω

Rev. A | Page 5 of 48

AD73322L

A and Y Versions

Parameter Min Typ Max Unit Test Conditions/Comments

0.0625 −0.25 dB

0.125 −0.6 dB

0.1875 −1.4 dB

0.25 −2.8 dB

0.3125 − 4.5 dB

0.375 −7.0 dB

0.4375 −9.5 dB

> 0.5 <−12.5 dB

LOGIC INPUTS

V

, Input High Voltage

INH

V

, Input Low Voltage 0 0.8 V

INL

DVDD − 0.8

IIH, Input Current −10 +10 µA

CIN, Input Capacitance 10 pF

LOGIC OUTPUT

VOH, Output High Voltage

DVDD − 0.4

VOL, Output Low Voltage 0 0.4 V |IOUT| ≤100 µA

Three-State Leakage Current −10 +10 µA

POWER SUPPLIES

AVDD1, AVDD2 2.7 3.3 V

2.7 3.3 V

DVDD I

9

DD

See Table 2

1

Test conditions: input PGA set for 0 dB gain, output PGA set for 6 dB gain, no load on analog outputs (unless otherwise noted).

2

At input to sigma-delta modulator of ADC.

3

Guaranteed by design.

4

Overall group delay is affected by the sample rate and the external digital filtering.

5

The ADC’s input impedance is inversely proportional to DMCLK and is approximated by (3/3 × 1011)/DMCLK.

6

Between VOUTP1 and VOUTN1 or between VOUTP2 and VOUTN2.

7

At VOUT output.

8

Frequency responses of ADC and DAC measured with input at audio reference level (the input level that produces an output level of −10 dBm0), with 38 dB

preamplifier bypassed and input gain of 0 dB.

9

Test conditions: no load on digital inputs, analog inputs ac-coupled to ground, no load on analog outputs.

DVDD V

DVDD V |IOUT| ≤100 µA

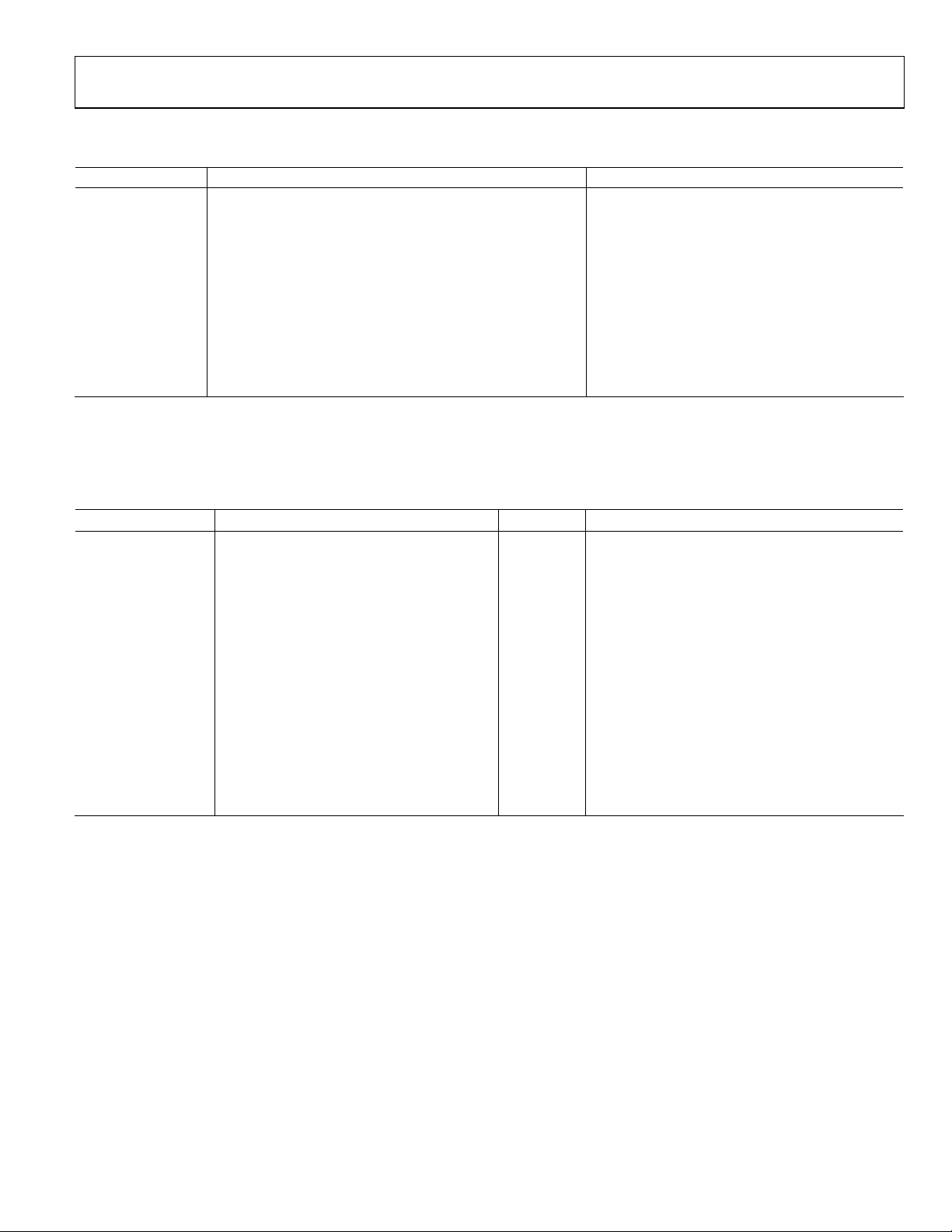

CURRENT SUMMARY

AVDD = DVDD = 3.3 V. These values are in mA and are typical values unless otherwise noted.

Table 2.

Analog

Conditions

Current

ADCs on only 3.4 6.3 9.7 12 1 YES REFOUT disabled

DACs on only 8.8 6.5 15.3 20 1 YES REFOUT disabled

ADCs and DACs on 11.6 7.0 18.6 23 1 YES REFOUT disabled

ADCs and DACs and

13.8 7.0 20.8 26 1 YES REFOUT disabled

Input amps on

ADCs and DACs and

13.2 7.0 20.2 26 1 YES REFOUT disabled

AGT on

All sections on 17.2 7.0 24.2 31 1 YES

REFCAP on only 0.65 0 0.67 1.25 0 NO REFOUT disabled

REFCAP and REFOUT

2.56 0 2.57 4.5 0 NO

On only

All sections off 0 1.25 1.25 1.8 0 YES

All sections off 0 µA 12.5 µA 12.7 µA 40 µA 0 NO

Digital

Current

Total

Current (Typ)

Rev. A | Page 6 of 48

Total

Current (Max)

SE MCLK ON Comments

MCLK active levels equal

to 0 V and DVDD

Digital inputs static and

Equal to 0 V or DVDD

AD73322L

SIGNAL RANGES

Table 3.

Mnemoic Description Range

VREFCAP 1.2 V ± 10%

VREFOUT 1.2 V ± 10%

ADC Maximum input range at V

IN

Nominal reference level 1.0954 V p-p

DAC Maximum voltage output swing

Single-Ended 1.578 V p-p

Differential 3.156 V p-p

Nominal voltage output swing

Single-Ended 1.0954 V p-p

Differential 2.1909 V p-p

Output bias voltage VREFOUT

TIMING CHARACTERISTICS

AVDD = 3 V ± 10%; DVDD = 3 V ± 10%; AGND = DGND = 0 V; TA = T

Table 4.

Parameter

Limit at T

= −40°C to +105°C

A

Clock Signals See Figure 2

t

1

t

2

t

3

61 ns min MCLK period

24.4 ns min MCLK width high

24.4 ns min MCLK width low

Serial Port See Figure 4 and Figure 5

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

t

1

0.4 × t

1

0.4 × t

1

20 ns min SDI/SDIFS setup before SCLK low

0 ns min SDI/SDIFS hold after SCLK low

10 ns max SDOFS delay from SCLK high

10 ns min SDOFS hold after SCLK high

10 ns min SDO hold after SCLK high

10 ns max SDO delay from SCLK high

30 ns max SCLK delay from MCLK

to T

MlN

Unit Description

ns min SCLK period

ns min SCLK width high

ns min SCLK width low

1.578 V p-p

, unless otherwise noted.

MAX

Rev. A | Page 7 of 48

AD73322L

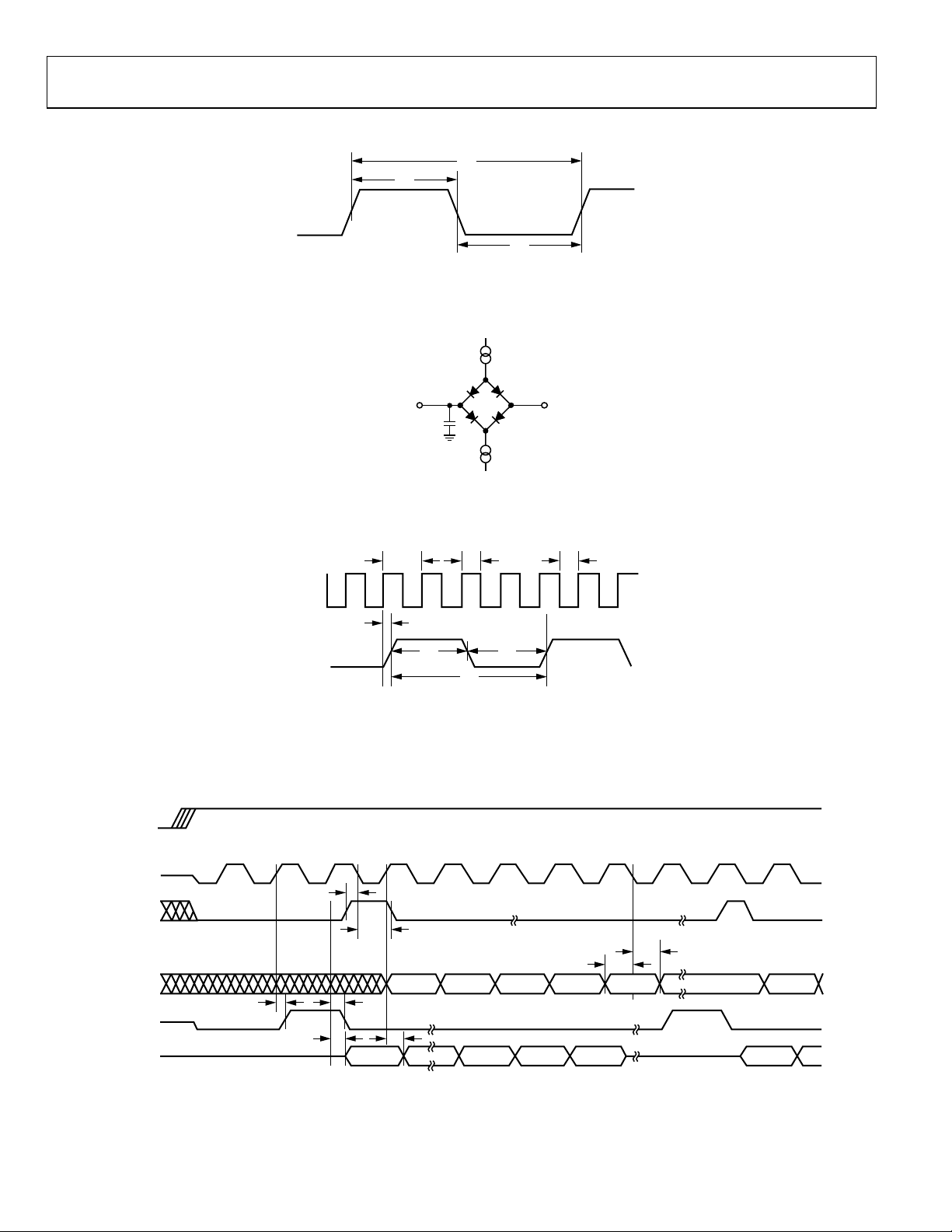

TIMING DIAGRAMS

t

1

t

2

Figure 2. MCLK Ti ming

t

3

00691-002

TO OUTPUT

PIN

15pF

C

L

100µAI

100µAI

OL

2.1V

OH

00691-003

Figure 3. Load Circuit for Timing Specifications

MCLK

SCLK*

t

1

t

13

* SCLK IS INDIVIDUALLY PROGRAMMABLE

IN FREQUENCY (MCLK/4 SHOWN HERE).

t

2

t

5

t

6

t

4

t

3

00691-004

Figure 4. SCLK Ti ming

SE (I)

SCLK (O)

SDIFS (I)

SDI (I)

SDOFS (O)

SDO (O)

THREESTATE

THREESTATE

THREESTATE

t

7

t

8

t

8

t

7

D15D0D1D14D15

t

9

t

12

t

10

t

11

D15 D2 D1 D0 D14

D15

00691-005

Figure 5. Serial Port (SPORT)

Rev. A | Page 8 of 48

AD73322L

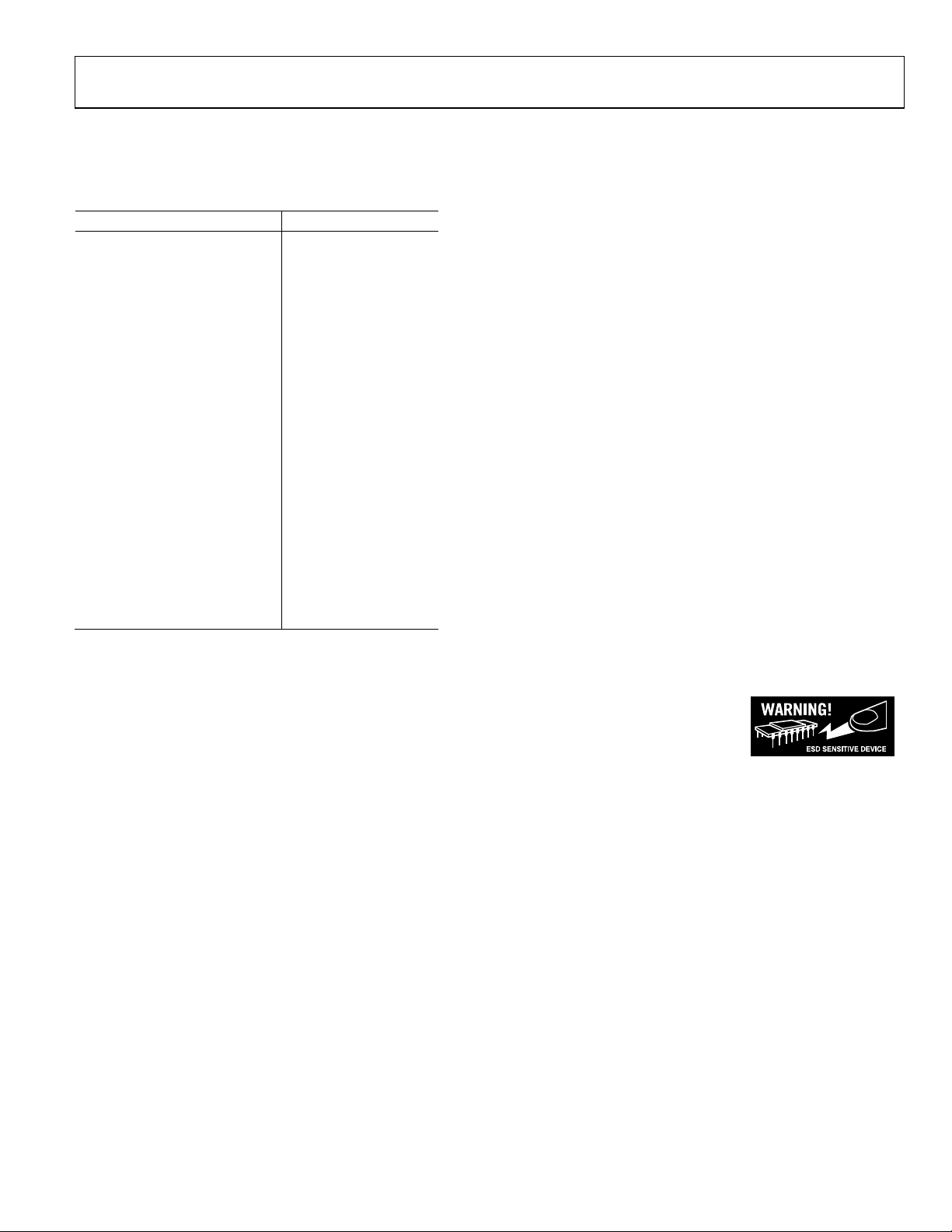

ABSOLUTE MAXIMUM RATINGS

TA = 25°C unless otherwise noted.

Table 5.

Parameters Ratings

AVDD, DVDD to GND −0.3 V to +4.6 V

AGND to DGND −0.3 V to +0.3 V

Digital I/O Voltage to DGND −0.3 V to (DVDD + 0.3 V)

Analog I/O Voltage to AGND −0.3 V to (AVDD + 0.3 V)

Operating Temperature Range

Industrial (A Version) −40°C to +85°C

Extended (Y Version) −40°C to +105°C

Storage Temperature Range −65°C to +150°C

Maximum Junction Temperature 150°C

SOIC, θJA Thermal Impedance 71.4°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

LQFP, θJA Thermal Impedance 53.2°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

TSSOP, θJA Thermal Impedance 97.9°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the uman body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 9 of 48

AD73322L

2

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

VFBN2

VINP1

1

VFBP1

2

VINN1

3

VFBN1

4

REFOUT

REFCAP

AVDD2

AGND2

DGND

DVDD

RESET

SCLK

MCLK

SDO

5

AD73322L

TOP VIEW

6

(Not to Scale)

7

8

9

10

11

12

13

14

Figure 6. 28-Lead Wide Body

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VINN2

VFBP2

VINP2

VOUTN1

VOUTP1

VOUTN2

VOUTP2

AVDD1

AGND1

SE

SDI

SDIFS

SDOFS

00691-006

1

VINP1

2

VFBP1

3

VINN1

4

VFBN1

REFOUT

REFCAP

5

AD73322L

TOP VIEW

6

7

AVDD2

8

AGND2

9

DGND

10

DVDD

11

RESET

12

SCLK

13

MCLK SDIFS

14

SDO

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Figure 7. 28-Lead Thin Shrink

VFBN2

VINN2

VFBP2

VINP2

VOUTN1

VOUTP1

VOUTN2

VOUTP2

AVDD1

AGND1

SE

SDI

SDOFS

00691-007

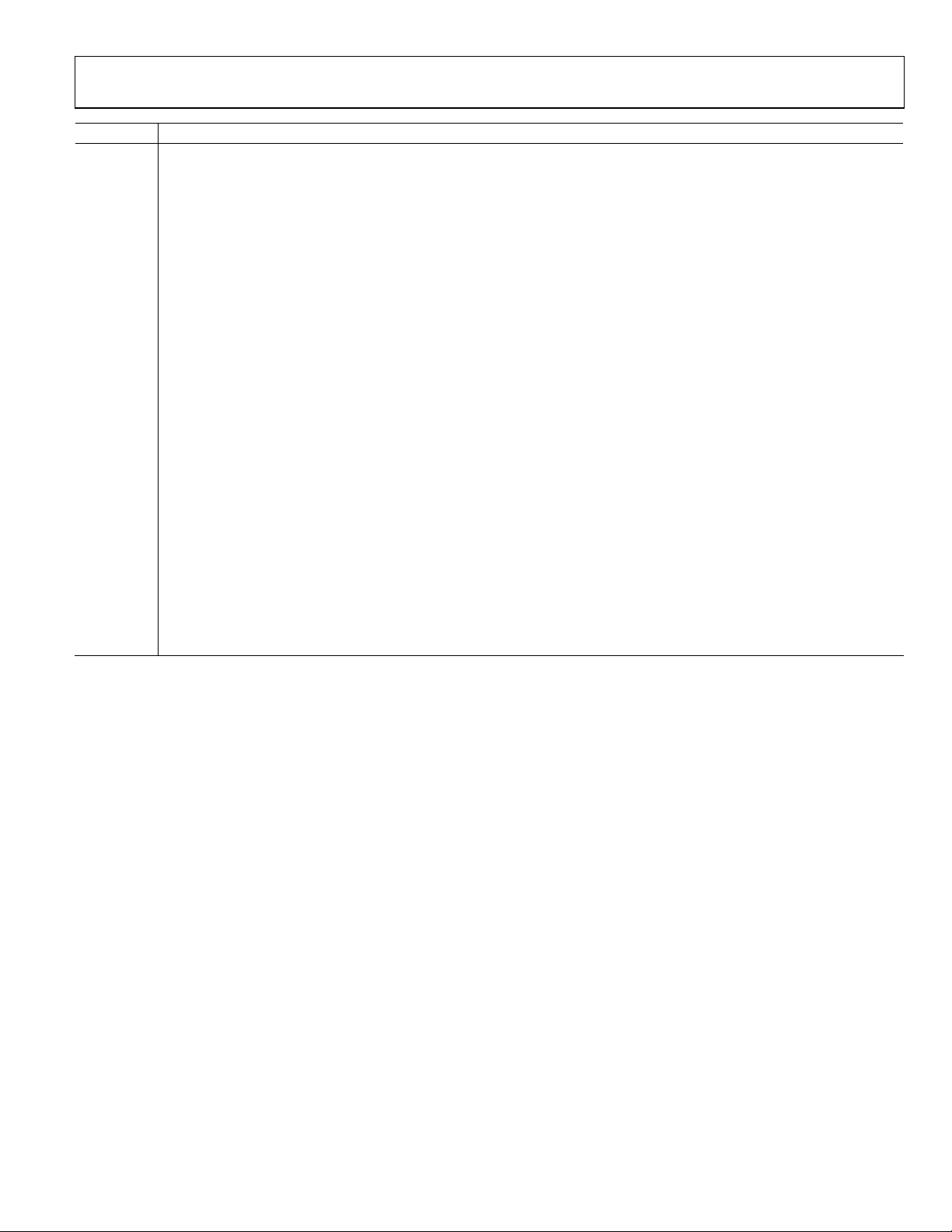

AVDD2

AVDD2

AGND2

AGND2

AGND2

AGND2

DGND

DGND

DVDD

1

2

3

4

5

6

7

8

9

10

11

REFOUT

REFCAP

NC = NO CONNECT

VFBN142VINN141VFBP140VINP139NC38VFBN

44NC43

PIN 1

12NC13

14

15

SCLK

RESET

AD73322L

TOP VIEW

(Not to Scale)

16

MCLK

SDO

17NC18

VINN236VFBP235VINP234NC

37

19

20

SDIFS

SDOFS

SDI

21SE22

NC

33

32

31

30

29

28

27

26

25

24

23

NC

VOUTN1

VOUTP1

NC

VOUTN2

VOUTP2

NC

AVDD1

AVDD1

AGND1

AGND1

00691-008

Figure 8. 44-Lead Plastic Thin Quad Flatpack

Table 6. Pin Function Descriptions

Mnemonic Function

VINP1 Analog Input to the inverting input amplifier on Channel 1’s positive input.

VFBP1

Feedback Connection from the output of the inverting amplifier on Channel 1’s positive input. When the input amplifiers are

bypassed, this pin allows direct access to the positive input of Channel 1’s sigma-delta modulator.

VINN1 Analog Input to the inverting input amplifier on Channel 1’s negative input.

VFBN1

Feedback connection from the output of the inverting amplifier on Channel 1’s negative input. When the input amplifiers are

bypassed, this pin allows direct access to the negative input of Channel 1’s sigma-delta modulator.

REFOUT Buffered Reference Output, which has a nominal value of 1.2 V.

REFCAP A bypass capacitor to AGND2 of 0.1 µF is required for the on-chip reference. The capacitor should be fixed to this pin.

AVDD2 Analog Power Supply Connection.

AGND2 Analog Ground/Substrate Connection2.

DGND Digital Ground/Substrate Connection.

DVDD Digital Power Supply Connection.

RESET

Active Low Reset Signal. This input resets the entire chip, resetting the control registers and clearing the digital circuitry.

Rev. A | Page 10 of 48

AD73322L

Mnemonic Function

SCLK

MCLK Master Clock Input. MCLK is driven from an external clock signal.

SDO

SDOFS

SDIFS

SDI

SE

AGND1 Analog Ground/Substrate Connection.

AVDD1 Analog Power Supply Connection.

VOUTP2 Analog Output from the Positive Terminal of Output Channel 2.

VOUTN2 Analog Output from the Negative Terminal of Output Channel 2.

VOUTP1 Analog Output from the Positive Terminal of Output Channel 1.

VOUTN1 Analog Output from the Negative Terminal of Output Channel 1.

VINP2 Analog Input to the inverting input amplifier on Channel 2’s positive input.

VFBP2

VINN2 Analog Input to the inverting input amplifier on Channel 2’s negative input.

VFBN2

Serial Clock Output. This rate determines the serial transfer rate to/from the codec. It is used to clock data or control

information to and from the serial port (SPORT). The frequency of SCLK is equal to the frequency of the master clock (MCLK)

divided by an integer number—this integer number being the product of the external master clock rate divider and the serial

clock rate divider.

Serial Data Output. Both data and control information may be output on this pin and are clocked on the positive edge of

SCLK. SDO is in three-state when no information is being transmitted and when SE is low.

Framing Signal Output for SDO Serial Transfers. The frame sync is one bit wide and is active one SCLK period before the first

bit (MSB) of each output word. SDOFS is referenced to the positive edge of SCLK. SDOFS is in three-state when SE is low.

Framing Signal Input for SDI Serial Transfers. The frame sync is one bit wide and is valid one SCLK period before the first bit

(MSB) of each input word. SDIFS is sampled on the negative edge of SCLK and is ignored when SE is low.

Serial Data Input. Both data and control information may be input on this pin and are clocked on the negative edge of SCLK.

SDI is ignored when SE is low.

SPORT Enable. Asynchronous input enable pin for the SPORT. When SE is set low by the DSP, the output pins of the SPORT are

three-stated and the input pins are ignored. SCLK is also disabled internally in order to decrease power dissipation. When SE is

brought high, the control and data registers of the SPORT are at their original values (before SE was brought low); however,

the timing counters and other internal registers are at their reset values.

Feedback connection from the output of the inverting amplifier on Channel 2’s positive input. When the input amplifiers are

bypassed, this pin allows direct access to the positive input of Channel 2’s sigma-delta modulator.

Feedback connection from the output of the inverting amplifier on Channel 2’s negative input. When the input amplifiers are

bypassed, this pin allows direct access to the negative input of Channel 2’s sigma-delta modulator.

Rev. A | Page 11 of 48

AD73322L

TERMINOLOGY

Absolute Gain

A measure of converter gain for a known signal. Absolute gain

is measured (differentially) with a 1 kHz sine wave at 0 dBm0

for the DAC and with a 1 kHz sine wave at 0 dBm0 for the

ADC. The absolute gain specification is used for gain tracking

error specification.

Sample Rate

The rate at which the ADC updates its output register and the

DAC updates its output from its input register. The sample rate

can be chosen from a list of four that are fixed relative to the

DMCLK. Sample rate is set by programming bits DIR0-1 in

Control Register B of each channel.

Crosstalk

Crosstalk is due to coupling of signals from a given channel to

an adjacent channel. It is defined as the ratio of the amplitude

of the coupled signal to the amplitude of the input signal.

Crosstalk is expressed in dB.

Gain Tracking Error

Measures changes in converter output for different signal levels

relative to an absolute signal level. The absolute signal level is

0 dBm0 (equal to absolute gain) at 1 kHz for the DAC and 0

dBm0 (equal to absolute gain) at 1 kHz for the ADC. Gain

tracking error at 0 dBm0 (ADC) and 0 dBm0 (DAC) is 0 dB

by definition.

Group Delay

The derivative of radian phase with respect to radian frequency,

dø(f)/df. Group delay is a measure

of the average delay of a

system as a function of frequency. A linear system with a

constant group delay has a linear phase response. The deviation

of group delay from a constant indicates the degree of nonlinear

phase response of the system.

Idle Channel Noise

The total signal energy measured at the output of the device

when the input is grounded (measured in the frequency range

300 Hz to 3400 Hz).

Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and

fb, any active device with nonlinearities creates distortion

products at sum and difference frequencies of mfa ± nfb where

m, n = 0, 1, 2, 3, etc. Intermodulation terms are those for which

neither m nor n is equal to zero. For final testing, the secondorder terms include (fa + fb) and (fa − fb), while the third-order

terms include (2fa + fb), (2fa − fb), (fa + 2fb) and (fa − 2fb).

Power Supply Rejection

Measures the susceptibility of a device to noise on the power

supply. Power supply rejection is measured by modulating the

power supply with a sine wave and measuring the noise at the

output (relative to 0 dB).

SNR + THD

Signal-to-noise ratio plus harmonic distortion is the ratio of the

rms value of the measured input signal to the rms sum of all

other spectral components in the frequency range 300 Hz to

3400 Hz, including harmonics but excluding dc.

ABBREVIATIONS

Table 7.

Abbreviation Definition

ADC Analog-to-digital converter.

AFE Analog front end.

AGT Analog gain tap.

ALB Analog loop-back.

BW Bandwidth.

CRx

CRx:n

DAC Digital-to-analog converter.

DGT Digital gain tap.

DLB Digital loop-back.

DMCLK

FS Full scale.

FSLB

PGA Programmable gain amplifier.

SC Switched capacitor.

SLB SPORT loop-back.

SNR Signal-to-noise ratio.

SPORT Serial port.

THD Total harmonic distortion.

VBW Voice bandwidth.

A control register where x is a placeholder for

an alphabetic character (A to H). There are eight

read/write control registers on the AD73322L—

CRA through CRH.

A bit position, where n is a placeholder for a

numeric character (0 to 7), within a control

register, where x is a placeholder for an

alphabetic character (A to E). Position 7

represents the MSB and Position 0 represents

the LSB.

Device (internal) master clock. This is the

internal master clock resulting from the

external master clock (MCLK) being divided by

the on-chip master clock divider.

Frame sync loop-back—where the SDOFS of

the final device in a cascade is connected to the

RFS and TFS of the DSP and the SDIFS of first

device in the cascade. Data input and output

occur simultaneously. In the case of nonFSLB,

SDOFS and SDO are connected to the Rx port of

the DSP while SDIFS and SDI are connected to

the Tx port.

Rev. A | Page 12 of 48

AD73322L

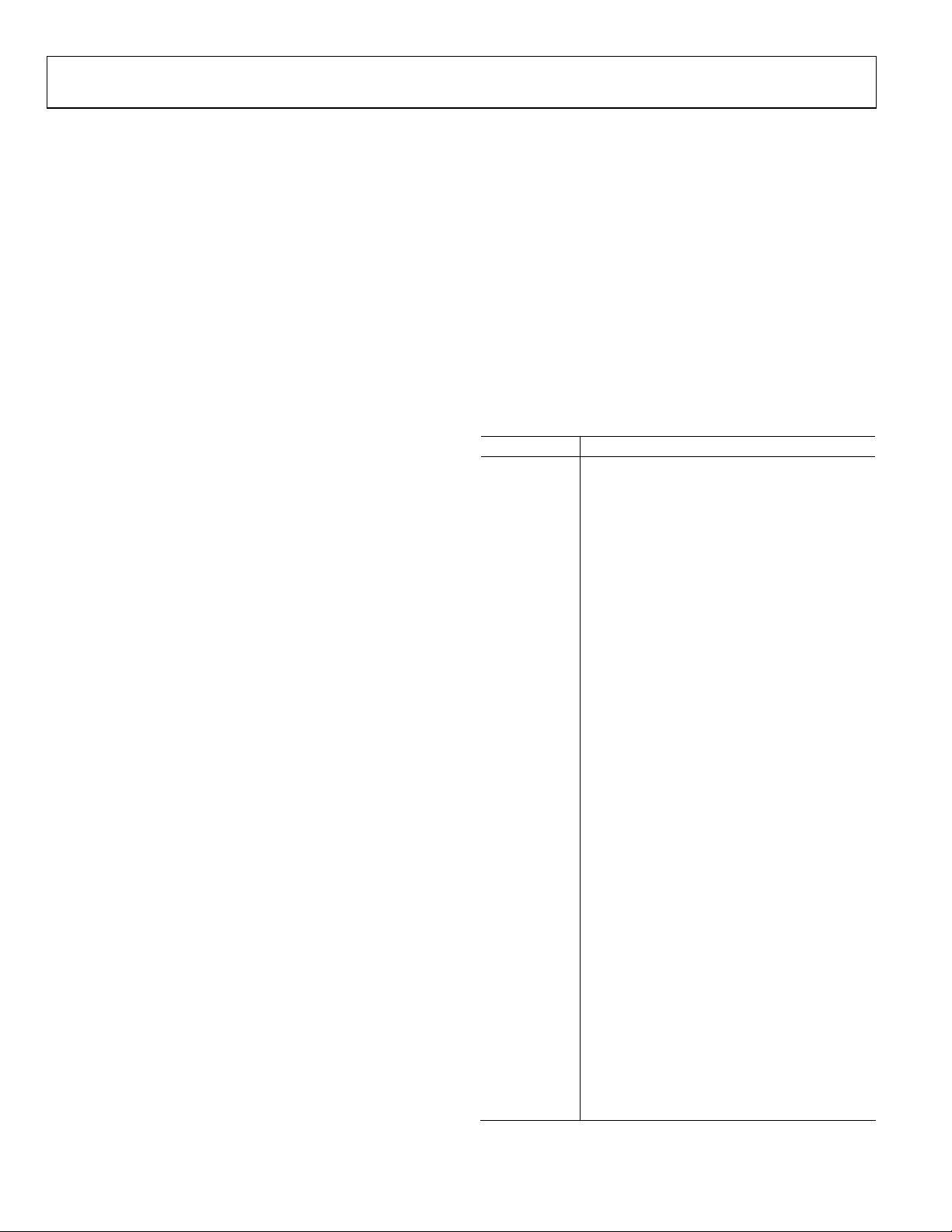

TYPICAL PERFORMANCE CHARACTERISTICS AND FUNCTIONAL BLOCK DIAGRAM

80

70

60

50

40

30

S/(N + D) (dB)

20

10

0

–10

–85 –75 –65 –55 –45 –35 –25 –15 –5

Figure 9. S/N(N = D) vs. V

VIN (dBm0)

(ADC @ 3 V) over Voice Bandwidth

IN

(300 Hz to 3.4 kHz)

VFBN1

VINN1

ANALOG

LOOPBACK

VINP1

VFBP1

V

REF

GAIN

±1

5

3.17

00691-009

INVERT

SINGLE-ENDED

ENABLE

0/38dB

PGA

80

70

60

50

40

30

S/(N + D) (dB)

20

10

0

–10

–85 –75 –65 –55 –45 –35 –25 –15 –5

Figure 10. S/N(N = D) vs. V

VIN (dBm0)

(DAC @ 3 V) over Voice Bandwidth

IN

(300 Hz to 3.4 kHz)

DVDDAVDD2AVDD1

DIGITAL

Σ-∆

MODULATOR

GAIN

±1

DECIMATOR

SDI

SDIFS

SCLK

3.17

5

00691-010

VOUTP1

VOUTN1

REFCAP

REFOUT

VFBN2

VINN2

VINP2

VFBP2

VOUTP2

VOUTN2

+6/15dB

PGA

REFERENCE

CONTINUOUS

TIME

LOW-PASS

FILTER

SWITCHED

CAPACITOR

LOW-PASS

FILTER

1-BIT

DAC

DIGITAL

Σ-∆

MODULATOR

INTER-

POLATOR

SERIAL

I/O

PORT

RESET

MCLK

SE

AD73322L

V

REF

ANALOG

LOOPBACK

+6/–15dB

PGA

GAIN

±1

CONTINUOUS

TIME

LOW-PASS

FILTER

INVERT

SINGLE-ENDED

ENABLE

SWITCHED

CAPACITOR

LOW-PASS

FILTER

AGND1 AGND2 DGND

0/38dB

PGA

1-BIT

DAC

DIGITAL

Σ-∆

MODULATOR

DIGITAL

Σ-∆

MODULATOR

GAIN

±1

DECIMATOR

INTER-

POLATOR

SDO

SDOFS

00691-011

Figure 11. Functional Block Diagram

Rev. A | Page 13 of 48

AD73322L

FUNCTIONAL DESCRIPTIONS

ENCODER CHANNELS

Both encoder channels consist of a pair of inverting op amps

with feedback connections that can be bypassed if required, a

switched capacitor PGA and a sigma-delta analog-to-digital

converter (ADC). An on-board digital filter, which forms part

of the sigma-delta ADC, also performs critical system-level

filtering. Due to the high level of oversampling, the input

antialias requirements are reduced such that a simple singlepole RC stage is sufficient to give adequate attenuation in the

band of interest.

PROGRAMMABLE GAIN AMPLIFIER

Each encoder section’s analog front end comprises a switched

capacitor PGA, which also forms part of the sigma-delta

modulator. The SC sampling frequency is DMCLK/8. The

PGA, whose programmable gain settings are shown in Table 8,

may be used to increase the signal level applied to the ADC

from low output sources such as microphones, and can be

used to avoid placing external amplifiers in the circuit. The

input signal level to the sigma-delta modulator should not

exceed the maximum input voltage permitted.

highest frequency of interest. In the case of the AD73322L, the

initial sampling rate of the sigma-delta modulator is DMCLK/8.

The main effect of oversampling is that the quantization noise is

spread over a very wide bandwidth, up to F

/2 = DMCLK/16

S

(Figure 13). This means that the noise in the band of interest is

much reduced. Another complementary feature of sigma-delta

converters is the use of a technique called noise-shaping. This

technique has the effect of pushing the noise from the band of

interest to an out-of-band position (Figure 14). The combination of these techniques, followed by the application of a

digital filter, sufficiently reduces the noise in band to ensure

good dynamic performance from the part (Figure 15).

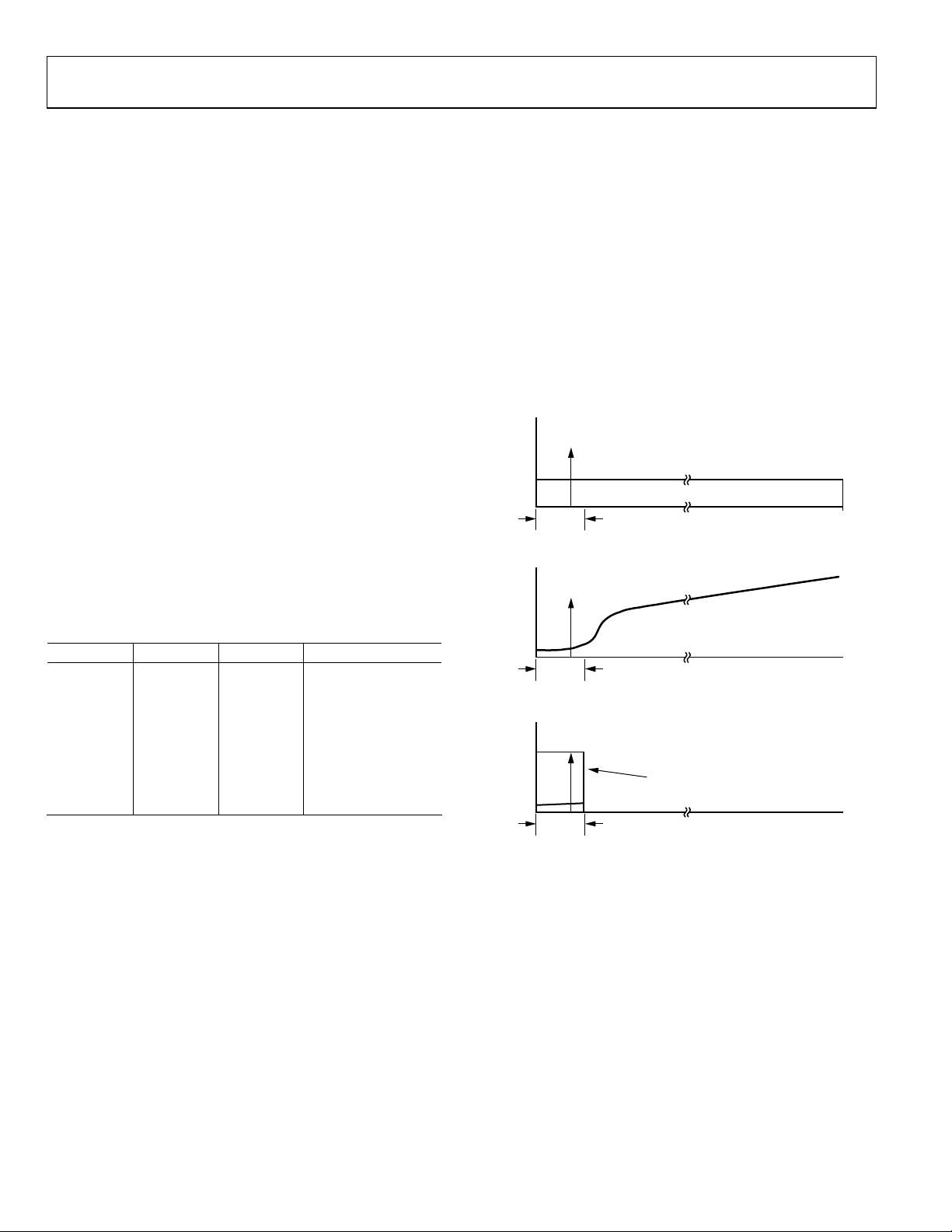

BAND

OF

INTEREST

A.

FS/2

DMCLK/16

The PGA gain is set by bits IGS0, IGS1, and IGS2 (CRD:0–2) in

control register D.

Table 8. PGA Settings for the Encoder Channel

IGS2 IGS1 IGS0 Gain (dB)

0 0 0 0

0 0 1 6

0 1 0 12

0 1 1 18

1 0 0 20

1 0 1 26

1 1 0 32

1 1 1 38

ADC

Both ADCs consist of an analog sigma-delta modulator and a

digital antialiasing decimation filter. The sigma-delta modulator

noise-shapes the signal and produces 1-bit samples at a

DMCLK/8 rate. This bit stream, representing the analog input

signal, is input to the antialiasing decimation filter. The

decimation filter reduces the sample rate and increases the

resolution.

ANALOG SIGMA-DELTA MODULATOR

The AD73322L’s input channels employ a sigma-delta

conversion technique, which provides a high resolution 16-bit

output with system filtering being implemented on-chip.

Sigma-delta converters employ a technique known as

oversampling, where the sampling rate is many times the

NOISE SHAPING

BAND

OF

INTEREST

BAND

OF

INTEREST

B.

DIGITAL FILTER

C.

Figure 12. Sigma-Delta Noise Reduction

FS/2

DMCLK/16

FS/2

DMCLK/16

Figure 13 through Figure 16 show the various stages of filtering

that are employed in a typical AD73322L application. Figure 13

shows the transfer function of the external analog antialias

filter. Even though it is a single RC pole, its cutoff frequency

is sufficiently far away from the initial sampling frequency

(DMCLK/8) that it takes care of any signals that could be

aliased by the sampling frequency. This also shows the major

difference between the initial oversampling rate and the bandwidth of interest. In Figure 14, the signal and noise-shaping

responses of the sigma-delta modulator are shown. The

signal response provides further rejection of any high

frequency signals, while the noise-shaping pushes the inherent

quantization noise to an out-of-band position. The detail of

00691-012

Rev. A | Page 14 of 48

AD73322L

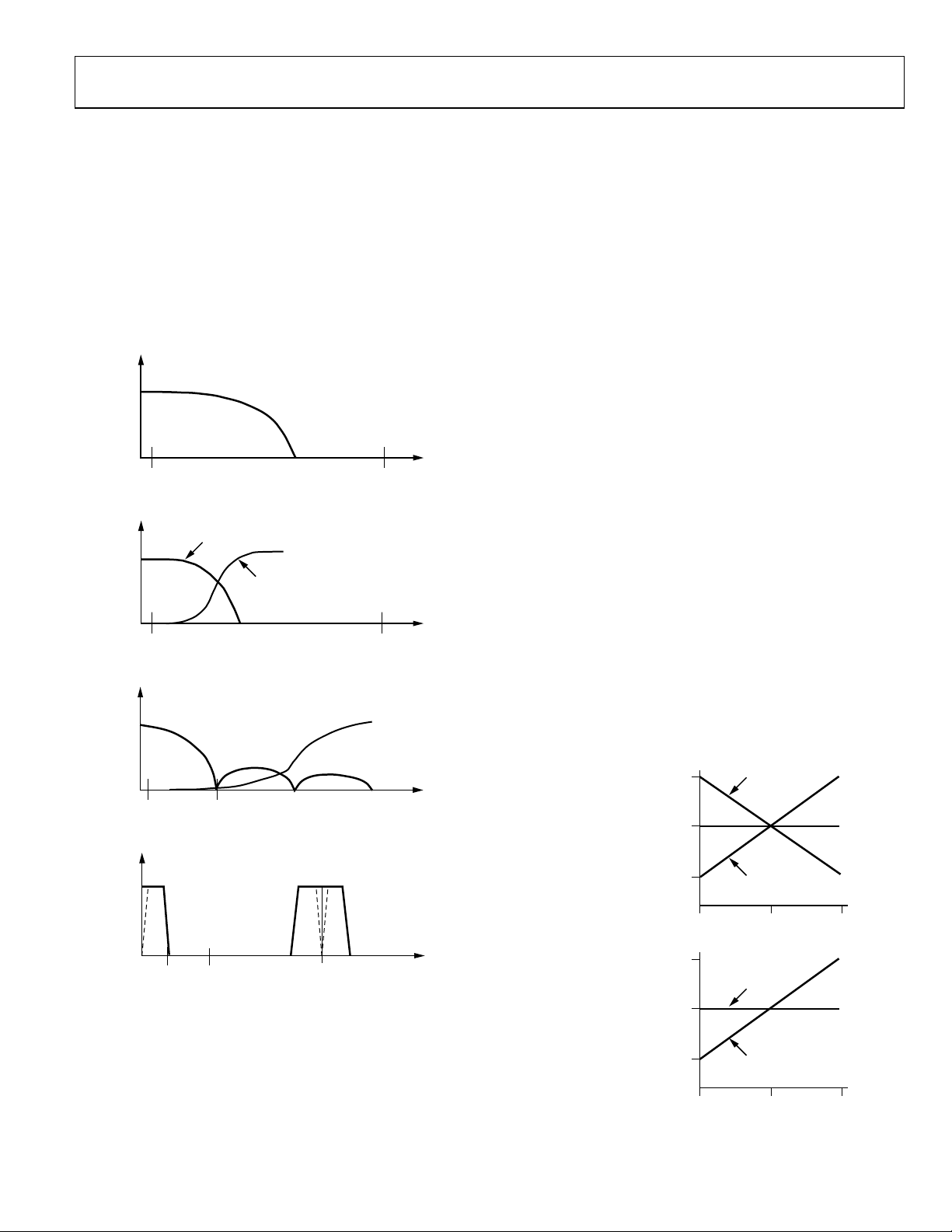

Figure 15 shows the response of the digital decimation filter

(sinc-cubed response) with nulls every multiple of DMCLK/256

corresponding to the decimation filter update rate for a 64 kHz

sampling. The nulls of the Sinc3 response correspond with

multiples of the chosen sampling frequency. The final detail in

Figure 16 shows the application of a final antialias filter in the

DSP engine. This has the advantage of being implemented

according to the user’s requirements and available MIPS. The

filtering in Figure 13 through Figure 16 is implemented in the

AD73322L.

Figure 13 to Figure 16 show ADC frequency responses.

FB = 4kHz F

Figure 13. Analog Antialias Filter Transfer Function

SIGNAL TRANSFER FUNCTION

NOISE TRANSFER FUNCTION

SINIT

= DMCLK/8

00691-013

The antialiasing decimation filter is a sinc-cubed digital filter

that reduces the sampling rate from DMCLK/8 to DMCLK/256,

and increases the resolution from a single bit to 15 bits or

greater (depending on chosen sampling rate). Its Z transform is

given as

[(1 − Z

−N

)/(1 − Z−1 )]

3

where N is set by the sampling rate

(N = 32 @ 64 kHz sampling N = 256 @ 8 kHz sampling)

Thus, when the sampling rate is 64 kHz, a minimal group delay

of 25 µs can be achieved.

Word growth in the decimator is determined by the sampling

rate. At 64 kHz sampling, where the oversampling ratio (OSR)

between sigma-delta modulator and decimator output equals

32, there are five bits per stage of the three-stage Sinc3 filter.

Due to symmetry within the sigma-delta modulator, the LSB

is always a zero; therefore, the 16-bit ADC output word has

2 LSBs equal to zero, one due to the sigma-delta symmetry and

the other being a padding zero to make up the 16-bit word. At

lower sampling rates, decimator word growth is greater than the

16-bit sample word, therefore truncation occurs in transferring

the decimator output as the ADC word. For example, at 8 kHz

sampling, word growth reaches 24 bits due to the OSR of 256

between the sigma-delta modulator and decimator output. This

yields 8 bits per stage of the three-stage sinc3 filter.

FB = 4kHz F

SINIT

= DMCLK/8

Figure 14. Analog Sigma-Delta Modulator Transfer Function

FB = 4kHz F

SINTER

= DMCLK/256

Figure 15. Digital Decimator Transfer Function

FB = 4kHz F

SRNAL

= 8kHz F

SINTER

= DMCLK/256

Figure 16. Final Filter (HPF) Transfer Function

DECIMATION FILTER

The digital filter used in the AD73322L carries out two

important functions. First, it removes the out-of-band

quantization noise, which is shaped by the analog modulator

and second, it decimates the high frequency bit stream to a

lower rate, 16-bit word.

00691-014

00691-015

00691-016

ADC CODING

The ADC coding scheme is in twos complement format, as

shown in Figure 17). The output words are formed by the

decimation filter, which grows the word length from the single

bit output of the sigma-delta modulator to a word length of up

to 24 bits (depending on decimation rate chosen), which is the

final output of the ADC block. In data mode this value is truncated to 16 bits for output on the serial data output (SDO) pin.

V

+ (V

ANALOG

INPUT

V

ANALOG

INPUT

REF

V

V

REF

× 0.32875)

REF

V

REF

– (V

× 0.32875)

REF

10...00 00...00 01...11

+ (V

– (V

REF

REF

× 0.6575)

× 0.6575)

10...00 00...00 01...11

REF

REF

Figure 17. ADC Transfer Function

V

INN

V

INP

ADC CODE DIFFERENTIAL

V

INN

V

INP

ADC CODE SINGLE-ENDED

00691-017

Rev. A | Page 15 of 48

Loading...

Loading...