www.BDTIC.com/ADI

High Precision Voltage Reference

FEATURES

Low drift: 1.5 ppm/°C

Low initial error: 1 mV

Pin programmable output

+10 V, +5 V, ±5 V tracking, −5 V

Flexible output force and sense terminals

High impedance ground sense

SOIC_W-16 and CERDIP-16 packages

MIL-STD-883-compliant versions available

GENERAL DESCRIPTION

The AD5881 represents a major advance in state-of-the-art

monolithic voltage references. Low initial error and low

temperature drift give the AD588 absolute accuracy performance

previously not available in monolithic form. The AD588 uses a

proprietary ion-implanted, buried Zener diode and laser-wafer

drift trimming of high stability thin film resistors to provide

outstanding performance.

The AD588 includes the basic reference cell and three

dditional amplifiers that provide pin programmable output

a

ranges. The amplifiers are laser trimmed for low offset and low

drift to maintain the accuracy of the reference. The amplifiers

are configured to allow Kelvin connections to the load and/or

boosters for driving long lines or high current loads, delivering

the full accuracy of the AD588 where it is required in the

application circuit.

The low initial error allows the AD588 to be used as a system

r

eference in precision measurement applications requiring

12-bit absolute accuracy. In such systems, the AD588 can provide

a known voltage for system calibration in software. The low

drift also allows compensation for the drift of other components

in a system. Manual system calibration and the cost of periodic

recalibration can, therefore, be eliminated. Furthermore, the

mechanical instability of a trimming potentiometer and the

potential for improper calibration can be eliminated by using

the AD588 in conjunction with auto calibration software.

The AD588 is available in 16-lead SOIC and CERDIP packages.

The AD588

CERDIP and are specified for 0°C to 70°C operation.

1

Protected by Patent Number 4,644,253.

JQ and AD588KQ grades are packaged in a 16-lead

, −10 V

Microcomputer

AD588

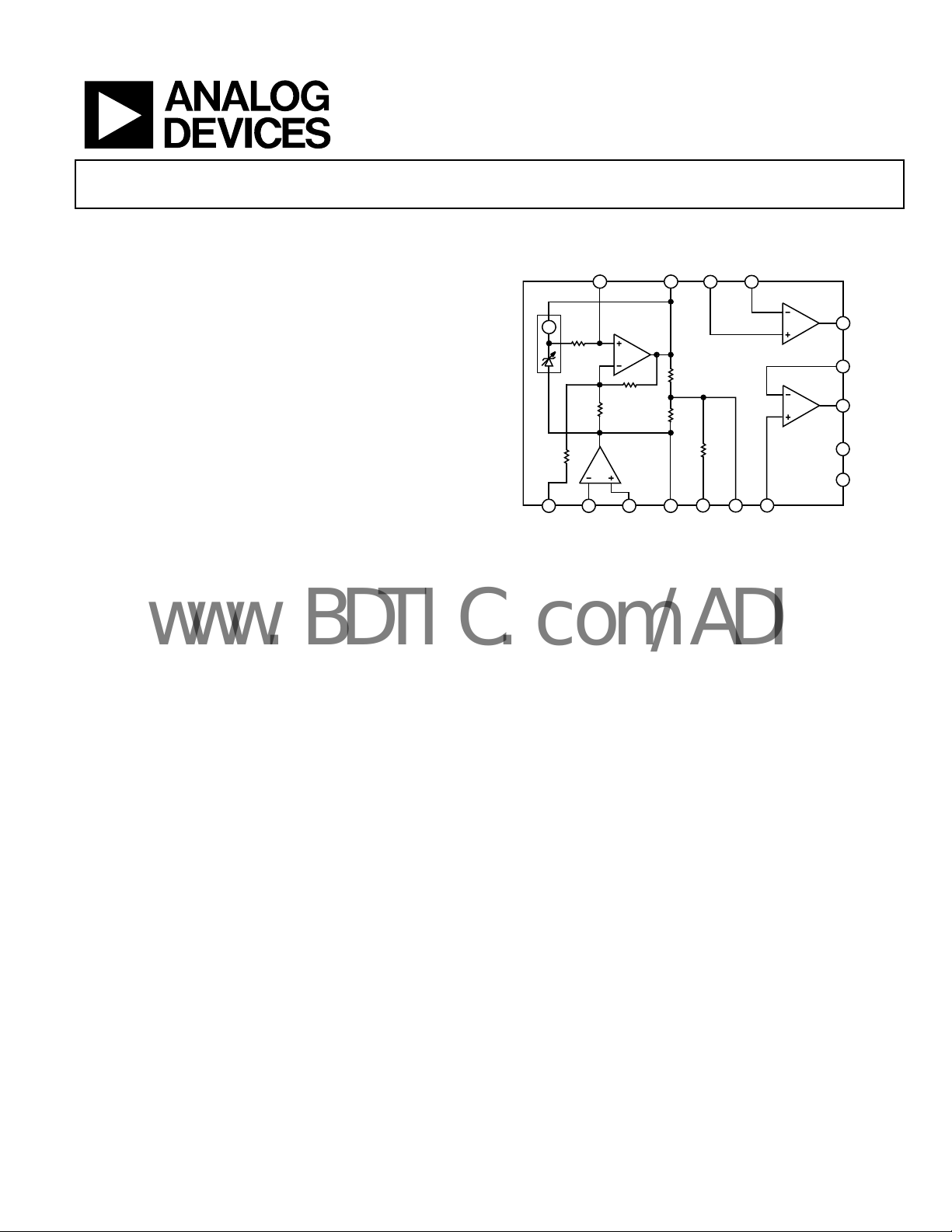

FUNCTIONAL BLOCK DIAGRAM

A3 IN

BAL

ADJ

A3 OUT

SENSE

3467

A3

A4

R6

AD588

13111281095

V

A4 IN

CT

1

14

15

2

16

A3 OUT

FORCE

A4 OUT

SENSE

A4 OUT

FORCE

+V

–V

GAIN

ADJ

R3

NOISE

REDUCTION

R

B

R2

A2

GND

SENSE

+IN

A1

R1

GND

SENSE

–IN

V

V

HIGH

R4

R5

LOW

Figure 1.

PRODUCT HIGHLIGHTS

1. The AD588 offers 12-bit absolute accuracy without any

user adjustments. Optional fine-trim connections are

provided for applications requiring higher precision. The

fine trimming does not alter the operating conditions of

the Zener or the buffer amplifiers, and so does not increase

the temperature drift.

2. O

utput noise of the AD588 is very low, typically 6 μV p-p.

A pin is provided for additional noise filtering using an

external capacitor.

3. A p

4. Pin st

recision ±5 V tracking mode with Kelvin output

connections is available with no external components.

Tracking error is less than 1 mV, and a fine trim is available

for applications requiring exact symmetry between the

+5 V and −5 V outputs.

rapping capability allows configuration of a wide

variety of outputs: ±5 V, +5 V, +10 V, −5 V, and −10 V dual

ou tp ut s or +5 V, − 5 V, +1 0 V, an d − 10 V si ng le ou tput s.

S

S

00531-001

Rev. G

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

AD588

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Temperature Performance......................................................... 10

General Description......................................................................... 1

Functional Block Diagram ..............................................................1

Product Highlights........................................................................... 1

Revision History ...............................................................................2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Theory of Operation ........................................................................ 6

Applications....................................................................................... 7

Calibration..................................................................................... 7

Noise Performance and Reduction ............................................9

Turn-On Time ............................................................................ 10

REVISION HISTORY

Kelvin Connections.................................................................... 11

Dynamic Performance............................................................... 13

Using the AD588 with Converters............................................... 15

AD7535 14-Bit Digital-to-Analog Converter......................... 15

AD569 16-Bit Digital-to-Analog Converter........................... 15

Substituting for Internal References ........................................ 16

AD574A 12-Bit Analog-to-Digital Converter........................ 16

Resistance Temperature Detector (RTD) Excitation............. 16

Boosted Precision Current Source........................................... 17

Bridge Driver Circuits ............................................................... 17

Outline Dimensions....................................................................... 19

Ordering Guide .......................................................................... 19

6/06—Rev. F to Rev. G

Changes to Table 5............................................................................ 7

Updated Outline Dimensions....................................................... 19

3/06—Rev. E to Rev. F

aced Figure 5 ............................................................................. 8

Repl

Updated Outline Dimensions....................................................... 19

11/05—Rev. D to Rev. E

pdated Format..................................................................Universal

U

Added SOIC Version..........................................................Universal

Changes to Pin 14 in Figures.............................................Universal

Changes to Pin 9 and Pin 10 in Figures...........................Universal

Changes to Specifications Section.................................................. 3

Added Table 3.................................................................................... 4

Added Pin Configuration and Function Descriptions Section.. 5

Added Table 4.................................................................................... 5

Changes to Grade in Reference and in Figure 12....................... 11

Updated Outline Dimensions....................................................... 19

Changes to Ordering Guide.......................................................... 19

2/03—Rev. C to Rev. D

A

dded KQ Model and Deleted SQ and TQ Models ......Universal

Changes to General Description .....................................................1

Change to Product Highlights.........................................................1

Changes to Specifications.................................................................2

Change to Ordering Guide...............................................................3

Updated Outline Dimensions....................................................... 15

10/02—Rev. B to Rev. C

hanges to General Description .....................................................1

C

Changes to Specifications.................................................................2

Changes to Ordering Guide.............................................................3

Changes to Table 1.............................................................................5

Deleted Figure 10c.............................................................................7

Outline Dimensions Updated....................................................... 15

Rev. G | Page 2 of 20

AD588

www.BDTIC.com/ADI

SPECIFICATIONS

Typical @ 25°C, 10 V output, VS = ±15 V, unless otherwise noted.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to

calculate

outgoing quality levels. All minimum and maximum specifications are guaranteed, although only those shown in boldface are tested on

all production units.

Table 1.

AD588JQ/AQ AD588BQ/KQ AD588ARWZ

Parameter

OUTPUT VOLTAGE ERROR

+10 V, −10 V Outputs

+5 V, −5 V Outputs

±5 V TRACKING MODE

Symmetry Error

OUTPUT VOLTAGE DRIFT

0°C to 70°C (J, K, B) ±2

−25°C to +85°C (A, B)

GAIN ADJ AND BAL ADJ2

Trim Range ±4

Input Resistance 150

LINE REGULATION

T

LOAD REGULATION

T

SUPPLY CURRENT

T

Power Dissipation 180

1

3

to T

MIN

MAX

to T

MIN

MAX

+10 V Output, 0 mA < I

−10 V Output, −10 mA < I

to T

MIN

6

MAX

Min Typ Max Min Typ Max Min Typ Max Unit

< 10 mA

OUT

< 0 mA

OUT

±3 −1 +1 −5 +5

±3 −1 +1 −5 +5

±1.5 ±0.75

±3

±3

±200

±4

150

±1.5

±3

±200

±50 ±50

±50 ±50

10

300

6

180

10

300

±2

±4

±1.5

±3

±3

150 kΩ

6

180

±200

±50

±50

10

300

mV

mV

mV

ppm/°C

ppm/°C

mV

μV/V

μV/mA

μV/mA

mA

mW

OUTPUT NOISE (Any Output)

0.1 Hz to 10 Hz 6 6 6 μV p-p

Spectral Density, 100 Hz 100 100 100 nV/√Hz

LONG-TERM STABILITY (@ 25°C) 15 15 15 ppm/1000 hr

BUFFER AMPLIFIERS

Offset Voltage 100 10 100 μV

Offset Voltage Drift 1 1 1 μV/°C

Bias Current 20 20 20 nA

Open-Loop Gain 110 110 110 dB

Output Current (A3, A4) −10 +10 −10 +10 −10 +10 mA

Common-Mode Rejection (A3, A4)

VCM = 1 V p-p 100 100 100 dB

Short Circuit Current 50 50 50 mA

TEMPERATURE RANGE

Specified Performance

J, K Grades 0 70 0 70 °C

A, B Grades −25 +85 −25 +85 −25 +85 °C

1

Specifications tested using ±5 V configuration, unless otherwise indicated. See Figure 4 through Figure 6 for output configurations at +10 V, −10 V, +5 V, −5 V

and ±5 V.

2

Gain and balance adjustments guaranteed capable of trimming output voltage error and symmetry error to zero.

3

For ±10 V output, ±VS can be as low as ±12 V. See Table 3 for test conditions at various voltages.

Rev. G | Page 3 of 20

AD588

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

+VS to −VS 36 V

Power Dissipation (25°C) 600 mW

Storage Temperature Range −65°C to +150°C

Lead Temperature (Soldering 10 sec) 300°C

Package Thermal Resistance (θ

Output Protection

Table 3. Test Conditions

Voltage Conditions

+10 V Output −VS = –15 V, +13.5 V ≤ +VS ≤ +18 V

−18 V ≤ –VS ≤ –13.5 V, +VS = +15 V −10 V Output

±5 V Output +VS = +18 V, –VS = –18 V

+V

= +10.8 V, −VS = −10.8 V

S

) 90°C/25°C/W

JA/θJC

All outputs safe if

shor

ted to ground

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. G | Page 4 of 20

AD588

A

www.BDTIC.com/ADI

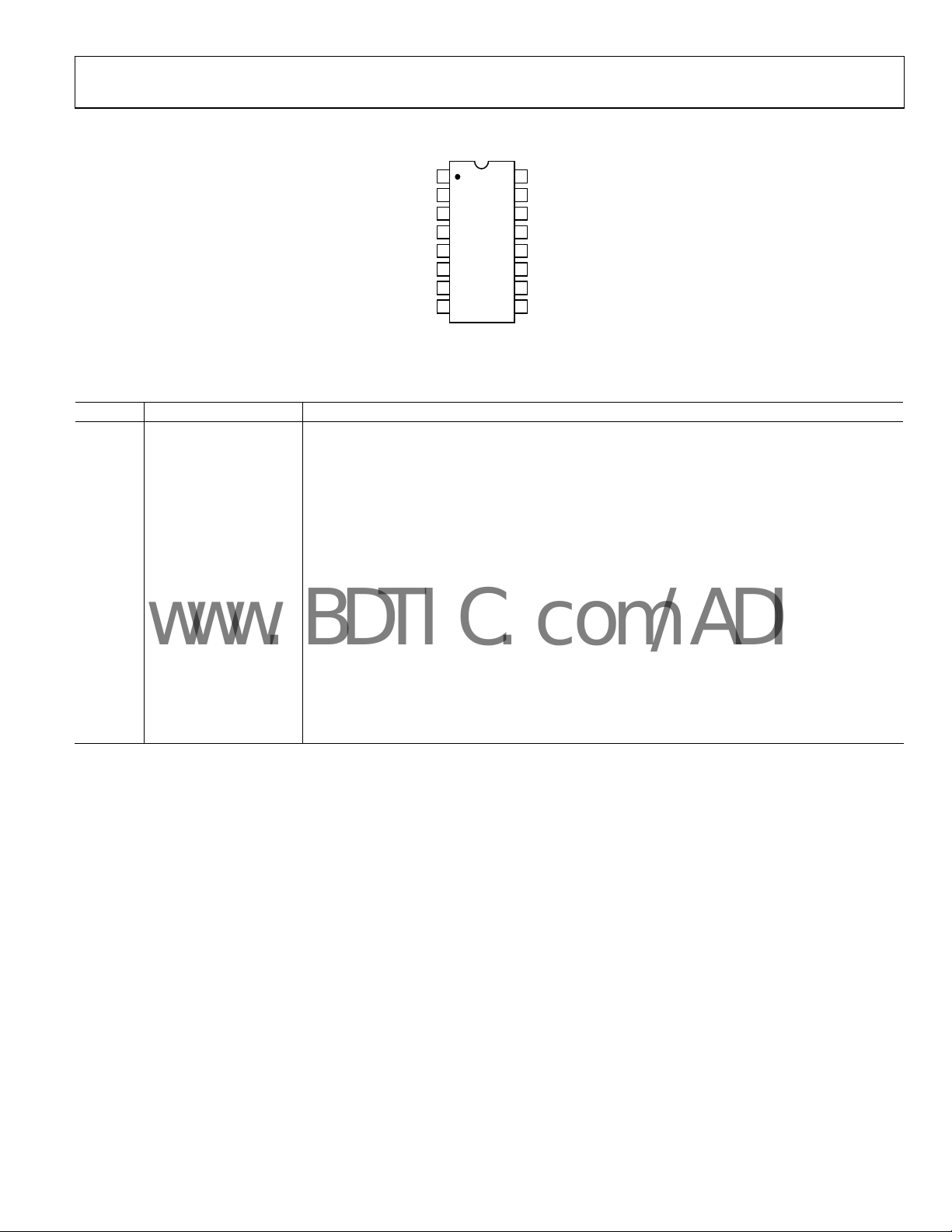

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

3 OUT FORCE

+V

A3 OUT SENSE

A3 IN

GAIN ADJ

V

HIGH

NOISE

REDUCTION

V

LOW

1

2

S

3

4

5

6

7

8

AD588

TOP VIEW

(Not to Scale)

16

–V

S

15

A4 OUT F ORCE

14

A4 OUT SENSE

13

A4 IN

12

BAL ADJ

11

V

CT

10

GND SENSE –IN

9

GND SENSE +IN

00531-002

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 A3 OUT FORCE Output from Buffering Amplifier 3 with Kelvin Force. Connect to Pin 3.

2 +VS Positive Power Supply.

3 A3 OUT SENSE

4 A3 IN

5 GAIN ADJ

6 V

Unbuffered Reference High Output.

HIGH

7 NOISE REDUCTION

Output from Buffering Amplifier 3 with Kelvin Sense. Connect to Pin 1.

+ Input to Amplifier 3. Connect to V

HIGH

, Pin 6.

Reference Gain Adjustment for Calibration. See the Calibration section.

Noise Filtering Pin. Connect external 1 μF capacitor to ground to reduce the output noise

(see the Noise Performance and Reduction section). Can be left open.

8 V

9 GND SENSE POSITIVE IN

10 GND SENSE NEGATIVE IN

11 V

12 BAL ADJ

13 A4 IN

14 A4 OUT SENSE

15 A4 OUT FORCE

16 −V

Unbuffered Reference Low Output.

LOW

+ Input to the Ground Sense Amplifier.

− Input to the Ground Sense Amplifier.

Center Tap Voltage used for Calibration. See the Calibration section.

CT

Reference Centering Adjustment for Calibration. See the Calibration section.

+ Input to Amplifier 4. Connect to V

LOW

, Pin 8.

Output of Buffering Amplifier 4 with Kelvin Sense. Connect to Pin 15.

Output of Buffering Amplifier 4 with Kelvin Force. Connect to Pin 14.

Negative Power Supply.

S

Rev. G | Page 5 of 20

AD588

A

www.BDTIC.com/ADI

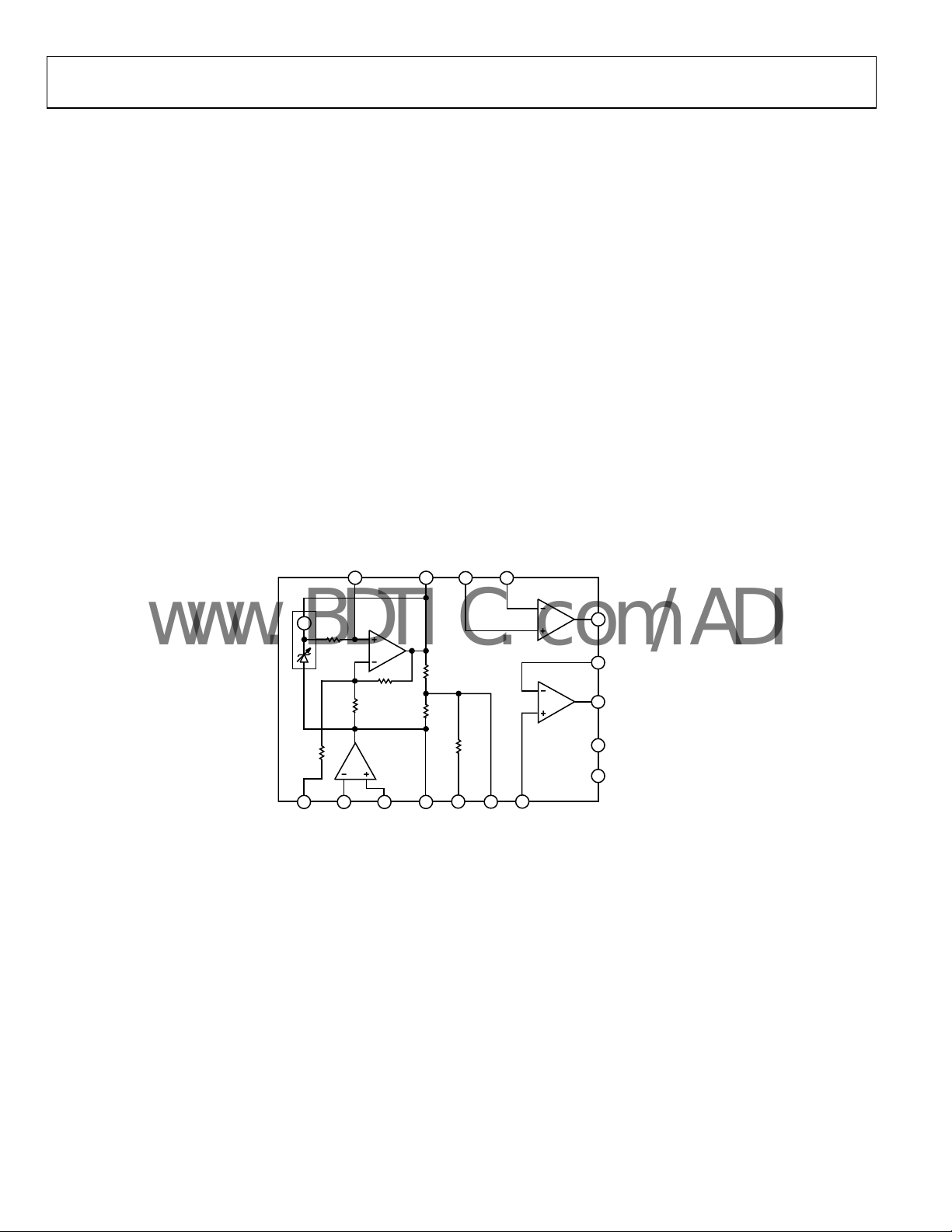

THEORY OF OPERATION

The AD588 consists of a buried Zener diode reference,

mplifiers used to provide pin programmable output ranges,

a

and associated thin-film resistors, as shown in Figure 3. The

t

emperature compensation circuitry provides the device with

a temperature coefficient of 1.5 ppm/°C or less.

Amplifier A1 performs several functions. A1 primarily acts to

a

mplify the Zener voltage from 6.5 V to the required 10 V

output. In addition, A1 provides for external adjustment of the

10 V output through Pin 5, GAIN ADJ. Using the bias

compensation resistor between the Zener output and the

noninverting input to A1, a capacitor can be added at the

NOISE REDUCTION pin (Pin 7) to form a low-pass filter and

reduce the noise contribution of the Zener to the circuit. Two

matched 10 kΩ nominal thin-film resistors (R4 and R5) divide

the 10 V output in half. Pin V

(Pin 11) provides access to the

CT

center of the voltage span and BAL ADJ (Pin 12) can be used

for fine adjustment of this division.

NOISE

REDUCTION

V

HIGH

Ground sensing for the circuit is provided by Amplifier A2. The

noninverting input (Pin 9) senses the system ground, which is

transferred to the point on the circuit where the inverting input

(Pin 10) is connected. This can be Pin 6, Pin 8, or Pin 11. The

output of A2 drives Pin 8 to the appropriate voltage. Thus, if

Pin 10 is connected to Pin 8, the V

pin is the same voltage as

LOW

the system ground. Alternatively, if Pin 10 is connected to the

V

pin, it is a ground; and Pin 6 and Pin 8 are +5 V and −5 V,

CT

respectively.

Amplifier A3 and Amplifier A4 are internally compensated and

a

re used to buffer the voltages at Pin 6, Pin 8, and Pin 11, as well

as to provide a full Kelvin output. Thus, the AD588 has a full

Kelvin capability by providing the means to sense a system

ground and provide forced and sensed outputs referenced to

that ground.

Note that both positive and negative supplies are required for

o

peration of the AD588.

3 OUT

A3 IN

SENSE

3467

1

14

15

2

16

A3 OUT

FORCE

A4 OUT

SENSE

A4 OUT

FORCE

+V

S

–V

S

00531-003

GAIN

ADJ

R

B

A1

R1

R2

R3

A2

GND

GND

SENSE

SENSE

+IN

–IN

Figure 3. AD588 Functional Block Diagram

R4

R5

R6

BAL

ADJ

V

CT

V

LOW

A3

A4

AD588

13111281095

A4 IN

Rev. G | Page 6 of 20

Loading...

Loading...