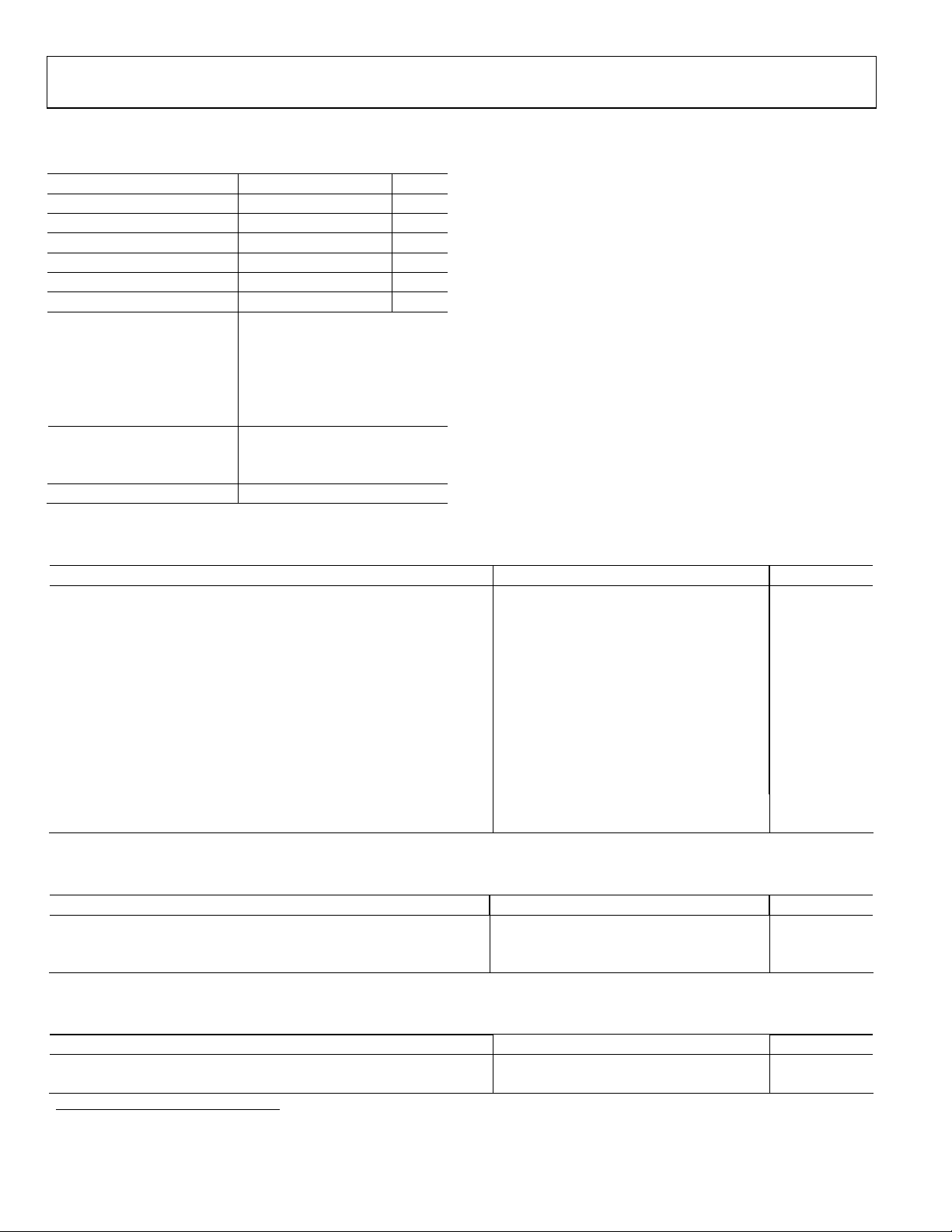

AC ’97 SoundMAX® Codec

AC ’97 2.3 COMPLIANT FEATURES

6 DAC channels for 5.1 surround

Greater than 90 dB dynamic range

20-bit resolution on all DACs

S/PDIF Output

Integrated stereo headphone amplifiers

Variable rate audio

MZ

M

MZ

HP

HP

OMSOMS

MZ

MZ A

A

A

A

M

M

= 96 kHz)

S

G

2CMIC

G

CD

DIFF AMP

A

SPRD

SPRD

LOSELLOSEL MIX

A

HPSELHPSEL

A

MS

AD1985

GA

MMM

GA

M

Σ

Σ

M

G = GAIN

A = ATTENUATION

M = MUTE

Z = HIGH Z

FUNCTIONAL BLOCK DIAGRAM

GA

GA

M

M

GA

M

GA

M

MGAM

GA

Σ

M

Double rate audio (f

Line-level mono phone input

High quality CD mixer input

Selectable MIC input with preamp

AUX and line in stereo inputs

External amplifier power down (EAPD)

Power management modes

Jack sensing and peripheral enumeration/identification

48-lead LQFP package

MIC1

MIC2

PHONE_IN

CD_L

CD_GND

CD_R

AUX_L

AUX_R

LINE_IN_L

LINE_IN_R

LFE_OUT

CENTER_OUT

LINE_OUT_L

MONO_OUT

LINE_OUT_R

SURR_OUT_L/

HP_OUT_L

SURR_OUT_R/

HP_OUT_R

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

MGAM

Figure 1.

AD1985

ENHANCED FEATURES

Integrated parametric equalizer (EQ)

Stereo microphone with preamplifiers

Integrated PLL for system clocking

Variable sample rate 7 kHz to 96 kHz

7 kHz to 48 kHz in 1 Hz increments

96 kHz for double rate audio

Advanced jack sense with auto topology switching

Software enabled V

power amp

Software enabled outputs for jack sharing

Auto down-mix and channel spreading

Microphone to mono output

Stereo microphone analog passthrough to outputs

Built-in stereo microphone and Center/LFE pin sharing

Selectable Center/LFE tip/ring swapping to support various

speaker products

G

Z

PCM L/R

ADC RATE

16-BIT

Σ-∆ ADC

16-BIT

Σ-∆ ADC

PCM C/LFE

DAC RATE

20-BIT

Σ-∆ DAC

20-BIT

Σ-∆ DAC

PC BEEP

GENERAT OR

PCMFRONT

DAC RATE

20-BIT

Σ-∆ DAC

20-BIT

Σ-∆ DAC

20-BIT

Σ-∆ DAC

20-BIT

Σ-∆ DAC

PCM SURR

DAC RATE

V

REF

CODEC CORE

V

REFOUT

M

G

M

MGA

M

M

M

M

M

MG

GA

A

GA

GA

GA

GA

RECORD

SELECTOR

M

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

for microphones and external

REFOUT

XTL_OUT XTL_IN SPDIF_OUT

VOLTAGE

REFERENCE

PLL

ADC

SLOT

LOGIC

DAC

SLOT

LOGIC

CSWP CSWP

EQ

BYPASS

EQ

BYPASS

EAPD

EAPD

EQ COEF STORAGE

AC '97

CONTROL

REGISTERS

ANALOGMIXING

CONTROL

JACK SENSE

JS0 JS1 JS2

SPDIF

TX

AC '97 INTERFACE V2.3

ID0

ID1

RESET

SYNC

BITCLK

SDATA_OUT

SDATA_IN

JS3

03610-A-001

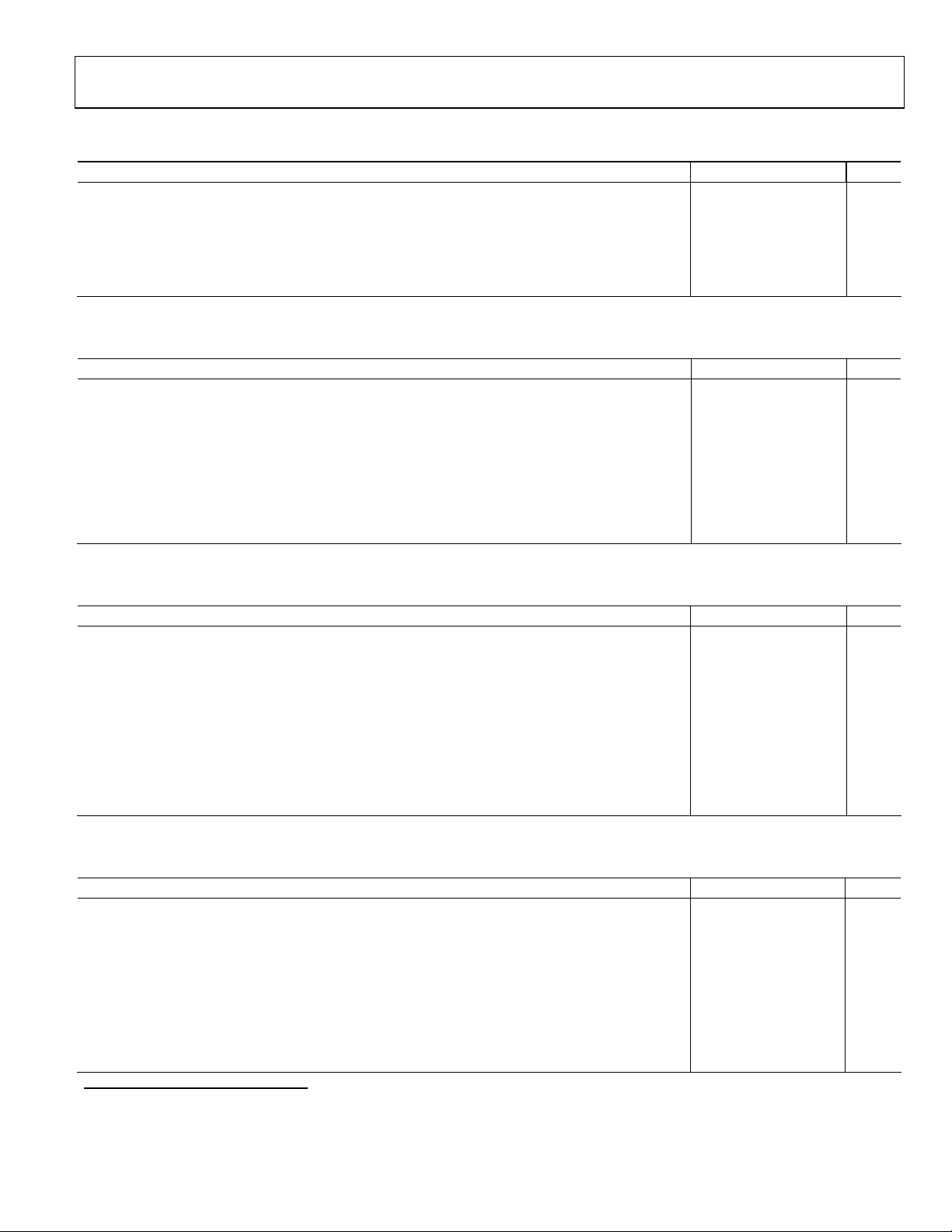

AD1985

TABLE OF CONTENTS

Detailed Functional Block Diagram .............................................. 3

Specifications..................................................................................... 4

Analog Input................................................................................. 4

Master Volume.............................................................................. 4

Programmable Gain Amplifier—ADC...................................... 4

Analog Mixer—Input Gain/Amplifiers/Attenuators............... 5

Digital Decimation and Interpolation Filters ........................... 5

Analog-to-Digital Converters..................................................... 5

Digital-to-Analog Converters..................................................... 5

Analog Output.............................................................................. 6

Static Digital Specifications......................................................... 6

Power Supply................................................................................. 6

Power-Down States ...................................................................... 7

Clock Specifications ..................................................................... 7

Timing Parameters....................................................................... 8

Absolute Maximum Ratings.......................................................... 10

Environmental Conditions........................................................ 10

ESD Caution................................................................................ 10

Pin Configuration and Functional Descriptions........................ 11

REVISION HISTORY

3/04—Data Sheet changed from Rev. 0 to Rev. A

Updated Format.................................................................Universal

Changes to Figure 1......................................................................... 1

Changes to Figure 2......................................................................... 3

Changes to Table 4........................................................................... 4

Changes to Tables 5, 7, and 8.......................................................... 5

Changes to Table 12 ........................................................................ 7

Changes to Pin Configuration..................................................... 11

Changes to Circuit Layout Note ..................................................11

Changes to Indexed Control Registers....................................... 13

Changes to Master Volume Register (Index 0x02).................... 15

Changes to Headphone Volume Register (Index 0x04) ...........16

Changes to Mono Volume Register (Index 0x06) ..................... 17

Changes to PC Beep Register (Index 0x0A) .............................. 18

Changes to Microphone Volume Register (Index 0x0E).......... 19

Changes to AUX In Volume Register (Index 0x16).................. 21

Changes to Record Select Control Register (Index 0x1A)....... 22

Changes to Record Gain Register (Index 0x1C) ....................... 23

Changes to Extended Audio ID Register (Index 0x28)............ 27

Changes to Center/LFE Volume Control

Register (Index 0x36).................................................................... 30

Changes to Surround Volume Control Register

(Index 0x38) ................................................................................... 31

Changes to Jack Sense/Audio Interrupt/Status Register

(Index 0x72) ................................................................................... 36

Changes to Miscellaneous Control Bits (Index 0x76) ..............39

Changes to Advanced Jack Sense Register (Index 0x78).......... 41

Updated Outline Dimensions...................................................... 47

Updated Ordering Guide.............................................................. 47

Pin Descriptions ......................................................................... 11

Indexed Control Registers......................................................... 13

Outline Dimensions....................................................................... 47

Ordering Guide........................................................................... 47

Rev. A | Page 2 of 48

3/03—Revision 0: Initial Version

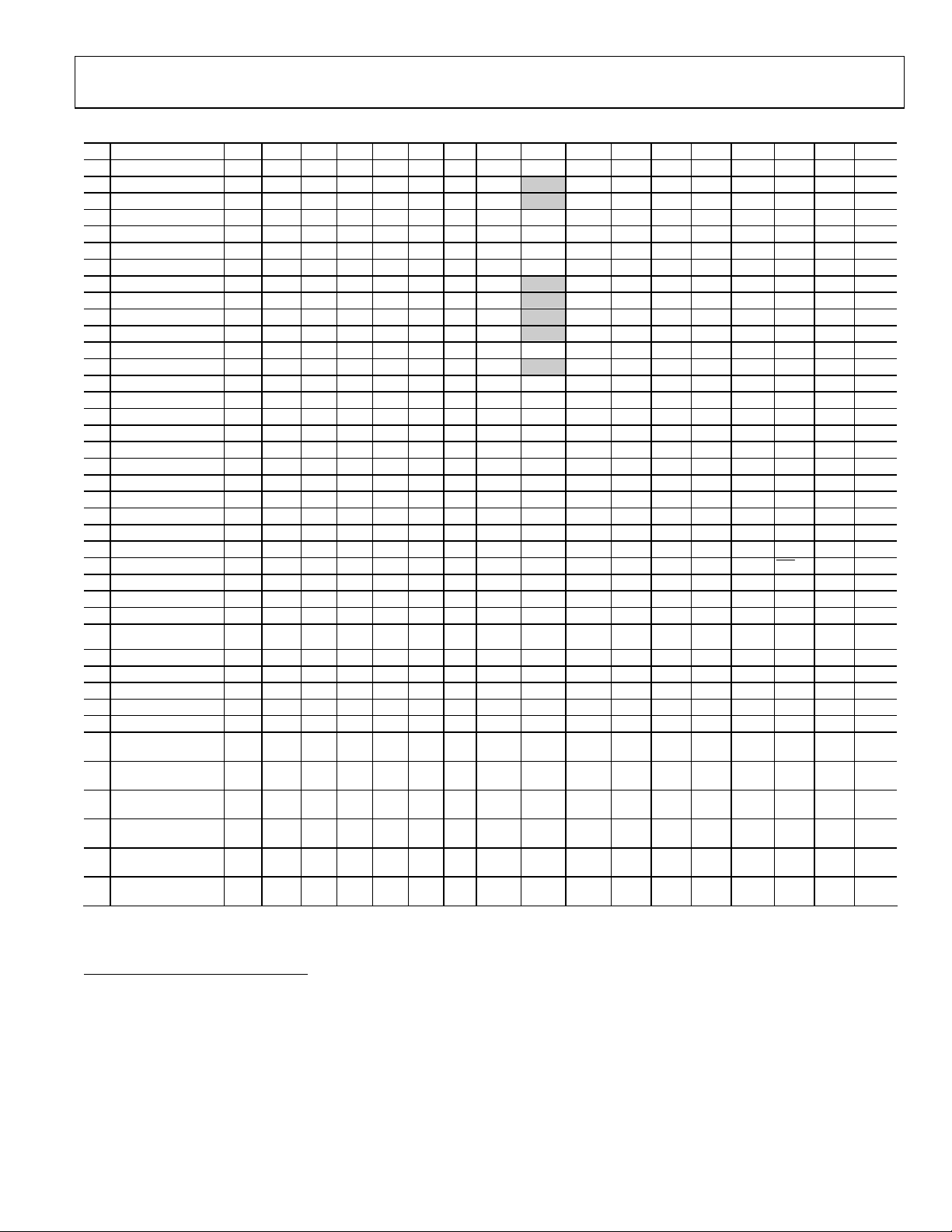

AD1985

T

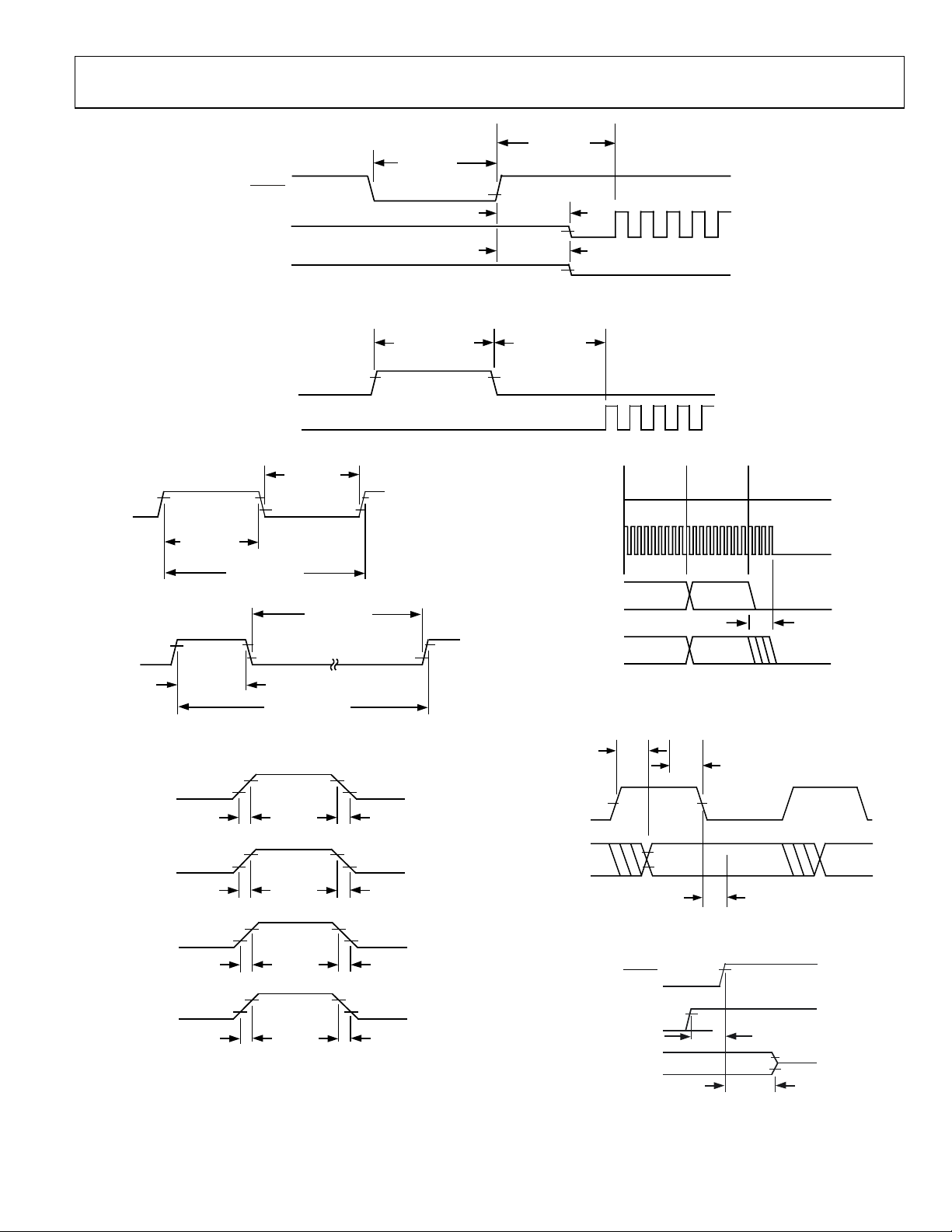

DETAILED FUNCTIONAL BLOCK DIAGRAM

ID0

ID1

RESET

TX

SPDIF

SYNC

BITCLK

SDATA_OU

SDATA_IN

JS3

AC '97 INTERFACE V2.3

EQ COEF STORAGE

AC '97

CONTROL

REGISTERS

JSENSE: 0x72

DEF=0x0000

CONTROL

JACK SENSE

ANALOG MIXING

JS0 JS1 JS2

VREFOUT: 0x76 D3-D2

DEF=00 (+2.25V)

00= +2.25V

01= HIGH Z

2CMIC: 0x76 D7

DEF=0 (MS Sel)

OMS: 0x74 D9

DEF=0(MIC_1/2)

XTL_OUT XTL_IN SPDIF_OUT

VOLTAGE

+2.25V

REF

V

G

Z

10= +3.7V

11= 0V

REFOUT

V

AD1985

MS: 0x20 D8

DEF=0 (MIC_1)

MGB[1:0]: 0x76 D1-D0

DEF=0 (+20dB)

M20: 0x0E D6

DEF=0 (0dB Gain)

010

REFERENCE

CODEC CORE

REC SELECTOR

MS

2CMIC

00= +20dB Gain

01= +10dB Gain

10= +30dB Gain

11 (reserved)

G

G

OMSOMS

1

ADC

PLL

PCM ADC RATE: 0x32

SLOT

7kHz-48kHz in 1Hz steps

DEF 0xBB80 48kHz

16-BIT

Σ-∆ ADC

M

Left

G

REC GAIN: 0x1C

0dB to +22.5dB

DEF=0x8000 0dB/MUTED

0x1A

D2-D0 RIGHT

D10-D8 LEFT

DEF=0x000

000= MIC

001= CD

CD

DIFF AMP

LOGIC

16-BIT

Σ-∆ ADC

M

G

010= ---

011= AUX

100= LINE_IN

Right

101= STR_MIX

110= MON_MIX

111= PHONE

DAC

SLOT

DSA: 0x28

D5-D4

DEF 00

LOGIC

1

0

CSWPCSWP

PCM C/LFE DAC RATE: 0x30

7kHz-48kHz in 1Hz steps

DEF 0xBB80 48kHz

20-BIT

Σ-∆ DAC

GAMGA

LFE Right

AC97 MODE: 0x18

M

ADI MODE: PCM VOL 0x36

+12dB to -34.5dB

DEF 0x8808 0dB/MUTED

LINE_IN VOL: 0x10 +12 to -34.5dB

DEF=0x8808 0dB/MUTED

0

DOWN MIX: 0x76

MIC VOL: 0x0E

DOWN MIX: 0x76

1

A

SPRD: 0x76 D6

DEF=0 (NoSprd)

MZ

LFE Right

1

0

20-BIT

Σ-∆ DAC

Center Left

DMIX 1,0 (D9,D8)

DEF=0x0 (MUTED)

GA

GA

GA

+12 to -34.5dB

DEF=0x8808

0dB/MUTED

GA

GA

DMIX 1,0 (D9,D8)

DEF=0x0 (MUTED)

0

1

SPRD

SPRD

A

MZ

CSWP: 0x74 D3

DEF=0 (NoCSwp)

M

M

M

GA

M

GA

M

GA

M

GA

MMM

LOSEL: 0x76 D5

Center Left

M

AUX VOL: 0x16

M

M

M

AUX VOL: 0x16

1

0

LOSELLOSEL MIX

A

DEF=0 (Mixer)

Left

MZ

PCBeep: 0x0A Vol: D4-D0

Mute: D15

Frequency: D12-D5

+0 to -45dB

DEF=0x8000 0dB/MUTED

+12 to -34.5dB

DEF=0x8808

0dB/MUTED

PHONE VOL: 0x0C

+12 to -34.5dB

DEF=0x8008

0dB/MUTED

CD VOL: 0x012 +12 to -34.5dB

+12 to -34.5dB

DEF=0x8808

0dB/MUTED

1

MIX: 0x20 D9

DEF=0 (Mixer)

EQ

0

EQB: 0x72 D9-D8

DEF=0 (EQ Enabled)

PC BEEP

GENERATOR

PCM FRONT DAC RATE: 0x2C

7kHz-48kHz in 1Hz steps

DEF 0xBB80 48kHz

A

M

PCM VOL: 0x18

+12dB to -34.5dB

DEF 0x8808 0dB/MUTED

DEF=0x8008 0dB/MUTED

0

1

A

M

LOSEL: 0x76 D5

DEF=0 (Mixer)

A

MZ

1

BYPASS

20-BIT

Σ-∆ DAC

Left

MGAM

Σ

0

Right

EAPD

EAPD

EQ

0

1

BYPASS

EQB

20-BIT

Σ-∆ DAC

GA

Right

20-BIT

PCM SURR DAC RATE: 0x2E

7kHz-48kHz in 1Hz steps

DEF 0xBB80 48kHz

AC97 MODE: 0x18

ADI MODE: PCM VOL 0x38

+12dB to -34.5dB

DEF 0x8808 0dB/MUTED

Σ

DOWN MIX: 0x76

DMIX 1,0 (D9,D8)

DEF=0x0 (MUTED)

Σ-∆ DAC

MGAM

M

20-BIT

Σ-∆ DAC

GA

EAPD: 0x26 D15

DEF=0 (Enabled)

M

G = GAIN

A = ATTENUATION

M = MUTE

0

A

Right

M

HP

Z = HIGH Z

HPSEL: 0x76 D10

DEF=0 (Surround)

HP STBY: PR6

reg 0x26 D14

1=power down, DEF=0

Σ

1

0

1

HPSELHPSEL

A

Left

M

HP

MIC1

MIC2

CD_L

CD_R

AUX_L

PHONE_IN

CD_GND

AUX_R

LINE_IN_L

LINE_IN_R

LFE_OUT

AC97 MODE: C&LFE VOL 0x36

ADI MODE: MASTER VOL 0x02

0dB to -46.5dB

DEF 0x8000 0dB/MUTED

OMS: 0x74 D9

DEF=0(MIC_1/2)

CLDIS:0x76 D11

DEF=0(enabled)

CENTER_OUT

LODIS:0x76 D12

LINE_OUT_L

LINE_OUT: MASTER VOL 0x02

0dB to -46.5dB

DEF=0x8000 0dB/MUTED

DEF=0 (enabled)

MONO_OUT

MONO_OUT: MONO VOL 0x06

0dB to -46.5dB

DEF=0x8000 0dB/MUTED

LODIS:0x76 D12

LINE_OUT_R

LINE_OUT: MASTER VOL 0x02

0dB to -46.5dB

DEF=0x8000 0dB/MUTED

DEF=0 (enabled)

AC97 MODE: SURR VOL 0x38

ADI MODE: HEADPHONE VOL 0x04

0dB to -46.5dB

DEF 0x8000 0dB/MUTED

Note: Setting to enable Surround 5.1 is LOSEL=1

HP_OUT_L

SURR_OUT_L/

HP_OUT_R

SURR_OUT_R/

03610-A-002

Figure 2. Detailed Functional Block Diagram

Rev. A | Page 3 of 48

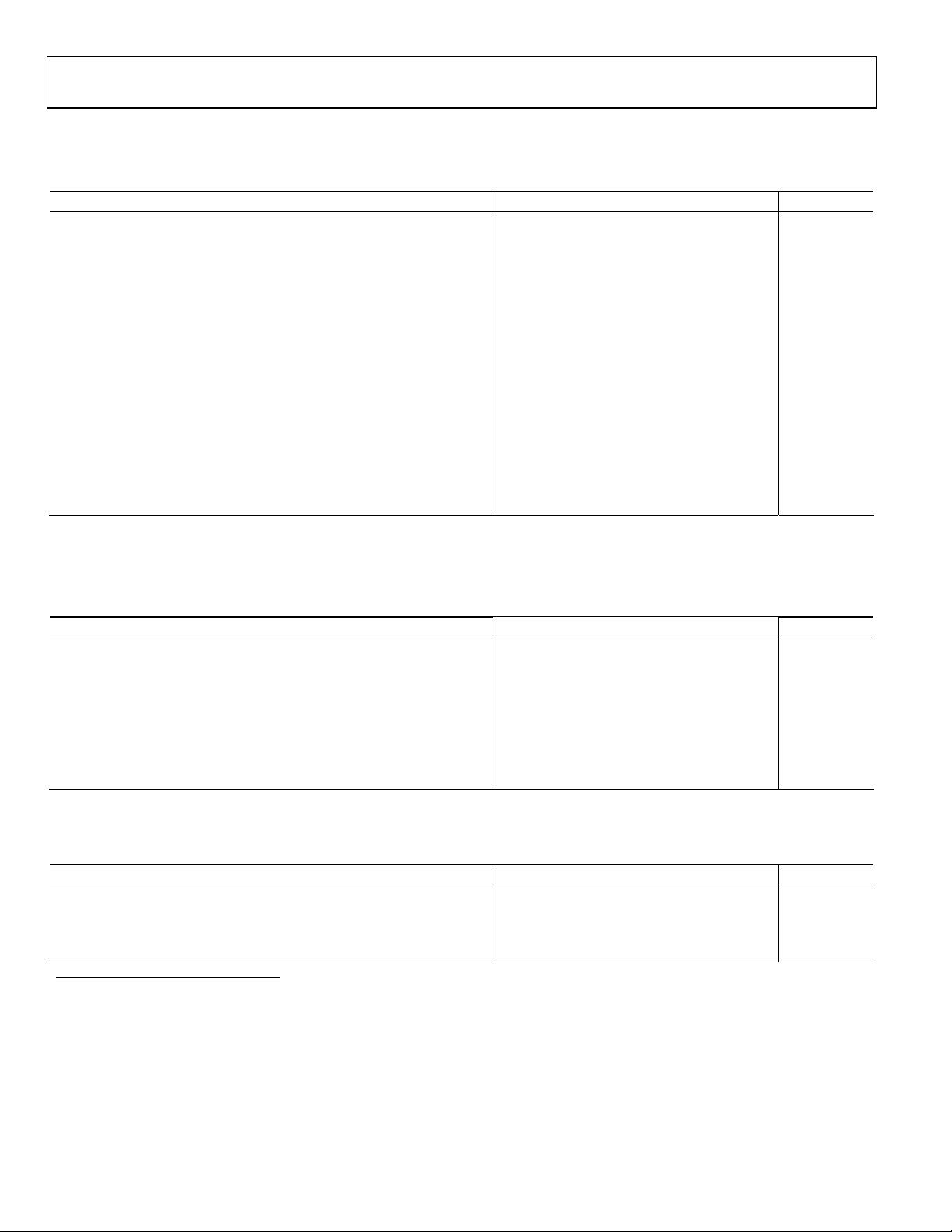

AD1985

SPECIFICATIONS

Table 1. Test Conditions, Unless Otherwise Noted

Parameter Value/Condition Unit

TEMPERATURE 25 °C

DIGITAL SUPPLY (DVDD) 3.3 V

ANALOG SUPPLY (AVDD) 5.0 V

SAMPLE RATE (fS) 48 kHz

INPUT SINE WAVE SIGNAL 1,008 Hz

ANALOG OUTPUT PASS BAND 20 to 20,000 Hz

DAC TEST CONDITIONS

ADC TEST CONDITIONS

CLOCK 24.576 MHz

ANALOG INPUT

Table 2.

Parameter Min Typ Max Unit

INPUT VOLTAGE

LINE_IN, CD, AUX, PHONE_IN 1 V rms

2.83 V p-p

MIC_IN with +30 dB Preamp 0.032 V rms

0.089 V p-p

MIC_IN with +20 dB Preamp 0.1 V rms

0.283 V p-p

MIC_IN with +10 dB Preamp 0.316 V rms

0.894 V p-p

MIC_IN with 0 dB Preamp 1 V rms

2.83 V p-p

Input Impedance1 20 kΩ

Input Capacitance1 5 7.5 pF

MASTER VOLUME

Table 3.

Parameter Min Typ Max Unit

STEP SIZE (LINE OUT, MONO OUT, SURROUND OUT, CENTER, LFE) 1.5 dB

OUTPUT ATTENUATION RANGE (0 dB TO −46.5 dB) 46.5 dB

MUTE ATTENUATION OF 0 dB FUNDAMENTAL1 80 dB

PROGRAMMABLE GAIN AMPLIFIER—ADC

Table 4.

Parameter Min Typ Max Unit

STEP SIZE (0 dB TO +22.5 dB) 1.5 dB

PGA GAIN RANGE 22.5 dB

1

Guaranteed, not tested.

Calibrated

Output –3 dB relative to full scale

10 kΩ output load: line

32 Ω output load: headphone

2 kΩ output load: center and LFE

47.5 kΩ output load: mono

Calibrated

0 dB PGA gain

Input –3 dB relative to full scale

Rev. A | Page 4 of 48

AD1985

ANALOG MIXER—INPUT GAIN/AMPLIFIERS/ATTENUATORS

Table 5.

Parameter Min Typ Max Unit

SIGNAL-TO-NOISE RATIO (SNR)

CD to LINE_OUT 90 dB

LINE, AUX, PHONE, to LINE_OUT 85 dB

MIC1 or MIC2 to LINE_OUT 80 dB

Step Size: All Mixer Inputs, Except PC Beep 1.5 dB

Input Gain/Attenuation Range (+12 dB to –34.5 dB): All Mixer Inputs, Except PC Beep 46.5 dB

DIGITAL DECIMATION AND INTERPOLATION FILTERS1

Table 6.

Parameter Min Typ Max Unit

PASS BAND 0 0.4 × fS Hz

PASS-BAND RIPPLE ±0.09 dB

TRANSITION BAND

STOP BAND

0.4 ×

f

S

0.6 ×

f

S

0.6 × f

∞ Hz

STOP-BAND REJECTION –74 dB

GROUP DELAY 16/fS s

GROUP DELAY VARIATION OVER PASS BAND 0 µs

ANALOG-TO-DIGITAL CONVERTERS

Table 7.

Parameter Min Typ Max Unit

RESOLUTION 16 Bits

TOTAL HARMONIC DISTORTION (THD) −85 dB

DYNAMIC RANGE (–60 dB IN; THD+N REFERENCED TO FULL-SCALE; A-WEIGHTED) 84 dB

SIGNAL-TO-INTERMODULATION DISTORTION (CCIF METHOD)1 85 dB

ADC CROSSTALK1

Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) −85 dB

LINE_IN to Other −95 dB

GAIN ERROR (FULL-SCALE SPAN RELATIVE TO NOMINAL INPUT VOLTAGE) ±10 %

INTERCHANNEL GAIN MISMATCH (DIFFERENCE OF GAIN ERRORS) ±0.5 dB

ADC OFFSET ERROR1 ±5 mV

DIGITAL-TO-ANALOG CONVERTERS

Table 8.

Parameter Min Typ Max Unit

RESOLUTION 20 Bits

TOTAL HARMONIC DISTORTION (THD); LINE_OUT, C/LFE –90 dB

TOTAL HARMONIC DISTORTION (THD); HP_OUT –75 dB

DYNAMIC RANGE (–60 dB IN; THD+N REFERENCED TO FULL-SCALE; A-WEIGHTED) 90 dB

SIGNAL-TO-INTERMODULATION DISTORTION (CCIF METHOD)1 100 dB

GAIN ERROR (OUTPUT FULL-SCALE VOLTAGE RELATIVE TO NOMINAL OUTPUT FULL-SCALE VOLTAGE)2 ±10 %

INTERCHANNEL GAIN MISMATCH (DIFFERENCE OF GAIN ERRORS) ±0.7 dB

DAC CROSSTALK (INPUT L, ZERO R, READ R_OUT; INPUT R, ZERO L, READ L_OUT)1 –100 dB

TOTAL OUT-OF-BAND ENERGY (MEASURED FROM 0.6 × fS TO 100 KHZ)1 –85 dB

Hz

S

1

Guaranteed, not tested.

2

C/LFE specified with 10 kΩ load.

Rev. A | Page 5 of 48

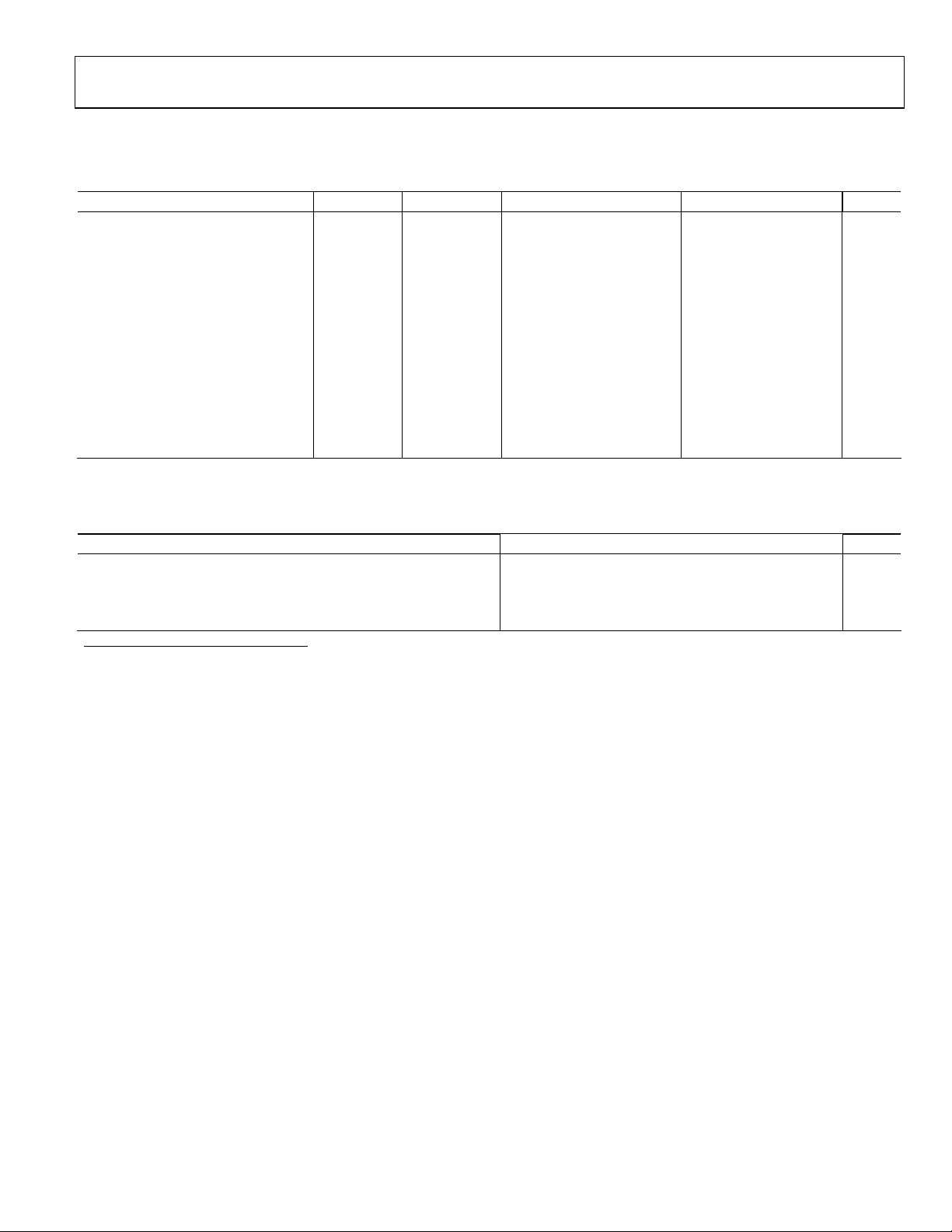

AD1985

ANALOG OUTPUT

Table 9.

Parameter Min Typ Max Unit

FULL-SCALE OUTPUT VOLTAGE: LINE OUT, MONO OUT, CENTER, LFE 1 V rms

2.83 V p-p

Output Impedance1 300 500 Ω

External Load Impedance1 2 10 kΩ

Output Capacitance1 15 pF

External Load Capacitance 1000 pF

FULL-SCALE OUTPUT VOLTAGE: HP_OUT 1 V rms

2.83 V p-p

External Load Capacitance1 1000 pF

External Load Impedance1 32 Ω

V

2.1 2.25 2.4 V

REF

V

(VREFH, VREFD = 00 in REGISTER 0x76) 2.25 V

REFOUT

V

(VREFH, VREFD = 10) 3.70 V

REFOUT

V

(VREFH, VREFD = 11) 0.0 V

REFOUT

V

CURRENT DRIVE 5 mA

REFOUT

MUTE CLICK (MUTED OUTPUT UNMUTED MIDSCALE DAC OUTPUT) ±5 mV

Note that setting V

with a stereo microphone application circuit.

to 0 V reduces crosstalk when Center/LFE is sharing the MIC jack. The Center/LFE crosstalk should be better than −60 dB at 100 Hz when sharing

REFOUT

STATIC DIGITAL SPECIFICATIONS

Table 10.

Parameter Min Typ Max Unit

DIGITAL INPUTS/OUTPUTS

High Level Input Voltage (VIH) 0.65 × DVDD V

Low Level Input Voltage (VIL) 0.35 × DVDD V

High Level Output Voltage (VOH), IOH = 2 mA 0.9 × DVDD V

Low Level Output Voltage (VOL), IOL = 2 mA 0.1 × DVDD V

INPUT LEAKAGE CURRENT –10 +10 µA

OUTPUT LEAKAGE CURRENT –10 +10 µA

INPUT/OUTPUT PIN CAPACITANCE 7.5 pF

POWER SUPPLY

Table 11.

Parameter Min Typ Max Unit

POWER SUPPLY RANGE—ANALOG (AVDD) 4.5 5.5 V

POWER SUPPLY RANGE—DIGITAL (DVDD) 2.97 3.63 V

POWER DISSIPATION—5 V/3.3 V 465 mW

POWER SUPPLY REJECTION (100 mV p-p SIGNAL @ 1 kHz)1 40 dB

1

Guaranteed, not tested.

Rev. A | Page 6 of 48

AD1985

POWER-DOWN STATES1

Table 12.

Parameter PR[K:I]

2

FULL POWER-UP 000 000 0000 55.5 56.0 mA

ADC 000 000 0001 47.4 49.9 mA

FRONT DAC 000 000 0010 49.5 47.9 mA

CENTER DAC 001 000 0000 55.5 56.0 mA

SURROUND DAC 010 000 0000 49.0 47.5 mA

LFE DAC 100 000 0000 55.1 56.0 mA

ADC + ALL DACs 111 000 0011 15.8 24.2 mA

MIXER 000 000 0100 55.5 34.3 mA

ADC + MIXER 000 000 0101 47.4 27.4 mA

ALL DACS + MIXER 111 000 0110 34.1 10.0 mA

ADC + ALL DACS + MIXER 111 000 0111 14.3 2.5 mA

STANDBY 111 011 1111 0.114 0.004 mA

HEADPHONE STANDBY 000 100 0000 55.5 48.3 mA

CLOCK SPECIFICATIONS

Table 13.

Parameter Min Typ Max Unit

INPUT CLOCK FREQUENCY (XTAL MODE OR CLOCK OSCILLATOR) 24.576 MHz

INPUT CLOCK FREQUENCY (REFERENCE CLOCK MODE) 14.31818 MHz

INPUT CLOCK FREQUENCY (USB CLOCK MODE) 48.000 MHz

RECOMMENDED CLOCK DUTY CYCLE 40 50 60 %

1

Currents measured with V

2

PR bits are controlled in Registers 0x2A and 0x26.

REFOUT

unloaded.

PR[6:0]

2

I DVDD (3.3 V) Typ I AVDD (5 V) Typ Unit

Rev. A | Page 7 of 48

AD1985

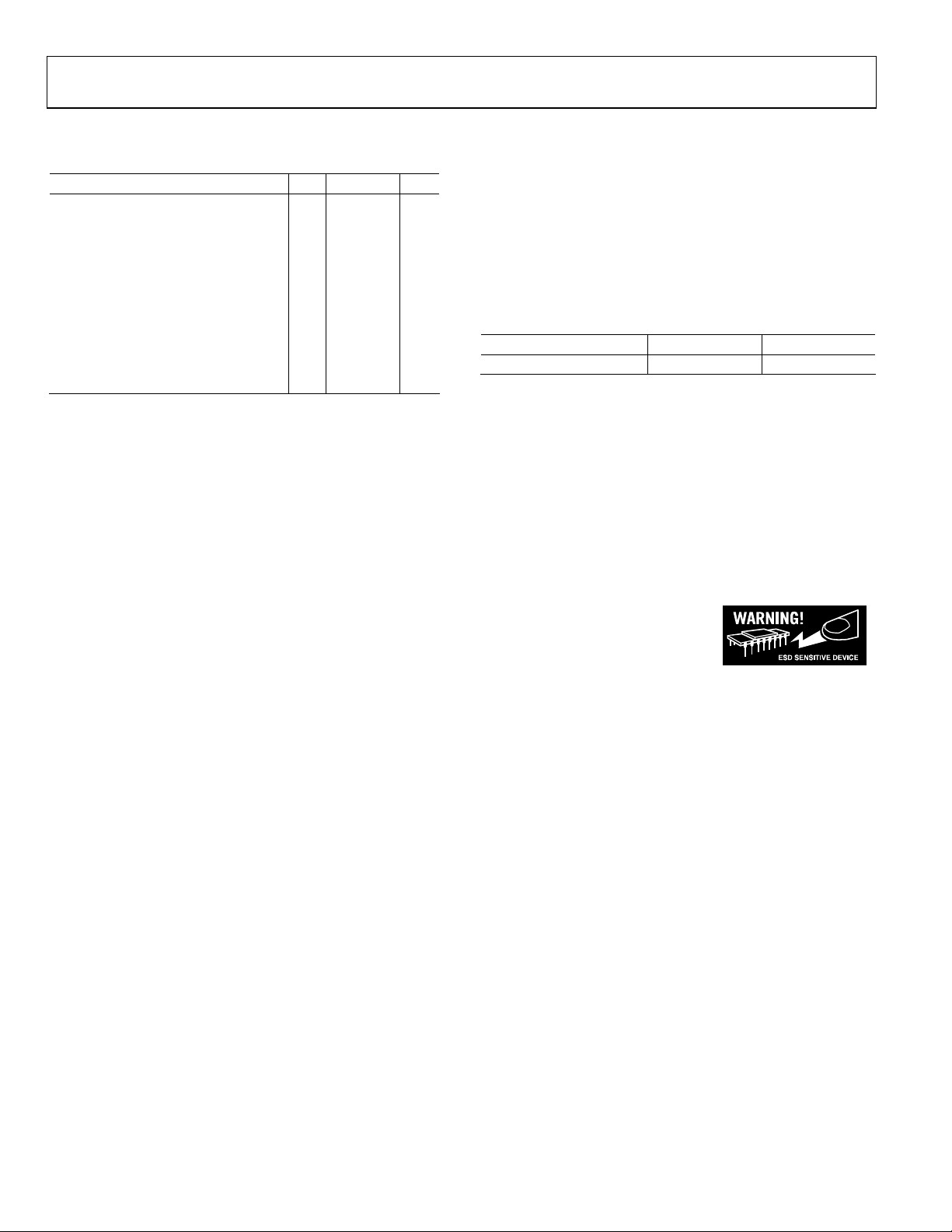

TIMING PARAMETERS

Guaranteed over operating temperature range.

Table 14.

Parameter Symbol Min Typ Max Unit

RESET ACTIVE LOW PULSE WIDTH

RESET INACTIVE TO SDATA_IN OR BIT_CLK ACTIVE DELAY

SYNC ACTIVE HIGH PULSE WIDTH t

SYNC LOW PULSE WIDTH t

SYNC INACTIVE TO BIT_CLK STARTUP DELAY t

BIT_CLK FREQUENCY

BIT_CLK PERIOD t

BIT_CLK OUTPUT JITTER

1, 2

BIT_CLK HIGH PULSE WIDTH t

BIT_CLK LOW PULSE WIDTH t

SYNC FREQUENCY

SYNC PERIOD t

SETUP TO FALLING EDGE OF BIT_CLK t

HOLD FROM FALLING EDGE OF BIT_CLK t

BIT_CLK RISE TIME t

BIT_CLK FALL TIME t

SYNC RISE TIME t

SYNC FALL TIME t

SDATA_IN RISE TIME t

SDATA_IN FALL TIME t

SDATA_OUT RISE TIME t

SDATA_OUT FALL TIME t

END OF SLOT 2 TO BIT_CLK, SDATA_IN LOW t

SETUP TO TRAILING EDGE OF RESET (APPLIES TO SYNC, SDATA_OUT)

RISING EDGE OF RESET TO HIGH-Z DELAY

t

RST_LOW

t

RST2CLK

SYNC_HIGH

SYNC_LOW

SYNC2CLK

CLK_PERIOD

CLK_HIGH

CLK_LOW

SYNC_PERIOD

SETUP

HOLD

RISECLK

FALLCLK

RISESYNC

FALLSYNC

RISEDIN

FALLDIN

RISEDOUT

FALLDOUT

S2_PDOWN

t

SETUP2RST

t

OFF

PROPAGATION DELAY 15 ns

RESET RISE TIME

50 ns

OUTPUT VALID DELAY FROM RISING EDGE OF BIT_CLK TO SDI VALID tCO 15 ns

RESET INACTIVE TO BIT_CLK STARTUP DELAY

t

TRI2ACTV

1.0

µs

162.8 ns

1.3

19.5

µs

µs

162.8 ns

12.288 MHz

81.4 ns

750 2000 ps

33 42 48 ns

33 38 48 ns

48.0 kHz

20.8

µs

10 2.5 ns

5 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

2 4 6 ns

0 1.0

µs

15.0 ns

25.0 ns

25 ns

1

Guaranteed, not tested.

2

Output jitter directly dependent on crystal input jitter; maximum specified for noncrystal operation.

Rev. A | Page 8 of 48

AD1985

T

T

,

t

RST2CLK

t

RST_LOW

RESET

t

BIT_CLK

SDATA_IN

Figure 3. Cold Reset Timing (Codec is Supplying the Bit_CLK Signal)

TRI2ACTV

t

TRI2ACTV

03610-0-003

BIT_CLK

SYNC

SDATA_IN

BIT_CLK

SYNC

t

CLK_HIGH

t

SYNC_HIGH

t

RISECLK

t

RISESYNC

t

RISEDIN

SYNC

BIT_CLK

t

CLK_LOW

t

CLK_PERIOD

t

SYNC_LOW

t

SYNC_PERIOD

Figure 5. Clock Timing

t

SYNC_HIGH

Figure 4. Warm Reset Timing

03610-0-005

t

FALLCLK

t

FALLSYNC

t

FALLDIN

t

SYNC2CLK

BIT_CLK

SDATA_OU

SDATA_IN

SLOT 1 SLOT 2

SYNC

BIT_CLK

SDATA_OU

WRITE TO

03 26

SDATA_IN

BIT_CLK NOT TO SCALE

Figure 7. AC Link Low Power Mode Timing

t

CO

V

IH

SYNC

Figure 8. AC Link Low Power Mode Timing

RESET

V

OH

V

OL

t

HOLD

t

SETUP

03610-0-004

DATA

PR4

V

IL

t

S2_PDOWN

03610-0-007

03610-0-008

SDATA_OUT

SDATA_OUT

t

RISEDOUT

Figure 6. Signal Rise and Fall Times

t

FALLDOUT

03610-0-006

SDATA_IN, BIT_CLK

EAPD, SPDIF_OUT

AND DIGITAL I/O

t

SETUP2RST

t

OFF

Hi-Z

03610-0-009

Figure 9. ATE Test Mode

Rev. A | Page 9 of 48

AD1985

ABSOLUTE MAXIMUM RATINGS

Table 15.

Parameter Min Max Unit

POWER SUPPLIES

Digital (DVDD) –0.3 +3.6 V

Analog (AVDD) –0.3 +6.0 V

INPUT CURRENT

(EXCEPT SUPPLY PINS)

ANALOG INPUT VOLTAGE

(SIGNAL PINS)

DIGITAL INPUT VOLTAGE

(SIGNAL PINS)

AMBIENT TEMPERATURE (OPERATING) 0 70 °C

STORAGE TEMPERATURE –65 +150 °C

±10.0 mA

–0.3 AV

–0.3 DV

+ 0.3 V

DD

+ 0.3 V

DD

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating

T

CASE

PD = Power Dissipation in W

= Thermal Resistance (Junction to Ambient)

θ

JA

= Thermal Resistance (Junction to Case)

θ

JC

Table 16. Thermal Resistance

Package Type θJA θ

LQFP 50.1°C/W 17.8°C/W

All measurements per EIA/JESD51 with 2S2P test board per EIA/JESD51-7.

= Case Temperature in °C

JC

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 10 of 48

AD1985

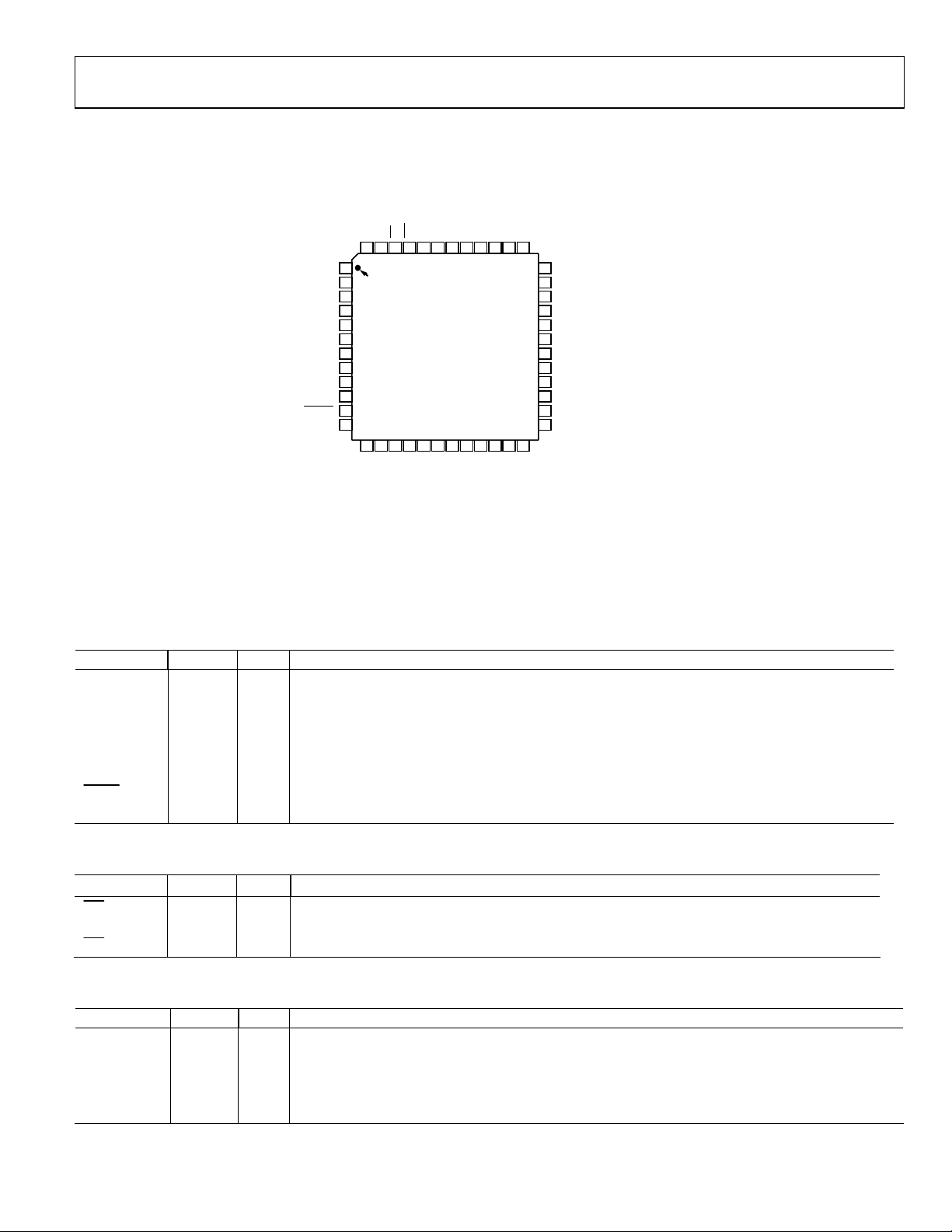

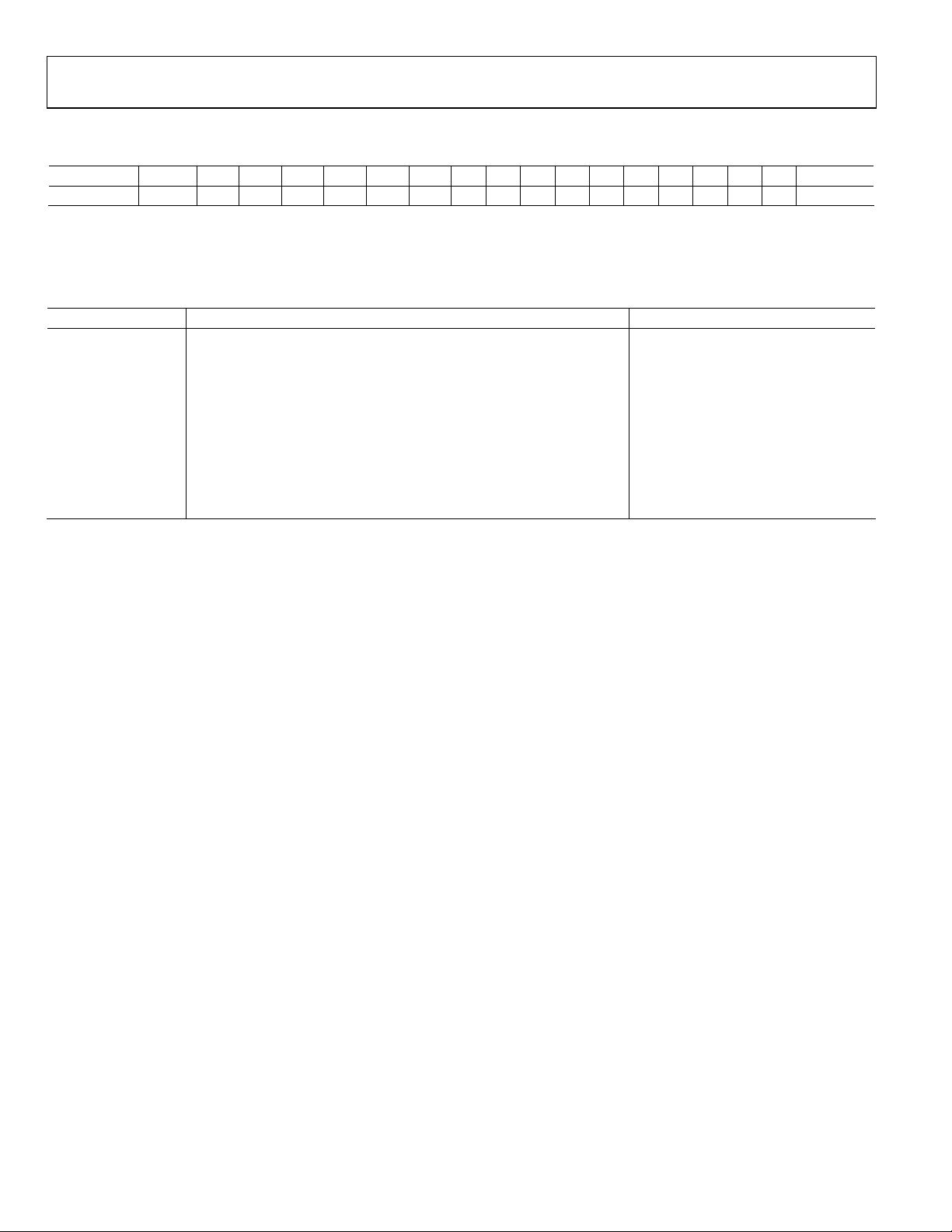

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DV

DD1

XTL_IN

XTL_OUT

DV

SS1

SDATA_OUT

BIT_CLK

DV

SS2

SDATA_IN

DV

DD2

SYNC

RESET

JS3

EAPD

ID1

AUX_L

AUX_R

SS3AVDD3

ID0

AV

AD1985

TOP VIEW

(Not to Scale)

JS1

JS0

SPDIF

48 47 46 45 44 39 38 3743 42 41 40

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

PHONE_IN

SS2

NC

CD_L

CD_GND_REF

DD2

SURR/HP_OUT_R

AV

SURR/HP_OUT_L

AV

MONO_OUT

LINE_OUT_R (FRONT)/SURR_R

36

LINE_OUT_L (FRONT)/SURR_L

35

AV

34

DD4

JS2

33

LFE_OUT

32

CENTER_OUT

31

AFILT2

30

AFILT1

29

V

28

REFOUT

V

27

REF

AV

26

SS1

AV

25

DD1

NC = NO CONNECT

MIC1

MIC2

CD_R

LINE_IN_L

LINE_IN_R

03610-A-011

Figure 10. 48-Lead LQFP Pin Configuration

Circuit Layout Note: In normal operation, Surround and Line Out are swapped to provide headphone drive on line outputs. Therefore, Pins 35 and 36 become the

surround L/R outputs and Pins 39 and 41 become the Line Out (Front) L/R outputs with headphone drive. See Bits LOSEL and HPSEL in Register 0x76 for details.

PIN FUNCTION DESCRIPTIONS

Table 17. Digital I/O

Mnemonic Pin No. I/O Description

XTL_IN 2 I Crystal Input (24.576 MHz) or External Clock In (24.576 MHz, 14.31818 MHz, or 48.000 MHz).

XTL_OUT 3 O Crystal Output.

SDATA_OUT 5 I AC Link Serial Data Output. AD1985 input stream.

BIT_CLK 6 O/I AC Link Bit Clock. 12.288 MHz serial data clock. (Input pin, for secondary mode only.)

SDATA_IN 8 O AC Link Serial Data Input. AD1985 output stream.

SYNC 10 I AC Link Frame Sync.

RESET

SPDIF 48 O SPDIF Output.

Table 18. Chip Selects/Clock Strapping

Mnemonic Pin No. I/O Description

ID0

ID1

11 I AC Link Reset. AD1985 master hardware reset.

45 I

Chip Select Input 0 (Active Low).

This pin can also be used as the chain input from a secondary codec.

46 I Chip Select Input 1 (Active Low).

Table 19. Jack Sense/EAPD

Mnemonic Pin No. Type Description

EAPD 47 O EAPD Output.

JS0 17 I JACK SENSE 0 Input.

JS1 16 I JACK SENSE 1 Input.

JS2 33 I JACK SENSE 2 Input.

JS3 12 I JACK SENSE 3 Input.

Rev. A | Page 11 of 48

AD1985

Table 20. Analog I/O

Mnemonic Pin No. I/O Description

PHONE_IN 13 I Monaural Line-Level Input.

AUX_L 14 I Auxiliary Input, Left Channel.

AUX_R 15 I Auxiliary Input, Right Channel.

CD_L 18 I CD Audio Left Channel.

CD_GND_REF 19 I CD Audio Analog Ground Reference for Differential CD Input.

CD_R 20 I CD Audio Right Channel.

MIC1 21 I Microphone 1 Input.

MIC2 22 I Microphone 2 Input.

LINE_IN_L 23 I Line In Left Channel.

LINE_IN_R 24 I Line In Right Channel.

CENTER_OUT 31 I/O Center Channel Output or Input to Recorder (depending on OMS bit in Reg 0x74).

LFE_OUT 32 I/O Low Frequency Enhanced Output or Input to Recorder (depending on OMS bit in Reg 0x74).

LINE_OUT_L/SURR_L 35 O Line Out (Front) Left Channel or Surround Left Channel (depending on LOSEL bit in Reg 0x76).

LINE_OUT_R/SURR_R 36 O Line Out (Front) Right Channel or Surround Right Channel (depending on LOSEL bit in Reg 0x76).

MONO_OUT 37 O Monaural Output to Telephony Subsystem Speakerphone.

SURR_OUT_L/HP_OUT_L 39 O Surround or Front Headphone Left Channel Output (depending on HPSEL bit in Reg 0x76).

SURR_OUT_R/HP_OUT_R 41 O Surround or Front Headphone Right Channel Output (depending on HPSEL bit in Reg 0x76).

Table 21. Filter/Reference

Mnemonic Pin No. I/O Description

V

27 O Voltage Reference Filter.

REF

V

28 O Voltage Reference Output (Intended for Mic Bias).

REFOUT

AFILT1 29 O Antialiasing Filter Capacitor—ADC Right Channel.

AFLIT2 30 O Antialiasing Filter Capacitor—ADC Left Channel.

Table 22. Power and Ground Signals

Mnemonic Pin No. Type Description

DV

1 I Digital VDD: 3.3 V.

DD1

DV

4 I Digital Ground.

SS1

DV

7 I Digital Ground.

SS2

DV

9 I Digital VDD: 3.3 V.

DD2

AV

25 I Analog VDD: 5.0 V.

DD1

AV

26 I Analog Ground.

SS1

AV

34 I Analog VDD: 5.0 V.

DD4

AV

38 I Analog VDD: 5.0 V.

DD2

AV

40 I Analog Ground.

SS2

AV

43 I Analog VDD: 5.0 V.

DD3

AV

44 I Analog Ground.

SS3

Table 23. No Connects

Mnemonic Pin No. Type Description

NC 42 N/A No Connect.

Rev. A | Page 12 of 48

AD1985

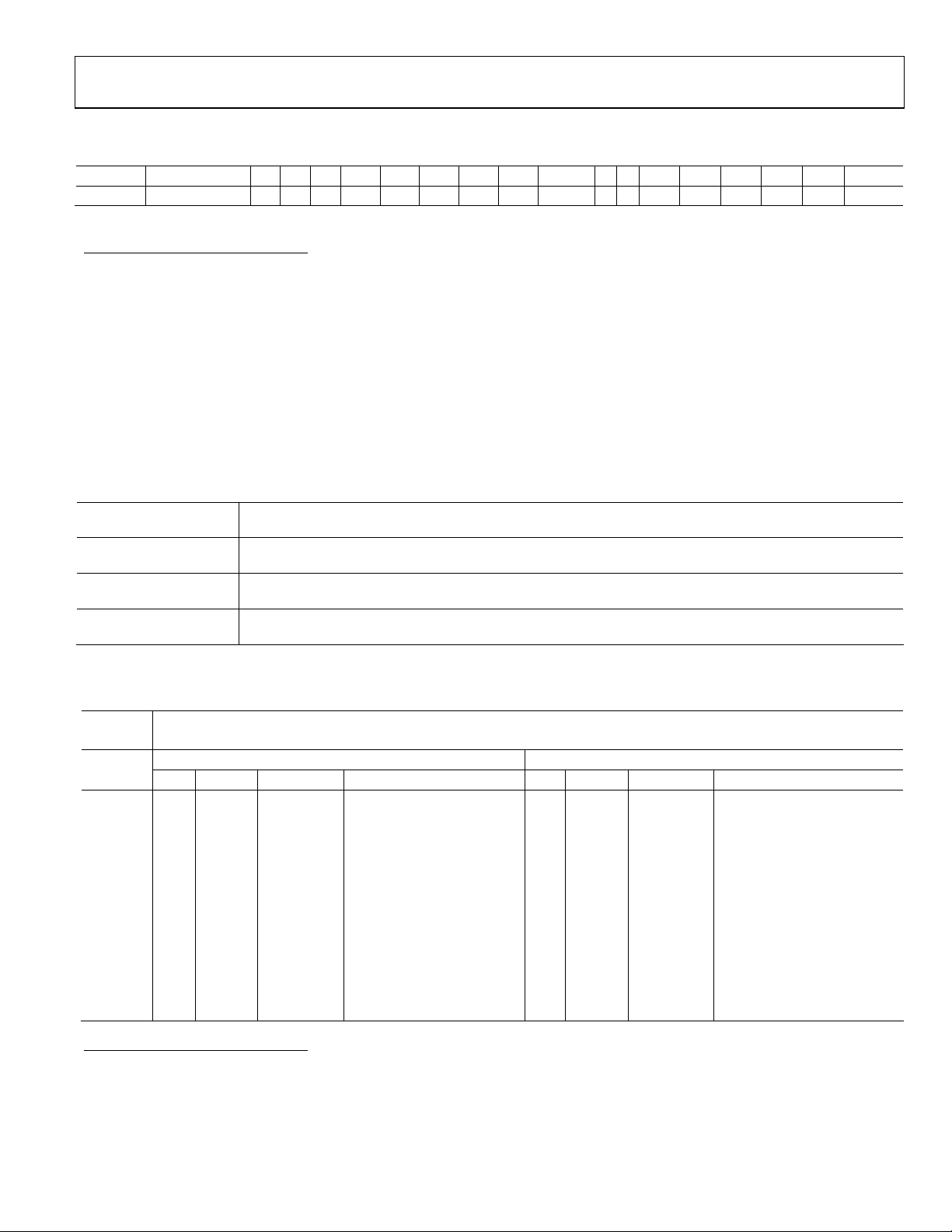

INDEXED CONTROL REGISTERS

Reg Name D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

0x00 Reset

0x02 Master Volume

0x04 Headphones Volume

0x06 Mono Volume

0x0A PC Beep

0x0C Phone_In Volume

0x0E MIC Volume

0x10 Line In Volume

0x12 CD Volume

0x16 AUX In Volume

0x18 PCM Out Vol

0x1A Record Select

0x1C Record Gain

0x20 General Purpose

0x24 Audio Int. and Paging

0x26 Power-Down Ctrl/Stat

0x28 Extended Audio ID

0x2A Ext’d Audio Stat/Ctrl

0x2C PCM Front DAC Rate

0x2E PCM Surr DAC Rate

0x30 PCM LFE/C DAC Rate

0x32 PCM L/R ADC Rate

0x36 Center/LFE volume

0x38 Surround Volume

0x3A SPDIF Control

0x60 EQ Control

0x62 EQ Data

0x70 J Sense/General

0x72 J Sense/Audio/Status

0x74 Serial Configuration

0x76 Misc Control Bits

0x78 Advanced Jack Sense

0x7C Vendor ID1

0x7E Vendor ID2

0x60

Codec Class/Rev

pg. 1

0x62

PCI SVID

pg. 1

0x64

PCI SID

pg. 1

0x66

Function Select

pg. 1

0x68

Function Information

pg. 1

0x6A

Sense Register

pg. 1

NOTES

Odd register addresses are aliased to the next lower even address.

Registers not shown and bits containing an X are assumed to be reserved.

Reserved registers should not be written. Zeros should be written to reserved bits.

1

For AC ‘97 compatibility, these RM bits must be enabled before they can have any effect.

X SE4 SE3 SE2 SE1 SE0 ID9 ID8 ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 0x0090

MM X X LMV4 LMV3 LMV2 LMV1 LMV0 MMRM1 X X RMV4 RMV3 RMV2 RMV1 RMV0 0x8000

HPM X X LHV4 LHV3 LHV2 LHV1 LHV0 HPRM1 X X RHV4 RHV3 RHV2 RHV1 RHV0 0x8000

MVM X X X X X X X X X X MV4 MV2 MV2 MV1 MV0 0x8000

PCBM X X PCBF7 PCBF6 PCBF5 PCBF4 PCBF3 PCBF2 PCBF1 PCBF0 PCBV3 PCBV2 PCBV1 PCBV0 X 0x8000

PHM X X X X X X X X X X PHV4 PHV3 PHV2 PHV1 PHV0 0x8008

MCM X X X X X X X X M20 X MCV4 MCV3 MCV2 MCV1 MCV0 0x8008

LM X X LLV4 LLV3 LLV2 LLV1 LLV0 LVRM1 X X RLV4 RLV3 RLV2 RLV1 RLV0 0x8808

CM X X LCV4 LCV3 LCV2 LCV1 LCV0 CDRM1 X X RCV4 RCV3 RCV2 RCV1 RCV0 0x8808

AM X X LAV4 LAV3 LAV2 LAV1 LAV0 AVRM1 X X RAV4 RAV3 RAV2 RAV1 RAV0 0x8808

OM X X LOV4 LOV3 LOV2 LOV1 LOV0 OMRM1 X X ROV4 ROV3 ROV2 ROV1 ROV0 0x8808

X X X X X LS2 LS1 LS0 X X X X X RS2 RS1 RS0 0x0000

IM X X X LIV3 LIV2 LIV1 LIV0 IMRM1 X X X RIV3 RIV2 RIV1 RIV0 0x8000

X X X X DRSS1 DRSS0 MIX MS LPBK X X X X X X X 0x0000

I4 I3 I2 I1 I0 X X X X X X X PG3 PG2 PG1 PG0 0xXXXX

EAPD PR6 PR5 PR4 PR3 PR2 PR1 PR0 X X X X REF ANL DAC ADC N/A

AID1 AID0 X X REV1 REV0 AMAP AIDLDAC AIDSDAC AIDCDAC DSA1 DSA0 X AIDSPDIF DRA AIDVRA 0xXBC7

VFORCE X PRK PRJ PRI SPCV X ASCLDAC ASCSDAC ASCCDAC SPSA1 SPSA0 X ASCSPDF ASCDRA ASCVRA 0xXXXX

SRF15 SRF14 SRF13 SRF12 SRF11 SRF10 SRF9 SRF8 SRF7 SRF6 SRF5 SRF4 SRF3 SRF2 SRF1 SRF0 0xBB80

SRS15 SRS14 SRS13 SRS12 SRS11 SRS10 SRS9 SRS8 SRS7 SRS6 SRS5 SRS4 SRS3 SRS2 SRS1 SRS0 0xBB80

SRCL15 SRCL14 SRCL13 SRCL12 SRCL11 SRCL10 SRCL9 SRCL8 SRCL7 SRCL6 SRCL5 SRCL4 SRCL3 SRCL2 SRCL1 SRCL0 0xBB80

SRA15 SRA14 SRA13 SRA12 SRA11 SRA10 SRA9 SRA8 SRA7 SRA6 SRA5 SRA4 SRA3 SRA2 SRA1 SRA0 0xBB80

LFEM X X LFE4 LFE3 LFE2 LFE1 LFE0 CNTM X X CNT4 CNT3 CNT2 CNT1 CNT0 0x8080

LSM X LSR5 LSR4 LSR3 LSR2 LSR1 LSR0 RSM X RSR5 RSR4 RSR3 RSR2 RSR1 RSR0 0x8080

AUD

JS1

INT

PRO 0x2000

JS0

N/A

INT

V X SPSR1 SPSR0 L CC6 CC5 CC4 CC3 CC2 CC1 CC0 PRE COPY

EQM X X X X X X X SYM CHS BCA5 BCA4 BCA3 BCA2 BCA1 BCA0 0x8080

CFD15 CFD14 CFD13 CFD12 CFD11 CFD10 CFD9 CFD8 CFD7 CFD6 CFD5 CFD4 CFD3 CFD2 CFD1 CFD0 0x0000

X X X X X X X X MMDIS JS2SEL X X X X X X N/A

JS

JS1

JS0

JS

JS

JS

JS1

JS0

JS1

SPRD

DMX

DMX

MT2

MT1

MT0

EQB

EQB

SLOT16 REGM2 REGM1 REGM0 REGM3 DRF OMS CHEN SPOVR LBKS1 LBKS0 INTS CSWP SPAL SPDZ SPLNK 0x1001

DACZ AC97NC MSPLT LODIS CLDIS HPSEL DMIX1 DMIX0 SPRD 2CMIC LOSEL SRU VREFH VREFD MBG1 MBG0 0x0000

X X X X X X X X JS3TMR JS2TMR JS3MD JS2MD JS3ST JS2ST JS3INT JS2INT N/A

VIDF7 VIDF6 VIDF5 VIDF4 VIDF3 VIDF2 VIDF1 VIDF0 VIDS7 VIDS6 VIDS5 VIDS4 VIDS3 VIDS2 VIDS1 VIDS0 0x4144

VIDT7 VIDT6 VIDT5 VIDT4 VIDT3 VIDT2 VIDT1 VIDT0 VIDREV7 VIDREV6 VIDREV5 VIDREV4 VIDREV3 VIDREV2 VIDREV1 VIDREV0 0x5375

X X X CL4 CL3 CL2 CL1 CL0 RV7 RV6 RV5 RV4 RV3 RV2 RV1 RV0 N/A

PVI15 PVI14 PVI13 PVI12 PVI11 PVI10 PVI9 PVI8 PVI7 PVI6 PVI5 PVI4 PVI3 PVI2 PVI1 PVI0 N/A

PI15 PI14 PI13 PI12 PI11 PI10 PI9 PI8 PI7 PI6 PI5 PI4 PI3 PI2 PI1 PI0 N/A

X X X X X X X X X X X FC3 FC2 FC1 FC0 T/R 0x0000

G4 G3 G2 G1 G0 INV DL4 DL3 DL2 DL1 DL0 IV X X X FIP N/A

ST2 ST1 ST0 S4 S3 S2 S1 S0 OR1 OR0 SR5 SR4 SR3 SR2 SR1 SR0 N/A

TMR

JS0

TMR

JS1

MD

JS0

MD

JS1

ST

JS0

ST

Rev. A | Page 13 of 48

AD1985

Reset (Index 0x00)

Reg Num Name D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

0x00 Reset X SE4 SE3 SE2 SE1 SE0 ID9 ID8 ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 0x0090

Note: Writing any value to this register performs a register reset, which causes all registers (except Register 0x74) to revert to their default values. Register 0x74 will only

reset Bits CSWP (D3), LBKS[1:0] (D[6:5]), and OMS (D9). The REGM and serial configuration bits are reset only by an external hardware reset.

Reading this register returns the ID code of the part and a code for the type of 3D stereo enhancement.

ID[9:0] Identify Capability: The ID decodes the capabilities of AD1985 based on the following:

Bit = 1 Function AD1985

ID0 Dedicated MIC PCM In Channel 0

ID1 Reserved (per AC ’97, 2.3) 0

ID2 Bass and Treble Control 0

ID3 Simulated Stereo (Mono to Stereo) 0

ID4 Headphone Out Support 1

ID5 Loudness (Bass Boost) Support 0

ID6 18-Bit DAC Resolution 0

ID7 20-Bit DAC Resolution 1

ID8 18-Bit ADC Resolution 0

ID9 20-Bit ADC Resolution 0

SE[4:0] Stereo Enhancement. The AD1985 does not provide hardware 3D stereo enhancement (all bits are 0).

Rev. A | Page 14 of 48

AD1985

Master Volume Register (Index 0x02)

Reg Num Name D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

0x02 Master Volume MM X X LMV4 LMV3 LMV2 LMV1 LMV0 MMRM1 X X RMV4 RMV3 RMV2 RMV1 RMV0 0x8000

1

For AC ’97 compatibility, Bit D7 (MMRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right

channels.

This register controls the LINE_OUT volume and mute bits.

Each volume subregister contains five bits, generating 32

Note that depending on the state of the AC97NC bit in Register

0x76, this register has the following additional functionality:

volume levels with increments of 1.5 dB each.

• For AC97NC = 0, the register controls the LINE_OUT output

AC ’97 defines the 6-bit volume registers, therefore, to maintain

attenuators only.

compatibility whenever the D5 or D13 bit is set to 1, its

respective lower five volume bits are automatically set to 1 by

the codec logic. On readback, all lower five bits will read 1s

• For AC97NC = 1, the register controls the LINE_OUT, center,

and LFE output attenuators.

whenever these bits are set to 1.

RMV[4:0]

Right Master Volume Control. The least significant bit represents 1.5 dB. This register controls the output from

0 dB to a maximum attenuation of 46.5 dB.

MMRM

Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel

separately from the MM bit. Otherwise, this bit will always read 0 and will have no effect when set to 1.

LMV[4:0]

Left Master Volume Control. The least significant bit represents 1.5 dB. This register controls the output from

0 dB to a maximum attenuation of 46.5 dB.

MM

Master Volume Mute. When this bit is set to 1, all channels are muted, unless the MSPLT bit in Register 0x76 is

set to 1, in which case, this mute bit will only affect the left channels.

Volume Settings for Master and Headphone

Reg.

0x76

Master Volume (0x02) and Headphone Volume (0x04)

Control Bits

Left Channel Volume D[13:8] Right Channel Volume D[5:0]

MSPLT1

0 0

D15 Write Readback Function D7

00

0000

0 0

00

1111

0 0

01

1111

00 0000 0 dB Gain x

00 1111 –22.5 dB Gain x

01 1111 –46.5 dB Gain x

1

Write Readback Function

00

00 0000 0 dB Gain

0000

00

00 1111 –22.5 dB Gain

1111

01

01 1111 –46.5 dB Gain

1111

0 0 1x xxxx 01 1111 –46.5 dB Gain x 1x xxxx 01 1111 –46.5 dB Gain

0 1 xx xxxx xx xxxx –∞ dB Gain, Muted x xx xxxx xx xxxx –∞ dB Gain, Muted

1 0 1x xxxx 01 1111 –46.5 dB Gain 1 xx xxxx xx xxxx

–∞ dB Gain, Only Right

Muted

1 1 xx xxxx xx xxxx

–∞ dB Gain, Only Left

0 1x xxxx 01 1111 –46.5 dB Gain

Muted

1 1 xx xxxx xx xxxx –∞ dB Gain, Left Muted 1 xx xxxx xx xxxx –∞ dB Gain, Right Muted

Note: x in the above table is a wild card, meaning the value has no effect.

1

For AC ’97 compatibility, Bit D7 is available only by setting the MSPLT bit, Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. If

MSPLT is not set, Bit D7 has no effect.

Rev. A | Page 15 of 48

Loading...

Loading...