Analog Devices AD1953 Datasheet

SigmaDSP™ 3-Channel, 26-Bit

a

FEATURES

5 V 3-Channel Audio DAC System

Digital Audio Output (2-Channel or 6-Channel

Packed Mode)

Accepts Sample Rates up to 48 kHz

7 Biquad Filter Sections per Channel

Dual Dynamic Processor with Arbitrary Input/Output

Curve and Adjustable Time Constants

0 ms to 6 ms Variable Delay/Channel for Speaker Alignment

Stereo Spreading Algorithm for Phat Stereo™ Effect

Program RAM Allows Complete New Program Download

via SPI Port

Parameter RAM Allows Complete Control of More Than

200 Parameters via SPI Port

SPI Port Features Safe-Upload Mode for Transparent

Filter Updates

2 Control Registers Allow Complete Control of Modes

and Memory Transfers

Differential Output for Optimum Performance

112 dB Signal-to-Noise (Not Muted) at 48 kHz Sample

Rate (A-Weighted Stereo)

70 dB Stop-Band Attenuation

On-Chip Clickless Volume Control

Hardware and Software Controllable Clickless Mute

Digital De-emphasis Processing for 32 kHz, 44.1 kHz, 48 kHz

Sample Rates

Flexible Serial Data Port with Right-Justified, Left-Justified,

2

S Compatible, and DSP Serial Port Modes

I

Auxiliary Digital Input

Graphical Custom Programming Tools

48-Lead LQFP Plastic Package

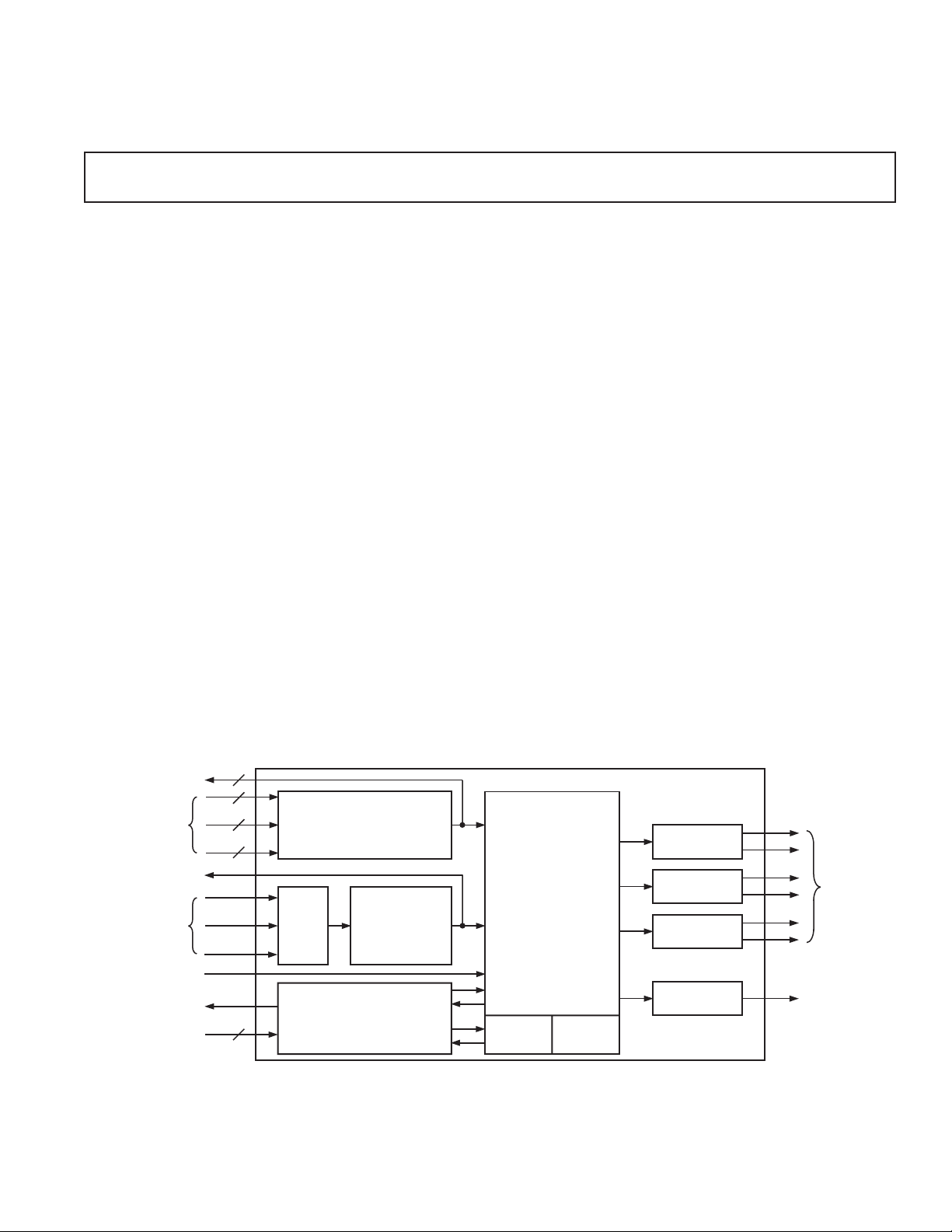

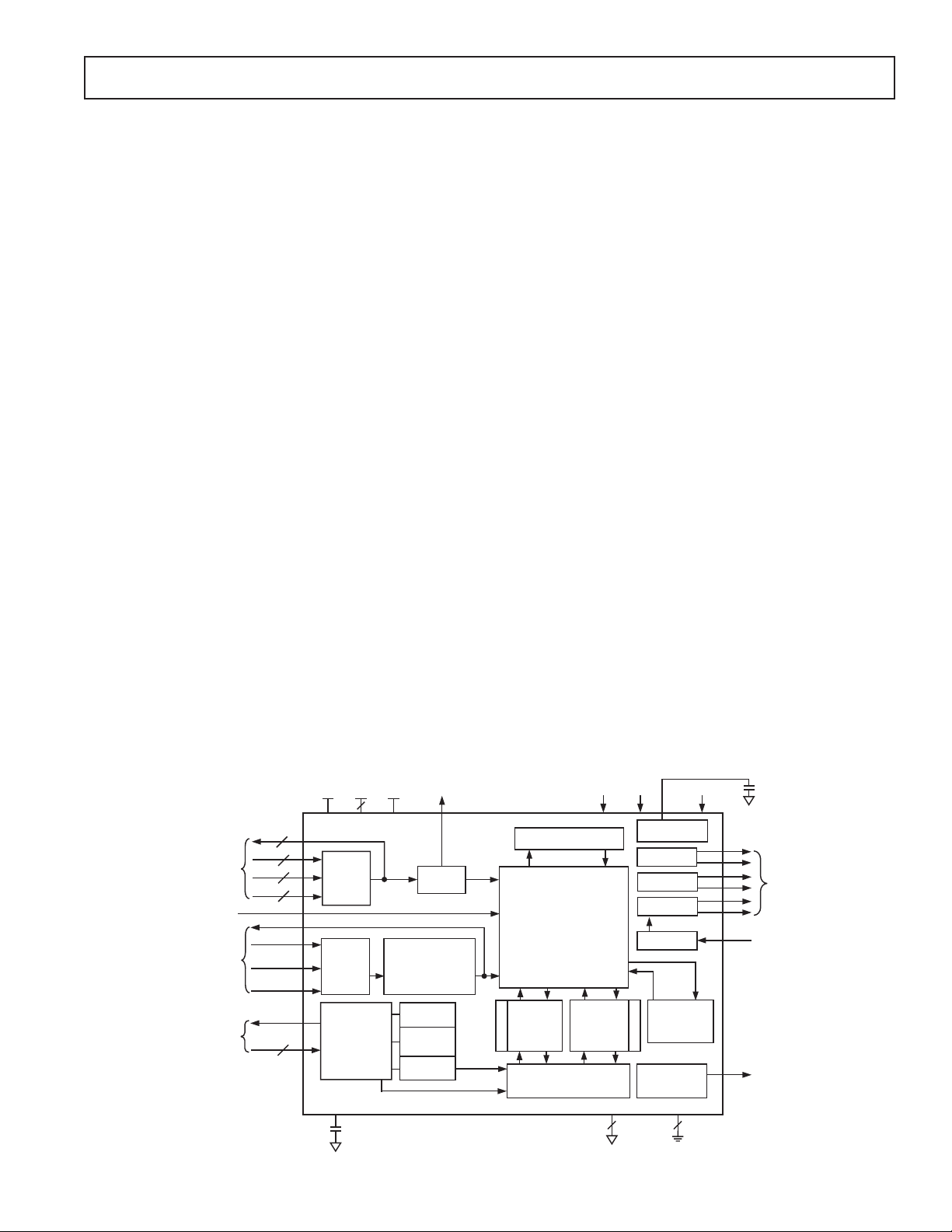

FUNCTIONAL BLOCK DIAGRAM

SERIAL DATA

OUTPUT

SERIAL DATA

INPUTS

MASTER CLOCK

OUTPUT

MASTER

CLOCK INPUTS

3

3

3

3

MCLK

MUX

AUDIO DATA

MUX

GENERATOR

(256/512 f

MCLK

)

S

Signal Processing DAC

AD1953

APPLICATIONS

2.0/2.1 Channel Audio Systems (2 Main Channels

Plus Subwoofer)

Multichannel Automotive Sound Systems

Multimedia Audio

Mini Component Stereo

Home Theater Systems (AC-3 Postprocessor)

Musical Instruments

In-Seat Sound Systems (Aircraft, Motor Coaches)

PRODUCT OVERVIEW

The AD1953 is a complete 26-bit, single-chip, 3-channel digital

audio playback system with built-in DSP functionality for speaker

equalization, dual-band compression/limiting, delay compensation, and image enhancement. These algorithms can be used to

compensate for real-world limitations of speakers, amplifiers,

and listening environments, resulting in a dramatic improvement

of perceived audio quality.

The signal processing used in the AD1953 is comparable to that

found in high end studio equipment. Most of the processing is

done in full 48-bit double-precision mode, resulting in very good

low level signal performance and the absence of limit cycles or

idle tones. The compressor/limiter uses a sophisticated two-band

algorithm often found in high end broadcast compressors.

(continued on page 9)

AD1953

26 22

DSP CORE

DATA FORMAT:

3.23 (SINGLE PRECISION)

3.45 (DOUBLE PRECISION)

DAC – L

DAC – R

DAC – SW

ANALOG

OUTPUTS

AUX SERIAL

DATA INPUT

SPI DATA

OUTPUT

SPI INPUT

3

SERIAL CONTROL

INTERFACE

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

DATA CAPTURE

OUT/TDM OUT

RAM ROM

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

DIGITAL

OUTPUT

AD1953

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

PRODUCT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . 6

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . 7

TYPICAL PERFORMANCE CHARACTERISTICS . . . . . 8

PERFORMANCE PLOTS . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PRODUCT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

SIGNAL PROCESSING . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Signal Processing Overview . . . . . . . . . . . . . . . . . . . . . . . 12

Numeric Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Coefficient Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Internal DSP Signal Data Format . . . . . . . . . . . . . . . . . . 13

High-Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Biquad Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Volume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Stereo Image Expander . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Main Compressor/Limiter . . . . . . . . . . . . . . . . . . . . . . . . 15

RMS Time Constant . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

RMS Hold Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

RMS Release Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Look-Ahead Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Post-Compression Gain . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Subwoofer Compressor/Limiter . . . . . . . . . . . . . . . . . . . . 17

De-Emphasis Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Using the Sub Reinjection Paths for Systems with No

Subwoofer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Interpolation Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

SPI PORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

SPI Address Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Volume Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Parameter RAM Contents . . . . . . . . . . . . . . . . . . . . . . . . 23

Options for Parameter Updates . . . . . . . . . . . . . . . . . . . . 24

Soft Shutdown Mechanism . . . . . . . . . . . . . . . . . . . . . . . 25

Safeload Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Summary of RAM Modes . . . . . . . . . . . . . . . . . . . . . . . . 25

SPI READ/WRITE DATA FORMATS . . . . . . . . . . . . . . . 26

INITIALIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Power-Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Setting the Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Setting the Data and MCLK Input Selectors . . . . . . . . . . 28

DATA CAPTURE REGISTERS AND OUTPUTS . . . . . . 28

SERIAL DATA INPUT/OUTPUT PORTS . . . . . . . . . . . . 30

Serial Data Input/Output Modes . . . . . . . . . . . . . . . . . . . 30

DIGITAL CONTROL PIN . . . . . . . . . . . . . . . . . . . . . . . . 31

Mute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

ANALOG OUTPUT SECTION . . . . . . . . . . . . . . . . . . . . 31

GRAPHICAL CUSTOM PROGRAMMING TOOLS . . . . 32

APPENDIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 34

–2–

REV. 0

AD1953

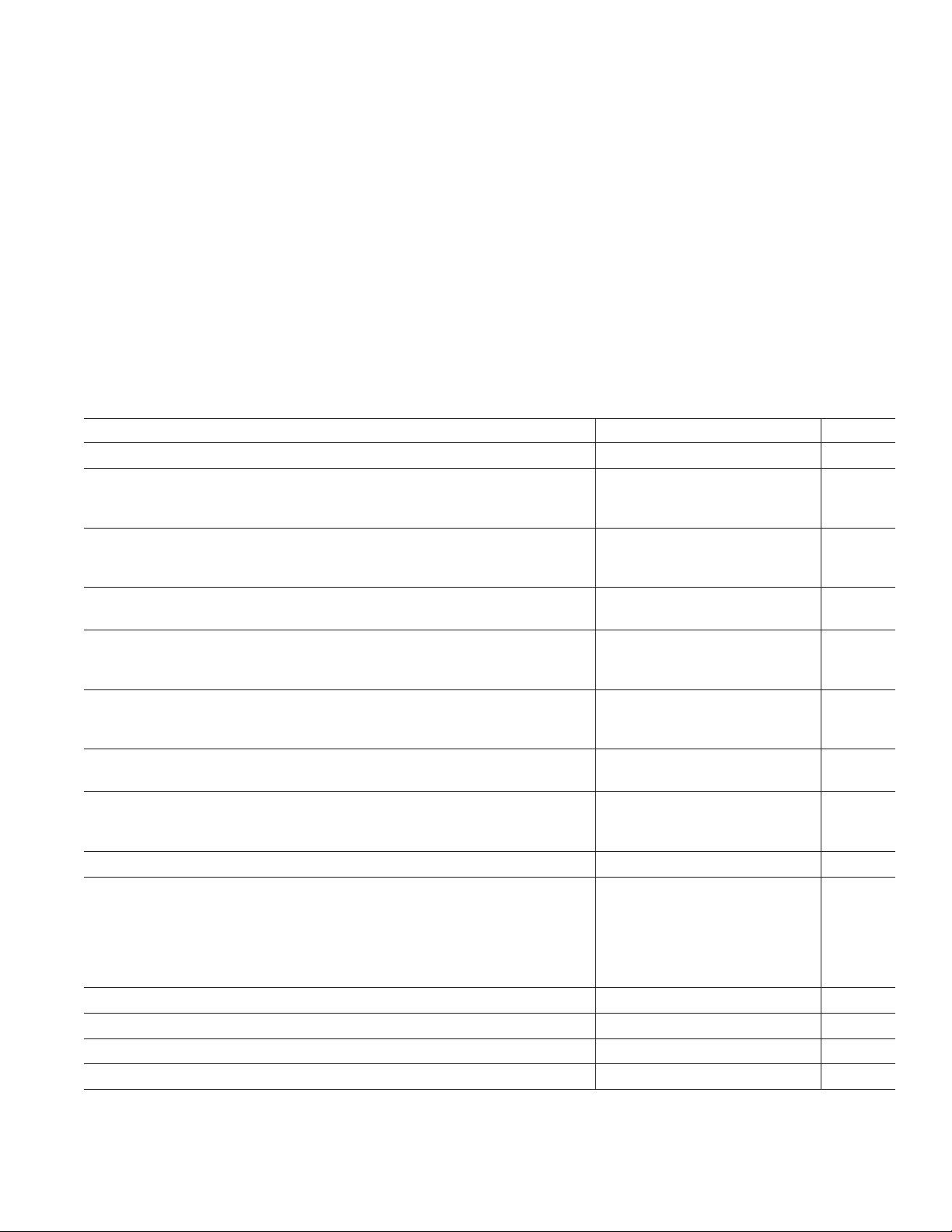

SPECIFICATIONS

TEST CONDITIONS, UNLESS OTHERWISE NOTED.

Supply Voltages (AVDD, DVDD) 5.0 V

Ambient Temperature 25°C

Input Clock 12.288 MHz

Input Signal 1.000 kHz 0 dB Full Scale

Input Sample Rate 48 kHz

Measurement Bandwidth 20 Hz to 20 kHz

Word Width 24 Bits

Load Capacitance 2200 pF

Load Impedance 2.74 kΩ

Input Voltage High 2.1 V

Input Voltage Low 0.8 V

ANALOG PERFORMANCE*

Parameter Min Typ Max Unit

RESOLUTION 24 Bits

SIGNAL-TO-NOISE RATIO (20 Hz to 20 kHz) (Left/Right Output)

No Filter (Stereo) 109 dB

With A-Weighted Filter 112 dB

DYNAMIC RANGE (20 Hz to 20 kHz, –60 dB Input) (Left/Right Output)

No Filter 109 dB

With A-Weighted Filter 108 112 dB

TOTAL HARMONIC DISTORTION PLUS NOISE (Left/Right Output)

VO = –0.5 dB –93 –100 dB

SIGNAL-TO-NOISE RATIO (20 Hz to 20 kHz) (Subwoofer Output)

No Filter (Stereo) 104 dB

With A-Weighted Filter 107 dB

DYNAMIC RANGE (20 Hz to 20 kHz, –60 dB Input) (Subwoofer Output)

No Filter 104 dB

With A-Weighted Filter 104 107 dB

TOTAL HARMONIC DISTORTION PLUS NOISE (Subwoofer Output)

VO = –0.5 dB –90 –96 dB

ANALOG OUTPUTS

Differential Output Range (± Full Scale) (Left/Right Output) 2.72 V p-p

Differential Output Range (± Full Scale) (Subwoofer Output) 2.79 V p-p

CMOUT 2.50 V

DC ACCURACY

Gain Error (Left/Right Channel) –5 +5 %

Gain Error (Subwoofer Channel) –8 +8 %

Interchannel Gain Mismatch –0.250 +0.250 dB

Gain Drift 150 ppm/°C

DC Offset –35 +35 mV

INTERCHANNEL CROSSTALK (EIAJ Method) –120 dB

INTERCHANNEL PHASE DEVIATION ±0.1 Degrees

MUTE ATTENUATION –107 dB

DE-EMPHASIS GAIN ERROR ±0.1 dB

*Performance of right and left channels is identical (exclusive of the Interchannel Gain Mismatch and Interchannel Phase Deviation specifications).

Specifications subject to change without notice.

REV. 0

–3–

AD1953

DIGITAL I/O

Parameter Min Typ Max Unit

Input Voltage High (V

Input Voltage High (V

Input Voltage Low (V

Input Leakage (I

Input Leakage (I

High Level Output Voltage (V

Low Level Output Voltage (V

Input Capacitance 20 pF

Specifications subject to change without notice.

) 2.1 V

IH

) – RESETB 2.25 V

IH

) 0.8 V

IL

@ VIH = 2.1 V) 10 µA

IH

@ VIL = 0.8 V) 10 µA

IL

), IOH = 2 mA DVDD – 0.5 V

OH

), IOL = 2 mA 0.4 V

OL

POWER

Parameter Min Typ Max Unit

SUPPLIES*

Voltage: Analog, and Digital 4.5 5 5.5 V

Analog Current 42 48 mA

Analog Current, Power-Down 40 46 mA

Digital Current 66 76 mA

Digital Current, SPI Power-Down 6 10 mA

Digital Current, Reset Power-Down 54 62 mA

DISSIPATION

Operation, Both Supplies 540 mW

Operation, Analog Supplies 210 mW

Operation, Digital Supplies 330 mW

SPI Power-Down, Both Supplies 230 mW

Reset Power-Down, Both Supplies 470 mW

POWER SUPPLY REJECTION RATIO

1 kHz 300 mV p-p Signal at Analog Supply Pins –80 dB

20 kHz 300 mV p-p Signal at Analog Supply Pins –80 dB

*ODVDD current is dependent on load capacitance and clock rate.

Specifications subject to change without notice.

TEMPERATURE RANGE

Parameter Min Typ Max Unit

Specifications Guaranteed 25 °C

Functionality Guaranteed –40 105 °C

Storage –55 125 °C

Specifications subject to change without notice.

–4–

REV. 0

AD1953

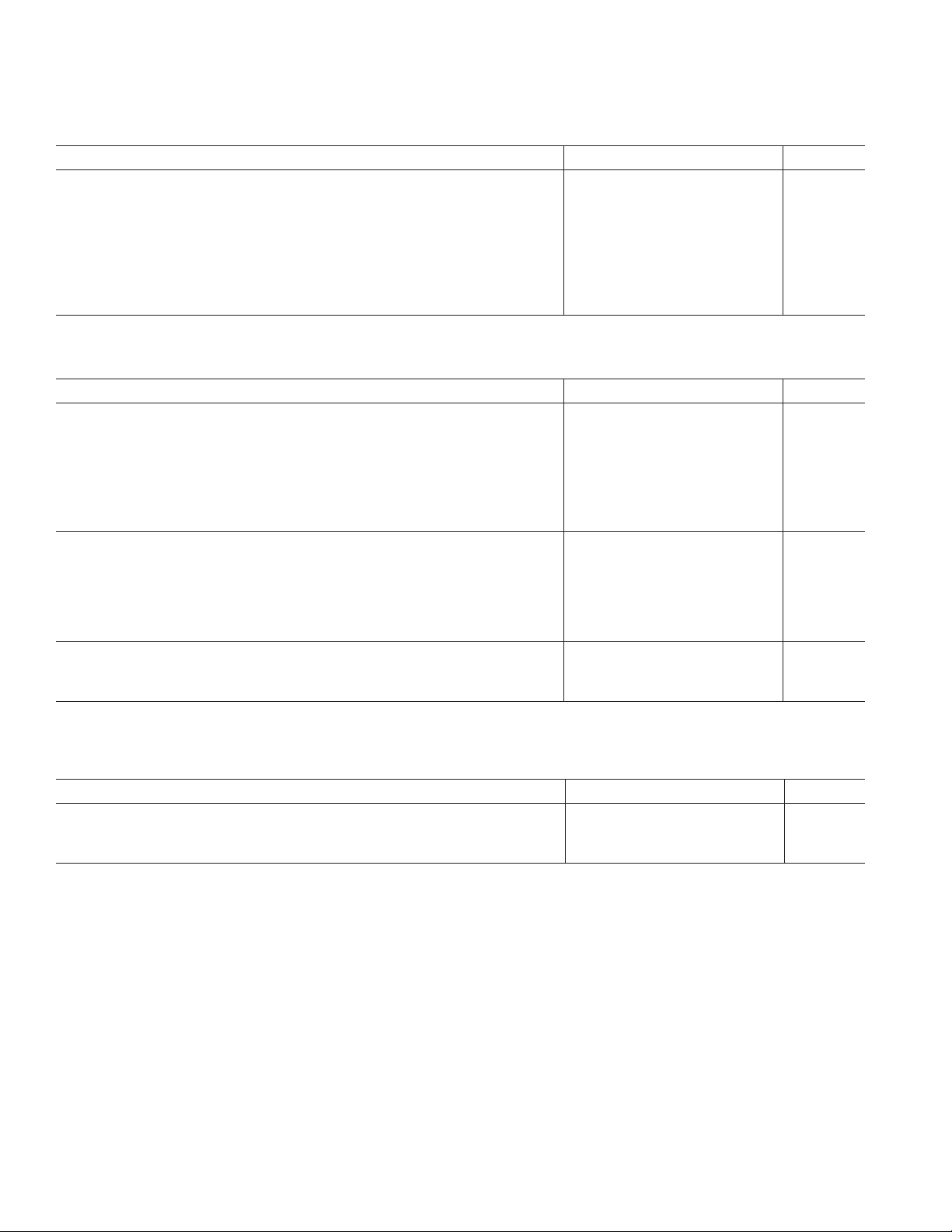

DIGITAL TIMING

Parameter Min Typ Max Unit

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

Specifications subject to change without notice.

MCLK Recommended Duty Cycle @ 12.288 MHz (256 fS Mode) 45 55 %

DMD

MCLK Recommended Duty Cycle @ 24.576 MHz (512 fS Mode) 40 60 %

DMD

MCLK Delay (All Mode) 25 ns

DMD

BCLK Low Pulsewidth 10 ns

DBH

BCLK High Pulsewidth 10 ns

DBH

BCLK Delay (to BCLKO) 25 ns

DBD

LRCLK Setup 0 ns

DLS

LRCLK Hold 10 ns

DLH

LRCLK Delay (to LRCLKO) 25 ns

DLD

SDATA Setup 0 ns

DDS

SDATA Hold 10 ns

DDH

SDATA Delay (to SDATAO) 25 ns

DDD

TDMFS Delay (from MCLK) 35 ns

TFS

TDMBC Delay (from MCLK) 35 ns

TBS

TDMO Delay (from TDMBC) 5 ns

TOS

CCLK Low Pulsewidth 12 ns

CCL

CCLK High Pulsewidth 12 ns

CCH

CLATCH Setup 10 ns

CLS

CLATCH Hold 10 ns

CLH

CLATCH High Pulsewidth 10 ns

CLD

CDATA Setup 0 ns

CDS

CDATA Hold 10 ns

CDH

COUT Delay 35 ns

COD

COUT Hold 2 ns

COH

DCSOUT Delay 35 ns

DCD

DCSOUT Hold 2 ns

DCH

PD/RST Low Pulsewidth 5 ns

PDRP

DIGITAL FILTER CHARACTERISTICS at 44.1 kHz

Parameter Min Typ Max Unit

Pass-Band Ripple ±0.01 dB

Stop-Band Attenuation 70 dB

Pass Band 20 kHz

0.4535 ⫻ f

Stop Band 24 kHz

0.5442 ⫻ f

Group Delay 24.625/f

Specifications subject to change without notice.

S

S

S

sec

REV. 0

–5–

AD1953

ABSOLUTE MAXIMUM RATINGS

*

DVDD to DGND . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

ODVDD to DGND . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

AVDD to AGND . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

Digital Inputs . . . . . . . . . . DGND – 0.3 V to DVDD + 0.3 V

Analog Inputs . . . . . . . . . . AGND – 0.3 V to AVDD + 0.3 V

AGND to DGND . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

Reference Voltage . . . . . . . . . . . . . . . . . . . (AVDD + 0.3)/2 V

Maximum Junction Temperature . . . . . . . . . . . . . . . . 125∞C

Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C

Soldering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300∞C/10 sec

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD1953YST –40∞C to +105∞C 48-Lead LQFP ST-48

AD1953YSTRL –40∞C to +105∞C 48-Lead LQFP ST-48 on 13" Reel

AD1953YSTRL7 –40∞C to +105∞C 48-Lead LQFP ST-48 on 7" Reel

EVAL-AD1953EB Evaluation Board

Package Characteristics (48-Lead LQFP)

Min Typ Max Unit

(Thermal Resistance 76 ∞C/W

JA

[Junction-to-Ambient])

(Thermal Resistance 17 ∞C/W

JC

[Junction-to-Case])

NC

MCLK2

MCLK1

MCLK0

AUX DATA

MUTE

DVD D

SDATA2

BCLK2

LRCLK2

SDATA1

BCLK1

NC = NO CONNECT

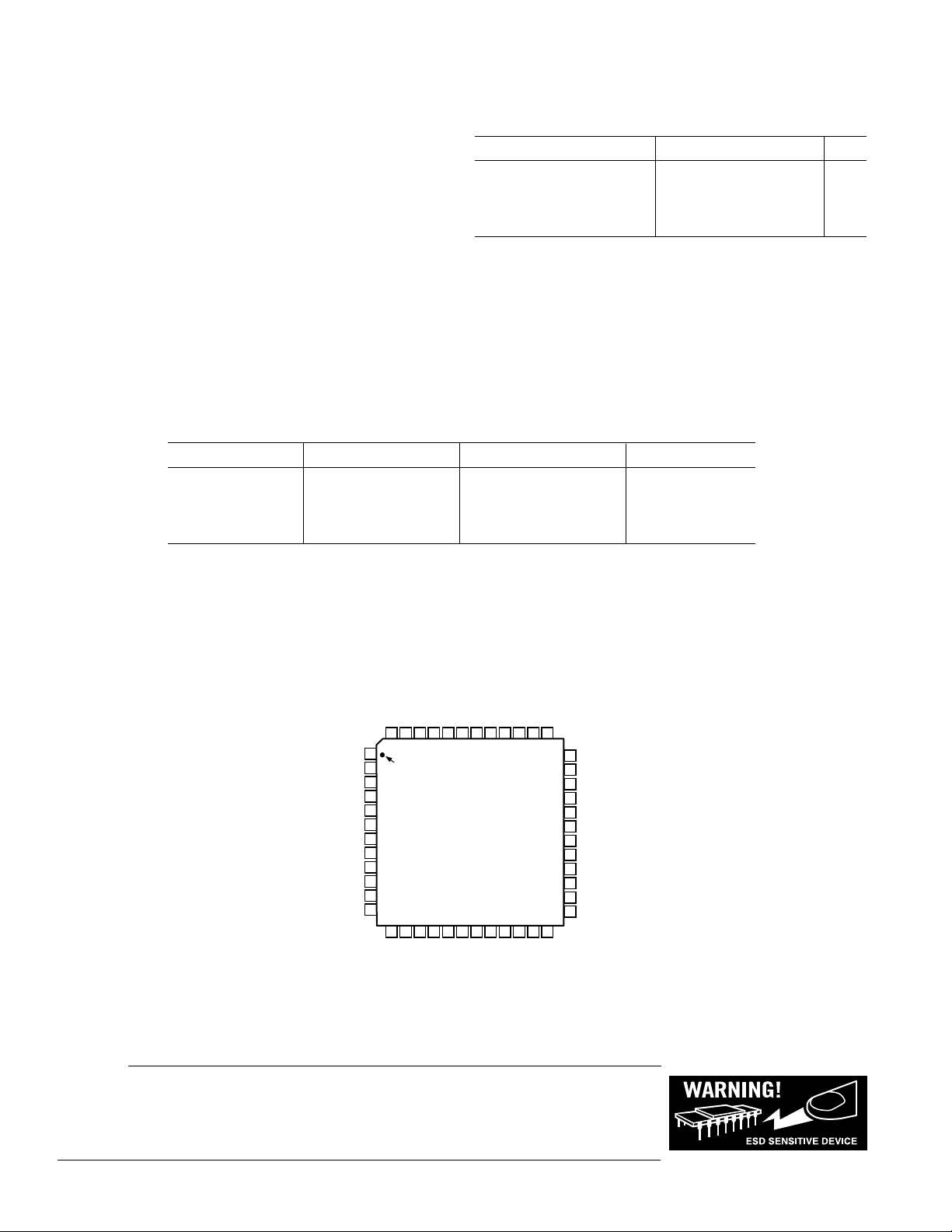

PIN CONFIGURATION

48-Lead LQFP

DGND

MCLKOUT

COUT

DCSOUT

ODVDD

LRMUXO/TDMFS

BMUXO/TDMBC

AD1953

TOP VIEW

CCLK

CDATA

LRCLK0

DMUXO/TDMO

CLATCH

48 4 7 46 4 5 44 39 38 3743 42 41 40

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

DGND

LRCLK1

(Not to Scale)

BCLK0

SDATA0

ZEROFLAG

FILTCAP

AV DD

RESETB

VREF

AGND

NC

NC

36

35

34

33

32

31

30

29

28

27

26

25

NC

AGND

VOUTL–

VOUTL+

AV DD

AGND

AV DD

VOUTR+

VOUTR–

AGND

VOUTS+

VOUTS–

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1953 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–6–

REV. 0

AD1953

PIN FUNCTION DESCRIPTIONS

Input/

Pin No. Mnemonic Output Description

1 NC No Connect

2 MCLK2 IN Master Clock Input 2 256/512 f

3 MCLK1 IN Master Clock Input 1 256/512 f

4 MCLK0 IN Master Clock Input 0 256/512 f

5 AUXDATA IN Auxiliary Serial Data Input

6 MUTE IN Mute Signal, Initiates Volume Ramp-Down

7 DVDD Digital Supply for DSP Core, 4.5 V to 5.5 V

8 SDATA2 IN Serial Data Input 2

9 BCLK2 IN Bit Clock 2

10 LRCLK2 IN Left/Right Clock 2

11 SDATA1 IN Serial Data Input 1

12 BCLK1 IN Bit Clock 1

13 DGND Digital Ground

14 LRCLK1 IN Left/Right Clock 1

15 SDATA0 IN Serial Data Input 0

16 BCLK0 IN Bit Clock 0

17 LRCLK0 IN Left/Right Clock 0

18 CDATA IN SPI Data Input

19 CCLK IN SPI Data Bit Clock

20 CLATCH IN SPI Data Framing Signal

21 RESETB IN Reset Signal, Active Low

22 AVDD Analog 5 V Supply

23 AGND Analog GND

24 NC No Connect

25 VOUTS– OUT Negative Sub Analog DAC Output

26 VOUTS+ OUT Positive Sub Analog DAC Output

27 AGND Analog GND

28 VOUTR– OUT Negative Left Analog DAC Output

29 VOUTR+ OUT Positive Left Analog DAC Output

30 AVDD Analog 5 V Supply

31 AGND Analog GND

32 AVDD Analog 5 V Supply

33 VOUTL+ OUT Positive Left Analog DAC Output

34 VOUTL– OUT Negative Left Analog DAC Output

35 AGND Analog GND

36 NC No Connect

37 NC No Connect

38 VREF IN Connection for Filtered AVDD/2

39 FILTCAP IN Connection for Noise Reduction Capacitor

40 ZEROFLAG OUT Zero Flag Output. High when both left and right channels are 0 for 1024 frames.

41 DMUXO/TDMO OUT Dual-function Pin: Serial Data MUX Output/TDM Mode Output Data

42 BMUXO/TDMBC OUT Dual-function Pin: Bit Clock MUX Output/TDM Mode Bit Clock Output (256 f

43 LRMUXO/TDMFS OUT Dual-function Pin: Left/Right Clock MUX Output/TDM Mode Frame Sync

Clock Output

44 ODVDD Digital Supply Pin for Output Drivers, 2.5 V to 5.5 V

45 DCSOUT OUT Data Capture Serial Output for Data Capture Registers. Use in conjunction

with selected LRCLK and BCLK to form a 3-wire output.

46 COUT OUT SPI Data Output, Three-Stated when Inactive

47 MCLKOUT OUT Master Clock Output 512/256 f

48 DGND Digital Ground

S

S

S

(Frequency Selected by SPI Register)

S

)

S

REV. 0

–7–

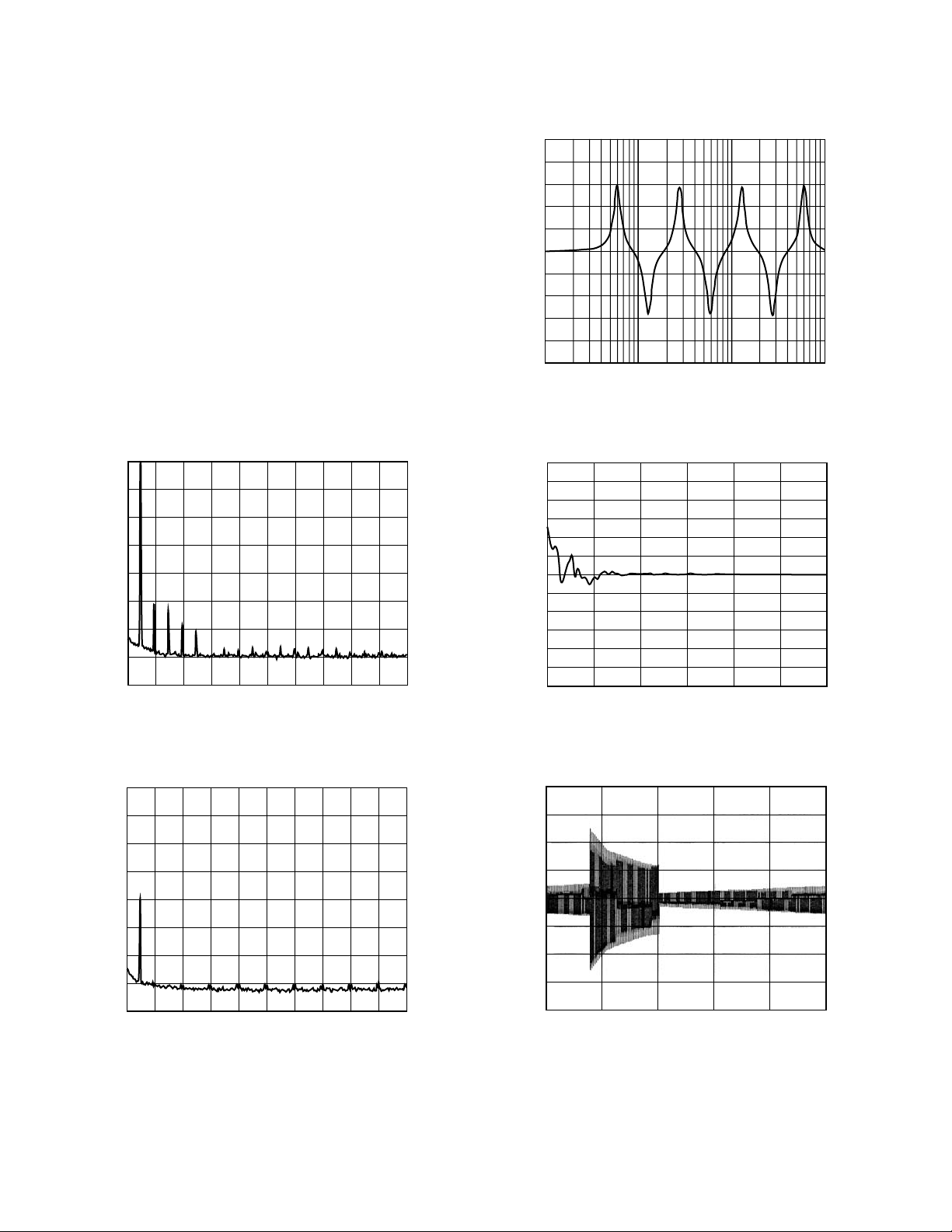

AD1953–Typical Performance Characteristics

PERFORMANCE PLOTS

The following plots demonstrate the performance achieved on the

actual silicon. TPC 1 shows an FFT of a full-scale 1 kHz signal

with a THD+N of –100 dB, which is dominated by a second

harmonic. TPC 2 shows an FFT of a –60 dB sine wave, demonstrating the lack of low level artifacts. TPC 3 shows a frequency

response plot with the seven equalization biquads set to an alternating pattern of 6 dB boosts and cuts. TPC 4 shows a linearity

plot, where the measurement was taken with the same equalization curve used to make TPC 3. When the biquad filters are not

in use, the signal passes through the filters with no quantization

effects. TPC 4 therefore demonstrates that using double-precision

math in the biquad filters has virtually eliminated any quantization

artifacts. TPC 5 shows a tone-burst applied to the compressor,

with the attack and recovery characteristics plainly visible. The

rms detector was programmed for normal rms time constants;

the hold/decay feature was not used for this plot.

0

–2

–4

–6

–8

–10

dB

–12

–14

–16

–18

–20

20 10k

50 200 500 5k

Hz

1k100

TPC 3. Frequency Response of EQ Biquad Filters

0

–20

–40

–60

–80

dB

–100

–120

–140

–160

0202468 141618

10 12

kHz

TPC 1. FFT of Full-Scale Sine Wave (32k Points)

0

–20

–40

–60

–80

dB

–100

–120

–140

–160

0202468 141618

10 12

kHz

TPC 2. FFT of –60 dB Sine Wave (32k Points)

3.0

2.5

2.0

1.5

1.0

0.5

0

dB

–0.5

–1.0

–1.5

–2.0

–2.5

–3.0

–120 0–100 –80 –20

–60 –40

dBFS

TPC 4. Linearity Plot

2.0

1.5

1.0

0.5

V

0

–0.5

–1.0

–1.5

–2.0

–120 0–100 –80 –20–60

ms

TPC 5. Tone-Burst Response with Compressor

Threshold Set to –20 dB

–8–

REV. 0

AD1953

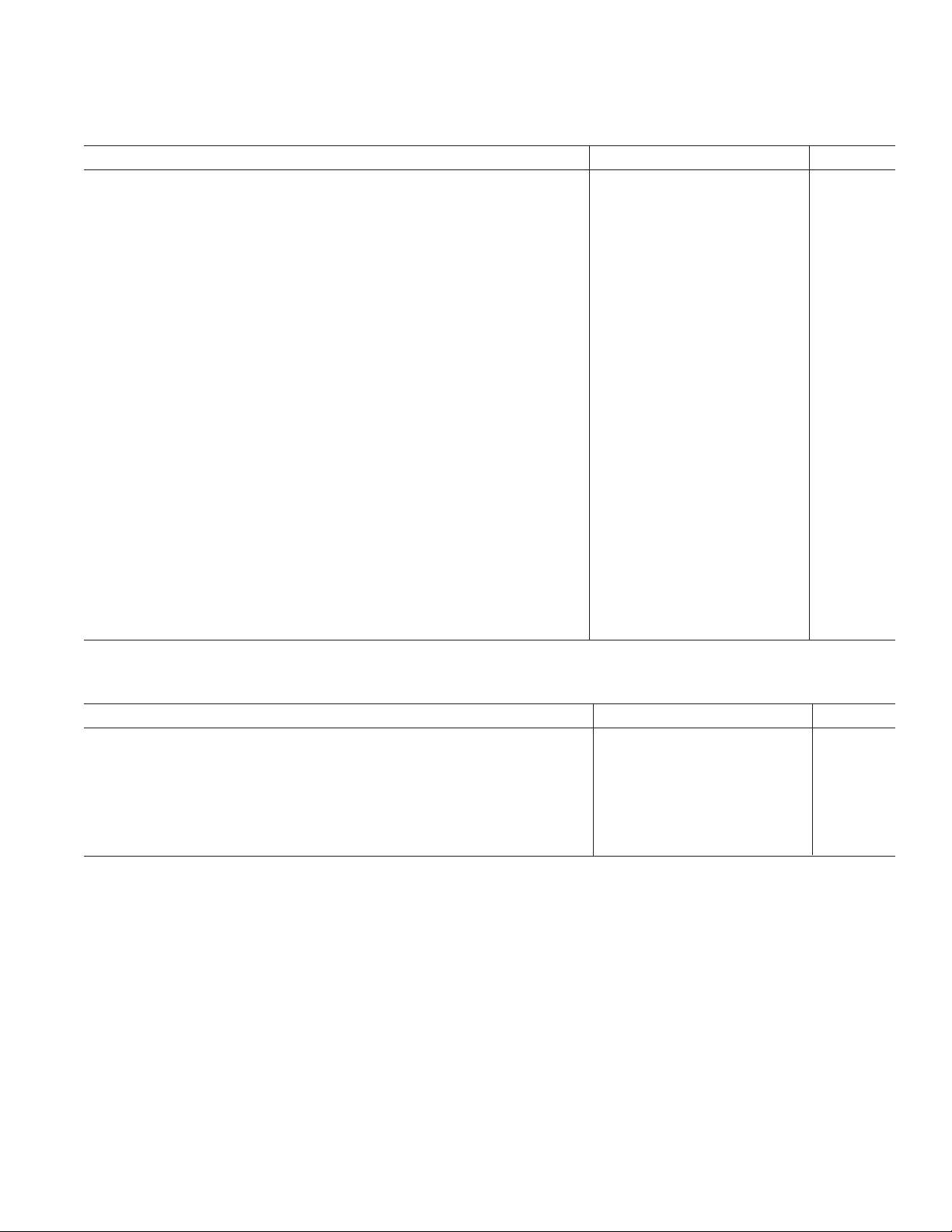

PRODUCT OVERVIEW (continued from page 1)

An extensive SPI port allows click-free parameter updates, along

with readback capability from any point in the algorithm flow.

The AD1953 also includes ADI’s patented multibit Σ-∆ DAC

architecture. This architecture provides 112 dB SNR and dynamic

range and THD+N of –100 dB. These specifications allow the

AD1953 to be used in applications ranging from low end

boom-boxes to high end professional mixing/editing systems.

The AD1953 has a digital output that allows it to be used purely

as a DSP. This digital output can also be used to drive an external DAC to extend the number of channels beyond the three

that are provided on the chip. This chip can be used with either

its default signal processing program or with a custom userdesigned program. Graphical programming tools are available

from ADI for custom programming.

Features

The AD1953 is comprised of a 26-bit DSP (48-bit with doubleprecision) for interpolation and audio processing, three multibit

Σ-∆ modulators, and analog output drive circuitry. Other features

include an on-chip parameter RAM using a “safe-upload” feature

for transparent and simultaneous updates of filter coefficients.

Digital de-emphasis filters are also included. On-chip input

selectors allow up to three sources of serial data and master

clock to be selected. The 3-channel configuration is especially

useful for 2.1 playback systems that include two

and a subwoofer. The default program

allows for independent

satellite speakers

equalization and compression/limiting for the satellite and

subwoofer outputs. Figure 1 shows the block diagram of the device.

The AD1953 contains a program RAM that is booted from an

internal program ROM on power-up. Signal-processing parameters are stored in a 256-location parameter RAM, which is

initialized on power-up by an internal boot ROM. New values

are written to the parameter RAM using the SPI port. The

values stored in the parameter RAM control the IIR equalization

filters, the dual-band compressor/limiter, the delay values, and

the settings of the stereo spreading algorithm.

The AD1953 has a very sophisticated SPI port that supports

complete read/write capability of both the program RAM and

the parameter RAM. Two control registers are also provided to

control the chip serial modes and various other optional features. Handshaking is included for ease of memory uploads/

downloads.

The AD1953 contains eight independent data-capture circuits

that can be programmed to tap the signal flow of the processor

at any point in the DSP algorithm flow. Two of these datacapture circuits can be read back over the SPI port, and the

other six are fed to a serial output pin operating either in TDM

mode (for all six channels) or 2-channel mode for simple connection to an external DAC. This allows the basic functionality

of the AD1953 to be easily extended.

The processor core in the AD1953 has been designed from the

ground up for straightforward coding of sophisticated compression/limiting algorithms. The AD1953 contains two independent

compressor/limiters with rms based amplitude detection and

attack/hold/release controls, together with an arbitrary compression curve that is loaded by the user into a lookup table that

resides in the parameter RAM. The compressor also features

look-ahead compression, which prevents compressor overshoots.

The AD1953 has a very flexible serial data input port that allows

for glueless interconnection to a variety of ADCs, DSP chips,

AES/EBU receivers, and sample rate converters. The AD1953

can be configured in left-justified, I

2

S, right-justified, or DSP

serial port compatible modes. It can support 16, 20, and 24 bits

in all modes. The AD1953 accepts serial audio data in MSB

first, twos complement format. The part can also be set up in a

4-channel serial input mode by simultaneously using the serial

input mux and the auxiliary serial input.

The AD1953 operates from a single 5 V power supply. It is

fabricated on a single monolithic integrated circuit and is housed

in a 48-lead LQFP package for operation over the temperature

range –40°C to +105°C.

REV. 0

SERIAL DATA I/O

GROUP

(2-CHANNEL

AND TDM)

AUX SERIAL

DATA INPUT

MASTER

CLOCK I/O

GROUP

SPI I/O

GROUP

DVD D AV D D ODVDD

3

3

3

3

3

FILTCAP AGND

3

DATA MEMORY, 512 26

3:1

AUDIO

DATA

1

MUX

3:1

MCLK

1

MUX

SPI PORT

NOTES

1

CONTROLLED THROUGH SPI CONTROL REGISTERS

2

DAC DOES NOT USE DIGITAL INTERPOLATION

SERIAL

IN

MCLK

GENERATOR

(256/512 fS IN)

OUT

256/512 f

S

CONTROL

REGISTERS

TRAP REG.

2

S, SPI)

(I

SAFELOAD

REGISTERS

1

3.23 (SINGLE PRECISION)

1

3.45 (DOUBLE PRECISION)

PROGRAM

512 35

BOOT ROM

MEMORY CONTROLLERS

RAM

Figure 1. Block Diagram

–9–

26 22

DSP CORE

DATA FORMAT:

PARAMETER

256 22

RESETB MUTE DE-EMPHASISZEROFLAG

RAM

REFERENCE

DAC –SW

BOOT ROM

DCSOUT TRAP

3

VREF

VOLTA G E

DAC – L

DAC – R

2

BIAS

COEFFICIENT

ROM

64 22

DGND

2

ANALOG

OUTPUTS

ANALOG

BIAS

DCSOUT

AD1953

Pin Functions

All input pins have a logic threshold compatible with TTL input

levels, and may therefore be used in systems with 3.3 V logic.

All digital output levels are controlled by the ODVDD pin,

which may range from 2.7 V to 5.5 V, for compatibility with a

wide range of external devices. (See Pin Function Descriptions.)

SDATA0, 1, 2—Serial Data Inputs.

One of these three inputs is selected by an internal MUX, set by

writing to Bits <7:6> in Control Register 2. Default is 00, which

selects SDATA0. The serial format is selected by writing to Bits

<3:0> of Control Register 0. See SPI Read/Write Data Formats

section for recommendations on how to change input sources

without causing a click or pop noise.

LRCLK0, 1, 2—Left/Right Clocks for Framing the Input Data.

The active LRCLK input is selected by writing to Bits <7:6>

in Control Register 2. Default is 00, which selects LRCLK0.

The interpretation of the LRCLK changes according to the serial

mode, set by writing to Control Register 0.

BCLK0, 1, 2—Serial Bit Clocks for Clocking in the Serial Data.

The active BCLK input is selected by writing to Bits <7:6> in

Control Register 2. Default is 00, which selects BCLK0. The

interpretation of BCLK changes according to the serial mode,

which is set by writing to Control Register 0.

DMUXO/TDMO, LRMUXO/TDMFS, BMUXO/TDMBC

Dual-function pins:

•

Function 1: Outputs of 3:1 MUX that selects one of the

three serial input groups.

•

Function 2: Used for 6-channel data capture outputs in

TDM Data Capture Mode.

These three pins operate as MUX outputs when Bit <8> of

Control Register 2 is a 1 and Bits <13:12> of Control Register 1

are 00. These pins may be used to send the selected serial input

signals to other external devices. The default is OFF.

In TDM mode, TDMBC provides a 256

×

fS clock signal,

TDMFS provides a frame sync signal, and TDMO provides the

TDM data for an external multichannel DAC or CODEC, such

as the AD1833 or AD1836 respectively. These output pins are

enabled by writing a 01 to Bits <13:12> of Control Register 1.

The default mode is 00, or OFF.

In TDM mode, the internal signals that are captured are controlled by writing Program Counter Trap numbers to SPI

addresses 268 to 273. When the internal Program Counter

contents are equal to the Trap values written to the SPI port, the

selected DSP register is transferred to parallel-to-serial registers

and shifted out of the TDMO pin.

MCLK0, 1, 2—Master Clock Inputs.

Active input selected by writing to Bits <5:4> of Control Register 2. The default is 00, which selects MCLK0. The master clock

frequency must be either 256 × f

or 512 × fS, where fS is the input

S

sampling rate. The master clock frequency is programmed by

writing to Bit <2> of Control Register 2. The default is 0, (512

). See Initialization section for recommendations concerning

× f

S

how to change clock sources without causing an audio click or

pop. Note that since the default MCLK source pin is MCLK0,

there must be a clock signal present on this pin on power-up so

that the AD1953 can complete its initialization routine.

MCLKO—Master Clock Output.

The master clock output pin may be programmed to produce

either 256 × fS, 512 × fS, or a copy of the selected MCLK input

pin. This pin is programmed by writing to Bits <1:0> of Control

Register 2. The default is 00, which disables the MCLKO pin.

CDATA—Serial Data In for the SPI Control Port.

See SPI Port section for more information on SPI port timing.

COUT—Serial Data Output.

This is used for reading back registers and memory locations. It

is three-stated when an SPI read is not active. See SPI Port

section for more information on SPI port timing.

CCLK—SPI Bit Rate Clock.

This pin either may run continuously or be gated off between

SPI transactions. See SPI Port section for more information on

SPI port timing.

CLATCH—SPI Latch Signal.

This pin must go LOW at the beginning of an SPI transaction,

and HIGH at the end of a transaction. Each SPI transaction

may take a different number of CCLKs to complete, depending

on the address and read/write bit that are sent at the beginning

of the SPI transaction. Detailed SPI timing information is given

in the SPI Port section.

RESETB—Active-Low Reset Signal.

After RESETB goes HIGH, the AD1953 goes through an initialization sequence where the program and parameter RAMs

are initialized with the contents of the on-board boot ROMs. All

SPI registers are set to 0, and the data RAMs are also zeroed.

The initialization is complete after 1024 MCLK cycles. Since

the MCLK IN FREQ SELECT (Bit <2> in Control Register 2)

defaults to 512 × f

at power-up, this initialization will proceed

S

at the external MCLK rate and will take 1024 MCLK cycles to

complete, regardless of the absolute frequency of the external

MCLK. New values should not be written to the SPI port until

the initialization is complete.

ZEROFLAG—Zero-Input Indicator.

This pin will go HIGH if both serial inputs have been inactive

(zero data) for 1024 LRCLK cycles. This pin may be used to

drive an external mute FET for reduced noise during digital

silence. This pin also functions as a test out pin, controlled by

the test register at SPI address 511. While most test modes are

not useful to the end user, one may be of some use. If the test

register is programmed with the number 7 (decimal), the

ZEROFLAG output will be switched to the output of the internal pseudo-random noise generator. This noise generator

operates at a bit rate of 128 × f

24

cycles. This mode may be used to generate white noise

per 2

, and has a repeat time of once

S

(or, with appropriate filtering, pink noise) to be used as a test

signal for measuring speakers or room acoustics.

DCSOUT—Data Capture Serial Out.

This pin will output the DSP’s internal signals, which can be

used by external DACs or other signal-processing devices. The

signals that are captured and output on the DCSOUT pin are

controlled by writing Program Counter Trap numbers to SPI

addresses 263 (for the left output) and 264 (for the right output).

When the internal Program Counter contents are equal to the

Trap values written to the SPI port, the selected DSP register is

transferred to the DCSOUT parallel-to-serial registers and

–10–

REV. 0

AD1953

shifted out on the DCSOUT pin. Table XXI shows the Program Counter Trap values and register-select values that should

be used to tap various internal points of the algorithm flow.

The DCSOUT pin is meant to be used in conjunction with the

LRCLK and BCLK signals that are provided to the serial input

port. The format of DCSOUT is the same as the format used

for the serial port. In other words, if the serial port is running in

2

I

S mode, then the DCSOUT pin, together with the LRCLK0

and BCLK0 pins (assuming input 0 is selected), will form a

valid 3-wire I

The DCSOUT pin can be used for a variety of purposes. If the

DCSOUT pin is used to drive another external DAC, then a 4.1

system is possible using a new program downloaded into the

program RAM.

AUXDATA—Auxiliary Serial Data Input.

The AUXDATA pin may be used in conjunction with a custom

program to access two extra channels of serial input data, allowing for a total of four input channels. The serial format is identical

to the selected format of SDATA0, 1, 2. The AUXDATA pin is

synchronous to the selected LRCLK and BCLK signal, and therefore should have the same timing as the main serial input signal.

MUTE—Mute Output Signal.

When this pin is asserted HIGH, a ramp sequence is started that

gradually reduces the volume to zero. When deasserted, the

volume ramps from zero back to the original volume setting.

The ramp speed is timed so that it takes 10 ms to reach zero

volume when starting from the default 0 dB volume setting.

VOUTL+, VOUTL– —Left-Channel Differential Analog Outputs. Full-scale outputs correspond to 1 V rms on each output pin,

or 2 V rms differential, assuming a VREF input voltage of 2.5 V. The

full-scale swing scales directly with VREF. These outputs are

capable of driving a load of > 5 kΩ, with a maximum peak current

of 1 mA from each pin. An external third-order filter is recommended for filtering out-of-band noise.

VOUTR+, VOUTR– —Right Channel Differential Outputs.

Output characteristics are the same as for VOUTL+ and VOUTL–.

2

S output.

VOUTS+, VOUTS– —Sub Channel Differential Outputs.

These outputs are designed to drive loads of 10 kΩ or greater,

with a peak current capability of 250 µA. This output does not

use digital interpolation, as it is intended for low frequency

application. An external third-order filter with a cutoff frequency

< 2 kHz is recommended.

VREF—Analog Reference Voltage Input.

The nominal VREF input voltage is 2.5 V; the analog gain

scales directly with the voltage on this pin. When using the

AD1953 to drive a power amplifier, it is recommended that the

VREF voltage be derived by dividing down and heavily filtering

the supply to the power amplifier. This provides a benefit if the

compressor/limiter in the AD1953 is used to prevent amplifier

clipping. In this case, if the DAC output voltage is scaled to the

amplifier power supply, a fixed compressor threshold can be

used to protect an amplifier whose supply may vary over a wide

range. Any ac signal on this pin will cause distortion, and a large

decoupling capacitor may therefore be necessary to ensure that

the voltage on VREF is clean. The input impedance of VREF is

greater than 1 MΩ.

FILTCAP—Filter Capacitor Point.

This pin is used to reduce the noise on an internal biasing point

in order to provide the highest performance. It may not be necessary to connect this pin, depending on the quality of the layout

and grounding used in the application circuit.

DVDD—Digital VDD for Core.

5 V nominal.

ODVDD—Digital VDD for All Digital Outputs.

Variable from 2.7 V to 5.5 V.

DGND (2)—Digital Ground.

AVDD (3)—Analog VDD.

5 V nominal. For best results, use a separate regulator for AVDD.

Bypass capacitors should be placed close to the pins and connected directly to the analog ground plane.

AGND (3)—Analog Ground.

For best performance, separate nonoverlapping analog and

digital ground planes should be used.

REV. 0

–11–

Loading...

Loading...