SigmaDSP® Multichannel

Anomaly Sheet for All Revisions

This anomaly list represents the known bugs, anomalies, and workarounds for the AD1940 and AD1941 SigmaDSP products. The

anomalies listed apply to all AD1940/AD1941 packaged material branded as follows:

First Line AD1940 or AD1941

Analog Devices, Inc. is committed, through future silicon revisions, to continuously improving silicon functionality. Analog Devices tries

to ensure that these future silicon revisions remain compatible with your present software/systems implementing the recommended

workarounds outlined here.

28-Bit Audio Processor

AD1940/AD1941

AD1940/AD1941 SILICON REVISION HISTORY

Silicon

Revision

Identifier

All silicon branded

Kernel

Revision

Identifier

Chip Marking

AD1940YST

AD1941YST

Silicon

Status

Release Rev. 0 2

Anomaly Sheet No. of Reported Anomalies

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

AD1940/AD1941

ANOMALIES

1. Incorrect Polarity of Serial Input Port Left-Justified Mode [er001]

Background: The input data format is set in the serial input control register.

Issue:

Workarounds:

When the AD1940/AD1941 serial input port is set to left-justified mode with left-justified formatted data being input to

the part, the channels will be swapped. This means that in the SigmaDSP core the left channel data is present when

LRCLK is low, and the right channel data shows on the high half of the LRCLK frame.

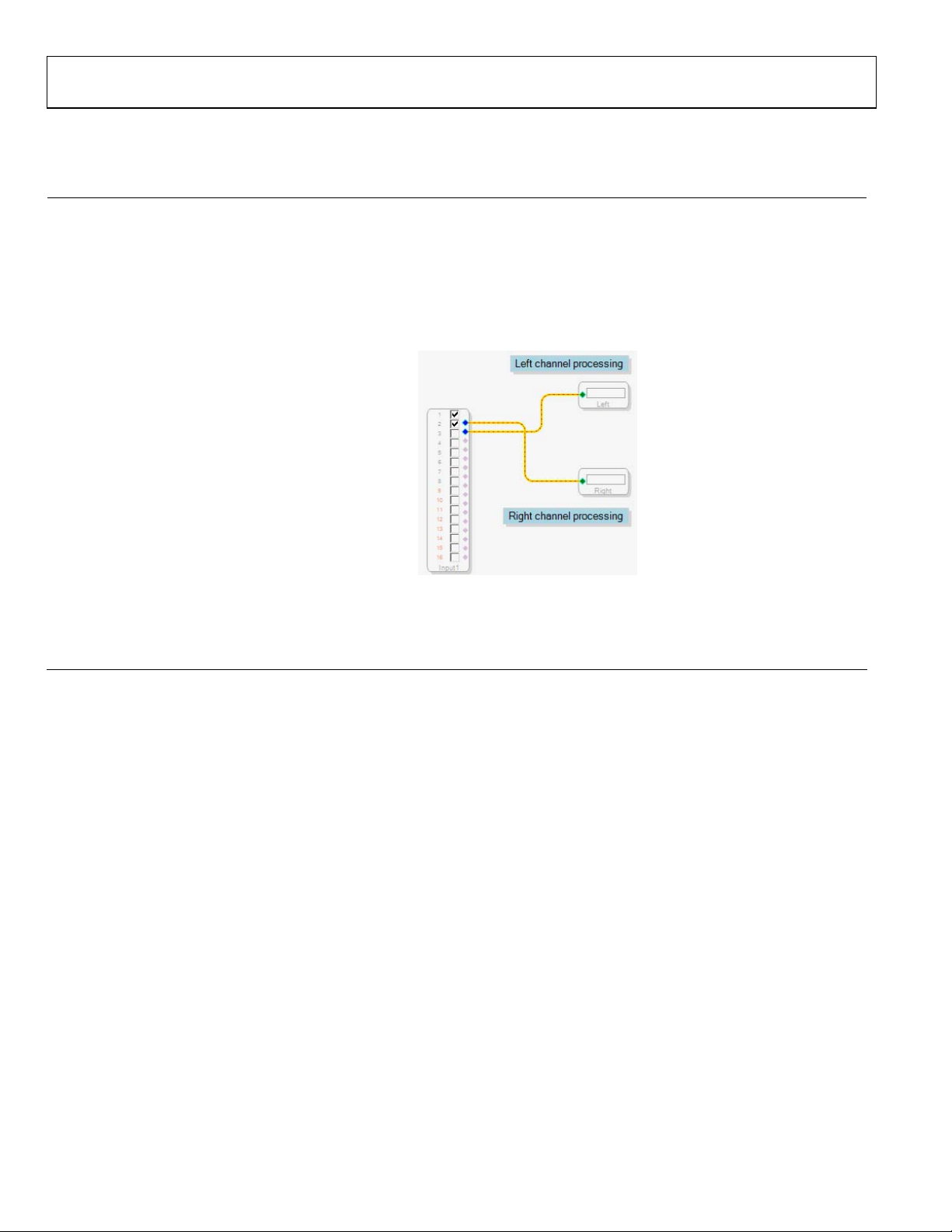

1. The easiest solution for this problem is to simply flip the channels from the serial input block in SigmaStudio™. In

this case, the serial input control register should be set up properly for left-justified mode, as described in the Data

Format Configurations table in the AD1940/AD1941 data sheet. Figure 1 shows how this can be done in

SigmaStudio. If SDATA_IN0 is used in left-justified mode, then SigmaStudio Input 1 is the right channel data, and

SigmaStudio Input 2 is the left channel data. This is the reverse of what is expected in left-justified mode.

2. In the serial input control register (Address 2646), set Bit 4 to 1 for “Frame begins on rising edge.” Normally, a left-

Related Issues: None.

Figure 1. Swapping Channels in SigmaStudio

justified frame begins on the falling edge. If this solution is used, there is a one-sample offset between the left and

right channels in a frame.

Rev. 0 | Page 2 of 4

Loading...

Loading...