Analog Devices AD1803JRU Datasheet

a

Modem/Telephony Codec

AD1803

FEATURES

Low Power Modem Telephony Codec

16-Bit Oversampling ⌺-⌬ Converter Technology

Intel AC’97 Rev 2.1-Compliant Modem Codec

Implementation

AC’97 or DSP Style Serial Interface

Supports All Modem/Fax Standards Including V.90

Multiple Crystal/Clock Rates Supported

Programmable Gain, Attenuation and Mute

On-Chip Signal Filters

Digital Interpolation and Decimation Filters

Analog Output Low Pass

Programmable Sample Rates

From 6.4 kHz to 16 kHz

With 1 Hz, 8/7 Hz and 10/7 Hz Resolution

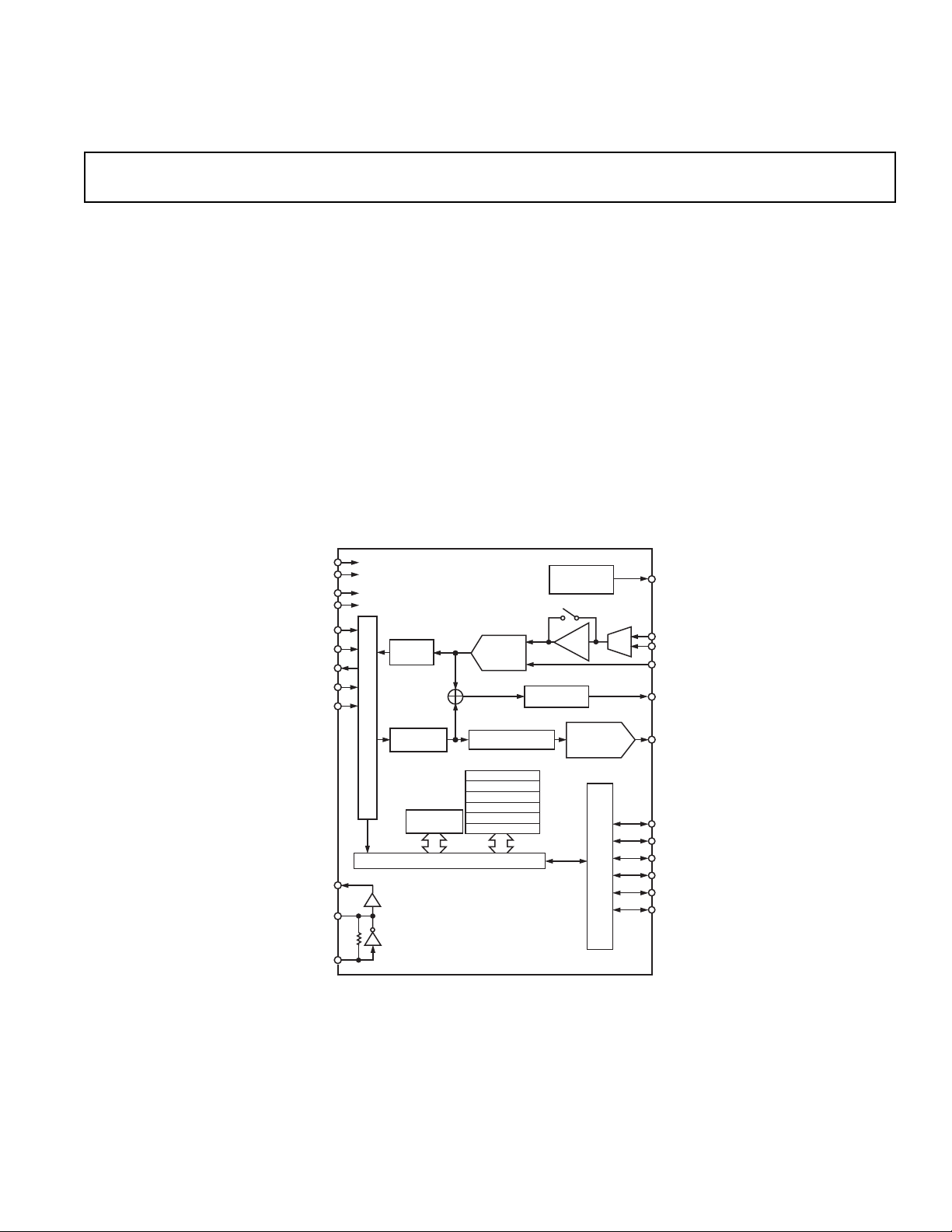

FUNCTIONAL BLOCK DIAGRAM

AVDD

AGND

DVDD

DGND

BIT_CLK

SYNC

SDATA_IN

SDATA_OUT

RESET

AC'97/DSP SERIAL PORT

ADC

FILTER

DAC

FILTER

AD1803

Digital Codec Engine with Variable Sample

Rate Conversion

Digital Monitor Speaker Output

24-Lead TSSOP Package

0.6 m CMOS Technology

Operation from 3.3 V or 5 V Supply

Advanced Power Management

APPLICATIONS

Modems (PC and Embedded)

Voice and Telephony

Fax Machines, Answering Machines, Speakerphones

PBX Systems

Smart Appliances

REFERENCE DESIGN

Available

⌺-⌬ ADC

PWM BLOCK

⌺-⌬ MODULATOR

VOLTAGE

REFERENCE

+20dB

DAC FILTER

+ GAIN

/ATTEN

MUX

VREF

G[1]/MIC

Rx

FILT

G[4]/MOUT

Tx

ADDRESS

REGISTER

REGISTER CONTROL LOGIC

CLK_OUT

XTALO

XTALI

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

CONTROL

REGISTERS

G[0]

G[2]

G[3]/WAKE

G[5]

G[6]

GENERAL-PURPOSE I/O

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

G[7]

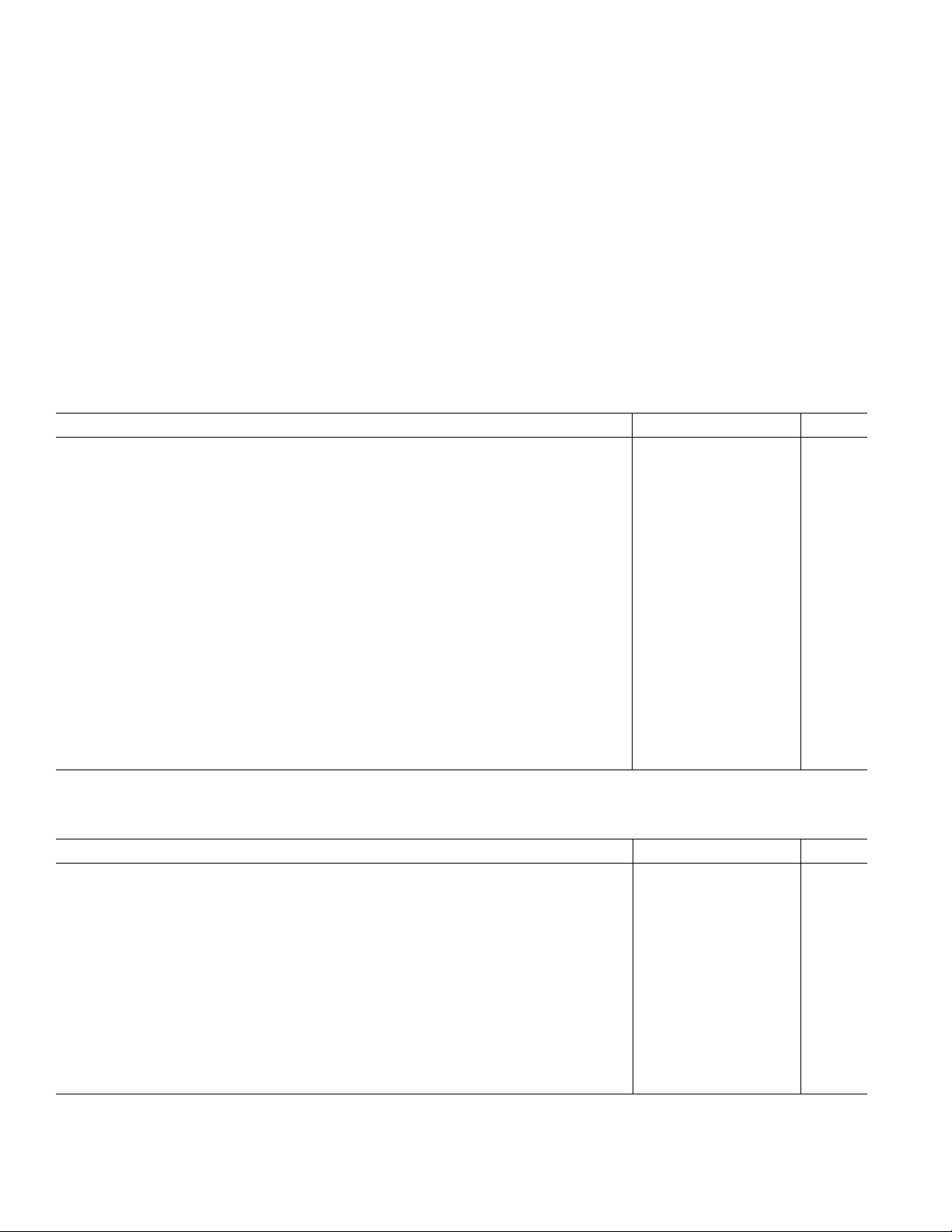

AD1803–SPECIFICATIONS

STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

Temperature 25°C

Digital Supply 3.3 V/5 V

Analog Supply 3.3 V/5 V

Sample Rate (f

) 8 kHz

S

Input Signal 1008 Hz

Analog Output Pass Band 20 Hz to 4 kHz

ADC FFT Size 512

DAC FFT Size 4096

V

IH

V

IL

V

OH

V

OL

I

OH

I

OL

ADC RECEIVE PATH

2.1 V

1.2 V

2.9 V

0.3 V

–2.0 mA

+2.0 mA

Full-Scale Input Voltage (RMS Values Assume Sine Wave Input, PGA Gain = 0 dB,

Offset Error = 0% of FS) 1.56 V rms

AD1803 Rx Input (0 dBm) 2.1 2.2 2.3 V p-p

Resistance—Rx Input*

with 0 dB Gain 110 kΩ

with +20 dB Gain 10 kΩ

Capacitance—Rx Input* 15 pF

Rx Programmable Gain

Gain Step Size (0 dB to 42.5 dB, All Steps Tested) 1.0 1.5 2.0 dB

Input Gain Span (Note: The ADC Gain is achieved using a 0 dB to 22.5 dB Variable Gain 41.5 42.5 43.5 dB

Stage and a 20 dB Fixed Gain Stage. The 22.5 dB to 42.5 dB Gain Steps are achieved by

enabling the 20 dB Gain Stage.)

Analog-to-Digital Converter

Dynamic Range (–60 dB Input, THD+N Referenced to Full-Scale, PGA Gain = 0 dB) 85 90 dB

Dynamic Range (–60 dB Input, THD+N Referenced to Full-Scale, PGA Gain = 6 dB)* 90 dB

Dynamic Range (–60 dB Input, THD+N Referenced to Full-Scale, PGA Gain = +12 dB)* 90 dB

THD+N (–1 dB Input Referenced to Full-Scale) –90 –85 dB

Signal-to-Intermodulation Distortion (CCIF Method)* 80 dB

Offset Error (0 V Analog Input, PGA Gain = 0 dB) 1 5 % of FS

*Guaranteed, not tested.

Specifications subject to change without notice.

DAC Output Test Conditions

0 dB Attenuation Relative to Full-Scale

Input 0 dB

Mute Off

10 kΩ Output Load

ADC Input Test Conditions

Autocalibrated

0 dB PGA Gain

Mute Off

Input –1.0 dB Relative to Full-Scale

Min Typ Max Unit

DAC TRANSMIT PATH

Min Typ Max Unit

Digital-to-Analog Converter

Dynamic Range (–60 dB Input, THD+N Referenced to Full-Scale, Output Gain = 0 dB) 85 dB

THD+N (–1 dB Input Referenced to Full-Scale) –75 dB

Signal-to-Intermodulation Distortion (CCIF Method)* 80 dB

Total Out-of-Band Energy (Measured from 0.555 × f

to 100 kHz)* –40 dB

S

DC Offset 100 mV

Programmable Gain/Attenuator

Step Size (+12 dB to –34.5 dB, All Steps Tested) 1.0 1.5 2.0 dB

Output Attenuation Span 45.5 46.5 48 dB

Full-Scale Output Voltage

AD1803 Tx Output (0 dBm) 2.1 2.2 2.3 V p-p

Pin Capacitance—AD1803 Tx 15 pF

Load Capacitance—AD1803 Tx 100 pF

*Guaranteed, not tested.

Specifications subject to change without notice.

–2–

REV. 0

AD1803

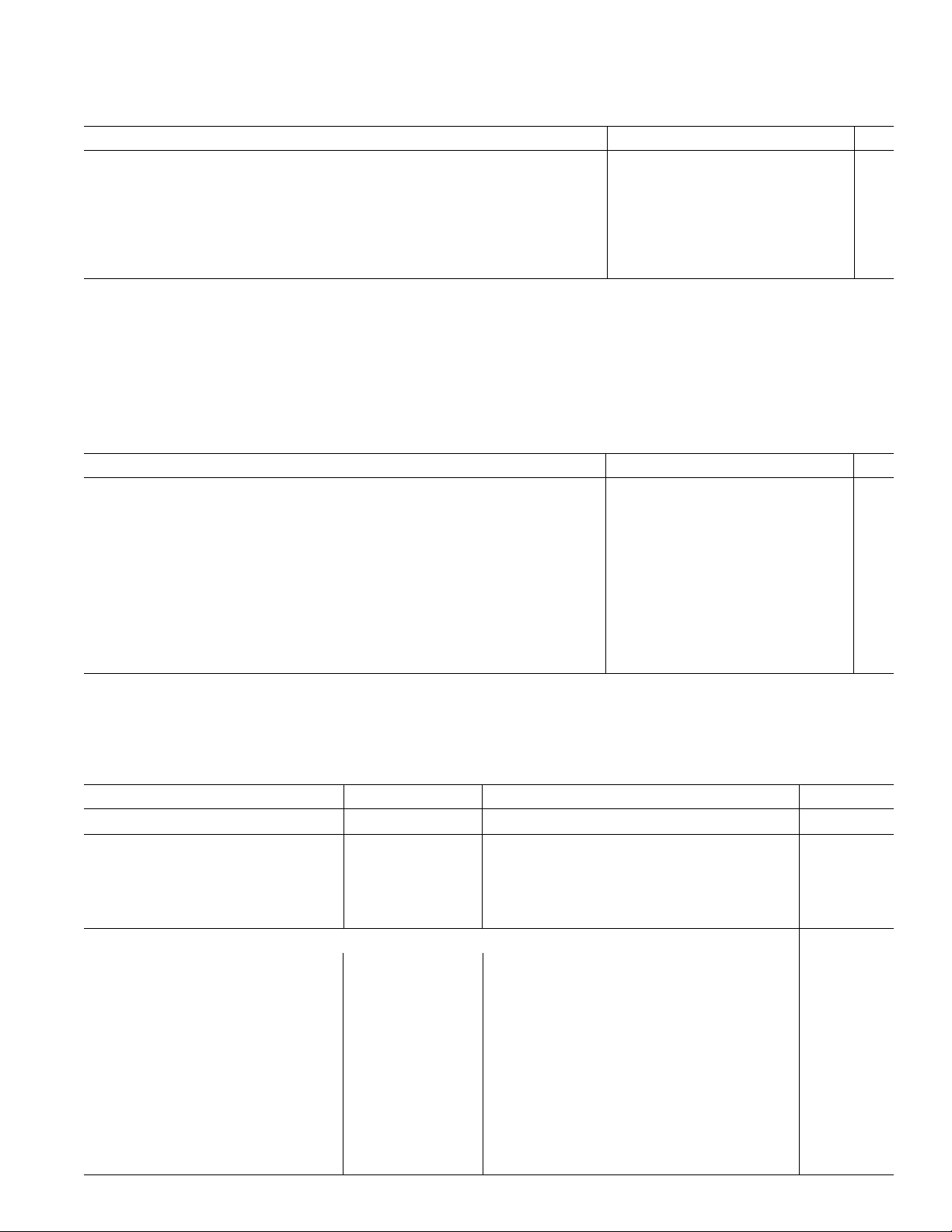

MONITOR OUTPUT

Min Typ Max Unit

Digital-to-Analog Converter

Dynamic Range (–60 dB Input, THD+N Referenced to Full-Scale, A-Weighted)* 50 dB

THD+N (Referenced to Full-Scale)* 0.316 1 %

–50 –40 dB

Programmable Gain/Attenuator

Step Size (–18 dB to +45 dB)* 2.4 3.0 3.6 dB

Output Attenuation Span* 63 dB

NOTES

*Guaranteed, not tested.

Specifications subject to change without notice.

The table above assumes the G[4]/MOUT pin is loaded with a 1 kΩ resistor in series with a parallel 4.7 kΩ resistor and 100 nF

capacitor combination tied to digital ground. This filter, with the output taken from the middle node, has a 1500 Hz corner to filter

out high-frequency Σ-∆ noise, and generates an approximate 1 V p-p output when using a 5 V digital supply with the monitor output

configured as first order (Bits MDM[1:0] set to 10 in Register 0 × 60 Bank 2) if the filter output load is greater than or equal

to 20 kΩ.

DIGITAL DECIMATION AND INTERPOLATION FILTERS

1

Min Typ Max Unit

Pass-Band Edge (–0.22 dB Point) 0.445 × f

Pass-Band (–3.0 dB Point) 0.490 × f

Hz

S

Hz

S

Pass-Band Ripple 0.0 –0.2 dB

Transition Band 0.445 × f

Stop-Band Edge

2

0.555 × f

S

S

0.555 × fSHz

Hz

Stop-Band Rejection (Plus 3 dB Roll-Off) 78.0 dB

Group Delay 21/f

S

s

Group Delay Variation Over Pass Band

0 kHz to 4 kHz 0.45 µs

0 kHz to 8 kHz 1.30 µs

Sample Rate 6.4 16 kHz

NOTES

1

Guaranteed, not tested.

2

The stop band repeats itself at multiples of 64 × fS, where fS is the sampling frequency. Thus the digital filter will attenuate to –78.0 dB or better across the frequency

spectrum except for a range ± 0.555 × fS wide at multiples of 64 × fS.

Specifications subject to change without notice.

TYPICAL SUPPLY CURRENT (For Most Common Modes of Operation)

Resource 3.3 V 5.0 V Register Writes To Enter Mode Assumption

GPIO Weak Pull-Up Current per Pin ~100 ~140 µA Default Settings After Power-On RESET

While RESET Is Asserted:

XTAL Off (All Down) <30.0 <40.0 µA Default Settings After Power-On RESET a

XTALI Enabled: Nominal Power 1.4 2.4 mA 5C:R34P4 = 1

XTALI Enabled: Low Power 1.0 1.7 5C:R34P4 = 1, 64b1:XTLP = 1

and CLKOUT Pin Running 1.6 3.2 and 5C:CLKEA = 1 b

While RESET Is Deasserted and Analog and Digital Codec in Full Power Mode

SPORT and CLKOUT Active 2.6 6.4 Default Settings After Power-On RESET b, c

and XTAL in Low Power Mode 2.2 5.7 and 64b1:XTLP = 1 b, c

and CLKOUT Inactive (Low) 1.7 4.3 and 5C:CLKED = 0 c

and VREF Powered Up 1.9 4.5 and 3E:VPDN = 0 c

and ADC Enabled 7.3 12.4 and 3E:APDN = 0 c

or

and DAC Enabled 8.2 13.7 and 3E:DPDN = 0 c, f

or

and ADC + DAC Enabled 9.2 14.7 and 3E:APDN = DPDN = 0 c, f

or

and ADC, DAC, + MON Enabled 9.3 14.9 and 3E:APDN = DPDN = 0, 5E : GPMON = 1 c, d, f

or

and ADC, DAC, + MON Enabled 10.2 16.3 and 3E:APDN = DPDN = 0, 5E : GPMON = 1 c, e, f

REV. 0

–3–

AD1803

ASSUMPTIONS

a Assumes all inputs are static (not switching) and all output loads are capacitive (nonresistive).

b Excludes current drawn by CLKOUT pin board loading.

c Assumes the serial interface is configured in AC’97 primary mode with 20 pF loads on pins SDATA_IN and BIT_CLK. Typical current will be approximately

0.8 mA less if the serial interface is configured in DSP mode with 20 pF loads on pins SYNC, BIT_CLK, and SDATA_IN (due to a lower BIT_CLK frequency).

d Assumes a 20 pF load on Pin G[4]/MOUT.

e Assumes the G[4]/MOUT pin is loaded with a 1 kΩ resistor in series with a parallel 4.7 kΩ resistor and 100 nF capacitor combination tied to digital ground. This

filter, with the output taken from the middle node, has a 1500 Hz corner to filter out high-frequency Σ-∆ noise, and generates an approximate 1 V p-p output when

using a 5 V digital supply with the Monitor output configured as first order (Bits MDM[1:0] set to 10 in Register 0 × 60 Bank 2) if the filter output load is greater

than or equal to 20 kΩ.

f Assumes no DAC load. 0.6 mA should be added if a 600 Ω load is used.

g All currents in mA unless otherwise noted.

Specifications subject to change without notice.

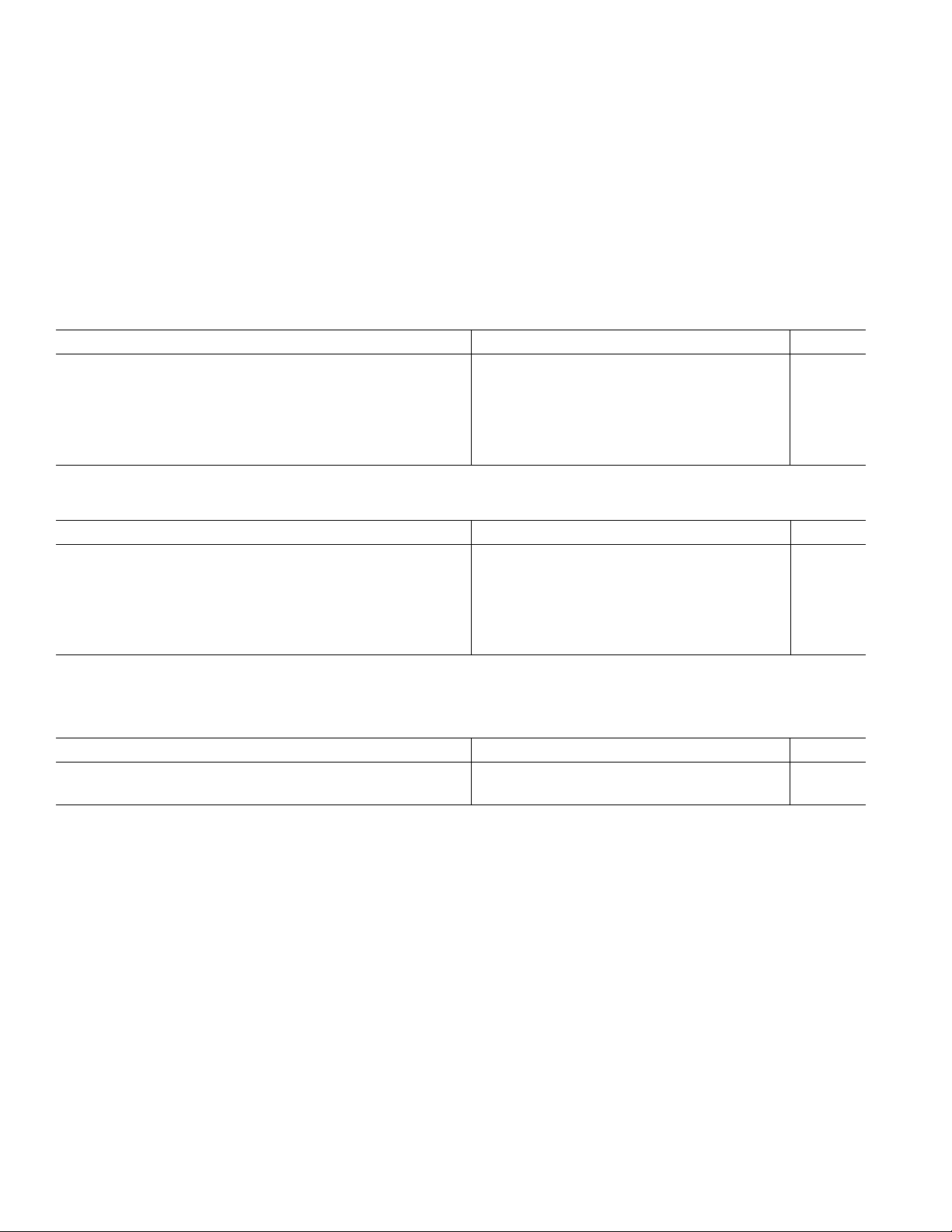

STATIC DIGITAL SPECIFICATIONS

Min Typ Max Unit

High Level Input Voltage (V

Low Level Input Voltage (V

High Level Output Voltage (V

Low Level Output Voltage (V

Input Leakage Current –10 +10 µA

Output Leakage Current –10 +10 µA

Specifications subject to change without notice.

POWER SUPPLY

Power Supply Range—Analog (3.3 V/5 V) AVDD 3.0/4.75 3.6/5.25 V

Power Supply Range—Digital (3.3 V/5 V) DVDD 3.0/4.75 3.6/5.25 V

Analog and Digital Supply Current—5 V *

Analog and Digital Supply Current—3.3 V *

Power Supply Rejection (100 mV p-p Signal @ 1 kHz) 40 dB

(At Both Analog and Digital Supply Pins, Both ADCs and DACs)

NOTES

*Refer to table on typical supply current.

Specifications subject to change without notice.

): Digital Inputs 0.65 × DVDD V

IH

) 0.35 × DVDD V

IL

), IOH = –0.5 mA 0.9 × DVDD V

OH

), IOL = +0.5 mA 0.1 × DVDD V

OL

Min Typ Max Unit

CLOCK SPECIFICATIONS

Min Typ Max Unit

Input Clock Frequency 12.288 24.576 32.768 MHz

Recommended Clock Duty Cycle 45 50 55 %

Specifications subject to change without notice.

–4–

REV. 0

AD1803

TIMING PARAMETERS (Guaranteed Over Operating Temperature Range and Supply Power)

Parameter Symbol Min Typ Max Unit

Serial Port—AC’97 Mode

RESET Active Low Pulsewidth t

RESET Inactive to BIT_CLK Start-Up Delay t

SYNC Active High Pulsewidth (Warm RESET)t

SYNC Inactive to BIT_CLK Start-Up Delay (Warm RESET)t

RST_LOW

RST2CLK

SYNC_HIGH

SYNC2CLK

BIT_CLK Frequency 12.288 MHz

BIT_CLK Period t

CLK_PERIOD

BIT_CLK Output Jitter* 750 ps

BIT_CLK High Pulsewidth t

BIT_CLK Low Pulsewidth t

CLK_HIGH

CLK_LOW

SYNC Frequency 48.0 kHz

SYNC Period t

Setup to Falling Edge of BIT_CLK t

Hold from Falling Edge of BIT_CLK t

Propagation Delay t

BIT_CLK Rise Time t

BIT_CLK Fall Time t

SYNC Rise Time t

SYNC Fall Time t

SDATA_IN Rise Time t

SDATA_IN Fall Time t

SDATA_OUT Rise Time t

SDATA_OUT Fall Time t

End of Slot 2 to BIT_CLK, SDATA_IN Low (MLNK Set) t

Setup to Trailing Edge of RESET t

SYNC_PERIOD

SETUP

HOLD

CO

RISECLK

FALLCLK

RISESYNC

FALLSYNC

RISEDIN

FALLDIN

RISEDOUT

FALLOUT

S2_PDOWN

SETUP2RST

(Applies to SYNC, SDATA_OUT)

Rising Edge of RESET to HI-Z Delay (ATE Test Mode) t

OFF

1.0 µs

162.8 ns

1.3 µs

162.8 ns

81.4 ns

36.62 40.69 44.76 ns

36.62 40.69 44.76 ns

20.8 µs

10.0 ns

10.0 ns

15 ns

246ns

246ns

246ns

246ns

246ns

246ns

246ns

246ns

2 1000 ns

15 ns

25 ns

Parameter Symbol Min Typ Max Unit

Serial Port—DSP Mode

RESET Active Low Pulsewidth t

RESET Inactive to BIT_CLK Start-Up Delay t

RST_LOW

RST2CLK

1.0 µs

162.8 ns

BIT_CLK Frequency 4.096 MHz

BIT_CLK Period t

CLK_PERIOD

244.14 ns

BIT_CLK Output Jitter* 750 ps

SYNC Frequency 8 kHz

SYNC Period t

Setup to Falling Edge of BIT_CLK t

Hold from Falling Edge of BIT_CLK t

Propagation Delay t

BIT_CLK Rise Time t

BIT_CLK Fall Time t

SYNC Rise Time t

SYNC Fall Time t

SDATA_IN Rise Time t

SDATA_IN Fall Time t

SDATA_OUT Rise Time t

SDATA_OUT Fall Time t

Setup to Trailing Edge of RESET t

SYNC_PERIOD

SETUP

HOLD

CO

RISECLK

FALLCLK

RISESYNC

FALLSYNC

RISEDIN

FALLDIN

RISEDOUT

FALLDOUT

SETUP2RST

10.0 ns

10.0 ns

246ns

246ns

246ns

246ns

246ns

246ns

246ns

246ns

15 ns

125 µs

15 ns

(Applies to SYNC, SDATA_OUT)

Rising Edge of RESET to HI-Z Delay (ATE Test Mode) t

NOTES

*Output jitter is directly dependent on crystal input jitter.

Specifications subject to change without notice.

OFF

25 ns

REV. 0

–5–

AD1803

RESET

BIT_CLK

SYNC

BIT_CLK

t

RST_LOW

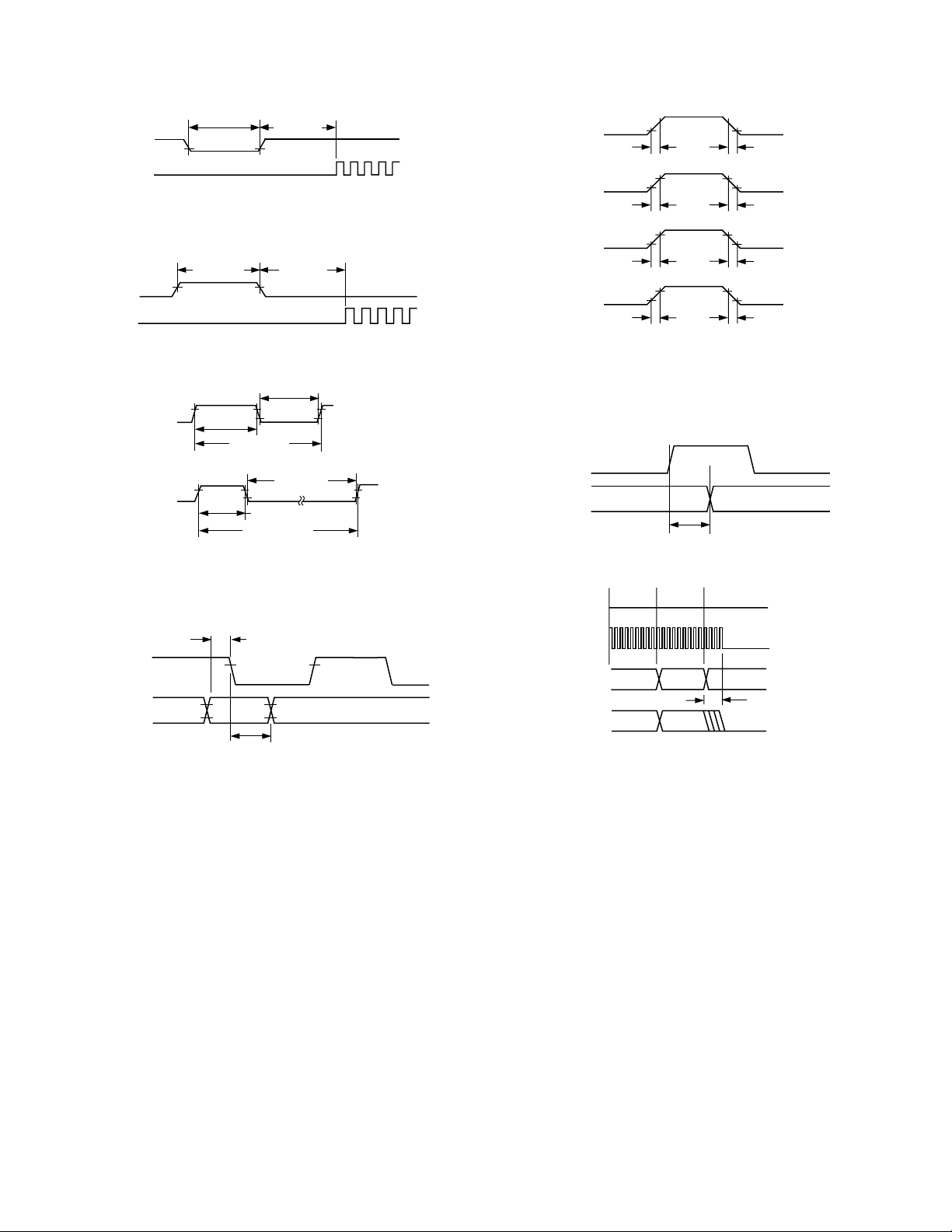

Figure 1. Cold

t

SYNC_HIGH

t

RST2CLK

RESET

t

SYNC2CLK

BIT_CLK

SYNC

SDATA_IN

SDATA_OUT

t

RISECLK

t

RISESYNC

t

RISEDIN

t

RISEDOUT

t

FALLCLK

t

FALLSYNC

t

FALLDIN

t

FALLDOUT

BIT_CLK

SYNC

SDATA_OUT

Figure 2. Warm

BIT_CLK

SYNC

t

CLK_HIGH

t

CLK_PERIOD

RESET

t

CLK_LOW

t

SYNC_LOW

t

SYNC_HIGH

t

SYNC_PERIOD

Figure 3. Clock Timing

t

SETUP

t

HOLD

Figure 4. Data Setup and Hold

Figure 5. Signal Rise and Fall Time

BIT_CLK

SDATA_IN

t

CO

Figure 6. Propagation Delay

WRITE

SLOT 2

DATA

MLNK

DON’T

CARE

t

S2_PDOWN

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

SLOT 1

TO 0x56

NOTE: BIT_CLK NOT TO SCALE

Figure 7. AC Link Low Power Mode Timing

–6–

REV. 0

AD1803

ABSOLUTE MAXIMUM RATINGS*

Min Max Unit

Power Supplies

Digital (DVDD) –0.3 +6.0 V

Analog (AVDD) –0.3 +6.0 V

Input Current (Except Supply Pins) ± 10.0 mA

Analog Input Voltage (Signal Pins) –0.3 AVDD

+ 0.3 V

Digital Input Voltage (Signal Pins) –0.3 DVDD + 0.3 V

Ambient Temperature (Operating) 0 70 °C

Storage Temperature –65 +150 °C

*Stresses greater than those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating

= T

T

AMB

= Case Temperature in °C

T

CASE

P

= Power Dissipation in W

D

= Thermal Resistance (Case-to-Ambient)

θ

CA

= Thermal Resistance (Junction-to-Ambient)

θ

JA

θ

= Thermal Resistance (Junction-to-Case)

JC

—(PD × θCA)

CASE

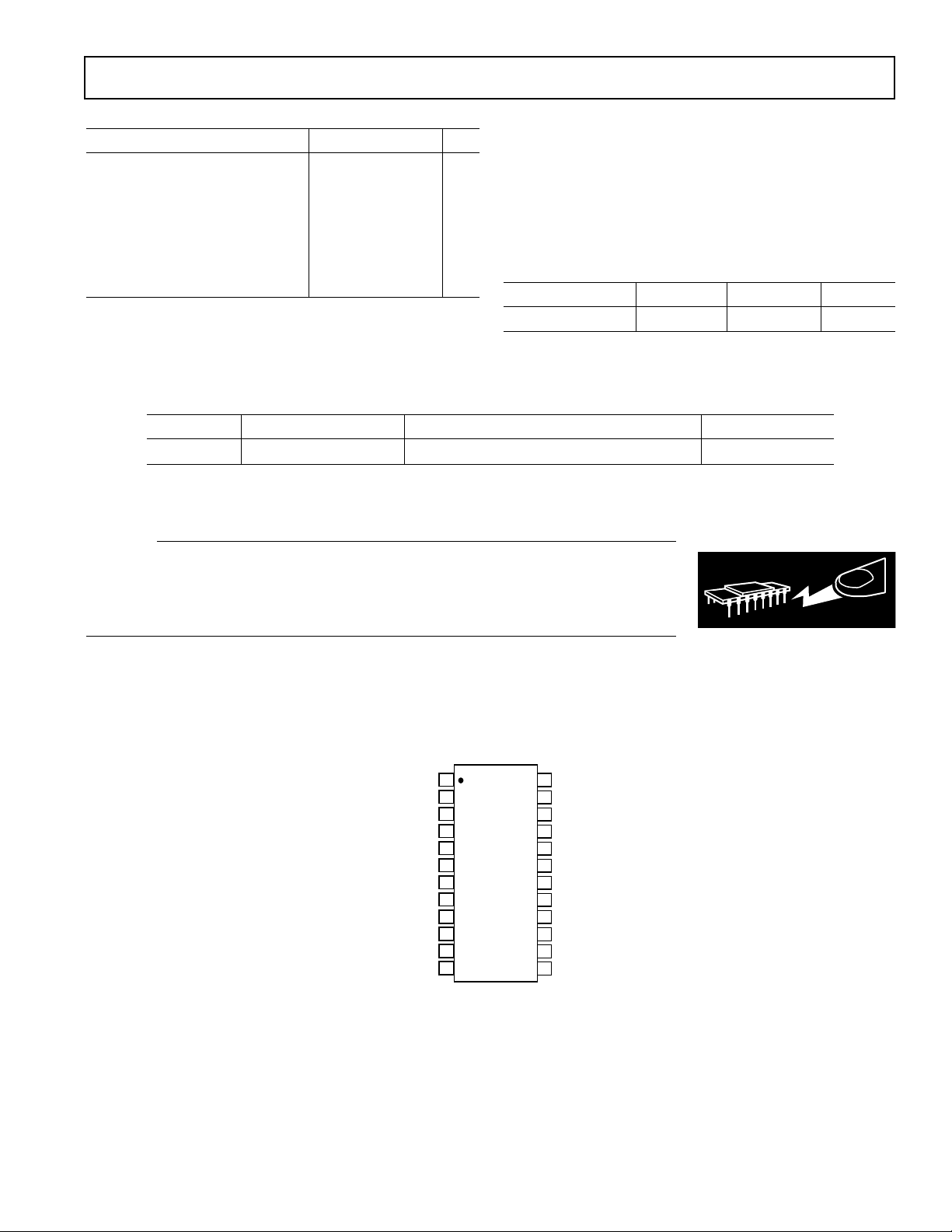

PACKAGE CHARACTERISTICS

Package

JA

TSSOP 83.8°C/W 15.6°C/W 68.2°C/W

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD1803JRU 0°C to 70°C 24-Lead Thin Shrink Small Outline Package RU-24

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD1803 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

JC

WARNING!

CA

ESD SENSITIVE DEVICE

PIN CONFIGURATION

24-Lead TSSOP

(RU-24)

CLK_OUT G[5]

BIT_CLK AGND

SDATA_IN V

SDATA_OUT FILT

G[4]/MOUT G[0]

G[3]/WAKE G[2]

1

2

DGND

3

DVDD G[7]

4

XTALO AVDD

5

XTALI Tx

SYNC Rx

RESET

6

7

8

9

10

11

12

AD1803

TOP VIEW

(Not to Scale)

24

23

22

21

20

19

18

17

16

15

14

13

G[6]

REF

G[1]/MIC

REV. 0

–7–

AD1803

PIN FUNCTION DESCRIPTIONS

Analog Signals

Pin Name TSSOP I/O Description

DVDD 3 I Digital Supply. Range: 5.0 V ± 10% or 3.3 V ± 10% (independent of AVDD).

DGND 2 I Digital Ground. Must be at same potential as AGND.

AVDD 21 I Analog Supply. Range: 5.5 V through 3.0 V (independent of DVDD).

AGND 19 I Analog Ground. Must be at same potential as DGND.

Clock Signals

Pin Name TSSOP I/O Description

XTALI 5 I Crystal or Clock Input (12.288, 24.576, or 32.768 MHz). This clock input is necessary

only if the AD1803 is configured in either AC’97 primary or DSP mode, or if a wake

interrupt from an event is required (in any mode). This pin must be tied to DVDD or DGND

(not floated) when clock input is not necessary. If a crystal is used, it must be parallel resonant first harmonic, and tied between this pin and the XTALO pin with load

capacitance specified by the crystal supplier. See Bits XTAL[1:0] in Register 0x5C for

further details.

XTALO 4 O Crystal Output. This pin should be floated when a crystal is not used.

CLK_OUT 1 O Buffered version of clock present on the XTALI pin, unless disabled. See Bits CLKED

and CLKEA in Register 0x5C for further details.

Serial Interface Signals (See Pins G[3:2] for Serial Interface Mode Selection)

Pin Name TSSOP I/O Description

RESET 10 I Active Low Power-Down. Level of power-down is determined by bits in Register 0x5C.

This pin must be asserted (driven LOW) as power is first applied until the supply is

stable. Contrary to the name of this pin, determined by Intel’s AC’97 specification, the

AD1803 is RESET exclusively by an internal power-on-RESET circuit.

BIT_CLK 6 I/O Serial Data Clock: Output if the AD1803 configured in AC’97 Primary or DSP mode,

Input if the AD1803 is configured in any AC’97 secondary mode.

SYNC 9 I/O Serial Data Frame Sync: Output if the AD1803 is configured in DSP mode, Input if the

AD1803 is configured in any AC’97 mode.

SDATA_IN 7 O Serial Data Output from AD1803.

SDATA_OUT 8 I Serial Data Input to AD1803.

General-Purpose I/O and Barrier Interface Signals

Pin Name TSSOP I/O Description

G[0] 14 I/O General-Purpose I/O.

G[1]/ 15 I General-Purpose I/O.

MIC I Or Analog MIC Input. See Bit GPMIC in Register 0x5E.

G[2] 13 I/O General-Purpose I/O. Also used to select Serial Interface mode (see below).

G[3]/ 12 I/O General-Purpose I/O.

WAKE O Or Wake Interrupt Output. See Bit GPWAK in Register 0x5E. Also used to select Serial

Interface mode (see below). When serving as WAKE, this pin will be driven high if

selected GPIO pins receive selected logic levels (see Registers 0x52 and 0x4E).

G[4]/ 11 I/O General-Purpose I/O.

MOUT O Or Monitor Output. See Bit GPMON in Register 0x5E.

G[5] 24 I/O General-Purpose I/O.

G[6] 23 I/O General-Purpose I/O.

G[7] 22 I/O General-Purpose I/O.

–8–

REV. 0

AD1803

NOTES

1. See Registers 0x4C through 0x54 and Bank 1 Register 0x60 for G[7:0] (General Purpose I/O) pin control.

2. By default all G[7:0] pins serve as inputs with weak (~30 kΩ equivalent) internal pull-up devices enabled.

3. Input voltage on Pins G[7:2,0] must not exceed DVDD by more than 0.3 V.

4. Input voltage on Pin G[1] must not exceed AVDD by more than 0.3 V.

5. The states of pins G[3:2] are sampled when RESET is deasserted (driven from LOW to HIGH) for the first time after power is applied to select AD1803 serial

interface mode. Once sampled, serial interface mode can be changed only by removing power from the AD1803.

G[3]/WAKE G[2] Serial Interface Mode

HIGH HIGH AC’97 Mode—Primary Device (ID: 00)

HIGH LOW AC’97 Mode—Secondary Device (ID: 01)

LOW HIGH AC’97 Mode—Secondary Device (ID: 10)

LOW LOW DSP Mode

Analog Signals

Pin Name TSSOP I/O Description

Rx 16 I Receive (ADC) Input.

Tx 20 O Transmit (DAC) Output.

FILT 17 I ADC Filter Bypass: Requires 1 µF Capacitor to AGND.

V

REF

18 I Voltage Reference: Requires 1 µF Capacitor to AGND.

PRODUCT OVERVIEW

The AD1803 is a low power 16-bit codec for modem, voice,

and telephony applications. It can also be used as a cellular

telephone interface.

The AD1803 is an Intel AC’97 Rev 2.1-compliant modem

codec (refer to Intel’s AC’97 specifications at www.intel.com)

with selectable AC’97 or a DSP-style serial interface.

The AD1803 codec uses high-performance ⌺-⌬ ADC and DACs

with programmable gain/attenuation. It has a digital ⌺-⌬ monitor

output with selectable mix from ADC and DAC channels for

call progress monitoring.

The AD1803 supports advanced power management with

several power-saving modes. The codec supports seven general

purpose I/O pins and a wake interrupt signaling mechanism on

GPIO events.

SERIAL INTERFACE MODE SELECTION

When power is first applied to the AD1803, RESET must be

asserted (RESET pin driven LOW), and kept asserted until the

power has stabilized. While RESET is asserted, the AD1803’s

serial interface mode is chosen by the state of Pins 12 and 13:

Pin 12 Pin 13 Mode Chosen

HIGH HIGH AC’97 Mode—Primary Device (ID: 00)

HIGH LOW AC’97 Mode—Secondary Device (ID: 01)

LOW HIGH AC’97 Mode—Secondary Device (ID: 10)

LOW LOW DSP Mode

Note that Pins 12 and 13 have weak pull-up devices internal to

the AD1803 which are enabled by default. Therefore, if these

pins are floated, AC’97 primary mode will be chosen. When

RESET is deasserted (RESET pin driven HIGH) for the first

time after power is applied, the states of Pins 12 and 13 are

latched locking in serial interface mode. Subsequent changes of

logic level presented on Pins 12 and 13 will have no effect on

serial port mode until power is removed from the AD1803.

After this first deassertion of RESET, Pins 12 and 13 will take

on new roles and serve as general purpose I/O control pins. The

AD1803 does not need an active clock source for proper operation during this mode selection.

SERIAL INTERFACE BEHAVIOR AND PROTOCOL WHEN

IN AC’97 MODE

The AD1803 serial interface is compatible with the Intel’s

“Audio Codec ’97” Revision 2.1 specification as either a primary or secondary modem/handset codec device. Consult this

specification for complete behavioral details. By default the

AD1803 will use Slot 5 to send and receive sample data,

but this may be changed to Slot 10 or 11. See Bits SPCHN,

SPGBP, SPDSS, SPISO, and SPDL[1:0] in Register 0x5E for

additional AC’97 mode configuration enhancements.

AC’97 Interface Modes

Primary Mode

Entered if GPIO[3] pin is HIGH and GPIO[2] pin is HIGH

when RESET pin is deasserted first time:

AD1803 is Timing Master: Drives BIT_CLK @ 12.288 MHz

AD1803 accepts the 48 kHz SYNC Timing Signal

AD1803 requires a crystal or clock on XTALI (see Bits

XTALI[1:0] in Register 0x5C for frequency).

Secondary Modes

Entered if GPIO[3] pin is HIGH and GPIO[2] pin is LOW

when RESET pin is deasserted first time or if GPIO[3] pin is

LOW and GPIO[2] pin is HIGH when RESET pin is deasserted

first time:

AD1803 is Timing Slave: Accepts BIT_CLK @ 12.288 MHz

AD1803 accepts the 48 kHz SYNC Timing Signal

AD1803 does not require a crystal or clock on XTALI (see Bits

XTALI[1:0] in Register 0x5C for frequency) unless wake from

an event during RESET is desired.

REV. 0

–9–

Loading...

Loading...