Analog Devices AD13280 a Datasheet

a

Dual Channel, 12-Bit, 80 MSPS A/D Converter

with Analog Input Signal Conditioning

AD13280

FEATURES

Dual, 80 MSPS Minimum Sample Rate

Channel-to-Channel Matching, 1% Gain Error

90 dB Channel-to-Channel Isolation

DC-Coupled Signal Conditioning

80 dB Spurious-Free Dynamic Range

Selectable Bipolar Inputs (1 V and 0.5 V Ranges)

Integral Single-Pole Low Pass Nyquist Filter

Two’s Complement Output Format

3.3 V Compatible Outputs

1.85 W per Channel

Industrial and Military Grade

APPLICATIONS

Radar Processing (Optimized for I/Q Baseband Operation)

Phased Array Receivers

Multichannel, Multimode Receivers

GPS Antijamming Receivers

Communications Receivers

PRODUCT DESCRIPTION

The AD13280 is a complete dual channel signal processing

solution, including on-board amplifiers, references, ADCs, and

output termination components to provide optimized system

performance. The AD13280 has on-chip track-and-hold circuitry

and utilizes an innovative multipass architecture to achieve 12-bit,

80 MSPS performance. The AD13280 uses innovative high

density circuit design and laser-trimmed thin-film resistor networks

to achieve exceptional channel matching, impedance control,

and performance while still maintaining excellent isolation,

and providing for significant board area savings.

Multiple options are provided for driving the analog input,

including single-ended, differential, and optional series filtering.

The AD13280 also offers the user a choice of analog input

signal ranges to further minimize additional external signal

conditioning, while still remaining general-purpose.

The AD13280 operates with ±5.0 V for the analog signal conditioning with a separate 5.0 V supply for the analog-to-digital

conversion, and 3.3 V digital supply for the output stage. Each

channel is completely independent, allowing operation with

independent encode and analog inputs, and maintaining minimal

crosstalk and interference.

The AD13280 is packaged in a 68-lead ceramic gull wing

package. Manufacturing is done on Analog Devices’ MIL-38534

Qualified Manufacturers Line (QML), and components are

available up to Class-H (–40°C to +85°C). The components are

manufactured using Analog Devices’ high speed complementary

bipolar process (XFCB).

PRODUCT HIGHLIGHTS

1. Guaranteed sample rate of 80 MSPS.

2. Input signal conditioning included; gain and impedance match.

3. Single-ended, differential, or off-module filter options.

4. Fully tested/characterized full channel performance.

5. Compatible with 14-bit (up to) 65 MSPS family.

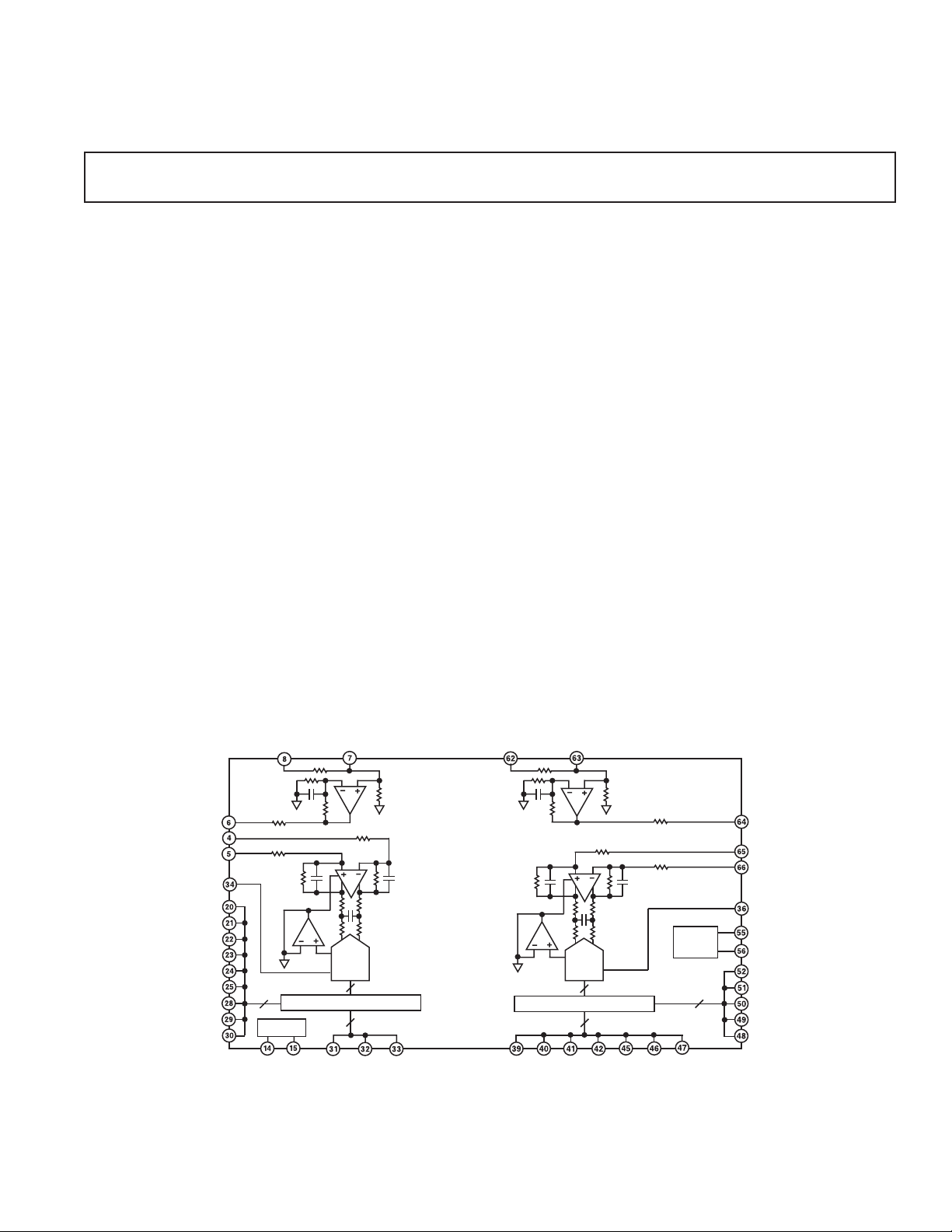

FUNCTIONAL BLOCK DIAGRAM

AMP-IN-A-1

VREF

DROUT

100 OUTPUT TERMINATORS

ENC

12

3

D9A D10A

D11A

(MSB)

AD13280

AMP-OUT-A

A–IN

A+IN

DROUTA

(LSB) D0A

D1A

D2A

D3A

D4A

D5A

D6A

D7A

D8A

AMP-IN-A-2

9

TIMING

ENC

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

AMP-IN-B-2 AMP-IN-B-1

AMP-OUT-B

B+IN

B–IN

DROUTB

TIMING

VREF

DROUT

12

100 OUTPUT TERMINATORS

7

D0B

D1B D3BD2B D4B D5B D6B

(LSB)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

5

ENC

ENC

D11B (MSB)

D10B

D9B

D8B

D7B

(AVCC = +5 V, AVEE = –5 V, DVCC = +3.3 V; applies to each ADC with Front-End

AD13280–SPECIFICATIONS

Parameter Temp Level Subgroup Min Typ Max Unit

RESOLUTION 12 Bits

DC ACCURACY

No Missing Codes Full IV 12 Guaranteed

Offset Error 25°CI 1 –2.2 ±1.0 +2.2 % FS

Offset Error Channel Match Full VI 1, 2, 3 –1.0 ± 0.1 +1.0 %

Gain Error

Gain Error Channel Match 25°CI 1 –1.5 ±0.5 +1.5 %

SINGLE-ENDED ANALOG INPUT

Input Voltage Range

AMP-IN-X-1 Full V ±0.5 V

AMP-IN-X-2 Full V ±1.0 V

Input Resistance

AMP-IN-X-1 Full IV 12 99 100 101 Ω

AMP-IN-X-2 Full IV 12 198 200 202 Ω

Capacitance 25°CV 4.0 7.0 pF

Analog Input Bandwidth

DIFFERENTIAL ANALOG INPUT

Analog Signal Input Range

A+IN to A–IN and B+IN to B–IN

Input Impedance 25°CV 618 Ω

Analog Input Bandwidth Full V 50 MHz

ENCODE INPUT (ENC, ENC)

Differential Input Voltage Full IV 12 0.4 V p-p

Differential Input Resistance 25°CV 10 kΩ

Differential Input Capacitance 25°CV 2.5 pF

SWITCHING PERFORMANCE

Maximum Conversion Rate

Minimum Conversion Rate

Aperture Delay (t

Aperture Delay Matching 25°CIV 12 250 500 ps

Aperture Uncertainty (Jitter) 25°CV 0.3 ps rms

ENCODE Pulsewidth High at Max Conversion Rate 25°CIV12 4.75 6.25 8 ns

ENCODE Pulsewidth Low at Max Conversion Rate 25°CIV12 4.75 6.25 8 ns

Output Delay (t

Encode, Rising to Data Ready, Rising Delay Full V 8.5 ns

1, 6

SNR

Analog Input @ 10 MHz 25°CI 4 66.5 70 dBFS

Analog Input @ 21 MHz 25°CI 4 66.5 70 dBFS

Analog Input @ 37 MHz 25°CI 46365 dBFS

1, 7

SINAD

Analog Input @ 10 MHz 25°CI 46669 dBFS

Analog Input @ 21 MHz 25°CI 46468.5 dBFS

Analog Input @ 37 MHz 25°CI 45459 dBFS

1

2

3

4

1

5

5

)25°CV 1.5 ns

A

) Full V 5 ns

OD

Amplifier, unless otherwise noted.)

Test Mil AD13280AZ/BZ

Full VI 2, 3 –2.2 ±1.0 +2.2 % FS

25°CI 1 –3 –1.0 +1 % FS

Full VI 2, 3 –5.0 ±2.0 +5.0 % FS

Max VI 2 –3.0 ±1.0 +3.0 %

Min VI 3 –5 ± 1.0 +5 %

Full V 100 MHz

Full V ±1V

Full VI 4, 5, 6 80 MSPS

Full IV 12 20 MSPS

Min II 6 64.5 dBFS

Max II 5 66.3 dBFS

Min II 6 64 dBFS

Max II 5 66.3 dBFS

Min II 6 61.5 dBFS

Max II 5 63 dBFS

Min II 6 63.5 dBFS

Max II 5 66 dBFS

Min II 6 63 dBFS

Max II 5 64 dBFS

Min II 6 53 dBFS

Max II 5 54 dBFS

–2–

REV. A

AD13280

Test Mil AD13280AZ/BZ

Parameter Temp Level Subgroup Min Typ Max Unit

S

PURIOUS-FREE DYNAMIC RANGE

Analog Input @ 10 MHz 25°CI 47580 dBFS

Analog Input @ 21 MHz 25°CI 46875 dBFS

Analog Input @ 37 MHz 25°CI 45662 dBFS

SINGLE-ENDED ANALOG INPUT

Pass-Band Ripple to 10 MHz 25°CV 0.05 dB

Pass-Band Ripple to 25 MHz 25°CV 0.1 dB

DIFFERENTIAL ANALOG INPUT

Pass-Band Ripple to 10 MHz 25°CV 0.3 dB

Pass-Band Ripple to 25 MHz 25°CV 0.82 dB

TWO-TONE IMD REJECTION

fIN = 9.1 MHz and 10.1 MHz 25°CI 4 75 80 dBc

and f2 are –7 dB Min II 6 71

f

1

= 19.1 MHz and 20.7 MHz 25°CV 4 77 dBc

f

IN

and f2 are –7 dB

f

1

= 36 MHz and 37 MHz 25°CV 4 60 dBc

f

IN

f1 and f2 are –7 dB

CHANNEL-TO-CHANNEL ISOLATION

TRANSIENT RESPONSE 25°CV 25 ns

DIGITAL OUTPUTS

11

Logic Compatibility CMOS

DVCC = 3.3 V

Logic “1” Voltage Full I 1, 2, 3 2.5 DVCC – 0.2 V

Logic “0” Voltage Full I 1, 2, 3 0.2 0.5 V

DVCC = 5 V

Logic “1” Voltage Full V DVCC – 0.3 V

Logic “0” Voltage Full V 0.35 V

Output Coding Two’s Complement

POWER SUPPLY

Supply Voltage

AV

CC

I (AV

AV

I (AV

DV

I (DV

I

) Current Full I 1, 2, 3 310 338 mA

CC

Supply Voltage

EE

) Current Full I 1, 2, 3 38 49 mA

EE

Supply Voltage

CC

) Current Full I 1, 2, 3 34 46 mA

CC

(Total) Supply Current per Channel Full I 1, 2, 3 369 433 mA

CC

12

12

12

Power Dissipation (Total) Full I 1, 2, 3 3.72 4.05 W

Power Supply Rejection Ratio (PSRR) Full V 0.01 % FSR/% V

NOTES

1

All ac specifications tested by driving ENCODE and ENCODE differentially. Single-ended input: AMP-IN-X-1 = 1 V p-p, AMP-IN-X-2 = GND.

2

Gain tests are performed on AMP-IN-X-1 input voltage range.

3

Full Power Bandwidth is the frequency at which the spectral power of the fundamental frequency (as determined by FFT analysis) is reduced by 3 dB.

4

For differential input: +IN = 1 V p-p and –IN = 1 V p-p (signals are 180° out of phase). For single-ended input: +IN = 2 V p-p and = –IN = GND.

5

Minimum and maximum conversion rates allow for variation in Encode Duty Cycle of 50% ± 5%.

6

Analog Input signal power at –1 dBFS; signal-to-noise ratio (SNR) is the ratio of signal level to total noise (first five harmonics removed). Encode = 80 MSPS. SNR is reported

in dBFS, related back to converter full scale.

7

Analog Input signal power at –1 dBFS; signal-to-noise and distortion (SINAD) is the ratio of signal level to total noise + harmonics. Encode = 80 MSPS. SINAD is reported in dBFS,

related back to converter full scale.

8

Analog Input signal at –1 dBFS; SFDR is the ratio of converter full scale to worst spur.

9

Both input tones at –7 dBFS; two-tone intermodulation distortion (IMD) rejection is the ratio of either tone to the worst third order intermod product.

10

Channel-to-channel isolation tested with A channel grounded and a full-scale signal applied to B Channel.

11

Digital output logic levels: DVCC = 3.3 V, C

12

Supply voltage recommended operating range. AVCC may be varied from 4.85 V to 5.25 V. However, rated ac (harmonics) performance is valid only over the range AVCC = 5.0 V

to 5.25 V.

Specifications subject to change without notice.

REV. A

1, 8

Min II 6 70

Max II 5 75

Min II 6 67

Max II 5 67

Min II 6 55

Max II 5 55

9

Max II 5 74

10

25°CIV 12 90 dB

Full IV 4.85 5.0 5.25 V

Full IV –5.25 –5.0 –4.75 V

Full IV 3.135 3.3 3.465 V

= 10 pF. Capacitive loads >10 pF will degrade performance.

LOAD

–3–

S

AD13280

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL

1

AVCC Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to 7 V

AV

Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . –7 V to 0 V

EE

Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to 7 V

DV

CC

Analog Input Voltage . . . . . . . . . . . . . . . . . . . . . V

EE

to V

Analog Input Current . . . . . . . . . . . . . . –10 mA to +10 mA

Digital Input Voltage (ENCODE) . . . . . . . . . . . . . 0 to V

ENCODE, ENCODE Differential Voltage . . . . . . . . 4 V max

Digital Output Current . . . . . . . . . . . . . . –10 mA to +10 mA

ENVIRONMENTAL

2

TEST LEVEL

I. 100% Production Tested

II. 100% Production Tested at 25°C, and sample tested at

specified temperatures. AC testing done on sample basis.

III. Sample Tested Only

CC

IV. Parameter is guaranteed by design and characterization testing.

CC

V. Parameter is a typical value only.

VI. 100% production tested with temperature at 25°C; sample

tested at temperature extremes.

Operating Temperature (Case) . . . . . . . . . –40°C to +85°C

Maximum Junction Temperature . . . . . . . . . . . . . . . . 175°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . 300°C

Storage Temperature Range (Ambient) . . –65°C to +150°C

NOTES

1

Absolute maximum ratings are limiting values applied individually, and beyond

which the serviceability of the circuit may be impaired. Functional operability is not

necessarily implied. Exposure to absolute maximum rating conditions for an

extended period of time may affect device reliability.

2

Typical thermal impedance for “ES” package: JC 2.2°C/W; JA 24.3°C/W.

ORDERING GUIDE

Model Temperature Range (Case) Package Description Package Option

AD13280AZ –25°C to +85°C 68-Lead Ceramic Leaded Chip Carrier ES-68C

AD13280AF –25°C to +85°C 68-Lead Ceramic Leaded Chip Carrier ES-68C

with Nonconductive Tie-Bar

5962-0053001HXA –40°C to +85°C 68-Lead Ceramic Leaded Chip Carrier ES-68C

AD13280/PCB 25°C Evaluation Board with AD13280AZ

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD13280 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

WARNING!

ESD SENSITIVE DEVICE

REV. A

AD13280

PIN FUNCTION DESCRIPTIONS

Pin Number Mnemonic Function

1, 35 SHIELD Internal Ground Shield between Channels

2, 3, 9, 10, 13, 16 AGNDA A Channel Analog Ground. A and B grounds should be connected as close to the device as possible.

4 A–IN Inverting Differential Input (Gain = 1)

5 A+IN Noninverting Differential Input (Gain = 1)

6 AMP-OUT-A Single-Ended Amplifier Output (Gain = 2)

7 AMP-IN-A-1 Analog Input for A Side ADC (Nominally ± 0.5 V)

8 AMP-IN-A-2 Analog Input for A Side ADC (Nominally ± 1.0 V)

11 AV

12 AV

14 ENCODEA Complement of Encode; Differential Input

15 ENCODEA Encode Input; Conversion Initiated on Rising Edge

17 DV

18, 19, 37, 38 NC No Connect

20–25, 28–33 D0A–D11A Digital Outputs for ADC A. D0 (LSB)

26, 27 DGNDA A Channel Digital Ground

34 DROUTA Data Ready A Output

36 DROUTB Data Ready B Output

39–42, 45–52 D0B–D11B Digital Outputs for ADC B. D0 (LSB)

43, 44 DGNDB B Channel Digital Ground

53 DV

54, 57, 60, 61, 67, 68 AGNDB B Channel Analog Ground. A and B grounds should be connected as close to the device as possible.

55 ENCODEB Encode Input. Conversion initiated on rising edge.

56 ENCODEB Complement of Encode. Differential input.

58 AV

59 AV

62 AMP-IN-B-2 Analog Input for B Side ADC (Nominally ±1.0 V)

63 AMP-IN-B-1 Analog Input for B Side ADC (Nominally ±0.5 V)

64 AMP-OUT-B Single-Ended Amplifier Output (Gain = 2)

65 B+IN Noninverting Differential Input (Gain = 1)

66 B–IN Inverting Differential Input (Gain = 1)

AA Channel Analog Negative Supply Voltage (Nominally –5.0 V or –5.2 V)

EE

AA Channel Analog Positive Supply Voltage (Nominally 5.0 V)

CC

AA Channel Digital Positive Supply Voltage (Nominally 5.0 V/ 3.3 V)

CC

BB Channel Digital Positive Supply Voltage (Nominally 5.0 V/ 3.3 V)

CC

BB Channel Analog Positive Supply Voltage (Nominally 5.0 V)

CC

BB Channel Analog Negative Supply Voltage (Nominally –5.0 V or –5.2 V)

EE

REV. A

10

AGNDA

11

AVEEA

AV

A

12

CC

13

AGNDA

AGNDA

DV

CC

NC

NC

D1A

D2A

D3A

D4A

D5A

DGNDA

14

15

16

A

17

18

19

20

21

22

23

24

25

26

ENCODEA

ENCODEA

D0A(LSB)

NC = NO CONNECT

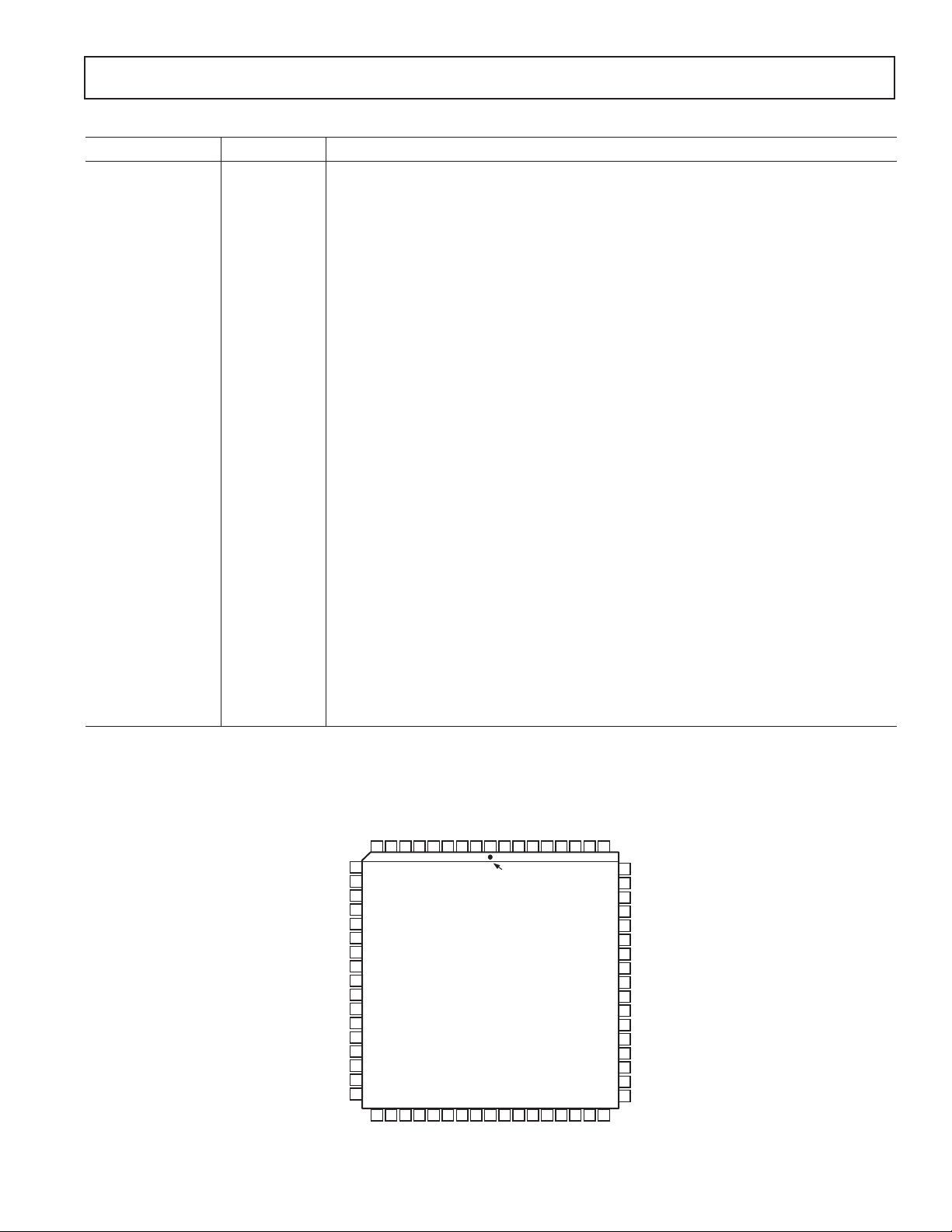

PIN CONFIGURATION

AGNDA

AMP-OUT-A

AMP-IN-A-2

AMP-IN-A-1

9618765 686766656463624321

27 4328 29 30 31 32 33 34 35 36 37 38 39 40 41 42

D8A

D7A

D6A

DGNDA

AGNDA

A+IN

A–IN

AGNDA

AD13280

TOP VIEW

(Not to Scale)

D9A

D10A

DROUTA

D11A(MSB)

AGNDB

SHIELD

AGNDB

B–IN

B+IN

AMP-OUT-B

AMP-IN-B-1

PIN 1

IDENTIFIER

SHIELD

DROUTB

D0B(LSB)

D2B

D1B

NC

NC

–5–

AGNDB

AMP-IN-B-2

60

AGNDB

59

AVEEB

58

AV

57

AGNDB

56

ENCODEB

55

ENCODEB

54

AGNDB

53

DV

52

D11B(MSB)

D10B

51

D9B

50

49

D8B

48

D7B

47

D6B

46

D5B

45

D4B

44

DGNDB

D3B

DGNDB

B

CC

B

CC

AD13280

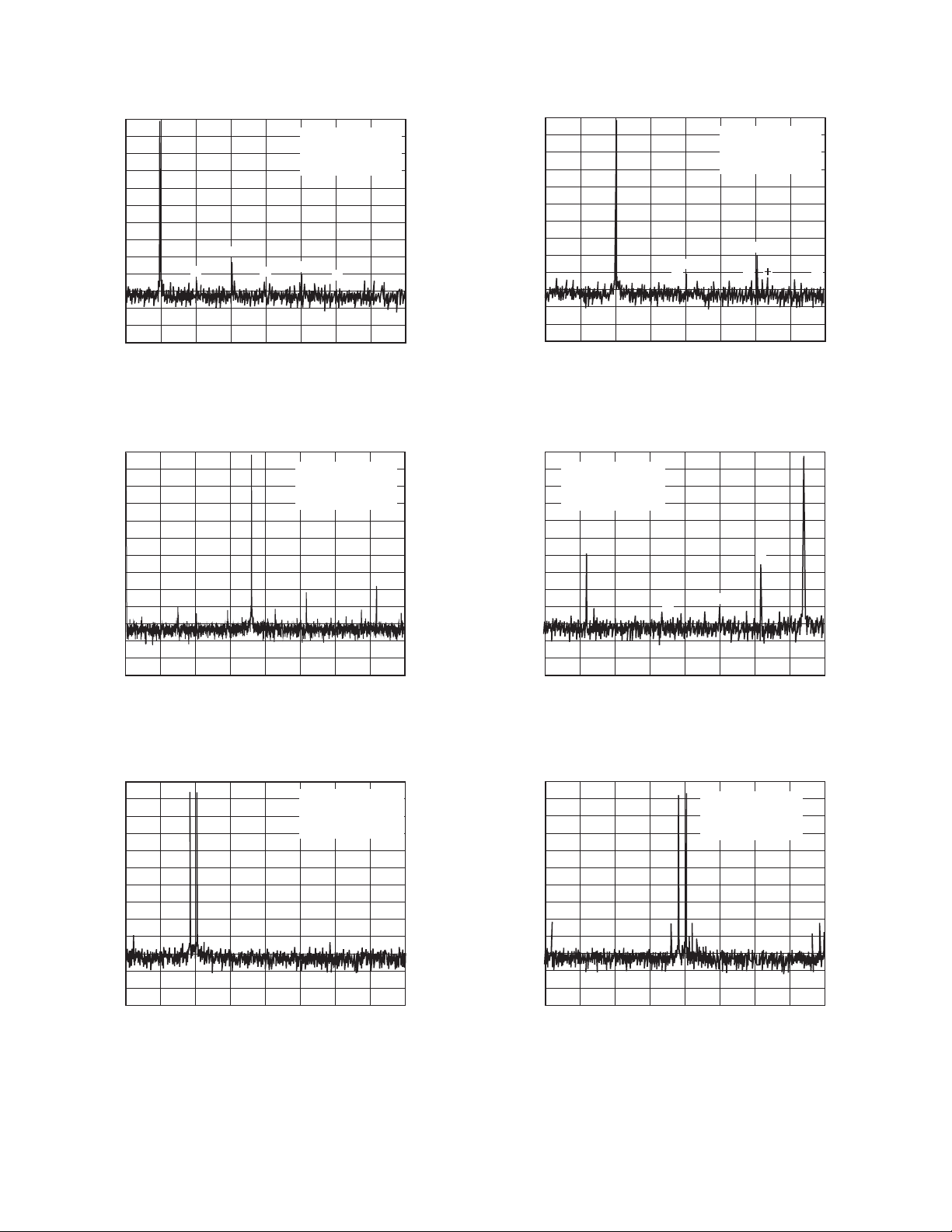

–Typical Performance Characteristics

dB

–100

–110

–120

–130

dB

–100

–110

–120

–130

–10

–20

–30

–40

–50

–60

–70

–80

–90

–10

–20

–30

–40

–50

–60

–70

–80

–90

0

3

2

0

51015202530

4

FREQUENCY – MHz

TPC 1. Single Tone @ 5 MHz

0

0

51015202530

FREQUENCY – MHz

ENCODE = 80MSPS

A

= 5MHz (–1dBFS)

IN

SNR = 69.4dBFS

SFDR = 81.9dBc

5

6

35 40

ENCODE = 80MSPS

A

= 18MHz (–1dBFS)

IN

SNR = 69.79dBFS

SFDR = 76.81dBc

35 40

dB

–100

–110

–120

–130

dB

–100

–110

–120

–130

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

0

51015202530

FREQUENCY – MHz

TPC 4. Single Tone @ 10 MHz

0

–10

ENCODE = 80MSPS

A

= 37MHz (–1dBFS)

–20

–30

–40

–50

–60

–70

–80

–90

IN

SNR = 68.38dBFS

SFDR = 57.81dBc

2

6

4

0

51015202530

FREQUENCY – MHz

ENCODE = 80MSPS

A

= 10MHz (–1dBFS)

IN

SNR = 69.19dBFS

SFDR = 79.55dBc

3

2

6

5

3

5

4

35 40

35 40

TPC 2. Single Tone @ 18 MHz

0

–10

–20

–30

–40

–50

–60

dB

–70

–80

–90

–100

–110

–120

–130

0

51015202530

FREQUENCY – MHz

TPC 3. Two Tone @ 9 MHz/10 MHz

ENCODE = 80MSPS

A

= 9MHz AND

IN

10MHz (–7dBFS)

SFDR = 82.77dBc

35 40

TPC 5. Single Tone @ 37 MHz

0

ENCODE = 80MSPS

A

IN

20MHz (–7dBFS)

SFDR = 74.41dBc

dB

–100

–110

–120

–130

–10

–20

–30

–40

–50

–60

–70

–80

–90

0

51015202530

FREQUENCY – MHz

TPC 6. Two Tone @ 19 MHz/20 MHz

= 19MHz AND

35 40

–6–

REV. A

Loading...

Loading...