Page 1

Arria 10 Avalon-ST Interface for PCIe

Solutions

User Guide

Last updated for Altera Complete Design Suite: 15.0

Subscribe

Send Feedback

UG-01145_avst

2015.05.04

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

Contents

Datasheet............................................................................................................. 1-1

Arria 10 Avalon-ST Interface for PCIe Datasheet...................................................................................1-1

Arria 10 Features .............................................................................................................................1-2

Release Information ....................................................................................................................................1-6

Device Family Support ...............................................................................................................................1-7

Configurations .............................................................................................................................................1-7

Arria 10 Avalon-ST Example Designs...................................................................................................... 1-9

Debug Features ..........................................................................................................................................1-10

IP Core Verification ..................................................................................................................................1-11

Compatibility Testing Environment ..........................................................................................1-11

Performance and Resource Utilization ..................................................................................................1-11

Recommended Speed Grades ..................................................................................................................1-11

Steps in Creating a Design for PCI Express........................................................................................... 1-11

Getting Started with the Arria 10 Hard IP for PCI Express ..............................2-1

Qsys Design Flow.........................................................................................................................................2-2

Generating the Testbench ..............................................................................................................2-3

Simulating the Example Design ....................................................................................................2-3

Generating Quartus II Synthesis Files...........................................................................................2-4

Understanding the Files Generated...............................................................................................2-4

Understanding Simulation Log File Generation......................................................................... 2-4

Understanding Physical Placement of the PCIe IP Core .......................................................... 2-5

Adding Virtual Pin Assignment to the Quartus II Settings File (.qsf)..................................... 2-5

Compiling the Design in the Qsys Design Flow .........................................................................2-5

Modifying the Example Design .....................................................................................................2-7

Using the IP Catalog To Generate Your Arria 10 Hard IP for PCI Express as a Separate

Component..................................................................................................................................2-8

Files Generated for Altera IP Cores...............................................................................................2-9

Getting Started with the Configuration Space Bypass Mode Qsys Example

Design ............................................................................................................. 3-1

Copying the Configuration Space Bypass Mode Example Design .......................................................3-2

Generating the Qsys System ......................................................................................................................3-3

Generating Quartus II Synthesis Files...........................................................................................3-4

Understanding the Generated Files ..............................................................................................3-4

Understanding Simulation Log File Generation......................................................................... 3-5

Simulating the Example Design ................................................................................................................3-5

Timing for Configuration Read to Function 0 for the 256-Bit Avalon-ST Interface ............3-6

Timing for Configuration Write to Function 0 for the 256-Bit Avalon-ST Interface ...........3-8

Timing for Memory Write and Read of Function 1 256-Bit Avalon-ST Interface ................3-9

Partial Transcript for Configuration Space Bypass Simulation ..............................................3-11

Altera Corporation

Page 3

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

TOC-3

Parameter Settings.............................................................................................. 4-1

System Settings ............................................................................................................................................4-1

Base Address Register (BAR) and Expansion ROM Settings ............................................................... 4-5

Base and Limit Registers for Root Ports .................................................................................................. 4-7

Device Identification Registers ..................................................................................................................4-7

PCI Express and PCI Capabilities Parameters ........................................................................................4-8

Device Capabilities ..........................................................................................................................4-9

Error Reporting .............................................................................................................................4-10

Link Capabilities ........................................................................................................................... 4-11

MSI and MSI-X Capabilities ........................................................................................................4-12

Slot Capabilities .............................................................................................................................4-13

Power Management ......................................................................................................................4-14

Vendor Specific Extended Capability (VSEC).......................................................................................4-15

PHY Characteristics ................................................................................................................................. 4-15

Physical Layout of Hard IP In Arria 10 Devices.................................................5-1

Channel and Pin Placement for the Gen1, Gen2, and Gen3 Data Rates..............................................5-4

Channel Placement and fPLL Usage for the Gen1 and Gen2 Data Rates............................................5-5

Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate...................................... 5-7

Interfaces and Signal Descriptions .................................................................... 6-1

Avalon-ST RX Interface .............................................................................................................................6-2

Avalon-ST RX Component Specific Signals ................................................................................6-4

Data Alignment and Timing for the 64-Bit Avalon-ST RX Interface ......................................6-6

Data Alignment and Timing for the 128-Bit Avalon-ST RX Interface ................................. 6-11

Data Alignment and Timing for 256-Bit Avalon-ST RX Interface ........................................6-15

Tradeoffs to Consider when Enabling Multiple Packets per Cycle ....................................... 6-15

Avalon-ST TX Interface ...........................................................................................................................6-16

Avalon-ST Packets to PCI Express TLPs ...................................................................................6-22

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface ................................... 6-22

Data Alignment and Timing for the 128-Bit Avalon-ST TX Interface ................................. 6-25

Data Alignment and Timing for the 256-Bit Avalon-ST TX Interface ................................. 6-28

Root Port Mode Configuration Requests ..................................................................................6-31

Clock Signals ..............................................................................................................................................6-31

Reset, Status, and Link Training Signals.................................................................................................6-31

ECRC Forwarding .....................................................................................................................................6-36

Error Signals .............................................................................................................................................. 6-36

Interrupts for Endpoints ..........................................................................................................................6-37

Interrupts for Root Ports ......................................................................................................................... 6-38

Completion Side Band Signals ................................................................................................................6-38

Parity Signals ............................................................................................................................................. 6-41

LMI Signals ................................................................................................................................................6-42

Transaction Layer Configuration Space Signals ...................................................................................6-44

Configuration Space Register Access Timing ...........................................................................6-47

Configuration Space Register Access .........................................................................................6-47

Altera Corporation

Page 4

TOC-4

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

Hard IP Reconfiguration Interface .........................................................................................................6-52

Power Management Signals .................................................................................................................... 6-54

Physical Layer Interface Signals ..............................................................................................................6-57

Serial Data Signals .........................................................................................................................6-57

PIPE Interface Signals .................................................................................................................. 6-57

Test Signals .................................................................................................................................... 6-62

Registers...............................................................................................................7-1

Correspondence between Configuration Space Registers and the PCIe Specification .....................7-1

Type 0 Configuration Space Registers ..................................................................................................... 7-5

PCI Express Capability Structures.............................................................................................................7-5

Altera-Defined VSEC Registers................................................................................................................. 7-8

CvP Registers................................................................................................................................................7-9

Uncorrectable Internal Error Mask Register ........................................................................................ 7-12

Uncorrectable Internal Error Status Register ....................................................................................... 7-13

Correctable Internal Error Mask Register .............................................................................................7-14

Correctable Internal Error Status Register ............................................................................................7-14

Arria 10 Reset and Clocks................................................................................... 8-1

Reset Sequence for Hard IP for PCI Express IP Core and Application Layer ....................................8-2

Clocks ........................................................................................................................................................... 8-4

Clock Domains ................................................................................................................................8-4

Clock Summary ...............................................................................................................................8-6

Interrupts.............................................................................................................9-1

Interrupts for Endpoints.............................................................................................................................9-1

MSI Interrupts .................................................................................................................................9-1

MSI-X ............................................................................................................................................... 9-4

Implementing MSI-X Interrupts................................................................................................... 9-4

Legacy Interrupts ............................................................................................................................ 9-6

Interrupts for Root Ports ........................................................................................................................... 9-7

Error Handling ................................................................................................. 10-1

Physical Layer Errors ................................................................................................................................10-2

Data Link Layer Errors .............................................................................................................................10-2

Transaction Layer Errors .........................................................................................................................10-3

Error Reporting and Data Poisoning .....................................................................................................10-6

Uncorrectable and Correctable Error Status Bits .................................................................................10-7

IP Core Architecture......................................................................................... 11-1

Top-Level Interfaces .................................................................................................................................11-3

Avalon-ST Interface ......................................................................................................................11-3

Clocks and Reset ........................................................................................................................... 11-4

Local Management Interface (LMI Interface) .......................................................................... 11-4

Hard IP Reconfiguration ............................................................................................................. 11-4

Altera Corporation

Page 5

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

Interrupts ....................................................................................................................................... 11-4

PIPE ................................................................................................................................................ 11-4

Transaction Layer ..................................................................................................................................... 11-5

Configuration Space .....................................................................................................................11-6

Error Checking and Handling in Configuration Space Bypass Mode ...................................11-7

Protocol Extensions Supported .................................................................................................11-10

Data Link Layer .......................................................................................................................................11-10

Physical Layer ..........................................................................................................................................11-12

TOC-5

Transaction Layer Protocol (TLP) Details........................................................12-1

Supported Message Types ........................................................................................................................12-1

INTX Messages ..............................................................................................................................12-1

Power Management Messages .................................................................................................... 12-2

Error Signaling Messages .............................................................................................................12-3

Locked Transaction Message ...................................................................................................... 12-4

Slot Power Limit Message ............................................................................................................12-4

Vendor-Defined Messages ...........................................................................................................12-4

Hot Plug Messages ........................................................................................................................12-5

Transaction Layer Routing Rules ........................................................................................................... 12-6

Receive Buffer Reordering .......................................................................................................................12-7

Using Relaxed Ordering ...............................................................................................................12-9

Throughput Optimization................................................................................ 13-1

Throughput of Posted Writes ................................................................................................................. 13-3

Throughput of Non-Posted Reads ......................................................................................................... 13-3

Design Implementation.................................................................................... 14-1

Making Pin Assignments to Assign I/O Standard to Serial Data Pins ..............................................14-1

Recommended Reset Sequence to Avoid Link Training Issues ......................................................... 14-1

SDC Timing Constraints.......................................................................................................................... 14-2

Optional Features..............................................................................................15-1

Configuration via Protocol (CvP) .......................................................................................................... 15-1

ECRC ..........................................................................................................................................................15-2

ECRC on the RX Path .................................................................................................................. 15-2

ECRC on the TX Path .................................................................................................................. 15-3

Hard IP Reconfiguration ..................................................................................16-1

Testbench and Design Example ....................................................................... 17-1

Endpoint Testbench ................................................................................................................................. 17-2

Root Port Testbench .................................................................................................................................17-3

Chaining DMA Design Examples .......................................................................................................... 17-4

BAR/Address Map ........................................................................................................................17-8

Altera Corporation

Page 6

TOC-6

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

Chaining DMA Control and Status Registers ...........................................................................17-9

Chaining DMA Descriptor Tables ........................................................................................... 17-12

Test Driver Module ................................................................................................................................ 17-15

DMA Write Cycles ................................................................................................................................. 17-16

DMA Read Cycles ...................................................................................................................................17-18

Root Port Design Example .................................................................................................................... 17-20

Root Port BFM ........................................................................................................................................17-22

BFM Memory Map .....................................................................................................................17-24

Configuration Space Bus and Device Numbering ................................................................. 17-24

Configuration of Root Port and Endpoint ..............................................................................17-24

Issuing Read and Write Transactions to the Application Layer .......................................... 17-29

BFM Procedures and Functions ........................................................................................................... 17-30

ebfm_barwr Procedure .............................................................................................................. 17-30

ebfm_barwr_imm Procedure ....................................................................................................17-31

ebfm_barrd_wait Procedure ..................................................................................................... 17-32

ebfm_barrd_nowt Procedure ....................................................................................................17-33

ebfm_cfgwr_imm_wait Procedure ...........................................................................................17-34

ebfm_cfgwr_imm_nowt Procedure ......................................................................................... 17-34

ebfm_cfgrd_wait Procedure ......................................................................................................17-35

ebfm_cfgrd_nowt Procedure .....................................................................................................17-36

BFM Configuration Procedures................................................................................................ 17-37

BFM Shared Memory Access Procedures ............................................................................... 17-39

BFM Log and Message Procedures .......................................................................................... 17-42

Verilog HDL Formatting Functions ........................................................................................ 17-46

Procedures and Functions Specific to the Chaining DMA Design Example......................17-50

Setting Up Simulation.............................................................................................................................17-57

Changing Between Serial and PIPE Simulation ..................................................................... 17-57

Using the PIPE Interface for Gen1 and Gen2 Variants .........................................................17-57

Viewing the Important PIPE Interface Signals........................................................................17-57

Disabling the Scrambler for Gen1 and Gen2 Simulations ....................................................17-57

Disabling 8B/10B Encoding and Decoding for Gen1 and Gen2 Simulations.....................17-58

Debugging .........................................................................................................18-1

Frequently Asked Questions.............................................................................. A-1

Lane Initialization and Reversal ........................................................................B-1

Additional Information......................................................................................C-1

Altera Corporation

Simulation Fails To Progress Beyond Polling.Active State..................................................................18-1

Hardware Bring-Up Issues ......................................................................................................................18-1

Link Training .............................................................................................................................................18-2

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready .......................................18-2

Use Third-Party PCIe Analyzer ..............................................................................................................18-5

BIOS Enumeration Issues ........................................................................................................................18-5

Page 7

Getting Started with the Arria 10 Hard IP for PCI Express with the Avalon-ST Interface

TOC-7

Revision History for the Avalon-ST Interface.........................................................................................C-1

How to Contact Altera............................................................................................................................... C-6

Typographic Conventions......................................................................................................................... C-7

Altera Corporation

Page 8

2015.05.04

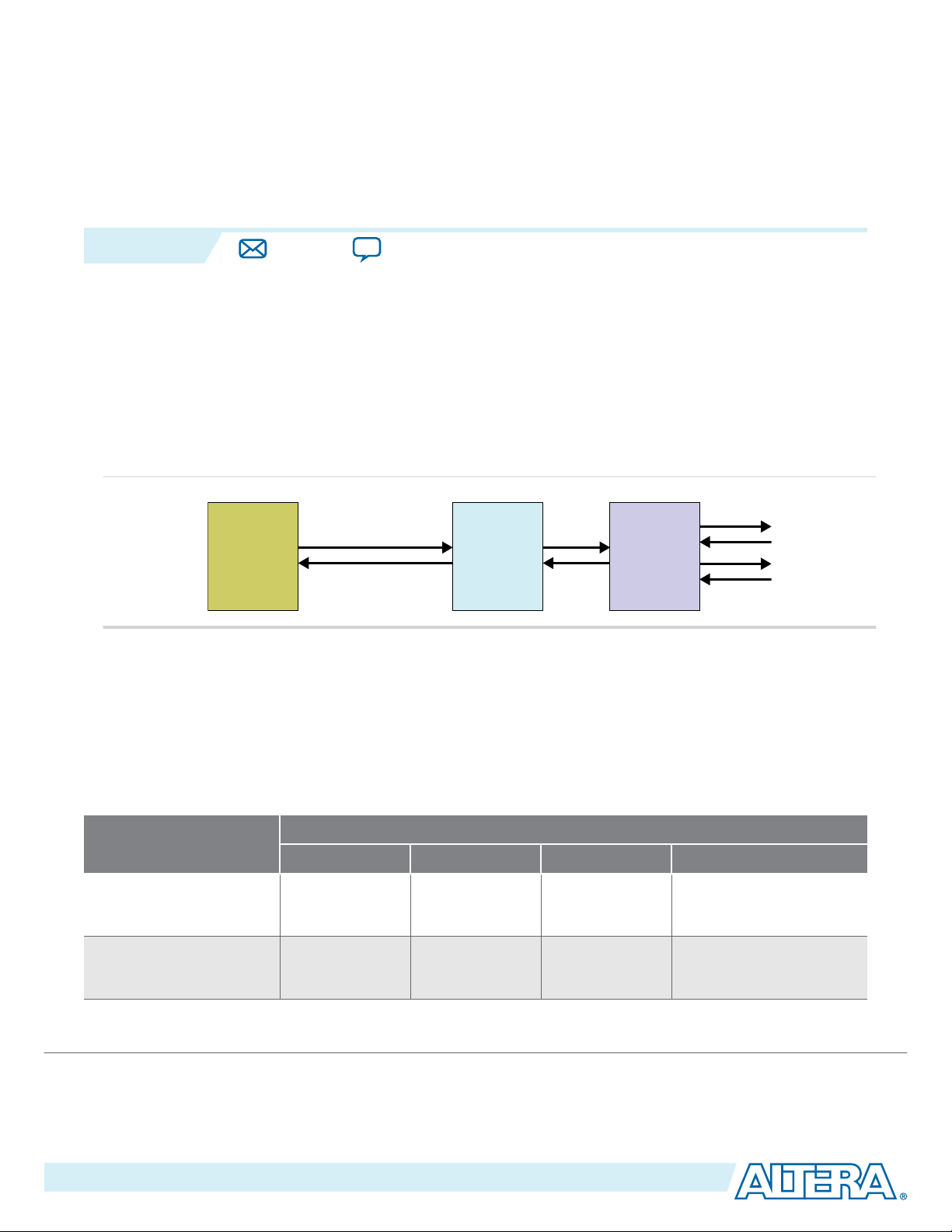

Application

Layer

(User Logic)

Avalon-ST

Interface

PCIe Hard IP

Block

PIPE

Interface

PHY IP Core

for PCIe

(PCS/PMA)

Serial Data

Transmission

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Datasheet

1

UG-01145_avst

Subscribe

Send Feedback

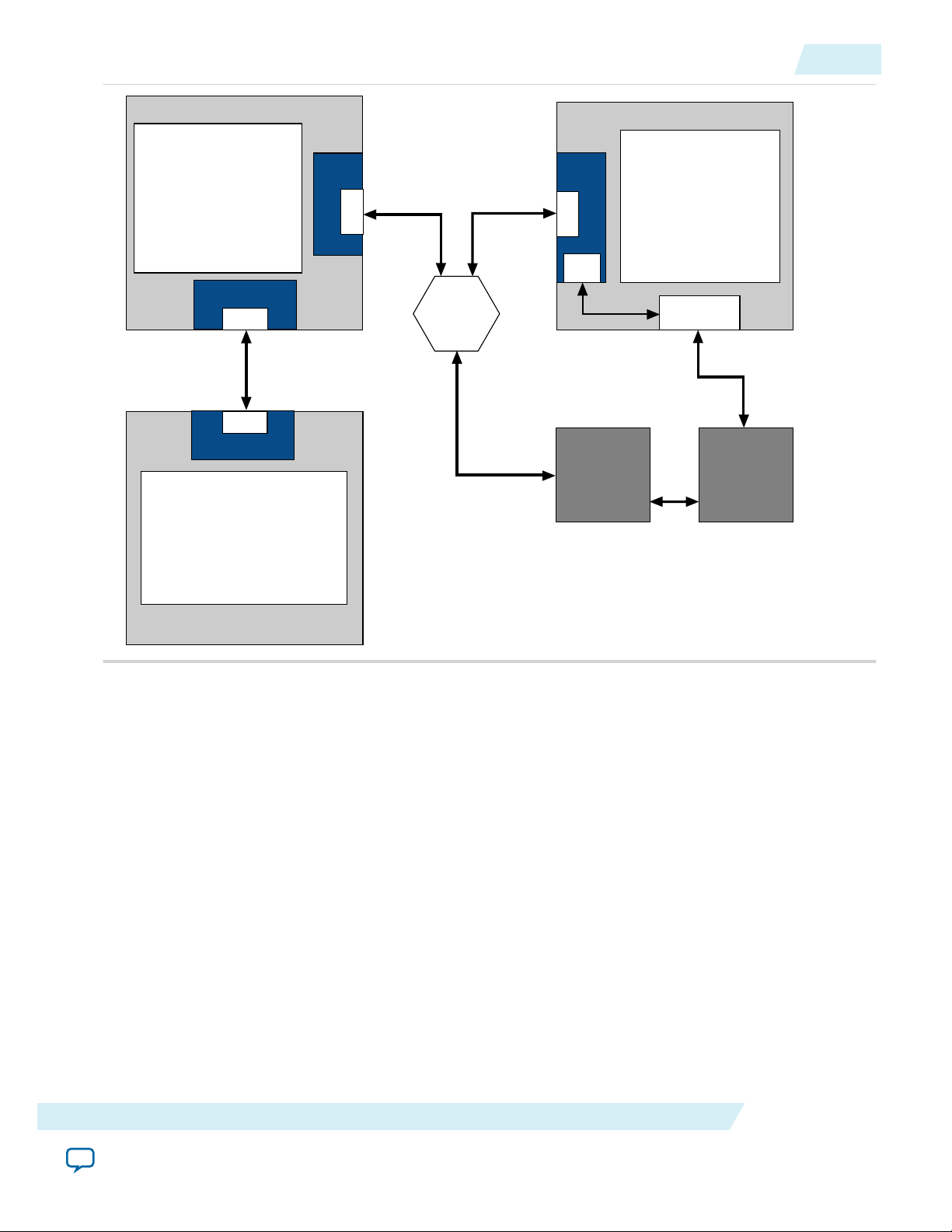

Arria 10 Avalon-ST Interface for PCIe Datasheet

®

Altera® Arria® 10 FPGAs include a configurable, hardened protocol stack for PCI Express

compliant with PCI Express Base Specification 3.0. The Hard IP for PCI Express using the Avalon

Streaming (Avalon-ST) interface is the most flexible variant. However, this variant requires a thorough

understanding of the PCIe

®

Protocol.

Figure 1-1: Arria 10 PCIe Variant with Avalon-ST Interface

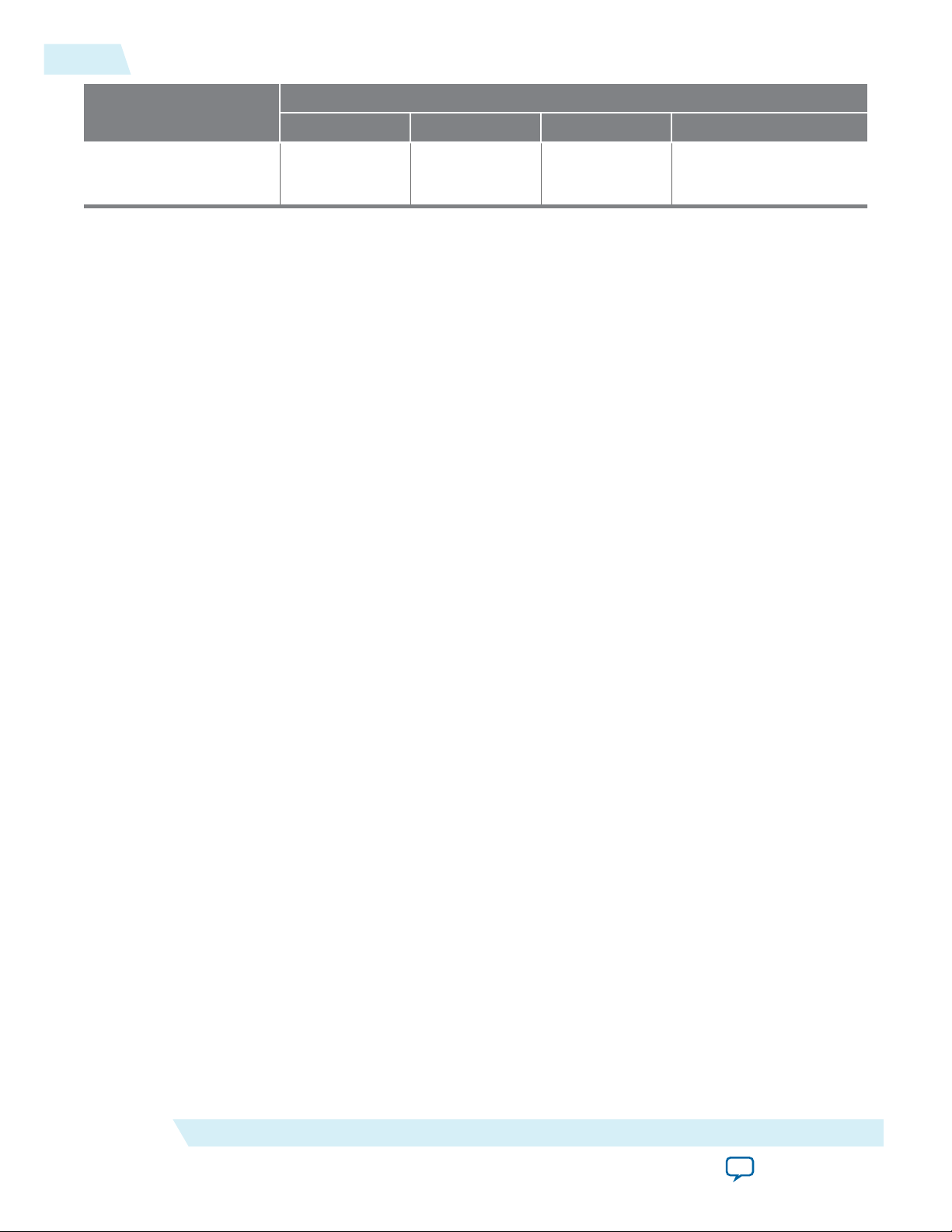

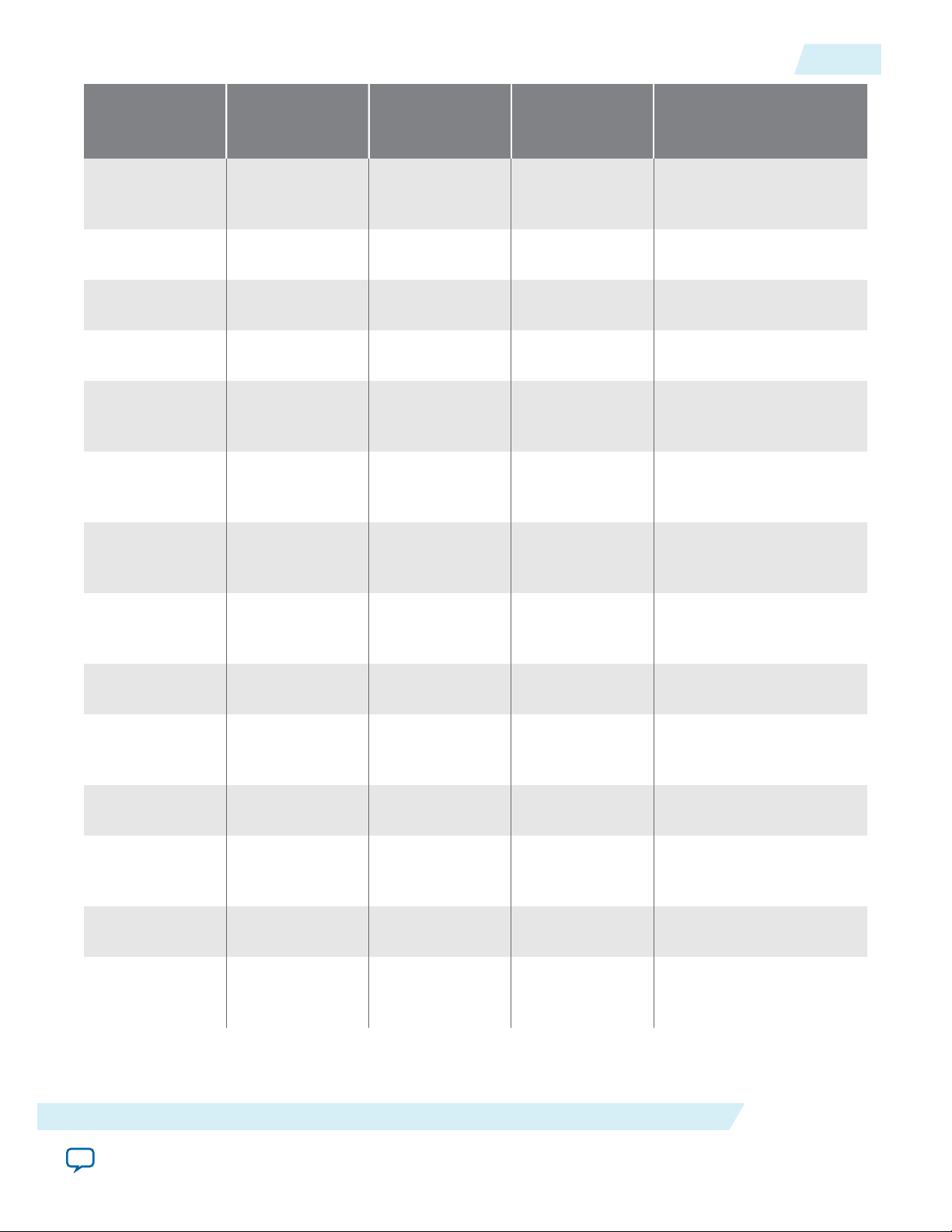

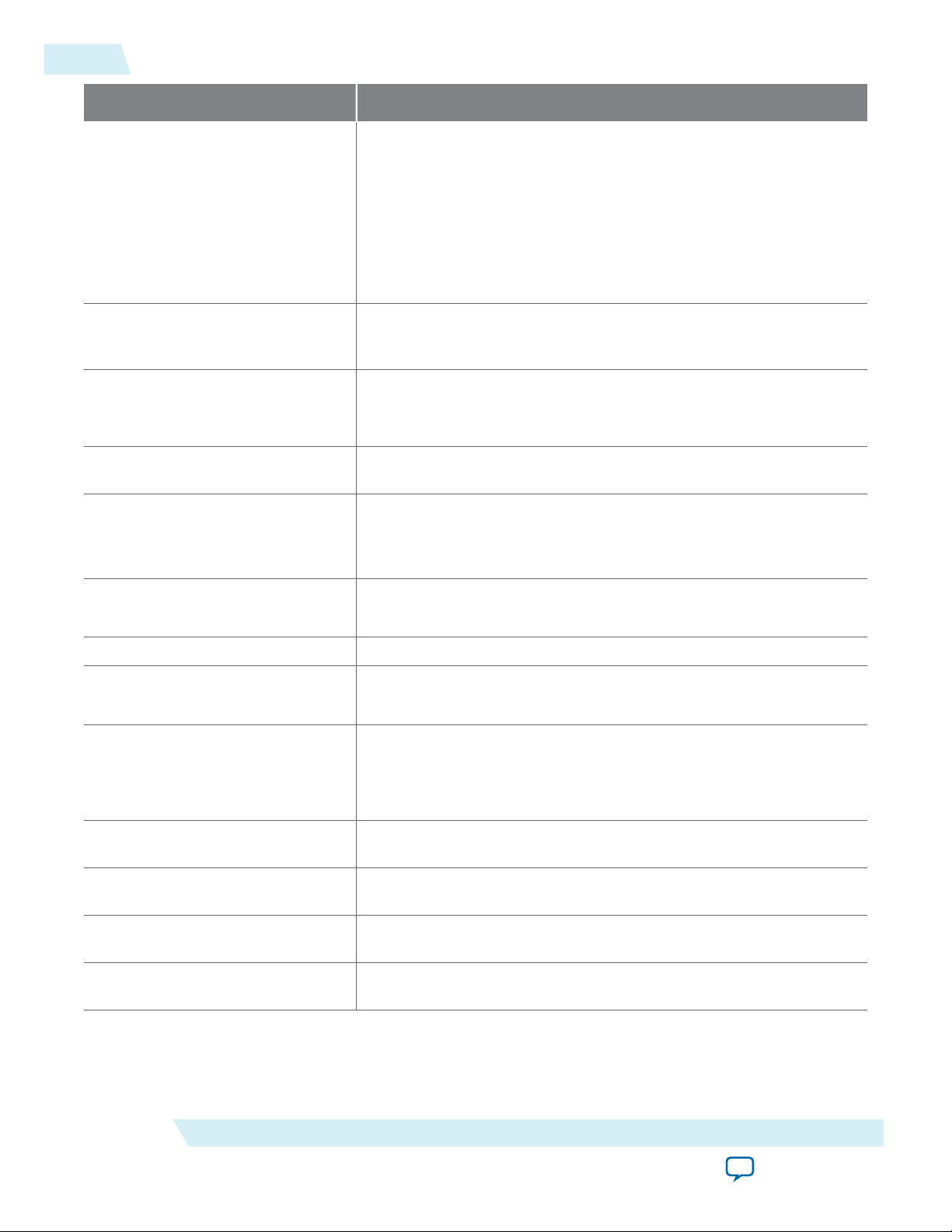

Table 1-1: PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen1, Gen2, and Gen3 for 1, 2, 4,

and 8 lanes. This table provides bandwidths for a single transmit (TX) or receive (RX) channel. The numbers

double for duplex operation. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per

second for Gen2, and 8.0 giga-transfers per second for Gen3. Gen1 and Gen2 use 8B/10B encoding which

introduces a 20% overhead. In contrast, Gen3 uses 128b/130b encoding which reduces the data throughput lost to

encoding to less than 1%.

that is

®

PCI Express Gen1

(2.5 Gbps)

PCI Express Gen2

(5.0 Gbps)

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

Link Width

×1 ×2 ×4 ×8

2 4 8 16

4 8 16 32

ISO

9001:2008

Registered

Page 9

1-2

Arria 10 Features

UG-01145_avst

2015.05.04

Link Width

×1 ×2 ×4 ×8

PCI Express Gen3

(8.0 Gbps)

Refer to the AN 456: PCI Express High Performance Reference Design for more information about

calculating bandwidth for the hard IP implementation of PCI Express in many Altera FPGAs, including

the Arria 10 Hard IP for PCI Express IP core.

Devices

Related Information

• PCI Express Base Specification 3.0

• AN 456: PCI Express High Performance Reference Design

• Creating a System with Qsys

Arria 10 Features

New features in the Quartus® II 15.0 software release:

• Added Enable Altera Debug Master Endpoint (ADME) parameter to support optional Native PHY

register programming with the Altera System Console.

The Arria 10 Hard IP for PCI Express supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

hard IP.

• Support for ×1, ×2, ×4, and ×8 configurations with Gen1, Gen2, or Gen3 lane rates for Root Ports and

Endpoints.

• Dedicated 16 KByte receive buffer.

• Optional support for Configuration via Protocol (CvP) using the PCIe link allowing the I/O and core

bitstreams to be stored separately.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

• Support for multiple packets per cycle with the 256-bit Avalon-ST interface.

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

• Easy to use:

7.87 15.75 31.51 63

Altera Corporation

• Flexible configuration.

• Substantial on-chip resource savings and guaranteed timing closure.

• No license requirement.

• Example designs to get started.

Datasheet

Send Feedback

Page 10

UG-01145_avst

2015.05.04

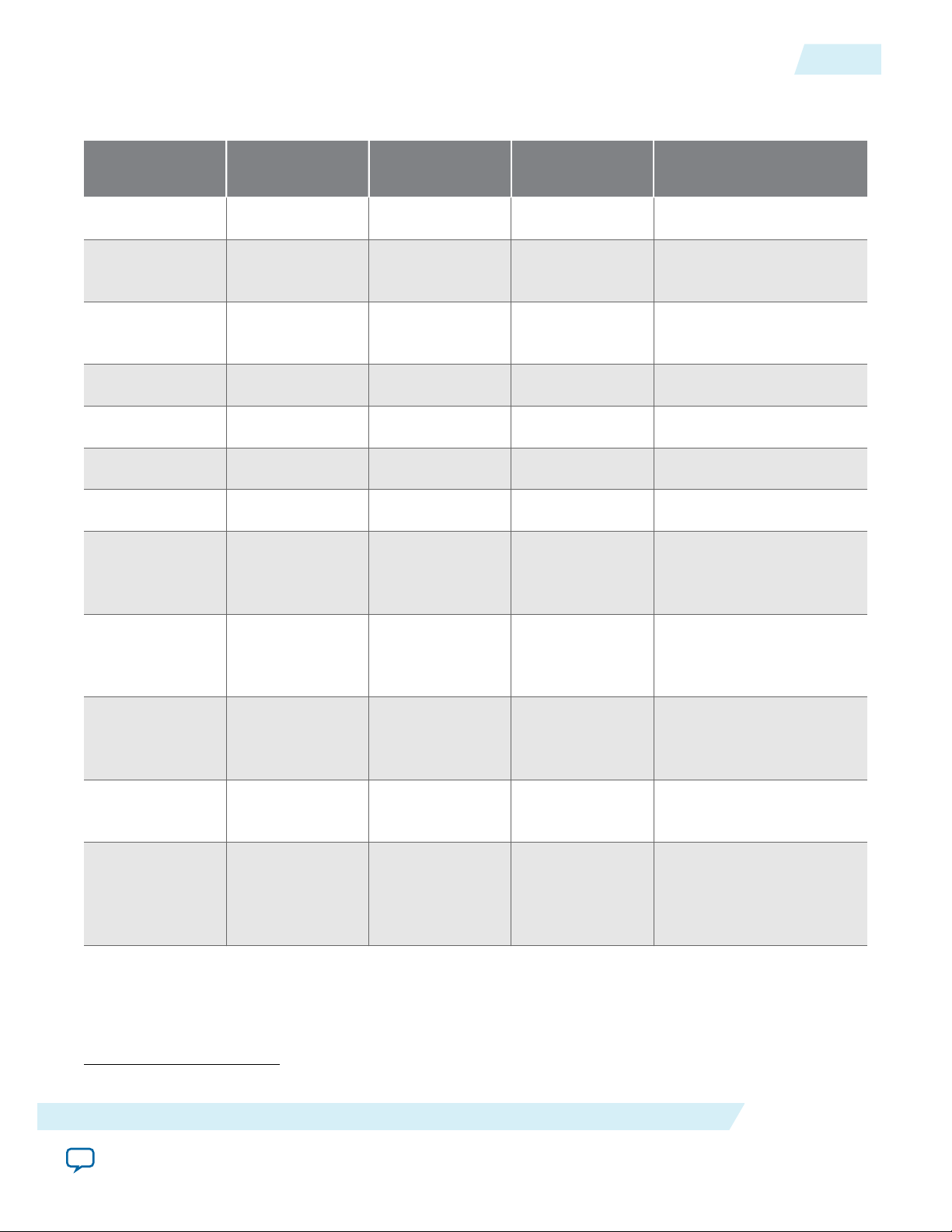

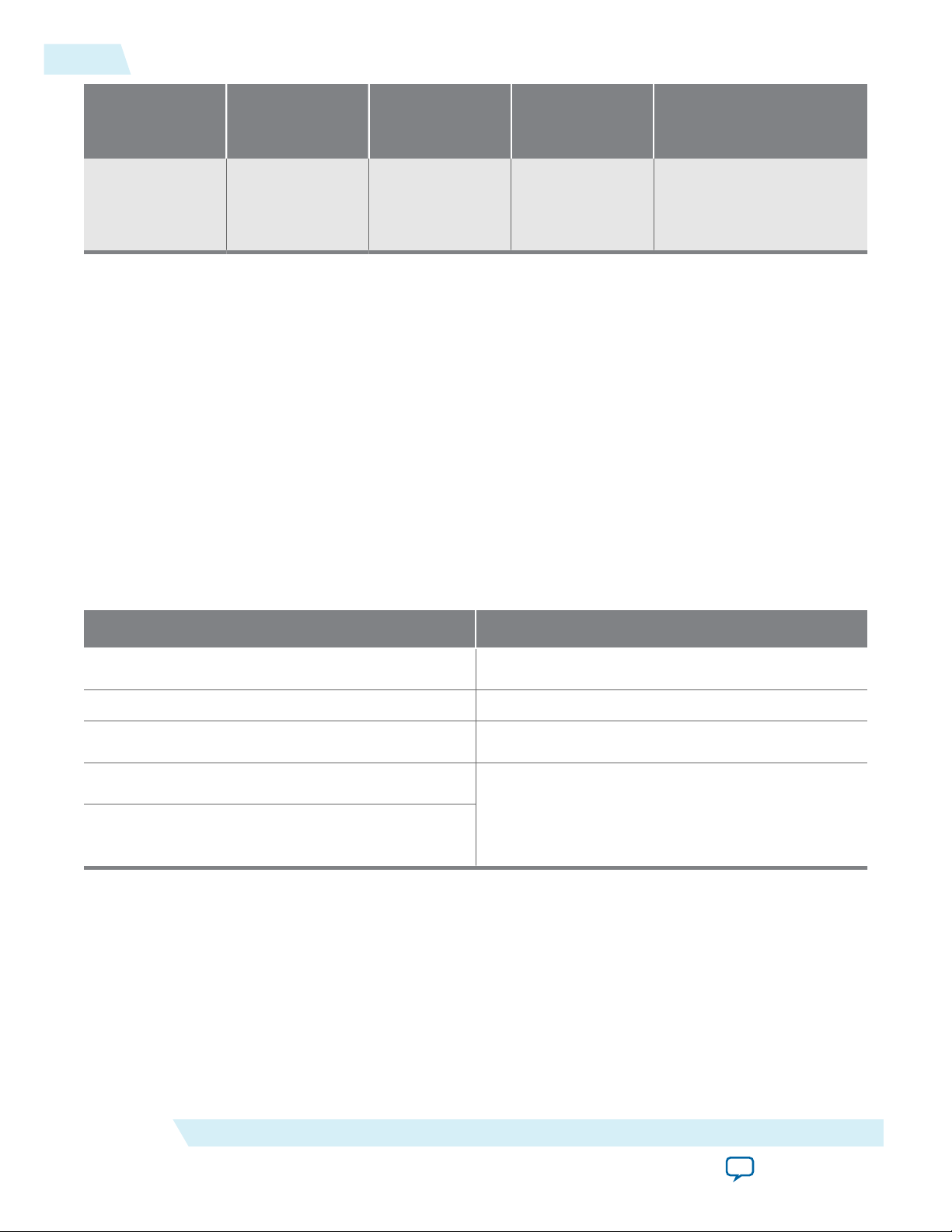

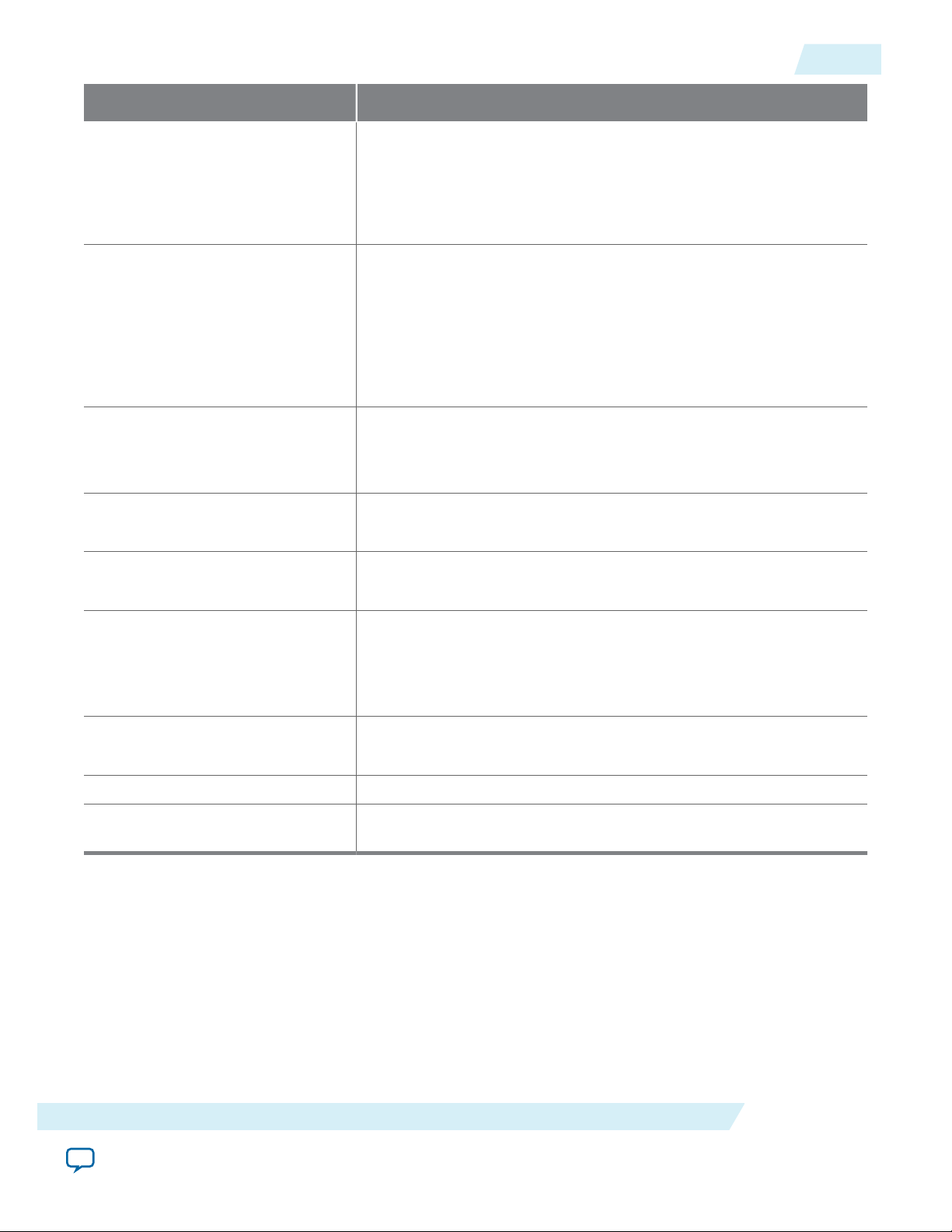

Table 1-2: Feature Comparison for all Hard IP for PCI Express IP Cores

The table compares the features of the four Hard IP for PCI Express IP Cores.

Arria 10 Features

1-3

Feature Avalon-ST Interface Avalon-MM

Interface

Avalon-MM DMA Avalon-ST Interface with SR-

IP Core License Free Free Free Free

Native

Supported Supported Supported Supported

Endpoint

Legacy

Endpoint

(1)

Supported Not Supported Not Supported Not Supported

Root port Supported Supported Not Supported Not Supported

Gen1 ×1, ×2, ×4, ×8 ×1, ×2, ×4, ×8 Not Supported

Gen2 ×1, ×2, ×4, ×8 ×1, ×2, ×4, ×8 ×4, ×8

Gen3 ×1, ×2, ×4, ×8 ×1, ×2, ×4 ×2, ×4, ×8

64-bit Applica‐

Supported Supported Not supported Not supported

×8

×4, ×8

×2, ×4, ×8

tion Layer

interface

IOV

128-bit

Supported Supported Supported Supported

Application

Layer interface

256-bit

Supported Not Supported Supported Supported

Application

Layer interface

Maximum

payload size

Number of tags

128, 256, 512,

1024, 2048 bytes

256 8 16 256

supported for

non-posted

requests

(1)

Not recommended for new designs.

128, 256 bytes 128, 256 bytes 128, 256 bytes

Datasheet

Altera Corporation

Send Feedback

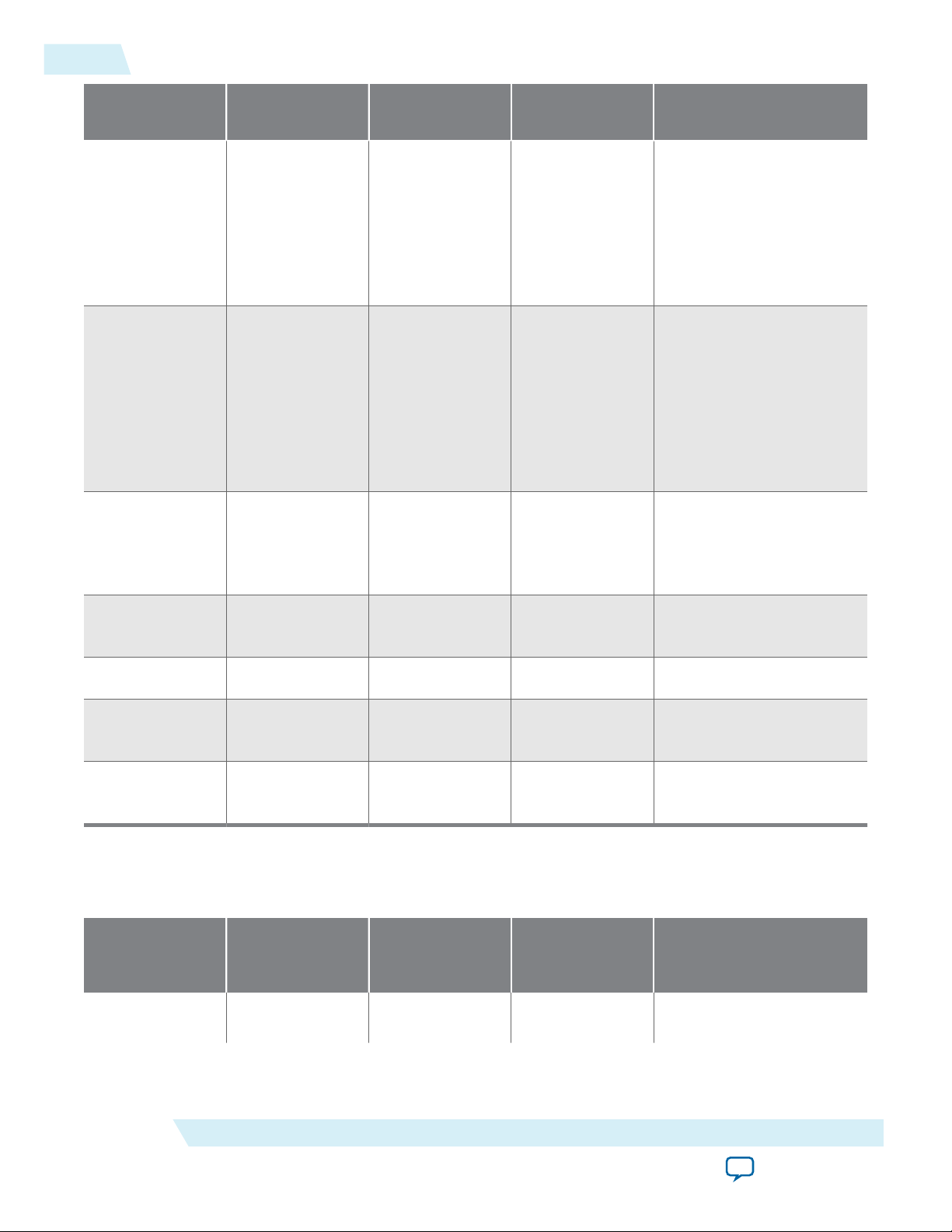

Page 11

1-4

Arria 10 Features

UG-01145_avst

2015.05.04

Feature Avalon-ST Interface Avalon-MM

Interface

Automatically

Not supported Supported Supported Not supported

handle out-oforder

completions

(transparent to

the Application

Layer)

Automatically

Not supported Supported Supported Not Supported

handle requests

that cross 4

KByte address

boundary

(transparent to

the Application

Layer)

Polarity

Supported Supported Supported Supported

Inversion of

PIPE interface

signals

Avalon-MM DMA Avalon-ST Interface with SR-

IOV

Number of MSI

requests

1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 (for

Physical Functions)

MSI-X Supported Supported Supported Supported

Legacy

Supported Supported Supported Supported

interrupts

Expansion

Supported Not supported Not supported Not supported

ROM

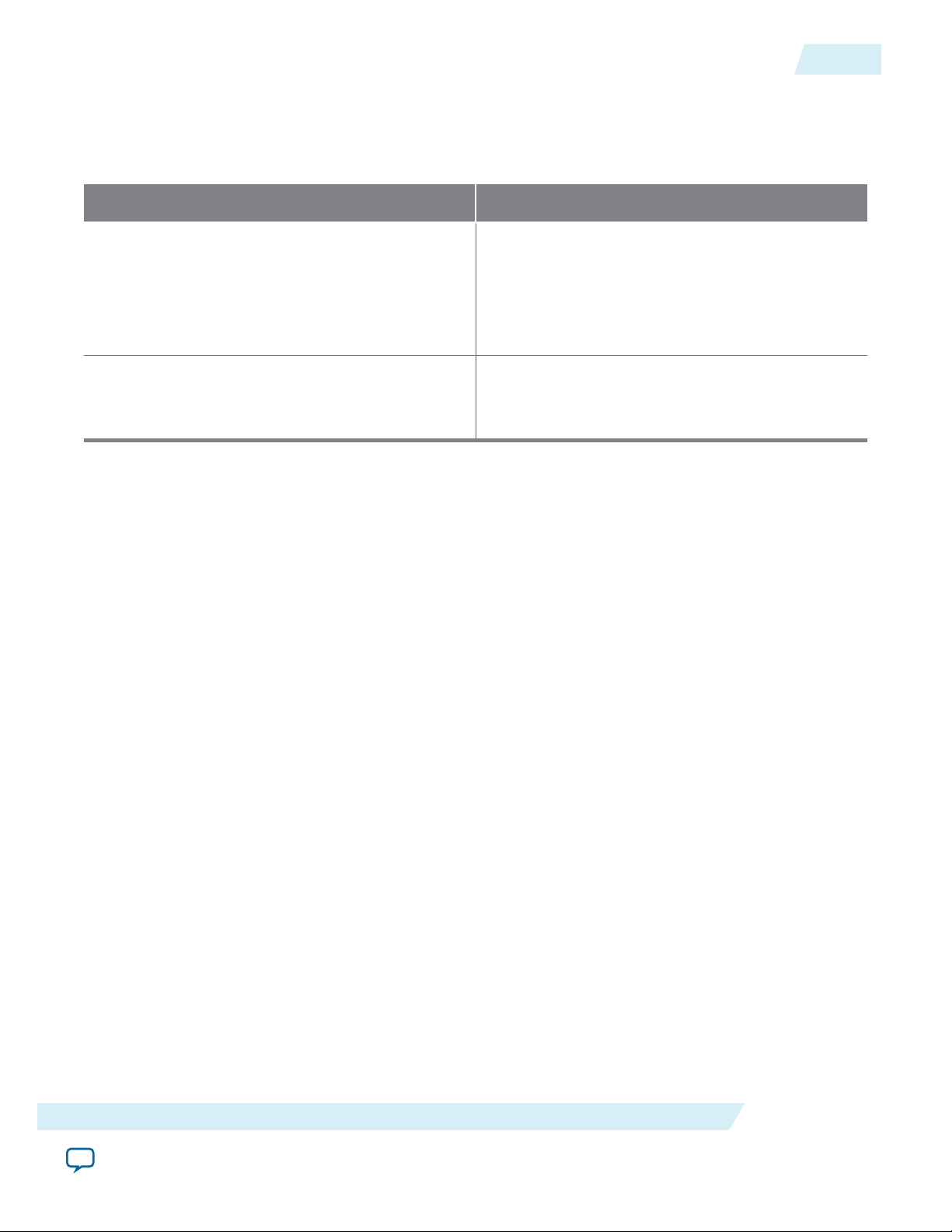

Table 1-3: TLP Support Comparison for all Hard IP for PCI Express IP Cores

The table compares the TLP types that the four Hard IP for PCI Express IP Cores can transmit. Each entry

indicates whether this TLP type is supported (for transmit) by endpoints (EP), Root Ports (RP), or both (EP/RP).

Transaction Layer

Packet type (TLP)

(transmit support)

Memory Read

Avalon-ST Interface Avalon-MM

Interface

Avalon-MM DMA Avalon-ST Interface with SR-

EP/RP EP/RP EP EP

IOV

Request (Mrd)

Altera Corporation

Datasheet

Send Feedback

Page 12

UG-01145_avst

2015.05.04

Arria 10 Features

1-5

Transaction Layer

Packet type (TLP)

(transmit support)

Memory Read

Lock Request

(MRdLk)

Memory Write

Request (MWr)

I/O Read

Request (IORd)

I/O Write

Request (IOWr)

Config Type 0

Read Request

(CfgRd0)

Config Type 0

Write Request

(CfgWr0)

Config Type 1

Read Request

(CfgRd1)

Avalon-ST Interface Avalon-MM

Interface

Avalon-MM DMA Avalon-ST Interface with SR-

EP/RP EP EP

EP/RP EP/RP EP EP

EP/RP EP/RP EP

EP/RP EP/RP EP

RP RP EP

RP RP EP

RP RP EP

IOV

Config Type 1

Write Request

(CfgWr1)

Message

Request (Msg)

Message

Request with

Data (MsgD)

Completion

(Cpl)

Completion

with Data

(CplD)

CompletionLocked (CplLk)

Completion

Lock with Data

(CplDLk)

RP RP EP

EP/RP EP/RP EP

EP/RP EP/RP EP

EP/RP EP/RP EP EP

EP/RP EP EP

EP/RP EP

EP/RP EP

Datasheet

Altera Corporation

Send Feedback

Page 13

1-6

Release Information

UG-01145_avst

2015.05.04

Transaction Layer

Packet type (TLP)

(transmit support)

Fetch and Add

Avalon-ST Interface Avalon-MM

EP

AtomicOp

Request

(FetchAdd)

The Arria 10 Avalon-ST Interface for PCIe Solutions User Guide explains how to use this IP core and not

the PCI Express protocol. Although there is inevitable overlap between these two purposes, use this

document only in conjunction with an understanding of the PCI Express Base Specification.

Note: This release provides separate user guides for the different variants. The Related Information

provides links to all versions.

Related Information

• Arria 10 Avalon-MM Interface for PCIe Solutions User Guide

• Arria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide

• Arria 10 Avalon-ST with SR-IOV PCIe Solutions User Guide

Release Information

Interface

Avalon-MM DMA Avalon-ST Interface with SR-

IOV

Table 1-4: Hard IP for PCI Express Release Information

Item Description

Version 15.0

Release Date May 2015

Ordering Codes No ordering code is required

Product IDs There are no encrypted files for the Arria 10 Hard

IP for PCI Express. The Product ID and Vendor ID

Vendor ID

are not required because this IP core does not

require a license.

Altera Corporation

Datasheet

Send Feedback

Page 14

UG-01145_avst

2015.05.04

Device Family Support

Table 1-5: Device Family Support

Device Family Support

Device Family Support

1-7

Arria 10

Preliminary. The IP core is verified with prelimi‐

nary timing models for this device family. The IP

core meets all functional requirements, but might

still be undergoing timing analysis for the device

family. It can be used in production designs with

caution.

Other device families Refer to the Altera's PCI Express IP Solutions web

page for support information on other device

families.

Related Information

• Altera's PCI Express IP Solutions web page

Configurations

The Arria 10 Hard IP for PCI Express includes a full hard IP implementation of the PCI Express stack

including the following layers:

• Physical (PHY), including:

• Physical Media Attachment (PMA)

• Physical Coding Sublayer (PCS)

• Media Access Control (MAC)

• Data Link Layer (DL)

• Transaction Layer (TL)

Datasheet

The Hard IP supports all memory, I/O, configuration, and message transactions. It is optimized for Altera

devices. The Application Layer interface is also optimized to achieve maximum effective throughput. You

can customize the Hard IP to meet your design requirements.

Altera Corporation

Send Feedback

Page 15

Altera FPGA

User Application

Logic

PCIe

Hard IP

RP

PCIe

Hard IP

EP

User Application

Logic

PCI Express Link

Altera FPGA

1-8

Configurations

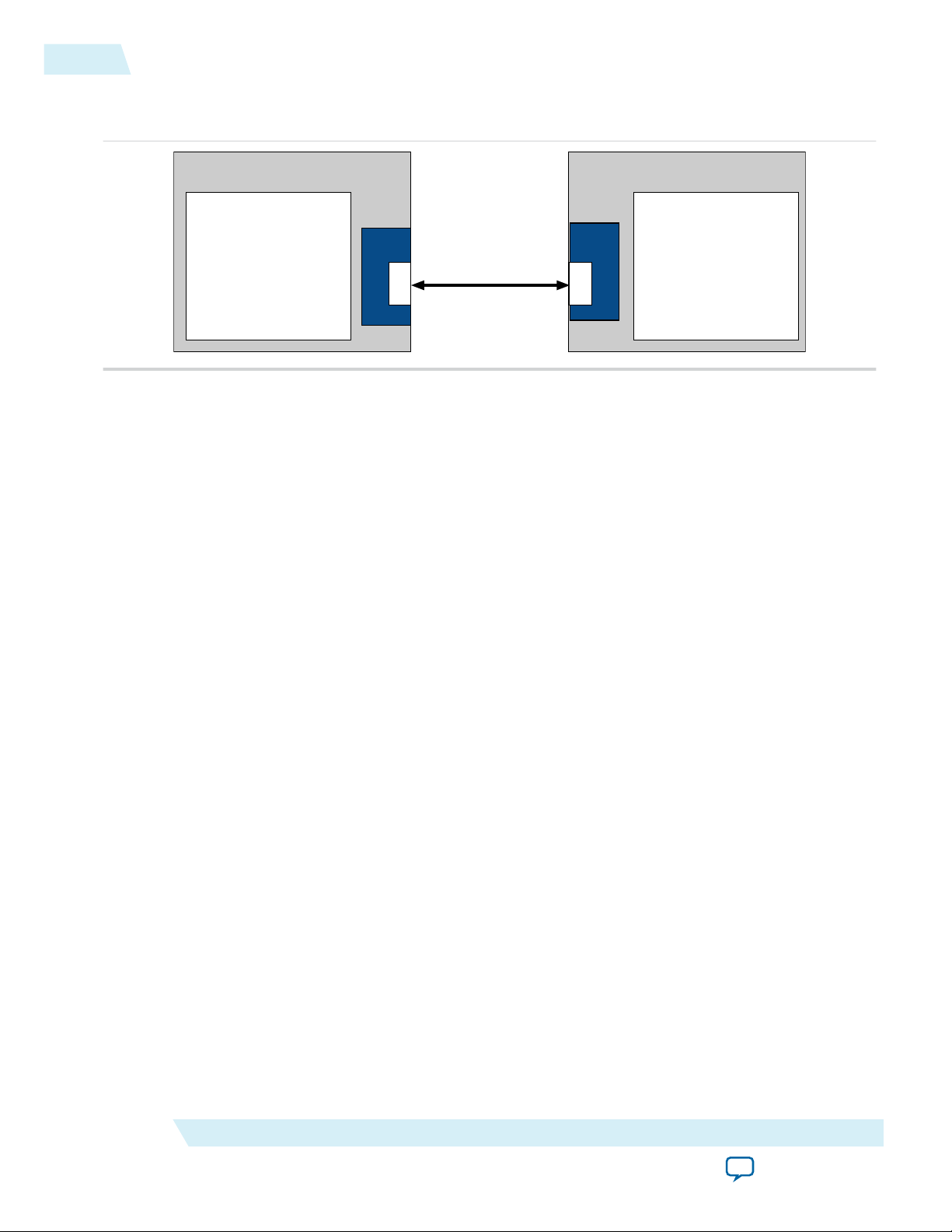

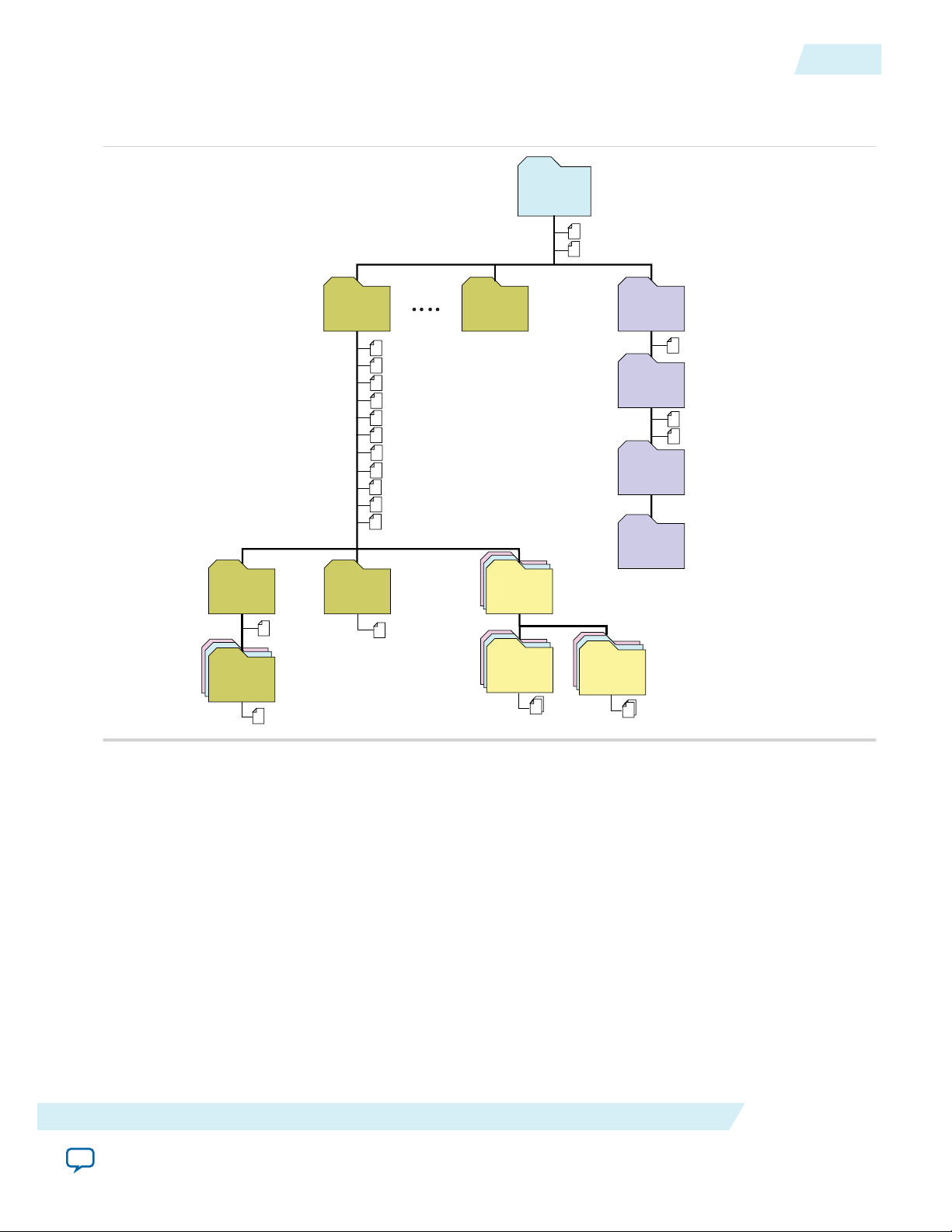

Figure 1-2: PCI Express Application with a Single Root Port and Endpoint

The following figure shows a PCI Express link between two Arria 10 FPGAs.

Figure 1-3: PCI Express Application Using Configuration via Protocol

The Arria 10 design below includes the following components:

• A Root Port that connects directly to a second FPGA that includes an Endpoint.

• Two Endpoints that connect to a PCIe switch.

• A host CPU that implements CvP using the PCI Express link connects through the switch. For more

information about configuration over a PCI Express link, refer to Configuration via Protocol (CvP)

on page 15-1.

UG-01145_avst

2015.05.04

Altera Corporation

Datasheet

Send Feedback

Page 16

PCIe Link

PCIe Hard IP

RP

Switch

PCIe

Hard IP

RP

User Application

Logic

PCIe Hard IP

EP

PCIe Link

PCIe Link

User Application

Logic

Altera FPGA Hard IP for PCI Express

Altera FPGA with Hard IP for PCI Express

Active Serial or

Active Quad

Device Configuration

Configuration via Protocol (CvP)

using the PCI Express Link

Serial or

Quad Flash

USB

Download

cable

PCIe

Hard IP

EP

User

Application

Logic

Altera FPGA with Hard IP for PCI Express

Config

Control

CVP

USB

Host CPU

PCIe

UG-01145_avst

2015.05.04

Arria 10 Avalon-ST Example Designs

1-9

Related Information

Configuration via Protocol (CvP)Implementation in Altera FPGAs User Guide

Arria 10 Avalon-ST Example Designs

Altera provides example designs to familiarize you with the available functionality. Each design connects

the device under test (DUT) to an application programming platform (APP), labeled APPs in the figure

below. Starting in the Quartus II 14.1 release, if you change these parameters Qsys updates the testbench

Datasheet

to match the parameters you've selected.

Send Feedback

Altera Corporation

Page 17

1-10

Debug Features

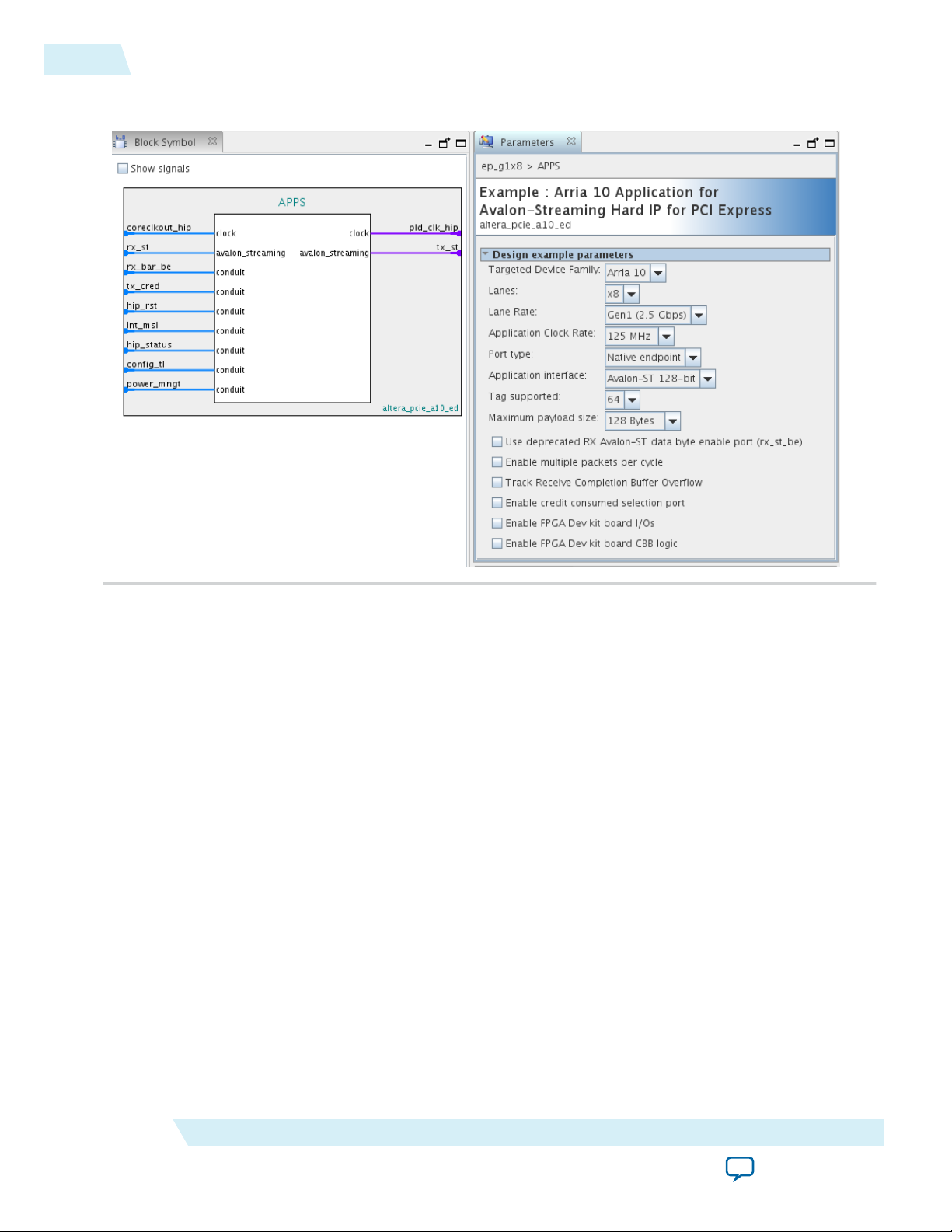

Figure 1-4: Example Design Preset Parameters

UG-01145_avst

2015.05.04

You can download the Qsys example designs for the Arria 10 Hard IP for PCI Express from the

<install_dir>/ip/altera/altera_pcie/altera_pcie_a10_ed/example_design/a10 directory.

When you click the Example Design button in the Parameter Editor, you are prompted to specify the

example design location. After example design generation completes, this directory contains one or two

example designs. One is the example design from the <install_dir> that best matches the current parameter

settings. This example design provides a static DUT. The other example design is a customized example

design that matches your parameter settings exactly; starting in the Quartus II software v14.1, this feature

is available for most but not all IP core variations. If this feature is not available for your particular

parameter settings, the Parameter Editor displays a warning.

Debug Features

Debug features allow observation and control of the Hard IP for faster debugging of system-level

problems.

Related Information

Debugging on page 18-1

Altera Corporation

Datasheet

Send Feedback

Page 18

UG-01145_avst

2015.05.04

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive verification. The

simulation environment uses multiple testbenches that consist of industry-standard bus functional

models (BFMs) driving the PCI Express link interface. Altera performs the following tests in the

simulation environment:

• Directed and pseudorandom stimuli are applied to test the Application Layer interface, Configuration

Space, and all types and sizes of TLPs

• Error injection tests that inject errors in the link, TLPs, and Data Link Layer Packets (DLLPs), and

check for the proper responses

• PCI-SIG® Compliance Checklist tests that specifically test the items in the checklist

• Random tests that test a wide range of traffic patterns

Altera provides example designs that you can leverage to test your PCBs and complete compliance base

board testing (CBB testing) at PCI-SIG, upon request.

Compatibility Testing Environment

Altera has performed significant hardware testing to ensure a reliable solution. In addition, Altera

internally tests every release with motherboards and PCI Express switches from a variety of manufac‐

turers. All PCI-SIG compliance tests are run with each IP core release.

IP Core Verification

1-11

Performance and Resource Utilization

Because the PCIe protocol stack is implemented in hardened logic, it uses no core device resources (no

ALMs and no embedded memory).

Related Information

Fitter Resources Reports

Recommended Speed Grades

Recommended speed grades are pending characterization of production Arria 10 devices.

Related Information

• Area and Timing Optimization

• Altera Software Installation and Licensing Manual

• Setting up and Running Analysis and Synthesis

Steps in Creating a Design for PCI Express

Datasheet

Before you begin

Select the PCIe variant that best meets your design requirements.

Altera Corporation

Send Feedback

Page 19

1-12

Steps in Creating a Design for PCI Express

UG-01145_avst

2015.05.04

• Is your design an Endpoint or Root Port?

• What Generation do you intend to implement?

• What link width do you intend to implement?

• What bandwidth does your application require?

• Does your design require CvP?

1. Select parameters for that variant.

2. Simulate using an Altera-provided example design. All of Altera's static PCI Express example designs

are available under <install_dir>/ip/altera/altera_pcie/. Alternatively, generate an example design that

matches your parameter settings, or create a simulation model and use your own custom or thirdparty BFM. The Qsys Generate menu generates simulation models. Altera supports ModelSim®-Altera

for all IP. The PCIe cores support the Aldec RivieraPro, Cadence NCsim, Mentor Graphics ModelSim,

and Synopsys VCS and VCS-MX simulators.

3. Compile your design using the Quartus II software. If the versions of your design and the Quartus II

software you are running do not match, regenerate your PCIe design.

4. Download your design to an Altera development board or your own PCB. Click on the All Develop‐

ment Kits link below for a list of Altera's development boards.

5. Test the hardware. You can use Altera's SignalTap® II Logic Analyzer or a third-party protocol

analyzer to observe behavior.

6. Substitute your Application Layer logic for the Application Layer logic in Altera's testbench. Then

repeat Steps 3–6. In Altera's testbenches, the PCIe core is typically called the DUT (device under test).

The Application Layer logic is typically called APPS.

Related Information

• Parameter Settings on page 4-1

• Getting Started with the Arria 10 Hard IP for PCI Express on page 2-1

• All Development Kits

Altera Corporation

Datasheet

Send Feedback

Page 20

Getting Started with the Arria 10 Hard IP for PCI

APPS

altpcied_<dev>_hwtcl.v

Hard IP for PCI Express Testbench for Endpoints

Avalon-ST TX

Avalon-ST RX

reset

status

Avalon-ST TX

Avalon-ST RX

reset

status

DUT

<instance_name>_altera_pcie

_a10_hip_<version>

_<generated_string>.v

Root Port Model

altpcie_tbed_<dev>_hwtcl.v

PIPE or

Serial

Interface

Root Port BFM

altpcietb_bfm_rpvar_64b_x8_pipen1b

Root Port Driver and Monitor

altpcietb_bfm_vc_intf

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Express

2015.05.04

UG-01145_avst

Subscribe

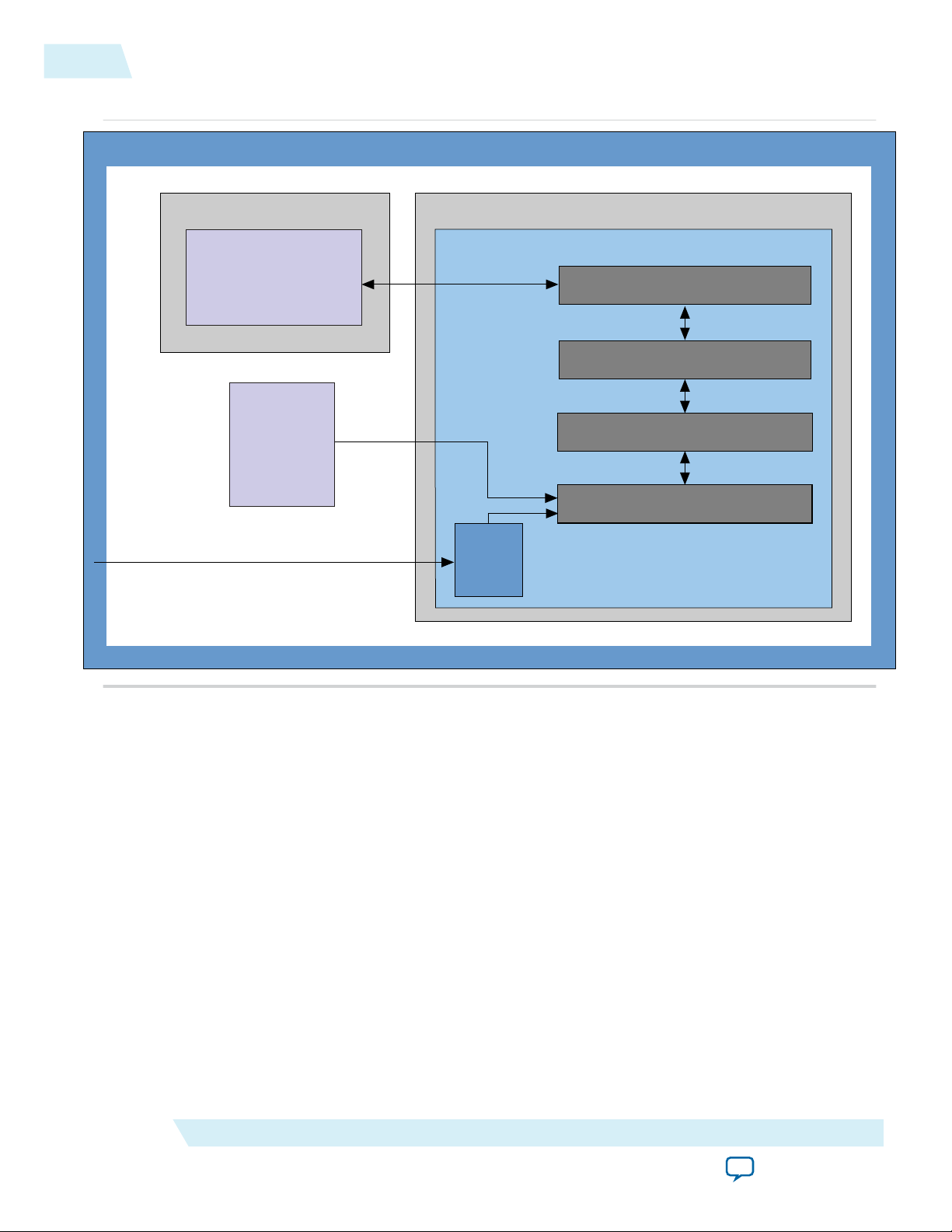

This section provides instructions to help you quickly customize, simulate, and compile the Arria 10 Hard

IP for PCI Express IP Core. When you install the Quartus II software you also install the IP Library. This

installation includes design examples for Hard IP for PCI Express under the <install_dir>/ip/altera/altera_

pcie/ directory.

After you install the Quartus II software, you can copy the design examples from the <install_dir>/ip/altera/

altera_pcie/altera_pcie_a10_ed/example_design/a10 directory. This walkthrough uses the Gen1 ×8 Endpoint,

ep_g1x8.qsys. The following figure illustrates the top-level modules of the testbench in which the DUT, a

Gen1 Endpoint, connects to a chaining DMA engine, labeled APPS in the following figure, and a Root

Port model. The simulation can use the parallel PHY Interface for PCI Express (PIPE) or serial interface.

Figure 2-1: Testbench for an Endpoint

Send Feedback

2

Note:

The Quartus II software automatically creates a simulation log file, altpcie_monitor_<dev>_dlhip_tlp_

file_log.log, in your simulation directory. Refer to Understanding Simulation Log File Generation for

details.

Altera provides example designs to help you get started with the Arria 10 Hard IP for PCI Express IP

Core. You can use example designs as a starting point for your own design. The example designs include

scripts to compile and simulate the Arria 10 Hard IP for PCI Express IP Core. This example design

provides a simple method to perform basic testing of the Application Layer logic that interfaces to the

Hard IP for PCI Express.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 21

2-2

Qsys Design Flow

For a detailed explanation of this example design, refer to the Testbench and Design Example chapter. If

you choose the parameters specified in this chapter, you can run all of the tests included in Testbench and

Design Example chapter.

For more information about Qsys, refer to System Design with Qsys in the Quartus II Handbook. For more

information about the Qsys GUI, refer to About Qsys in Quartus II Help.

Related Information

• Testbench and Design Example on page 17-1

• Understanding Simulation Log File Generation on page 2-4

• System Design with Qsys

• About Qsys

Qsys Design Flow

Copy the ep_g1x8.qsys design example from the <install_dir>/ip/altera/altera_pcie/altera_pcie/altera_pcie_

a10_ed/example_designs/a10 to your working directory.

The following figure illustrates this Qsys system.

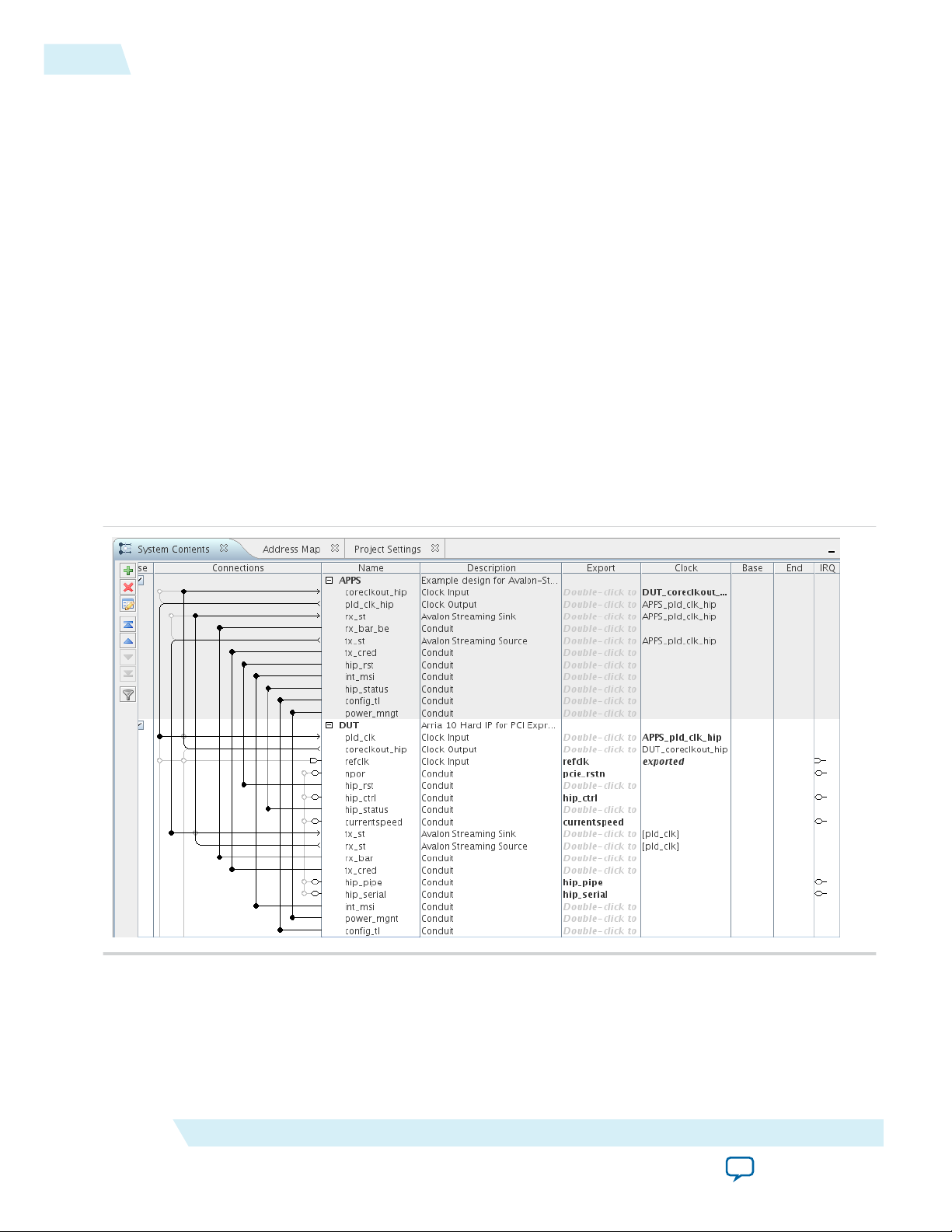

Figure 2-2: Complete Gen1 ×8 Endpoint (DUT) Connected to Example Design (APPS)

UG-01145_avst

2015.05.04

Altera Corporation

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Page 22

UG-01145_avst

2015.05.04

The example design includes the following components:

• DUT—This is Gen1 ×8 Endpoint. For your own design, you can select the data rate, number of lanes,

and either Endpoint or Root Port mode.

• APPS—This Root Port BFM configures the DUT and drives read and write TLPs to test DUT

functionality. An Endpoint BFM is available if your PCI Express design implements a Root Port.

Generating the Testbench

1. On the Generate menu, select Generate Testbench System. Specify the parameters listed in the

following table.

Table 2-1: Parameters to Specify on the Generation Tab in Qsys

Parameter Value

Testbench System

Create testbench Qsys system Standard, BFMs for standard Qsys interfaces

Create testbench simulation model Verilog

Generating the Testbench

2-3

Allow mixed-language simulation Turn this option off

Output Directory

Clear output directories for selected generation

Turn this option off

targets

Testbench <working_dir>/ep_g1x8_tb/

2.

Click the Generate button at the bottom of the Generation tab to create the testbench.

Note:

This testbench assumes that you are running the DMA application that the example design

available in the installation directory creates. Otherwise, the testbench tests will probably fail unless

your own testbench has equivalent functionality.

Simulating the Example Design

1. Start your simulation tool. This example uses the ModelSim® software.

2. From the ModelSim transcript window, in the testbench directory, <working_dir>/ep_g1x8_tb/ep_g1x8_

tb/sim/mentor, type the following commands:

a. do msim_setup.tcl

b. ld_debug (This command compiles all design files and elaborates the top-level design without any

optimization.)

c. run -all

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Altera Corporation

Page 23

2-4

Generating Quartus II Synthesis Files

The simulation includes the following stages:

• Link training

• Configuration

• DMA reads and writes

• Root Port to Endpoint memory reads and writes

Disabling Scrambling to Interpret TLPs at the PIPE Interface

1. Go to <project_directory/ep_g1x8_tb/ep_g1x8_tb/altera_pcie_a10_tbed_140/sim/.

2. Open altpcietb_bfm_top_rp.v.

3. Locate the assignment for test_in[2:1]. Set test_in[2] = 1 and test_in[1] = 0. Changing

test_in[2] = 1 disables data scrambling on the PIPE interface.

4. Save altpcietb_bfm_top_rp.v.

Generating Quartus II Synthesis Files

1. On the Generate menu, select Generate HDL.

2. For Create HDL design files for synthesis, select Verilog.

You can leave the default settings for all other items.

3. Click Generate to generate files for Quartus II synthesis.

4. Click Finish when the generation completes.

UG-01145_avst

2015.05.04

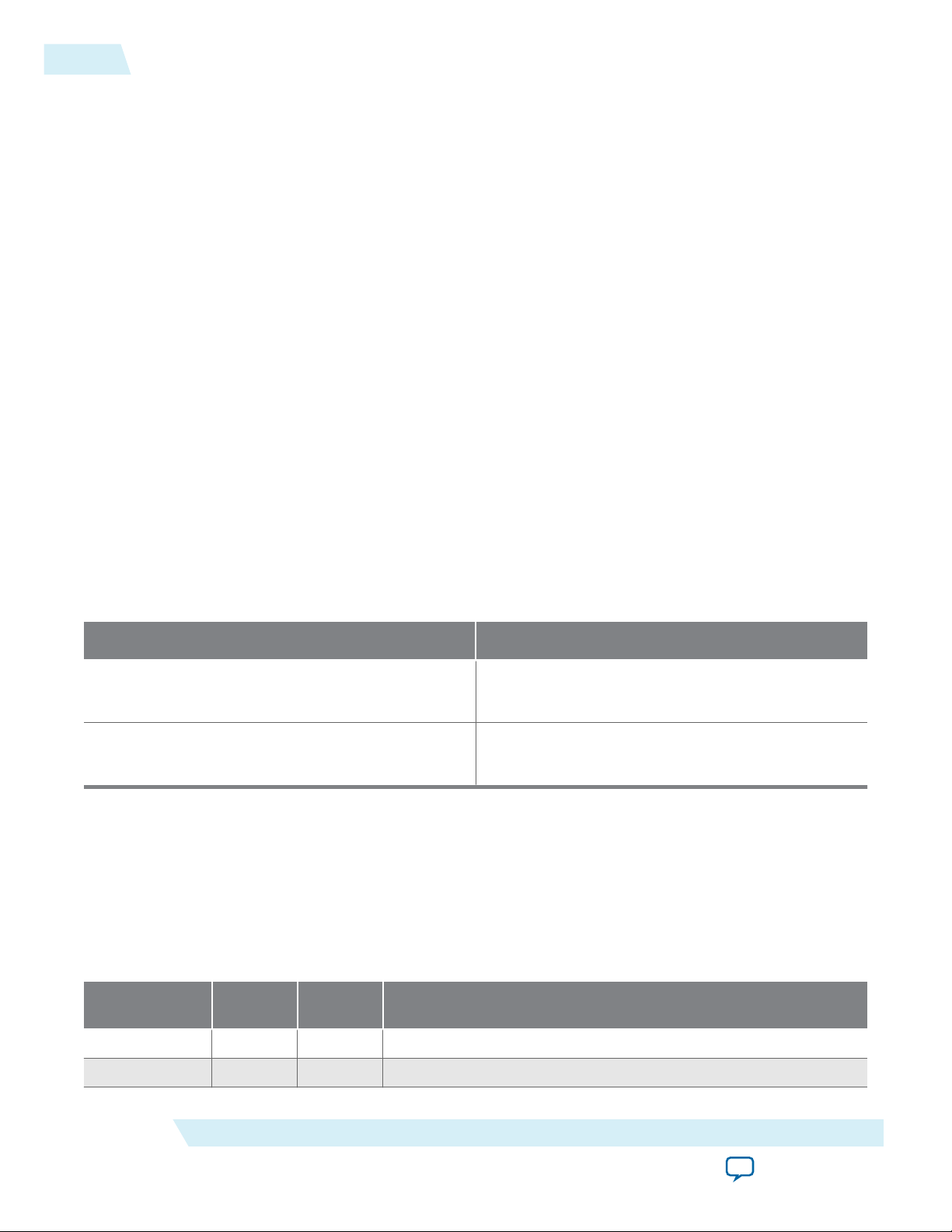

Understanding the Files Generated

Table 2-2: Overview of Qsys Generation Output Files

Directory Description

<testbench_dir>/<variant_name>/synth Includes the top-level HDL file for the Hard IP for

PCI Express.

<testbench_dir>/<variant_name>/sim/<cad_vendor>

Includes the HDL source files and scripts for the

simulation testbench.

For a more detailed listing of the directories and files the Quartus II software generates, refer to Files

Generated for Altera IP Cores in Compiling the Design in the Qsys Design Flow.

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file, altpcie_

monitor_<dev>_dlhip_tlp_file_log.log in your simulation directory.

Table 2-3: Sample Simulation Log File Entries

Time TLP Type Payload

(Bytes)

TLP Header

17989 RX CfgRd0 0004 04000001_0000000F_01080008

17989 RX MRd 0000 00000000_00000000_01080000

Altera Corporation

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Page 24

UG-01145_avst

2015.05.04

Understanding Physical Placement of the PCIe IP Core

2-5

Time TLP Type Payload

(Bytes)

TLP Header

18021 RX CfgRd0 0004 04000001_0000010F_0108002C

18053 RX CfgRd0 0004 04000001_0000030F_0108003C

18085 RX MRd 0000 00000000_00000000_0108000C

Understanding Physical Placement of the PCIe IP Core

For more information about physical placement of the PCIe blocks, refer to the links below. Contact your

Altera sales representative for detailed information about channel and PLL usage.

Related Information

• Channel Placement and fPLL Usage for the Gen1 and Gen2 Data Rates on page 5-5

• Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate on page 5-7

Adding Virtual Pin Assignment to the Quartus II Settings File (.qsf)

To compile successfully you must add a virtual pin assignment statement for the PIPE interface to

your .qsf file. The PIPE interface is useful for debugging, but is not a top-level interface of the IP core.

1. Browse to the synthesis directory that includes the .qsf for your project, <project_dir>/ep_g1x8/

2. Open ep_g1x8.qsf.

3. Add the following assignment statement:

set_instance_assignment -name VIRTUAL_PIN ON -to hip_pipe_*

4. Save the .qsf file.

Compiling the Design in the Qsys Design Flow

To compile the Qsys design example in the Quartus II software, you must create a Quartus II project and

add your Qsys files to that project.

1. Before compiling, you can optionally turn on two parameters in the testbench. The first parameter

specifies pin assignments that match those for the Altera Development Kit board I/Os. The second

parameter enables the Compliance Base Board (CBB) logic on the development board. In the Gen1 x8

example design, complete the following steps if you want to enable these parameters:

a. Right-click the APPS component and select Edit.

b. Turn on Enable FPGA Dev kit board I/Os.

c. Turn on Enable FPGA Dev kit board CBB logic.

d. Click Finish.

e. On the Generate menu, select Generate Testbench System and then click Generate.

f. On the Generate menu, select Generate HDL and then click Generate. (You can use the same

parameters that are specified in Generating the Testbench earlier in this chapter).

2. In the Quartus II software, click the New Project Wizard icon.

3. Click Next in the New Project Wizard: Introduction (The introduction does not appear if you

previously turned it off.)

4. On the Directory, Name, Top-Level Entity page, enter the following information:

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Altera Corporation

Page 25

2-6

Compiling the Design in the Qsys Design Flow

a. The working directory shown is correct. You do not have to change it.

b. For the project name, click the browse button browse to the synthesis directory that includes your

Qsys project, <working_dir>/ep_g1x8/synth and click Choose. If the top-level design entity and Qsys

system names are identical, the Quartus II software treats the Qsys system as the top-level design

entity.

c. For What is the name of this project, select your variant name ep_g1x8. Then click Open. If the

top-level design entity and Qsys system names are identical, the Quartus II software treats the Qsys

system as the top-level design entity.

d. For Project Type select Empty project.

5. Click Next to display the Add Files page.

6. Complete the following steps to add the Quartus II IP File ( .qip )to the project:

a. Click the browse button. The Select File dialog box appears.

b. Browse up one level to <working_dir>/ep_g1x8/ button.

c. In the Files of type list, select IP Variation Files (*.qip *.sip).

d. Click ep_g1x8.qip and then click Open.

e. On the Add Files page, click Add.

7. Click Next to display the Device page.

8. On the Family & Device Settings page, choose the following target device family and options:

UG-01145_avst

2015.05.04

a. In the Family list, select Arria 10 (GX/SX/GT).

b. In the Devices list, select Arria 10 All.

c. In the Devices list, select All.

d. In the Available devices list, select the appropriate device. For Arria 10 ES2 development kits, select

10AX115S1F45I3SGE2.

9. Click Next to close this page and display the EDA Tool Settings page.

10.From the Simulation list, select ModelSim®. From the Format list, select the HDL language you

intend to use for simulation.

11.Click Next to display the Summary page.

12.Check the Summary page to ensure that you have entered all the information correctly.

13.Click Finish to create the Quartus II project.

14.Before compiling, you must assign I/O standards to the pins of the device. Refer to Making Pin

Assignments to Assign I/O Standard to Serial Data Pins for instructions.

15.You must connect the pin_perst reset signal to the correcsponding nPERST pin of the device. Refer to

the definition of pin_perst in the Reset, Status, and Link Training Signals section for more informa‐

tion.

16.Next, set the value of the test_in bus to a value that is compatible for hardware testing. In Qsys design

example provided, test_in is a top-level port.

a. Comment out the test_in port in the top-level Verilog generated file.

b. Add the following declaration, wire[31:0] test_in, to the same top-level Verilog file.

c. Assign hip_ctrl_test_in = 32'hA8.

d. Connect test_in to hip_ctrl_test_in.

17.To compile your design using the Quartus II software, on the Processing menu, click Start Compila‐

Altera Corporation

Refer to the definition of test_in in the Test Signals section for more information about the bits of the

test_in bus.

tion. The Quartus II software then performs all the steps necessary to compile your design.

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Page 26

<your_testbench>_tb.csv

<your_testbench>_tb.spd

<your_ip>.cmp - VHDL component declaration file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.qip - Lists IP synthesis files

<your_ip>.sip - Contains assingments for IP simulation files

<your_ip>.v or .vhd

Top-level IP synthesis file

<your_ip>.v or .vhd

Top-level simulation file

<simulator_setup_scripts>

<your_ip>.qsys - System or IP integration file

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

<your_ip>_generation.rpt - IP generation report

<your_ip>.debuginfo - Contains post-generation information

<your_ip>.html - Connection and memory map data

<your_ip>.bsf - Block symbol schematic

<your_ip>.spd - Combines simulation scripts for multiple cores

<your_ip>_tb.qsys

Testbench system file

<your_ip>.sopcinfo - Software tool-chain integration file

<project directory>

<EDA tool setup

scripts>

<your_ip>

IP variation files

<testbench>_tb

testbench system

sim

Simulation files

synth

IP synthesis files

sim

simulation files

<EDA tool name>

Simulator scripts

<testbench>_tb

<ip subcores> n

Subcore libraries

sim

Subcore

Simulation files

synth

Subcore

synthesis files

<HDL files>

<HDL files>

<your_ip> n

IP variation files

testbench files

UG-01145_avst

2015.05.04

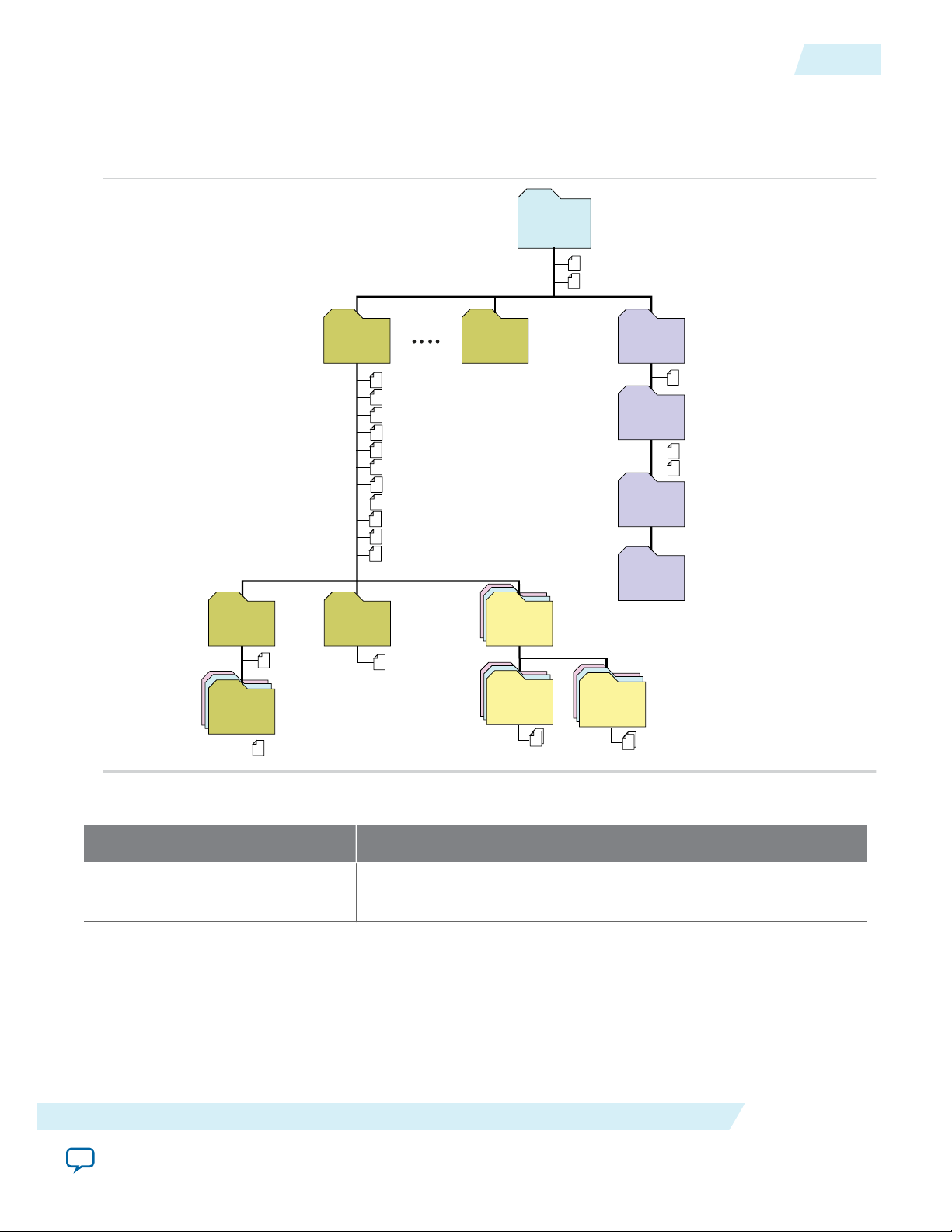

Files Generated for Altera IP Cores

Figure 2-3: IP Core Generated Files

Modifying the Example Design

2-7

Related Information

• Making Pin Assignments to Assign I/O Standard to Serial Data Pins on page 14-1

• Test Signals on page 6-62

• Reset, Status, and Link Training Signals on page 6-31

• Generating the Testbench on page 2-3

• Simulating the Example Design on page 3-5

• Simulating the Example Design on page 3-5

Modifying the Example Design

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

To use this example design as the basis of your own design, replace the Chaining DMA Example shown in

the following figure with your own Application Layer design. Then modify the Root Port BFM driver to

generate the transactions needed to test your Application Layer.

Altera Corporation

Page 27

Hard IP for PCI Express

Altera FPGA

PCB

Root

Port

BFM

perstn (npor)

Reset

APPS DUT

Chaining DMA

(User Application)

Transaction Layer

Data Link Layer

PHY MAC Layer

PHY IP Core for PCI Express

2-8

Using the IP Catalog To Generate Your Arria 10 Hard IP for PCI Express as a Separate Component

Figure 2-4: Testbench for PCI Express

UG-01145_avst

2015.05.04

Using the IP Catalog To Generate Your Arria 10 Hard IP for PCI Express as a Separate

Component

Altera Corporation

You can also instantiate the Arria 10 Hard IP for PCI Express IP Core as a separate component for

integration into your project.

You can use the Quartus II IP Catalog and IP Parameter Editor to select, customize, and generate files

representing your custom IP variation. The IP Catalog (Tools > IP Catalog) automatically displays IP

cores available for your target device. Double-click any IP core name to launch the parameter editor and

generate files representing your IP variation.

For more information about the customizing and generating IP Cores refer to Specifying IP Core

Parameters and Options in Introduction to Altera IP Cores. For more information about upgrading older

IP cores to the current release, refer to Upgrading Outdated IP Cores in Introduction to Altera IP Cores.

Related Information

• Qsys Design Flow on page 2-2

• Introduction to Altera IP Cores

• Managing Quartus II Projects

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Page 28

<your_testbench>_tb.csv

<your_testbench>_tb.spd

<your_ip>.cmp - VHDL component declaration file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.qip - Lists IP synthesis files

<your_ip>.sip - Contains assingments for IP simulation files

<your_ip>.v or .vhd

Top-level IP synthesis file

<your_ip>.v or .vhd

Top-level simulation file

<simulator_setup_scripts>

<your_ip>.qsys - System or IP integration file

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

<your_ip>_generation.rpt - IP generation report

<your_ip>.debuginfo - Contains post-generation information

<your_ip>.html - Connection and memory map data

<your_ip>.bsf - Block symbol schematic

<your_ip>.spd - Combines simulation scripts for multiple cores

<your_ip>_tb.qsys

Testbench system file

<your_ip>.sopcinfo - Software tool-chain integration file

<project directory>

<EDA tool setup

scripts>

<your_ip>

IP variation files

<testbench>_tb

testbench system

sim

Simulation files

synth

IP synthesis files

sim

simulation files

<EDA tool name>

Simulator scripts

<testbench>_tb

<ip subcores> n

Subcore libraries

sim

Subcore

Simulation files

synth

Subcore

synthesis files

<HDL files>

<HDL files>

<your_ip> n

IP variation files

testbench files

UG-01145_avst

2015.05.04

Files Generated for Altera IP Cores

The Quartus II software generates the following IP core output file structure:

Figure 2-5: IP Core Generated Files

Files Generated for Altera IP Cores

2-9

Table 2-4: IP Core Generated Files

File Name Description

<my_ip>.qsys

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

The Qsys system or top-level IP variation file. <my_ip> is the name

that you give your IP variation.

Altera Corporation

Page 29

2-10

Files Generated for Altera IP Cores

File Name Description

<system>.sopcinfo Describes the connections and IP component parameterizations in

your Qsys system. You can parse its contents to get requirements

when you develop software drivers for IP components.

Downstream tools such as the Nios II tool chain use this file.

The .sopcinfo file and the system.h file generated for the Nios II tool

chain include address map information for each slave relative to each

master that accesses the slave. Different masters may have a different

address map to access a particular slave component.

<my_ip>.cmp The VHDL Component Declaration (.cmp) file is a text file that

contains local generic and port definitions that you can use in VHDL

design files.

UG-01145_avst

2015.05.04

<my_ip>.html

A report that contains connection information, a memory map

showing the address of each slave with respect to each master to

which it is connected, and parameter assignments.

<my_ip>_generation.rpt IP or Qsys generation log file. A summary of the messages during IP

generation.

<my_ip>.debuginfo Contains post-generation information. Used to pass System Console

and Bus Analyzer Toolkit information about the Qsys interconnect.

The Bus Analysis Toolkit uses this file to identify debug components

in the Qsys interconnect.

<my_ip>.qip

Contains all the required information about the IP component to

integrate and compile the IP component in the Quartus II software.

<my_ip>.csv Contains information about the upgrade status of the IP component.

<my_ip>.bsf A Block Symbol File (.bsf) representation of the IP variation for use

in Quartus II Block Diagram Files (.bdf).

<my_ip>.spd

Required input file for ip-make-simscript to generate simulation

scripts for supported simulators. The .spd file contains a list of files

generated for simulation, along with information about memories

that you can initialize.

<my_ip>.ppf The Pin Planner File (.ppf) stores the port and node assignments for

<my_ip>_bb.v You can use the Verilog black-box (_bb.v) file as an empty module

<my_ip>.sip Contains information required for NativeLink simulation of IP

<my_ip>_inst.v or _inst.vhd HDL example instantiation template. You can copy and paste the

Altera Corporation

IP components created for use with the Pin Planner.

declaration for use as a black box.

components. You must add the .sip file to your Quartus project.

contents of this file into your HDL file to instantiate the IP variation.

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Page 30

UG-01145_avst

2015.05.04

<my_ip>.regmap If the IP contains register information, the .regmap file generates.

Files Generated for Altera IP Cores

File Name Description

The .regmap file describes the register map information of master

and slave interfaces. This file complements the .sopcinfo file by

providing more detailed register information about the system. This

enables register display views and user customizable statistics in

System Console.

2-11

<my_ip>.svd

<my_ip>.v

or

<my_ip>.vhd

mentor/

aldec/

/synopsys/vcs

/synopsys/vcsmx

Allows HPS System Debug tools to view the register maps of

peripherals connected to HPS within a Qsys system.

During synthesis, the .svd files for slave interfaces visible to System

Console masters are stored in the .sof file in the debug section.

System Console reads this section, which Qsys can query for register

map information. For system slaves, Qsys can access the registers by

name.

HDL files that instantiate each submodule or child IP core for

synthesis or simulation.

Contains a ModelSim® script msim_setup.tcl to set up and run a

simulation.

Contains a Riviera-PRO script rivierapro_setup.tcl to setup and run a

simulation.

Contains a shell script vcs_setup.sh to set up and run a VCS

®

simulation.

Contains a shell script vcsmx_setup.sh and synopsys_ sim.setup file to

set up and run a VCS MX® simulation.

/cadence

Contains a shell script ncsim_setup.sh and other setup files to set up

and run an NCSIM simulation.

/submodules Contains HDL files for the IP core submodule.

<child IP cores>/ For each generated child IP core directory, Qsys generates /synth and /

sim sub-directories.

Getting Started with the Arria 10 Hard IP for PCI Express

Send Feedback

Altera Corporation

Page 31

Getting Started with the Configuration Space

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Bypass Mode Qsys Example Design

2014.08.18

UG-01145_avst

Subscribe

This Qsys design example demonstrates Configuration Space Bypass mode for the Arria 10 Hard IP for

PCI Express IP Core. A Root Port BFM provides stimulus to the Endpoint design. The Endpoint bypasses

the standard Configuration Space to access the custom Configuration Space and memory of two

functions. The Configuration Space Bypass Example Design performs the following functions:

• Accepts Configuration, Memory, and Message TLPs on the Arria 10 Hard IP for PCI Express RX

Avalon-ST interface

• Translates Type 0 Configuration Read and Configuration Write Requests to Avalon-MM read and

write requests that target the Configuration Space of either Function 0 or Function 1.

• Responds to invalid Type 0 Configuration Requests with an Unsupported Request (UR) status in a

Completion Message.

• Converts single dword Memory Read and Memory Write Requests to access 32-bit registers of the

target function using the Avalon-MM interface.

• Maps two contiguous MBytes of memory for the two functions with the first MByte for Function 0 and

the second MByte for Function 1.

• Sets up two registers for each function.

• Drops the following invalid Write Requests:

Send Feedback

3

• Memory Write Requests with a payload of more than one dword

• Messages with data

• Returns Completer Abort (CA) status in Completion message for invalid Memory Read Requests such

as Memory Read Requests with a payload greater than one dword.

• Returns a Completion Status of Successful Completion for valid Configuration Requests to Function 0

and Function 1.

The following figure illustrates, the components of the Configuration Space Bypass Mode Qsys Example

Design. The example design includes the following components:

• DUT: The Arria 10 Hard IP for PCI Express. The example turns on the Enable Configuration Space

Bypass parameter.

• APPS: The Configuration Space Bypass application demonstrates Configuration Space Bypass mode.

• pcie_reconfig_driver_0: The PCIe Reconfig Driver drives the Transceiver Reconfiguration Controller.

This driver is a plain text Verilog HDL file that you can modify if necessary to meet your system

requirements.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device