Page 1

ALTDLL and ALTDQ_DQS

Megafunctions User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Software Version: 9.1

Document Version: 5.0

Document Date: February 2012

Page 2

Copyright © 2010 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other

words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other

countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty,

but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of

any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services

.

UG-01032-5.0

Page 3

Contents

Chapter 1. About these Megafunctions

Device Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Chapter 2. Getting Started

Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Build the Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Simulate the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Create Timing Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Compile the Design and Verify Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Adjust Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Design Example: Implementing Read Paths Using Stratix III Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Generate the Megafunctions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Compile and Simulate the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

Chapter 3. Parameter Settings

ALTDLL Parameter Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

ALTDQ_DQS Parameter Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Chapter 4. Functional Description

Custom External Memory Interface Datapaths Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

ALTDLL Megafunction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

DLL block and DLL offset control block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

ALTDQ_DQS Megafunction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

DQS Input Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6

DQ Input Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

DQ Output/OE Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–10

DQS Output/OE Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

DQ/DQS OCT Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–14

Delay Chains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–15

Deskew Delay Chains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–16

ALTIOBUF Megafunction and Delay Chains Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–18

DQS_CONFIG / IO_CONFIG Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

Configuring Dynamic Delay Chains Using the IO_CONFIG Block . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

ALTDLL Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–31

ALTDQ_DQS Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–33

DQS Input Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–33

DQS Output Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–35

DQS OE Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–36

DQ/DQS OCT Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–37

DQ Input Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–38

DQ Output Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–40

DQ OE Path Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–42

DQSn I/O Path Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–43

DQS_CONFIG/IO_CONFIG Megafunction Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–45

Correct Settings for External Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 4

iv

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III Devices . . . . . . . . . . . . . . . . 4–49

Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–49

Understanding the Simulation Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–60

Appendix A. Clear Box Generator

Using Clear Box Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Clear Box Generator Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

Clear Box Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

Additional Information

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 5

1. About these Megafunctions

The ALTDLL and ALTDQ_DQS megafunctions provide a custom external memory

interface solution to access an FPGA's architecture and allow you to build your own

custom external memory interface physical layer (PHY) blocks.

®

Altera

when implementing a specialized or customized intellectual property (IP) for an

Altera-supported external memory interface that is not supported in Altera's IP or a

proprietary interface that is not supported by Altera.

The ALTDLL and ALTDQ_DQS custom external memory interface solution offers

more efficient logic synthesis and device implementation, and saves valuable design

time if you choose to code your own logic. The ALTDLL megafunction configures the

dedicated DQS phase-shift circuitry, and the ALTDQ_DQS megafunction implements

the read and write PHY required for the interface.

While the ALTDLL and ALTDQ_DQS custom external memory interface solution is

primarily for building custom memory interface PHY blocks, you can also use this

solution to interface with any external device, such as ASIC, ASSP or another FPGA,

through the double data rate (DDR) interface.

recommends that you use the ALTDLL and ALTDQ_DQS megafunctions

1 The ALTDLL and ALTDQ_DQS megafunctions are specifically for memory interfaces

that support memory burst lengths of two. For common memory interfaces that

support memory burst lengths of four, Altera recommends that you use the

ALTMEMPHY- or UniPHY-based memory controllers to take advantage of the

benefits of Altera's IP and timing closure methodologies.

f For more information about the ALTMEMPHY- or UniPHY-based memory controllers

that Altera offers, refer to the volume 3 of the External Memory Interface Handbook.

Device Support

The ALTDLL and ALTDQ_DQS megafunctions support the following Altera device

families:

■ Arria

■ HardCopy

■ HardCopy IV

■ Stratix

■ Stratix IV

®

II GX

®

III

®

III

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 6

1–2 Chapter 1: About these Megafunctions

ALTIOBUF (DQS/DQSN)

ALTIOBUF (BIDIR_DQ)

ALTIOBUF (INPUT_DQ)

ALTIOBUF (OUTPUT_DQ)

ALTDQ_DQS

x9

ALTDQ_DQS

x9

ALTDQ_DQS

x9

ALTDQ_DQS

x9

ALTDLL

ALTPLL

Features

Features

The ALTDLL and ALTDQ_DQS megafunctions offer the following features:

■ ALTDLL

■ A delay-locked loop (DLL) block to center-align the read strobe with read data.

■ Phase offset control blocks to fine-tune the delay time on the read strobe using

static or dynamic offset.

■ ALTDQ_DQS

■ Supports RLDRAM II memory interface.

■ DDR registers on the input and output paths to read or write to an external

DDR interface.

■ Half-rate registers to enable successful data transfers between the I/O registers

and the core logic.

■ Access to dynamic on-chip termination (OCT) controls to switch between

parallel termination during reads to series termination during writes.

■ Access to I/O delay chains to fine-tune delays on the data or strobe signals

statically or dynamically.

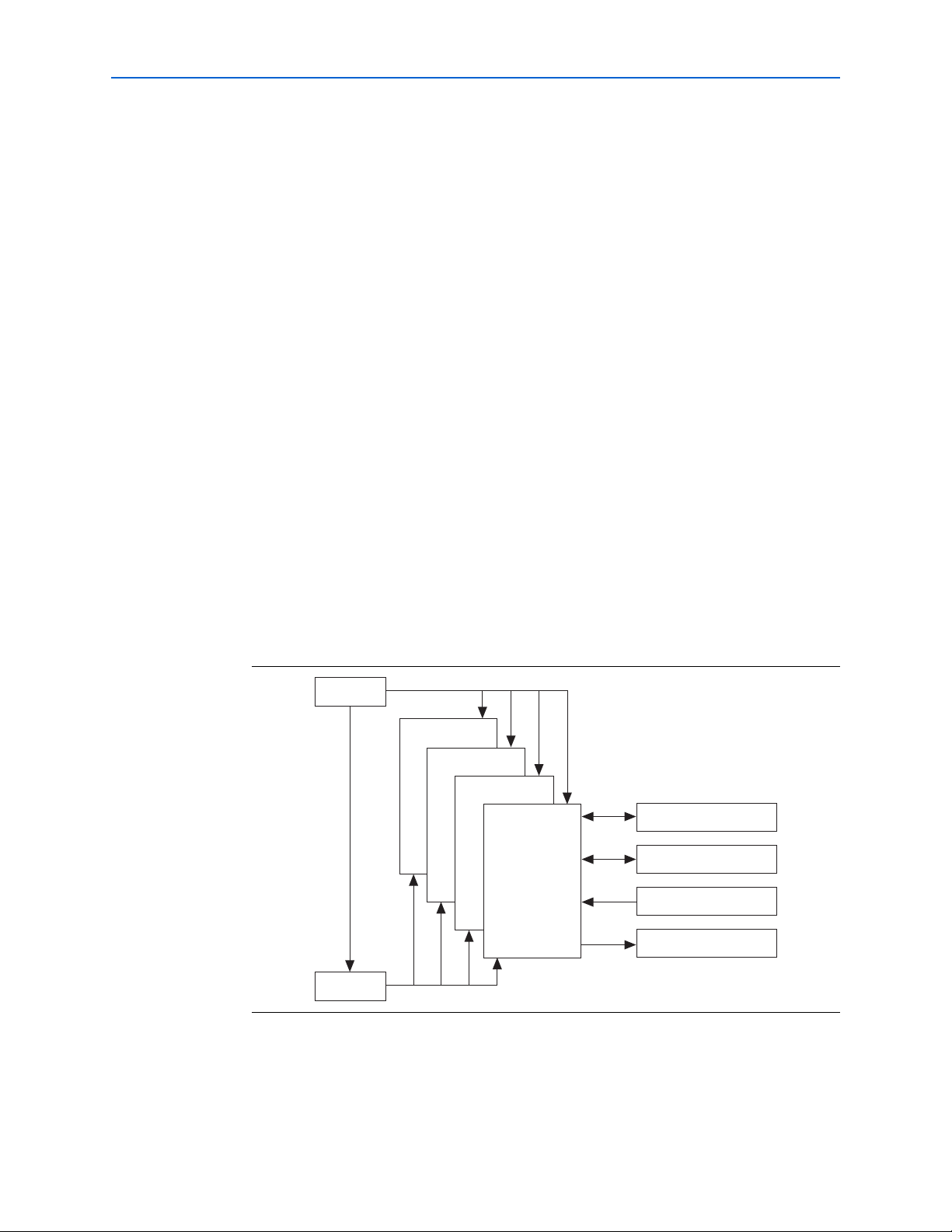

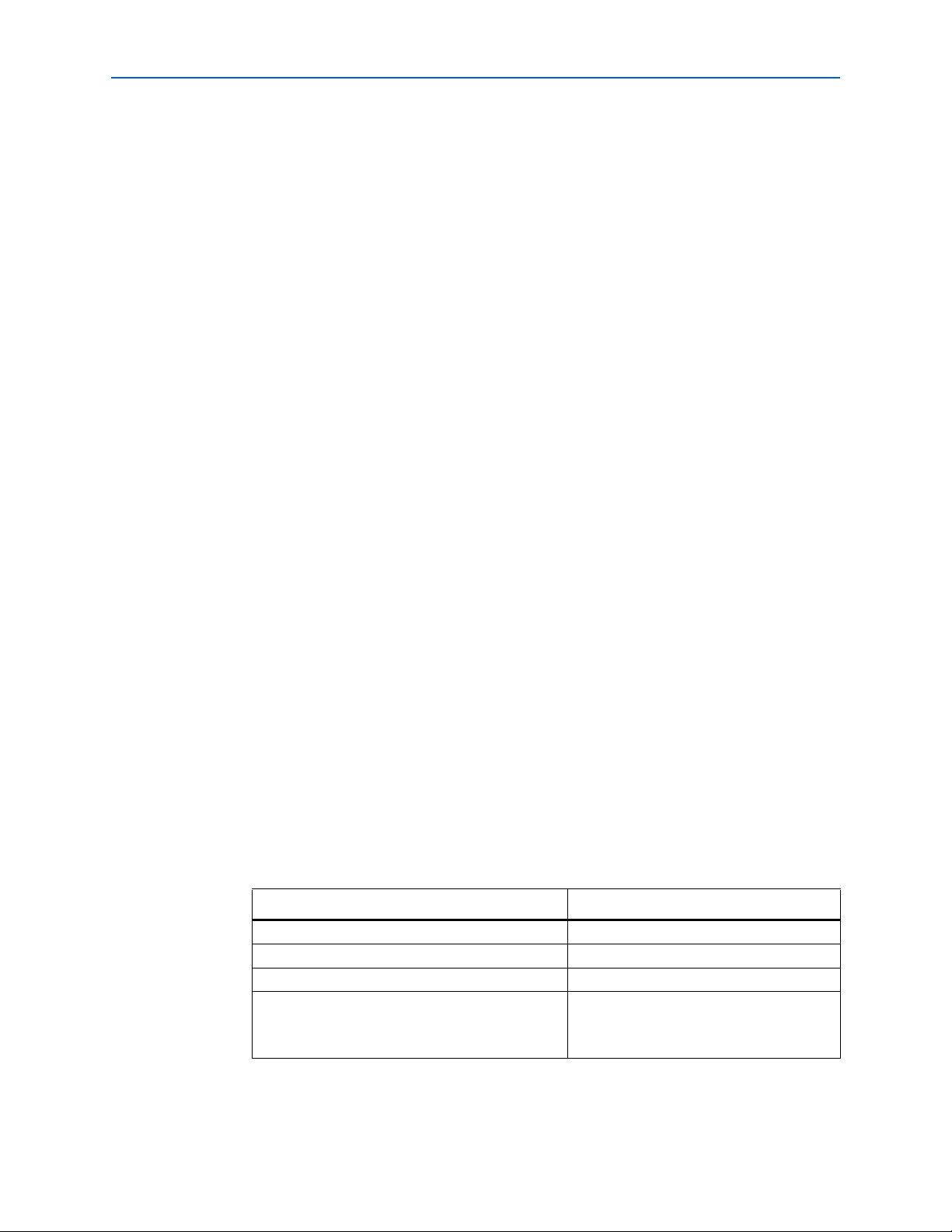

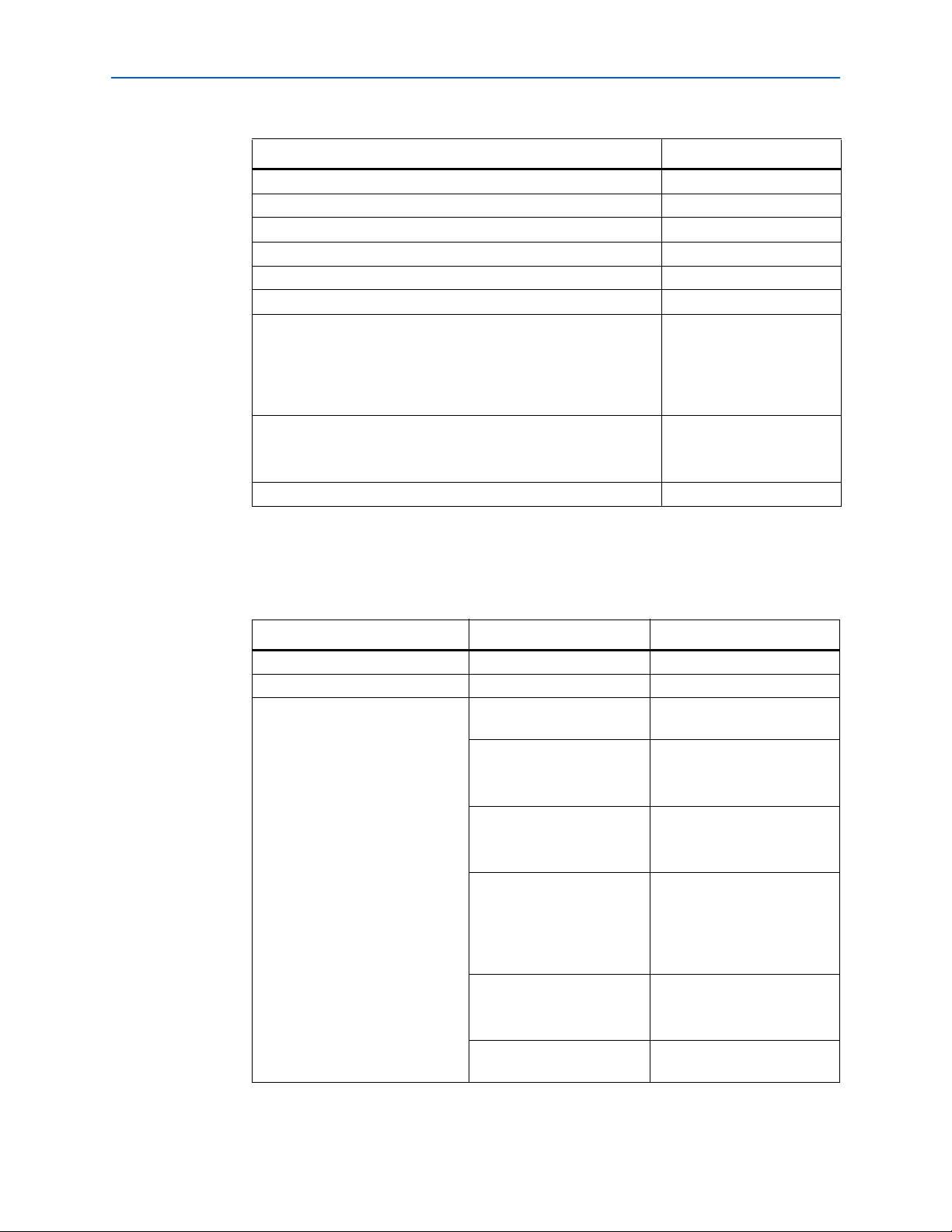

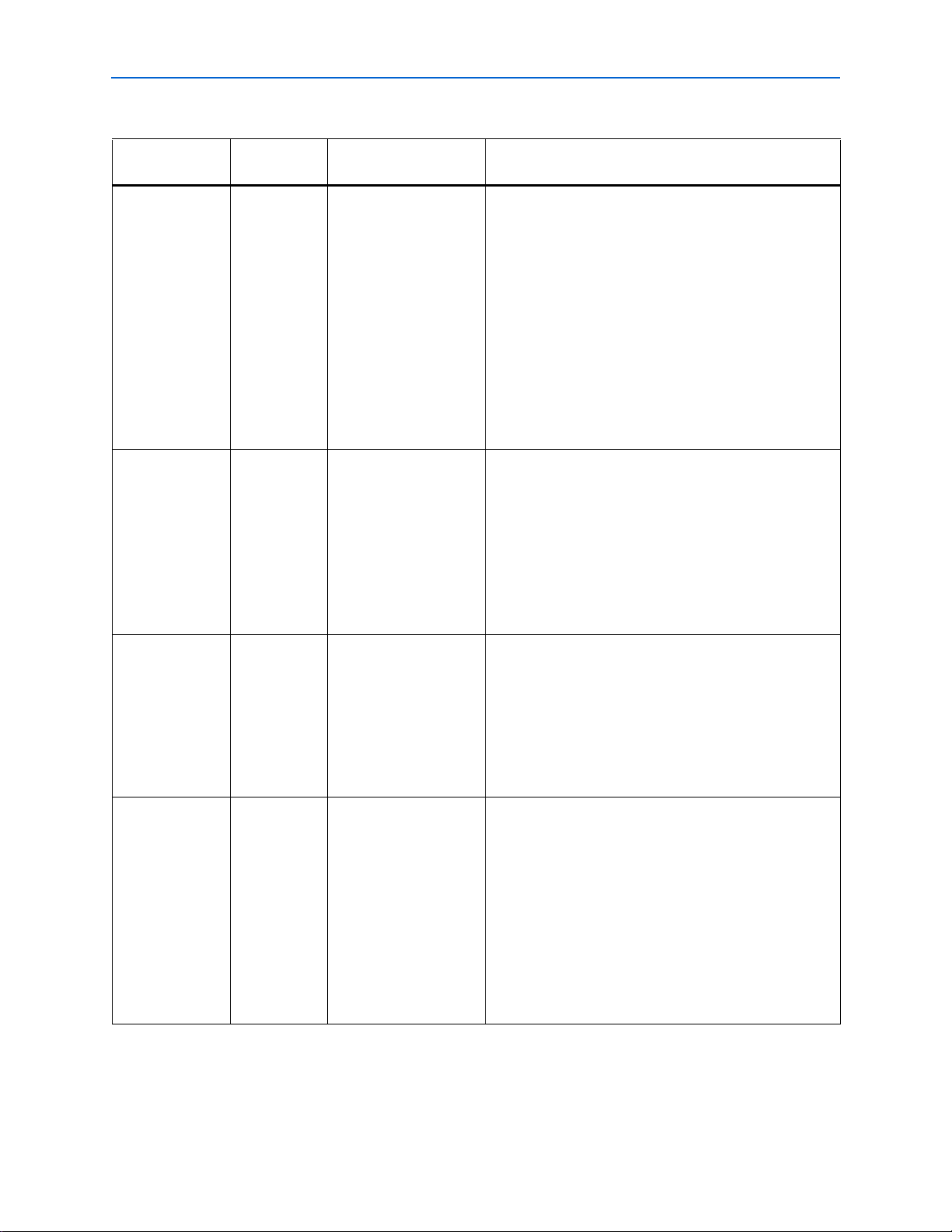

Figure 1–1 shows a high-level overview of how you can connect the ALTDQ_DQS

megafunction with other megafunctions such as ALTPLL, ALTDLL, and ALTIOBUF,

to create a full custom external memory interface. Figure 1–1 shows a 36-bit interface

created with ALTDQ_DQS instantiations, where each instantiation is configured in

the ×9 mode.

Figure 1–1. System-Level View

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 7

Design Flow

Build the Datapath

Simulate the Design

Create Timing Constraints

Compile the Design and Verify Timing

Adjust Constraints

2. Getting Started

This chapter describes the FPGA design flow to implement a custom memory

interface datapath using the ALTDLL and ALTDQ_DQS megafunctions and Altera’s

FPGA hardware features.

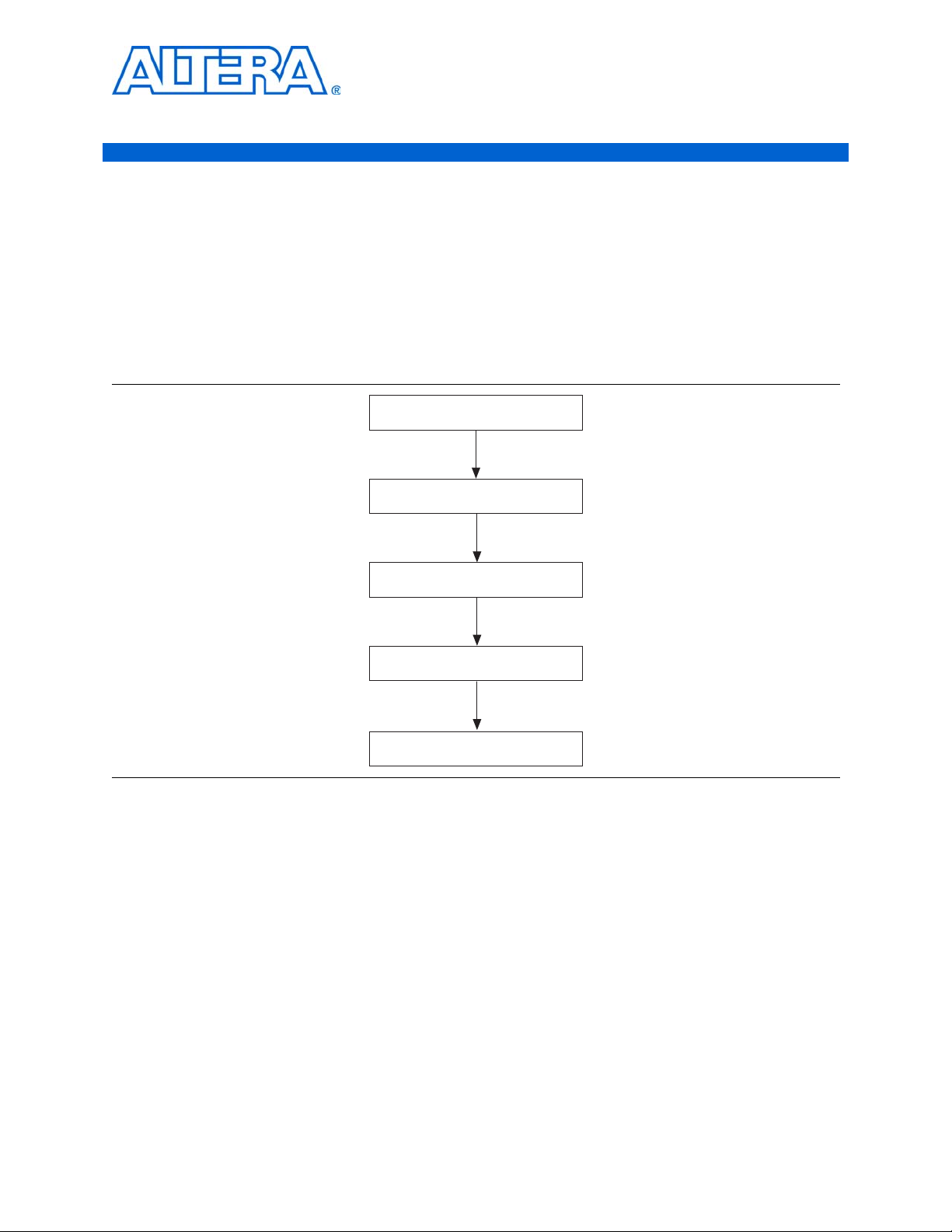

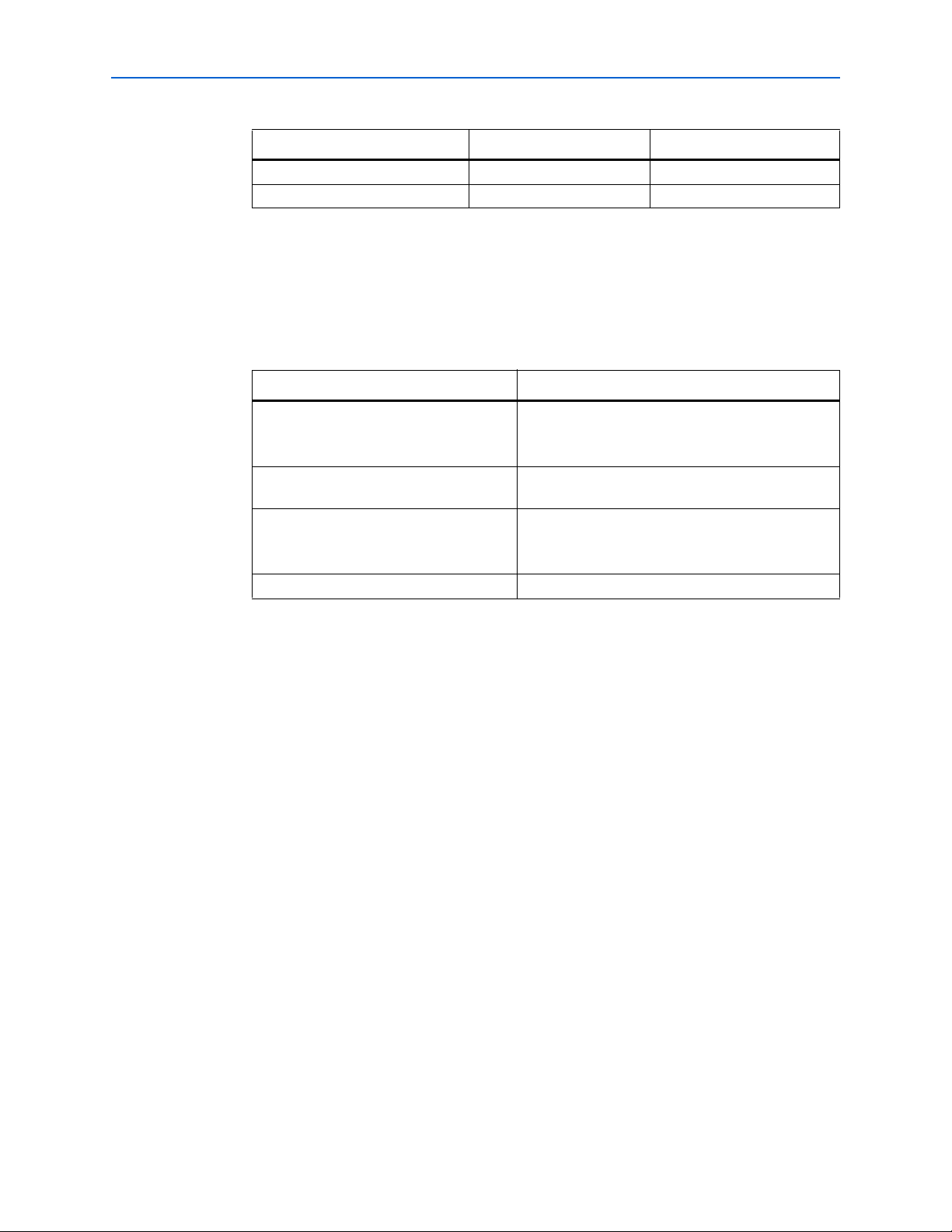

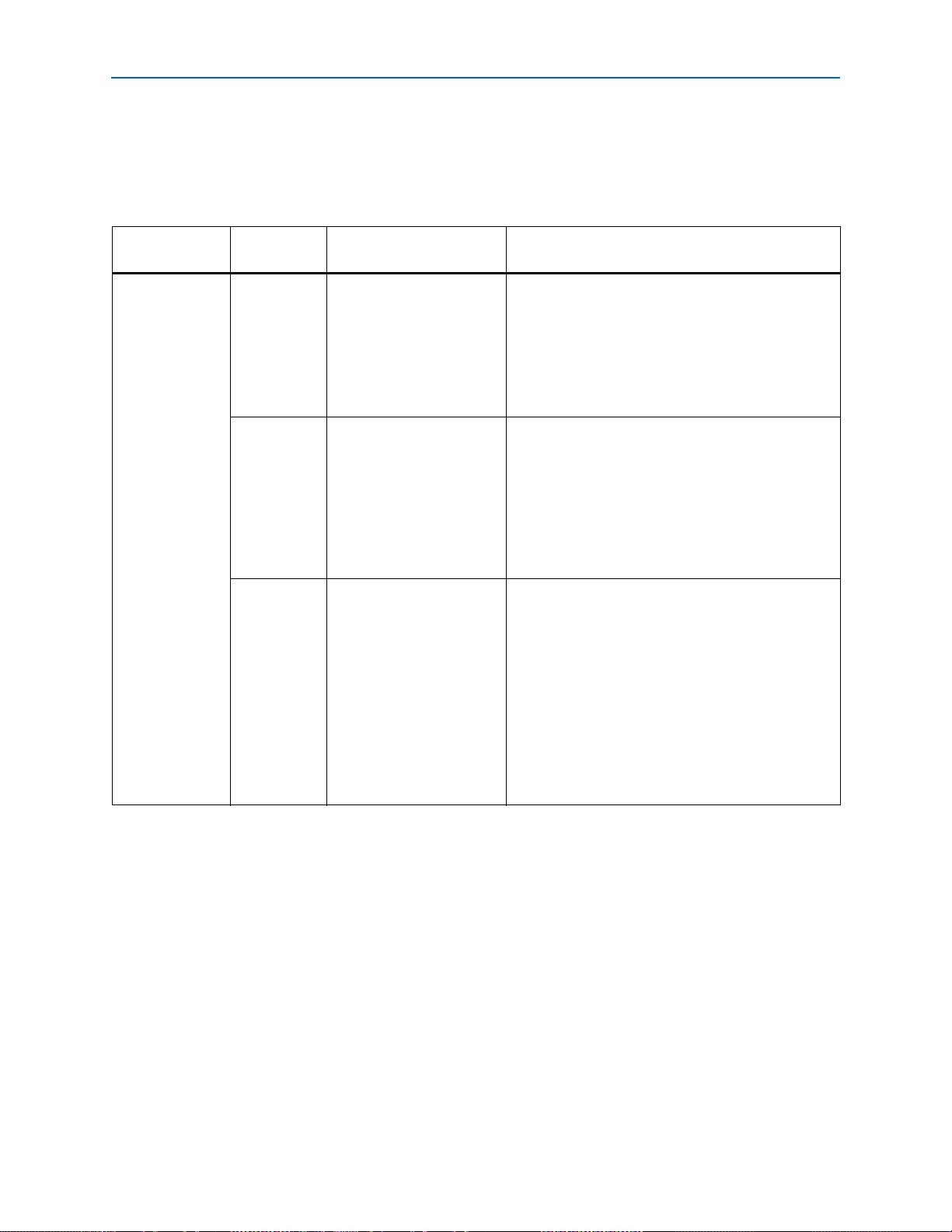

Figure 2–1 shows the design flow for creating a custom memory datapath system

with the ALTDLL and ALTDQ_DQS megafunctions and the Quartus

Figure 2–1. Design Flowchart

®

II software.

Build the Datapath

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

After you identify the requirements for your custom external memory interface, the

first stage is to build a datapath to interface with the memory blocks.

To build the datapath, you must perform the following steps:

1. Create a project in the Quartus II software that targets the preferred Altera device.

2. Instantiate the ALTPLL megafunction to provide the required clocking scheme for

the custom PHY.

f For more information about instantiating megafunctions and the clocking

scheme, refer to Instantiate the ALTPLL Megafunction section in volume 5 of

the External Memory Interface Handbook. For more information about using

PLLs, refer to the ALTPLL Megafunction User Guide.

3. Instantiate the ALTDLL megafunction to implement the DLL.

Page 8

Chapter 2: Getting Started 2–2

Design Flow

4. Instantiate the ALTDQ_DQS megafunction to implement the read and write PHY

required for the interface.

5. Integrate the custom PHY with user logic, and a custom or third party memory

controller if needed.

6. Instantiate the ALTIOBUF megafunction to use the I/O buffers for pin

connections. This megafunction enables dynamic OCT capabilities for the

respective interface pins.

f For more information about the pin connections, refer to “ALTIOBUF

Megafunction and Delay Chains Integration” on page 4–18. For more

information about the ALTIOBUF megafunction, refer to I/O Buffer

(ALTIOBUF) Megafunction User Guide.

7. Connect all the instances of ALTPLL, ALTDLL, ALTDQ_DQS, ALTIOBUF, and

other custom memory controllers in the Quartus II software.

The following sections discuss other megafunctions or customized controller logic

that are used in some cases.

ALTOCT Megafunction

If you use the OCT capabilities in the targeted devices, you eliminate the need for

external series or parallel termination resistors, and you simplify the design of a PCB.

If the I/O in your design uses calibrated series, parallel, or dynamic termination, your

design requires a calibration block. This block requires a pair of R

located in a bank that shares the same V

voltage as your memory interface. This

CCIO

calibration block is not required to be in the same bank or side of the device as the I/O

elements it is serving. To use these capabilities in the FPGA, you must turn on the Use

dynamic OCT path option when parameterizing the ALTDQ_DQS megafunction,

and instantiate the ALTOCT megafunction.

and RDN pins

UP

f For more information about the OCT capabilities in the DQ/DQS path, refer to

“DQ/DQS OCT Path” on page 4–14.

Customized Controller Logic

In some cases, you require a customized controller logic to control the PHY created

with the ALTDLL and ALTDQ_DQS instances. You must create a controller logic for

the following instances:

■ Controller logic for data, data_valid, and strobe pins for the custom external

memory interface.

■ If you use calibrated termination, controller logic for all pins in the ALTOCT

instances associated with the custom external memory interface.

f For more information about calibrated termination, refer to Dynamic

Calibrated On-Chip Termination (ALTOCT) Megafunction User Guide.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 9

2–3 Chapter 2: Getting Started

Design Flow

Simulate the Design

After instantiating the megafunctions, the Quartus II software generates design

source files and Verilog or VHDL simulation model files. Simulate these files in

Modelsim-AE, Modelsim SE, or other third-party functional simulator tools.

f For information about functional and gate-level timing simulations, refer to

Simulating Altera Designs chapter in volume 3 of the Quartus II Handbook.

Create Timing Constraints

The ALTDLL and ALTDQ_DQS megafunctions do not provide automatic timing

scripts for custom external memory interfaces. You must create your own timing

constraints for the following paths and clocks:

■ Timing paths from FPGA I/O to external device.

■ Timing paths from I/O registers to core logic.

■ PLL and other clock constraints.

After creating your constraints, perform the timing analysis using the TimeQuest

timing analyzer in the Quartus II software.

f Because the timing analysis for custom external memory interfaces are the same as the

timing analysis for source-synchronous interfaces, refer to the Timing Analysis section

in volume 3 of the Quartus II Handbook and AN 433: Constraining and Analyzing

Source-Synchronous Interfaces.

The ALTDLL and ALTDQ_DQS custom PHY solution supports timing analysis using

the TimeQuest timing analyzer with Synopsys Design Constraints (SDC)

assignments. You can derive the timing constraints from the external device data

sheet and tolerances from the board layout.

f For more information about timing constraints, refer to “Appendix D: Interface

Timing Analysis” section in AN 328: Interfacing DDR2 SDRAM with Stratix II, Stratix II

GX, and Arria GX Devices.

For more information about creating timing constraints in SDC format for the

TimeQuest timing analyzer, refer to the The Quartus II TimeQuest Timing Analyzer

chapter of the Quartus II Handbook. Depending on which simulation tool you are

using, refer to the appropriate chapter in the Simulation section in volume 3 of the

Quartus II Handbook.

Compile the Design and Verify Timing

After constraining your design, compile your design in the Quartus II software to

generate timing reports to verify whether timing has been met.

After compiling your design in the Quartus II software, run the verifying timing

script to produce the timing report for different paths, such as write data, read data,

address and command, and core (entire interface) timing paths in your design.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 10

Chapter 2: Getting Started 2–4

Design Example: Implementing Read Paths Using Stratix III Devices

The timing analyzer reports margins on the following paths:

■ Address and command setup and hold margin

■ Half-rate address and command setup and hold margin

■ Core setup and hold margin

■ Core reset and removal setup and hold margin

■ Write setup and hold margin

■ Read capture setup and hold margin

f For more information about timing analysis and reporting using the ALTDLL and

ALTDQ_DQS external memory solution, refer to the Analyzing Timing of Memory IP

chapter in volume 2 of the External Memory Interface Handbook.

Adjust Constraints

The timing report shows the worst case setup and hold margin for the different paths

in your design. If the setup and hold margin do not meet timing requirements, adjust

the phase setting of the clocks that latch the data.

For example, the address and command outputs are clocked by an address and

command clock that may be different than the system clock, which is 0°. The system

clock clocks the clock outputs going to the memory. If the report timing script

indicates that using the default phase setting for the address and command clock

results in more hold time than setup time, adjust the address and command clock to

be less negative than the default phase setting to ensure that there is less hold margin.

Similarly, adjust the address and command clock to be more negative than the default

phase setting if there is more setup margin.

Design Example: Implementing Read Paths Using Stratix III Devices

This section provides a walkthrough of a simple design example. The design example

demonstrates a Stratix III device reading from an external DDR2 SDRAM. The DDR2

external memory interface is implemented using the ALTDLL and ALTDQ_DQS

megafunctions. This design requires 1 DQS and 8 DQ input pins. The DQS frequency

for the design is 150 MHz and the data rate is 300 Mbps.

1 For a more complex design example, refer to “Design Example: Implementing

Half-Rate DDR2 Interface in Stratix III Devices” on page 4–49.

f The design examples are available next to the ALTDLL and ALTDQ_DQS

Megafunctions User Guide on the Documentation: User Guides page of the Altera

website.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 11

2–5 Chapter 2: Getting Started

Design Example: Implementing Read Paths Using Stratix III Devices

Generate the Megafunctions

Create a Quartus II project and generate the following megafunctions:

■ ALTPLL megafunction

■ ALTDLL megafunction

■ ALTDQ_DQS megafunction

■ ALTIOBUF megafunction

Create a Quartus II Project

Create a project in the Quartus II software that targets the EP3SL150F1152-C2 device

for the DDR2 SDRAM by performing the following steps:

1. Open the altdll_altdq_dqs_DesignExample_ex1.zip file and extract the

altdll_altdq_dqs_design_ex1.qar file.

2. In the Quartus II software, restore the altdll_altdq_dqs_design_ex1.qar file into

your working directory.

3. Open the altdll_altdq_dqs_design_ex1.bdf file.

Generate the ALTPLL Megafunction

Before generating the ALTDLL and ALTDQ_DQS megafunctions, you must generate

the ALTPLL megafunction first by performing the following steps:

1. Double-click anywhere on the Block Editor window. The Symbol window appears.

2. Click MegaWizard Plug-In Manager. Page 1 of the MegaWizard

Manager appears.

3. Select Create a new custom megafunction variation.

4. Click Next. Page 2a of the MegaWizard Plug-In Manager appears.

5. Select Create a new custom megafunction variation.

6. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select ALTPLL,

and Ver ilo g HD L, and type the file name as PLL_50MHz.v.

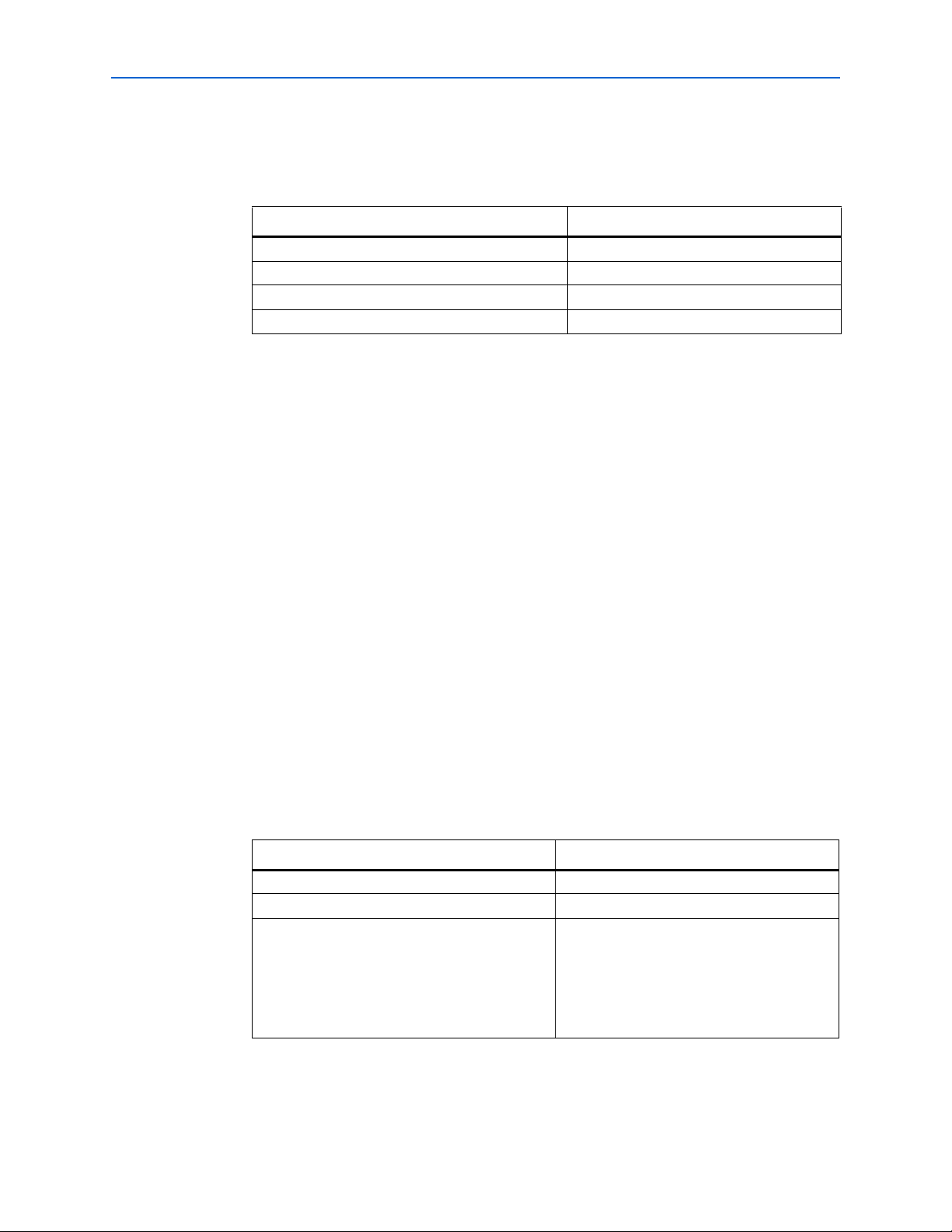

7. On the Parameter Settings tab, on the General/Modes page, specify the

parameters as shown in Tab le 2 –1 . These parameters configure the general

settings for the ALTPLL instance.

Table 2–1. ALTPLL Parameter Settings

Settings Value

Currently selected device family Stratix III

Match project/default Turned on.

What is the frequency of the inclock0 input? 50 MHz

How will the PLL outputs be generated? With no compensation

This option is selected because the PLL is

used to clock the ALTDLL instance only.

™

Plug-In

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 12

Chapter 2: Getting Started 2–6

Design Example: Implementing Read Paths Using Stratix III Devices

8. On the Output Clocks tab, on the clk c0 page, specify the parameters as shown in

Tab le 2 –2 . You don’t have to parameterize the other pages on the Output Clocks

tab because you only use one clock for this design.

Table 2–2. ALTPLL Output Clocks/clk c0 Settings

Settings Value

Use this clock Turned on

Enter output clock frequency 150 Mhz

Clock phase shift 0 deg

Clock duty cycle (%) 50

9. Click Finish.

10. Click Finish. The ALTPLL instance is generated.

11. Click OK to close the Symbol window.

12. Place the instance on the altdll_altdq_dqs_design_ex1.bdf Block Editor.

Generate the ALTDLL Megafunction

To generate the ALTDLL megafunction, perform the following steps:

1. Double-click anywhere on the Block Editor window. The Symbol window appears.

2. Click MegaWizard Plug-In Manager. Page 1 of the MegaWizard Plug-In Manager

appears.

3. Select Create a new custom megafunction variation.

4. Click Next. Page 2a of the MegaWizard Plug-In Manager appears.

5. Select Create a new custom megafunction variation.

6. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select ALTDLL,

and Ver ilo g HD L, and type the file name as dll_150MHz.v.

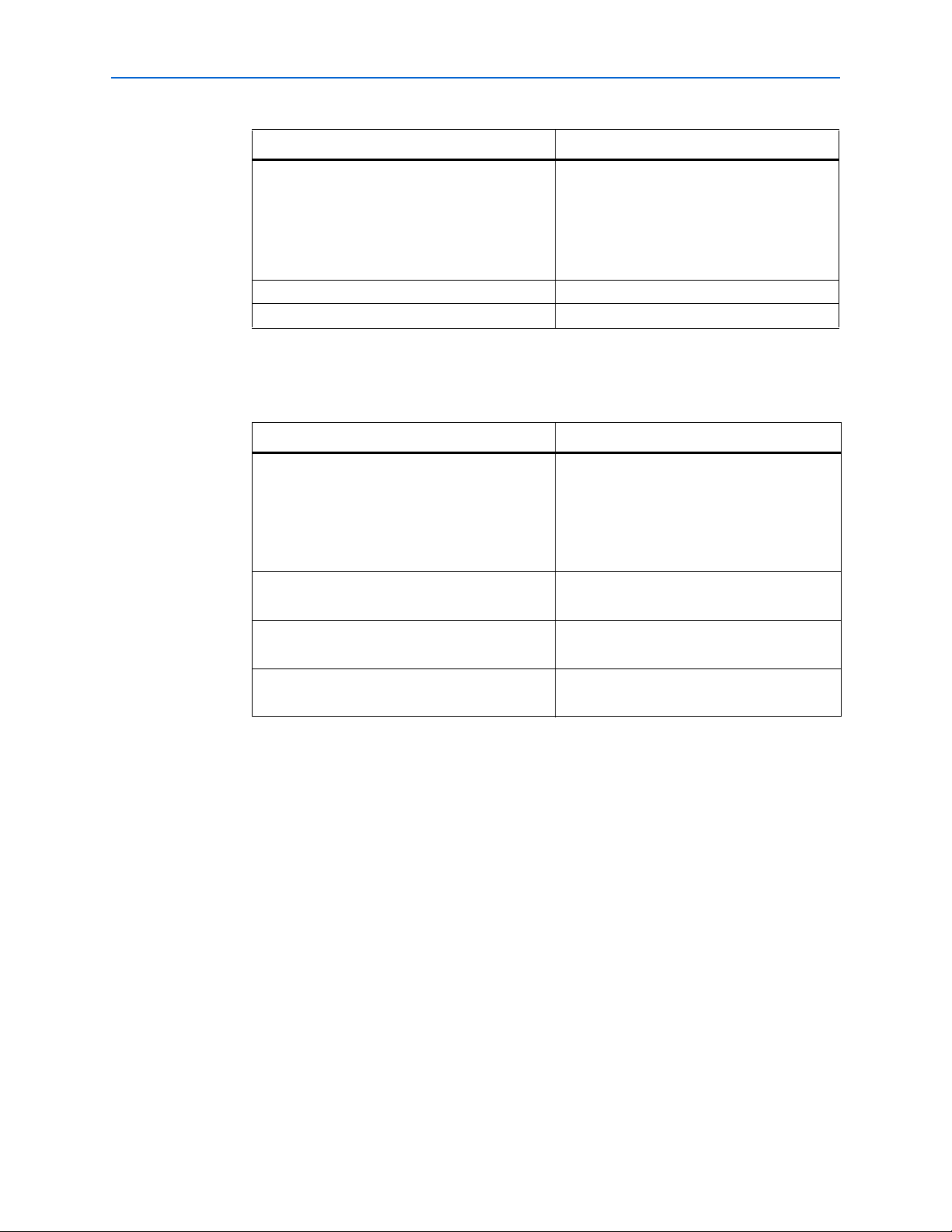

7. On the Parameter Settings tab, on the General page, specify the parameters as

shown in Tabl e 2– 3. These parameters configure the general settings for the

ALTDLL instance.

Table 2–3. ALTDLL GeneraL Settings

Settings Value

Currently selected device family Stratix III

Match project/default Turned on.

Number of Delay Chains 12

Refer to Stratix III Device Datasheet: DC and

Switching Characteristics of Stratix III Devices

chapter in the Stratix III Device Handbook, and

pick a DLL mode that supports 150 MHz and

find the DLL setting.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 13

2–7 Chapter 2: Getting Started

Table 2–3. ALTDLL GeneraL Settings

Settings Value

DQS Delay Buffer Mode Low

Input Clock Frequency 150 MHz

Turn on jitter reduction Turned off.

Design Example: Implementing Read Paths Using Stratix III Devices

Refer to Stratix III Device Datasheet: DC and

Switching Characteristics of Stratix III Devices

chapter in the Stratix III Device Handbook, and

pick a DLL mode that supports 150 MHz and

find the DLL setting.

8. On the DLL Offset Controls/Optional Ports page, specify the parameters as

shown in Tabl e 2– 4.

Table 2–4. ALTDLL Parameter Settings/DLL Offset Controls/Optional Ports Settings

Settings Value

DLL Phase Offset Control A

Instantiate dll_offset_ctrl block

DLL Phase Offset Control B

Instantiate dll_offset_ctrl block

Optional Ports

Create a dll_aload port

Optional Ports

Create a dll_dqsupdate port

Turned off.

The design is intended to run slow, so you do

not need to select this parameter. However, if

the read timing is unbalanced, you can

fine-tune the DQS phase shift using this

parameter.

Turned off.

Turned off.

Turned off.

9. Click Finish.

10. Click Finish. The ALTDLL instance is generated.

11. Click OK to close the Symbol window.

12. Place the instance on the Block Editor.

Generate the ALTDQ_DQS Megafunction

To generate the ALTDQ_DQS megafunction, perform the following steps:

1. Double-click anywhere on the Block Editor window. The Symbol window appears.

2. Click MegaWizard Plug-In Manager. Page 1 of the MegaWizard Plug-In Manager

appears.

3. Select Create a new custom megafunction variation.

4. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select

ALTDQ_DQS, and Verilog HDL, and type the file name as dq_dqs_input_path.v.

5. On the Parameter Settings page, specify the parameters as shown in Ta bl e 2– 5.

These parameters configure the general settings for the ALTDQ_DQS instance.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 14

Chapter 2: Getting Started 2–8

Design Example: Implementing Read Paths Using Stratix III Devices

.

Table 2–5. Parameter Settings

Parameter Value

RLDRAMII Mode NONE

Number of bidirectional DQ 0

Number of input DQ 8

Number of output DQ 0

Number of stages in dqs_delay_chain 3

DQS input frequency 150 MHz

Use half-rate components Turned off.

The design uses full-rate

memory components, so

you do not select this

option.

Use Dynamic OCT Turned off.

Dynamic OCT is not used for

input paths.

Add memory interface specific fitter grouping assignments Turned on.

6. On the Advanced Options tab, on the DQS IN page, specify the parameters as

shown in Tabl e 2– 6. These parameters configure the DQS input path of the

ALTDQ_DQS instance.

Table 2–6. Advance Options (DQS IN)

Parameter Sub-options Value

Enable DQS Input Path — Turned on.

Enable dqs_delay_chain —Selected.

Advanced delay chain options Select dynamically using

Turned off.

configuration registers

DQS delay chain

‘delayctrlin’ port source

DLL

The DQS delay-chain settings

is based on the DLL.

DQS Delay Buffer Mode Low

Use the same mode selected

in the DLL settings.

DQS Phase Shift 9000..

Specify a 90° DQS phase shift.

The phase-shift value must

inter-relate with the selected

dqs_delay_chain stage.

Enable DQS offset control Turned off.

Disable DQS delay fine-tuning

using offset feature.

Enable DQS delay chain

Turned off.

latches

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 15

2–9 Chapter 2: Getting Started

Table 2–6. Advance Options (DQS IN)

Parameter Sub-options Value

Enable DQS busout delay chain — Turned on.

Enable DQS enable block — Turned on.

Design Example: Implementing Read Paths Using Stratix III Devices

7. On the DQS OUT/OE page, turn off the Enable DQS output path option. When

you deselect the Enable DQS output path option, the other options on this page

are disabled.

8. On the DQ IN page, specify the parameters as shown in Tabl e 2– 7. These

parameters configure the DQ input path of the ALTDQ_DQS instance.

Table 2–7. Advance Options (DQ IN)

Options Value

DQ input register mode DDIO

Select DDIO to enable double data rate capture for

DQ.

DQ input register clock source dqs_bus_out port and turn off Connect DDIO clkn to

DQS_BUS from complementary DQSn

Use DQ input phase alignment Turned off.

The feature is for half-rate components; the design

uses full-rate memory components.

Use DQ input delay chain Turned on.

9. On the DQ OUT/OE page, all the options are automatically disabled because the

design is not using output DQ. The parameters on this page configure the DQ

output and OE paths of the ALTDQ_DQS instance.

10. On the Half-rate page, for the IO Clock Divider Invert Phase parameter, turn on

Never because the design requires full-rate components. The other options are

automatically disabled. The parameters on this page configure the half-rate

settings of the ALTDQ_DQS instance.

11. On the OCT Path page, all the options are automatically disabled because the

design is not using input and output DQS or bidirectional DQ. The parameters on

this page configure the OCT path of the ALTDQ_DQS instance.

12. On the DQSn I/O page, turn off the Use DQSn I/O option because the design is

not using DQSn. When you turn off the Use DQSn I/O option, the other options

on this page are disabled.

13. In the Reset/Config Ports tab, tun off all the parameters.

14. Click Finish.

15. Click Finish. The ALTDQ_DQS instance is generated.

16. Click OK to close the Symbol window.

17. Place the instance on the Block Editor.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 16

Chapter 2: Getting Started 2–10

Design Example: Implementing Read Paths Using Stratix III Devices

Generate the ALTIOBUF Megafunction

You must generate the ALTIOBUF megafunction to set the following I/O buffer

settings:

■ 1 input buffer for input DQS pin

■ 8 input buffers for input DQ pins

To generate the ALTIOBUF megafunction, perform the following steps:

1. Double-click anywhere on the Block Editor window. The Symbol window appears.

2. Click MegaWizard Plug-In Manager. Page 1 of the MegaWizard Plug-In Manager

appears.

3. Select Create a new custom megafunction variation.

4. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select

ALTIOBUF, and Ver ilo g HD L, and type the file name as ibuf_input_dqs.v (for

DQS pin) or ibuf_input_dq.v (for DQ pins).

5. On the Parameter Settings page, specify the parameters as shown in Ta bl e 2– 8.

These parameters configure the general settings for the ALTIOBUF instance.

Table 2–8. ALTIOBUF General Settings

Value

Settings

1 input buffer for the

input DQS pins

8 input buffer for the

input DQ pins

Currently selected device family Stratix III Stratix III

How do you want to configure this module? As an input buffer As an input buffer

What is the number of buffers to be

18

instantiated?

Use bus hold circuitry Turned off. Turned off.

Use differential mode Turned off. Turned on.

Use open drain output Turned off. Turned off.

Use output enable port Turned off. Turned off.

Use dynamic termination control Turned off. Turned off.

Use series and parallel termination control Turned off. Turned off.

6. On the Dynamic Delay Chains page, specify the parameters as shown in

Tab le 2 –9 .

Table 2–9. ALTIOBUF Dynamic Delay Chain Settings

Value

Settings

1 input buffer for the

input DQS pins

8 input buffer for the

input DQ pins

Enable input buffer dynamic delay chain Turned off. Turned off.

Enable output buffer dynamic delay chain 1 Turned off. Turned off.

Enable output buffer dynamic delay chain 2 Turned off. Turned off.

Create a ‘clkena’ port Turned off Turned off.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 17

Chapter 2: Getting Started 2–11

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

7. Click Finish.

Design Example: Implementing Read Paths Using Stratix III Devices

8. Click Finish. The ALTIOBUF instance is generated.

9. Click OK to close the Symbol window.

10. Place the instance on the Block Editor.

f For more information about connecting all the instances, refer to “Integrate the I/O Buffer Modules with the

ALTDQ_DQS modules” on page 4–55.

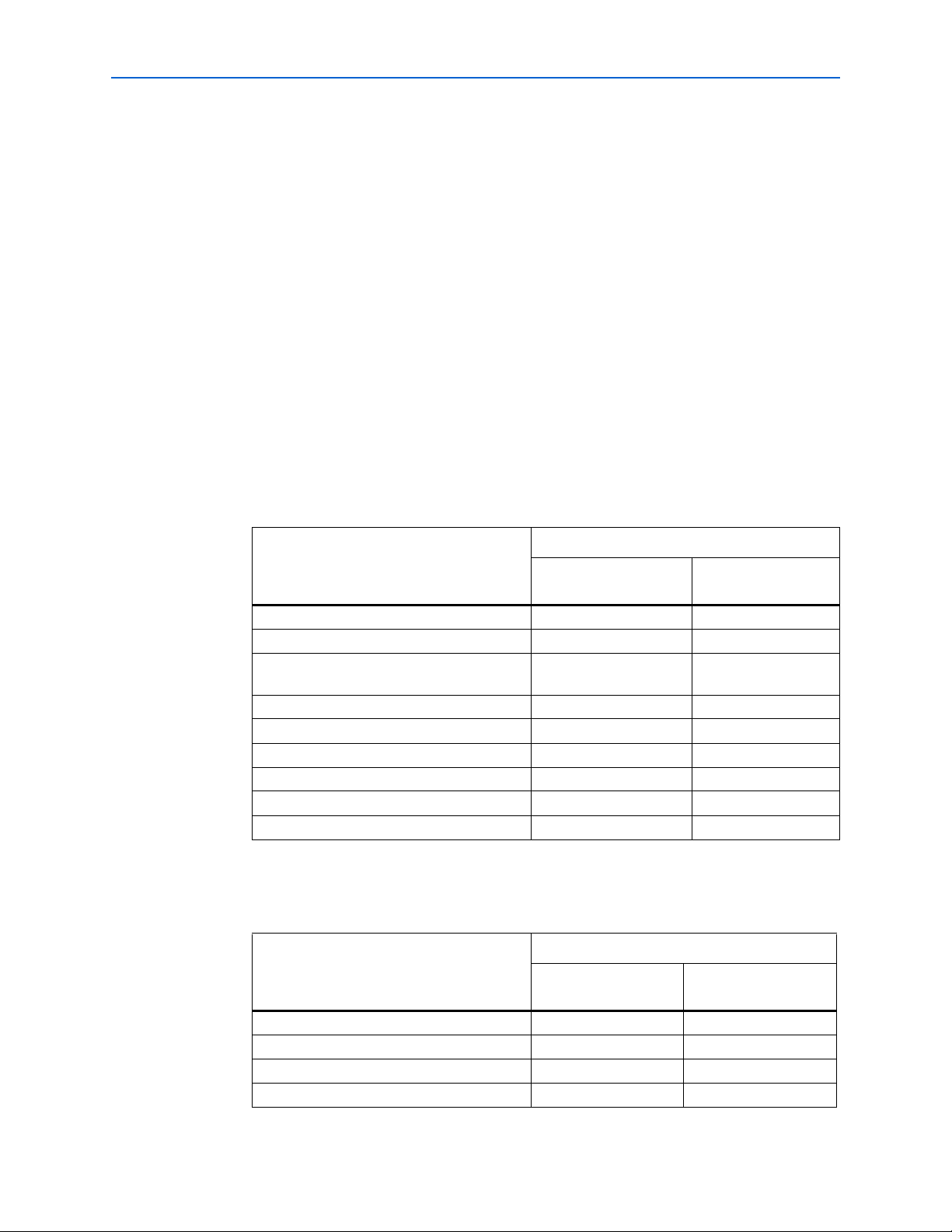

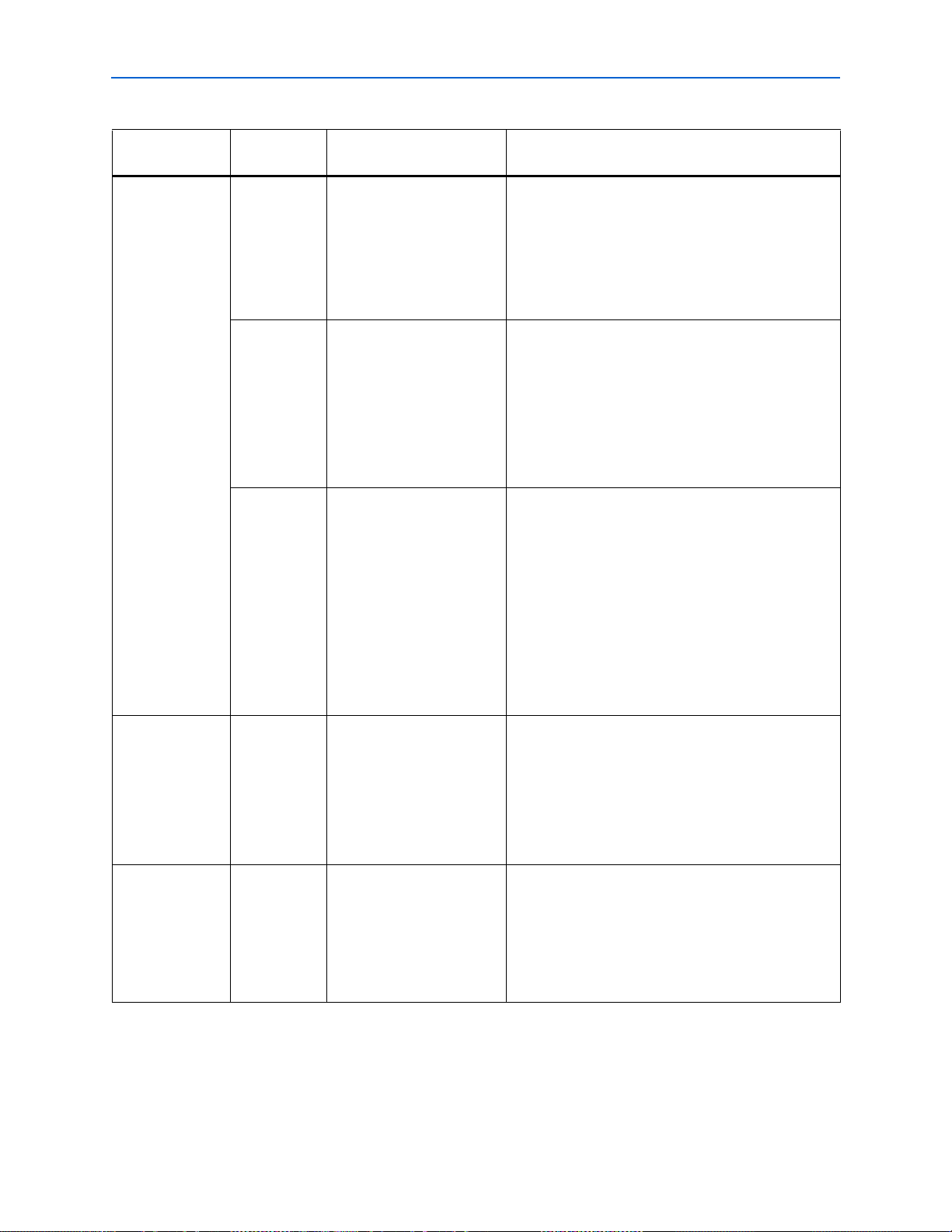

11. On the Block Editor, connect all the instances as shown in Figure 2–2 on page 2–11.

Figure 2–2. Block Diagram of the Design Example

Page 18

2–12 Chapter 2: Getting Started

Design Example: Implementing Read Paths Using Stratix III Devices

Compile and Simulate the Design

On the Processing menu, click Start Compilation to compile the design. After the

design is compiled, you can view the implemention in the RTL Viewer. You can also

view the resource usage in the Compilation Report.

After you compile your design, simulate the design in the ModelSim-Altera software

to generate a waveform display of the device behavior. Set up and simulate the design

in the ModelSim-Altera software by performing the following steps:

1. Unzip the altdll_altdq_dqs_ex1_msim.zip file to your preferred working

directory on your PC.

2. Start the ModelSim-Altera software.

3. On the File menu, click Change Directory.

4. Select the folder in which you unzipped the files in the

altdll_altdq_dqs_ex1_msim.zip folder.

5. Click OK.

6. On the Tools menu, point to Tc l and click Execute Macro.

7. Select the altdll_altdq_dqs_ex1_msim.do file and click Open. This is a script file

for the ModelSim-Altera software to automate all the necessary settings for the

simulation.

8. Verify the results with the simulation waveform.

1 You can rearrange, remove and add signals, and change the radix by

modifying the script in the altdll_altdq_dqs_ex1_msim.do file.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 19

The Quartus II software provides the MegaWizard Plug-In Manager that helps you

quickly customize your megafunction variation. The parameter editor provides a list

of megafunctions and available options for each variation.

Altera recommends that you use the parameter editor to instantiate the ALTDLL and

ALTDQ_DQS megafunctions. However, for advanced users, if you want to bypass the

MegaWizard Plug-In Manager and use the megafunctions as directly parameterized

instantiations in your design, you can use the clear box generator. For more

information about the clear box generator, refer to Appendix A, Clear Box Generator.

1 Some advanced parameters can only be modified through the clear box parameters.

ALTDLL Parameter Editor

This section provides information about the ALTDLL MegaWizard parameters.

3. Parameter Settings

1 For advanced users who may use the clearbox generator, the clearbox parameter

names are provided for the corresponding MegaWizard parameters.

The ALTDLL Parameter Settings page in the ALTDLL parameter editor allows you to

configure the parameters in the following pages:

■ General

■ DLL Offset Controls/Optional Ports

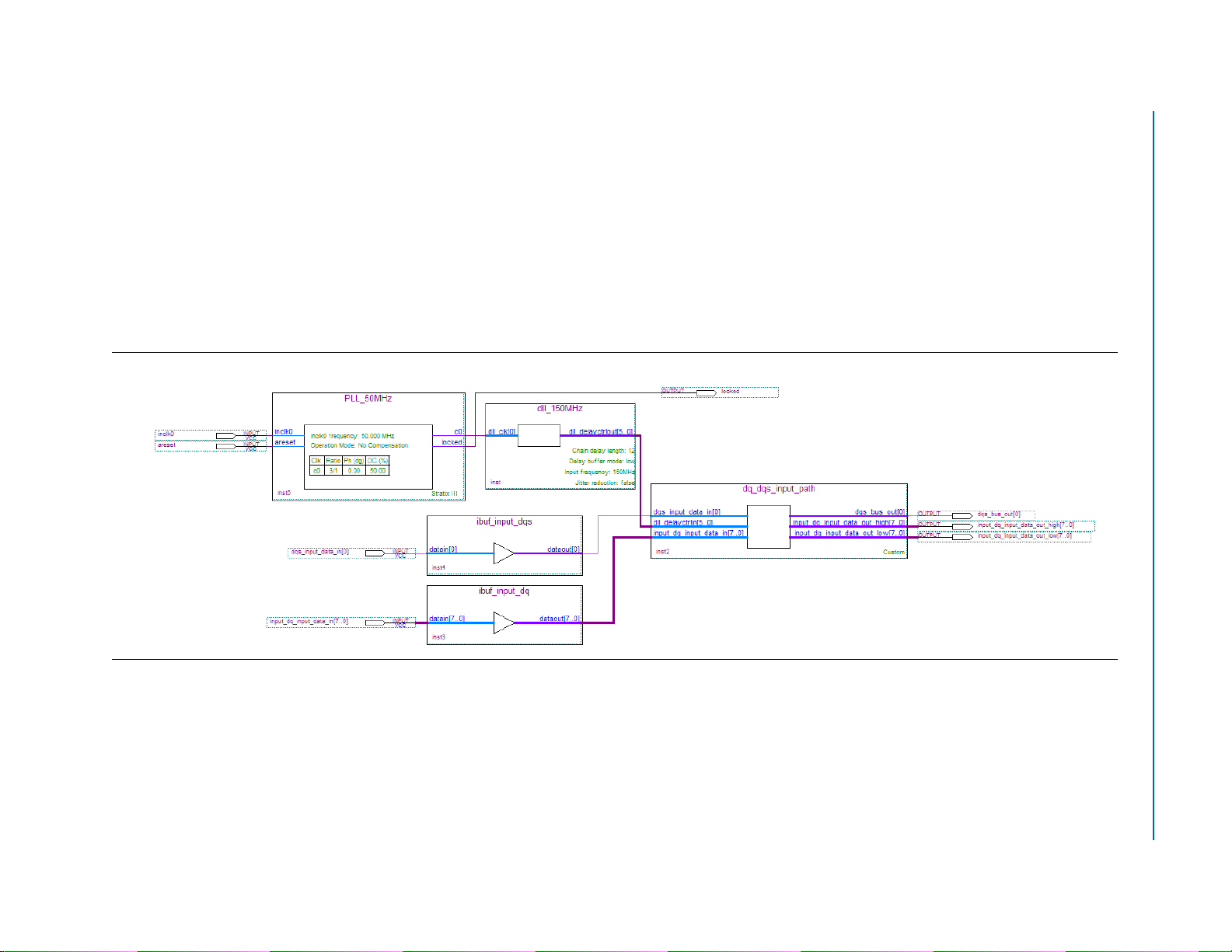

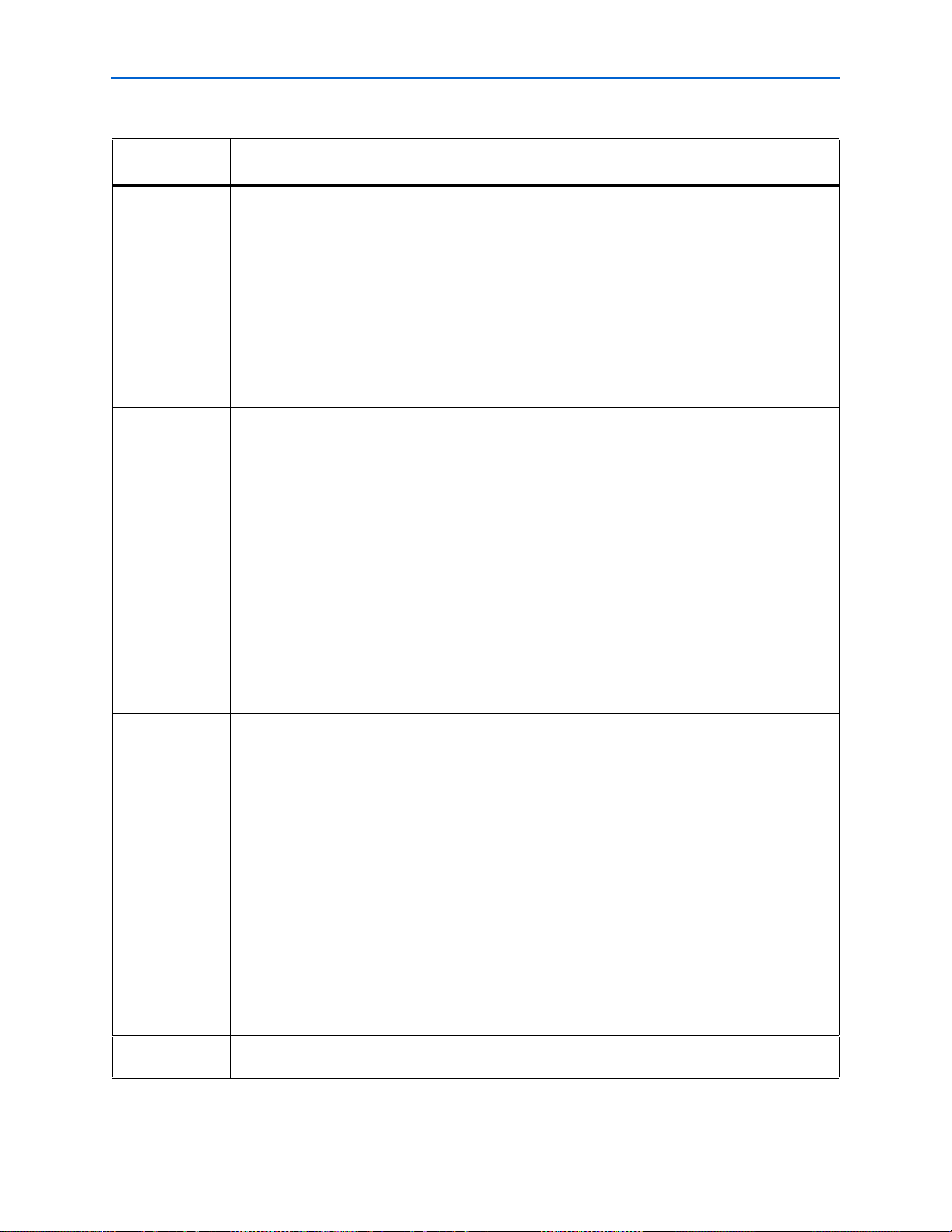

Tab le 3 –1 shows the options available on the General page.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 20

3–2 Chapter 3: Parameter Settings

ALTDLL Parameter Editor

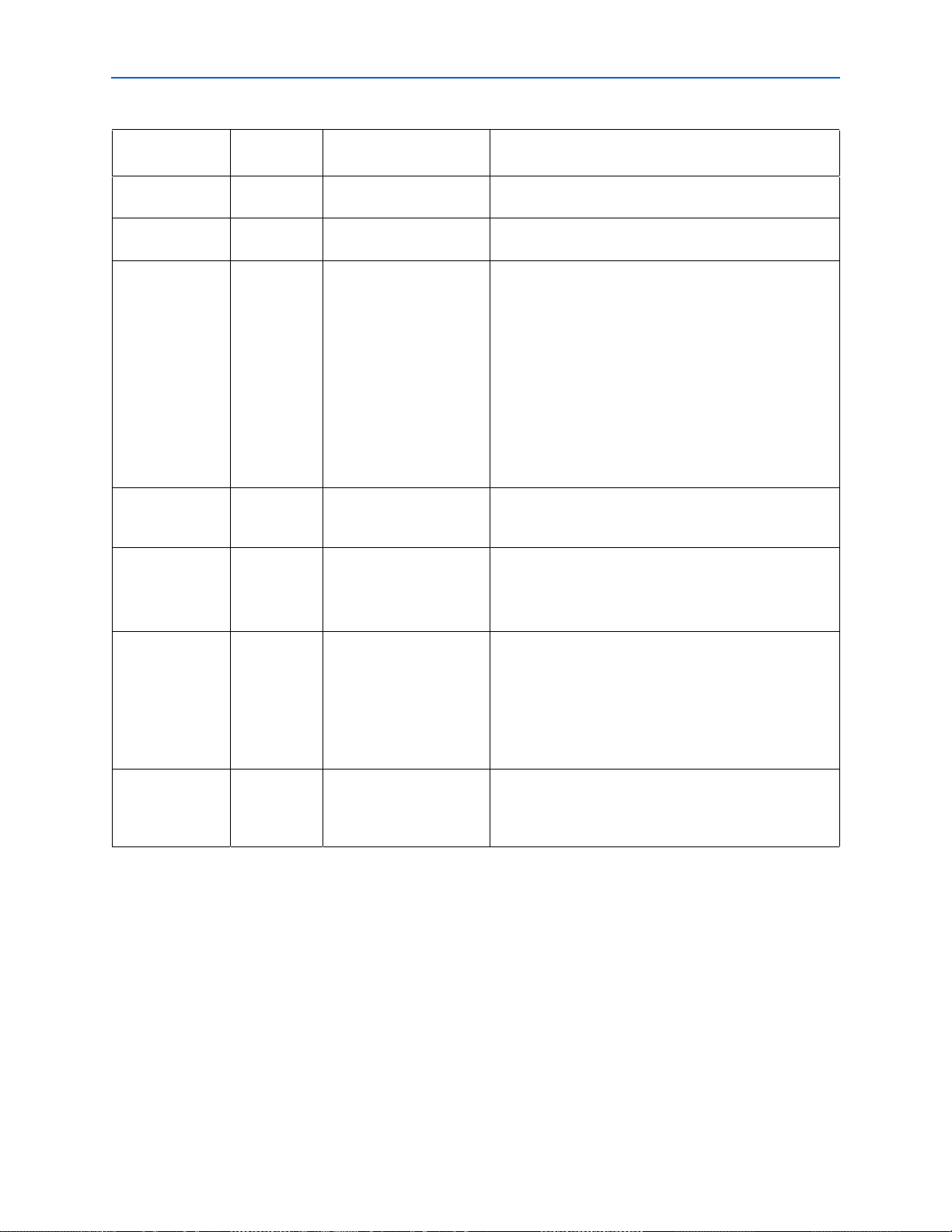

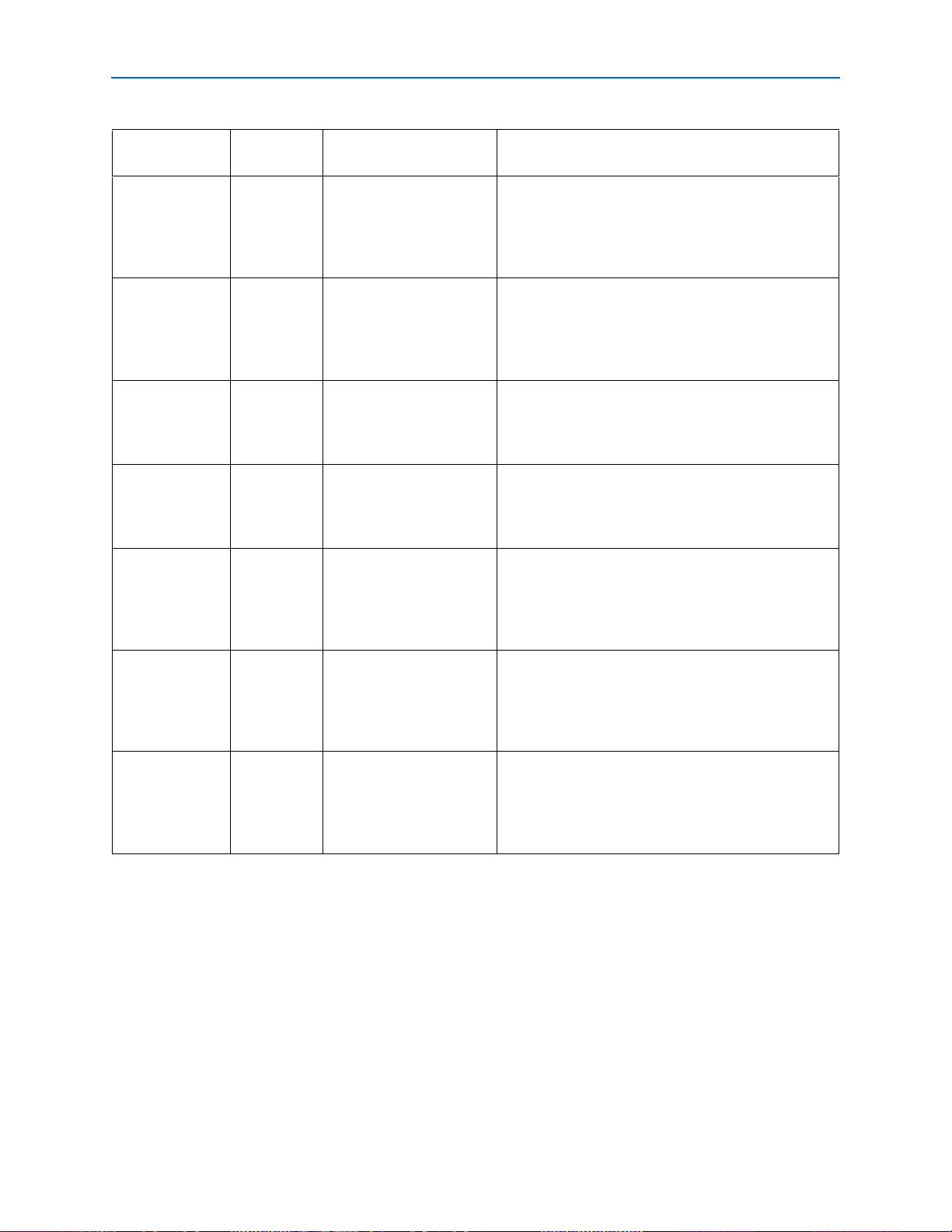

Table 3–1. Options on General Settings Page

Clear Box

Parameter Name Legal Value

Number of Delay

Chains

6, 8, 10, 12,

or 16

Parameter Name Description

DELAY_CHAIN_

LENGTH

Represents the number of delay buffers in the delay loop.

The DLL consists of 6, 8, 10, 12, or 16 DLL-controlled

delay buffers chained together. The total delay in the DLL

delay chain is computed with the following equation:

delay = delay_chain_length

x delay_buffer_delay

The DLL uses the delay chain to implement a 360° phase

shift. By comparing the incoming clock to the 360°-shifted

clock, the DLL determines the delay setting to implement

an actual 360° phase shift in its delay chain. Because each

delay buffer is identical, each buffer in the delay chain

implements a phase shift that is equal to

(360/delay_chain_length)°.

The default value is 12.

DQS Delay Buffer

Mode

Low or High DELAY_BUFFER_

MODE

Specifies the frequency mode for the variable delay

buffers.

If you select Low, the

dll_offset_ctrl_a_offsetctrlout [5..0]

or dll_offset_ctrl_b_offsetctrlout

[5..0] output is limited to a maximum value of 63.

If you select High, the output is limited to a maximum value

of 31.

The default value is Low.

Input Clock

Frequency

INPUT_FREQUENCY Specifies the frequency of the clock (in MHz) that is

connected to the clk input port. This frequency must be

within the valid range for the device you are using. You can

specify a duration in ps. The value is in floating-point

format with no decimal point limit.

The default value is 300 MHz.

For information about the clock range for the Altera

devices, refer to the respective device handbook.

Turn on jitter

reduction

— JITTER_REDUCTION Enables the jitter reduction circuit. Jitter affects the signal

integrity of the clock signal from a PLL clock source or an

external clock pin. If you turn on this parameter, the jitter

reduction circuit is enabled on the

dll_delayctrlout[5..0] and

dll_offset_ctrl_a_offsetctrlout [5..0],

or the dll_offset_ctrl_b_offsetctrlout

[5..0] output port.

When the jitter reduction circuit is enabled, the DLL may

require up to 1,024 clock cycles to lock. When the jitter

reduction circuit is disabled, the DLL requires only up to

256 clock cycles to lock.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 21

Chapter 3: Parameter Settings 3–3

ALTDLL Parameter Editor

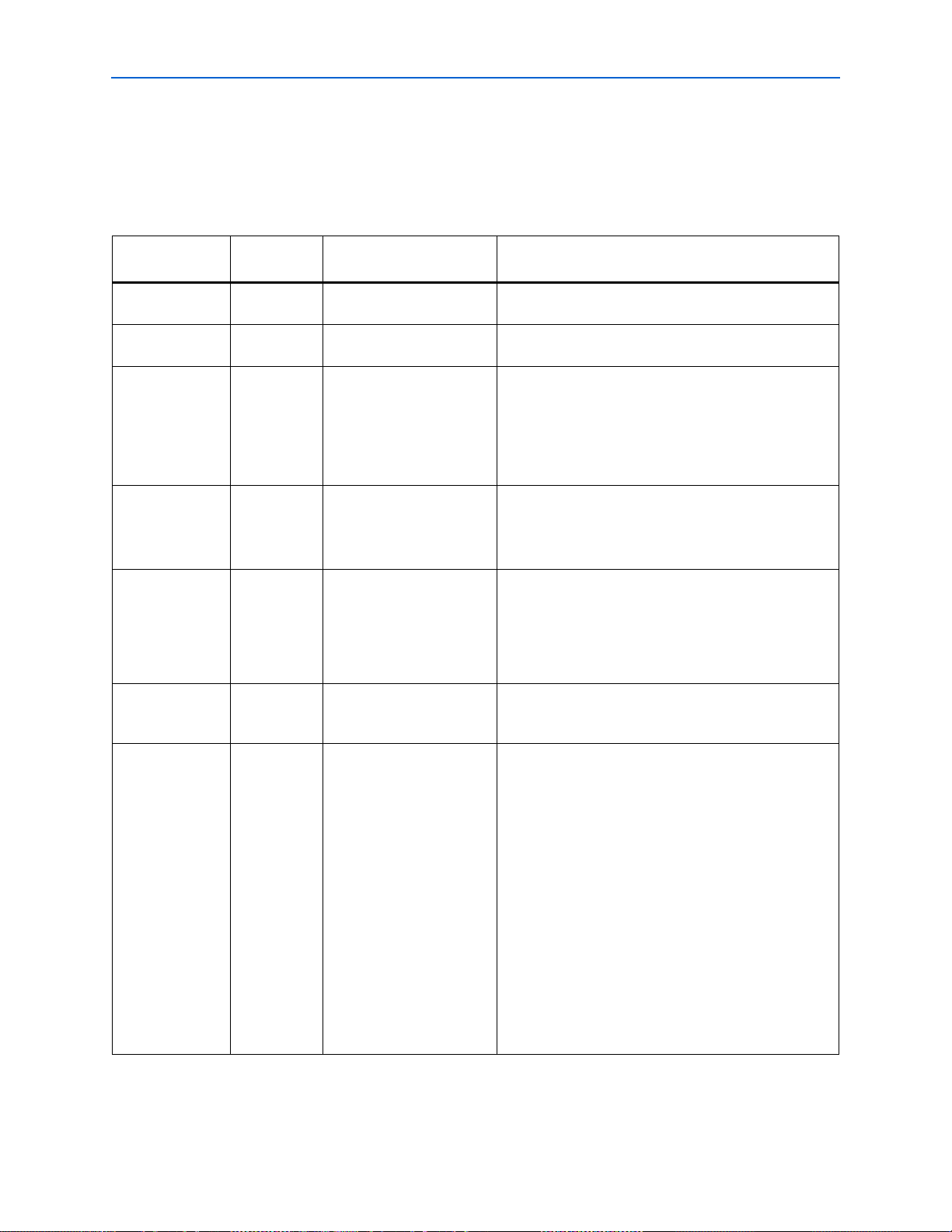

The DLL Offset Controls/Optional Ports page allows you to instantiate the DLL

offset control blocks (A and B), specify whether to use static offset, and create the

dll_aload and dll_dqsupdate optional ports. Tab le 3– 2 shows the options

available on DLL Offset Controls/Optional Ports page.

.

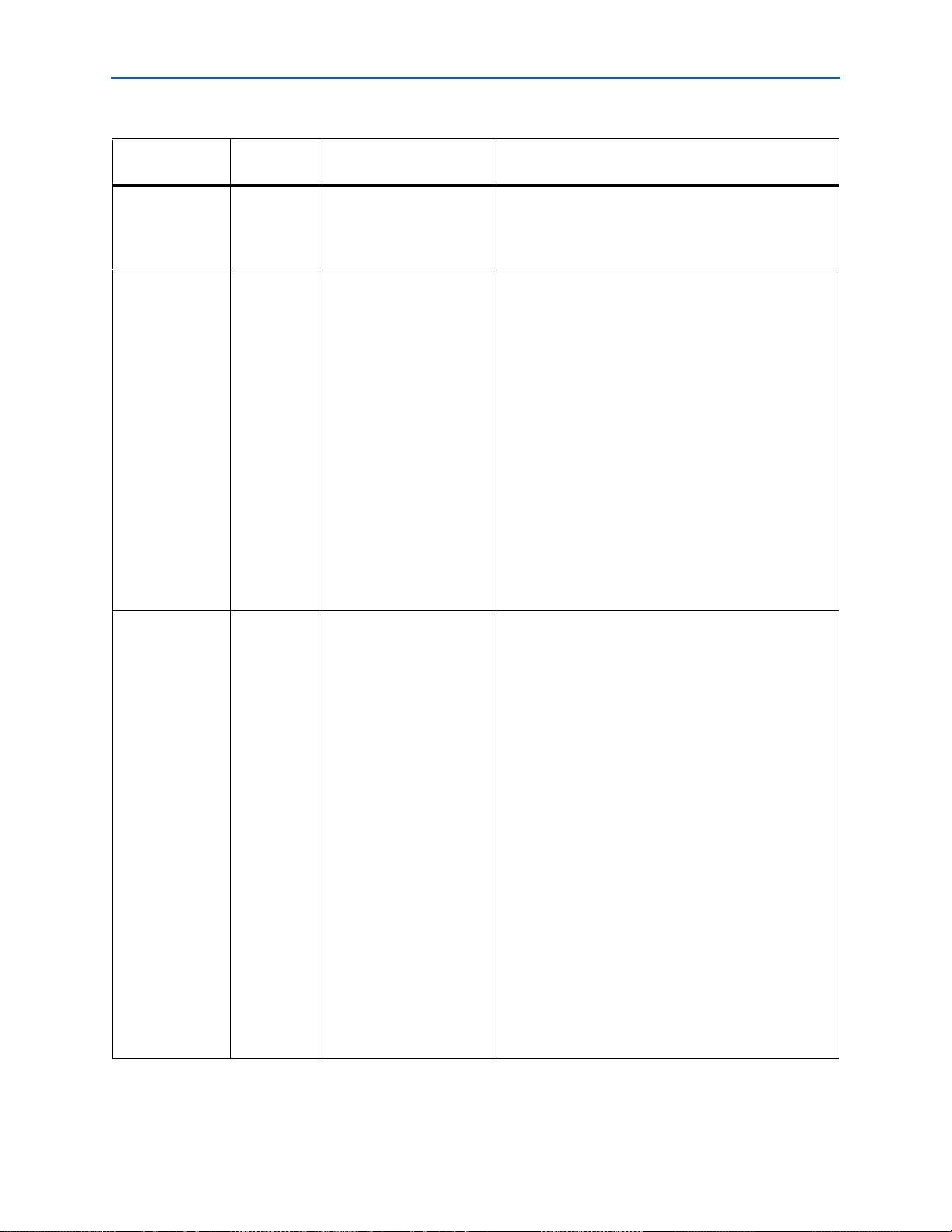

Table 3–2. Options on DLL Offset Controls/Optional Ports Page (Part 1 of 2)

Clear Box

Parameter Name Legal Value

DLL Phase Offset

Control A

Instantiate

dll_offset_ctrl

block

Set statically

to

or

Set

dynamically

Parameter Name Description

USE_DLL_OFFSET_

CTRL_A

Instantiates DLL_OFFSET_CTRL_A block. The block

can be placed either at the top, bottom, or side of the

FPGA device, depending on how the Quartus II Fitter

places it. If you turn on this parameter, you must

specify whether you want to set the blocks statically or

dynamically.

using offset

input port

–63 to 63 DLL_OFFSET_CTRL_A_

STATIC_OFFSET

The Set statically to option is a signed integer. Turn on

this option if you want a fixed offset value, and key in

the value you want.

This fixed value is added to the DLL feedback counter

and the output is generated on the

dll_offset_ctrl_a_offsetctrlout

[5..0]output port.

The default value is 0.

— DLL_OFFSET_CTRL_A_

USE_OFFSET

The Set dynamically using offset input port option

determines the output of the

dll_offset_ctrl_a_offsetctrlout

[5..0] output port. Turn on this option if you want a

dynamic offset value.

If you turn on this option, depending on whether the

dll_offset_ctrl_a_addnsub signal is

asserted or not, the phase offset specified on the offset

input bus is added or subtracted from the DLL feedback

counter output to get the

dll_offset_ctrl_a_offsetctrlout

[5..0]output.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 22

3–4 Chapter 3: Parameter Settings

ALTDLL Parameter Editor

Table 3–2. Options on DLL Offset Controls/Optional Ports Page (Part 2 of 2)

Clear Box

Parameter Name Legal Value

DLL Phase Offset

Control B

Instantiate dll

offset_ctrl block

Set statically

to

or

Set

dynamically

using offset

Parameter Name Description

USE_DLL_OFFSET_

CTRL_B

Instantiates DLL_OFFSET_CTRL_B block. The block

can be placed either at the top, bottom, or side of the

FPGA device, depending on how the Quartus II Fitter

places it.

If you turn on this option, you must specify whether

you want to set the blocks statically or dynamically.

input port

–63 to 63 DLL_OFFSET_CTRL_B_

STATIC_OFFSET

The Set statically to option is a signed integer.

Turn on this option if you want a fixed offset value, and

key in the value you want.

This fixed value is added to the DLL feedback counter

and the output is generated on the

dll_offset_ctrl_b_offsetctrlout[5..0

]output port.

The default value is 0.

— DLL_OFFSET_CTRL_B_

USE_OFFSET

The Set dynamically using offset input port option

determines the output of the

dll_offset_ctrl_b_offsetctrlout

[5..0] output bus. Turn on this option if you want a

dynamic offset value.

If you turn on this option, depending on whether the

dll_offset_ctrl_b_addnsub signal is

asserted or not, the phase offset specified on the offset

input bus is added or subtracted from the DLL feedback

counter output to get the

dll_offset_ctrl_b_offsetctrlout

[5..0]output.

Optional Ports

Create a

dll_aload

port

— DLL_ALOAD Enables the asynchronous-load signal for the DLL up or

down counter. When the dll_aload signal is high,

the counter is asynchronously loaded with the initial

delay setting of 16 in low-frequency mode when you

select Low for the DQS Delay Buffer Mode parameter,

or 32 in high-frequency mode when you select High for

the DQS Delay Buffer Mode parameter. This input

defaults to GND.

Optional Ports

Create a

‘dll_dqsupdate’

port

— DLL_DQSUPDATE Enables the update-enable signal for the delay-setting

latches in the DQS pins. This signal only feeds the

dqsupdateen port of the ALTDQ_DQS

megafunction.

To use the dll_dqsupdate signal, you must turn on

the Enable DQS delay chain latches option on the

DQS IN page in the ALTDQ_DQS parameter editor.

The Simulation Model page allows you to optionally generate simulation model files.

The Summary page displays a list of the types of files to be generated. The

automatically generated variation file contains wrapper code in the language you

specified earlier. On this page, you can specify additional types of files to be

generated.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 23

Chapter 3: Parameter Settings 3–5

ALTDQ_DQS Parameter Editor

Choose from the following file types:

■ Quartus II IP file (<function name>.qip)

■ Instantiation template file (<function name>.v)

■ Verilog HDL black box file (<function name>_bb.v)

■ AHDL Include file (<function name>.inc)

■ VHDL component declaration file (<function name>.cmp)

■ Quartus II symbol file (<function name>.bsf)

If you select Generate netlist on the Simulation Model page, the file for that netlist is

also available. A gray checkmark indicates a file that is automatically generated, and a

green checkmark indicates generation of an optional file

ALTDQ_DQS Parameter Editor

This section provides information about the ALTDQ_DQS MegaWizard parameters.

1 For advanced users who may use the clearbox generator, the clearbox parameter

names are provided for the corresponding MegaWizard parameters.

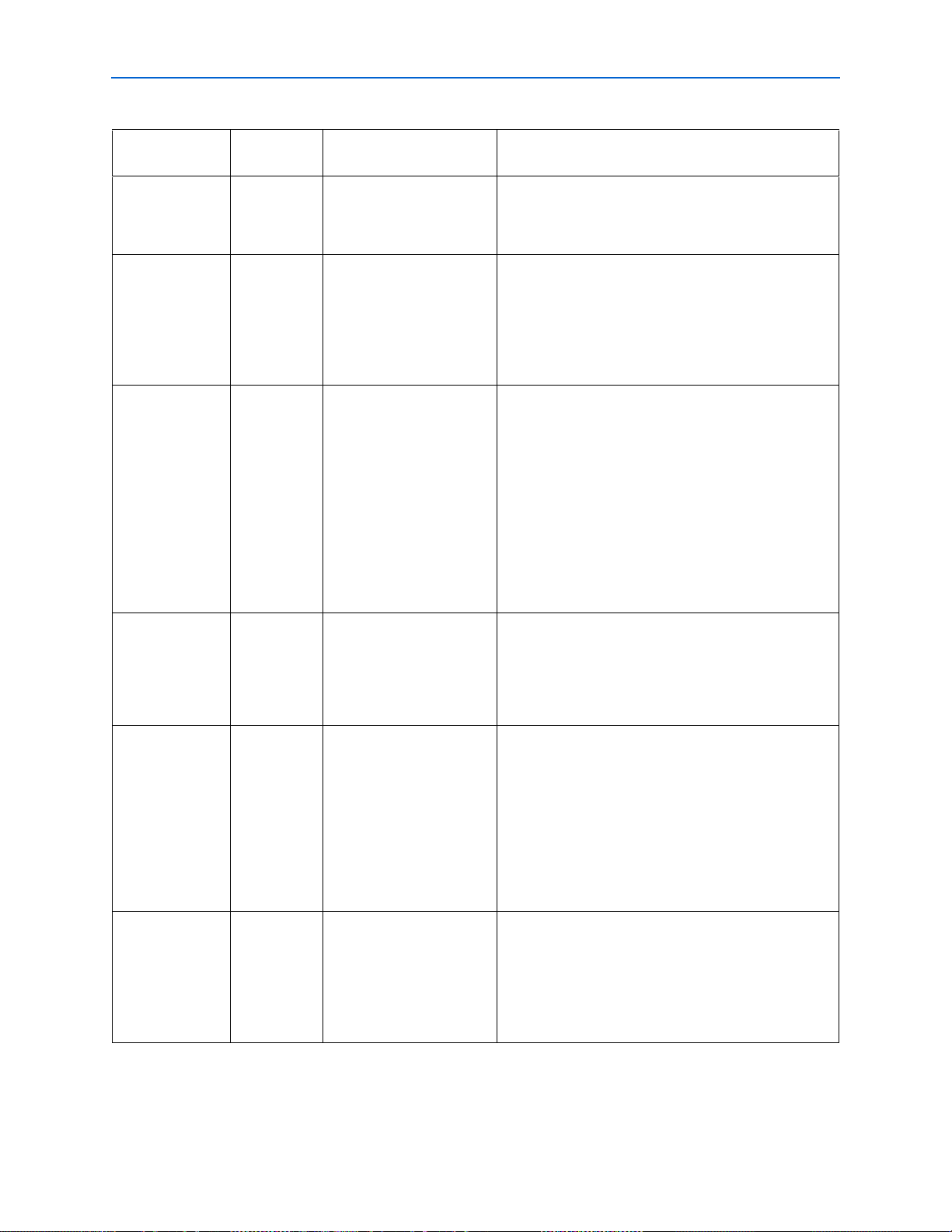

The Parameter Settings page in the ALTDQ_DQS parameter editor allows you to

configure the parameters in Tab le 3 –3 .

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 24

3–6 Chapter 3: Parameter Settings

.

ALTDQ_DQS Parameter Editor

Table 3–3. Options on Parameter Settings Page (Part 1 of 2)

Clear Box

Parameter Name Legal Value

RLDRAMII mode NONE, x9,

x18, or x36

Parameter Name Description

RLDRAMII_MODE Enables RLDRAM II support for ALTDQ_DQS instance.

If you select x9 or x18 mode, the DK pins do not have

group assignments, but they must be placed in the same

bank or chip edge as the other pins in the interface. If you

select x36 mode, the DK/DK# pins must be placed

manually in DQS locations.

If you select x18 mode, place the DM pins in either group

0 or group 1, which forces QVLD to the other group. If you

select x36 mode, place the DM pins in group 0 or 1, and

QVLD to be in group 0 or 1.

All combinations are allowed. Not supported in Arria II GX.

Data mask pin

group

NONE,

GROUP0, or

GROUP1

DM_LOC Specifies the group assignment for the DM pin group.

If you select NONE for the RLDRAMII mode option, then

this option defaults to NONE.

If you select x9 for the RLDRAMII mode option, then this

option defaults to NONE.

If you select x18 for the RLDRAMII mode option, then for

this option you can select either NONE, GROUP0, or

GROUP1. If you select GROUP0, then GROUP1 is used for

the Q valid signal group option, and if you select

GROUP1, then GROUP0 is used for the Q valid signal

group option.

If you select x36 for the RLDRAMII mode option, then for

this option you can select either NONE, GROUP0, or

G

ROUP1.

Not supported in Arria II GX devices.

Q valid signal

group

NONE,

GROUP0, or

GROUP1

QVLD_LOC Specifies the group assignment for the Q valid signal

group.

If you select NONE for the RLDRAMII mode option, then

this option defaults to NONE.

If you select x9 for the RLDRAMII mode option, then this

option defaults to GROUP0.

If you select x18 for the RLDRAMII mode option, then this

option depends on the Data mask pin group option. If you

select GROUP0 for the Data mask pin group option, then

GROUP1 is defaulted for this option, and if you select

GROUP1 for the Data mask pin group option, then

GROUP0 is defaulted for this option.

If you select x36 for the RLDRAMII mode option, then for

this option you can select either NONE, GROUP0, or

GROUP1.

Not supported in Arria II GX devices.

Number of

bidirectional DQ

0–48 NUMBER_OF_

BIDIR_DQ

Specifies the number of bidirectional DQ ports used in the

ALTDQ_DQS instance.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 25

Chapter 3: Parameter Settings 3–7

ALTDQ_DQS Parameter Editor

Table 3–3. Options on Parameter Settings Page (Part 2 of 2)

Clear Box

Parameter Name Legal Value

Number of input

0–48 NUMBER_OF_

DQ

Number of output

0–48 NUMBER_OF_

DQ

Number of stages

1, 2, 3, and 4 DQS_DELAY_CHAIN_

in

dqs_delay_chain

Parameter Name Description

Specifies the number of input DQ ports used in the

INPUT_DQ

ALTDQ_DQS instance.

Specifies the number of output DQ ports used in the

OUTPUT_DQ

ALTDQ_DQS instance.

Specifies the stages of DQS_DELAY_CHAIN. The

PHASE_SETTING

number of stages depends on the intended phase shift

that you want to clock for <IO>_DDIO_IN block in the

DQ input path. The bigger the value you specify, the longer

the delay.

The coarse phase shift depends on this option. For

example, in Stratix IV devices, if you set the frequency

mode to 1, you will get a phase shift of 20°, 60°, 90°, or

120°. If you set Number of stages in dqs_delay_chain

value to 2, you will get 60° phase shift and if you set the

Number of stages in dqs_delay_chain value to 1, you will

get 30° phase shift.

DQS input

frequency

— DQS_INPUT_

FREQUENCY

Specifies the input frequency of the DQS strobe in MHz.

The input frequency must match the DLL (ALTDLL) input

frequency.

Use half rate

components

— USE_HALF_RATE Instantiates the half-rate blocks in the ALTDQ_DQS

instance. This parameter is used only when the external

memory interface requires half-rate mode.

Not supported in Arria II GX devices.

Use dynamic OCT

path

— USE_DYNAMIC_OCT Instantiates the dynamic OCT blocks in the ALTDQ_DQS

instance. This parameter enables access to dynamic OCT

paths on both DQ and DQS paths. The dynamic OCT

features enable parallel termination (R

the external memory and disable R

) during reads from

t

during writes to the

t

external memory.

Not supported in Arria II GX devices.

Add memory

interface specific

fitter grouping

— ADD_MEM_FITTER_

GROUP_ASSIGNMENTS

Enables the Quartus II Fitter to automatically assign the

memory interface I/O ports to the memory interface I/O

pins on the FPGA.

assignments

The Advanced Options page allows you to configure the parameters in the following

pages:

■ DQS IN

■ DQS OUT/OE

■ DQ IN

■ DQ OUT/OE

■ Half-rate

■ OCT Path

■ DQSn I/O

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 26

3–8 Chapter 3: Parameter Settings

■ Reset/Config Ports

ALTDQ_DQS Parameter Editor

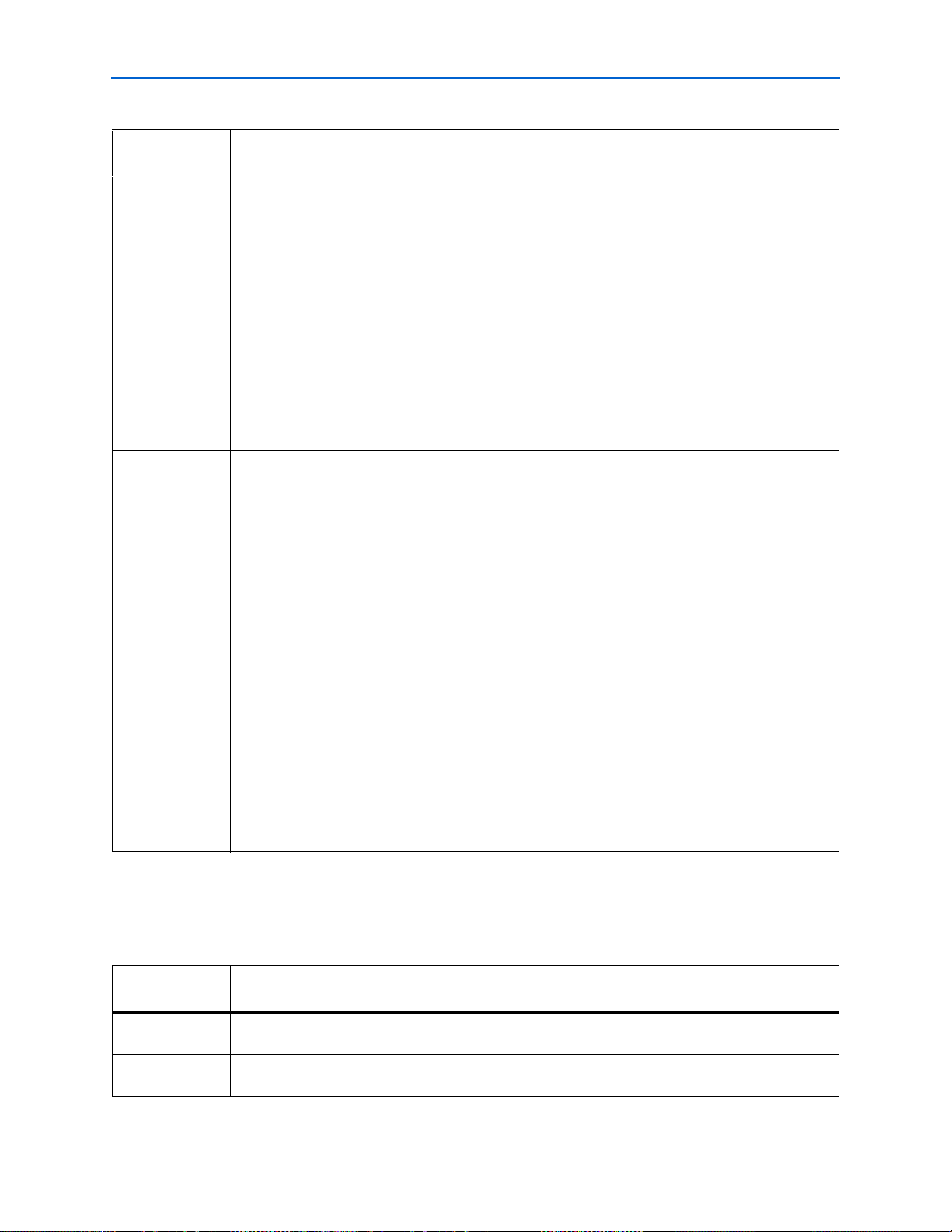

Tab le 3 –4 describes the options available on the DQS IN page. This page allows you

to configure the DQS input path. For more information about the DQS input path,

refer to “DQS Input Path” on page 4–6.

Table 3–4. Options on DQS IN Page (Part 1 of 3)

Clear Box

Parameter Name Legal Value

Enable DQS Input

—

Path

Enable DQS Input

—

Path

Delay chain

— USE_DQS_INPUT_

usage:

Enable dynamic

delay chain

Parameter Name Description

USE_DQS_INPUT_PATH

USE_DQS_INPUT_PATH

Instantiates the DQS input path.

Instantiates the DQS input path.

Enables <IO>_INPUT_DELAY_CHAIN (D1) on the

DELAY_CHAIN

DQS input path. If you turn on this parameter,

DQS_DELAY_CHAIN block in the path is disabled. D1

is a run-time adjustable delay chain.

To configure delay chains dynamically, refer to “Delay

Chains” on page 4–15.

Delay chain

usage:

Enable

— USE_DQS_DELAY_

CHAIN

Enables DQS_DELAY_CHAIN block. The DQS delay

chain is a DLL-controlled delay chain used to phase shift

the DQS read clock.

dqs_delay_chain

Enable DQS

busout delay

chain

— USE_DQSBUSOUT_

DELAY_CHAIN

Enables DQSBUSOUT_DELAY_CHAIN (Da). This

busout delay chain fine-tunes the outputs of

DQS_DELAY_CHAIN block so that the DQS strobe

timing matches the DQS enable signal. The DQS strobe

has 15 steppable delays, with each step having 50 ps of

delay. Da is a run-time adjustable delay chain.

Enable DQS

enable block

— USE_DQS_ENABLE Enables DQS_ENABLE block. This block grounds the

DQS input strobe when the strobe goes to high

impedance state (Z) after a DDR read postamble.

Enable DQS

enable control

block

— USE_DQS_ENABLE_

CTRL

Enables DQS_ENABLE_CTRL block that controls a

DQS enable circuitry.

You must determine an efficient working

resync_postamble_clk clock phase which clocks

this block to ensure smooth data transfer. The

ALTDQ_DQS megafunction cannot determine the phase

for the data transfer.

Use round trip delay (RTD) analysis or create a custom

data training circuitry to write and read back a training

pattern to and from the memory device and then

dynamically adjust the PLL’s resyncronization clock

phase to find an efficient working phase.

Even though this block controls the DQS enable signal,

the megafunction does not consider the necessary

timing for this signal. Refer to the external memory

interface requirements for the necessary timing.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 27

Chapter 3: Parameter Settings 3–9

ALTDQ_DQS Parameter Editor

Table 3–4. Options on DQS IN Page (Part 2 of 3)

Clear Box

Parameter Name Legal Value

Enable DQS

— — Enables DQS_ENABLE_DELAY_CHAIN (Db) that

enable block

delay chain

Parameter Name Description

fine-tunes the outputs of DQS_ENABLE_CTRL block

so that the DQS enable signal timing matches the DQS

strobe. Db is a run-time adjustable delay chain.

Advanced Delay

Chain Options

Set dynamically

using

configuration

registers

Advanced Delay

Chain Options

DQS delay chain

delayctrlin port

source

— USE_DQS_DELAY_

CHAIN_PHASECTRLIN

DLL or Core DQS_DELAY_CHAIN_

DELAYCTRLIN_SOURCE

Determines the phasectrlin input for the phase

setting. If you turn on this option, it dynamically chooses

the phase applied to the dqsbusout output during the

FPGA run time. If you turn off this option, the phase

setting is determined by the Number of stages in

dqs_delay_chain option in the Parameter Settings

page. This delay chain fine-tunes the DQS strobe signal.

Determines whether you want the delayctrlin port

to be controlled by DLL (outputs) or from the Core

(FPGA).

If you select DLL, the dll_delayctrlin[5..0]

port is connected to the

dll_delayctrlout[5..0] port of the DLL. The

DLL option adjusts the delay setting in

DQS_DELAY_CHAIN block across pressure, volume,

and temperature (PVT). Altera recommends that you

always select DLL to optimize the read capture at the DQ

input register. If you select Core, the

core_delayctrlin port is fed by the core.

Advanced Delay

Chain Options

DQS Delay Buffer

Mode

Low or High DELAY_BUFFER_MODE Specifies whether the variable delay buffers in the

DQS_DELAY_CHAIN work in low-frequency or

high-frequency mode. The frequency mode must match

the frequency mode you select for the DQS Delay Buffer

Mode parameter on the Parameter Settings page in the

ALTDLL parameter editor.

Advanced Delay

Chain Options

DQS Phase Shift

0–36,000 DQS_PHASE_SHIFT Specifies the phase shift between the delayed DQS signal

and the input DQS signal in units of hundreds of degrees,

for example, a 90° phase shift is represented as 9,000.

Use this parameter for static timing analysis only

be

cause timing analysis cannot determine the phase

shift through the delayctrlin[5..0],

phasectrlin[2..0], and

offsetctrlin[5..0] ports on the megafunction

the way a simulation can. This is an optional field and

defaults to 0.

Advanced Delay

Chain Options

Enable DQS

offset control

— DQS_OFFSETCTRL_

ENABLE

Enables offset values to be added to

DQS_DELAY_CHAIN block. If you turn on this option,

make sure that the ALTDLL instance is set to use the DLL

offset control blocks. This option connects the outputs

from the DLL offset control blocks to the DQS delay

chain block. This parameter is optional and turned off by

default.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 28

3–10 Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

Table 3–4. Options on DQS IN Page (Part 3 of 3)

Clear Box

Parameter Name Legal Value

Advanced Delay

— DQS_CTRL_LATCHES_

Chain Options

Enable DQS

delay chain

latches

Parameter Name Description

Enables the delayctrlin[5..0] and

ENABLE

offsetctrlin[5..0] inputs to be registered by

the dqsupdateen signal. The DLL continues changing

its delay settings value due to the feedback system.

These DLL values are propagated through the

delayctrlout and offsetctrlout signals of

the DLL and DLL offset control blocks to

DQS_DELAY_CHAIN block to calibrate the necessary

delay settings. These values are updated based on the

dll_dqsupdate port from the DLL, which is

connected to the dqsupdateen port. To use this

option, you must turn on the Create a ‘use

dll_dqsupdate’ port option on the DLL Offset

Controls/Optional Ports page in the ALTDLL parameter

editor.

Advanced Enable

Control Options

DQS Enable

Control Phase

Setting

Set statically

to

or

Set

dynamically

using

configuration

DQS_ENABLE_CTRL_

PHASE_SETTING

If you turn on the Set statically to option, you can select

the phase setting for the delay chains from 0 up to 4 to

fine-tune the DQS enable signal.

If you turn on the Select dynamically using

configuration registers option, the phase setting is

determined by the phasectrlin input for the delay

chains.

registers

Advanced Enable

Control Options

DQS Enable

Control Invert

Phase

Always,

Never, or

Based on

configuration

registers

DQS_ENABLE_CTRL_

INVERT_PHASE

If you turn on Always, the phase output is inverted.

If you turn on Never, the phase output is not inverted.

If you turn on Based on configuration registers, the

phaseinvertctrl input determines whether or not

the inverter is used. The inverter can be used to increase

the number of available phases. This is an optional field

and defaults to Never.

Enable DQS

enable block

delay chain

— USE_DQSENABLE_

DELAY_CHAIN

Enables DQS_ENABLE_DELAY_CHAIN

ch

ain fine-tunes the outputs of DQS_ENABLE_CTRL

block so that the DQS enable signal timing matches the

. This delay

DQS strobe. This delay chain is a run-time adjustable

delay chain.

Tab le 3 –5 describes options available on the DQS OUT/OE page. This page allows

you to configure the DQS output and output enable (OE) paths. For more information

about the DQS output and OE paths, refer to “DQS Output/OE Path” on page 4–12.

Table 3–5. Options on DQS OUT/OE Page (Part 1 of 2)

Clear Box

Parameter Name Legal Value

Enable DQS

— USE_DQS_OUTPUT_

output path

Enable DQS

— USE_DQS_OUTPUT_

output path

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Parameter Name Description

Instantiates the DQS output path.

PATH

Instantiates the DQS output path.

PATH

Page 29

Chapter 3: Parameter Settings 3–11

ALTDQ_DQS Parameter Editor

Table 3–5. Options on DQS OUT/OE Page (Part 2 of 2)

Clear Box

Parameter Name Legal Value

DQS Output Path

— USE_DQS_OUTPUT_

Options

Enable DQS

output delay

Parameter Name Description

Enables DQS_OUTPUT_DELAY_CHAIN1 (D5) in the

DELAY_CHAIN1

DQS output path. This parameter is used for deskew

purposes or SSN reduction.

D5 is a run-time adjustable delay chain.

chain1

DQS Output Path

Options

Enable DQS

output delay

— USE_DQS_OUTPUT_

DELAY_CHAIN2

Enables DQS_OUTPUT_DELAY_CHAIN2 (D6) in the

DQS output path. This parameter is used for deskew

purposes or SSN reduction.

D6 is a run-time adjustable delay chain.

chain2

DQS Output Path

Options

DQS output

register mode

DQS Output

Not used, FF,

or DDIO

DQS_OUTPUT_REG_

MODE

Enables the DQS_OUTPUT_FF or

DQS_OUTPUT_DDIO_OUT output registers. Select FF

if you want flip-flop output registers or DDIO if you want

double data rate I/O registers.

— USE_DQS_OE_PATH Instantiates DQS output enable path.

Enable Options

Enable DQS

output enable

DQS Output

Enable Options

Enable DQS

output enable

— USE_DQS_OE_DELAY_

CHAIN1

Enables DQS_OUTPUT_DELAY_CHAIN1 (D5) in the

DQS OE path. This parameter is used for deskew

purposes or SSN reduction. D6 is a run-time adjustable

delay chain.

delay chain1

DQS Output

Enable Options

Enable DQS

output enable

— USE_DQS_OE_DELAY_

CHAIN2

Enables DQS_OUTPUT_DELAY_CHAIN2 (D6) in the

DQS OE path. This parameter is used for deskew

purposes or SSN reduction. D6 is a run-time adjustable

delay chain.

delay chain2

DQS Output

Enable Options

DQS output

enable register

Not used, FF,

or DDIO

DQS_OE_REG_MODE Enables the DQS_OUTPUT_FF or

DQS_OUTPUT_DDIO_OUT output registers. Select FF

if you want flip-flop registers or DD

data rate I/O registers.

IO if you want double

mode

Tab le 3 –6 describes options available on the DQ IN page. This page allows you to

configure the DQ input path. For more information about the DQ input path, refer to

“DQ Input Path” on page 4–8.

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 30

3–12 Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

Table 3–6. Options on DQ IN Page (Part 1 of 3)

Clear Box

Parameter Name Legal Value

DQ Input Register

Options

Not used, FF,

or DDIO

DQ input register

mode

DQ Input Register

Options

DQ input register

clock source

‘dqs_bus_ou

t’ port,

Inverted

‘dqs_bus_ou

t’ port, or

Core

Parameter Name Description

Enables the DQ input registers (<IO>_INPUT_FF or

DQ_INPUT_REG_MODE

<IO>_DDIO_IN registers). Select FF if you want

flip-flop registers or DDIO if you want double data rate

I/O registers.

DQ_INPUT_REG_CLK_

SOURCE

Specifies how the DQ input registers should be clocked.

You can either clock it from the ‘dqs_bus_out’ port (DQS

input path), the Inverted ‘dqs_bus_out’ port (DQS input

path), or directly from the Core (FPGA).

Altera recommends that you turn on the ‘dqs_bus_out’

port option to clock the DQ input register. When reading

from the external memory, the DQ data that comes into

the DDIO must be center-aligned with the DQS strobe

that goes through the DQS input path and comes out the

dqs_bus_out port. By center-aligning the DDIO with

DQS strobe, you maximize the setup and hold margins at

the DQ input register.

You can also connect the dqs_bus_out port to the

full-rate DQ input register for complementary clocking

purpose as used in QDR and QDR II applications. You

can connect the dqs_bus_out port by turning on the

Connect DDIO clkn to DQS_BUS from complementary

DQSn option.

DQ Input Register

Options

Use DQ input

phase alignment

— USE_DQ_IPA Enables the input phase alignment (<IO>_IPA_LOW or

<IO>_IPA_HIGH) blocks. The input phase alignment

blocks represent the circuitry required to phase-shift the

input signal the DQ data for resynchronization and

alignment purpose. The resynchronization and alignment

are done to match the arrival delay of the DQS (triggered

by the fly-by clock on a DDR-DIMM) to the latest arrival

delay of a DQS from the DIMM.

Because this block is meant for resynchronization, the

ALTDQ_DQS megafunction does not consider the

clocking requirements of this block. You must figure the

clocking requirements using the RTD analysis or create a

custom data training circuitry to read or write back a

training pattern to and from the memory device, and

then dynamically adjust the PLL’s resyncronization clock

phase to find a good working phase.

For more component information about the available

alignment and resynchronization registers in this block,

refer to the “I/O Element (IOE) Registers” section in the

External Memory Interface chapter of the respective

device handbooks. For the available levelling delay

chains in this block, refer to the “Leveling Circuitry”

section in the External Memor

y Interface chapter of the

respective device handbooks.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 31

Chapter 3: Parameter Settings 3–13

ALTDQ_DQS Parameter Editor

Table 3–6. Options on DQ IN Page (Part 2 of 3)

Clear Box

Parameter Name Legal Value

DQ Input Register

— DQ_RESYNC_REG_MODE Enables the DQ resynchronization register.

Options

Parameter Name Description

Supported in Arria II GX devices only.

Use DQ resync

register

DQ Input Register

Options

Use DQ half rate

‘dataoutbypass’

port

— DQ_HALF_RATE_USE_

DATAOUTBYPASS

If you turn on this parameter, the dataoutbypass

input dynamically routes the directin input to the

dataout output for <IO>_HALF_RATE_INPUT

block. Using this parameter, you can bypass the half-rate

registers in <IO>_HALF_RATE_INPUT block

dynamically during the FPGA run-time.

Not supported in Arria II GX devices.

Advanced DQ IPA

Options

DQ Input Phase

Alignment Phase

Setting

Advanced DQ IPA

Options

Add DQ Input

Phase Alignment

Input Cycle Delay

Advanced DQ IPA

Options

Invert DQ Input

Phase Alignment

Phase

Advanced DQ IPA

Options

Register DQ input

phase alignment

Set statically

to

DQ_IPA_PHASE_

SETTING

or

Set

dynamically

using

configuration

registers

Always,

Never, or

DQ_IPA_ADD_INPUT_

CYCLE_DELAY

Based on

configuration

registers

Always,

Never, or

DQ_IPA_INVERT_

PHASE

Based on

configuration

re

gisters

— DQ_IPA_BYPASS_

OUTPUT_REGISTER

If you turn on the Set statically to option, the phase

setting can be selected from values 0 to 7 for the delay

chains. If you turn on the Select dynamically using

configuration registers option, the phase setting is

determined by the phasectrlin input for the delay

chains. This parameter fine-tunes the resynchronization

phase for the DQ input data. The phase settings are also

called the levelling delay chains that handle the fly-by

clock topology in DDR3 interfaces.

If you turn on Always, a single cycle delay is added to

the input path. If you turn on Never, no delay is added. If

you turn on Based on configuration registers, the

enainputcycledelaysetting input controls

whether or not a single cycle delay is added to the input

path.

If you turn on Always, the phase output is inverted. If

you turn on Never, the phase output is not inverted. If

you turn on Based on configuration registers, the

phaseinvertctrl input determines whether or not

the inverter is used. The inverter is used to increase the

number of available phases.

Controls the output register in the DQ input path. If you

turn on this option, the output data bypasses the output

register. If you turn off this option, then the data goes

through the output register.

bypass output

© February 2012 Altera Corporation ALTDLL and ALTDQ_DQS Megafunctions User Guide

Page 32

3–14 Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

Table 3–6. Options on DQ IN Page (Part 3 of 3)

Clear Box

Parameter Name Legal Value

Advanced DQ IPA

— DQ_IPA_ADD_PHASE_

Options

Register DQ input

phase alignment

add phase

Parameter Name Description

If you turn on this option, a negative edge-triggered

TRANSFER_REG

register is added in the data path for the clock phase

transfer. If you turn off this option, no register is added.

The negative-edge register is used to guarantee the

setup and hold time for a phase transfer.

transfer

Use DQ input

delay chain

— USE_DQ_INPUT_DELAY

_CHAIN

Enables <IO>_INPUT_DELAY_CHAIN (D1). This

parameter is used for deskew purposes or SSN

reduction on the DQ input path.

Not supported in Arria II GX devices.

For more information about configuring delay chains

dynamically, refer to “Delay Chains” on page 4–15.

Tab le 3 –7 describes options available on the DQ OUT/OE page. This page allows you

to configure the DQ output and OE paths. For more information about the DQ output

and OE paths, refer to “DQ Output/OE Path” on page 4–10.

Table 3–7. Options on DQ OUT/OE Page (Part 1 of 2)

Clear Box

Parameter Name Legal Value

DQ Output Path

— USE_DQ_OUTPUT_

Options

Parameter Name Description

DELAY_CHAIN1

Enable DQ output

delay chain1

DQ Output Path

Options

— USE_DQ_OUTPUT_

DELAY_CHAIN2

Enable DQ output

delay chain2

DQ Output Path

Options

Not used, FF,

or DDIO

DQ_OUTPUT_REG_MODE Enables the full-rate DQ output registers

DQ output

register mode

DQ Output Enable

— USE_DQ_OE_PATH Instantiates the DQ output enable path.

Options

Enable DQ output

enable

DQ Output Enable

Options

— USE_DQ_OE_DELAY_

CHAIN1

Enable DQ output

enable delay

chain1

Enables <IO>_OUTPUT_DELAY_CHAIN1 (D5) in the

DQ output path. This parameter is used for deskew

purposes or SSN reduction. D5 is a run-time adjustable

delay chain.

For more information about configuring delay chains

dynamically, refer to “Delay Chains” on page 4–15.

Enables <IO>_OUTPUT_DELAY_CHAIN2 (D6) in the

DQ output path. This parameter is used for deskew

purposes or SSN reduction. D6 is a run-time adjustable

delay chain.

For more information about configuring delay chains

dynamically, refer to “Delay Chains” on page 4–15.

(<IO>_OUTPUT_FF or <IO>_OUTPUT_DDIO_OUT

registers).

Enables <IO>_OE_DELAY_CHAIN1 (D5) in the DQ OE

path. This parameter is used for deskew purposes or

SSN reduction. D5 is a run-time adjustable delay chain.

For more information about configuring delay chains

dynamically, refer to “Delay Chains” on page 4–15.

ALTDLL and ALTDQ_DQS Megafunctions User Guide © February 2012 Altera Corporation

Page 33

Chapter 3: Parameter Settings 3–15

ALTDQ_DQS Parameter Editor

Table 3–7. Options on DQ OUT/OE Page (Part 2 of 2)

Clear Box

Parameter Name Legal Value

DQ Output Enable

— USE_DQ_OE_DELAY_

Options

Enable DQ output

enable delay

chain2

DQ Output Enable

Options

Not used, FF,

or DDIO

DQ output enable

register mode

Parameter Name Description

Enables <IO>_OE_DELAY_CHAIN2 (D6) in the DQ OE

CHAIN2

path. This parameter is used for deskew purposes or

SSN reduction. D6 is a run-time adjustable delay chain.

For more information about configuring delay chains

dynamically, refer to “Delay Chains” on page 4–15.

DQ_OE_REG_MODE Enables the full-rate DQ output-enable registers

(<IO>_OE_FF or <IO>_OE_DDIO_OE registers).

Select FF if you want flip-flop registers or DDIO if you

want double data rate I/O registers.

Tab le 3 –8 describes the options available on the Half-rate page.

Table 3–8. Options on Half-Rate Page (Part 1 of 2)

Clear Box

Parameter Name Legal Value

IO Clock Divider

Source

Core,

‘dqs_bus_ou

t’ port, or

Inverted

‘dqs_bus_ou

t’ port

Parameter Name Description

IO_CLOCK_DIVIDER_

CLK_SOURCE

Specifies the I/O clock divider clock source which can be

from the Core (FPGA), the ‘dqs_bus_out’ port (DQS

input path), or the Inverted ‘dqs_bus_out’ port (DQS

input path).

Altera recommends that you turn on the ‘dqs_bus_out’

port option to clock the DQ input register. When reading

from the external memory, the DQ data that comes from

the full-rate DQ input registers must be synchronized to

the half-rate input block, if half-rate interfaces are used.

If the full-rate DQ input registers are clocked by the DQS

input path via the dqs_bus_out port, then the I/O

clock divider (and other clock source settings) must also

be clocked via the dqs_bus_out port.

Create

‘io_clock_divider

_masterin’ input

port

— USE_IO_CLOCK_

DIVIDER_MASTERIN

Enables the masterin input to synchronize this divider

with another I/O clock divider. If you turn off this option,

this divider operates independently. This mode is meant

for the master divider of a group of dividers. Turn on this

parameter when you chain the I/O clock divider blocks

from multiple ALTDQ_DQS instances.

Create

‘io_clock_divider

_clkout’ output

— — Divides the clock output signal by two. The clock out

signal can be connected to the clock input of a half-rate

Input block or fed to the FPGA core.