Page 1

DR-140T/E/TE1/TE 2

Serv ic e M a n u al

C O N T E N T S

• SP ECIFICATIONS

1) General................................................................................2

2) Tran smitter................*

3) R eceiver...............................................................................3

• CIRC UIT DESCRIPTION

1) R eceiver S yte m

2) Transmitter System ....................................................5-6

3) PLL C ircuit.........................................................................6

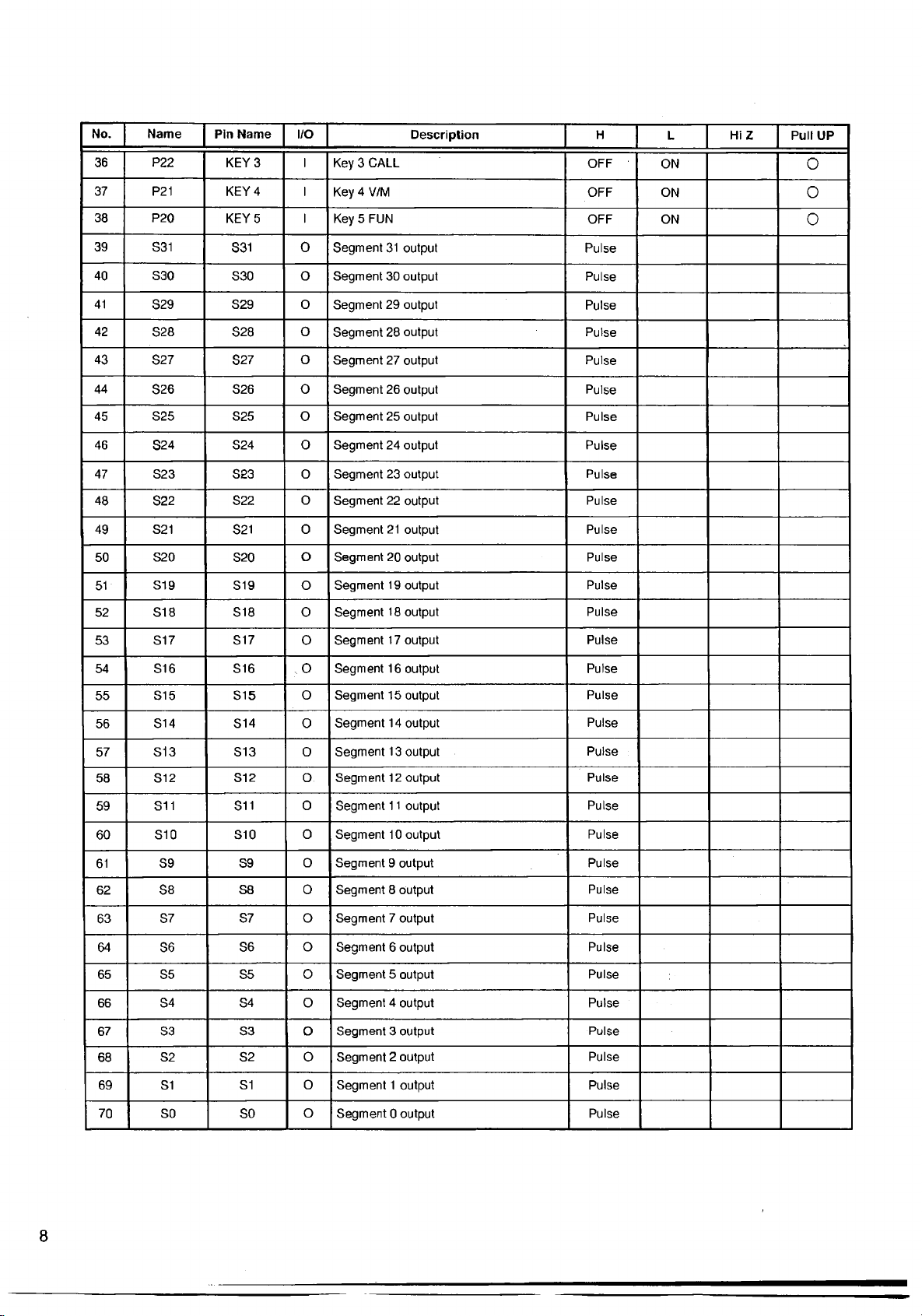

4) Terminal Function of C PU ...........................................7

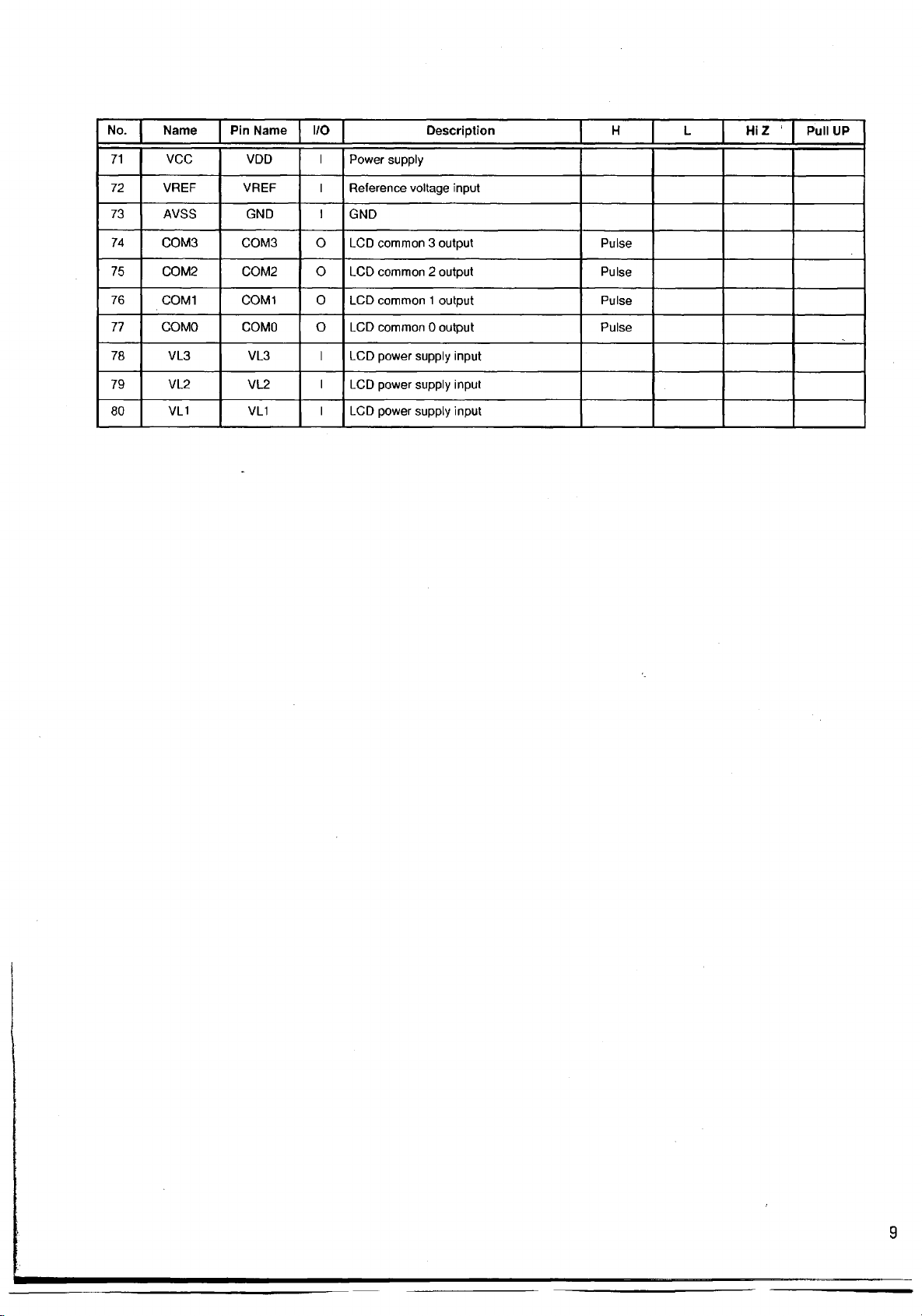

• SEM ICONDUCTO R DATA

1) AK2341 ............................................................................10

2) AN78L05M ...................................................................11

3) LA4425A ..........................................................................11

4) M 5 218FP.........................................................................11

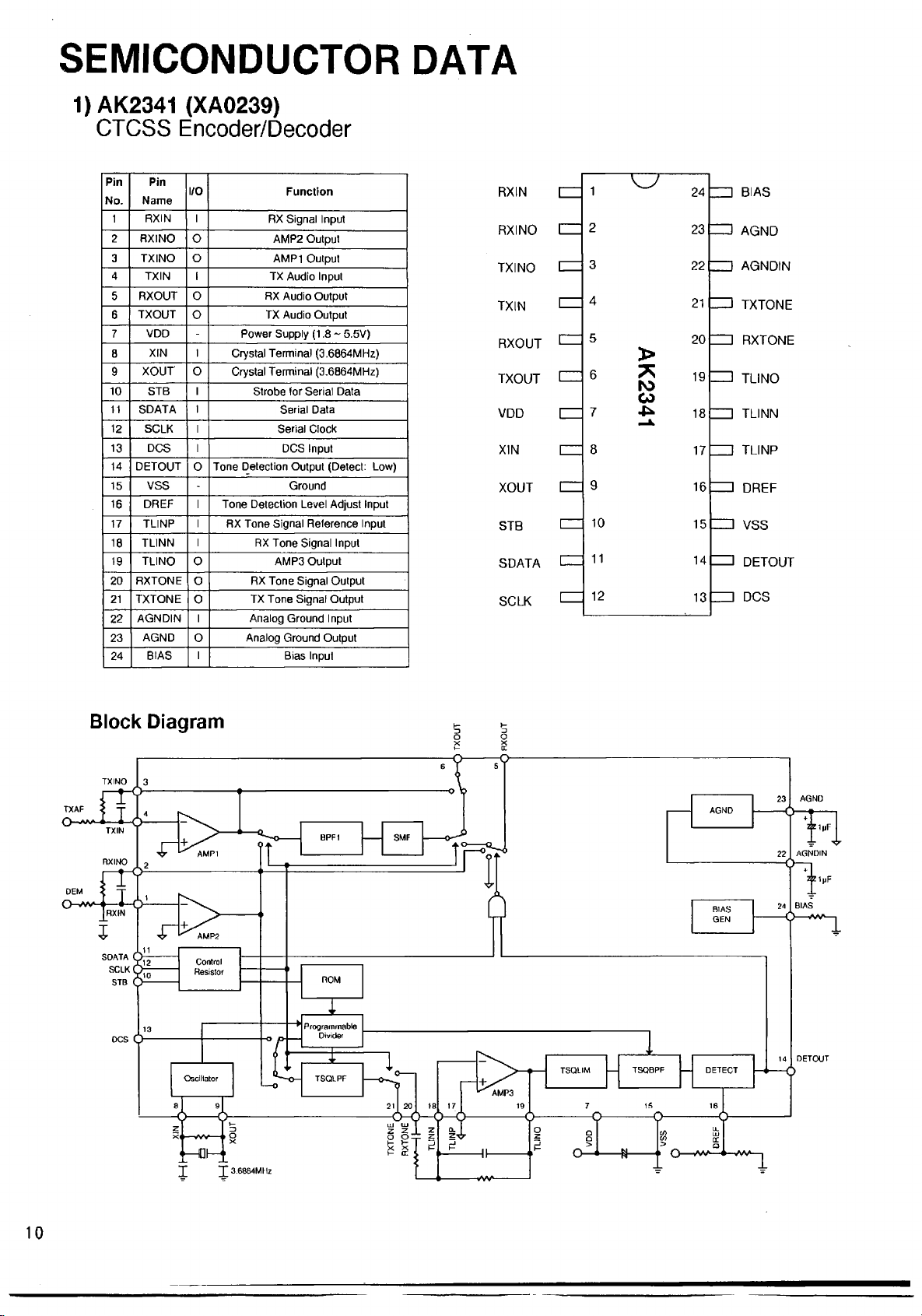

5) M 56760FP...................................................................... 12

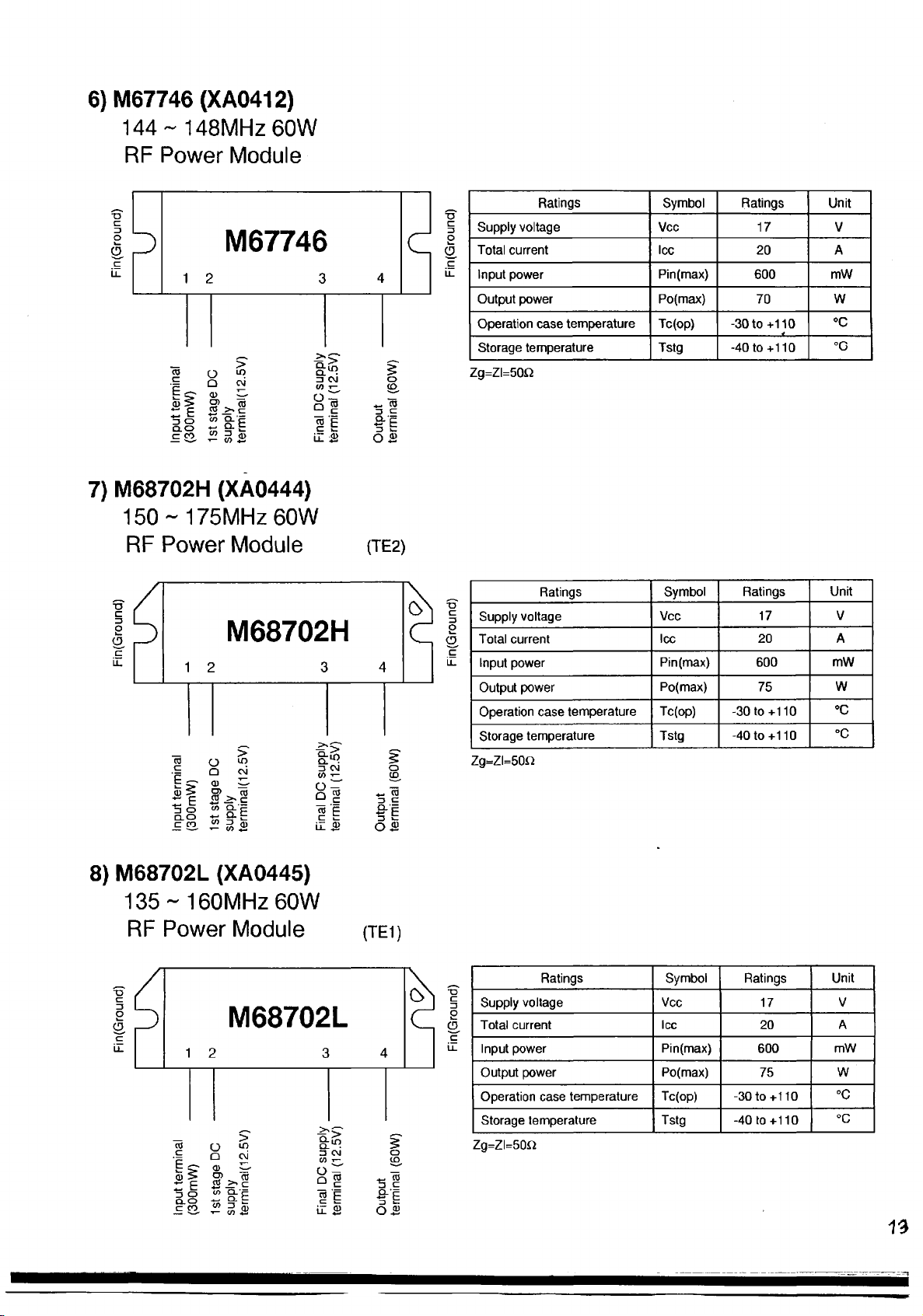

6) M 6774 6............................................................................13

7) M68702H..........................................................................13

6) M 68702L..........................................................................13

9) M C7808CT...................................................................... 14

10) RH5VL32AA-T1 ............................................................14

11) RH5VL45AA-T1 ............................................................14

12) TK10930VTL...................................................................15

13) jczPC2710T......................................................................16

14 )24LC16B 16

15).Transistor,D iode and LED Outline D raw ing s

16) L C D ....................................................................................18

• EXPLO DED VIEW

1) Bottom V ie w

2) LCD A ssem bly...............................................................20

3) Top, and Front V ie w .....................................................21

........................................................

.........................................................4 -5

...................................................................19

.......

• PARTS LIST

Main U nit...................................................................... 21 -2 2

2

17

Packing.................................................................................23

CPU Unit...............................................................................23

SP Unit ..............................................................................

VCO U nit.............................................................................23

Mechanical Parts ..............................................................23

EJ-20U .................................................................................24

• AD JU STMENT

1) Required Test Equipment

2) PLL Adjustm ent.............................................................26

3) TX Adjustme nt

4) RX Adjustment..............................................................27

5) Adjustment Points

• PC BOAD VIEW

1) Main Unit Side A ...........................................................29

2) Main Unit Side B...........................................................30

3) CPU Unit Side A ..........................................................31

4) CPU Unit Side B............................................................31

5) VCO Unit Side A ...........................................................32

6) VCO Unit Side B ...........................................................32

7) EJ-20U (CTCSS Unit: O ptio n)..................................33

• BLO CK D IAG RA M ...................................................................34

• SCHEMATIC DIAGRAM

1) Main Unit T/E....................................................

2) Main Unit TE 1/T E2 ...............................................37 -3 8

3) CPU U n it

4) VCO U nit

5) EJ-20U (CTCSS Unit: O ption)

.............................................................26

........................................................................

........................................................................40

..........................................

........................................................28

...............................

.....

23

25

35-3 6

39

41

ALINCO, inc

Page 2

SPECIFICATIONS

1) General

TX Frequency Range:

RX Frequency Range:

CTCSS Encode:

CTCSS Decode:

Microphone:

Frequency Resolution

Antenna Impedance:

Power Input:

Current Drain @13.8V DC:

Dimensions:

Weight:

Memory Channels:

Display:

Tone Bursts:

Time Out Timer:

Busy Channel Lock Out:

Penalty Timer:

Scan Function:

T 144.000- 147.995MHz

E 144.000- 145.995MHz

TE1 136.000- 155.000MHz

TE2 150.000- 173.995MHz

T 118.000 - 135.995MHz (AM), 136.000 - 173.995MHz (FM)

E 144.000 - 145.995MHz (FM)

TE1 136.000 - 173.995MHz (FM)

TE2 136.000 - 173.995MHz (FM)

Standard 50 Tones

Optional 50 Tones

Electret Cond* with DTMF

5, 10, 12.5, 15, 20, 30, 50kHz steps, user adjustable

50Q unbalanced

13.8 V DC ± 10%

RX - Squelched: less than 800mA

TX - High: approx. 10.5A, Low: approx. 3.5A

141mm(W) x 41mm(H) x 154mm(D) (without projections)

approx. 0.86kg

50 Channels plus CALL channel; each stores RX; TX offset,

CTCSS encode, optional CTCSS decode and alphanumeric display

information

Alphanumeric, English and Cyrillic alphabets, numbers 0-9, figures,

up to 7 characters; backlit LCD

1000, 1450, 1750, 2100 Hz

30 to 450 seconds; selectable in 30 second increments

Available - Requires Optional EJ20U CTCSS Tone Decode Unit

0-15 seconds

Busy or Timed; Up or Down, memory or VFO

2) Transmitter

Output Power (approx.):

Emission:

Modulation System:

Max. Frequency Deviation:

Spurious Emission:

Operations:

TX/RX Offset Range:

High 50W / Low 5W (T/E), High 35W / Low 5W (TE1/TE2)

F3E FM

Variable Reactance Frequency Modulation

± 5kHz

-60dB or under below carrier

Simplex or Semi-Duplex Modes

From 0 up to ± 99.995MHz (full tuning range of radio)

Offset may be saved as part of information stored in any memory

channel

Page 3

3) Receiver

Receiving System:

IF Frequencies:

Sensitivity:

Selectivity:

Audio Output:

Speaker Impedance:

Specifications are subject to change without notice or obligation. Performance specifications apply only to

transmit bands. Names of certain products mentioned in this catalog are used for identification purposes only

and may be trademarks or registered trademarks of their respective company.

Dual Conversion Superheterodyne

First: 30.85MHz; Second: 455kHz

12dB SINAD -15dB|i

More than ± 6kHz at -6dB; Less than ± 15kHz at -60dB

More than 2.5 Watts @10% distortion

8£2

Page 4

CIRCUIT DESCRIPTION

1) Receiver System

1. Antenna Switching Circuit

(Main unit)

The signal from the anlenna is input to RF amplifier circuit passing through the 5

stages low-pass filter (L15 ~ L18, C76 ~ C80, C148), the anlenna switching circuit

(D9, D11, L14, C63), T type high-pass filter (L11, LI 2, C57, C64, C58, C59) and

band switch circuit (D20 T, E version only). The antenna switching circuit uses XI4

diode switch circuit.

2. RF Amplifier Circuit

(Main unit)

RF signal is amplified approximately 2GdB by RF amplifier, RF amplifier circuit

uses dual gate FET to get good inter-modulation characteristics. The RF amplifier

consists of vollage tuned band-pass filter (L1, L2, L4, L5, D2, D3, D5, D6) and RF

AMP (Q6). The signal is amplified after eliminating unwanted signals so that

image interference characteristics are improved.

3. 1st Mixer Circuit

(Main unit)

The amplified signal is converted into the first IF signal of 30.85MHz by mixer

circuit (Q5). Mixer circuit uses dual gate FET to improve multifrequency character

istics such as inter-modulation. The output signal from mixer circuit is led fo 1st IF

circuit.

4. Air Band Circuit

(Main unit I T, E version)

The output signal from band switch circuit is led to low-pass filter circuit (L7, L8,

C55, C56) and input to RF amplifier circuit (Q11). There the signal is amplified

approximately 20dB and input to the mixer circuit.

5.1st IF Circuit

(Main unit)

The output 1 st IF signal from mixer circuit is led to crystal filter XF1.

Unwanted frequency band of IF signal is eliminated by a crystal filler. The result

ing signal is led to the 2nd IF amplifier, and the signal is output to 2nd IF circuit.

6. 2nd IF Circuit and Detector Circuit

(Main unit)

The 1st IF signal is led to 2nd mixer circuit of IC1, then it is converted into the 2nd

IF signal (455kHz) by 2nd local signal. IC1 has the 2nd mixer, 2nd local oscillator

circuit, quadrature detector circuit and AM detector circuit. The 2nd local oscillator

oscillates 2nd local signal (30.395MHz). The 2nd IF output signal from mixer (pin

3 of IC1) circuit is led to ceramic filler {FL1). Unwanted frequency band of 2nd IF

signal is eliminated by a ceramic filter. The resulting FM signal is led to the limiter

amplifier (pin 7 of IC1) circuit and quadrature deteclor circuit (pin 11 of IC 1 and

ceramic discriminator Xt), and the 2nd IF signal is converted to AF signal. The FM

AF signal is output from pin 12 of 1C1 to AF circuit. The AM signal is input to AM

detector circuit (pin 5 of IC1), and the AM AF signal is output from pin 13 of IC1.

Page 5

7. AF and Mute Circuit

(Main unit)

8. Squelch Circuit

(CPU unit)

2) Transmitter System

1. Microphone Amplifier Circuit

(CPU unit)

The AF signal from IC1 is filtered by the low-pass filter amplifier (Q2) and led to the

high-pass filter amplifier (Q1), and output to the AF gain volume. Q3 and Q4 are

switched ON/OFF by AFC signal from CPU, then AF signal is muted when the

squelch is ON.

IC1 has the noise amplifier, rectifier circuit and comparator circuit. The noise signal

from pin 12 of IC1 is input to the noise amplifier (pin19 of IC1) and passed through

buffer amplifier (Q28), rectified by D8, then it is input to comparator circuit (pin 21

of IC1). When the noise signal is decreased by the receiving signal, the compara

tor output SD becomes low.

The voice from external microphone is amplified by the microphone amplifier

(Q303), and passed through the microphone mute circuit (Q304), the signal is

input to the microphone gain potentiometer (VR3) in the main unit.

2. Limiter Amplifier Circuit

(Main unit)

3. Modulation Circuit

(VCO unit)

4. Drive Amplifier Circuit

(Main unit)

5. RF Younger Amplifier Circuit

(Main unit)

The signal from microphone gain potentiometer (VR3) is amplified by limiter

amplifier and low-pass (IC4). The resulting signal is passed through the modula

tion adjustment potentiometer (VR4), then input to VCO unit. IC4A is limiter

amplifier with pre-emphasis characteristics. IC4B is low-pass filter.

The adjusted AF signal in VR4 is led to the VCO unit. The frequency modulation is

executed when the audio signal is supplied to the D207.

The signal from VCO unit is input to the drive amplifier (IC3). IC3 has high gain of

approximately 30dB and high level of approximately 10dBm wide band amplifier.

The signal from IC3 is passed through diode switch D12, and input to younger

amplifier Q13. Q13 has approximately 15dB gain and output level is 400mW. The

output signal of younger amplifier is led to the PA amplifier (IC2).

Page 6

6. RF Power Amplifier Circuit

(Main unit)

7. Antenna Switch Circuit

(RF unit)

8. A PC Circuit

(RF unit)

IC2 is the power module, which obtains stable output power (50W T/E, 35W TE1/

TE2) within the band. The signal of younger amplifier is amplified by the PA

amplifier (IC2), and then led to the antenna switch circuit.

When transmitting, D11 and D9 are ON in the antenna switch circuit, L14 becomes

parallel components. This causes the output signal of IC2 not to go to the RX

circuit. The signal is led to the antenna connector passing through the low-pass

filter (L15 ~ L18, C76 ~ C80, C148).

When the TX signal is passed through the low-pass filter, matching voltage and

mismatching voltage are detected by the D14 and D15. When the antenna

impedance is 50£2, the detected voltage of D14 and D15 are minimum. But when

the antenna impedance is not 50ft, the detected voltage becomes higher. The

detected voltage is passed through the power setting potentiometer (VR1), and the

signal is amplified by Q17, Q16 and Q14. The transmitting power is controlled by

the voltage of V1 (IC2) and collector voltage of Q13. When the temperature of the

unit goes high, the powerdown circuit (R104, TH2) prevents the device from being

damaged.

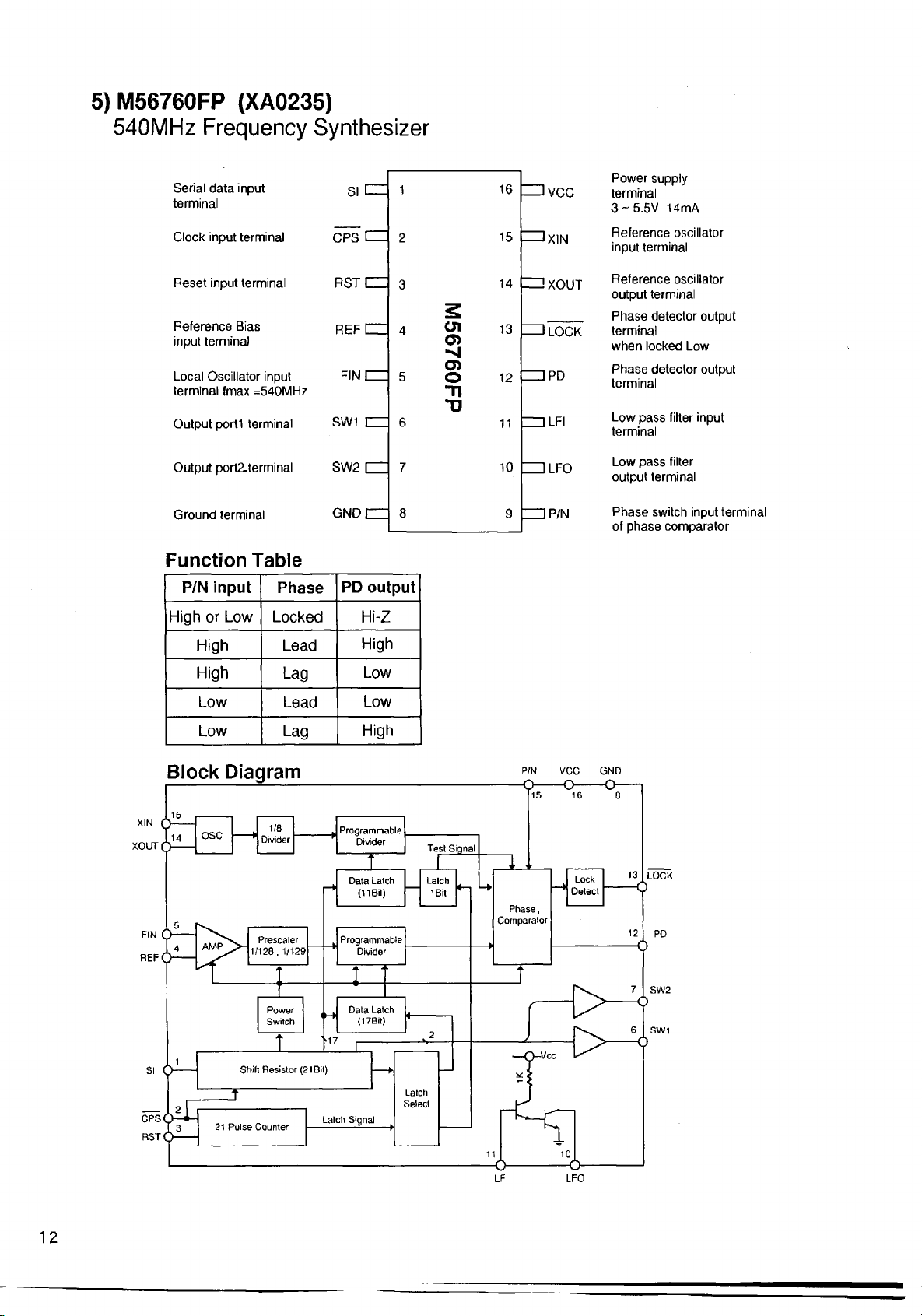

3) PLL Circuit

1. Summary

2. Reference Oscillator Circuit

(Main unit)

3. Loop Filter Circuit

(VCO unit)

4. VCO Circuit

(VCO unit)

The PLL circuit uses PLL IC (IC201) equipped with built-in dual modulus prescaler.

The PLL IC serial data is sent from CPU.

The VCO output frequency divided by N is compared with reference frequency in

the phase comparator.

The reference frequency is obtained by X3 (12.8MHz), and its output is led to the

VCO unit.

The phase error of phase comparator is integrated to DC voltage by loop filter

circuit, and supplied to D201, D202 of varicap diode jn VCO unit. The time

constant of the active loop filter (consisting of Q202 and Q210) is determined by

C211, C212, R228, R210. The output is passed through the lag filte r (R213,

C208), and input to VCO unit.

The circuit is the Hartley oscillator circuit (Q201), and the signal is output passing

through the buffer amplifier (Q204). C247 is switched by D205 to vary the capaci

tance, and the oscillating frequency range is shifted.

Page 7

4) Terminal function of CPU

No.

1 AN7 SD

2 AN6 SMT

3 AN5

4

5 P63

6 P62

7

8 P60

9

10

11

12

13

14

Nam e

P64

P61

P57 AM 0 AM/FM selection AM FM

TOUT

P55

CNTR TBST

P53 T8 0

P52

Pin Name I/O Description

TON1 0 Tone output 1 Pulse

TON2

TON3

TON4 O

BEEP 0

- HL

STB2

TICD

H L H iZ

I

SD signal input

I S meter signal input Analog

BP1 I Band plan Analog

I

UL

Unlock input Unlock

0 Tone output 2

0 Tone output 3 Pulse

Tone output 4

Beep sound output, SCR ON-OFF Pulse

TX, Squelch level H/L Power

0

0 Tone burst output / microphone mute

TX power supply control TX

0ITone unit strobe

Tone unit detection input

Squelch

Signal

Pulse

Pulse

Low

Low

RX

Pulse

None

Pull UP

No signal

Lock

r

High

High

TX. Pulse

OFF

Normal

Equipped

15 P51

16

17

18

19 TXD

20 RXD

21

22 INTO

23

24

25 RST

26

27

28

29

30 VSS

31 P27

32

33 P25 DOWN

34 P24 KEY 1

35

INT2 RE2

P47

P46 DATA 0

INT1

P41 SQL 0

P40 TSQD I

P71

P70

XIN

XOUT

P26

P23

STB1

CLK 0

CTX

CRX

RE1

BU

RST

SCL

SDA

XIN

XOUT

GND I

PTT

UP

KEY 2

0 PLL strobe permitted

I Rotary encoder down input OFF

Clock signal output

Data signal output

0 Data output for the cloning mode Pulse

I

Data input for the cloning mode

I

Rotary encoder up input OFF

I

Backup signal input

AF mute Mute

Tone signal detection input No Tone

I

Reset signal input

0 Clock input for E2PROM

10 Data input for E2PROM Pulse

I

Internal clock input

0 Internal clock output

GND

I

PTT key

I

UP key

I

Down key OFF

I Key 1 H/L

I

Key 2 SET OFF ON

Pulse

Pulse

Pulse

Normal

at work

Pulse

OFF ON

OFF

OFF ON

Inhibited

ON

ON

Backup

Tone

OV

ON

ON

o

o

Normal

o

o

o

o

o

Page 8

No.

Name Pin Name I/O

Descriptio n H

L H iZ

Pull UP

36

37

38

39 S31

40 S30 S30

41

42

43

44

45

46

47 S23

48

49 S21 S21

50

51

52 S18

P22

P21 KEY 4

P20 KEY 5 I

S29 S29 0 Segment 29 output

S28

S27

S26 S26

S25 S25

S24

S22 S22

S20

S19

KEY 3

S31

S28

S27 0

S24 0 Segment 24 output

S23 0 Segment 23 output Pulse

S20

S19 o

S18 o

I

Key 3 CALL OFF

I

Key 4 V/M

Key 5 FUN

0

Segment 31 output

0 Segment 30 output

0

Segment 28 output

Segment 27 output

0

Segment 26 output

Segment 25 output

0

0 Segment 22 output

0 Segment 21 output Pulse

o

Segment 20 output Pulse

Segment 19 output Pulse

Segment 18 output Pulse

OFF

OFF

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

ON

ON

ON

o

o

o

53 S17

54

55 S15 S15

56

57 S13

58

59 S11 S11

60 S10 S10

61

62

63

64

65 S5

66

67 S3 S3 o Segment 3 output Pulse

68

69 S1

S16 S16

S14

S12 S12

S9 S9

S8 S8

S7

S6

S4 S4

S2

S17

S14

S13 0

S7

S6 o

S5

S2

S1 0 Segment 1 output

Segment 17 output

o

0 Segment 16 output Pulse

Segment 15 output

o

Segment 14 output

0

Segment 13 output Pulse

Segment 12 output Pulse

0

0 Segment 11 output

0 Segment 10 output Pulse

Segment 9 output

0

0 Segment 8 output Pulse

o Segment 7 output Pulse

Segment 6 output Pulse

Segment 5 output

0

Segment 4 output

o

o Segment 2 output

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

Pulse

70

SO SO

o

Segment 0 output Pulse

Page 9

No.

Name

Pin Name

I/O Description H L HiZ

Pull UP

71

72 VREF VREF I

73

74

75

76

77

78 VL3

79

80 VL1 VL1 I LCD power supply input

vcc

AVSS

COM3 COM3

COM2

COM1

COMO

VL2 VL2

VDD I

GND I

COM2 0 LCD common 2 output

COM1

COMO 0

VL3

Power supply

Reference voltage input

GND

O LCD common 3 output

0 LCD common 1 output

LCD common 0 output

LCD power supply input

I

I

LCD power supply input

Pulse

Pulse

Pulse

Pulse

9

Page 10

SEMICONDUCTOR DATA

1) AK2341 (XA0239)

CTCSS Encoder/Decoder

Pin

Pin

No.

1

2

RXINO 0 AMP2 Output

3 TXINO

4

RXOUT 0

5

TXOUT

6

7

8

9

10

11 SDATA

12 SCLK

13

DETOUT

14

15 VSS

16

17

18

19 TLINO

20 RXTONE

21 TXTONE

AGNDIN

22

23

24 BIAS

I/O

Name

RXIN I

o

TXIN I

0

VDD

XOUT

STB

-

I

XIN

Crystal Terminal (3.6864MHz)

o Crystal Terminal (3.6864MHz)

I

I

I

DCS

I

0 Tone Detection Output (Detect: Low)

-

DREF I Tone Detection Level Adjust Input

TLINP

TLINN I

I

RX Tone Signal Reference Input

o

o

o

I Analog Ground Input

AGND

0

I

Function

RX Signal Input

AMP1 Output

TX Audio Input

RX Audio Output

TX Audio Output

Power Supply (1.8 ~ 5.5V)

Strobe for Serial Data

Serial Data

Serial Clock

DCS Input

Ground

RX Tone Signal Input

AMP3 Output

RX Tone Signal Output

TX Tone Signal Output

Analog Ground Output

Bias Input

RXIN

RXINO

TXINO

TXIN

RXOUT

TXOUT

VDD

XIN

XOUT n z

STB

SDATA

SCLK

d =

n z

n z

n z

n z

n z

n z

n z

n z

[Z Z

n z

1

2

3

4

5

24

23

22

21

20

Z U

= ]

Z Z 2

= □

zzn

BIAS

AGND

AGNDIN

TXTONE

RXTONE

>

6

7

8

9

7s

PO

19

Z D

TLINO

CO

18

17

16

10

11

12

15

14

13 =Z1

Z □

Z Z 3

=□

=□

= l

TLINN

TLINP

DREF

VSS

DETOUT

DCS

Block Diagram

10

Page 11

2 ) AN78L05M (XA0238)

5V Voltage Regulator

3) LA4425A (XA0410)

5W Audio Power Amplifiers

u u u

Output Common Input

AN78L05M

4) M5218FP (XA0068)

Dual Low Noise

Operational Amplifiers

Output 1 1

Inverting Input 1 2

Non Inverting Input 1 3

Power Supply Minus 4

1 2 3 4 5

8 Power Supply Plus

7 Output 2

6 Inverting Input 2

5 Non Inverting Input 2

Page 12

5) M56760FP (XA0235)

540MHz Frequency Synthesizer

Serial data input

terminal

Clock input terminal

Reset input terminal

Reference Bias

input terminal

Local Oscillator input

terminal fmax =540MHz

Output p ortl terminal

Output port2-terminal

Ground terminal

Function Table

P/N input

High or Low

High

Phase

Locked Hi-Z

Lead

S l t =

ere n z

RST C Z

REF tZ Z

FIN n z

swi n z

SW 2 I—

GND I

----

PD output

High

1

2

3

16

15

14

=]v c c

XIN

ZZÏ XOUT

2

CJ1

4

o

o>

5

o

13

12

H D LOCK

ZZÏPD

T I

"U

6

7

8

11

10

9

=□ LFI

ZZ] LFO

= D P /N

Power supply

terminal

3 -5.5 V 14mA

Reference oscillator

input terminal

Reference oscillator

output terminal

Phase detector output

terminal

when locked Low

Phase detector output

terminal

Low pass filter input

terminal

Low pass filter

output terminal

Phase switch input terminal

of phase comparator

XIN

XOUT

FIN

REF

CPS

RST

High

Low

Low

SI

Lag

Lead

Lag

Low

Low

High

LFI LFO

Page 13

6) M67746 (XA0412)

144 - 148MHz 60W

RF Power Module

*o

c

3

D

CO

c

I ?

Z E

3 O

CLO

C CO

M67746

12 3 4

>

uq

o

cvi

□

a>

O)

«

c

to

R-e

Q. ^

4-*

CO

7) M68702H (XA0444)

1 50 - 175MHz 60W

RF Power Module

— *>

9-in

Q ^

s !

il £

$

o

CO

ro

D C

f i

o .£

(TE2)

C

~o

c

Supply voltage Vcc 17

3

Total current

Input power

Output power

Operation case temperature

Storage temperature Tstg

Zg=ZI=50Q

Supply voltage

Total current

Input power

Output power

Operation case temperature Tc(op)

Storage temperature

Zg=Z I=50ii

Ratings

Ratings

Symbol

Icc 20

Pin (max)

Po(max)

Tc(op)

Symbol Ratings

Vcc

Icc

Pin (max)

Po(max)

Tstg -40 t o +110

Ratings

600

70

-30 to +110

-40 t o +110

17

20 A

600

75

-30 t o +110

Unit

V

A

mW

W

°C

°0

Unit

V

mW

W

°C

°C

8) M68702L (XA0445)

135 - 160MHz 60W

RF Power Module

(TE1)

Ratings

Supply voltage

Total current Icc 20

Input power

Output power Po(max) 75

Operation case temperature

Storage temperature Tstg

Zg=ZI=50i2

Symbol

Vcc

Pin (max) 600

Tc(op) -30 t o +110

Ratings

-40 to +110

Unit

17

V

A

mW

W

°C

°C

Page 14

9) MC7808CT (XA0082)

8V Voltage Regulator

Test Circuit

10) RH5VL32AA-T1 (XA0198)

C-MOS Voltage Detector

Equivalent Circuit

.VDD

OUT

vss

11) RH5VL45AA-T1 (XA0208)

C-MOS Voltage Detector

Equivalent Circuit

lv d d

U Ü u

OUT VDD VSS

RH5VL32AA

14

OUT

m i ' i t

OUT VDD VSS

RH5VL45AA

VSS

Page 15

12) TK10930VTL (XA0223)

Narrow Band FM IF IC

IF i n O

1 0 .7 M H z

/ 1

z 1-

3

C L .

Z n

ü.

cc

51

Param ete r S ymbol

Sup ply voltage

Pow e r dissipation

Stora ge te m p e rature

Operating tem p erature Top

Ope rating v o ita g e

Operating frequency

Param ete r

Su pply Current 1

Su pply Current 2 1cc2

Mixer C o nvers ion G ain

Mixer tnput Impedan c e

FM

Limiting Sens itivity

Outp u t Vo ltage Vo1

Distortion

Output Im pedanc e Zo 800 n

Filter G ain

Sca n Control Hi Voltage SH 2.3

Sca n Control Low Voltage SL

Squ elch H ysteresis

S m eter Output V o ltage SO 0.0 5

S m eter O utpu t Voltage S1

S m eter Output Vo ltage S2 0.7

S m eter Outp u t Vo ltage

S mete r O u tput Völtag e S4

S m e ter Output Voltage S5 1.8

AM

Se nsitivity US

Output Voltage

Distortion-1

Disto rtio n-2

S/N

AM OFF Vo -0.3 0.3

Vcc m ax

Pd 400

Tstg -5 5 -+ 1 5 0

Vo p

(op

oy m oo i

Icc1 6.8 8.9

Mg

Mz

Lim it

THD1

Gf

Hys 30 mV

S3 1.2 1.8

Vo2

TH D2 1.0 2.0 % 1kHz, 30%, Vin=1m V

TH D 3 2.0 4.0

S/N

Ratings Un it

10.0

V

mW

°c

-3 0-+ 75

2.5 -8 .5

-6 0 M Hz

Min

85

30 38 dB Fin=30kHz, V o =100mV

0.05

1.6 2 .3

20 15 JiV

60 120 160

40

°c

V

Ratings

Typical

3.9

Max

5.3

20

3.6

2.0

150 230 m Vrm s 10m Vin +/-3kH z DEV

1.0 2.0 % 1 0mVin +/-3kHz DEV

0.5 0.9 V Vin=0.01mV, R S= 6 8 kfi

1.2

2.4

48

8.0

0.3

0.5

1.7

2.5 V

2.9 V

2.9

Ta=25°C Vcc=3V

Un it Condition

mA

No signal. AM O N

mA No signal, AM O FF

dB

KQ D C Te st

-3.0dB

tiV

lOm Vin

V Squelch inpu t=2.5V

V

Squelch input=0V

V Vin =0m V, RS=68kS2

Vin=0 .1m V, R S = 68k ii

V

Vin=1m V , R S = 6 8kii

Vin=1 OmV, R S=6 8 ki^

V

Vin=100mV, RS=68 ki2

required input level to gel

20mV rms output

mVrms

1kHz, 30% , Vin= 1m V

1kHz, 30%, Vin=1 mV

%

dB 1kHz, 30%. Vin=1 m V

%

4 7K A F O U T P U T (A M )

r - 0

F M A F O U T A F O U T P U T (F M )

i r °

Page 16

13) nPC2710T (XA0449)

RF Amplifier

Parameter

Supply voltage

Circuit current

Power gain

Saturated output power

Noise figure

Upper frequency (-3dB)

Isolation ISL

Input return loss

Output return loss RLout Vcc=5V, f=500MHz

Gain flatness aGp

Test Circuit

______

Symbol

Vcc

Icc

GP

Po(sat)

NF Vcc=5V, f=500MHz

fu

RLin

Vcc

Vcc=5V, no signal

Vcc=5V, f=500MHz

Vcc=5V, f=500MHz, Pin=-8dBm

Vcc=5V, Reference freq. =100MHz

Vcc=5V, f=500MHz

Vcc=5V, f=500MHz 6 dB

Vcc=5V f=0.1 ~ 0.6GHz ±0 .8

Condition

GND

GND Q T

Input

Ratings

5.0

22

33

+13.5

3.5

1000

39

12

Top View

O

Unit

V

mA

dB

dBm

dB

MHz

dB

dB

dB

Output

1F| GND

Vcc

14) 24LC16B (XA0351)

16K bits CMOS Serial EEPROM

Block Diagram

__________________

WP

AO

A1 \z z

A2

Vss

n z

n z 3

Pin Name

Vss

SDA

SCL Serial clock

WP W rite protect

Vcc

A0, A 1, A2

1

IO

2

-1 ^

1“

O

o>

4

GND terminal

Serial address/data I/O

+2.5 V -5.5V power supply

No connection

CD

Description

8

7

6

5

H3

z n

Z Z ]

Z Z i

Vcc

WP

SCL

SDA

Page 17

1 5) Tra n s i s to r , Diode a n d L ED O u tl in e Dr a win g s

T o p V i e w

Page 18

16) LCD

LCD Pattern

EEia_ENC 4 D jEC 6^ +

M M l l y / l ly / l w ly / l l y / l M

i m ii s i m r n r n m m n r ,

lo w m m i

LCD connection table

No. COM.O COM.1 COM.2 COM.3 No. COM.O

1

2 COM.1 22

3 COM.2

4

5

6

7

8

9

10

11

12

13 4a 4b 4c

14

15

16

17

18

19

20

COM.O

COM.O

1j

1a

2j

2a

3j

3a 3b 3c

4]

5j

5a 5b

6j

6a

7j

7a 7b

• m

1k

1b 1c LOW 27

2k

2b 2c BUSY 29 DEC

3k

4k

5k

6k

6b 6c

7k

8f 8e

ig

2g

3g

4g

5g

5c

6g

7g

7c

COM.3

11

21 28

31

• (D

41

• (2)

51

■ (3)

61

■ @

71

FULL

8d

21

23 9a 9b

24

25

26

30

31

32

33

34

35 ENC 2f

36

37

8a 8b

M

7i

—

6i

+

5i

4i 4h

1 ©

3i

1 ©

2i

1i

FUNC

COM.1

9f

7h

7f

6h 6n

6f

5h

5f

4f

3h

3f

2h

1h

1f

COM.2 COM.3

8g

9e 9d

9g

7n

7e 7d

6e

5n

5e 5d

4n 4m

4e

3n 3m

3e 3d

2n

2e 2d

in

1e

8c

9c

7m

6m

6d

5m

4d

2m

1m

1d

18

Page 19

E XP L O DE D V IEW

19

Page 20

3 ) To p and Fr ont View s

Screw Torque: 5kgcm

AE0014

KZ0047Z

UX1047

FG0040

AE0014

ES0017

EM0152

YZ0062

UA0037Z

AE0014

AE0014

[T. E: XA0412 (M67746)

TE1: XA0445 (M68702L)

1.TE2: XA0444 (M68702H)

KZ0039A

AV0001

KZ0040A

FP0004

AD0010 AD0010

FF0028

AV0001

AV0001

NB0063Z

AE0014

KZ0045Z

AE0014

A t O U 1 4

KS0041CZ

Page 21

Ver.

g ¡g

1

T/E

2

T/E

T/E

T/E

? E o o

| 5 2 s s 5 s s s i |

i - I 3 I | |

1SV215TPH4

DTZ5.1BTT11

1SV215 TPH4

1SV215TPH4

DA204U T106

1SV215TPH4

MI4U/

Parts Name

1

Diode

Diode

Diode

XD0165

XD0132

XD0132

01

D2

D3

t D j D I D I o U i o O i o O U j o j j )

■So

ccz

Descriptor

Parts No.

OA204U T106

Diode

Diode

Diode

Diode

Diode

XD0132

XD0130

XD0132

XD0130

XD0013

D8D9

04D506

w g 5 § S ro 0

o o o o i-oPoFi-'ö^o

a s

ü ü ü ü Î ü h ü Î h d P ü P o g ü ü ü ü ü d ü ü ü d ü ü ü P ü ü ü ü u ü ü ü o u ii o ü i ü l

g o. o. .

9

. a. cl g g. g. g. g o a Ç g. 'S .g. a. .g. o. g ,g .g. p. a a a g a ö a o. o. a g .g .o. g a a a a a a o. n o. q

s g

ü O üü ü ü ü U ü u u û iü n iü iD ü O ü S ü U ü Ô â o u u u iD ü ü ü ü o o ü ë o u u o ü Ô a ü

________________________aoocjooooaooooooooooooooooooooooüoo _ _ _ _ _ ____

8 8 8 8 8 f e 8 8 ? iS 5 ? S S t S ? 8 § 5 a a a 8 8 8 a 8 s 8 8 S 8 8 ! 5 S 8 § 5 5 ? 5 ? ^ ? a 5 a a J ! 5 gs

ooooooo oo oo ooooooo ooooo ooooo ooooo ooooo ooooo ooooo ooooo o

1SS355TE17

DTZ5.1BTT11

DAN235UT 106

MI407

Diode

Diode

Diode

XD0165

XD0013

XD0246

D1Q

D12

0 1 1

o ü

bnbgäS nnfiSflSnnMBflociBnnSflnM flnnnnn än

1SS355 TE17

1SS355 TE 17

MA742 TX

MA742TX

DA204U T106

G3B

1SS355 TE 17

DA204UT 106

DAN235UT 106

DAN235UT 106

KBF-455RL-12A

M67746

TK10930VTL

M68702H

UPC2710T

M6S702L

M5218AFP/600E

2 5 I S

0 1

0 1

0 1

0 1

0 1

Diode

Diode

Diode

Diode

Diode

Diode

Diode

Diode

Diode

Diode

Diodo

Paramir CîI+a»

XD0254

XD0250

XD0250

XD0254

XD0254

XD0130

XD0107

Dl3

D14

D15

D16

D17

D18

D19

o

. 5

n S Eü ïî

8 8 8 S

XD0130

XD0246

XD0246

XD0254

XC0022

XA0223

2 1

D20

D

D22

D25

FI 1

5 8 8 0 8 3

0 1

1C

1C

XA0412

XAQ444

XA0445

XA0449

XA0068

XA0082

XA0410

8 0

H üîiOSÏÏSSS

0 0

S S

Jack

Coil

Coil

Coil

Coil

UJ0038

QA0084

QA0084

QA0043

QA0084

8 S S S § S § § S § u § ^ m § S S

Ü O O O Ü O O O O O K ü C tü Oü O Ü --

7 7 7

1

Coil

QA0084

S ï ï l i S g l i S i

chip L. 1

chip L 1 Chip L 1 chipL. 1Coil f

QC0067

QC0065

Coil f

Air Core Coil \

QC0065

QC0065

QKA85A

QKA85A

ÛKA35D

UÛ

L11

L13

L12

o o o o o

_ £ £ £ !c

O O O O O

Mr Core Coil f>

% Core Coil ^

QKA45E

QKA45E

1

LM

L15 I

— o. a a

33Ü3

'ir Core Coil

Mr Core Coil N

Mr Core Coil K

:hip L f\

:hip L N

QKA4SE

QKA45E

3KA45E

3C0039

X0063

1

L17 (

Lia 1L19 <

L16 (

120

1

Ver.

T/E

T/E

T/E

2

T/E/12T/E/1

1

T/E

2

2

T/E

LJ UJ LU LU LLf U

? ^

0

<d <o t

<cac

1

1

ÎÎÎÎÎÏ

0

c

/3

Parts Name

C1608CH1H680JTA

C1608JB1H102KTA

C1608CH1H470JTA

.........i .................Î . 1

OO OO OO O SO OO OO OO O O O O O PO PO g 1

.9- .9- .9* .0- .0- .9- .9 $ 9- 9- 9- a a. a a o. a a a

oo o o o oo iB o o oo oo oo oo oo Q iS c D o o t

Description

S S ® “ ï ! 2 ï § n ; S ï n n ” î î! 2 8 S !! ÎS i? n ® 1 8 ! S (2 S S 8 S g § S Ï S 8 8 8 8 g S ï n S ^ S S ! 3 8

o o o o o o o t o a o o o o o o o o o o o « o r t o o o O o o Q o o o o o o o o o o o o o r t c o o o o o o o r o O c j

npiMMDcinonnonnnrtniortn'tooonioioininiiiiiiiiimiiiiflnionMnrtonnoonnnnnnofia

Parts No.

OO O ÜO O OÜ O OO O OO O OÜO O OO O OOU OOO O OO O OOO O OO O OOO ÜOO O OO O OOO C JO

ccz

C53

C54

C55

C1608CH1H270JT A

16MV 47HW+TS

C1608CH1H270JTA

C1608CH1H150JTA

C1608CH1H470JTA

0

C59

C57

C58

C56

C1608CH1H100CTA

C1608JB1H102KTA

C1608CH1H150JTA

C1608JB1H102KTA

C1608CH1H121JTA

C1608JB1H102KTA

C1608JB1H102KTA

C1608CH1H180JTA

C1608CH1H150JTA

d o

C60

C61

C63

C64

C62

C68

C65

C66

C68

C67

C1608CH1H150JTA

C1608CH1H120JTA

C69

C69

16MV 10SW+TS

C1608JB1H102KTA

GRM42-6X7R102K500PT

. 9 8 9 - 6

C70

C72

C71

a § [

C73

16MV 1QSW+TS

o o o ^ o o o o o ü o o o o o o Ë - u o o o o o ü o o P u o o u o o o F o u ^ u i- o o o o o o o

!

1

0

CL'£Q.

i

UJOUJ

O

£

0 0 O

d d

CL

tza!c

d d

d d d d d ddd d

2

a

a

.9-

g

2a.Jr

c .

UJ

Ü

6

O

O

a

'sz ÈCLC .

0 O O Ü 0

0

Q-

S laÈ ÈCL-C

0

0 1 -

O

w <n v) t

3 0 S S S c

) O 0

j 0 o 0 0 t

RCC05SL180J-L46AE

C160BJB1H102KTA

c or d: a: cc

or*r*ftcc*i

j d d d d c

¿ 0 0 0 0

? S E C S? !

D tl II I I <

> O ü

C75

C74

C75

C75

d d d ddd d

CL

CLicCL

a

£

È

O 0

'n

U O

H

O O

uü-LHunc

0 0

c.

RCC05SL120J-L46AE

0

RCC05SL180J-L46AE

RCC05SL120J-L46AE

«

0

ü C

Ceramic C.

Ceramic C.

Ceramic C.

C76

C78

C79

C80C80

|C77

C80

^ § S ë © S S §

d0!

a

a

a a

s :

a6a

SZ

JZ ’j z

O a 0 O O O O 0

's i

C1608JB1H102KTA

ChipC.

C81

d d

a

■£

C1608JB1H102KTA

Chip C.

C82

d d

a

.9-

C1608CH1H220JTA

C1608CH1H220JTA

C1608JB1H102KTA

Chip C.

Chip C.

ChipC.

C84

C85

C83

d d Ü3d d

CLsza

£0£a£

O O O O

16MV 10SW+TS

C1608CH1H020CTA

C1608CH1HQ20CT A

16MV 10SW+TS

C1608JB1H102KTA

C1608CH1H010CTA

C1608CH1H01OCTA

hip C.

Chip C.

Chip C.

Chip C.

C

C88C89

C86

C87

C1608JB1H102KTA

C1608JB1H102KT A

C1608JB1H103KTA

Electrolytic C.

Electrolytic C.

Chip C

Chip C.

Chip C.

Chip C.

C90

C91 ,

C93

C92

C94

C95

o oS s S ^ S S S S S S S

ë

0

d ddd d d d

d J-

a

9-

9-

.9-

i

sz

IZ

JZ

IZCLJZCL£ È

UJ

0

OOO

O

o

16MV 10SW+TS

16MV 10SW+TS

C1608JB1H102KTA

C1608JB1H222KTA

C1608JB1H102KTA

Electrolytic C.

Electrolytic C.

Chip C.

Chip C.

Chip C.

C98

C99

C96

C100

IC97

DR140T: T, DR140E: E. DR140TE1: 1, DR140TE2: 2 21 22 DR140T: T, DR140E: E, DR140TÉ1: 1, DR140TE2:

CL

CL

CL

Q.

r .

■C

£a£

O 0

U

6

O

PARTS LIST

«_» vj u vi i’/ vj u v* v j vv »V w v; *•/ v; iv iv

OJniUZ>DZ)UJDDD3333Z)Z)33

O Ü Ü O O O O O O O Ü O O O O O O O

o ö o o ö o ö o o o ö ü o o o o o o o ö ö

O ' - N O ' I l I l l I l S l D f f l Q r

8

.. McocOCTconoroDCTMOtoMo

CO ’’t

8 8

iQNainNSSu)inin

oööo o o c m o S S o o o ö ö

U^DD3DWDDD3Z)Z)3OT

ooaoooooouooooo

S C O O l O i - M 'f in il lS B O l O ' -M

80833333 3 3 33888

IW U U (V CI V/ IV l'J i 1

riiuawurJisDiJuu

ooooooooooo

21

Page 22

ro

ro

Main Unit

Parts No.

No.

L21

QKA95D

L21 QKA75G

122 QC0063

QLD012 Coil

L23

Q1 XT0095

XT0095

Q2

XT0095

03

XT0095

Q4

XE0028

Q5

XE0028

Q5

Q7 XT0096

Q8 XU0131

XE0021

Q9

Q10

XU0152

XT0096

Q11

XU0112

Q12

XT0084 Transistor

Q13

Q14 XT0112

Q15

XE0021

Q16

XT0095 Transistor 2SC4081 T106R

Q17 XT0094

Q18

XT0081 Transistor 2SB1132T 100Q

Q19

XU0131 Transistor

020

XU0131 Transistor

Q22

XU0131

023

XT0148

024

XU0152

025

XT0095

026

XU0131 Transistor

027

XU0152

Q28 XT0095 Transistor 2SC4081 T106R

Rt

RK3026

R2

RK3030

R3

RK3026

R4

RK3042 Chip R.

R5

RK3043

R6

RK3043

R7

RK3026

RK3026

R8

RK3071

R9

R10 RK3054 Chip R.

R11 RK3026

R12

RK3058

R13

RK3071

R14

RK3038

315

RK3058 Chip R.

R16

RK3058 Chip R.

Rl7

RK3057 Chip R.

R18 RK3054

R19 RK3034

RK3064

R20

R21

RK3042

Description

Air Core Coil

Air Core Coil

Chip L.

Transistor

Transistor

Transistor

Transistor

FET

FET

Transistor

Transistor

FET

Transistor

Transistor

Transistor

Transistor

FET

Transistor

Transistor

Transistor

Transistor UMC5TR

Transistor

Transistor

Chip R.

Chip R.

Chip R. ERJ3GSYJ101V

Chip R. ERJ3GSYJ272V

Chip R. ERJ3GSYJ272V

Chip R.

Chip R.

Chip R. ERJ3GSYJ564V

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ102V

Chip R.

Chip R. ERJ3GSYJ471V

Chip R.

Chip R. ERJ3GSYJ222V

MR3.0 9.5T0.6

MR5.0 7.5T0.6

NL322522T047J

QL0012

2SC4081 T106R

2SC4081 T106R

2SC4081 T106R

2SC4081 T106R

3SK131V12-T1

3SK131V12-T1

2SC4099 T106N

OTC114EUT106

2SK880GR TE85L

UMC5TR

2SC4099 T106N

QTA114YU T106

2SC2954T1

2SS1292F

2SK880GR TES5L

2SA1576 T106R

DTC114EU T106

DTC114EU T106

DTC114EU T106

2SB1124-TD

2SC4081 T106R

DTC114EU T106

UMC5TR

ERJ3GSYJ101V

ERJ3GSYJ221V

ERJ3GSYJ222V

ERJ3GSYJ101V

ERJ3GSYJ101V

ERJ3GSYJ223V

ERJ3GSYJ101V

ERJ3GSYJ473V

ERJ3GSYJ564V

ERJ3GSYJ473V

ERJ3GSYJ473V

ERJ3GSYJ393V

ERJ3GSYJ223V

ERJ3GSYJ154V

Parts Name Ver.

T/E/2

1

E

T/E

T/E

T/E

T/E

T/E

Ref.

Parts No. Description Parts Name

No.

R22 RK3038

RK3054 Chip R.

R23

R24 RK3030

RK3045 Chip R.

R25

R28 RK3046 Chip R.

RK3062 Chip R. ERJ3GSYJ104V

R27

R28 RK3026 Chip R.

RK3054

R29

R30

RK3050

R31

RK3052

R32 RK3036

R33

RK3062

R34

RK3062

RK3021

R35

R36 RK3022

R37

RK3038

RK3042 Chip R.

R38

R39 RK3058 Chip R.

R40

RK3062

R41

RK3054

R42

RK3062 Chip R.

R43

RK3062

R44

RK3057 Chip R.

R46 RK3050 Chip R.

RK3026

R48

RK3074

R49

RK3047

R50

RK3034

R51

RK3066 Chip R.

R52

RK3074 Chip R.

R53

R54

RK3001

R5Ô RK3026

R56 RK4018

RK3014 Chip R.

R57

RK3026 Chip R.

R58

R59 RK3026

RK4024

R80

RK3014

R61

R62

RK0020

RK0028

R62

RK3017 Chip R.

R63

R64

RK3034 Chip R.

R65

RK3062

RK3017

R66

R68 RK0001

RK3031

R69

RK3031

R70

R71 RK3031

RK3031

R72

R73 RK3062

R74

RK3050

R75 RK3051

R76

RK3038

R77 RK3050

Chip R. ERJ3GSYJ102V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

ChipR.

Chip R. ERJ3GSYJ101V

Chip R. ERJ3GSYJ105V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ6GEYJ151V

Chip R.

Chip R. ERJ3GSYJ104V

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ271V

Chip R. ERJ3GSYJ271V

Chip R. ERJ3GSYJ271V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Ver.

ERJ3GSYJ223V

ERJ3GSYJ221V

ERJ3GSYJ392V

ERJ3GSYJ472V

ERJ3GSYJ101V

ERJ3GSYJ223V

ERJ3GSYJ103V

ERJ3GSYJ153V

5RJ3GSYJ681V

ERJ3GSYJ104V

ERJ3GSYJ104V

ERJ3GSYJ390V

ERJ3GSYJ470V

ERJ3GSYJ102V

ERJ3GSYJ222V

ERJ3GSYJ473V

ERJ3GSYJ104V T/E

ERJ3GSYJ223V

ERJ3GSYJ104V

ERJ3GSYJ104V

ERJ3GSYJ393V

ERJ3GSYJ103V

ERJ3GSYJ562V

ERJ3GSYJ471V T/E

ERJ3GSYJ224V

ERJ3GSYJ105V T/E

ERJ3GSY0R00V

ERJ3GSYJ101V

ERJ-12YJ220U

ERJ3GSYJ100V

ERJ3GSYJ101V

ERJ3GSYJ101V

ERJ-12YJ6S0V

ERJ3GSYJ100V

ERJ6GEYJ471V

ERJ3GSYJ180V

ERJ3GSYJ471V

ERJ3GSYJ180V

ERJ6GEYJ100V

ERJ3GSYJ271V

ERJ3GSYJ104V

ERJ3GSYJ103V

ERJ3GSYJ123V

ERJ3GSYJ102V

ERJ3GSYJ103V

T/E

T/E

T/E

T/E

2

T/E/1

DR140T: T, DR140E: E, DR140TE1: 1, OR140TE2: 2

Page 23

Ref.

Parts No. Description

No.

R78

RK3052 Chip R.

R79

RK4026

R80

RK3050

R81 RK3050

R82 RK3062

R83

RK3043

R84

RK3042

R85

RK3060

R86

RK3060

R87

RK3042

R88

RK3042

RK4034

R89

R90 RK3049

R91

RK3057 Chip R. ERJ3GSYJ393V

RK3062 Chip R.

R92

R93

RK3050

R94

RK3026

R95

RK3038

R95

RK3050

R97 RK3054 ChipR.

RK3Q23

R98

RK3030

R99

RK3062

R100

R101

RK3001 Chip R.

RK3044

R102

R1Û3

RK3050 Chip R. ERJ3GSYJ103V

R104

RK3001

R105

RK3053

RK3054 Chip R. ERJ3GSYJ223V

R106

R107

RK3033

R1Q8 RK3041

RK3046

R109

RK3044

R110

R111

RK3050

RK4034

R112

R113 RK3043 Chip R.

RK305Û

R115

RK3050

R116

RK3042

R117

R118 RK3001 Chip R.

R119

RK3Û42

R120

RK3042

R121

RK3001 Chip R.

R122

RK3042

R123

RK3042 Chip R.

R124

RK3001

R125

RK3062 Chip R.

R125 RK3050

R127

RK3050

R128 RK3038

R129

RK3058

R130 RK3026

R131

RK3038 Chip R. ERJ3GSYJ102V

R132 RK3067

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ222V

Chip R.

Chip R.

Chip R.

ChipR. ERJ3GSYJ101V

Chip R.

Chip R. ERJ3GSYJ103V

Chip R. ERJ3GSYJ560V

Chip R-

Chip R.

Chip R. ERJ3GSYJ332V

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ182V

Chip R.

Chip fl. ERJ3GSYJ332V

ChipR.

Chip R. ERJ-12YJ471U

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ222V T/E

Chip R.

Chip R. ERJ3GSY0R00V

Chip R. ERJ3GSYJ103V

Chip R. ERJ3GSYJ103V

Chip R. ERJ3GSYJ102V

Chip R. ERJ6GEYJ473V

Chip R.

Chip R.

Parts Name

ERJ3GSYJ153V

ERJ-12YJ101V

ERJ3GSYJ103V

ERJ3GSYJ103V

ERJ3GSYJ104V

ERJ3GSYJ272V

ERJ3GSYJ222V

ERJ3GSYJ683V

ERJ3GSYJ683V

ERJ3GSYJ222V

ERJ-12YJ471U

ERJ3GSYJ822V

ERJ3GSYJ104V

ERJ3GSYJt03V

ERJ3GSYJ102V

ERJ3GSYJ223V

ERJ3GSYJ221V T/E/1

ERJ3GSYJ104V

ERJ3GSYQROOV

ERJ3GSY0R00V

ERJ3GSYJ183V

ERJ3GSYJ102V

ERJ3GSYJ472V

ERJ3GSYJ103V

ERJ3GSYJ272V

ERJ3GSYJ103V

ERJ3GSYJ103V

ERJ3GSYJ222V T/E

ERJ3GSY0R00V

ERJ3GSYJ222V

ERJ3GSYOROOV

ERJ3GSYJ222V

ERJ3GSYJ222V T/E

ERJ3GSYJ104V

ERJ3GSYJ101V

ERJ3GSYJ274V

Ver.

1/2

T/E

1/2

T/E

T/E

T/E

Réf.

Parts No.

No.

R133

R01013

R134

RD1013 Resistor

R136

RK3052

R137

RK3054 Chip R.

R140

RH0039

TC1

CT0012

TH2

XSQ013

VR1

RH0108

VR2

RH0103

VR3 RH0060 Trim Pot

VR4

RH0103

VR5

RH0103

VR6

RH0061

X1 XK0001

X2 XQ005SA

X3 XQ0054Z

XF1

XF0014Z Crystal Filter UM1 30.85MHZ

SD0034 Earth Spring

UE0257

EHM45Z

DS0351

ADFM78

FP01C3Z

YZ0012

HK0408

HP0016

HP0035

HPO037

HU0069

HU0073

HU0075

PH0009

PK0063

PR0237

PS0242

PT0004A

ADUA38

FM0114

AJ0025

YZ0138 Adhesive Tape

FM0079 Wrench

EF0005 Fuse 15A

AE0Û12

AA0013

AJQQ03

AZ0009 Spring Washer

AZ0010

AN0002

Description

Resistor

Chip R. ERJ3GSYJ153V

Chip R.

Trimmer CTZ10AW

Thermistor

Trim Pot

T rim Pot

Trim Pot

Trim Pot

Trim Pot

Ceramic Oiscri

Crystal UM5 30.395MHz

Crystal

Packing

Main Unit / Packing

Parts Name

R01013

RD1013

ERJ3GSYJ223V

ERJ6GEYJ222V

TD5-C268DH

EVm1YSX50B15

EVM1YSX50B14

MVR32HXBRN473

EVM1YSX50B14

EVM1YSX50B14

MVR32HXBRN472

CDB455C7

HC49U 12.8MHZ

Antenna Cable

Microphone

Model Name Plate

Bracket

Button Cover

Adhesive Tape

Item Carton

Vinyl Bag (or Button Cover

Vinyl Bag for Radio

Vinyl Bag for Braket

Fixture DR610

Fixture 45 x 146

Fixture

Registration Card T

Schematic Diagram

FCC Part 15 Seal

Instruction Manual

Lot Numcwr Seal

Power Cable

MIC Hanger

Screw

Bolt

Screw

Screw

Washer

Nut

Ver.

T/1/2

T/1/2

2

T

DR140T: T, DR140E: E, DR140TE1: 1, DR140TE2: 2

Page 24

CPU Unit

Ref.

No.

Parts No.

Description

Parts Name

CPU Unit

FM0077Z

DG0013Z

FG0241Z

TL0018

TL0019

FP0110 LED Spacer

TT1002 Tube 1.0 6mm

C301

CU3035

CU3035

C302

C303

CÜ3035 Chip C. C1608J81H102KTA

C304 CU3047 Chip C. C160SJB1H103KTA

C305 CS0237 Chip Tantal TMCMA1A475MTR

C306 CU3101 Chip C.

C307

CU3101 Chip C. C1608JB1C473KTA

C308 CU3035

C309

CU3035 Chip C.

CS0237

C310

C311

CU3085 Chip C. C1608CH1H30QJT-A

C312

CE0308

C313

CU3059

C314

CU3085

C315 CU3047 Chip C. C1608JB1H103KTA

C316

CU3049

C317 CU3043

CU3Q43

C318

C319

CU3043 Chip C. C1608JB1H472KTA

C320 CU3047

C321

CU3111

C322

CU3059

C323

CU3051 Chip C. C1608JB1E223KTA

C324

CE0312

CU3035 Chip C. C1608JB1H1Q2KTA

C325

C325 CE0312 Electrolytic C.

C327

CU3051 Chip C.

C328

CU3059

C329

CS0372 Chip Tantal TMCMB1C106MTR

C330

CU3019

C331

CS0220

C332

CS0220 Chip Tantal

C333 CU3031

C334

CU3C31 Chip C.

CN301

UX1201

CN302

UE0192

CN303 UE0192

CN304

UE0170

XL0051

0301

X00254

0302

XD0127

0303

D304 XD0255 Diode

XD0254

0305

ELD036

EL301

XA0446

IC302

XA0351

IC3D3

Chip C.

Chip C. C1608JB1H102KTA

Chip C.

Chip Tantal

Electrolytic C.

Chip C.

Chip C- C1608CH1H300JT-A

Chip C.

Chip C. C1608JB1E153KTA

Chip C. C16Q8JB1H472KTA

Chip C. C1608J81H103KTA

Chip C.

Chip C. C1608JF1E104ZTA

Electrolytic C.

Chip C. C1608JF1E104ZTA

Chip C. C1608CH1H470JTA

Chip Tantal

Chip C. C1608JB1H471KTA

Wire

Connector

Connector

Connector

LED

Diode 1SS355TE17

Diode

Diode

LCD

IC

IC

LCO Holder OR 130

LCD Light DR130

LCD Rubber Connector

LCD Filter

LCD Filter

C1608J81H102KTA

C1608JB1C473KTA

C1608JB1H102KTA

C1608JB1H102KTA

TMCMA1A475MTR

6.3CV 100BS

C1608JF1E104ZTA

C1608JB1E153KTA

C1068J81C104MTA

ECEV1CA1Q0R

ECEV1CA100R

C1608JB1E223KTA

TMCMA 1C225MTR

TMCMA1C225MTR

C1603JB1H471KTA

Wire DR140TE1. 1/2

11R JE

11RJE

B9BZFI

VRPG3312X

MA704WA TX

MA8110HTX

1SS355TE17

LCD HLC8943-013400

M38223M4-108H

24LC16BT-I/SN

Ref.

Ver.

Parts No.

No.

IC304

XA0238 IC

IC305

XA0208

IC306 XA0198

UJ0037

JK301

JW301 MPAL05GG Wire #30PH1-050-H1

JW302

MPAL05GG

JW303 MPAL05GG

JW304

MACL04GG

EP0003

LP301

LP302 EP0003 Lamp BQ031 30403A

Q301

XU0112

Q302

XU0112

Q303 XT0095 Transistor 2SC4081 T106R

Q304

XT0095

XU0060 Transistor

Q305

Q306 XT0113 Transistor

Q307

XT0095

Q308 XU0131

R301

RK3001

RK3038

R302

R304 RK3038 Chip R. ERJ3GSYJ102V

RK3026 Chip R.

R305

R306 . RK3038

RK3034 Chip R.

R307

R308

RK3038

R309

RK3058

R310

RK3038

R311

RK3043

RK3038

R312

RK3034 Chip R.

R313

R314

RK3072

R315 RK3038

R316 RK3038 Chip R. ERJ3GSYJ102V

R317

RK3038

RK3050

R318

RK30S9

R319

R320

RK3046

R321 RK3074

R322

RK3026

R323 RK3050

R324

RK3046

R325

RK3038

RK3001 Chip R. ERJ3GSY0R00V

R326

RK3074

R327

R328 RK3046

RK3044

R329

RK3062 Chip R.

R330

RK3038 Chip R.

R331

R332

RK3050

R333 RK3038

R334 RK3050 Chip R.

RK3001 Chip R.

R335

RK3054 Chip R.

R337

RK3068

R338

Description

IC

IC

Jack

Wire

Wire

Wire #30AH1-040-H1

Lamp

Transistor

Transistor

Transistor

T ransistor

Transistor

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ102V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ101V

Chip R.

Chip R. ERJ3GSYJ472V

Chip R. ERJ3GSYJ102V

Chip R.

Chip R. ERJ3GSYJ472V

Chip R. ERJ3GSYJ332V

Chip R.

Chip R.

Chip R.

Parts Name

AN78L05M E1

RH5VA45AA T1

RH5VA32AA T1

C4T-U1-PC

#3QPH1-050-H1 1/2

#30PH1-050-H1

8Q031 30403A

DTA114YU T106

DTA114YU T106

2SC4081 T106R

UMC2TR

2SC2873YTE12R

2SC4081 T106R

DTC114EU T106

ERJ3GSY0R00V

ERJ3GSYJ102V

ERJ3GSYJ101V

ERJ3GSYJ102V

ERJ3GSYJ471V

ERJ3GSYJ102V

ERJ3GSYJ473V

ERJ3GSYJ272V

ERJ3GSYJ102V

ERJ3GSYJ471V

ERJ3GSYJ684V

ERJ3GSYJ102V

ERJ3GSYJ102V

ERJ3GSYJ103V

ERJ3GSYJ563V

ERJ3GSYJ472V

ERJ3GSYJ105V

ERJ3GSYJ103V

ERJ3GSYJ105V

ERJ3GSYJ104V

ERJ3GSYJ102V

ERJ3GSYJ103V

ERJ3GSYJ102V

ERJ3GSYJ103V

ERJ3GSY0R00V

ERJ3GSYJ223V

ERJ3GSYJ334V

Ver.

1/2

1/2

T

T/E

ro

CO

DR140T: T, DR140E: E, DR140TE1: 1. DR140TE2: 2

Page 25

Ref.

Parts No.

No.

RK3062

R339

R341

RK3001

R342 RK3038

R343 RK3046

R344

RK3050

RK3054

R345

RK3050

R346

R347 RK3062

RK3038

R348

R349 RK3001

RK3001

R350

RK3102

R353

RK3102

R355

RK3050

R356

RK3050

R357

RK3062

R353

RK3102

R360

RK3050 Chip R.

R361

RK3058

R363

R364

RK3055

R365 RK3070

RK3058

R366

RK3102

R36S

RK3050

R369

RK3102

R370

RK3038

R371

RK0014

R372

RK3042

R373

RK3070

R375

R376 RK3046

R377 RK3055

RK3070

R378

RK3001

R379

R380 RK3058 Chip R. ERJ3GSYJ473V

R381 RK3070

R382 RK3034 Chip R. ERJ3GSYJ471V

RK3034

R383

UR0002 Encoder

RE301

SW301 UU0025

SW302 UU0015

UU0015 Switch SKQD 901

SW303

SW304 UU0Û15 Switch SKQD 901

UU0025

SW30S

SW306 UQ0011

RV0035

VR301

XQ0091

X301

UP0317A DR140 P.C.B.

ES0017 Speaker

FG0040

UX1047

Description

Chip R. ERJ3GSYJ104V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ223V

Chip R. ERJ3GSYJ103V

Chip R. ERJ3GSYJ104V

Chip R. ERJ3GSYJ102V

Chip R.

Chip R. ERJ3GSY0R00V

Chip R. ERJ3GSYJ203V

Chip R. ERJ3GSYJ203V

Chip R. ERJ3GSYJ103V

Chip R.

Chip R. ERJ3GSYJ104V

Chip R.

Chip R. ERJ3GSYJ473V

Chip R.

Chip R.

Chip R. ERJ3GSYJ473V

Chip R.

Chip R. ERJ3GSYJ103V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ474V

ChipR. ERJ3GSYJ472V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Switch SKQMAL

Switch

Switch

Switch ESB64801

Trim Pat

Crystal

SP Unit

Wire

Parts Name

ERJ3GSY0R00V T/E

ERJ3GSYJ102V

ERJ3GSYJ472V

ERJ3GSYJ103V

ERJ3GSYOROOV E

ERJ3GSYJ 1.03V

ERJ3GSYJ203V

ERJ3GSYJ103V

ERJ3GSYJ273V

ERJ3GSYJ474V

ERJ3GSYJ203V

ERJ3GSYJ203V

ERJ3GSYJ102V

ERJ6GEYJ630V

ERJ3GSYJ222V

ERJ3GSYJ273V

ERJ3GSYJ474V

ERJ3GSYOROOV

ERJ3GSYJ474V

ERJ3GSYJ471V

EVOWQGF1524B

SKQO 901

SKQMAL

EVUF2JFK4814

38C 4.9152MHZ

VS-57-0814-1.5W

Speaker Cushion

Harness DR 130

CPU Unit I SP unit I VCO Unit

Réf.

Ver.

T

Parts No.

No.

TS116AZ Case

C201

CU3103

CU3106

C202

C203

CU3035

C204

CU3035

C205

CU3035

C206

CU3101

C207

CU3035

C208 CS0235 Chip Tantal TMCSA1V334MTR

CU3043 Chip C.

C209

C210 CU3043

CS0371

C211

CS0371

C212

C213 CU3023 Chip C.

CU3025

C213

CU3024 Chip C.

C213

CU3043

C214

CU3035 Chip C.

C216

CS 0217

C217

C218 CU30C3 Chip C.

C219

CU3035

C221

CU3031

C223 CU3015

C224

CU3035 Chip C.

CU3035 Chip C.

C225

CU3059

C226

CU3Û35

C229

C230 CS0216

C232 CU3035 Chip C.

C233

CU303S

C245

CU3035

C246

CS0220

C247

CU3007

CU3005

C247

C247 CU3006

C248

CU3001 Chip C.

C249

CU3022

CN201

UE0188

CN202 UE0185 Connector

0201

X00298 Diode

0202 XD02S8 Diode

0205 XD0112 Diode

0206 X00230 Diode

XD0298

0207

XA0235

IC201

L203

QC0042

L204

QC0042

QC0045 Chip L.

L205

QA0067

L202

Description

VCO Unit

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip C. C1608JB1H102KTA

Chip C.

Chip Tantal

Chip Tantal TMCMA1C335MTR

Chip C.

Chip C.

Chip Tantal

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip Tantal

Chip C.

Chip C.

Chip Tantal

Chip C.

Chip C.

Chip C.

Chip C.

Connector

Diode

IC

ChlpL

Chip L.

Coil

Parts Name

VCO Case

C1608UJ1H150JTA

C1608UJ1H390JTA

C1608JB1H102KTA

C1608J81H102KTA

C1608JB1H102KTA

C1608BIC473KTA

C1608JB1H472KTA

C1608JB1H472KTA

TMCMA1C335MTR

C160BCH1H101JTA

C1608CH1H151JTA

C1608CH1H121 JTA

C1608JB1H472KTA

C1608JB1H102KTA

TMCMC1A226MTR

C1608CH1H020CTA

C1608JB1H102KTA

C1608JB1H471KTA

C1608CH1H220JTA

C1608J81H102KT A

C1608JB1H102KTA

C*608JF1E104ZTA

C1608JB1H102KTA

TMCMB1A106MTR

C1608JB1H102KTA

C1608JB1H102KTA

C1608JB1H102KTA

TMCMA1C225MTR

C1608CH1H060CTA

C1608CH1H040CTA 2

C1608CH1H050CTA

C1608CH1H0R5CTA

C1608CH1H820JTA

B9P-BC-2

B6P-8C-2

1 SV273(TPH3)

1 SV273(TPH3)

1SV128 TE85L

OAN202U T106

1SV273(TPH3)

M56760FP

NL322522T1R8J

NL322522T1R8J

NL322522T3R3J

100M OSC-2 -T

Ver.

T/E

1

2

1

T/E

DR140T: T, DR140E; E. 0R140TE1: 1, DRUOTE2: 2

Page 26

VCO Unit I Mechanical Parts I EJ-20u

Ref.

Parts No.

No.

Q201 XE0010

Q202 XT0111

Q203 XT0111 Transistor

Q204

XT0096

Q207

XU0131

Q208

XU0131

Q206

XU0060

Description

FET

Transistor

Transistor

Transistor

Transistor

Transistor UMC2TR

2SK508K52 T2B

2SC4081LNT106S

2SC4081LN T106S

2SC4099 T106N

DTC114EU T106

0TC114EU T106

Parts Name

Ver.

R201 RK3038

R202

RK3038

R203 RK303S Chip R.

RK3046 Chip R.

R206

RK3058 Chip R.

R207

R2Û8 RK3034 Chip R. ERJ3GSYJ471V

R21Ü

RK3040

R212 RK3030

R213

RK3041 Chip R.

R214

RK3022 Chip R. ERJ3GSYJ470V

R216 RK3026

R217

RK3018

R218

RK30S0

R219

RK3038

R221 RK3001

R224

RK3034

RK3054 Chip R.

R225

R226

RK3026

R228 RK3041

R229 RK3026

R231 RK3058 Chip R.

R232

HK3058

R233 RK3040

R234 RK3046 Chip R.

RK3026

R235

RK3046

R236

R237 HK3066

R238 RK3058

Chip R. ERJ3GSYJ102V

Chip R. ERJ3GSYJ102V

Chip R.

Chip R. ERJ3GSYJ221V

ERJ3GSYJ102V

ERJ3GSYJ472V

ERJ3GSYJ473V

ERJ3GSYJ152V

ERJ3GSYJ182V

Chip R.

Chip R.

ChipR.

Chip R.

Chip R. ERJ3GSYOROOV

Chip R. ERJ3GSYJ471V

Chip R.

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. ERJ3GSYJ101V

ChipR.

Chip R.

Chip R. ERJ3GSYJ473V

ERJ3GSYJ101V

ERJ3GSYJ220V

ERJ3GSYJ103V

ERJ3GSYJ102V

ERJ3GSYJ223V

ERJ3GSYJ101V

ERJ3GSYJ1B2V

ERJ3GSYJ101V

ERJ3GSYJ473V

ERJ3GSYJ473V

ERJ3GSYJ152V

ERJ3GSYJ472V

ERJ3GSYJ472V

ERJ3GSYJ224V

Mechanical Parts

AD0010 D3+8FeNi

AEÛ014

AV0001

FF0028

FM0152

KS0041C2

KZ0039A

KZ0040A

K200452

KZ0047Z Top Case

NB0063Z

SS0Û52Z Chassis

TS0125Z

FP0004

B2.6+8FeBC

B2.6+6FeNi

Nonwovens

IC Spring

Bottom Case

Dial Knob

Volume Knob

Front Panel

Power Switch Knob

Front Shield Case

Cable Tie

1/2

DR140T: T, DR140E: E, OH

Page 27

Parts No. Description

EJ-20U

C501

CS0236 Chip Tantal

C502

CU3059 Chip C. C1608JF1E104ZTA

C503

CS0230 Chip Tantal TMCMA1E105MTR

C504

CU3059

C505

CS0230 Chip Tantal TMCMA1E105MTR

C506 CS0230

C507

CS0230 Chip Tantal

C508 CU3023

C509 CS0237

C510

CU3019

C511 CU3035

C512

CU3015 Chip C.

C513 CU3015

Chip C. C1608JF1E104ZTA

Chip Tantal

Chip C.

Chip Tantal TMCMA1A475MTR

Chip C.

Chip C.

Chip C.

TMCMAOJ685MTR

TMCMA1E105MTR

TMCMA1E105MTR

C1608CH1H101JTA

C1608CH1H470JTA

C1608JB1H102KTA

C1608CH1H220KTA

C1608CH1H220KTA

Parts Name Ver.

CN501

UX1050

C501 XA0239

QS01 XT0095 Tansistor

R5Q1 RK3040 Chip R.

R502 RK3022 Chip R.

RK3067 Chip R.

R503

R504

RK3038

R505 RK3051

R506

RK3049 Chip R.

R507

RK3067 Chip R.

R5D8 RK3047

R509 RK3068 Chip R.

RK3054

R510

R5J1 RK3054

R512

RK3055

RK3074

R513

R514 RK3065

RK3048 Chip R.

R515

RK3056

R516

RHO106

VR501

XQ0077

X501

HK0305

HP0029 Protection Bag

FG0057

UP0243

YZ0042

Wire EJ20u

IC

ChipR.

Chip R. ERJ3GSYJ123V

Chip R.

Chip R.

Chip R.

Chip R.

ChipR.

Chip R.

Chip R.

Trim. Pot

Crystal

Adhesion

AK2341

2SC4081 T106R

ERJ3GSYJ152V

ERJ3GSYJ470V

ERJ3GSYJ274V

ERJ3GSYJ102V

ERJ3GSYJ822V

ERJ3GSYJ274V

ERJ3GSYJ562V

ERJ3GSYJ334V

ERJ3GSYJ223V

ERJ3GSYJ223V

ERJ3GSYJ273V

ERJ3GSYJ105V

ERJ3GSYJ184V

ERJ3GSYJ682V

ERJ3GSYJ333V

EVM1YSX50BQ4

38C 3.686400MHz

Carton

Rubber Cushion

P.C.B.

Bond G17

140TE1: 1, DR140TE2: 2

Page 28

A DJ US T ME NT

1 ) Re q uire d Te s t Equip men t

1. Digital Multimeter

d. Distortion Meter

Measurable frequency:

2. Regulated Power Supply

Supply voltage: 13.8VDC

Current: 15A or more

3. Oscilloscope

Measurable frequency: Audio Frequency

4. Spectrum Analyzer f- Linear Detector

Measuring range: Up to 2GHz or more

5. Tracking Generator

Output frequency: Up to 2GHz or more

Input level:

Distortion level:

e. Audio Generator

Output frequency:

Output impedance:

1kHz

Up to 40dB

1 % ~ 1 0 0 %

1kHz ~ 10kHz

600£2

6. Dummy Road

Measurable frequency: Up to 500MHz

Impedance: 50Q

Power: 60W or more

7. Speaker

Impedance:

8 Q

8. SSG

Output frequency:

Output level:

Modulation:

Up to 1GHz

-20dB/0.1ji.V to120dB/1V

AM/FM

9. Transceiver Tester

Up to 500MHz

a. Frequency Counter

b. Power Meter

Impedance:

Measuring range:

50£2

60W or more

c. Audio Voltmeter

Measurable frequency:

Sensitivity:

28

50Hz ~ 10kHz

1mV~ 10V

Page 29

Test Equipment

1. All SSG output is indicated by EMF.

2. Audio Output level: 50mW~100mW at 8Q

3. Power supply voltage: 13.8V

3. Test frequency can be variable ±100kHz.

2 ) P LL A d j us t m e n t

Item Condition

Equipment Terminal Parts

Measurement Adjustment

Specifications

Method

Reference

Frequency

VCO

f=145.00MHz (T, E.TE1)

f=162.00MHz (TE2)

TX

f=173.99MHz

RX

3) T X A dj u s tm e n t

High

Power

Low

Power

Deviation

MIC Gain AG: 1kHz 4mV emf

CTCSS

Tone

Level

f=145.00MHz (T, E.TE1)

f=162.00MHz (TE2)

High TX

f=145.00MHz (T, E, TE1)

f=162.00MHz (TE2)

LowTX

f=145.00MHz (T,E,TE1)

f=162.00MHz (TE2)

Low TX

AG: 1kHz 40mV emf

f=145.00MHz (T,E,TE1)

f=162.00MHz (TE2)

Low TX

AG: OFF

TONE SW: ENC

88.5Hz

Freq. Counter

Power Meter

Digital

Multimeter

Power Meter

Current Meter

Linear Det.

Oscilloscope

Power Meter

AG

ANT

PD

ANT

145.00MHz (T, E, TE1)

TC1

162.00MHz (TE2)

VCO

L302

VR5

VR6

VR4 4.7kHz/DEV

VR3

52W (T, E)

36W (TE1, TE2)

7.0V + 0.1V

5.5W

3.0kHz/DEV

Check

±100Hz

+ 1.0W

10.5A or below (T, E)

8.5A or below (TE1.2)

5.5 + 0.5W

4.7kHz ± 0.2kHz/DEV

3.0kHz + 0.2kHz/DEV

0.6 ~ 1.1kHz/DEV

Tone

Burst

TBSTON 1750Hz

Check 2.5 ~ 3.9kHz/DEV

Page 30

4) RX Adjustment

Item Condition

f= 144.00MHz (T, E)

f=137.00MHz (TE1)

Sensitivity

S Meter

f=150.00MHz (TE2)

SSG OUT: -lOdBjLL

1 kHz 3.5kHz/Dev

f=144.00MHz (T, E)

f=137.00MHz (TE1)

f=150.00MHz (TE2)

SSG OUT: -8.5dBjLi

1 kHz 3.5kHz/Dev

f=145.00MHz (T, E, TE1)

f=162.00MHz (TE2)

SSG OUT: 18.0dBp.

Mod: OFF

SSG OFF

Measurement

Equipment Terminal Parts

SSG

SINAD Meter

Oscilloscope

(0.2V/Dev)

Level Meter

SM

LCD

S Meter

L1 ~L5

VR1

Adjustment

Method

Turn the coils L5, L4,

L2, L1, L3 to the max.

in order. Adjust the

coils repeatedly.

Check

Set to the point where

all segments start

flashing.

Check Does not light.

Specifications

SINAD is 12dB or

more.

SQL level

f=145.00MHz (T, E, TE1)

f= 162.00MHz (TE2)

SSG OUT: -12dB|i

Mod: OFF

SSG OFF

LCD

Busy

Busy

OFF

VR2

Set to the threshold

point to close the

squelch.

Check

Busy OFF

SQL L mode

Busy OFF

I

27

Page 31

5 ) Adju s t ment Points

28

Page 32

m

ïJ ù m

m m

BPS

¡aSS

mW

29

Page 33

2) Main Unit Side B

fonrm.

» 1

; m :t=r T ;

>0 S'*, K<

^ i M S i

S ' i p J i - - 6r a - :

(S O W Tt T "

a t u i o t *>'“

9to

"w e M a w c m & m

V a c #

I B S

•i.«ivi* *. ¿it * i. .

v m .

W M

d fee i

« m O j-

.<•;

K t ln O f i

«»¡no

atolTTn

if -

tiiik .

x X ' l f

p :

r t . * .o i £—

* ,» *■ ;■ ;: ■■■',' ;.? < i j « i

I ? *1* *13 ¿ 3 ),, * IK

(4t,u iwfltU

30

Page 34

3) CPU Unit Side A

4) CPU Unit Side B

-S jf 'V ta jp v ? - 1

’Urn- V O * ! / ? i

n r f>. -' j s l

5 k :■ * * 4 » * & -A '

x iz -iir jr '' y

./ ! '(|

¡r*. ” ’it*n''. cjW

■ j !f f f W 3 7 ^

n il)

‘ * $ 5

■up A m *

TLJT Wlr ,

'(LD- $ $ l |

•UP.'l aw*,

S I I K p

H

T Ftui-i

31

Page 35

5) VCO Unit Side A

R?08

lO T g e n a g r

' ■ ^ í a i H r a S

M i i ^ - ' f l c ? ! ! . ! Q J 2 É 1

6) VCO Unit Side B

«jfV i «:' „ ° \

S ^ í í d ' í v , ;

R ^ á k '. ■

v

■

g ñ % ,

M I

o

OJ

z

u

32

‘&¿ir>,w. ¿5fv¡(rí .!& y;

Page 36

7) EJ-20U (CTCSS Unit:Option)

CD

R 5 1 4 R 5 . 1 5

C N 5 0 1

R 5 0 4

33

Page 37

ÍÍ8MHí

s i

. me gnln

S s

„ Î

B

«1

I |

H R

O

~U

c z

c z

O

~ 0

c

§ o

- Ï

§ £

s 8

£ s

5 N

3

S g

*

*

o

r-

- o

X

r*

*

i

1«

i

TJ

e

XI

455KH2

Î

<

o

o

i

c z

1«

HWv

n O

4—

c

1

*0

d—

1 “

S

oír

y

hdP

X2 3 0. 39 5M H 2

P

i a

>

Ï

o

o

T

±

CZ

3 - 4 ^

3-0^ 2-''

9—?_2

a_ o ^ o - /

VM

CALL

coNwccroB ron cicss unii

FUNC

i W m s á

connector ron tranking unit

--TEI.1E2 UNIT OMV

i

II

3?

“ ^ Y h s==

-PiH^

?o

P7

— r

SSS

sss

CÜD

V

IL

l'T U -

%

LO-

- » ï

0 Ï

J

í s

a *,

2 o

T i

í.s

J

I JL

So

* ft

)

□

m

I

----------------------------------

¡g __

f f

4

lA iv a o v ia > i o o i a

Page 38

1) M a in U n itT /E

Page 39

2) M a in U n it T E 1 /T E 2

FL1 LF-H12S

R73

100K

Scoter SET

pSC408 R17

Diaorzs.jB

;4cgg

XF 133.35MHz

QAaao.

026

DA2C4N

)A0 08 <

I

JC01S©

RFOUT

CNO

MOD

Ria7

IK

22PI15P I M687Q2L QKA75G

10P 15P M687Q2H QKA9SD

R^05

12**2)A

38

Page 40

m CO

O

" ö

c

c

3

R301 (eoím)

(Pink)

JW 301

R341 (8 Mini)

<PW0

JW 302

(B a m ) 1 ! 0 0

R350

(Pirk)

JW 3 03

(Bu.) 1

JW 30 4

(6« m) 0 1 0

R349

UX12 01

03

CO

T

1 l

0

1 1

0

0 I 0

0 0

£

0

0 1

0 0

TE1 TE2

0 0

1

0

1

1

1

0

1

0

1

0

0

1

Page 41

4^

O

4) VCO Unit

XC225

-^ 0 .001

8?!?1 4 EU

Ver.

C213

C247

TE 100P 5P

TE1

TE2

BV

150P

120P

200P

6P

4P

5P

Page 42

5) EJ-20U(CTCSS Unit: Option)

-F*

Page 43