Page 1

DR-130

Service Manual

CONTENTS

SPECIFICATIONS

1)

General

2

PARTS LAST

2)

Transmitter

2

MAIN Unit

22-23

3)

Receiver

2

CPU Unit

24

CIRCUIT DESCRIPTION

VCO Unit

251)Receiver System

3

SP Unit

252)Transmitter System

4

EJ19u.

253)PLL Circuit

4

Mechanical Parts

254)Terminal Function of Microprocessor

5 - 7

Others

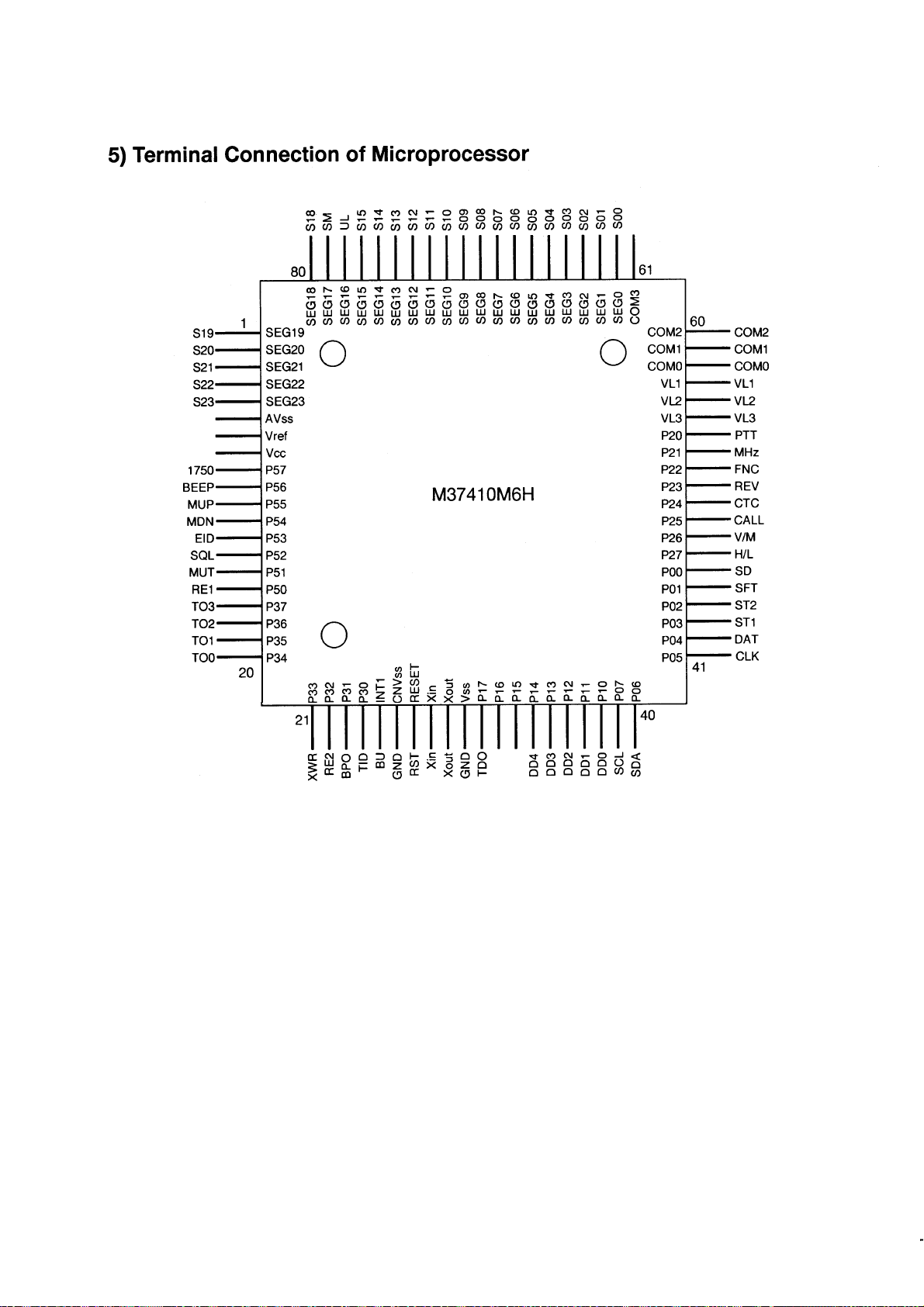

255)Terminal Connection of Microprocessor

8

Packing..

25

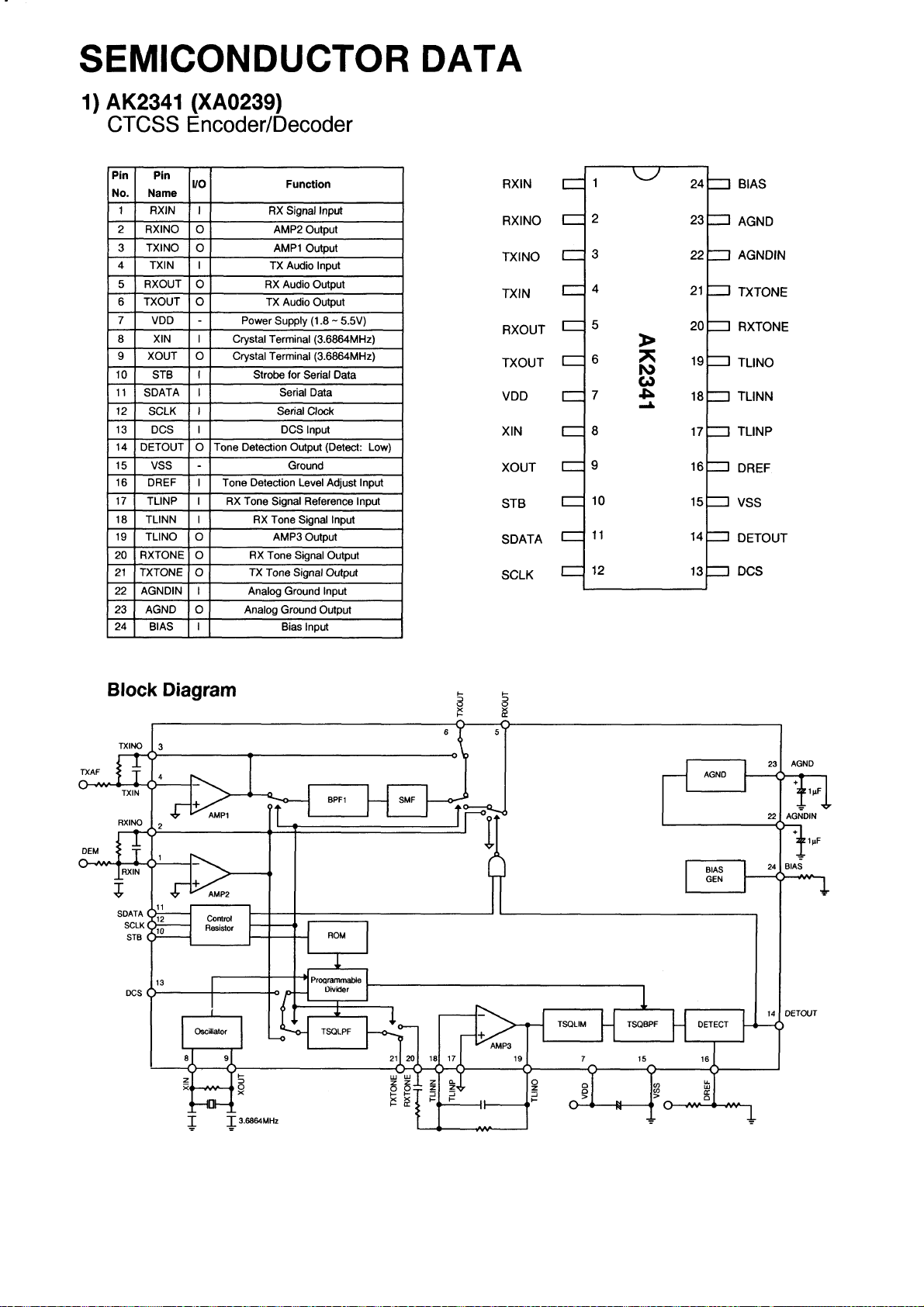

SEMICONDUCTOR DATA

EJ20u

261)AK2341

9

EMS-5A

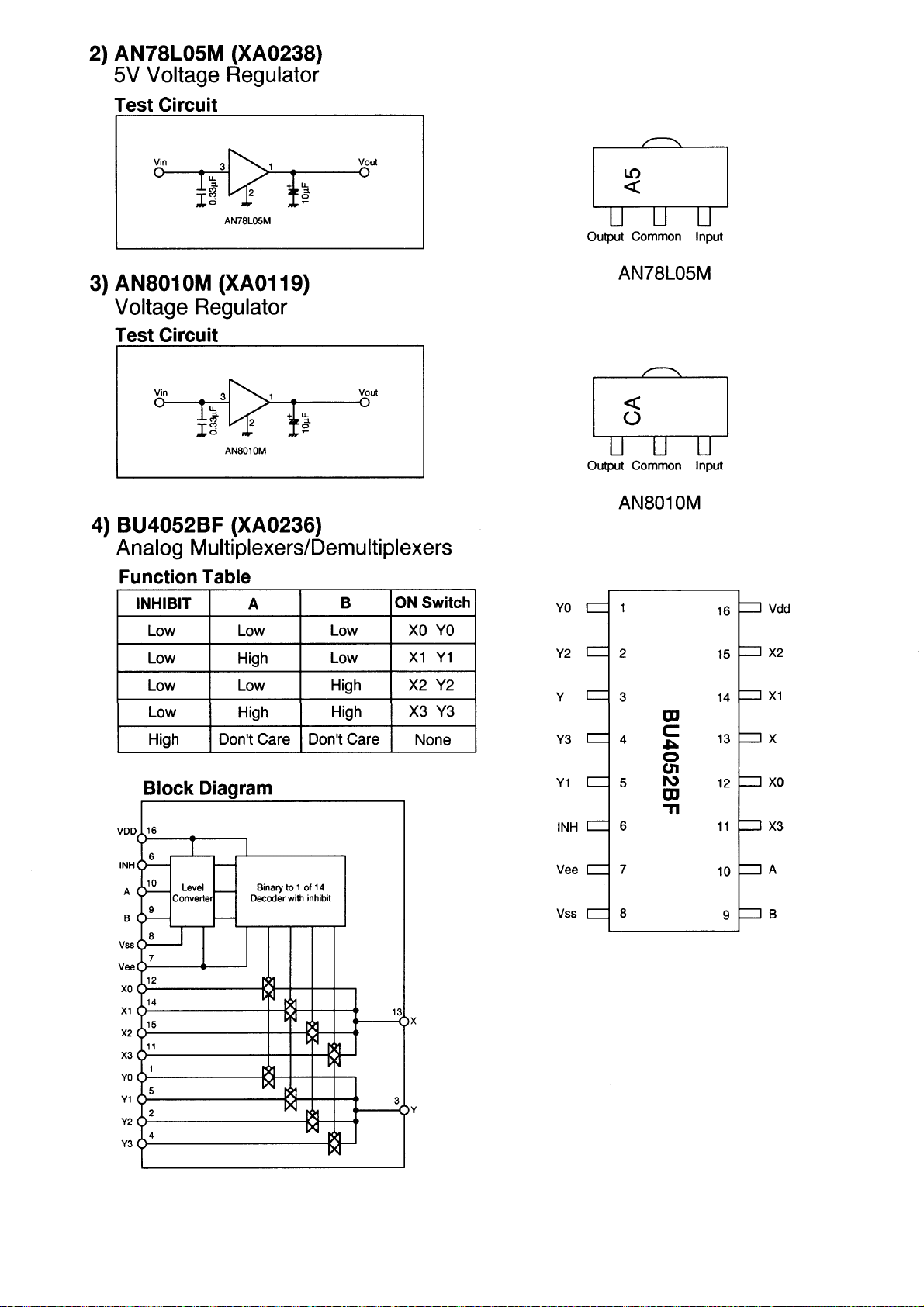

262)AN78LO5M

10

EMS-11

263)AN8010M

10

ADJUSTMENT

4)

BU4052BF

10

1) Required Test Equipment.

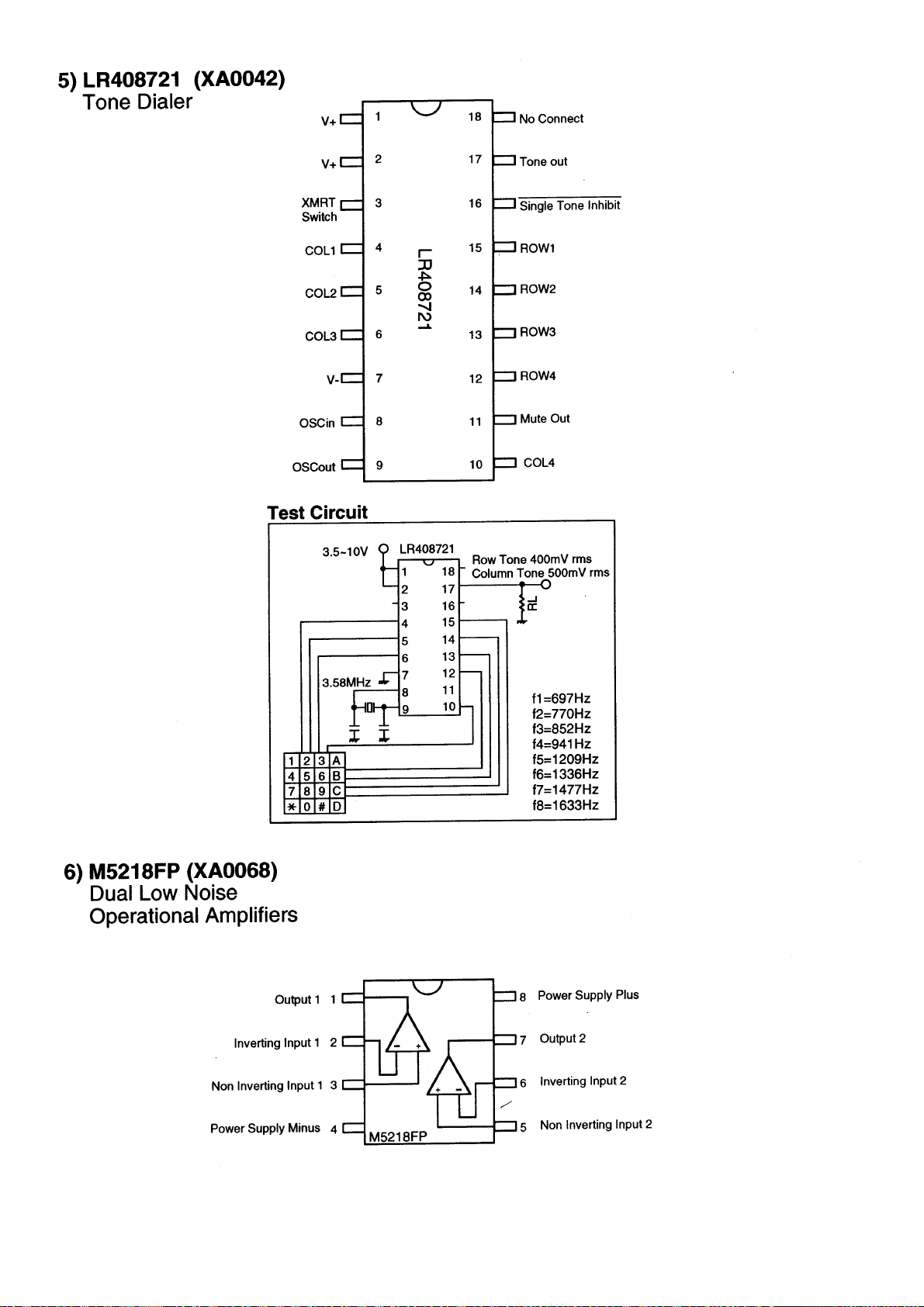

275)LR408721

11

2) Adjustment for DR-130

28~29

6)

M5218FP

11

3) Adjustment Points

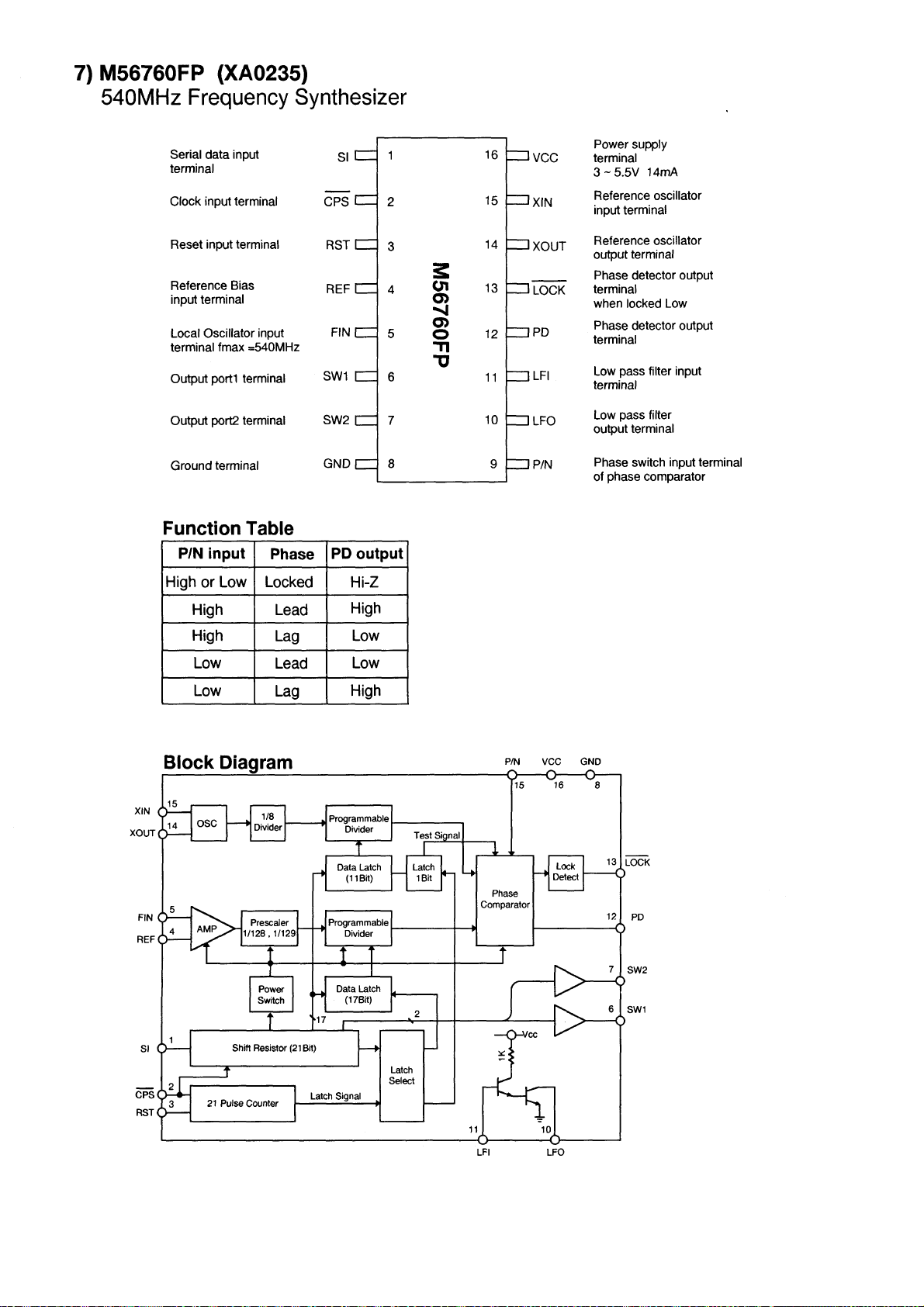

307)M56760FP

12

4) Adjustment Quick Reference

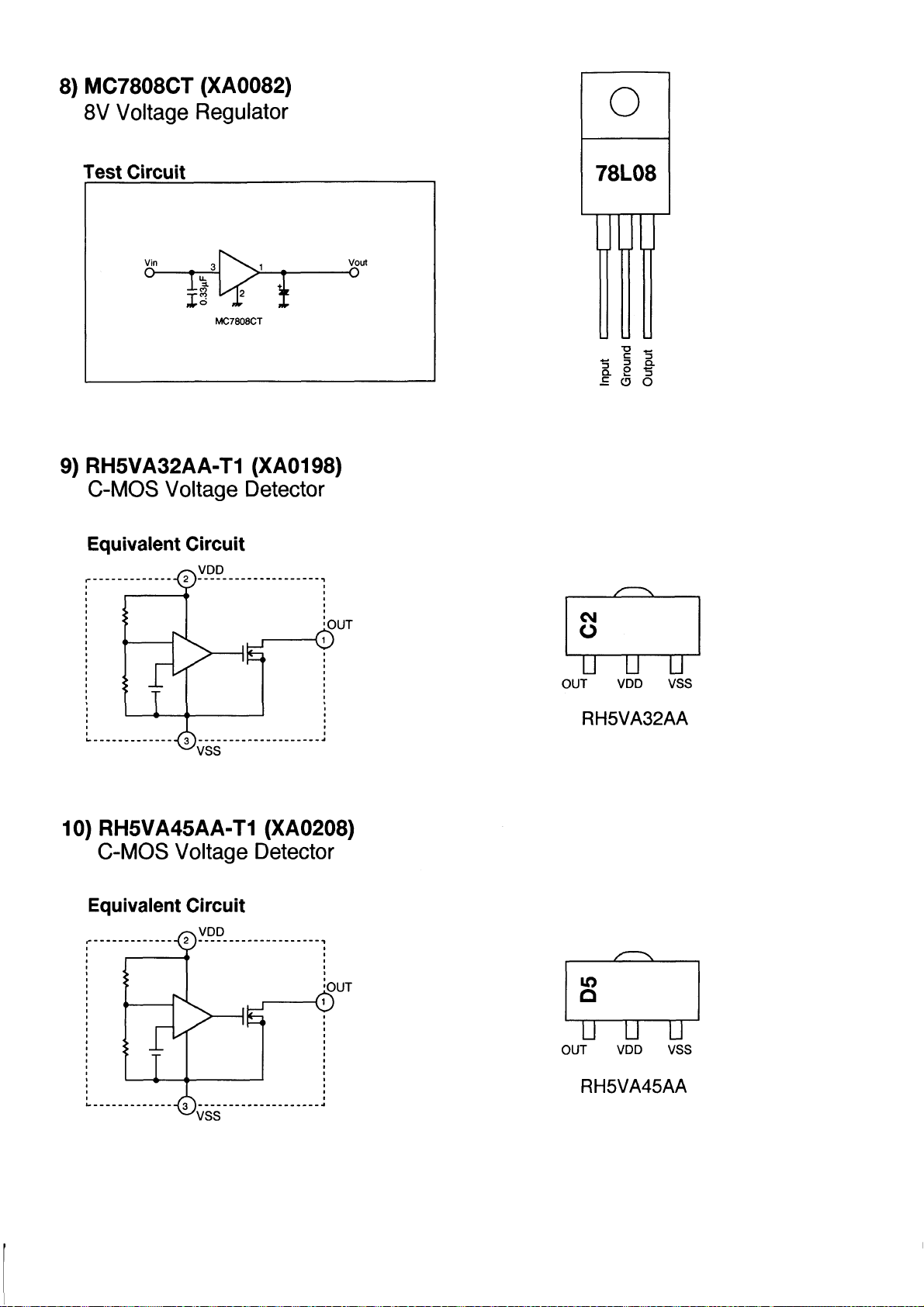

308)MC7808CT

13

CIRCUIT DIAGRAM

9)

RH5VA32AA-T1

13

1) EMS-5A

31

10)

RH5VA45AA-T1

13

2) EMS-11

31

11)

S-AV17

14

3) Main Unit (T/E/EZ/EA/TA)

32

12)

TK10487MTR

15

4) Main Unit (TEl1/TE2)

33

13)

AT24CO2N-10SI-2.7

15

5) CPU Unit

34

14)

AT24CO8-10SI-2.7

15

PC BOARD VIEW

15)

uPC1241H

16

1) Main Unit Side A

35

16)

16

2) Main Unit Side B

36

17)

LCD Connection

17

3) CPU Unit Side A.

37

EXPLODED VIEW

4) CPU Unit Side B

371)Bottom View

18

5) VCO Unit Side A

382)LCD View

18

6) VCO Unit Side B

383)Top, Front View 1

19

BLOCK DIAGRAM

394)Top, Front View 2

20

VERSION TABLE

21

ALINCO INCORPORATED

Transistor, Diode and LED Outline Drawings

TWIN 21 M.I.D. TOWER BUILDING 23F, 1-61, 2-CHOME,

SHIROMI CHUO-KU , OSAKA, 540-8580 JAPAN

Tel (81)6-6946-8150 fax (81)6-6946-8175

e-mail: export@alinco.co.jp

Page 2

SPECIFICATIONS

:

1) General

Frequency Coverage:

RX: 136.000 ~ 174.000MHz (T version)

TX: 144.000 ~ 148.000MHz (T version)

RX: 144.000 ~ 146.000MHz (E/EZ version)

TX: 144.000 ~ 146.000MHz (E/EZ version)

RX: 130.000 ~ 174.000MHz (EA/TA version)

TX: 130.000 ~ 174.000MHz (EA/TA version)

RX: 136.000 ~ 155.000MHz (TE1 version)

TX: 136.000 ~ 155.000MHz (TE1 version)

RX: 150.000 ~ 174.000MHz (TE2 version)

TX: 150.000 ~ 174.000MHz (TE2 version)

Frequency Resolution: 5, 10, 12.5, 15,20,25kHzsteps

Antenna Impedance: 50 ohm unbalanced

Power Supply Requirements

Current Drain at l3.8V

Dimensions: 140mm(W) x 40mm(H) x 154mm(D)

Weight: 0.86kg (approx.)

2) Transmitter High: 50Watts (DR-130T/E)

Output Power: High: 35Watts (DR-130TE1/2)

Emission Mode: F3E(FM)

Modulation System: Variable Reactance Frequency Modulation

Max. Frequency Deviation: +/ -5kHz (Wide Version)

Spurious Emission: -60dB or below carrier

Microphone: Electret Condenser Microphone

Operating Mode: Simplex/Semi-Duplex

Offset : 0ffset from 0 to 15.995MHz

3) Receiver

Receiving System: Superheterodyne Dual Conversion

Intermediate Frequency: 1stIF: 17.2MHz

Sensitivity: More than +/-6kHz at -6dB (Wide Version)

Selectivity: Less than +/-15kHz at -60dB (Wide Version)

DC 13.8 +/-10% Volts DC

Receiving: Squelched less than 800mA

Transmitting: High/10.0A (approx.)

Low/3.5A (approx.)

High:10Watts (DR-130EZ)

Low: 5Watts (Approx.)

+/ -2.5kHz (Narrow Version)

2nd lF: 455kHz

12dB SINAD less than -l6dBu (144.000MHz ~ 147.995MHz)

Audio Power Output: More than 2.5W 10% Distortion

Speaker Impedance: 8 ohm

Page-2

Page 3

CIRCUIT DESCRTPTION

1) Receiver System

1. Front End

The signal from the antenna is passed through a low-pass filter and input to

the voltage step up circuit consisting Of L14. The signal from L14 is led to

the gate of Q1. D19 is the diode limiter circuit against the excessive input

power of more than 20dBm. Q1 is the FETwhich has two gates. The

voltage of the gate 2 is set higher to get the high gain and sensitivity. The

signal from Q1 is led to the triple band pass filter (L4, L5, L6), and gets the

high image rejection ratio.

2. Mixer Circuit

The signal from the triple band pass filter is converted into the first lF signal

of 17.2MHz. The receiving signal is led to the gate 1 of Q2, and the first

local oscillator signal is led to the gate 2 of Q2. To get the high conversion

gain, the local oscillator signal voltage is set to about 1V. To reduce the

high adjacent channel interference, the band width of the FL2 is set to

20kHz. The signal from FL2 is amplified by Q8, and input to FM IF system

IC3 of TK10487.

3. lF Circuit

The TK10487 has the second local oscilltor circuit, mixer circuit, detector

circuit, squelch circuit, and so on. Pin1 and 2 are the terminals of the crystal

oscillator circuit. Pin2 (emitter) is connected to the ground via the resister

R3 to prevent the oscillator from decreasing the power at the low temperature. Pin4 of IC3 is connected to FL1 directly because the matching resistor

for ceramic filter is built-in. The quadrature circuit (pin10 of IC3) is connected to the ceramic resonator X2 for the temperature stability and good

quality. The signal from pin11 of IC3 is connected to the LPF. The detected

AF signal, which has flat frequency characteristics, is led to the control unit

and used as both squelch signal and tone squelch signal. De-emphasis

circuit consists of R31, R32, C26 and C27. The LPF amplifier consisting of

Q5 and Q6 is located far away from the VR in the control unit, so it outputs

the high voltage signal to prevent S/N from the deterioration. The squelch

switch circuit consists of Q4 and Q16, and switches on/off at the point where

there is no voltage to prevent from the switching noise. The S meter signal

from pin12 of IC3 is led to the CPU in the control unit after adjusting the level

at D20 and VR5. The S meter signal is thermal compensated by TH1 and

stabilized. The noise amplifier consists of pin13 and 14, the built-in OP

amplifier in IC3. The output signal of noise amplifier is amplified by Q14,

rectified by D5, and then led to the pin15 (hysteresis comparator input) of

IC3.

4. AF Circuit

IC4 is about 5W audio power amplifier IC. When the capacity of pin1 in C16

is increased more, the output incidental noise becomes smaller. The highpitched tone becomes smaller at the same time, This radio's capacity of

C16 is determined considering the high-pitched tone.

Page-3

Page 4

2) Transmitter System

1. Modulation Circuit

3) PLL Circuit

The microphone amplifier IC1 (IDC, LPF) consists of two operational amplifiers. The signal from the microphone is led to pre-emphasis circuit consisting

of C36 and R47 and then to the limiter circuit. The limiter circuit uses the

saturation of the OP amplifier. The amplified signal is input to the low-pass

filter IC1A. The output signal from the microphone amplifier is passed

through variable resistors VR2 for modulatlon adjustment and input to the

VCO unit. Sub tone deviation is determined by R24, R25 and VR2. The

radio does not have the adjustment variable resistor for sub tone deviation.

2. TX Amp. Circuit

The signal from VCO is ampriied by TX, RX wide band LO amplifier Q19.

The signal from Ql9 is passed through the transmission/reception selector,

and amplified byQ20 and Q15. The PA unit is driven at 200mW driving

power.

3. PA Circuit

IC5 is 50W powered amplifier module. The output power is controlled by

the voltage ofV1. The RF signal amplified 50W in PA is passed through D3

and three-stage transmission/reception low-pass filter, and input to the

antenna connector.

4. ALC Circuit

The power detection circuit consisting of D17 and D18 rectifies the output

signal voltage. The detected DC voltage is led to the VR1 (power adjust

trimmer), and amplified by Q3, Q9 and Ql3. Output power is controlled by

voltage of V1 in lC5 and collector voltage of Ql5. When the temperature

goes up unusually, the power down circuit consisting of R101 and TH2

works to prevent the device from the destruction.

The VCO unit is designed for the PLL circuit, putting the VCO on one side,

and PLL circuit on the other side.

Q301 in the VCO is grounded using the gate oscmator, and its frequency

covers 134MHz to 174MHz without transmission/reception shift circuit.

lC301 is pulse swallow system based PLL IC with the built-in prescaler,

which synthesizes 150MHzlband signal.

The loop filter consisting of Q302 and Q303 is the active type.

Page-4

Page 5

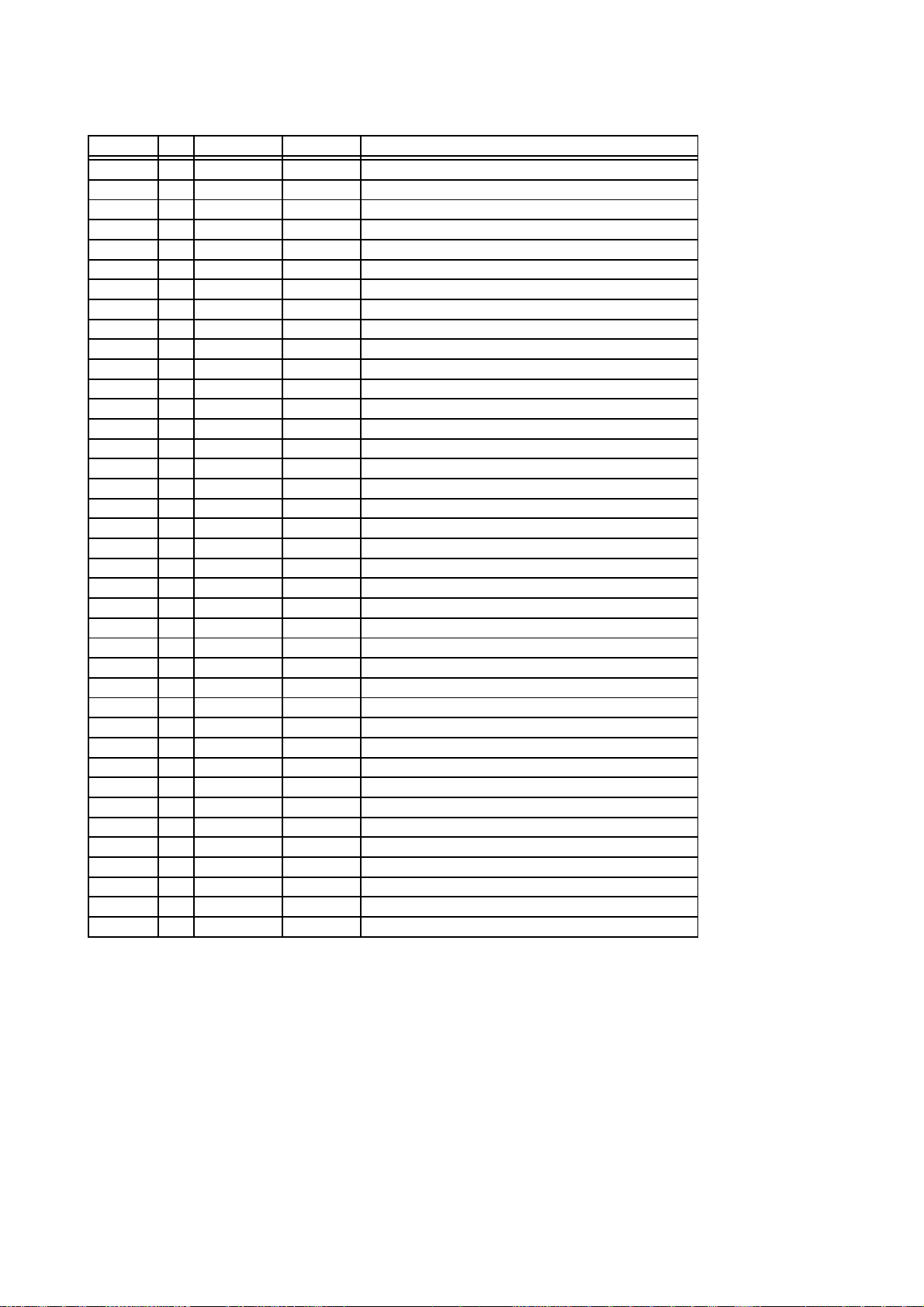

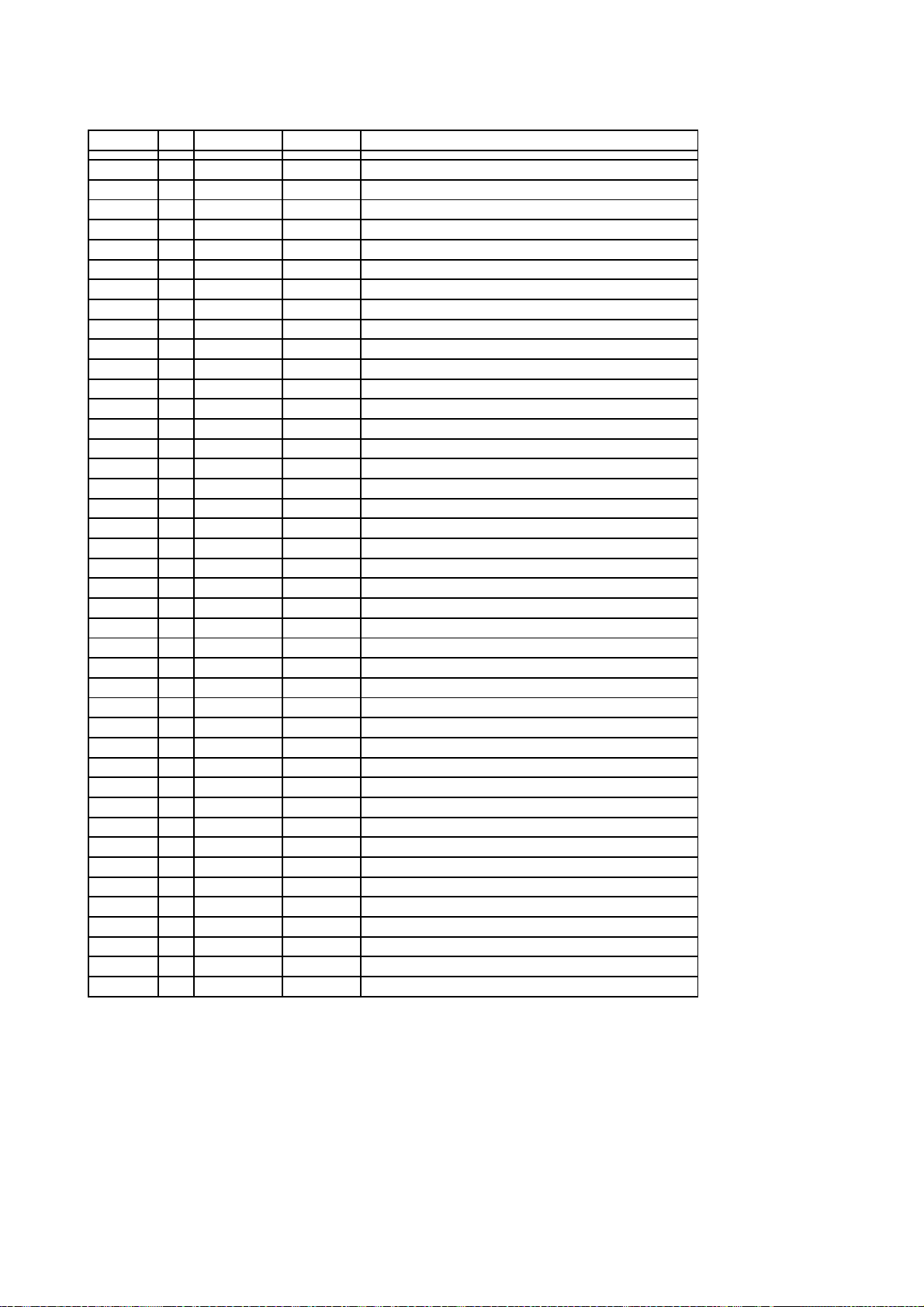

4) Terminal Function of Microprocessor

h

Port No. I/O Logic PinName Description

1 O SEG19 LCDSegment19 Output

2 O SEG20 LCDSegment20 Output

3 O SEG21 LCDSegment21 Output

4 O SEG22 LCDSegment22 Output

5 O SEG23 LCDSegment23 Output

6 I GND AnalogGround 0V

7 I Vref Reference Voltage Input 5V

8 I Vcc CPU Power Supply hnput 5V

9 O 1750_ ToneBurstOutput

10 O Clock BEEP BeepToneOutput

11 I Active Low MUP Channel Up Input (Microphone Control)

12 I Active Low MDN Channel Down Input (Microphone Control)

13 I NoUse EID

14 O Active Low SQL Squelch Control (L: Audio is off.)

15 O ActiveHigh MUT Microphone Mute (H: Mic Amp is off.)

16 I Active Low REl RotaryEncoder Input

17 O Clock TO3 ToneOutput

18 O Clock TO2 ToneOutput

19 O Clock TO1 ToneOutput

20 O Clock TO0 ToneOutput

21 I ActiveHigh XWR EEPROM Write Status External Input

22 I Active Low RE2 RotaryEncoder Input

23 O Active Low BPO Band Plan Detection Input (Common)

24 I Active Low TID Tone Unit Detection Input

25 I Active Low BU Back Up Signal Detection input

26 I GND Ground

27 l Active Low RST ResetInput

28 I Xin Crystal Oscillator Terminal (3.58MHz)

29 O Xout Crystal Oscillator Terminal (3.58MHz)

30 I GND Ground

31 I Active Low TDO CTCSS Tone Detection Output

32 O Active Hig

33 O NoUse

34 I Active Low DD4 Band Plan 4 (V/U Selection)

35 I Active Low DD3 Band Plan 3 (445/435 Selection)

36 I Active Low DD2 Band Plan 2 (5k/12.5k Selection)

37 I Active Low DD1 Band Plan 1

38 I Active Low DD0 Band Plan 0

39 O Clock SCL Clock Output for EEPROM

DTD For Trunking

Page-5

Page 6

Port No. I/O Logic PinName Description

h

h

40 I/O Clock SDA Data Output for EEPROM

41 O Clock CLK Clock Output

42 O Clock DAT DataOutput

43 O Clock ST1 Strobe Output for PLL IC

44 O Clock ST2 Strobe Output for CTCSS IC

45 I Active Low SFT Shift Key Input

46 I Active Hig

47 O Active Hig

SD Signal Detection Input

H/L Transmission Power (H: Low Power)

48 I Active Low V/M VFO/Memory Key Input

49 I Active Low CAL Call Key Input

50 I Active Low CTC CTCSS Mode Set Input

51 I Active Low REV Reverse Key Input

52 I Active Low FNC Function Key Input

53 I Active Low MHz MHzKeyInput

54 I Active Low PTT PTTKeyInput

55 I LV3 Power Supply Input for LCD

56 I LV2 Power Supply Input for LCD

57 I LV1 Power Supply Input for LCD

58 I COM0 LCD Common 0 Output

59 I COM1 LCD Common 1 Output

60 I COM2 LCD Common 2 Output

61 I No Use

62 O SEG00 LCD Segment 00 Output

63 O SEG01 LCD Segment 01 Output

64 O SEG02 LCD Segment 02 Output

65 O SEG03 LCD Segment 03 Output

66 O SEG04 LCD Segment 04 Output

67 O SEG05 LCD Segment 05 Output

68 O SEG06 LCD Segment 06 Output

69 O SEG07 LCD Segment 07 Output

70 O SEG08 LCD Segment 08 Output

71 O SEG09 LCD Segment 09 Output

72 O SEG10 LCD Segment 10 Output

73 O SEG11 LCD Segment 11 Output

74 O SEG12 LCD Segment 12 Output

75 O SEG13 LCD Segment 13 Output

76 O SEG14 LCD Segment 14 Output

77 O SEG15 LCD Segment 15 Output

78 I ActiveHigh UL UnlockInput

79 I Analog SM SignalMeterInput

80 O SEG18 LCD Segment 18 Output

Page-6

Page 7

Page-8

Page 8

Page-9

Page 9

Page-10

Page 10

Page-11

Page 11

Page-12

Page 12

Page-13

Page 13

Page-14

Page 14

Page-15

Page 15

Page-16

Page 16

Page-17

Page 17

Page 18

FF0028

ES0017

KZ0047AZ

FM0152

FF0031

KS0041B

Page-19

Page 19

FM0152

FF0030

SS0052B

FP0034

NK0009B

NK0010A

Page-20

Page 20

VERSION TABLE

1)CPU UNIT

W1 W2 W3/W4 R284

T JP - - - 0 - - - UE0165 E JP JP - 0 0 - - - UE0165 EZ JP JP - - 0 - lK 1K EA - - - 0 0 - - - UE0165 TA - - - - 0 - - - UE0165 TE1 - - JP - - - - - UE0165 TE2 - - JP - - - - - UE0165 -

TX Free RX Free Tranking 12.5k/5k Tranking V/U

R294/R295

R286 R296 R297 CN204 IC208

2) MAIN UNIT

C71,7

C7 C43 C62 C63 C68

T/E/EZ/EA/TA 1000p 33p 47p 10u/16V 15p 47p 22p 22p TE1 - 33p 100p 100u/16V 22p 56p 22p 12p 0.01uF

TE2 - 47p 33p 100u/16V 10p 1000p 18p 10p 0.01uF

C150

153 154

155 156 C151 C152 D4

T/E/EZ/EA/TA - - - - 1SV215 lSS355 S-AV7 QA0084

TE1 1000p 10u/20V 10u/35V lSS355 1SV215 lSS355 M67781L QA0084

TE2 1000p 10u/20V 10u/35V lSS355 1SV214 - M67781H QA0100

L12 P3 R43 R57 R101 R102 R111 R121 R122 R130 W5

T/E/EZ/EA/TA QKA35D - 47k 22 15k 1k 0 - - 47k TE1 QKA35D 0 47k 100 2.2k 4.7k - - 220 - JP

TE2 QKA45D 0 27k 100 2.2k 4.7k - 0 220 - JP

D11 12

13 16 D15 lC5 L4,5,6,14

4,75,7 C112 C139 C149

AT24CO8-10SI

3) VCO UNIT

C315 C331 C332 D304 R315 R316 R332 R333 R334

T/E/EZ/EA/TA 3p - - - 10k 100 - - TE1 3p 4700p 0.5p 1SV215 22k 56 8.2k 8.2k 220k

TE2 1p 4700p 0.5p 1SV215 22k 56 10k 8.2k 220k

Page-21

Page 21

C

A

A

A

C

C

A

A

A

A

A

C

A

C

C

A

A

C

C

C

A

C

C

C

C

2: TE2

None: all models page-22

NAIN Unit NAIN Unit

l C105 CE0340 EIectrolytic.C 16MV 47HC+TS CU3035 Chip C. C1608JB1H102KTA l,2

0 C104 CU3035 Chip C. C1608JB1H102KTA C156 - 0

2 C106 CU3012 Chip C. C1608CH1H120DTA CN1 UE0191 Connector 11PSJE

16MV 10HW+TS C101 CU3047 Chip C. C1608JB1H103KTA C155 - 0

16MV l0HW+TS 0 C107 CU3035 Chip C. C1608JB1H102KTA CN2 UE0191 Connector 11PSJE

16MV 100HC+TS 1,2 C108 CU3035 Chip C. C1608JB1H102KTA CN3 UE0043 Connector PI22A02M

0 CC5020 Ceramic C. DD05-979SL-1 80J 500 2 XD0254 Diode 1SS355 1,2

1 C113 CU3035 Chip C. C1608JB1H102KTA D5 XD0130 Diode DA204U T106

2 C114 CU3035 Chip C. C1608JB1H102KTA D6 XD0130 Diode DA204U T106

l C118 CE0339 EIectrolytic.C 16MV10HW+TS D11 XD0132 Diode 1SV215TPH4 0,1

0 C117 CU3035 Chip C. C1608JB1H102KTA D10 XD0254 Diode 1SS355

l C123 CU7003 Chip C. C3K31NAR102K XD0131 Diode 1SV214TPH4 2

l C126 CU3064 Chip C. C1608CH1H1R5CTA - 2

0 C125 CU3035 Chip C. C1608JB1H102KTA D15 XD0254 Diode 1SS385 0,1

16MV 10HW+TS CU3020 Chip C. C1608CH1H560JT

16MV 1000HC+T CU3035 Chip C. C1608JB1H102KTA 2 C124 CU3035 Chip C. C1608JB1H102KTA D14 XD0246 Diode DAN235U T106

16MV 470HC+TS C75 CU3019 Chip C. C1608CH1H470JT

l C129 CU3035 Chip C. C1608JB1H102KTA D17 XD0250 Diode MA742-TX

16MV 47HC+TS CU3035 Chip C. C1608JB1H102KTA 2 C127 CU3035 Chip C. C1608JB1H102KTA D16 XD0132 Diode 1SV215TPH4 0.1

50MV 2R2SW+TS C76 CU3019 Chip C. C1608CH1H470JT^ 0 C128 CU3035 Chip C. C1608JB1H102KT XD0131 Diode 1SV214TPH4 2

16MV 47HC+TS CU3020 Chip C. C1608CH1H560JT

16MV 10HW+TS C78 CU3035 Chip C. C160GJB1H102KTA C132 CE0339 EIectrolytic.C 16MV10HW+TS D20 XD0145 Diode DTZ2.2A TT11

16MV l0HW+TS C85 CU3035 Chip C. C1608JB1H102tCTA C140 CS0232 Chip Tantal TMCMA1V474MTR 1C5 XA0185 lC S-AV17 0

16MV 10HW+TS C92 CU3019 Chip C. C1608CH1H470JTA CU3035 Chip C. C1608JB1H102KTA 1.2

16MV 10HW+TS C93 CU3035 Chip C. C1608JB1H102KTA C151 - 0 0 : T/E/EZ/EA/TA

NAIN Unit C54 CS0237 Chip Tantal TMCMA1A475MTR C95 CU3035 Chip C. C1608JB1H102KTA C152 - 0

PARTS LIST

Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver

C1 CU3035 Chip C. C1608JB1H102KTA C55 CU3035 Chip C. C1608JB1H102KTA C96 CU3035 Chip C. C1608JB1H102KTA CS0375 Chip Tantal TMCME1V106MTR 1,2

C2 CU3044 Chip C. C1608JB1H562KTA C56 CU3011 Chip C. C1608CH1H100CTA C97 CU3019 Chip C. C1608CH1H470JTA C153 - 0

C3 CU3100 Chip C. C1608JB1C393ZTA C57 CU3031 Chip C. C1608JH1H471KTA C98 CU0027 Chip C. C2012CH1H470K CU3035 Chip C. C1608JB1H102KTA l,2

C4 CU3044 Chip C. C1608JB1H562KTA C58 CU3035 Chip C. C1608JB1H102KTA C99 CU3019 Chip C. C1608CH1H470JrTA C154 - 0

- - 1,2 C62 CU3019 Chip C. C1608CH1H470JT

C5 CU3002 Chip C. C1608CH1H010CTA C59 CU3018 Chip C. C1608CH1H390JTA C100 CU3035 Chip C. C1608JB1H102KTA CU3035 Chip C. C1608JB1H102KTA l,2

C6 CU3002 Chip C. C1608CH1H010CTA C60 CE0339 EIectrolytic.

C7 CU3035 Chip C. C1608JB1H102KTA 0 C61 CU3022 Chip C. C1608CH1H820JTA C103 CU3012 Chip C. C1608CH1H120DTA CU3035 Chip C. C1608JB1H102KTA 1,2

C8 CS0049 Chip Tantal TMCSA1C105MTR CU3023 Chip C. C1608CH1H101JT

C10 CU3059 Chip C. C1608JF1E104ZTA C63 CE0339 EIectrolytic.

C9 CU3059 Chip C. C1608JF1E104ZTA CU3017 Chip C. C1608CH1H330JT

C11 CU3047 Chip C. C1608JB1H103KTA CE0341 EIectrolytic.

C12 CU3047 Chip C. C1608JB1H103KTA C64 CU3005 Chip C. C1608CH1H040CTA C109 CU3003 Chip C. C1608CH1H020CTA D1 XD0136 Diode DTZ5.1ATT11

C13 CU3047 Chip C. C1608JB1H103KTA C65 CC5068 Ceramic C. RCC06SL390J-L46AU C110 CU3003 Chip C. C1608CH1H020CTA D2 XD0014 Diode Ml308

C14 CU3047 Chip C. C1608JB1H103KTA C66 CC5068 Ceramic C. RCC06SL390J-L46AU C111 CU3035 Chip C. C1608JB1H102KTA D3 XD0013 Diode Ml407

C17 CU3059 Chip C. C1608JF1E104ZTA CU3015 Chip C. C1608CH1H220JT

C18 CU8042 Chip C. C2012JB1C104KTA CU3011 Chip C. C1608CH1H100CT

C20 CU3035 Chip C. C1608JB1H102KTA C69 CU3035 Chip C. C1608JB1H102KTA C115 CU3023 Chip C. C1608CH1H101JTA D8 XD0254 Diode 1SS385

C15 CU3047 Chip C. C1608JB1H103KTA C67 CC5068 Ceramic C. RCC06SL390J-L46AU C112 CC5064 Ceramic C. RCC05S L220J-L46AE 0,1 D4 - 0

C16 CU3102 Chip C. C1608JB1C333KTA C68 CU3013 Chip C. C1608CH1H150JT

C21 CU3028 Chip C. C1608CH1H271KTA C70 CU3015 Chip C. C1608CH1H220JTA C116 CU3035 Chip C. C1608JB1H102KTA D9 XD0107 Diode G3B

C22 CU3035 Chip C. C1608JB1H102KTA C71 CU3019 Chip C. C1608CH1H470JT

C23 CU3047 Chip C. C1608JB1H103KTA CU3020 Chip C. C1608CH1H560JT

C24 CU3059 Chip C. C1608JF1E104ZTA CU3035 Chip C. C1608JB1H102KTA 2 C119 CE0338 EIectrolytic.C 25MV 4R7SW+TS XD0131 Diode 1SV214TPH4 2

C25 CU3102 Chip C. C1608JB1C333KTA C72 CS0049 Chip Tantal TMCSA1C105MTR C120 CU3035 Chip C. C1608JB1H102KTA D12 XD0132 Diode 1SV215TPH4 0,1

C26 CU3047 Chip C. C1608JB1H103KTA C73 CU3035 Chip C. C1608JB1H102KTA C121 CU3035 Chip C. C1608JB1H102KTA XD0131 Diode 1SV214TPH4 2

C27 CU3049 Chip C. C1608JB1E153KTA C74 CU3019 Chip C. C1608CH1H470JT^ 0 C122 CE0341 EIectrolytic.C 16MV 100HC+TS D13 XD0132 Diode 1SV215TPH4 0.1

C28 CE0339 EIectrolytic.

C30 CE0342 EIectrolytic.

C31 CS0049 Chip Tantal TMCSA1C105MTR CU3020 Chip C. C1608CH1H560JT

C29 CE0343 EIectrolytic.

C33 CE0337 EIectrolytic.

C32 CE0340 EIectrolytic.

C34 CE0340 EIectrolytic.

C35 CU3035 Chip C. C1608JB1H102KTA CU3035 Chip C. C1608JB1H102KTA 2 C130 CU3039 Chip C. C1608JB1H222KTA D18 XD0250 Diode MA742-TX

C36 CU3047 Chip C. C1608J81H103KTA C77 CU3015 Chip C. C1608CH1H220JTA C131 CU3036 Chip C. C1608JB1H102KTA D19 XD0130 Diode DA204U T106

C38 CE0339 EIectrolytic.

C39 CU3031 Chip C. C1608JH1H471KTA C79 CU3047 Chip C. C1608JB1H103KTA C133 CU3035 Chip C. C1608JB1H102KTA FL1 XC0001 Filter CFW455F

C40 CS0049 Chip Tantal TMCSA1C105MTR C80 CU3005 Chip C. C1608CH1H040CTA C134 CU3023 Chip C. C1608CH1H101JTA FL2 XF0015 Filter UM1-172M

CU3019 Chip C. C1608CH1H470JTA 2 C84 CU3035 Chip C. C1608JB1H102KTA CC5058 Ceramic C. DC05-979SL100J500 2 1C4 XA0079 lC uPC124lH

C4l CU3047 Chip C. C1608JB1H103KTA C81 CU3047 Chip C. C1608JB1H103KTA C135 CU3023 Chip C. C16C8CH1H101JTA 1C1 XA0068 lC M5218FP-T01-1

C42 CU3035 Chip C. C1608JB1H102KTA C82 CU3035 Chip C. C1608J81H102KTA C139 CC5064 Ceramic C. RCC05SL220J-L46A E 0 1C2 XA0082 lC MC7808CT

C43 CU3017 Chip C. C1608CH1H330JTA 0.1 C83 CU3035 Chip C. C1608JB1H102KTA CC5059 Ceramic C. DD05-979SL120J500 1 1C3 XA0144 IC TK10487M

C44 CE0339 EIectrolytic.

C45 CU3035 Chip C. C1608JB1H102KTA C86 CU3035 Chip C. C1608JB1H102KTA C141 CU3035 Chip C. C1608JB1H102KTA XA0273 IC M67781L 1

C46 CU3059 Chip C. C1608JF1E104ZTA C87 CU3035 Chip C. C1608JB1H102KTA C147 CS0236 Chip Tantal TMCMA0J685MTR XA0274 IC M67781H 2

C47 CS0049 Chip Tantal TMCXSA1C105MTR C88 CU3064 Chip C. C1608CH1H1R5CTA C148 - 1C6 XA0119 lC AN8010M-E1

C48 CU3035 Chip C. C1608JB1H102KTA C89 CU3035 Chip C. C1608JB1H102KTA C149 - 0 JK1 UA0037 Connector R-B2.0'0.2 Plug 15A

C49 CU3024 Chip C. C1608CH1H121KTA C90 CU3035 Chip C. C1608JB1H102KTA CU3047 Chip C. C1608JB1H103KTA 1,2

C50 CU3019 Chip C. C1808CH1H470JTA C9l CU3035 Chip C. C1608JB1H102KTA C150 - 0

C52 CE0339 EIectrolytic.

C53 CS0049 Chip Tantal TMCSA1C105MTR C94 CS0049 Chip Tantal TMCSA1C105MTR CS0227 Chip Tantal TMCMC1D106MTR 1.2 1: TE1

C51 CE0339 EIectrolytic.

Page 22

MAIN Unit MAIN Unit

Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver

JK2 UE0190 Connector ANT Cable R1 RK0108 Chip R. ERJ6GEYJ2R2V R55 RK3050 Chip R. ERJ3GSYJ103V R111 - 1.2

QA0100 Coil 2 R7 RK3042 Chip R. ERJ3GSYJ222V R60 RK3034 Chip R. ERJ36SYJ471V R121 - 0,1

JK4 UJ0024 Connector SJ1403JDIJ010 R2 RK2024 Chip R. MCR50JZHJ471 R56 RK3050 Chip R. ERJ3GSYJ103V R112 RK3049 Chip R. ERJ3GSYJ822V

L1 QC0063 Coil NL322522TJ047M R3 RK3050 Chip R. ERJ3GSYJ103V R57 RK3018 Chip R. ERJ3GSYJ220V 0 R113 RK3050 Chip R. ERJ3GSYJ103V

L2 QC0063 Coil NL322522TJ347M R4 RK307l Chip R. ERJ3GSYJ564V RK3026 Chip R. ERJ3GSYJ101V 1,2 R114 RK3062 Chip R. ERJ3GSYJ104V

L3 QC0048 Coil NL322522T-100K R5 RK3034 Chip R. ERJ3GSYJ471V R58 RK3038 Chip R. ERJ3GSYJ102V R115 RK3038 Chip R. ERJ3GSYJ102V

L4 QA0084 Coil 0,1 R6 RK3062 Chip R. ERJ3GSYJ104V R59 RK3053 Chip R. ERJ3GSYJ183V R116 RK3023 Chip R. ERJ3GSYJ560V

QA0100 Coil 2 R9 RK3001 Chip R. ERJ3GSYJ000V R62 RK3054 Chip R. ERJ3GSYJ223V R122 - 0

L5 QA0084 Coil 0,1 R8 RK3042 Chip R. ERJ3GSYJ222V R61 RK3038 Chip R. ERJ3GSYJ102V RK3001 Chip R. ERJ3GSYJ000V 2

L6 QA0084 Coil 0,1 R10 RK3071 Chip R. ERJ3GSYJ564V R63 RK3032 Chip R. ERJ3GSYJ331V RK3030 Chip R. ERJ3GSYJ221V 1.2

QA0100 Coil 2 R11 RK3046 Chip R. ERJ3GSYJ472V R64 RK3042 Chip R. ERJ3GSYJ222V l R123 RK3038 Chip R. ERJ3GSYJ102V

L7 QC0067 Coil N L322522T-R10M R12 RK3038 Chip R. ERJ3GSYJ102V R65 RK3026 Chip R. ERJ3GSYJ101V R130 RK3058 Chip R. ERJ3GSYJ473V 0

L8 QC0063 Coil N L322522T-047M R13 RK3038 Chip R. ERJ3GSYJ102V R66 RK3050 Chip R. ERJ3GSYJl03V - 1.2

L9 QKA45E Coil MR 3.0 4.5 T 0.8 R14 RK3071 Chip R. ERJ3GSYJ564V R67 RK3026 Chip R. ERJ3GSYJ101V R131 RK3042 Chip R. ERJ3GSYJ222V 2

L10 QKA45E Coil MR 3.0 4.5 T 0.8 R15 RK3050 Chip R. ERJ3GSYJ103V R68 RK3030 Chip R. ERJ3GSYJ221V TCl CT0012 Trimmer CTZ-10AW

L11 QKA45E Coil MR 3.0 4.5 T 0.8 R16 RK4028 Chip R. ERJ-12YJ151 R69 RK3050 Chip R. ERJ3GSYJ103V TH1 XS0012 Thermistor TD5-C220DH

R18 RK3042 Chip R. ERJ3GSYJ222V R71 RK3026 Chip R. ERJ3GSYJ101V VR1 RH0106 Trim. Pot EVM1YSX50BQ4

QA0100 Coil 2 R21 RK3051 Chip R. ERJ3GSYJ123V R75 RK3052 Chip R. ERJ3GSYJ153V VR5 RH0106 Trim. Pot EVM1YSX50BQ4

L12 QKA35D Coil R17 RK3057 Chip R. ERJ3GSYJ393V R70 RK3051 Chip R. ERJ3GSYJ123V TH2 XS0013 Thermistor TD5-C2680DH

L13 QKA95D Coil MR3.09.5T0.6 R19 RK3060 Chip R. ERJ3GSYJ683V R73 RK3052 Chip R. ERJ3GSYJ153V VR2 RH0103 Trim. Pot EVMIYSX50B14

L14 QA0084 Coil 0,1 R20 RK3060 Chip R. ERJ3GSYJ683V R74 RK3052 Chip R. ERJ3GSYJ153V VR4 RH0060 Trim. Pot MVR32HXBRN473

L15 QC0067 Coil N L322522T-R10M R22 RK3050 Chip R. ERJ3GSYJ103V R76 RK3026 Chip R. ERJ3GSYJ101V VR6 RH0061 Trim. Pot MVR32HXBRN472

L16 QKA35D Coil MR3.03.5T0.6 R23 RK3050 Chip R. ERJ3GSYJ103V R77 RK3050 Chip R. ERJ3GSYJ103V X1 XQ0054 Crystal X49U-12.8MHz

M106 SD0034 Earth Spdrg DR130 R24 RK3050 Chip R. ERJ3GSYJ103V R78 RK3026 Chip R. ERJ3GSYJ101V X2 XK0002 Discrinbnator CDBM455C7

Q1 XE0012 FET 3SK131V11. 12T1 R25 RK3047 Chip R. ERJ3GSYJ562V R79 RK3038 Chip R. ERJ3GSYJ102V X3 XQ0059 Crystal X49U-16.745MHz

Q2 XE0012 FET 3SK131V11. 12T1 RK3046 Chip R. ERJ3GSYJ472V 2 R80 RK3050 Chip R. ERJ3GSYJ103V TS0092 VC0 Shield

Q3 XT0094 Transistor 2SA1576 T106R R26 RK3026 Chip R. ERJ3GSYJ101V R81 RK3052 Chip R. ERJ3GSYJ153V TT1001 Tube 0.7 1mm x 6

Q4 XT0095 Transistor 2SC4081 T106R R27 RK3038 Chip R. ERJ3GSYJ102V R82 RK3038 Chip R. ERJ3GSYJ102V TZ0049 Silicon Dumper

Q5 XT0095 Transistor 2SC408l T106R R28 RK3058 Chip R. ERJ3GSYJ473V R83 RK3022 Chip R. ERJ3GSYJ470V TZ0056 Silicon Dumper 49U

Q6 XT0095 Transistor 2SC4081 T106R R29 RK3042 Chip R. ERJ3GSYJ222V R84 RK3034 Chip R. ERJ3GSYJ471V YZ0001 Silicon Grease G746

Q7 XT0061 Transistor 2SB1132 T100Q R30 RK3045 Chip R. ERJ3GSYJ392V R85 RK3043 Chip R. ERJ3GSYJ272V

Q8 XT0096 Transistor 2SC4099 T106N R31 RK3054 Chip R. ERJ3GSYJ223V R86 RK3045 Chip R. ERJ3GSYJ392V

Q9 XT0037 Transistor 2SC2412K T146R R32 RK3057 Chip R. ERJ3GSYJ393V R88 RK3014 Chip R. ERJ3GSYJ100V

Q10 XU0131 Transistor DTC114EU T106 R33 RK3038 Chip R. ERJ3GSYJ102V R89 RK0028 Chip R. ERJ6GSYJ471V

Qll XU0148 Transistor DTC144EU T106 R34 RK4018 Chip R. ERJ-12YJ220 R91 RK3001 Chip R. ERJ3GSYJ000V

Q12 XU0112 Transistor DTA114YU T106 R35 RK3050 Chip R. ERJ3GSYJ103V R92 RK3038 Chip R. ERJ3GSYJ102V

Q13 XT0112 Transistor 2SBl292F R36 RK3038 Chip R. ERJ3GSYJ102V R93 RK3062 Chip R. ERJ3GSYJ104V

Q14 XT0095 Transistor 2SC408l T106R R37 RK3045 Chip R. ERJ3GSYJ392V R94 RK3050 Chip R. ERJ3GSYJ103V

Q15 XT0084 Transistor 2SC2954-Tl R38 RK3054 Chip R. ERJ3GSYJ223V R96 RK3071 Chip R. ERJ3GSYJ564V

Q16 XT0095 Transistor 2SC408l Tl06R R39 RK3032 Chip R. ERJ3GSYJ331V R98 RK0069 Chip R. ERJ6GSYJ104V

Q17 XU0152 Transistor UMC5TR R40 RK3054 Chip R. ERJ3GSYJ223V R99 RK3052 Chip R. ERJ3GSYJ153V

Q18 XE0001 Transistor 2SK880GR TE85L R41 RK3042 Chip R. ERJ3GSYJ222V R100 RK3044 Chip R. ERJ3GSYJ332V

Q19 XT0114 Transistor 2SC4403 R42 RK3041 Chip R. ERJ3GSYJ182V R101 RK3052 Chip R. EFU6GSYJ153V 0

Q20 XT0030 Transistor 2SCX3BB6-T1 R43 RK3058 Chip R. ERJ3GSYJ473V 0 RK0039 Chip R. ERJ6GSYJ222V l,2

Q2l XT0099 Transistor 2SA1736Y TEl2L RK3055 Chip R. ERJ3GSYJ273V 2 R102 RK3038 Chip R. ERJ3GSYJ102V 0

Q22 XT0095 Transistor 2SC4081 T106R R44 RK3014 Chip R. ERJ3GSYJ100V RK3046 Chip R. ERJ3GSYJ472V l.2

Q24 XU013l Transistor DTCl14EUTl06 R45 RK3026 Chip R. ERJ3GSYJ101V R103 RK3026 Chip R. ERJ3GSYJ101V

R47 RK3062 Chip R. ERJ3GSYJ104V R105 RK3042 Chip R. ERJ3GSYJ222V

R48 RK3026 Chip R. ERJ3GSYJ10lV R106 RK3062 Chip R. ERJ3GSYJ104V 0 : T/E/EZ/EA/TA

R49 RK3038 Chip R. ERJ3GSYJ102V R107 RK0001 Chip R. ERJ6GSYJ100V 1: TE1

R50 RK3071 Chip R. ERJ3GSYJ564V R108 RK3043 Chip R. ERJ3GSYJ272V 2: TE2

R51 RK3054 Chip R. ERJ3GSYJ223V R109 RK3062 Chip R. ERJ3GSYJ104V None: all models page-23

Q30 XU0148 Transistor DTC144EU R46 RK3001 Chip R. EFU3GSYJ000V R104 RK3050 Chip R. ERJ3GSYJ103V

R53 RK3044 Chip R. ERJ3GSYJ332V R111 RK3001 Chip R. ERJ3GSYJ000V 0

R54 RK4034 Chip R. ERJ-12YJ471

Page 23

C

C

0 : T/E/EZ/EA/TA

2: TE2

None: all models page-24

E/EA

R287 RK3001 Chip.R ERJ3GSYJ000V 1: TE1

EZ RK3001 Chip.R ERJ3GSYJ000V

ECEVICA100R IC201 XA0289 IC M37410M6H R230 RK3038 Chip.R ERJ3GSYJ102V R294 RK3001 Chip.R ERJ3GSYJ000V 0

ECEVICA100R R203 RK3072 Chip.R ERJ3GSYJ684V R257 RK3001 Chip.R ERJ3GSYJ000V X203 XQ0045 Crystal DSMT3.58MHz18P

CPU Unit Ref No Parts No. Description Parts Name Ver R224 RK3055 Chip.R ERJ3GSYJ273V R288 RK3052 Chip.R ERJ3GSYJ153V

C207 CU3035 Chip C. C1608JB1H102KTA 1C202 XA0364 IC AT24CO2N-10SI-2.7 R231 RK3038 Chip.R ERJ3GSYJ102V - - 1.2

C208 CS0232 Chip Tantal TMCMAI V474MTR IC205 XA0238 IC AN78L05M R232 RK3050 Chip.R ERJ3GSYJ103V R295 RK3001 Chip.R ERJ3GSYJ000V 0

C209 CU3035 Chip C. C1608JB1H102KTA IC206 XA0208 IC RH5VA45AA-T1 R234 RK3038 Chip.R ERJ3GSYJ102V - - 1,2

C210 CU3035 Chip C. C1608JB1H102KTA lC207 XA0198 IC RH5VA32AA-T1 R235 RK3038 Chip.R ERJ3GSYJ102V R296 - -

C211 CU3035 Chip C. C1608JB1H102KTA IC208 - R236 RK3074 Chip.R ERJ3GSYJ105V RK3038 Chip.R ERJ3GSYJ102V EZ

C212 CU3035 Chip C. C1608JB1H102KTA XA0367 IC AT24CO8-10SI-2.7 EZ R238 RK3038 Chip.R ERJ3GSYJ102V R297 - -

C213 CU3035 Chip C. C1608JB1H102KTA lC209 XA0236 IC BU4052BF R239 RK3082 Chip.R ERJ3GSYJ104V RK3038 Chip.R ERJ3GSYJ102V EZ

C215 CU3035 Chip C. C1608JB1H102KTA JK201 UE0035 Connector FM214-8SMPY R241 RK3062 Chip.R ERJ3GSYJ104V S201 UU0015 Switch SKQD-90l

C216 CU3059 Chip C. C1608JF1E104ZTA EL0024 LCDDRW1 R242 RK3062 Chip.R ERJ3GSYJ104V S202 UU0015 Switch SKQD-901

C217 CU3051 Chip C. C1608JB1E223KTA PL201 EP0003 Lamp BQO3l-30403A R243 RK3062 Chip.R ERJ3GSYJ104V S203 UU0015 Switch SKQD-901

C218 CU3059 Chip C. C1608JF1E104ZTA PL202 EP0003 Larnp BQO31 -30403A R244 RK3062 Chip.R ERJ3GSYJ104V S204 UU0015 Switch SKQD-90l

C219 CU3059 Chip C. C1608JF1E104ZTA Q201 XT0095 Transistor 2SC4081 TlO6R R247 RK3050 Chip.R ERJ3GSYJ103V S205 UU0015 Switch SKQD-901

C220 CU3059 Chip C. C1608JF1E104ZTA Q202 XT0113 Transistor 2SC2873Y TE1 2L R248 RK3050 Chip.R ERJ3GSYJ103V S206 UU0015 Switch SKOD-90l

C221 CU3023 Chip C. C1608CH1H101JTA Q203 XU0029 Transistor DTC114YU T106 R249 RK305O Chip.R EFu3GSYJ103V S207 UU0015 Switch SKQD-901

C222 CU3023 Chip C. C1608CH1H101JTA Q204 XU0145 Transistor DTC143TU T106 R250 RK3046 Chip.R ERJ3GSYJ472V S209 UQ0011 Switch ESBJ64801

C223 CU3051 Chip C. C1608JB1E223KTA Q205 XU0112 Transistor DTA114YU T106 R251 RK3046 Chip.R ERJ3GSYJ472V S210 UR0002 Switch EVQ-WQGFl 524B

C225 CU3023 Chip C. C1608CH1H101JTA Q206 XU0112 Transistor DTA114YU T106 R252 RK3046 Chip.R ERJ3GSYJ472V VR201 RV0009 Trim. Pot EVU-F2AF20B14

C226 CU3023 Chip C. C1608CH1H101JTA Q208 XU0060 Transistor UMC2TR R253 RK3038 Chip.R ERJ3GSYJ102V VR20 RV0009 Trim. Pot EVU-F2AF20B14

C227 CU3035 Chip C. C1608JB1H102KTA Q209 XU0112 Transistor DTA114YU T106 R254 RK3038 Chip.R ERJ3GSYJ102V W1 MACL04AA #30 Blue 02JD40-02

C229 CS0209 Chip Tanta[ TMCMB0J 106MTR R201 RK3062 Chip.R ERJ3GSYJ104V R255 RK0014 Chip.R ERJ3GSYJ000V T/E/EZ

C230 CU3035 Chip C. C1608JB1H102KTA R202 RK3052 Chip.R ERJ3GSYJ153V R256 RK3042 Chip.R ERJ3GSYJ222V W2 MRCL04AA #30 Red 02JD40-02 EAEZ

C231 CE0312 EIectrolytic.

C234 CU3035 Chip C. C1608JB1H102KTA R204 RK3052 Chip.R ERJ3GSYJ158V R258 RK3046 Chip.R ERJ3GSYJ472V DG0003 LCD Light

C235 CU3047 Chip C. C1608JB1H103KTA R205 RK3043 Chip.R ERJ3GSYJ272V R259 RK3054 Chip.R ERJ3GSYJ223V FG0133 LCD Rubber Connector

C236 CU3031 Chip C. C1608JH1H471KTA R206 RK3026 Chip.R ERJ3GSYJ101V R260 RK3038 Chip.R ERJ3GSYJ102V FM0077 LCD Hokk!r

C237 CU3035 Chip C. C1608JB1H102KTA R207 RK3038 Chip.R ERJ3GSYJ102V R261 RK3038 Chip.R ERJ3GSYJ102V FP0034 Mic ebnnector SpacN>r

C238 CU3035 Chip C. C1608JB1H102KTA R208 RK3026 Chip.R ERJ3GSYJ101V R262 RK3038 Chip.R ERJ3GSYJ102V FP0069 Crystal Sheet

C239 CU3023 Chip C. C1608CH1H101JTA R209 RK3074 Chip.R ERJ3GSYJ105V R263 RK3038 Chip.R ERJ3GSYJ102V TL0008 LCD Finer

C240 CU3023 Chip C. C1608CH1H101JTA R210 RK3052 Chip.R ERJ3GSYJ153V R264 RK3038 Chip.R ERJ3GSYJ102V TT1002 Tube Tube 1mm x 12

C241 CU3023 Chip C. C1608CH1H101JTA R211 RK3062 Chip.R ERJ3GSYJ104V R265 RK3050 Chip.R ERJ3GSYJ103V YZ0042 Adhesion Bond G17

C242 CU3035 Chip C. C1608JB1H102KTA R212 RK3054 Chip.R ERJ3GSYJ223V R267 RK3038 Chip.R ERJ3GSYJ102V

C243 CS0237 Chip Tanta1 TMCMAI A475MTR R213 RK3070 Chip.R ERJ3GSYJ474V R268 RK3038 Chip.R ERJ3GSYJ102V

C244 CU3051 Chip C. C1608JB1E223KTA R214 RK3058 Chip.R ERJ3GSYJ473V R269 RK3054 Chip.R ERJ36SYJ223V

C245 CS0237 ChlPTantal TMCMAI A475MTR R215 RK3102 Chip.R ERJ3GSYJ203V R270 RK3001 Chip.R ERJ3GSYJ000V

C246 CU3035 Chip C. C1608JB1H102KTA R216 RK3050 Chip.R ERJ3GSYJ103Y R271 RK3062 Chip.R ERJ3GSYJ104V

C247 CU3085 Chip C. C1608CH1H300JTA R217 RK3102 Chip.R ERJ3GSYJ203V R272 RK3058 Chip.R ERJ3GSYJ473V

C248 CU3085 Chip C. C1608CH1H300JTA R218 RK3050 Chip.R ERJ3GSYJ103Y R273 RK3058 Chip.R ERJ3GSYJ473V

C249 CS0218 ChipTantal TMCMDI A476MTR R219 RK3102 Chip.R EFU3GSYJ203V R274 RK3038 Chip.R ERJ3GSYJ102V

C250 CU3043 Chip C. C1608JB1H472KTA R220 RK3050 Chip.R ERJ3GSYJ103Y R275 RK3062 Chip.R ERJ3GSYJ104V

C251 CU3043 Chip C. C1608JB1H472KTA R221 RK3102 Chip.R ERJ3GSYJ203V R276 RK3034 Chip.R ERJ3GSYJ471V

C252 CU3059 Chip C. C1608JF1E104ZTA R222 RK3102 Chip.R ERJ3GSYJ203V R277 RK3034 Chip.R ERJ3GSYJ471V

CN201 UE0170 Connector B9B-ZR R223 RK3058 Chip.R ERJ3GSYJ473V R279 RK3001 Chip.R ERJ3GSYJ000V

CN2 UE0192 Connector 11R-JE R280 RK3038 Chip.R ERJ3GSYJ102V

CN2 UE0192 Connector 11RJE R281 RK3038 Chip.R ERJ3GSYJ102V

CPU Unit CPU Unit

Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver

C201 CU3035 Chip C. C1608JB1H102KTA D201 XD0255 Diode MA8110H R225 RK3046 Chip.R ERJ3GSYJ472V R289 RK3052 Chip.R ERJ3GSYJ153V

C202 CU3035 Chip C. C1608JB1H102KTA D202 XD0127 Diode MA704WA TX R226 RK3070 Chip.R ERJ3GSYJ474V R290 RK3052 Chip.R ERJ3GSYJ153V

C203 CU3035 Chip C. C1608JB1H102KTA D203 XD0230 Diode DAN202UTl06 R227 RK3038 Chip.R ERJ3GSYJ102V R291 RK3052 Chip.R ERJ3GSYJ153V

C204 CU3035 Chip C. C1608JB1H102KTA D204 XD0230 Diode DAN202UT106 R228 RK3038 Chip.R ERJ3GSYJ102V R292 RK3052 Chip.R ERJ3GSYJ153V

C205 CU310l Chip C. C1608JB1C473KTA D205 XL0029 LED TLSG264 R229 RK3038 Chip.R ERJ3GSYJ102V R293 RK3050 Chip.R ERJ3GSYJ103V

C206 CE0312 EIectrolytic.

CN2 UE0165 Connector B4B-ZR R284 - - -

Page 24

A

T/EZ

/TA

HU0075 Fixture (B)

E/EA

2: TE2

None: all models page-25

1,2 R332 - 0 TS0080 Front Shield Case PR0215 Seat EZ

VCO Unit Q303 XT0111 Transistor 2SC4081 LN T106S SP Unit Others

Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver

C301 CU3013 Chip C. C1608CHIH Q304 XT0096 Transistor 2SCAO99T 106N ES0017 Speaker VS-57-O814-1.5W EMS-5A Microphone (E/EZ/EA)

C302 CU3016 Chip C. C1608CHIH Q305 XT0096 Transistor 2SC4099T 106N FG0040 Speaker Cushion EMS-11 Microphone T/TA

C303 CU3035 Chip C. C1608JB1H102KTA Q306 XU0060 Transistor UMC2TR UX1047 Wire DS0260 Specifications Card T/TA

C304 CS0063 Chip Tantal TMCSAI V104MTR R301 RK3022 ChIPR. ERJ3GSYJ470V EJ19u DS0280 Specifications Card E/EA

C305 CU3035 Chip C. C1608JB1H102KTA R302 RK3034 Chip R. ERJ3GSYJ47lV C401 CU3035 ChlP.C C1608JB1H102KTA DS0281 Specifications Card EZ

C306 CU3047 Chip C. C1608JB1H103KTA R303 RK3034 Chip R. ERJ3GSYJ471V IC401 XA0367 IC AT24CO8-10SI-2.7 PH0009 Registration Card T

C307 CU3035 Chip C. C1608JB1H102KTA R306 RK3046 Chip R. ERJ3GSYJ472V R401 RK3038 ChlP.R ERJ3GSYJ102V PR0157 Seal TA

C308 CS0235 Chip Tantal TMCSA 1V334MTR R307 RK3058 Chip R. ERJ3GSYJ473V R402 RK3038 Chip.R ERJ3GSYJ102V PR0161 Seal EA

C3O9 CU3043 Chip C. C1608JB1H472KTA R308 RK3046 Chip R. ERJ3GSYJ472V FG0057 Cushion Packing

C310 CU3043 Chip C. C1608JB1H472KTA R309 RK3046 Chip R. ERJ3GSYJ472V UX1049 Wire EJl9u AA0013 Screw M5+20 FeCr

C311 CS0220 Chip Tantal TMCMA1C225MTR R310 RK3040 Chip R. ERJ3GSYJ152V Mechanical Parts AE0012 Screw Fe3PM4x8BC

C312 CS0220 Chip Tantal TMCMA1C225MTR R311 RK3044 Chip R. ERJ3GSYJ332V AD0010 Screw D3+8FeNi AN0002 Nut Nut M-5FeCr

C313 CU3035 Chip C. C1608JB1H102KTA R312 RK3026 Chip R. ERJ3GSYJ101V AE0014 Screw B2.6+8FeBG AJ0093 Screw M5+20FeCr

CU3002 Chip C. C1608CH1H010CTA 2 I R315 RK3050 Chip R. ERJ3GSYJ103V 0 FF0015 Light Shield Cloth EF0005 Fuse FGBO15A

C314 CU3043 Chip C. C1608JB1H472KTA R313_ RK3044 Chip R. ERJ3GSYJ332V AJ0017 Screw 2.6+6FeNi2 _ AZ0009 Washer Sprirg SW-5FeCr

C315 CU3004 Chip C. C1608CH1H030CTA 0,1 R314 RK3022 Chip R. ERJ3GSYJ470V AK0003 Screw OB2.6+ FeNi1 AZ0010 W-5FeCr

C316 CU3035 Chip C. C1608JB1H102KTA RK3054 Chip R. ERJ3GSYJ223V 1,2 FF0021 Volume Tape ADFM78 Bracket

C317 CS0217 Chip Tantal TMCMC 1A226MTR R316 RK3026 Chip R. ERJ3GSYJ101V 0,1 FF0028 Cloth FM0079 Spanner

C318 CU3003 Chip C. C1608CH1HO20CTA RK3023 Chip R. ERJ3GSYJ560V 2 FF0030 Cloth HH0042 CushionDR130

C319 CU3035 Chip C. C1608JB1H102KTA R317 RK3018 Chip R. ERJ3GSYJ220V FF0031 Cloth HK0306 Item Carton DR130 T/TA

C320 CU3015 Chip C. C1608CH1H220JTA R318 RK3050 Chip R. ERJ3GSYJ103V FG0138 Rubber Cushin DR130 HK0308 Item Cafbn DR130

C321 CU3031 Chip C. C1608JB1H471KTA R319 RK3038 Chip R. EFU3GSYJ102V FM0152 IC Spring E/EA/EZ

C322 CU3035 Chip C. C1608JB1H102KTA R320 RK3044 Chip R. ERJ3GSYJ332V FM0083 Washer Spnrg Washer

C323 CU3015 Chip C. C1608CH1H220JTA R321 RK300l Chip R. ERJ3GSYJ000V ND0004 Dlal Cover HP0006 (Screw set) Protection Bag

C324 CU3035 Chip C. C1608JB1H102KTA R322 RK3034 Chip R. ERJ3GSYJ47lV NK0009B Dial Knob HP0009 (Code) Protection Bag

C325 CU3035 Chip C. C1608JB1H102KTA R323 RK3054 Chip R. ERJ3GSYJ223V NK0010 VolurTN3i Knob HP0016 (Button cover) Protection Bag

C326 CU3059 Chip C. C1608JF1E104ZTA R324 RK3034 Chip R. ERJ3GSYJ471V NP0066 Power Switch Knob HP0028 (Instr. card) Protection Bag

C328 CU3035 Chip C. C1608JB1H102KTA R325 RK3054 Chip R. ERJ3GSYJ223V KS0041B Bottom Case HP0037 (Brackt) Protection Bag

C329 CU3035 Chip C. C1608JB1H1O2KTA R326 RK3026 Chip R. ERJ3GSYJ101V KZ0001B Front Panel DR130T HP0035 (Radio) Protection Bag

C330 CU3035 Chip C. C1608JB1H102KTA R327 RK3026 Chip R. ERJ3GSYJ10lV HU0073 Fixture (A) DR130

CU3043 Chip C. C1608JB1H472KTA 1,2 R329 RK3026 Chip R. ERJ3GSYJ101V KZ0009A Top Case KZ0003 Button Cover

CU3001 Chip C. C1608CH1HOR5CT

C331 - 0 R328 RK3043 Chip R. ERJ3GSYJ272V KZ0004B Front Panel DR130E

CN301 UE0188 Connector B9P-BC-2 RK3049 Chip R. ERJ3GSYJ821V 1 PS0181 Instrution Card E/EA

CN302 UE0185 Connector B6P-BC-2 RK3050 Chip R. ERJ3GSYJ103V 2 PS0182 Instrution Card

D301 XD0l32 Diode 1SV215TPH4 R333 - 0 (T/TA/TE1/TE2/EZ)

C332 - 0 R331 RK3038 Chip R. ERJ3GSYJ102V SS0052C Chassis PK0047 Schematic Diagram

D302 XD0132 Diode 1SV215TPH4 RK3050 Chip R. ERJ3GSYJ821V 1,2 PT0004A Lot Nurrdber Sear

XD0132 Diode 1SV215TPH4 1.2 TS0081 Case VCO Case YZ0121 Tape 10mm

D303 XD0130 Diode DA204UT106 R334 - 0 ADUA38 R-B2.x3M Receptacle 15A

D304 - 0 RK3066 Chip R. ERJ3GSYJ224V l,2 YZ0118 Tape 50mm

QC0043 Coil NL322522T-2R2J-3 2

IC301 XA0235 IC M56760FP

L302 QA0067 Coil QA0067

L303 QC0044 Coil NL322522T-3R3M 1

QC0040 Coil NL322522T-1R2J-3 2

L304 QC0044 Coil NL322522T-3R3M 1

L305 QC0045 Coil NL322522T-3R3M

QC0043 Coil NL322522T-2R2J-3

Q301 XE0010 FET 2SK5O8K52-T2B 0 : T/E/EZ/EA/TA

Q302 XT0111 Transistor 2SC4081 LN T106S 1: TE1

Page 25

C

A

Wire #28A02-020-02

A

Wire #28Y02-020-02

0 : T/E/EZ/EA/TA

1: TE1

2: TE2

None: all models page-26

MS56.3V IOOuF C3 CU8003 Chip C. C2012JF1E104Z AP0008 Screw PM3+8FeBC

EJ20u EMS-5A EMS-11 AJ0013 Screw 1M2.3+12FeCr

HK0305 Carton

HP0029 Protection Bag

PG0057 Rubber Cushion

UP0243a P.C.B.

EJ20u /EMS-5A EMS-11

Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver Ref No Parts No. Description Parts Name Ver

C501 CS0236 Chip TantaI TMCMAOJ685MTR C1 CC5029 Ceramic C. X1E393KYA C1 CU8003 Chip C. C2012JF1E104Z AJ0025 Screw 1M3.5+10FeN

C502 CU3059 Chip C. C1608JF1E104ZTA C2 CK0011 Ceramic C. SC45J1C104Z-A C2 CU8035 Chip C. C2012 B1E393K AP0004 Screw PM2+5FeCr

C503 CS0230 Chip Tantal TMCMA1E105MTR C3 CE0037 EIectrolytic.

C504 CU3059 Chip C. C1608JF1E104ZTA C4 CK0003 Ceramic C. 50V102 C4 CU8012 Chip C. C2012JB1H471KTA DE0007 Stopper

C505 CS0230 Chip Tanta1 TMCMA1E105MTR Dl XD0067 Diode MA700 C5 CU8012 Chip C. C2012JB1H471KTA EY0006 Microphone WM-6OAT

C506 CS0230 Chip TantaI TMCMA1E105MTR Rl RD0031 Reststor R20 1/4W 680 C6 CU8016 Chip C. C2012JB1H102K FG0045 MIC Rubber Cushion

C507 CS0230 ChlPTantaI TMCMA1E105MTR R2 RD0021 Reststor R20 1/4W 180 C7 CE0315 EIectrolytic.C ECEV1CA470P FG0055 Rubber Switch

C508 CU3023 Chip C. C1608CH1H10lJTA R3 RD0039 Reststor R20 1/4W 2.2K C8 CK0004 Ceramic C. CK45-F1H102ZTA HP0036 Protection Bag

C509 CS0237 ChlP TantaI TMCMA1A475MTR R4 RD0039 Resistor R20 1/4W 2.2K ClO CS0066 Chip Tantal TMCSB 1D225MTR KB0033 Rear Case

C510 CU3019 Chip C. C1608CH1H470JTA R6 RD0040 Resistor R20 1/4W 2.7K FAR1 XB000l Crystal FARC4CA0358000K01R KM0153 Front Case

C511 CU3035 Chip C. C1608JB1H102KTA S1 US0015 Switd1 HSWO880-01-210 ICl XA0042 IC LR40872 NP0041 PTT Button

C512 CU3015 Chip C. C16O8CH1H220KTA S2 UU0009 Switch EVQ-QHJ04G Q1 XT0031 Tansistor 2SC2712Y TE85L NP0042 Up Button

C513 CU3015 Chip C. C1608CH1H220KTA S3 UU0009 Switch EVQ-QHJ04G R1 RK0062 ChIPR. ERJ6GEYJ473V NP0043 Down Button

CN501 UX1050 Wire EJ20u S4 UM0002 Switch MICn Switch SS-5 R2 RK0062 ChIPR. ERJ6GEYJ473V NS0003 Slide Switch

IC501 XA0239 IC AK2341 AS0142 Screw Set R3 RK0035 ChipR. ERJ6GEYJlO2V SC0004 PTT Spring

Q501 XT0095 Tansistor 2SC4081 T106R DE0006 Stopper R4 RK0039 ChipR_ ERJ6GEYJ222V TT1002 Tube 1.Ox1mm

R501 RK3040 Chip R. ERJ3GSYJ152V EY0006 Microphone WM-60AT R5 RK0039 ChipR_ ERJ6GEYJ222V UE0125A Curl Code EMS3

R502 RK3022 Chip R. ERJ3GSYJ470V FG0045 Mic Rubber Cushion R7 RK0039 ChipR_ ERJ6GEYJ222V UP0183B P.C.B.

R503 RK3067 Chip R. ERJ3GSYJ274V HP0036 ProtectIOn Bag R8 RK0021 ChIPR. ERJ6GEYJ181V

R504 RK3038 Chip R. ERJ3GSYJ102V KB0033 Rear Case R9 RK0040 ChipR. ERJ6GEYJ272V

R505 RK3051 Chip R. EFJ3GSYJ123V KM0071 Front Case R10 RK0069 ChipR. ERJ6GEYJ104V

R506 RK3089 Chip R. ERJ3GSYJ912V NP0041 PTT Button R15 RK0025 ChlPR. Efu6GEYJ331V

R507 RK3067 Chip R. ERJ3GSYJ274V NP0042 Up Button R16 RK3001 ChipR. ERJ3JSYJ000V

R508 RK3047 Chip R. ERJ3GSYJ562V NP0043 Down Button R17 RK3001 ChipR. ERJ3JSYJ000V

R509 RK3068 Chip R. ERJ3GSYJ334V NS0003 Slide Knob SW1 UM0002 Switch Micro Switch SS-5

R510 RK3054 Chip R. ERJ3GSYJ223V SC0004 PTT Sprirg SW2 UU0009 Switch EVQJQHJ-04G

R511 RK3054 Chip R. ERJ3GSYJ223V UE0051A Curl Code SW3 UU0009 Switch EVCLQHJJO4G

R515 RK3048 Chip R. ERJ3GSYJ682V W2 MYCK02

VR501 RH0106 Trim. Pot EVM1YSX50BQ4

R512 RK3055 Chip R. ERJ3GSYJ273V UP0193 P.C.a. SW4 US0015 Switch HSWO880JD1 -210

R513 RK3074 Chip R. EFU3GSYJ105V UX0133 Wire EMS-5 VR1 RH0031 Trim. Pot CVR42A-103AW1D

X501 XQ0057 Crystal DS-MAT3.6864MHz

R514 RK3066 Chip R. ERJ3GSYJ224V W1 MACK02

YZ0042 Adhesion Bond G17

Page 26

ADJUSTMENT

y

1) Required Test Equipment

1. Digital Multimeter

Voltage range: FS= 18V or so Input level: Up to 40dB

Input resistance: 1M ohm or more Distortion level: 1% - l00%

2. Regulated Power Suppl

Supply voltage: 13.80V Output frequency: 88.5Hz and lkHz

Current : 15A or more Output impedance: 600 ohm, unbalanced

11. Distortion Meter

Measurable frequency 1kHz

12. Audio Generator

3. Oscilloscope

Measurable frequency: DC to 30MHz

4. Spectrum Analyzer

Measuring range: Up to 2GHz or more CN: 60dB or more

13. Linear Detector

Measurable frequencyUp to 500MHz

Characteristics: FIat

5. Tracking Generator

Output frequency: Up to 2GHz or more

6. Audio Dummy Load

Impedance: 8 ohm

Dissipation: 5W or more

7. SSG

Output frequency: 1GHz or more

Output level: -20dB/0.1uV to 120dB/1V

Moduration: FM

8. Frequency Counter

Measurable frequency.I Up to 500MHz

Measurements stability: 0.2ppm or so

9. Power Meter

Measurable frequency.I Up to 500MHz

Impedance: 50 ohm, unbalanced

Measuring range: Full scale of 60W or so

10. Audio Voltmeter

Measurable frequency: 50Hz to 10kHz

Sensitivity: 1mV ~ 10V

Page-27

Page 27

2) Adjustment for DR130

SSG Mod:1KHz +/-3.5KHz/DEV

SP terminal is connected to 8ohm dummy load.

RX speaker output level is 50 to 100mW

1. Power supply voltage is 13.8V. Power switch is off.

2. Turn the squelch and volume knobs counterclockwise.

3. Press and hold the "F"key,then turn on the power switch.

The display shows that the frequency is 145.00MHz

PLL Adjustment

Condition Measurement Adjustment Specification/

Item Test equipmen Unit Terminal Unit Parts Method Remarks

Frequency Frequency:145.00MHz Freq.Counter 145.00 +/- 100Hz

power: Low *1 Power Meter Back ANT MAIN TC1 MHz

PTT: ON

PLL VCO Frequency:145.00MHz Digital Main SD PLL L302 2.0V 1.8-2.2V

PTT: OFF *1 Multimeter VCO Check 0.7-1.0V

RX Adjustment (ALL SSG out =EMF)

Condition Measurement Adjustment Specification/

Item Test equipmen Unit Terminal Unit Parts Method Remarks

Frequency:145.03MHz L4-L6 SINAD: Turn the coil L14,

SSG out:0dBu *1 L14 MAX L4,L5,L6,L4,L5 to

SSG the MAX in order

RX Frequency:145.03MHz Distortion Meter

Sensitivity SSG out:-10dBu *1 Main TP1 Main SINAD is above12dB

Frequency:134.00MHz Check

SSG out:-2.0dBu *2

Frequency:174.00MHz

SSG out:-2.0dBu *3

Frequency:145.03MHz Full

S Meter SSG out: 15dBu *1 Main VR5 flashing

Mod: OFF LCD S Meter Front

Frequency:145.03MHz Panel

SSG out:0dBu *1 Check S Meter does not

Mod: OFF light.

Frequency:145.03MHz Front Make

SQL SSG out:-10dBu *1 LCD Busy Panel Main sure that

SQL is Busy ON

SQL VR:Threshold open

*1 or bond-center of your radio version

*2 or bond lower limit of your radio version

*3 or bond upper limit of your radio version

Page-28

Page 28

TX Adjustment

r

e

Condition Measurement Adjustment Specification/

Item Test equipmen Unit Terminal Unit Parts Method Remarks

VR1: max

Power:High

PTT: ON

High Power Frequency:145.00MHz 52w

Power:High *1 VR1 +/- 1.0W

PTT: ON Power Meter Back ANT Main Below 10.5A

Frequency:130.00MHz Above 5W

Power:High *2 Check (T.E.EZ)

PTT: ON

Frequency:174.00MHz Above 5W

or 155MHz Check (T.E.EZ)

Power:Low *3

PTT: ON

Frequency:130.00MHz

Low Power Power:Low *1 VR5 5.0w +/- 0.5W

PTT: ON (T.E.EZ)

Frequency:145.00MHz

DEV Power: Low *1 VR2 4.7kHz 4.7 +/-0.2kHz/Dev

AG:1KHz -30dBm /Dev

PTT: ON

Frequency:145.00MHz AG

MIC Gain Power: Low *1 Linear Detecto

AG:1KHz -47dBm Power Meter /Dev

PTT: ON

Frequency:145.00MHz

CTCSS Ton

DEV AG: OFF

Tone Burst Power: Low *1 Check 2.5-3.5kHz/Dev

DEV AG: OFF

Power: Low *1 Check 0.60-0.85kHz/Dev

PTT: ON

ToneSW(88.5Hz):ON

Frequency:145.00MHz

PTT: ON

ToneSW:ON

Back ANT Main 4.0kHz 4.0 +/-0.2kHz/Dev

*1 or bond-center of your radio version

*2 or bond lower limit of your radio version

*3 or bond upper limit of your radio version

If the logic boad EJ-21D or EJ21D exists ,first pull out the logic board

and re-connect W3,W4,W5, so that the radio comes back to conventional

Page-29

Page 29

3) Adjustment Points

4) Adjustment Quick Reference

SSG Output = EMF

Parts Item Specifications Specifications

L4 RX Sensitivity -10dBpV (12dB SINAD) -10dBpV (12dB SINAD)

L5 RX Sensitivity -10dBpV (12dB SINAD) -10dBpV (12dB SINAD)

L6 RX Sensitivity -10dBpV (12dB SINAD) -10dBpV (12dB SINAD)

L14 RX Sensitivity -10dBpV (12dB SINAD) -10dBpV (12dB SINAD)

L302 VCO Frequency 1.8V~2.2V 1.8V~2.2V

TC1 Reference Frequency 145.00MHz +/-100Hz 145.00MHz +/-100Hz

VR1 TX High Power 52W +/- 1.0W 52W +/- 1.0W

10.5W +/- 0.5W (EZ) 10.5W +/- 0.5W (EZ)

VR2 Deviation 4.7kHz +/-0.2kHz 2.4kHz +/-0.1kHz

VR4 Mic Gain 4.0kHz +/-0.2kHz 2.0kHz +/-0.1kHz

VR5 S Meter 15dBu "Full" 15dBu "Full"

VR6 TX LowPower 5W+/-0.5W 5W+/-0.5W

Page 30

Page 30

Page 31

Page 32

Page 33

Page-34

Page 34

Page 35

Page 36

Page 37

Page 38

Loading...

Loading...