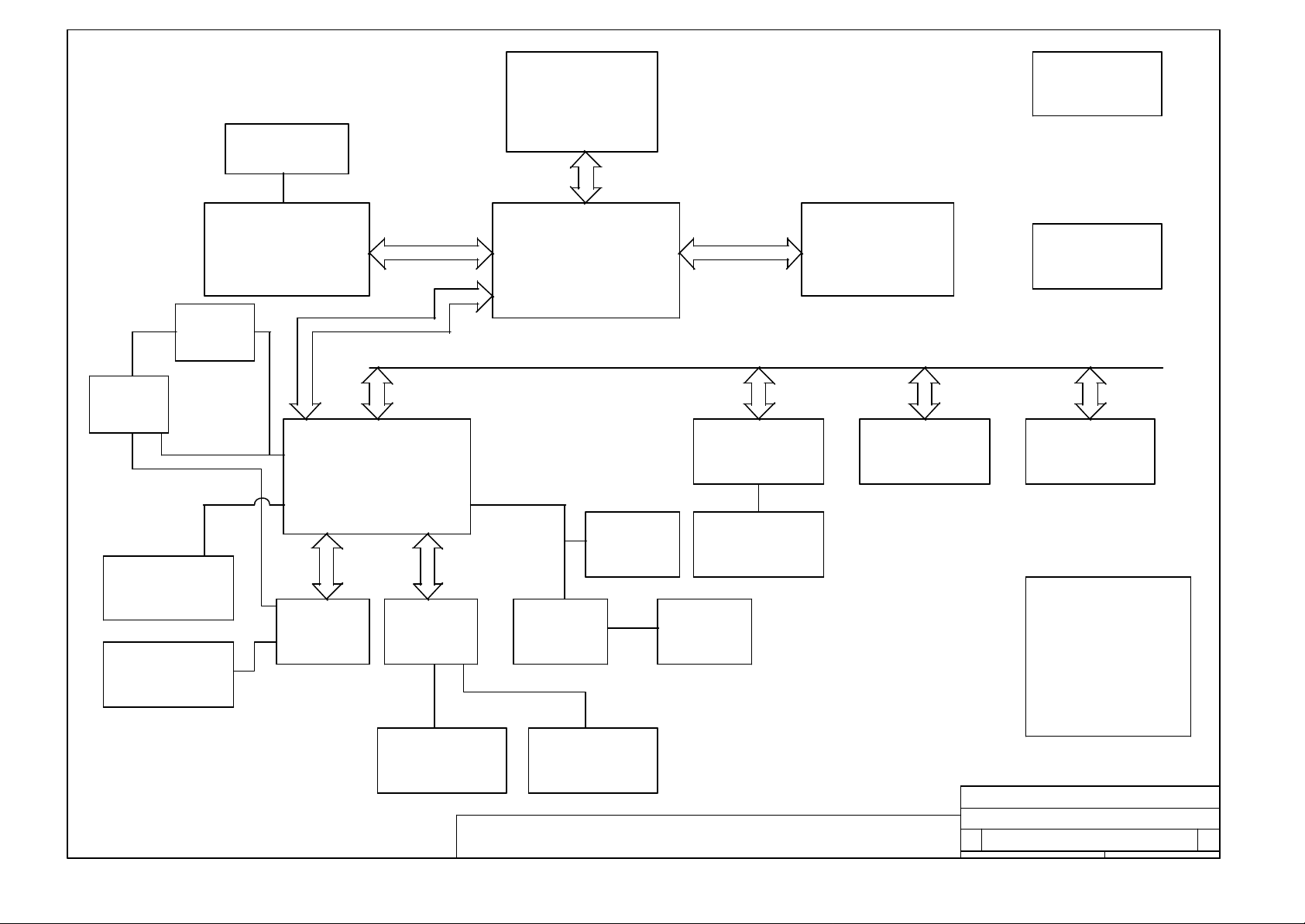

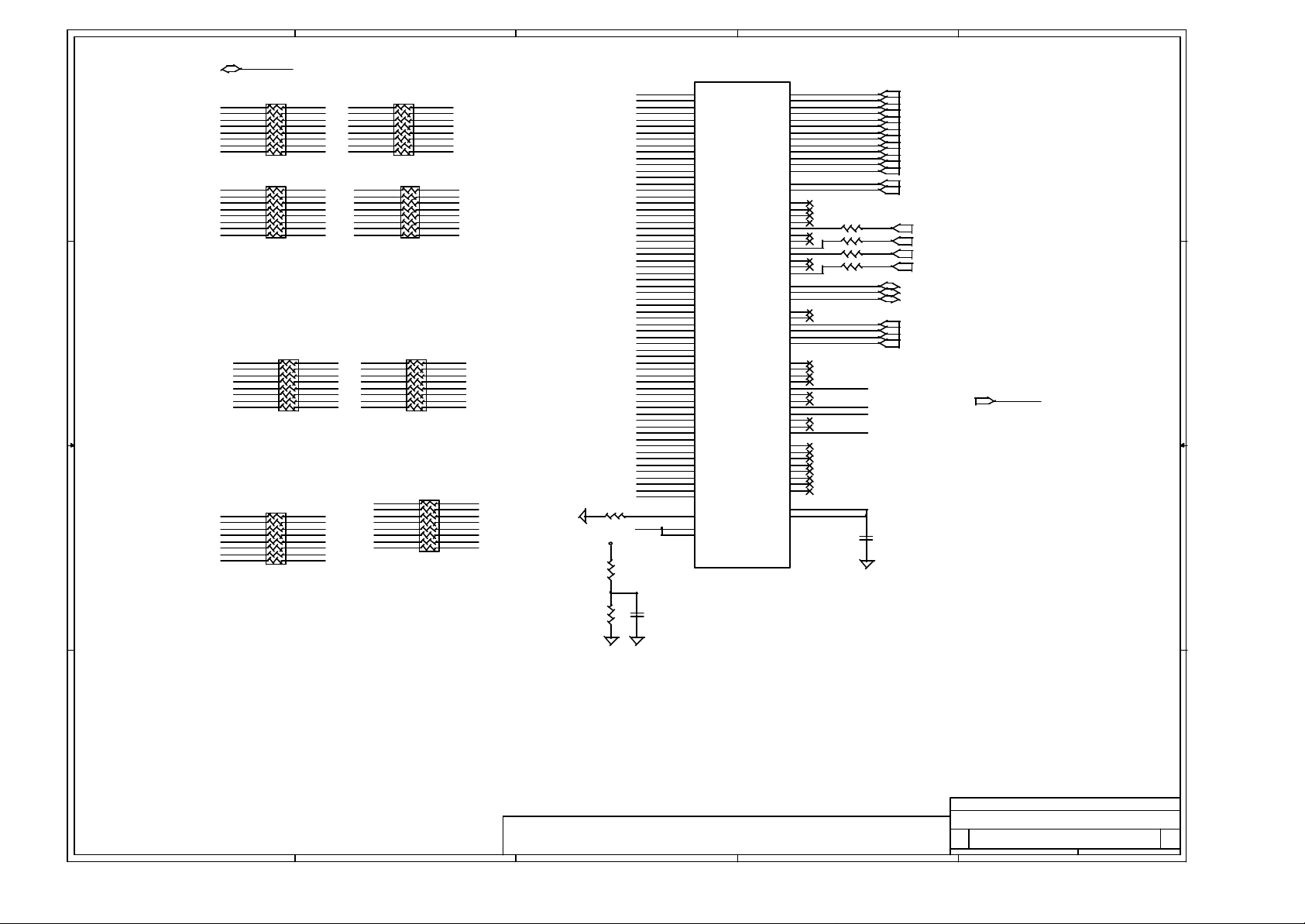

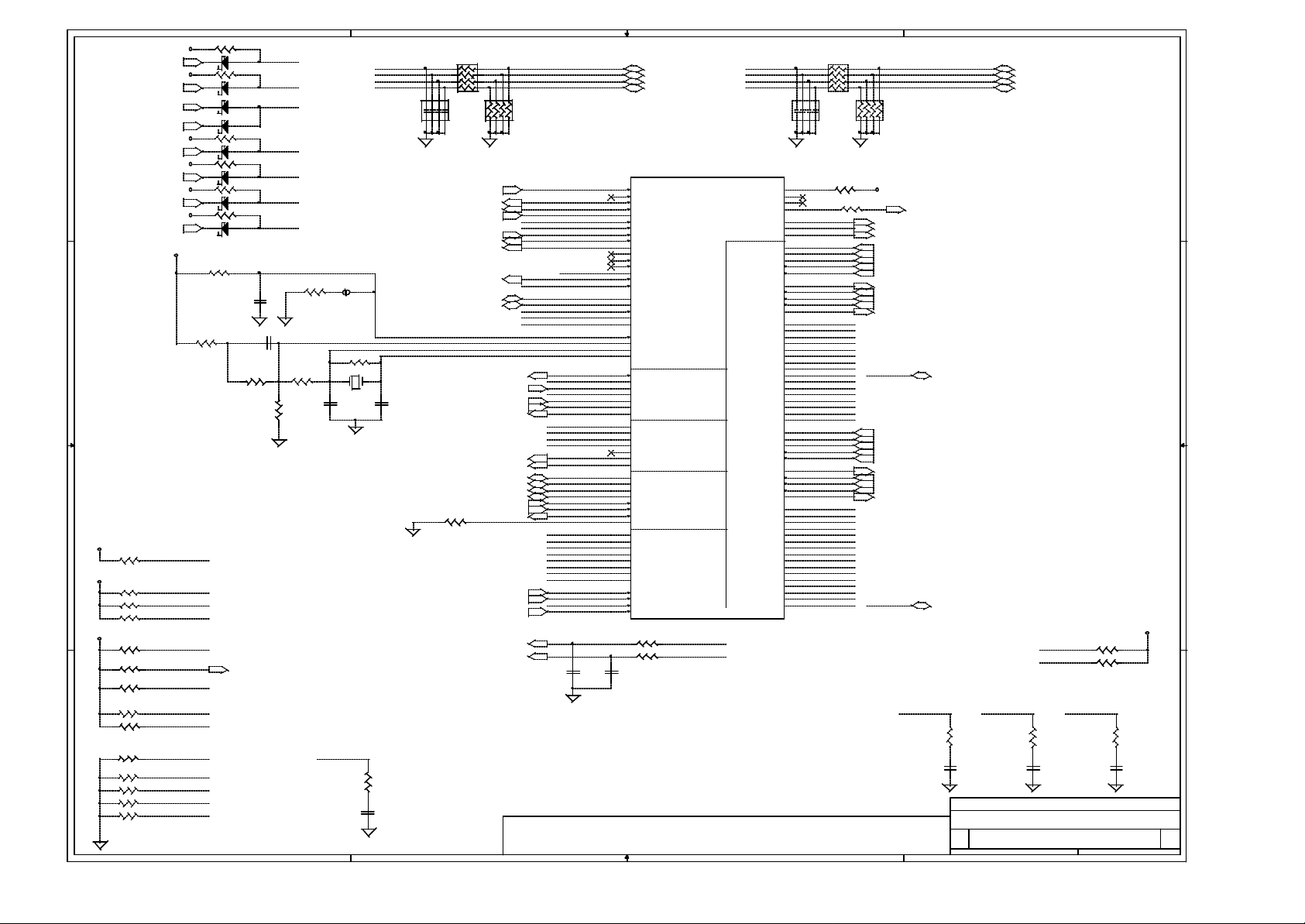

Acer TravelMate 1400XV Schematics

COMPAL CONFIDENTIAL

MODEL NAME : ACR10 LA-1252

REV:1.0

CRT & TV-OUT

LCD

PAGE 16

Pentium4/Northwood

mPGA478 CPU

PAGE 2,3

PSB

CLOCK

ICS950805

PAGE 11

INTERNAL IDE

IDE/CD

/FDD

PAGE 22

USB/BlueTooth

LPT PORT

MDC

ATI M6P

16MB DDR SDRAM

PIRQA#

Direct CD

Play

PAGE 21

PAGE 25

PAGE 24

PAGE 12,13,14,15

HUB Link

ICH2

FUNC 0: LAN, HUB-TO-PCI ,

PCI-TO-LPC BRIDGE

FUNC 1: IDE Controller

FUNC 2: USB Controller #1

FUNC 3: SM BUS Controller

FUNC 4: USB Controller #2

FUNC 5: AC97 Audio Controller

FUNC 5: AC97 Modem Controller

LPC

SIO

LPC 47N227

PAGE 23

PCI BUS

PAGE 8,9,10

LPC

EC/KBC

PC87591

PAGE 28

BIOS

EC BUFFER

Brookdale

MCH

Host-AGP Bridge

DRAM controller

Hub interface

AC LINK

MDC

Connector

AC97 Codec

PAGE 26 PAGE 27

Switchs &

Connectors

PAGE 29 PAGE 30

PROPRIETARY NOTE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PAGE 4,5,6

PAGE 12

MEMORY BUSAGP BUS

AMP &

Audio Jack

CARDBUS

PCI1420

PCMCIA

SOCKET

PC133

SODIMM X2

BANK2,3,4,5

IDSEL: AD16

MASTER 3

PIRQA#, PIRQB#

SIRQ

PAGE 17

PAGE 18

PAGE 7

LAN Controller

INTEL PHY

PAGE 19

POWER

INTERFACE

PAGE 30

IDSEL: AD27

MASTER 0

PIRQA#,

PIRQD#

Mini PCI

Connector

PAGE 20

DC/DC POWER

+1.5V POWER

+1.8V POWER

+2.5V POWER

+3VALW POWER

+5VALW POWER

+12VALW POWER

CPU_VCC PO WER

PAGE 33,34,35,36,37,38

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1252

Size Document Number Rev

B

401219

星期三 九月

Date: Sheet of

1 39, 04, 2002

1A

A

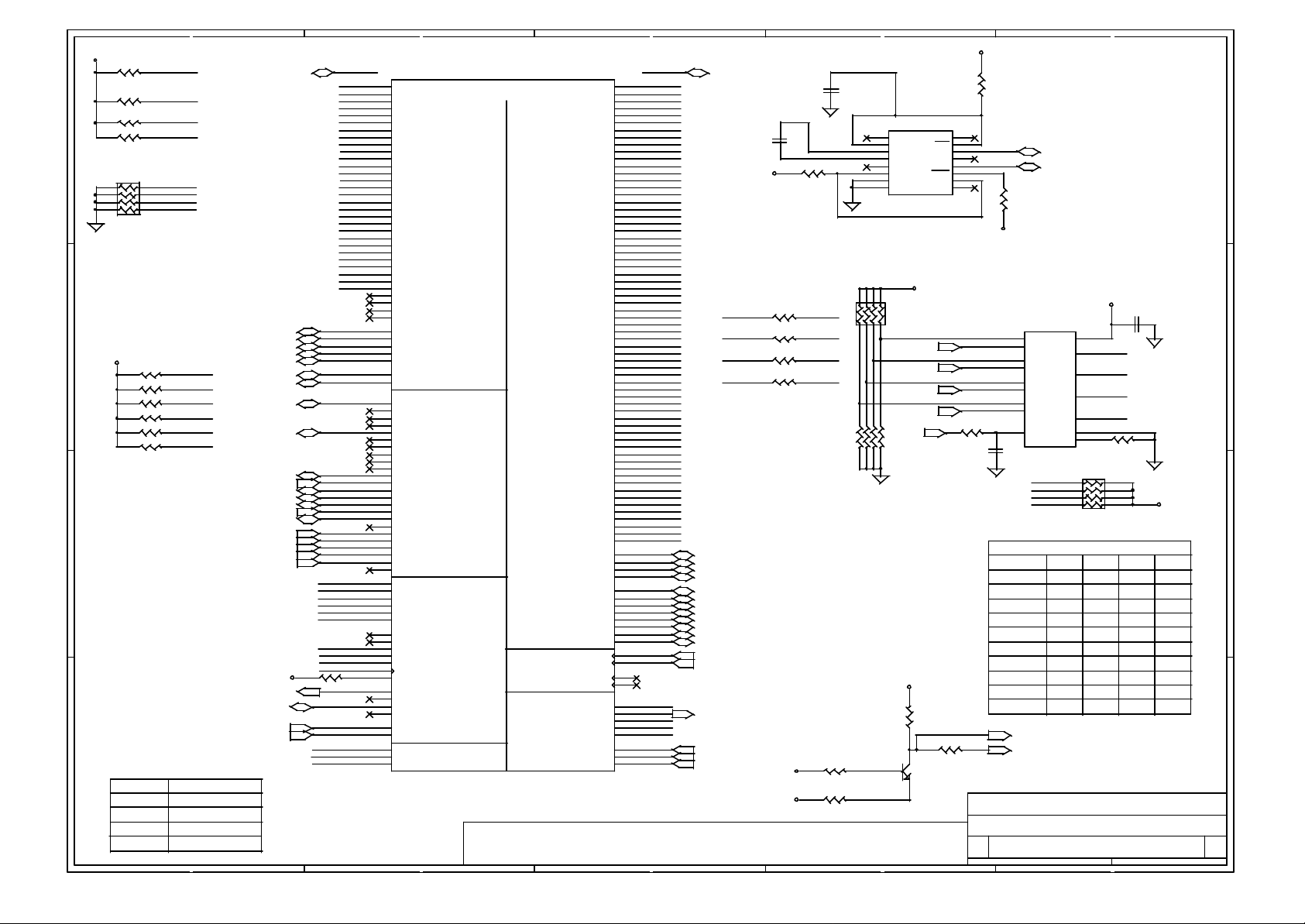

CPU_VCC

1 2

R274 51_1%

1 2

R91 56

1 2

R280 300

1 2

R290 51_1%

4 4

1 8

2 7

3 6

4 5

3 3

CPU_VCC

2 2

1 1

CPURST#

FERR#

CPU_PWRGD

BREQ0#

RP5

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_TDI

8P4R-1K

1 2

R250 51_1%

1 2

R251 51_1%

1 2

R262 51_1%

1 2

R253 51_1%

1 2

R254 51_1%

1 2

R263 51_1%

SELPSB[1:0] STSEM BUS FREQUENCY

00

01

10

11

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

CPU_PWRGD8

100MHZ

RESERVED

RESERVED

RESERVED

A

HREQ#04

HREQ#14

HREQ#24

HREQ#34

HREQ#44

ADSTB0#4

ADSTB1#4

BREQ0#4

HLOCK#4

HIT#4

HITM#4

DEFER#4

DRDY#4

CPURST#4

HTRDY#4

CPU_VCC

BSEL011

DBSY#4

CPUSLP#8

HA#[3..31]4

ADS#4

BNR#4

BPRI#4

RS#04

RS#14

RS#24

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

BREQ0#

CPURST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

1 2

R82 @62_1%

BSEL0

CPU_PWRGD

CPUSLP#

THERMDA

THERMDC

THERMTRIP#

M6

M3

M4

M1

W1

W2

AB1

G1

AC1

AA3

G2

AC3

J26

K25

K26

L25

G4

AB25

G5

AB2

AC6

AB5

AC4

AA5

AB4

AF26

AD6

AD5

AE25

AB23

AB26

K2

K4

L6

K1

L3

L2

N1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

T5

U4

V3

Y1

J1

K5

J4

J3

H3

L5

R5

V5

H6

D2

F3

E3

E2

H2

V6

J6

F1

F4

Y6

D5

C1

F7

E6

D4

C3

H5

B3

C4

A2

U23A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

ADSTB1#

ADS#

AP0#

AP1#

BINIT#

BNR#

IERR#

DP0#

DP1#

DP2#

DP3#

BREQ0#

BPRI#

LOCK#

HIT#

HITM#

DEFER#

DRDY#

MCERR#

RESET#

TRDY#

RS0#

RS1#

RS2#

RSP#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SKTOCC#

TDO

TDI

TMS

TRST#

TCK

PROCHOT#

BSEL0

BSEL1

DBSY#

DBR#

PWRGOOD

SLP#

THERMDA

THERMDC

THERMTRIP#

mPGA478

B

ADDR GROUP

CONTROL GROUP

THERMAL DIODE

B

Northwood

MISC

PROPRIETARY NOTE

C

HD#[0..63]

HD#0

B21

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

DATA GROUP

HOST CLK

LEGACY CPU

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI0#

DBI1#

DBI2#

DBI3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

BCLK0

BCLK1

ITPCLK0

ITPCLK1

A20M#

FERR#

IGNNE#

INTR/LINT0

NMI/LINT1

INIT#

STPCLK#

SMI#

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

E21

G25

P26

V21

E22

K22

R22

W22

F21

J23

P23

W23

AF22

AF23

AC26

AD26

C6

B6

B2

D1

E5

W5

Y4

B5

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

A20M#

FERR#

IGNNE#

INTR

NMI

C

HD#[0..63] 4

SB_A20M#

SB_IGNNE#

SB_INTR

SB_NMI NMI

DBI0# 4

DBI1# 4

DBI2# 4

DBI3# 4

DSTBN0# 4

DSTBN1# 4

DSTBN2# 4

DSTBN3# 4

DSTBP0# 4

DSTBP1# 4

DSTBP2# 4

DSTBP3# 4

HCLK_CPU 11

HCLK_CPU# 11

FERR# 8

CPUINIT# 8

STPCLK# 8

SMI# 8

2200PF

+5VS

1 2

1 2

1 2

1 2

CPU_VCC

CPU_VCC

12

C104

R67 1K

R95

0

R97

0

R66

0

R65

0

1 2

A20M#

IGNNE#

INTR

R92

@0

1 2

R142 56

1 2

R98 56

12

THERMDA

THERMDC

R93

C71

.1UF

@0

1 8

12

THERMTRIP#

D

1617VCC

U5

1

NC

2

VCC

3

DXP

4

DXN

5

NC

6

ADD1

7

GND

8 9

GND NC

MAX1617/MAX6654

RP7

@8P4R_1K

2 7

3 6

4 5

SB_A20M#8

SB_IGNNE#8

SB_INTR8

SB_NMI8

12

12

12

CPURST#4

R96

R94

@0

+3V

R144

1K

1 2

1

C

2

B

E

3

D

NC

STBY

SMBCLK

NC

SMBDATA

ALERT

ADD0

CPU_VCC

@0

1 2

R145

@0

Q8

2SC2411K

+5VS

12

R38

200

16

15

14

13

12

ATF#

11

10

SB_A20M#

SB_IGNNE#

SB_INTR

SB_NMI

1 2

R497

@1K

Compal Electronics, Inc.

Title

Size Document Number Rev

B

Date: Sheet of

EC_SMC2 21,28

EC_SMD2 21,28

12

R39

1K

+5VS

U7

2

3

5

6

11

10

14

13

1

C604

@0.22UF

1 2

RATIO

15X

16X

17X

18X

19X

20X

21X

22X

23X

24X

THERTRIP# 28

VR_ON 28,38

IOA

IOA

IOB

IOB

I1C

I1C

I1D

I1D

S

16

VCC

4

YA

7

YB

9

YC

12

YD

8

GND

15

E#

@QS3257

A20M#

IGNNE#

INTR

NMI

SW1 RATIO SELECT

NMI A20M# IGNNE# INTR

H

L

L

L

L

L

L

L

H

L

SCHEMATIC, M/B LA-1252

401219

星期三 九月

E

+3VS

A20M#

IGNNE#

INTR

NMI

1 2

R61 @1K

45

36

27

18

RP6

@8P4R_330

L

H

H

H

H

L

L

L

H

L

E

C96

1 2

@.1UF

L

H

H

L

L

H

H

L

H

L

CPU_VCC

L

H

L

H

L

H

L

H

L

L

1A

2 39, 04, 2002

A

C28

150U_D

10

9

8

7

6

10

9

8

7

6

+

VCCA

+

VCCIOPLL

CPU_VCC

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI12

C368

150U_D

VSSA

CPU_VCC

CPU_VCC

12

C365

1UF

AD20

AD22

AE23

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

A5

A4

A8

U23B

VCCA

VSSA

VCCIOPLL

VCCSENSE

VSSSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

CPU_VCC

4 4

3 3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

CPU_VCC

TESTHI8

TESTHI9

TESTHI10

TESTHI11

CPU_VCC

1 2

L6

4.7UH_0805

1 2

L7

4.7UH_0805

RP25

1

2

3

4

5

10P8R-4.7K

RP4

1

2

3

4

5

10P8R-4.7K

CPU_VCC

2 2

R291

49.9_1%

CPU_GTLREF

1 2

12

12

12

R287

100

C388

1UF

C379

220PF

C392

220PF

1 2

CPU_VCC

R62

@49.9_1%

H_GTLREF

1 2

12

12

12

C76

C72

1 1

R60

@100_1%

1 2

@1UF

@220PF

C65

@220PF

CPUVID

CPU_GTLREF

H_GTLREF

R294

51.1_1%

1 2

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

COMP0

COMP1

R59

51.1_1%

1 2

R492

@0

AD24

TESTHI0

AA2

TESTHI1

AC21

TESTHI2

AC20

TESTHI3

AC24

TESTHI4

AC23

TESTHI5

AA20

TESTHI6

AB22

TESTHI7

U6

TESTHI8

W4

TESTHI9

Y3

TESTHI10

A6

TESTHI11

AD25

TESTHI12

AA21

GTLREF

AA6

GTLREF

F20

GTLREF

F6

GTLREF

L24

COMP0

P1

COMP1

A22

RSVD

A7

RSVD

AD2

RSVD

AD3

RSVD

AE21

RSVD

AF3

12

RSVD

AF24

RSVD

AF25

RSVD

mPGA478

A

B

PLL ANALOG VOLTAGE

Northwood

POWER,

GROUND,

RESERVED

SIGNALS

B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D10

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

B4

B8

C11

C13

C15

C17

C19

C2

C22

C25

C5

C7

C9

D12

D14

D16

D18

D20

D21

D24

D3

CPU_VCC

CPU_VCC

CPU_VCC

CPU_VCC

CPU_VCC

CPU_VCC

CPU_VCC

CPU_VCC

12

C70

.1UF

12

C107

1UF

12

C35

10UF_1206

12

C32

10UF_1206

12

C372

10UF_1206

12

C445

10UF_1206

12

C450

10UF_1206

12

C145

10UF_1206

C167

+

470U_E

2.5V

C163

+

470U_E

2.5V

12

C66

.1UF

12

C98

1UF

12

C34

10UF_1206

12

C31

10UF_1206

12

C373

10UF_1206

12

C369

10UF_1206

12

C451

10UF_1206

12

C135

10UF_1206

C168

+

470U_E

2.5V

C166

+

470U_E

2.5V

C

12

C73

.1UF

12

C88

1UF

12

C33

10UF_1206

12

C30

10UF_1206

12

C374

10UF_1206

12

C413

10UF_1206

12

C452

10UF_1206

12

C130

10UF_1206

C

12

C77

.1UF

12

C85

1UF

+

+

12

C84

.1UF

12

C78

1UF

12

C29

10UF_1206

12

C367

10UF_1206

12

C446

10UF_1206

12

C423

10UF_1206

12

C118

10UF_1206

C164

470U_E

2.5V

C160

470U_E

2.5V

PROPRIETARY NOTE

12

12

C87

C97

.1UF

.1UF

CPU_VCC

12

12

C74

C67

1UF

1UF

12

C366

10UF_1206

12

C442

10UF_1206

12

C447

10UF_1206

12

C148

10UF_1206

12

C428

10UF_1206

C19

+

470U_E

2.5V

C18

+

470U_E

2.5V

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

E

CPU_VCC

12

C106

.1UF

12

C370

10UF_1206

12

C443

10UF_1206

12

C448

10UF_1206

12

C147

10UF_1206

12

C418

10UF_1206

12

.1UF

C103

12

C41

.1UF

12

C371

10UF_1206

12

C444

10UF_1206

12

C449

10UF_1206

12

C146

10UF_1206

12

C410

10UF_1206

CPU_VCC

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPUVID38

CPUVID

12

C40

1UF

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

E10

E12

E14

E16

E18

E20

F11

F13

F15

F17

F19

AE5

AE4

AE3

AE2

AE1

AF4

Y25

Y22

W24

W21

V26

V23

U25

U22

VCC

VCC

VCC

VCC

VCC

VCC

B7

VCC

B9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C8

VCC

VCC

VCC

VCC

VCC

VCC

D7

VCC

D9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

E8

VCC

VCC

VCC

VCC

VCC

VCC

F9

VCC

VID0

VID1

VID2

VID3

VID4

Northwood

POWER, GROUND AND NC

VCCVID

Y5

VSS

VSS

VSS

Y2

VSS

W6

VSS

W3

VSS

VSS

VSS

V4

VSS

VSS

VSS

V1

VSS

U5

VSS

VSS

VSS

mPGA478

VID[0..4]38

CPU_VID[0..4]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D6

D8

E1

E11

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3

G6

H1

H23

H26

H4

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

P2

P22

P25

P5

R1

R23

R26

R4

T21

T24

T3

T6

U2

U23C

+3V

RP3

C359

+

330U_E

2.5V

C105

+

330U_E

2.5V

C165

+

470U_E

2.5V

C468

+

330U_E

2.5V

C159

+

470U_E

2.5V

C161

+

470U_E

2.5V

C162

+

470U_E

2.5V

C360

+

330U_E

2.5V

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

1 8

2 7

3 6

4 5

8P4R-1K

R17

1K

12

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1252

Size Document Number Rev

B

401219

星期三 九月

D

Date: Sheet of

3 39, 04, 2002

E

1A

A

B

C

D

E

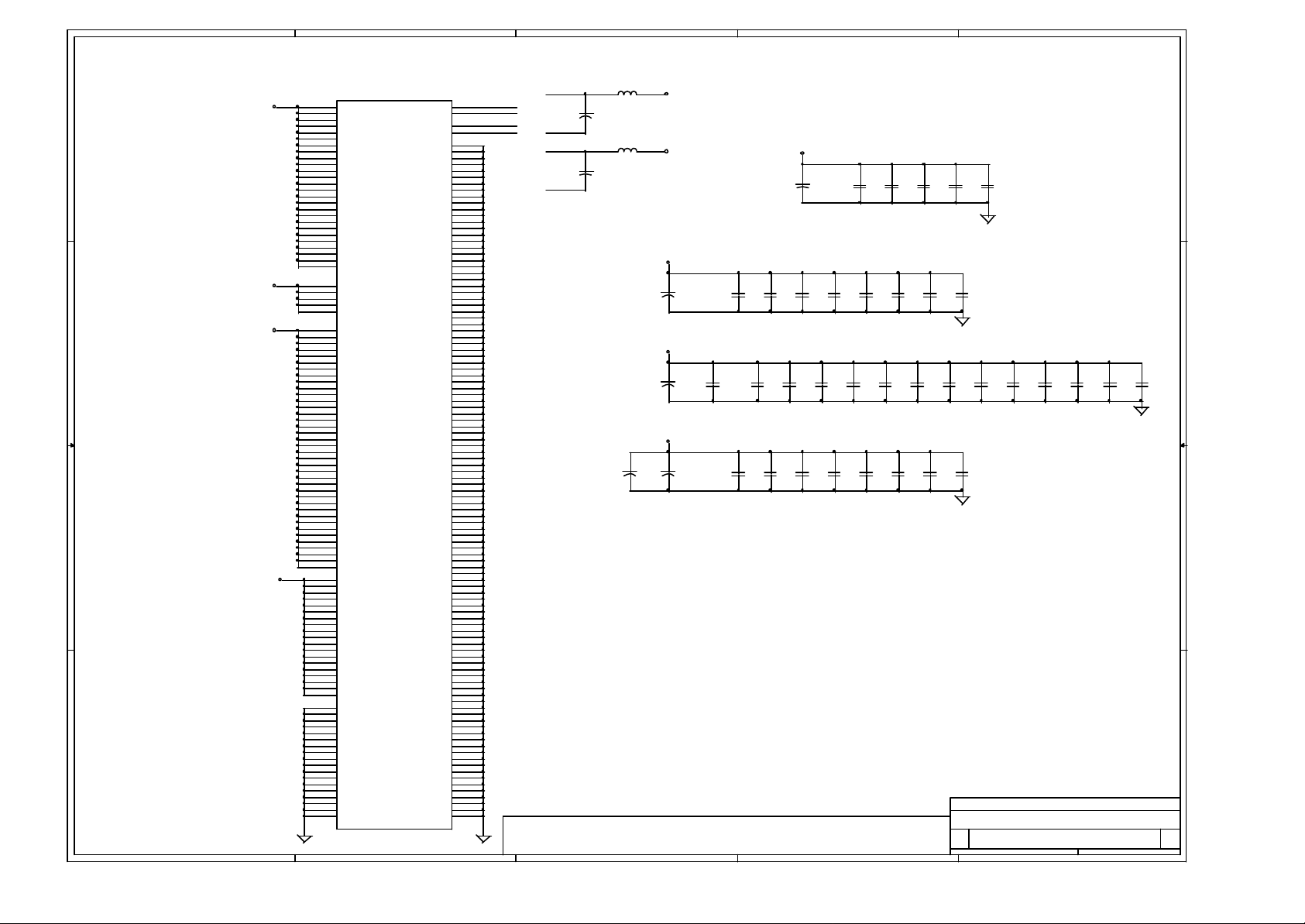

MC-1/3(GTL+,AGP,HUB)

HD#[0..63]2

1 1

2 2

DSTBN0#2

DSTBN1#2

DSTBN2#2

3 3

DSTBN3#2

DSTBP0#2

DSTBP1#2

DSTBP2#2

DSTBP3#2

DBI0#2

DBI1#2

DBI2#2

DBI3#2

CPU_VCC

4 4

HD#[0..63] HA#[3..31]

C81

.1UF

AC5

AD7

AC7

AC6

AC3

AC8

AG5

AG2

AH2

AG3

AH7

AH3

AG8

AG7

AG6

AH5

AC11

AC12

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

AD4

AE11

AC15

AD3

AD11

AC16

AD5

AG4

AH9

AD15

AA2

AB5

AA5

AB3

AB4

AA3

AA6

AE3

AB7

AE2

AE8

AF6

AF3

AE5

AF4

AF8

AE9

AE6

AE7

A

U22A

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

DBI0#

DBI1#

DBI2#

DBI3#

BROOKDALE

MCH_GTLREF

C82

.1UF

HOST

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

ADSTB0#

ADSTB1#

CPURST#

HLOCK#

DEFER#

HTRDY#

RCOMP0

RCOMP1

12

R63

49.9_1%

12

R56

100

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RS#0

RS#1

RS#2

BCLK#

BCLK

ADS#

BNR#

BPRI#

DBSY#

DRDY#

HIT#

HITM#

BR0#

SWNG0

SWNG1

HVREF

HVREF

HVREF

HVREF

HVREF

SWNG

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

U6

T7

R7

U5

U2

W2

W7

W6

R5

N6

K8

J8

AE17

W5

Y4

V3

W3

Y7

V5

V4

Y5

Y3

U7

V7

AC2

AC13

AA7

AD13

M7

R8

Y8

AB11

AB17

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

RCOMP0

RCOMP1

CPU_VCC

HA#[3..31] 2

HREQ#[0..4]

RS#[0..2]

ADSTB0# 2

ADSTB1# 2

CLK_HMCH# 11

CLK_HMCH 11

CPURST# 2

HLOCK# 2

DEFER# 2

ADS# 2

BNR# 2

BPRI# 2

DBSY# 2

DRDY# 2

HIT# 2

HITM# 2

HTRDY# 2

BREQ0# 2

1 2

R270 22

R20 221 2

SWNG

MCH_GTLREF

12

R18

300

12

R19

150

B

C43

0.01UF

HREQ#[0..4] 2

RS#[0..2] 2

PROPRIETARY NOTE

SBSTB12

GPAR12

PIPE#

RBF#12

WBF#

1 2

R273 40.2_1%

C83

0.1UF

GAD[0..31]

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GFRAME#

GDEVSEL#

GIRDY#

GTRDY#

GSTOP#

GPAR

GREQ#

GGNT#

PIPE#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

SBSTB

SBSTB#

RBF#

WBF#

AGPREF

GRCOMP

CLK_66M_MCH

C116

0.1UF

U22C

R27

G_AD0

R28

G_AD1

T25

G_AD2

R25

G_AD3

T26

G_AD4

T27

G_AD5

U27

G_AD6

U28

G_AD7

V26

G_AD8

V27

G_AD9

T23

G_AD10

U23

G_AD11

T24

G_AD12

U24

G_AD13

U25

G_AD14

V24

G_AD15

Y27

G_AD16

Y26

G_AD17

AA28

G_AD18

AB25

G_AD19

AB27

G_AD20

AA27

G_AD21

AB26

G_AD22

Y23

G_AD23

AB23

G_AD24

AA24

G_AD25

AA25

G_AD26

AB24

G_AD27

AC25

G_AD28

AC24

G_AD29

AC22

G_AD30

AD24

G_AD31

V25

G_C/BE#0

V23

G_C/BE#1

Y25

G_C/BE#2

AA23

G_C/BE#3

Y24

G_FRAME#

W28

G_DEVSEL#

W27

G_IRDY#

W24

G_TRDY#

W23

G_STOP#

W25

G_PAR

AG24

G_REQ#

AH25

G_GNT#

AF22

PIPE#

R24

AD_STB0

R23

AD_STB#0

AC27

AD_STB1

AC28

AD_STB#1

AF27

SB_STB

AF26

SB_STB#

AE22

RBF#

AE23

WBF#

AA21

AGPREF

AD25

GRCOMP

AD26

NC

AD27

NC

P22

66IN

BROOKDALE

12

R347

10

12

C473

10PF

HUBREF

C110

C109

0.1UF

0.1UF

1 2

1 2

1 2

+1_8VS

12

12

AGP

HUB

R73

150

1 2

R69

150

D

TESTIN#

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HI10

HIREF

HISTB

HISTB#

HLRCOMP

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

RSTIN#

C117

0.01UF

HIO

HI1

HI2

HI3

HI4

HI5

HI6

HI7

HI8

HI9

ST0

ST1

ST2

H26

B19

C5

C8

C23

C26

D12

F26

H27

K23

K25

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

P25

HL0

HL1

P24

N27

HL2

HL3

P23

M26

HL4

HL5

M25

L28

HL6

HL7

L27

M27

HL8

HL9

N28

M24

HL10

HUBREF

P26

N25

HL_STB

HL_STB#

N24

P27

+GMCH_HLCOMP

AH28

SBA0

SBA1

AH27

AG28

SBA2

SBA3

AG27

AE28

SBA4

SBA5

AE27

AE24

SBA6

SBA7

AE25

ST0

AG25

AF24

ST1

ST2

AG26

J27

1 2

R315

0

ST1CLK_66M_MCH

GPAR

AD_STB0#

AD_STB1#

SBSTB#

GAD[0..31]12

GC/BE#012

GC/BE#112

GC/BE#212

GC/BE#312

GFRAME#12

GDEVSEL#12

GIRDY#12

GTRDY#12

GSTOP#12

GREQ#12

GGNT#12

AD_STB012

AD_STB0#12

AD_STB112

AD_STB1#12

SBSTB#12

AGPREF12

CLK_66M_MCH11

+1_5VS

12

R57

1K

AGPREF

12

R58

1K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

HUBREF 8

HL_STB 8

1 2

R304

40.2_1%

R25 @2K

R285 100K

R299 6.8K

R277 6.8K

R275 6.8K

Title

Size Document Number Rev

B

Date: Sheet of

HL_STB# 8

+1_8VS

SBA[0..7]

HL[0..10]

ST0 12

ST1 12

ST2 12

PCIRST# 8,12,17,18,20,22,23,28,31

GTRDY#

GIRDY#

GDEVSEL#

12

12

12

12

12

GSTOP#

GFRAME#

GREQ#

GGNT#

SBSTB

RBF#

PIPE#

WBF#

AD_STB0

AD_STB1

SBSTB

ST1

Compal Electron ics, Inc.

SCHEMATIC, M/B LA-1252

401219

星期三 九月

E

SBA[0..7] 12

HL[0..10] 8

12

R289 6.8K

12

R281 6.8K

12

R279 6.8K

12

R292 6.8K

12

R278 6.8K

12

R269 6.8K

12

R268 6.8K

12

R272 @6.8K

12

R22 6.8K

12

R21 6.8K

12

R23 6.8K

12

R297 @6.8K

12

R276 @6.8K

12

R271 @6.8K

12

R24 @10K

4 39, 04, 2002

+1_5VS

1A

A

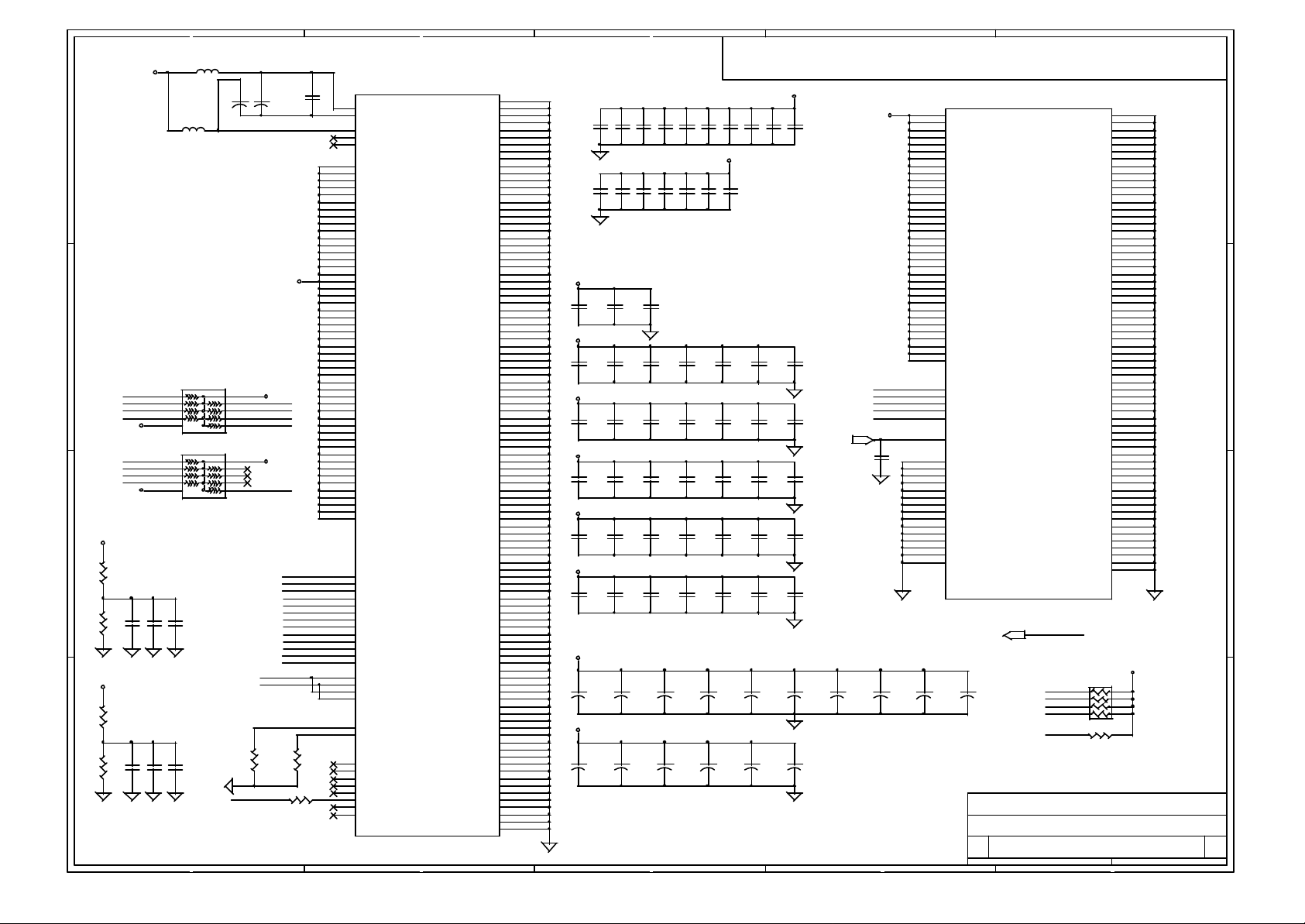

MD32

MD0

MD37

MD33

MD1

MD5

MD39

MD35

MD11

MD45

MD12

MD13

MD14

MD46

MD47

MD15

MD59

MD28

MD61

MD29

MD62

MD30

MD63

MD31

MD20

MD51

MD21

MD54

MD53

MD55

MD23

MD56

MD[0..63]

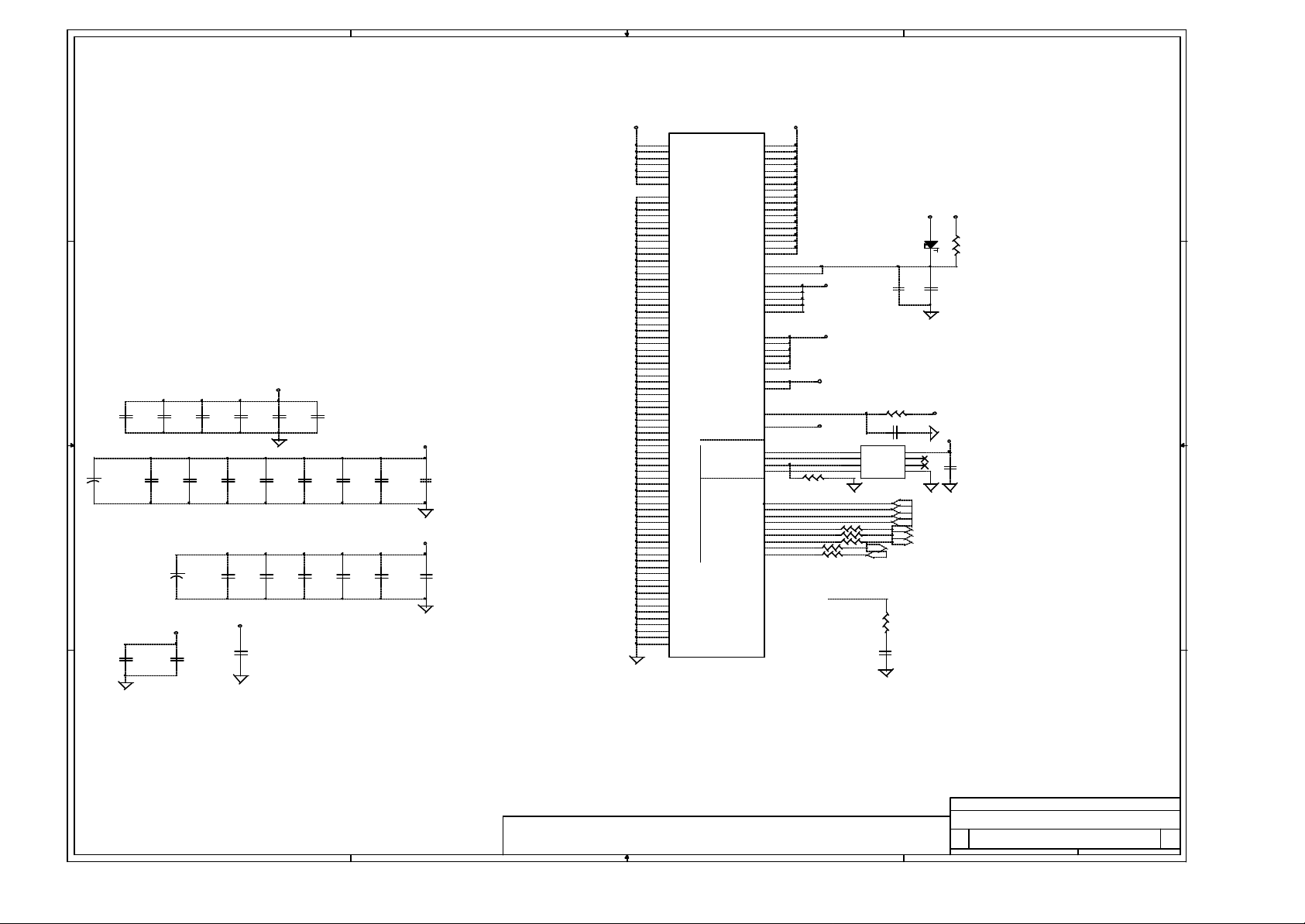

RP26

1

2

3

4

5

6

7

8 9

16P8R-22

RP29

1

2

3

4

5

6

7

8 9

16P8R-22

1

2

3

4

5

6

7

8 9

RP33

1

2

3

4

5

6

7

8 9

16P8R-22

16

15

14

13

12

11

10

16

15

14

13

12

11

10

RP31

16P8R-22

16

15

14

13

12

11

10

MMD32

MMD0

MMD37

MMD33

MMD1

MMD5

MMD39

MMD35

MMD11

MMD45

MMD12

MMD13

MMD14

MMD46

MMD47

MMD15

16

15

14

13

12

11

10

MMD59

MMD28

MMD61

MMD29

MMD62

MMD30

MMD63

MMD31

MMD20

MMD51

MMD21

MMD54

MMD53

MMD55

MMD23

MMD56

MD4

MD34

MD3

MD38

MD2

MD36

MD6

MD[0..63]7

1 1

2 2

3 3

MD40

MD9

MD41

MD8

MD10

MD42

MD43

MD44

MD48

MD16

MD49

MD17

MD18

MD50

MD19

MD52

RP27

1

2

3

4

5

6

7

8 9

16P8R-22

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

MD22

MD57

MD24

MD58

MD26

MD25

MD60

MD27

B

RP28

16P8R-22

RP30

16P8R-22

1

2

3

4

5

6

7

8 9

MMD4

16

15

MMD7MD7

MMD34

14

13

MMD3

MMD38

12

11

MMD2

MMD36

10

MMD6

16

15

14

13

12

11

10

16

15

14

13

12

11

10

RP32

16P8R-22

MMD40

MMD9

MMD41

MMD8

MMD10

MMD42

MMD43

MMD44

MMD48

MMD16

MMD49

MMD17

MMD18

MMD50

MMD19

MMD52

16

15

14

13

12

11

10

MMD22

MMD57

MMD24

MMD58

MMD26

MMD25

MMD60

MMD27

R310 22

R81

49.9_1%

1 2

+3V

R80

49.9_1%

SMVREF

1 2

1 2

C

MMD0

MMD1

MMD2

MMD3

MMD4

MMD5

MMD6

MMD7

MMD8

MMD9

MMD10

MMD11

MMD12

MMD13

MMD14

MMD15

MMD16

MMD17

MMD18

MMD19

MMD20

MMD21

MMD22

MMD23

MMD24

MMD25

MMD26

MMD27

MMD28

MMD29

MMD30

MMD31

MMD32

MMD33

MMD34

MMD35

MMD36

MMD37

MMD38

MMD39

MMD40

MMD41

MMD42

MMD43

MMD44

MMD45

MMD46

MMD47

MMD48

MMD49

MMD50

MMD51

MMD52

MMD53

MMD54

MMD55

MMD56

MMD57

MMD58

MMD59

MMD60

MMD61

MMD62

MMD63

SRCOMP

SMVREF

12

C128

0.1UF

C27

D26

D24

C22

C21

D20

C19

C18

C17

C12

C10

G28

C28

D27

C25

C24

D22

C20

D18

C13

C11

D10

F27

E27

B28

E25

B25

F23

B23

B13

E13

B11

E11

F9

C9

E8

E7

C7

D6

B5

D4

C3

B2

E28

B27

F25

E24

E23

E22

B21

E18

E14

E12

F11

E10

B9

E9

D8

B7

E6

C6

C4

B3

D3

J28

J9

J21

U22B

SMD0

SMD1

SMD2

SMD3

SMD4

SMD5

SMD6

SMD7

SMD8

SMD9

SMD10

SMD11

SMD12

SMD13

SMD14

SMD15

SMD16

SMD17

SMD18

SMD19

SMD20

SMD21

SMD22

SMD23

SMD24

SMD25

SMD26

SMD27

SMD28

SMD29

SMD30

SMD31

SMD32

SMD33

SMD34

SMD35

SMD36

SMD37

SMD38

SMD39

SMD40

SMD41

SMD42

SMD43

SMD44

SMD45

SMD46

SMD47

SMD48

SMD49

SMD50

SMD51

SMD52

SMD53

SMD54

SMD55

SMD56

SMD57

SMD58

SMD59

SMD60

SMD61

SMD62

SMD63

SRCOMP

SDREF

SDREF

BROOKDALE

D

E

MCH-2/3(SDRAM)

MAA0

G22

SMAA0

E21

MAA1

SMAA1

MAA2

F21

SMAA2

G21

MAA3

SMAA3

MAA4

E20

SMAA4

G20

MAA5

SMAA5

MAA6

E19

SMAA6

F19

MAA7

SMAA7

MAA8

G19

SMAA8

G18

MAA9

SMAA9

MAA10

E17

SMAA10

E15

SBS0

SBS1

SCK0

SCK1

SCK2

SCK3

SCK4

SCK5

SCK6

SCK7

SCK8

SCK9

SCK10

SCK11

SRAS#

SCAS#

SWE#

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SCS#0

SCS#1

SCS#2

SCS#3

SCS#4

SCS#5

SCS#6

SCS#7

SCS#8

SCS#9

SCB0

SCB1

SCB2

SCB3

SCB4

SCB5

SCB6

SCB7

G12

F17

G17

F13

G13

E2

C2

G15

G14

F3

E3

G16

F15

H5

G5

G23

J25

G27

G9

F4

G10

F5

G11

E5

H23

J23

G7

G8

J24

G24

H7

F7

G25

H25

G6

H6

C16

E16

C15

D14

B17

D16

B15

C14

G3

H3

MAA11

MAA12

SBS0

SBS1

SRASA#

SCASA#

RMWEA#

CKE2

CKE3

CKE4

CKE5

RRAS#2

RRAS#3

RRAS#4

RRAS#5

RDCLK

1 2

R335 10

1 2

R337 10

1 2

R334 10

1 2

R336 10

SMAA11

SMAA12

MEMORY

SCS#10

SCS#11

RDCLKIN

RDCLKO

12

C400

@10PF_0402

MAA0 7

MAA1 7

MAA2 7

MAA3 7

MAA4 7

MAA5 7

MAA6 7

MAA7 7

MAA8 7

MAA9 7

MAA10 7

MAA11 7

MAA12 7

SBS0 7

SBS1 7

CLK_SDRAM2 7

CLK_SDRAM3 7

CLK_SDRAM4 7

CLK_SDRAM5 7

SRASA# 7

SCASA# 7

RMWEA# 7

CKE2 7

CKE3 7

CKE4 7

CKE5 7

RRAS#[2..5]7

RRAS#[2..5]

4 4

Compal Electron ics, Inc.

Title

PROPRIETARY NOTE

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCHEMATIC, M/B LA-1252

Size Document Number Rev

B

401219

星期三 九月

Date: Sheet of

5 39, 04, 2002

E

1A

A

B

C

D

E

MCH-3/3(Power)

U22D

+1_5VS

1 1

+1_8VS

+3V

2 2

3 3

CPU_VCC

4 4

A

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

R14

R16

U14

U16

M22

N23

N26

C29

D11

D15

D19

D23

D25

G29

H10

H12

H14

H16

H18

H20

H22

H24

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

AB19

AB22

AC1

AC4

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ27

P13

P15

P17

T15

L25

L29

A5

A9

A13

A17

A21

A25

C1

D7

F6

F10

F14

F18

F22

G1

G4

H8

J5

J7

K6

K22

K24

K26

L23

M8

U8

AA9

AB8

AJ3

AJ5

AJ7

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

BROOKDALE

POWER/GND

B

VCCA0

VCCA1

VSSA0

VSSA1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDGND

T13

T17

U13

U17

A3

A7

A11

A15

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J26

J29

K5

K7

K27

L1

L4

L6

L8

L22

L24

L26

M23

N1

N4

N8

N13

N15

N17

N22

N29

P6

P8

P14

P16

R1

R4

R13

R15

R17

R26

T6

T8

T14

T16

T22

U1

U4

U15

U29

V6

V8

V22

W1

W4

W8

W26

Y6

Y22

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AJ9

AJ11

AJ13

AJ15AJ17

VCCA0

VCCA1

VSSA0

VSSA1

VCCA0

VSSA0

VCCA1

VSSA1

PROPRIETARY NOTE

1 2

L31 4.7UH_0805

+

C391

33U_D

1 2

L26 4.7UH_0805

+

C378

33U_D

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

12

+

C

C86

150UF_E

6.3V

+1_5VS

+1_5VS

CPU_VCC

C42

+

22UF_10V_1206

+3V

12

+

+1_5VS

C92

+

22UF_10V_1206

C425

150UF_E

6.3V

.1UF_0402

C123

4.7UF_0805

.1UF_0402

C47

C101

C46

.1UF_0402

C153

.1UF_0402

C95

.1UF_0402

+1_8VS

+

C94

22UF_10V_1206

C48

.1UF_0402

C152

.1UF_0402

C108

.1UF_0402

C68

.1UF_0402

C126

.1UF_0402

C91

.1UF_0402

C120

.1UF_0402

C149

.1UF_0402

D

C57

.1UF_0402

.1UF_0402

C112

.1UF_0402

C114

.1UF_0402

C56

.1UF_0402

C125

C111

.1UF_0402

C113

.1UF_0402

.1UF_0402

C151

.1UF_0402

.1UF_0402

C115

C121

.1UF_0402

.1UF_0402

C59

C69

.1UF_0402

C154

C122

.1UF_0402

C100

C90

.1UF_0402

Title

Size Document Number Rev

B

Date: Sheet of

C124

.1UF_0402

.1UF_0402

Compal Electron ics, Inc.

SCHEMATIC, M/B LA-1252

401219

星期三 九月

C127

.1UF_0402

.1UF_0402

E

C150

C134

.1UF_0402

6 39, 04, 2002

C144

.1UF_0402

1A

A

B

C

+3V

D

E

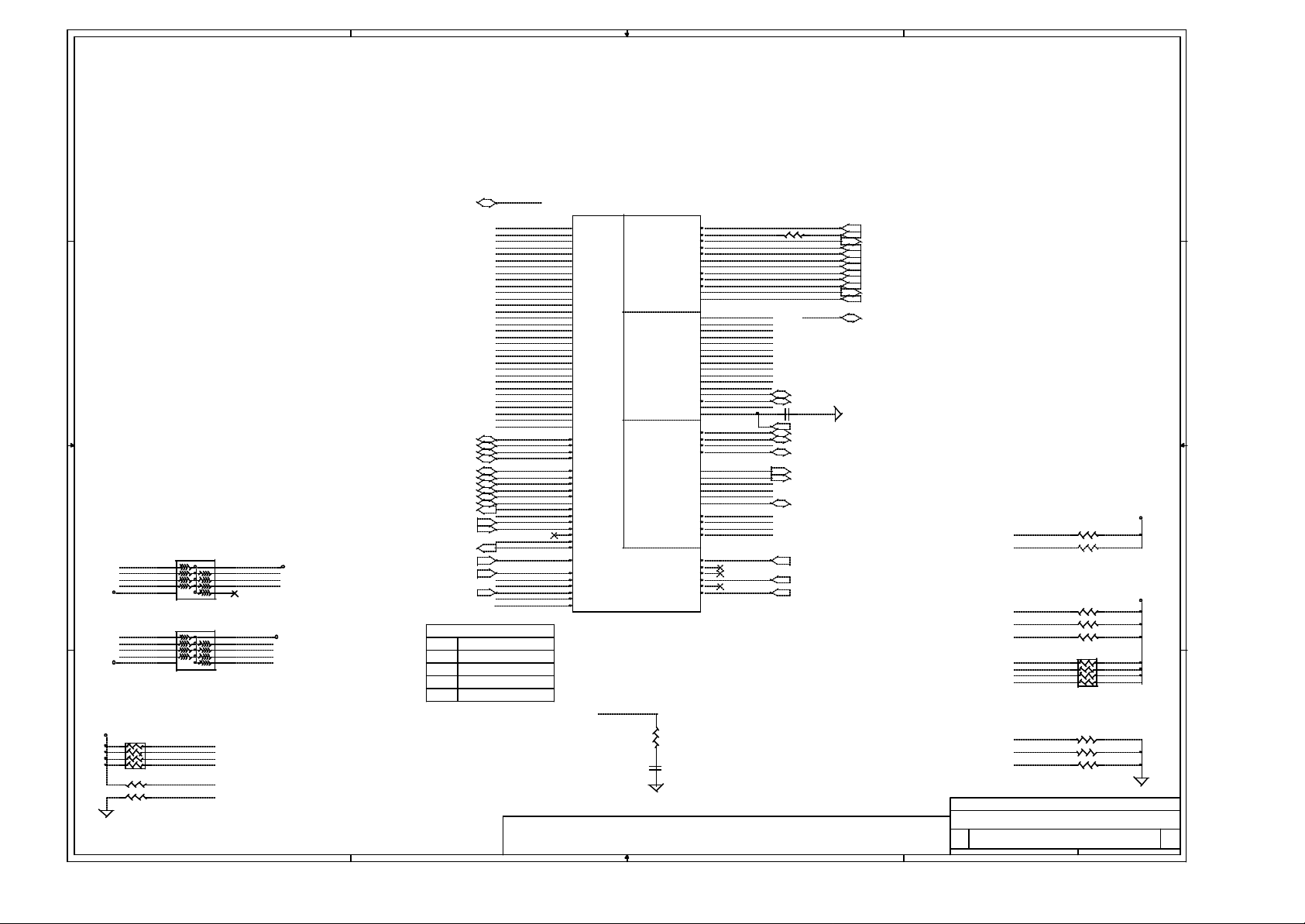

SO-DIM 144 PINS

BANK4/5

+

RAM MODULE CONN.

MAA[0..12]5

MD[0..63]5

1 1

RRAS#[2..5]5

2 2

3 3

4 4

MAA[0..12]

MD[0..63]

RRAS#[2..5]

CLK_SDRAM25

SRASA#5

RMWEA#5

+3V

+

+3V

C495

C192

.1UF

10UF_1206

6.3V

RP39

SCKDIMM1

1 8

SCKDIMM0

2 7

SDADIMM1

3 6

SDADIMM0

4 5 R361 1K

8P4R-10K

A

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

RCAS#2

MAA0

MAA1

MAA2

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

R360

C494

51_1%

270PF

SRASA# SCASA#

RMWEA# CKE3

RRAS#2 MAA12

RRAS#3

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MAA6

MAA8

MAA9

MAA10

RCAS#1

RCAS#0

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

SDADIMM0 SCKDIMM0

C499

.1UF

BANK2/3

+3V +3V

C497

.1UF

JP5

1

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15

DQ5

17

DQ6

19

DQ7

21

VSS

23

CE0#

25

CE1#

27

VCC

29

A0

31

A1

33

A2

35

VSS

37

DQ8

39

DQ9

41

DQ10

43

DQ11

45

VCC

47

DQ12

49

DQ13

51

DQ14

53

DQ15

55

VSS

57

RESVD/DQ64

59

RESVD/DQ65

61

RFU/CLK0

63

VCC

65

RFU

67

WE#

69

RE0#

71

RE1#

73

OE#/RESVD

75

VSS

77

RESVD/DQ66

79

RESVD/DQ67

81

VCC

83

DQ16

85

DQ17

87

DQ18

89

DQ19

91

VSS

93

DQ20

95

DQ21

97

DQ22

99

DQ23

101

VCC

103

A6

105

A8

107

VSS

109

A9

111

A10

113

VCC

115

CE2#/RESVD

117

CE3#/RESVD

119

VSS

121

DQ24

123

DQ25

125

DQ26

127

DQ27

129

VCC

131

DQ28

133

DQ29

135

DQ30

137

DQ31

139

VSS

141

SDA

143

VCC

S O-DIMM144 REVERSE

C491

C490

.1UF

.01UF

R358 1K

R373 1K

R375 1K

R376 1K

R371 1K

R372 1K

R374 1K

DIMM0

C488

.01UF

RCAS#0

RCAS#1

RCAS#2

RCAS#3

RCAS#4

RCAS#5

RCAS#6

RCAS#7

VSS

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

VSS

CE4#

CE5#

VCC

A3

A4

A5

VSS

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

VSS

RESVD/DQ68

RESVD/DQ69

RFU/CKE0

VCC

RFU

RFU/CKE1

RFU

RFU

RFU/CLK1

VSS

RESVD/DQ70

RESVD/DQ71

VCC

DQ48

DQ49

DQ50

DQ51

VSS

DQ52

DQ53

DQ54

DQ55

VCC

A7

A11/BA0

VSS

A12/BA1

A13/A11

VCC

CE6#/RESVD

CE7#/RESVD

VSS

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VSS

SCL

VCC

C486

.01UF

B

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

PROPRIETARY NOTE

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

RCAS#7RCAS#3

RCAS#6

MAA3

MAA4

MAA5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

CKE2

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MAA7

SBS0

SBS1

MAA11

RCAS#5

RCAS#4

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

C479

10UF_1206

6.3V

CKE2 5

SCASA# 5

CKE3 5

SBS0 5

SBS1 5

SM_SEL9

SCKP49,11

SDAP49,11

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

R138

51_1%

C190

270PF

C496

C500

1000PF

.01UF

CLK_SDRAM3 5

+3V

C510

.1UF

6

INH

10

A

9

B

3

X

13

Y

7

C

16

GND

8

VCC

GND

1000PF

X0

X1

X2

X3

Y0

Y1

Y2

Y3

C492

CLK_SDRAM45

U35

1

5

2

4

12

14

15

11

74HC4052

1000PF

SCKDIMM0

SCKDIMM1

SDADIMM0

SDADIMM1

C487

C489

1000PF

+3V +3V

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

RCAS#3

RCAS#2

MAA0

MAA1

MAA2

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

C477

R352

270PF

51_1%

SRASA# SCASA#

RMWEA# CKE5

RRAS#4 MAA12

RRAS#5

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MAA6 MAA7

MAA8

MAA9

MAA10 MAA11

RCAS#1

RCAS#0

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

SDADIMM1

JP23

1

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15

DQ5

17

DQ6

19

DQ7

21

VSS

23

CE0#

25

CE1#

27

VCC

29

A0

31

A1

33

A2

35

VSS

37

DQ8

39

DQ9

41

DQ10

43

DQ11

45

VCC

47

DQ12

49

DQ13

51

DQ14

53

DQ15

55

VSS

57

RESVD/DQ64

59

RESVD/DQ65

61

RFU/CLK0

63

VCC

65

RFU

67

WE#

69

RE0#

71

RE1#

73

OE#/RESVD

75

VSS

77

RESVD/DQ66

79

RESVD/DQ67

81

VCC

83

DQ16

85

DQ17

87

DQ18

89

DQ19

91

VSS

93

DQ20

95

DQ21

97

DQ22

99

DQ23

101

VCC

103

A6

105

A8

107

VSS

109

A9

111

A10

113

VCC

115

CE2#/RESVD

117

CE3#/RESVD

119

VSS

121

DQ24

123

DQ25

125

DQ26

127

DQ27

129

VCC

131

DQ28

133

DQ29

135

DQ30

137

DQ31

139

VSS

141

SDA

143

VCC

SO-DIMM144-STANDARD

+3V

+

C485

10UF_1206

6.3V

D

DIMM1

C478

.1UF

VSS

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

VSS

CE4#

CE5#

VCC

A3

A4

A5

VSS

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

VSS

RESVD/DQ68

RESVD/DQ69

RFU/CKE0

VCC

RFU

RFU/CKE1

RFU

RFU

RFU/CLK1

VSS

RESVD/DQ70

RESVD/DQ71

VCC

DQ48

DQ49

DQ50

DQ51

VSS

DQ52

DQ53

DQ54

DQ55

VCC

A7

A11/BA0

VSS

A12/BA1

A13/A11

VCC

CE6#/RESVD

CE7#/RESVD

VSS

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VSS

SCL

VCC

Title

Size Document Number Rev

B

Date: Sheet of

2

MD56

4

MD57

6

MD58

8

MD59

10

12

MD60

14

MD61

16

MD62

18

MD63

20

22

RCAS#7

24

RCAS#6

26

28

MAA3

30

MAA4

32

MAA5

34

36

MD48

38

MD49

40

MD50

42

MD51

44

46

MD52

48

MD53

50

MD54

52

MD55

54

56

58

60

CKE4

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

C498

.1UF

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

SBS0

SBS1

RCAS#5

RCAS#4

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

SCKDIMM1

C193

.1UF

CKE4 5

CKE5 5

C189

.1UF

R359

51_1%

C493

270PF

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1252

401219

星期三 九月

E

CLK_SDRAM5 5

C191

.01UF

7 39, 04, 2002

1A

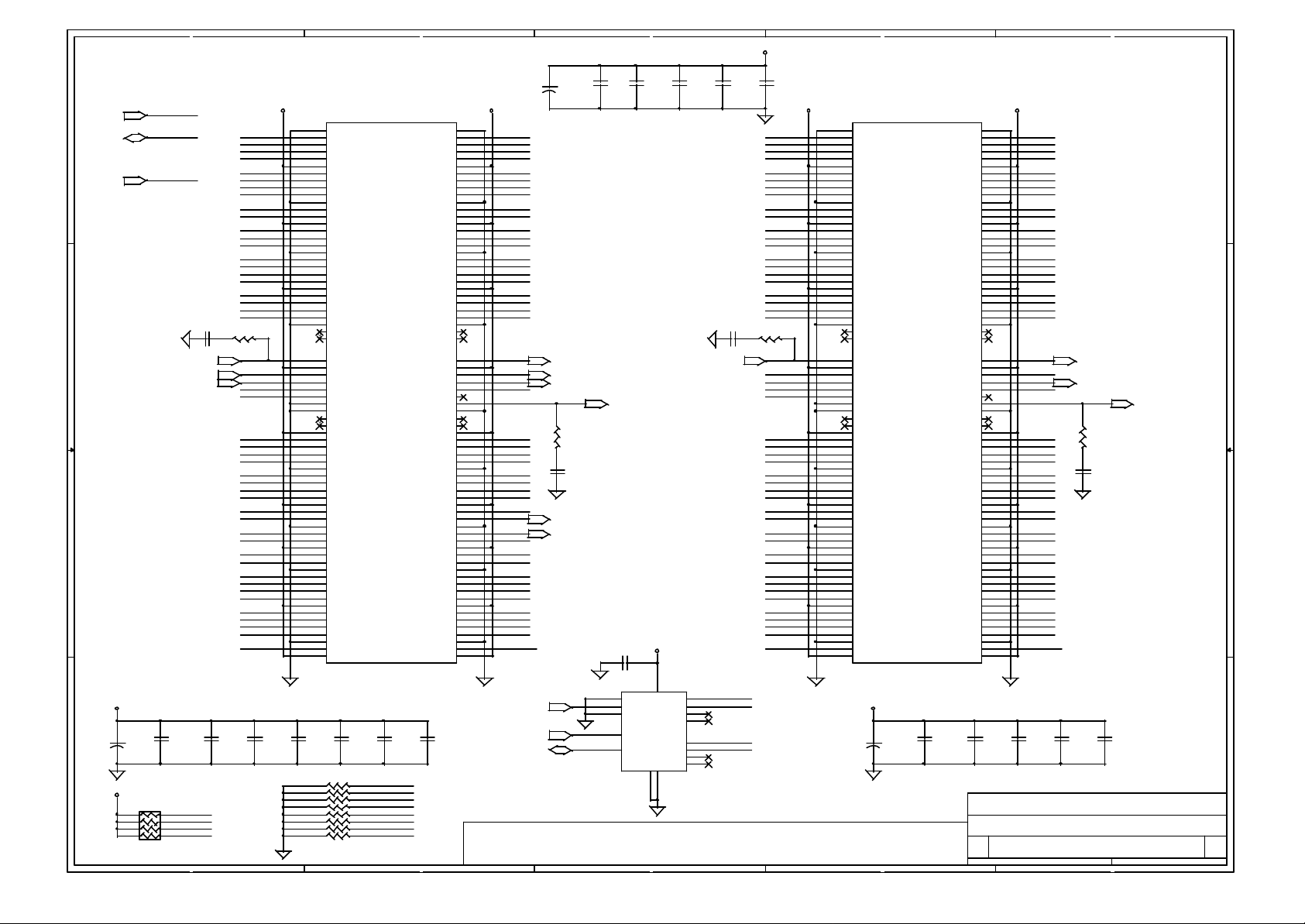

A

1 1

B

C

D

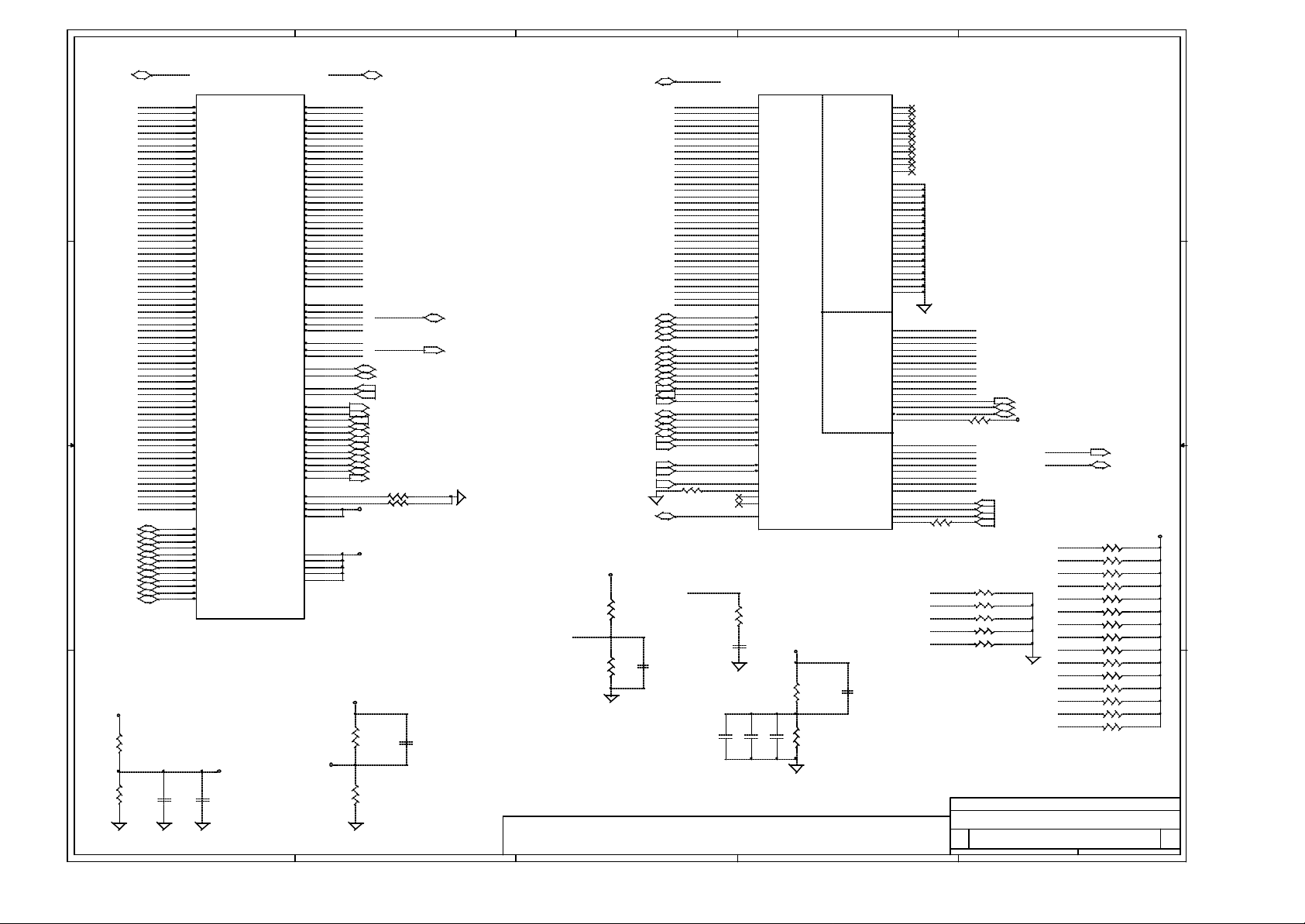

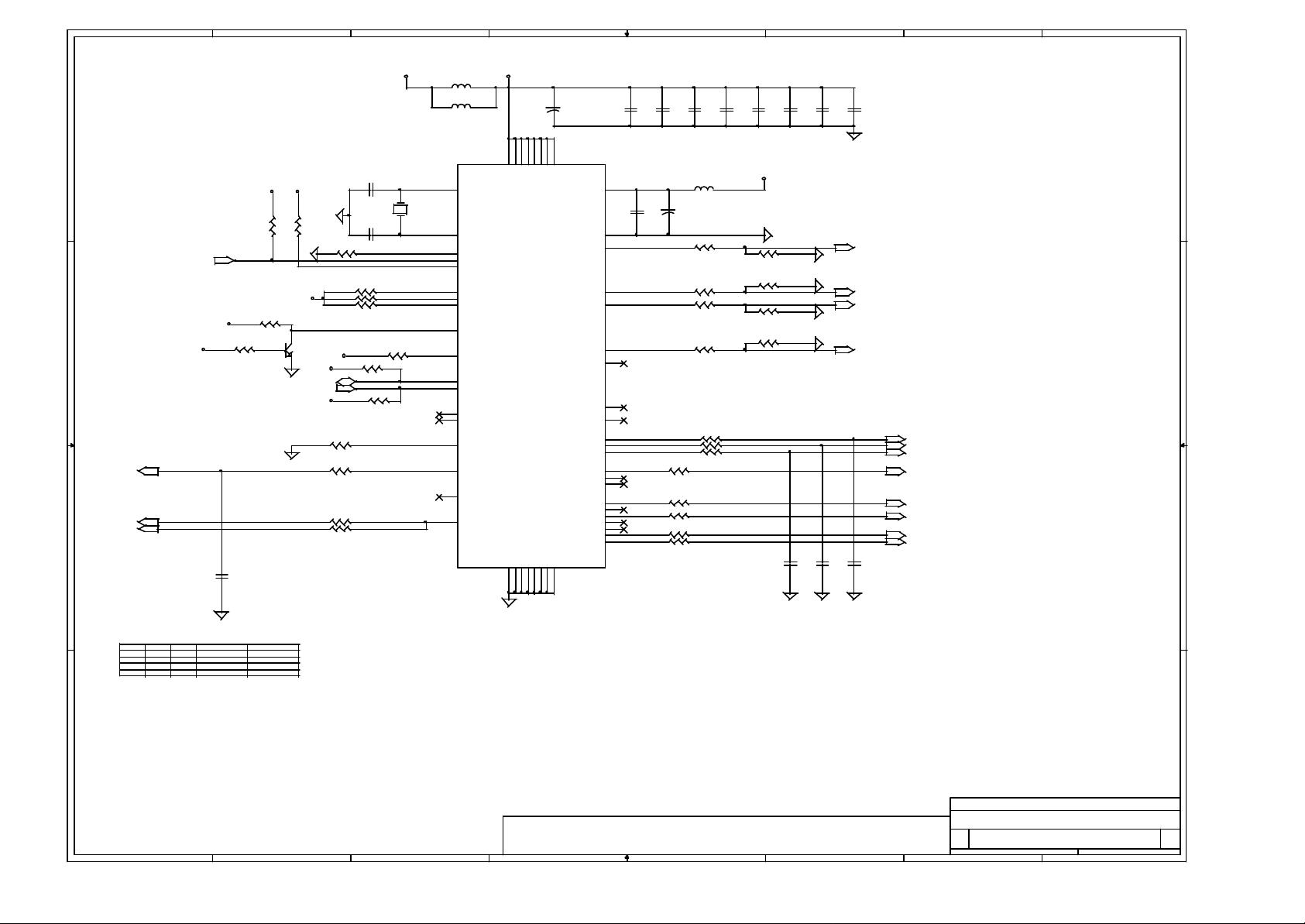

AD[0..31]17,20

2 2

C/BE#017,20

C/BE#117,20

C/BE#217,20

C/BE#317,20

DEVSEL#17,20

FRAME#17,20

TRDY#17,20

PCIRST#4,12,17,18,20,22,23,28,31

SERR#17,20

PCI Pullups

3 3

+3VS

+3VS

PERR#

REQA#

STOP#

SERR#

IRDY#

TRDY#

FRAME#

RP35

1

2

3

4

5

10P8R-8.2K

RP34

1

2

3

4

5

10P8R-8.2K

10

9

8

7

6

10

9

8

7

6

PIRQA#

PIRQB#

REQ#4

PIRQC#

PIRQD#DEVSEL#

SIRQ

PLOCK#

+3VS

+3VS

PERR#17,20

PME# has internal PU

PIDERST#22

PCLK_ICH11

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

+3VS

RP37

1 8

4 4

2 7

3 6

4 5

8P4R-8.2K

1 2

R350 8.2K

1 2

R349 @1K

REQ#0

REQ#1

REQ#2

REQ#3

GPI1

GNTA#

GNTA# Strapping for "A16 swap override" : "0" -> Enable

A

AD[0..31]

DEVSEL#

FRAME#

IRDY#17,20

STOP#17,20

REQ#020

REQ#317

IRDY#

TRDY#

STOP#

PAR17,20

PCIRST#

PLOCK#

SERR#

PERR#

REQA#

GNTA#

PCLK_ICH

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

GPI1

PCI REQ ASSIGMENT

WLAN

NC

NC

PCMCIA CONTROLLER

NC

B

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PROPRIETARY NOTE

ICH-2

(FW82801BA)

U33A

AA4

AD0

AB4

AD1

Y4

AD2

W5

AD3

W4

AD4

Y5

AD5

AB3

AD6

AA5

AD7

AB5

AD8

Y3

AD9

W6

AD10

W3

AD11

Y6

AD12

Y2

AD13

AA6

AD14

Y1

AD15

V2

AD16

AA8

AD17

V1

AD18

AB8

AD19

U4

AD20

W9

AD21

U3

AD22

Y9

AD23

U2

AD24

AB9

AD25

U1

AD26

W10

AD27

T4

AD28

Y10

AD29

T3

AD30

AA10

AD31

AA3

C/BE0#

AB6

C/BE1#

Y8

C/BE2#

AA9

C/BE3#

AB7

DEVSEL#

V3

FRAME#

W8

IRDY#

V4

TRDY#

W1

STOP#

W2

PAR

AA15

PCIRST#

AA7

PLOCK#

W7

SERR#

Y7

PERR#

Y15

PME#

M3

GPI0/REQA#

L2

GPO16/GNTA#

W11

PCICLK

R2

REQ0#

R3

REQ1#

T1

REQ2#

AB10

REQ3#

P4

REQ4#

L3

GPI1/REQB#/REQ5#

ICH-2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PCI

PCLK_ICH

CPU

HUB

IRQ

GPO17/GNTB#/GNT5#

12

12

A20M#

CPUSLP#

FERR#

IGNNE#

INIT#

INTR

NMI

SMI#

STPCLK#

RCIN#

A20GATE

CPUPWRGD

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HL11

HL_STB

HL_STB#

HLCOMP

HUBREF

PIRQA#

PIRQB#

PIRQC#

PIRQD#

IRQ14

IRQ15

APICCLK

APICD0

APICD1

SERIRQ

GPI2/PIRQE#

GPI3/PIRQF#

GPI4/PIRQG#

GPI5/PIRQH#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

R154

@33

C222

@22PF

D11

A12

R22

FERR#

A11

C12

CPUINIT#

C11

B11

SMI#

B12

C10

STPCLK#

RC#

B13

C13

GATEA20

CPU_PWRGD

A13

A4

HL0

HL1

B5

A5

HL2

HL3

B6

B7

HL4

HL5

A8

B8

HL6

HL7

A9

C8

HL8

HL9

C6

C7

HL10

HL11

C5

A6

HL_STB

HL_STB#

A7

A3

+ICH_HLCOMP

HUBREF

B4

P1

PIRQA#

PIRQB#

P2

P3

PIRQC#

PIRQD#

N4

F21

IRQ14

IRQ15

C16

N20

CLK_APIC_ICH

PICD0

P22

N19

PICD1

SIRQ

N21

GPI2

N3

N2

GPI3

GPI4

N1

M4

GPI5

PIN N3, M4 can not use GPIO.

M2

GNT#0

M1

R4

GNT#3

T2

R1

SIDERST#

L4

1 2

R383 0

C484 .1UF

C

HL_STB 4

HL_STB# 4

12

HUBREF 4

PIRQA# 12,17,20

PIRQB# 17

PIRQD# 20

IRQ14 22

IRQ15 21

SIRQ 17,23,28

GNT#0 20

GNT#3 17

SIDERST# 22

HL[0..10]

SB_A20M# 2

CPUSLP# 2

FERR# 2

SB_IGNNE# 2

CPUINIT# 2

SB_INTR 2

SB_NMI 2

SMI# 2

STPCLK# 2

RC# 28

GATEA20 28

CPU_PWRGD 2

HL[0..10] 4

+1_8VS

D

1 2

R357 @10K

1 2

R354 40.2_1%

1 2

R351 @8.2K

1 2

R410 10K

1 2

R390 10K

RP36

1 8

2 7

3 6

4 5

8P4R-100K

12

R414 10K

12

R409 10K

1 2

R415 0

8 39, 04, 2002

+3VS

HL11

+ICH_HLCOMP

SIDERST#

IRQ14

IRQ15

GPI4

GPI3

GPI2

GPI5

PICD0

PICD1

CLK_APIC_ICH

Compal Electron ics, Inc.

Title

SCHEMATIC, M/B LA-1252

Size Document Number Rev

B

401219

星期三 九月

Date: Sheet of

1A

A

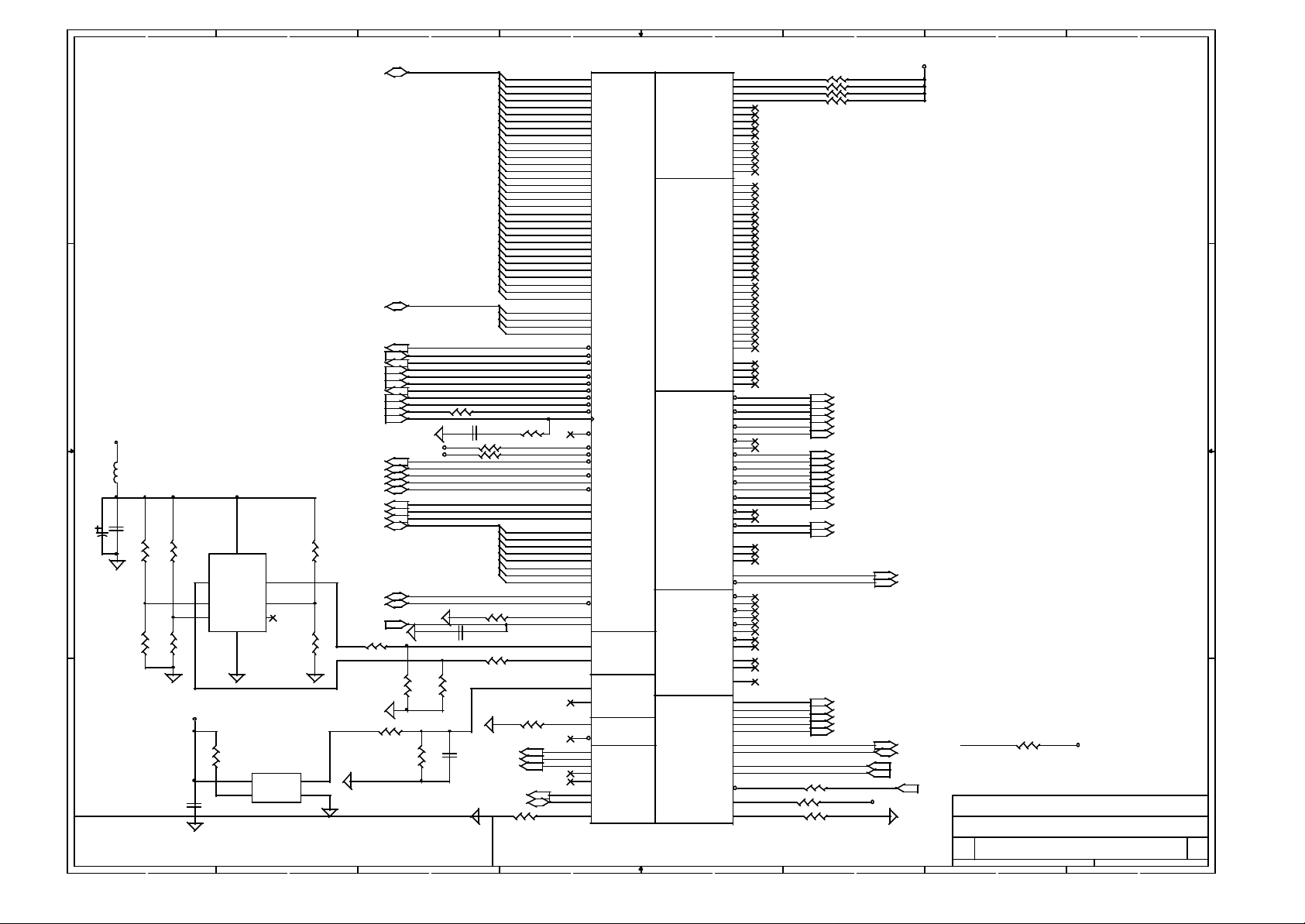

1 2

+3V

R403 10K

21

LLBATT#28

D38 RB751V

1 2

+3V

ON/OFF28,31

+3V

ACIN28,31,33,34,36

+3V

ECSMI#28

+3V

ECSCI#28

+3V

+RTCVCC

1 2

INTRUDER#

SMLINK0

SMLINK1

OVCUR#2

VGATE

CLKRUN#

LDRQ#1

DSCACHE#

ICH_AC_SDOUT

RSMRST#

IAC_BITCLK

IAC_SDATAI

IAC_SDATAI1

SPKR

R380 10K

D34 RB751V

D22 RB751V

D21 @RB751V

1 2

R388 10K

D36 RB751V

1 2

R370 10K

D33 RB751V

1 2

R362 10K

1 2

R384 10K

D35 RB751V

R190

1 2

15K

1UF_25V_0805

R191

1K

EC_LID_OUT#28

PBTN_OUT#28

1 1

EC_RIOUT#28

2 2

+RTCVCC

3 3

1 2

R183 10K

+3V

1 2

R175 10K

1 2

R184 10K

1 2

R178 10K

+3VS

1 2

R386 100K

1 2

R436 10K

1 2

R356 @10K

12

R355 10K

1 2

R179 @10K

AC_SDOUT Strapping: "1" -> Safe Mode Boot

4 4

R168 100K

R169 10K

R404 10K

R405 10K

R407 1K

12

12

12

12

12

SPKR Strapping: "0" -> No Reboot

A

BATTLOW#

21

LID#

PBTN#

21

21

21

ICH_ACIN

21

EXT_SMI#

21

SCI#

21

ICH_RI#

12

C303

1 2

+R_VBAIS

C282

.047UF

12

R479

22M

1 2

CLKRUN# 17,20,23,28

R392

1 2

1K

R181

1 2

10M

R480

2.4M

C538

12PF

J1

JOPEN

1 2

R406 10M

32.768KHZ

12

IAC_BITCLK

USBP2USBP2+

USBP0USBP0+

CP5

8P4C-22PF

1 8

2 7

3 6

12

X3

12

C539

12PF

1 2

R158 @10K

12

R170

@33

C543

@33PF

RP41

1 8

2 7

3 6

4 5

8P4R-15

4 5

B

USB2_DUSB2_D+

USB0_D- 25

12

AA13

D14

W16

AB18

R20

W21

AA17

R21

W15

AA18

C14

AA16

AB16

AB17

U19

U22

R19

W22

N22

AA11

W14

AB15

AB14

AA14

W12

AB13

AB12

W13

AB11

AA12

W17

AB19

AA19

W18

AB20

AA20

W19

W20

Y11

A15

V21

Y17

T19

V20

T20

T21

T22

V22

P19

P21

Y22

Y14

L1

Y12

Y13

Y18

Y19

Y20

Y21

1 2

R408 22

1 2

R180 22

USB0_D+ 25

U33B

THRM#

GPO19

SLP_S3#

SLP_S5#

PWROK

PWRBTN#

RI#

RSMRST#

GPIO25

SUSCLK

GPI6

GPO18

GPO20

GPIO24

SUSSTAT#

INTRUDER#

SMBDATA

SMBCLK

SMBALERT#/GPI11

SMLINK0

SMLINK1

RTCRST#

VBIAS

RTCX1

RTCX2

AC_RST#

AC_SYNC

AC_BIT_CLK

AC_SDOUT

AC_SDIN0

AC_SDIN1

SPKR

GPI8

GPI7

GPI12

GPI13

GPO21

GPIO27

GPIO28

LAD0/FWH0

LAD1/FWH1

LAD2/FWH2

LAD3/FWH3

LDRQ0#

LDRQ1#

LFRAME#/FWH4

FSO

USBP0+

USBP0USBP1+

USBP1USBP2+

USBP2USBP3+

ICH-2

USBP3OC0#

OC1#

OC2#

OC3#

SYSTEM

AC97

GPIO

LPC

USB

ICH_AC_SYNC

ICH_AC_SDOUT

182736

45

RP40

8P4R-15K

ATF_INT#28

SLP_S3#28

SLP_S5#28

SYS_PWROK32

RSMRST#10,32

FLASH#29

RTCCLK17,18

SUS_STAT#12,23,31

SDAP47,11

SCKP47,11

IAC_RST#24,26 PDD[0..15] 22

IAC_BITCLK24,26

IAC_SDATAI26

IAC_SDATAI124

SPKR27

SM_SEL7

USB_EN#25

LAD023,28

LAD123,28

LAD223,28

LAD323,28

LDRQ#028

LDRQ#123

LFRAME#23,28

OVCUR#025

OVCUR#125

OVCUR#325

IAC_SYNC24,26

IAC_SDATAO24,26

PROPRIETARY NOTE

B

ATF_INT#

SLP_S3#

SLP_S5#

SYS_PWROK

PBTN#

ICH_RI#

RSMRST#

BATTLOW#

INTRUDER#

SDAP4

SCKP4

ICH_ACIN

SMLINK0

SMLINK1

+RTCRST#

+VBIAS

RTCX1

RTCX2

ICH_AC_SYNC

IAC_BITCLK

ICH_AC_SDOUT

IAC_SDATAI

IAC_SDATAI1

SPKR

EXT_SMI#

DSCACHE#

SCI#

LID#

LAD0

LAD1

LAD2

LAD3

LDRQ#0

LDRQ#1

LFRAME#

USBP0+

USBP0USBP1+

USBP1USBP2+

USBP2USBP3+

USBP3-

OVCUR#2

OVCUR#3

12

C544

C293

22PF

22PF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

USBP3USBP3+

USBP1USBP1+

CP6

8P4C-22PF

TP0

GPO22

GPO23

VGATE/VRMPWRGD

CLK48

CLK14

CLK66

PDA0

PDA1

PDA2

PDCS1#

PDCS3#

PDREQ

PDDACK#

PDIOR#

PDIOW#

PIORDY

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

IDE

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDA0

SDA1

SDA2

SDCS1#

SDCS3#

SDDREQ

SDDACK#

SDIOR#

SDIOW#

SIORDY

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

C

U20

B14

A14

B15

P20

M19

D4

F20

F19

E22

E21

E19

G22

F22

G19

G21

G20

H19

H22

J19

J22

K21

L20

M21

M22

L22

L21

K22

K20

J21

J20

H21

H20

A16

D16

B16

C15

D15

B18

B17

D17

C17

A17

D18

B19

D19

A20

C20

C21

D22

E20

D21

C22

D20

B20

C19

A19

C18

A18

1 8

2 7

RP44

1 8

2 7

3 6

4 5

8P4R-15

RP43

8P4R-15K

3 6

4 5

R400 1K

1 2

VGATE

1 2D32 RB751V

R478 @0

CLK_USB_ICH

CLK_14M_ICH

CLK_HUB_ICH

PDA0

PDA1

PDA2

PDCS1#

PDCS3#

PDDREQ

PDDACK#

PDIOR#

PDIOW#

PDIORDY

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8