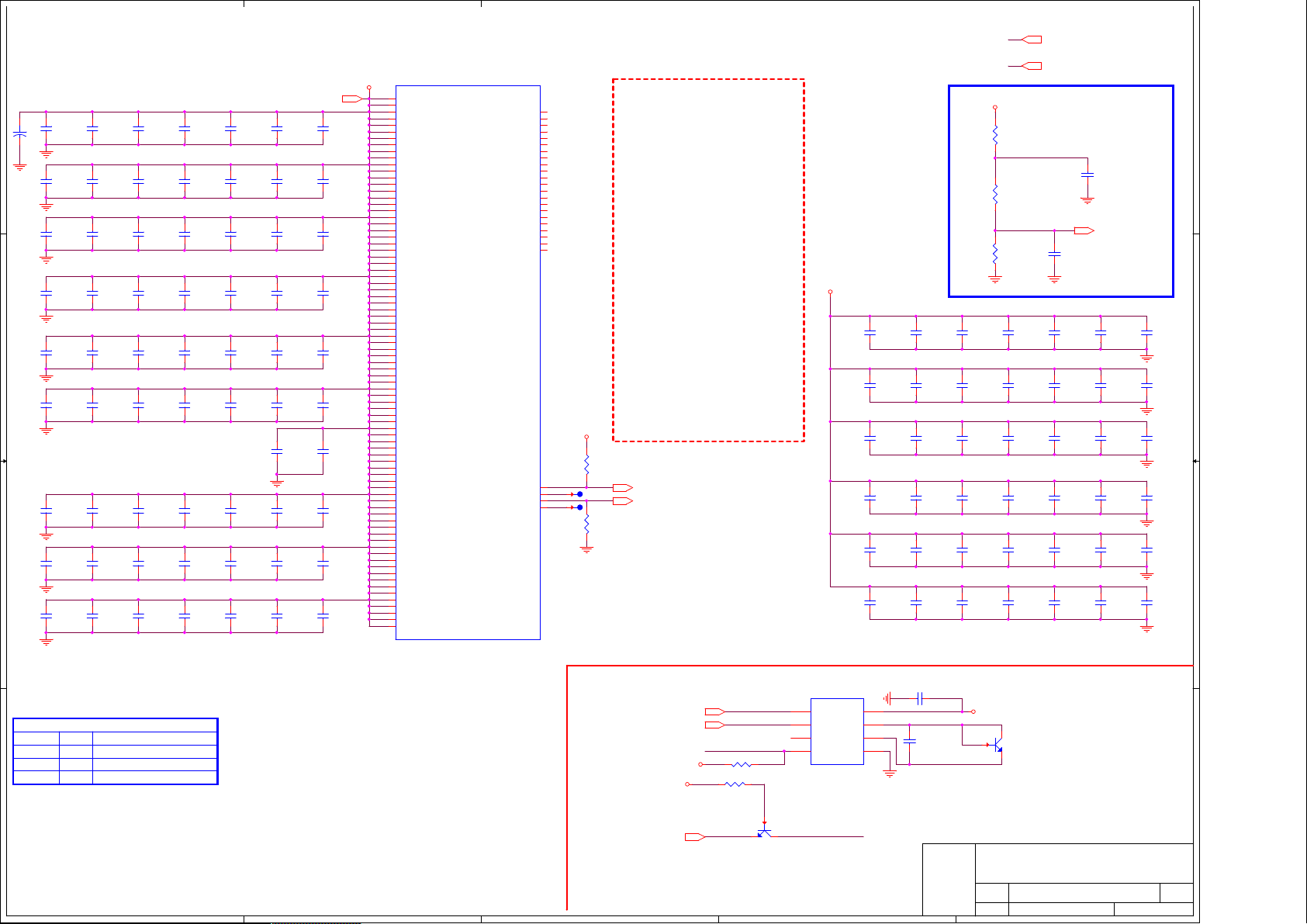

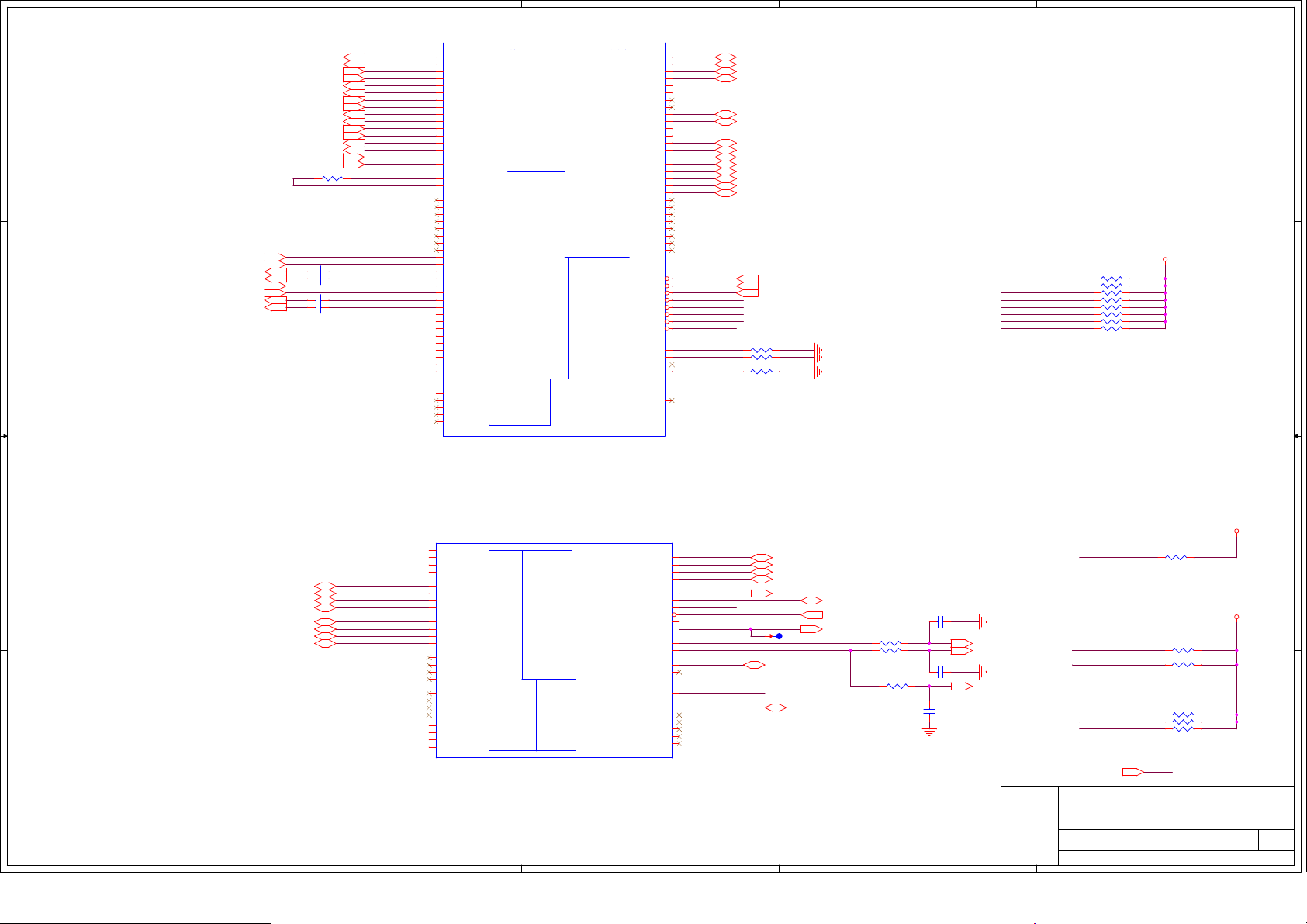

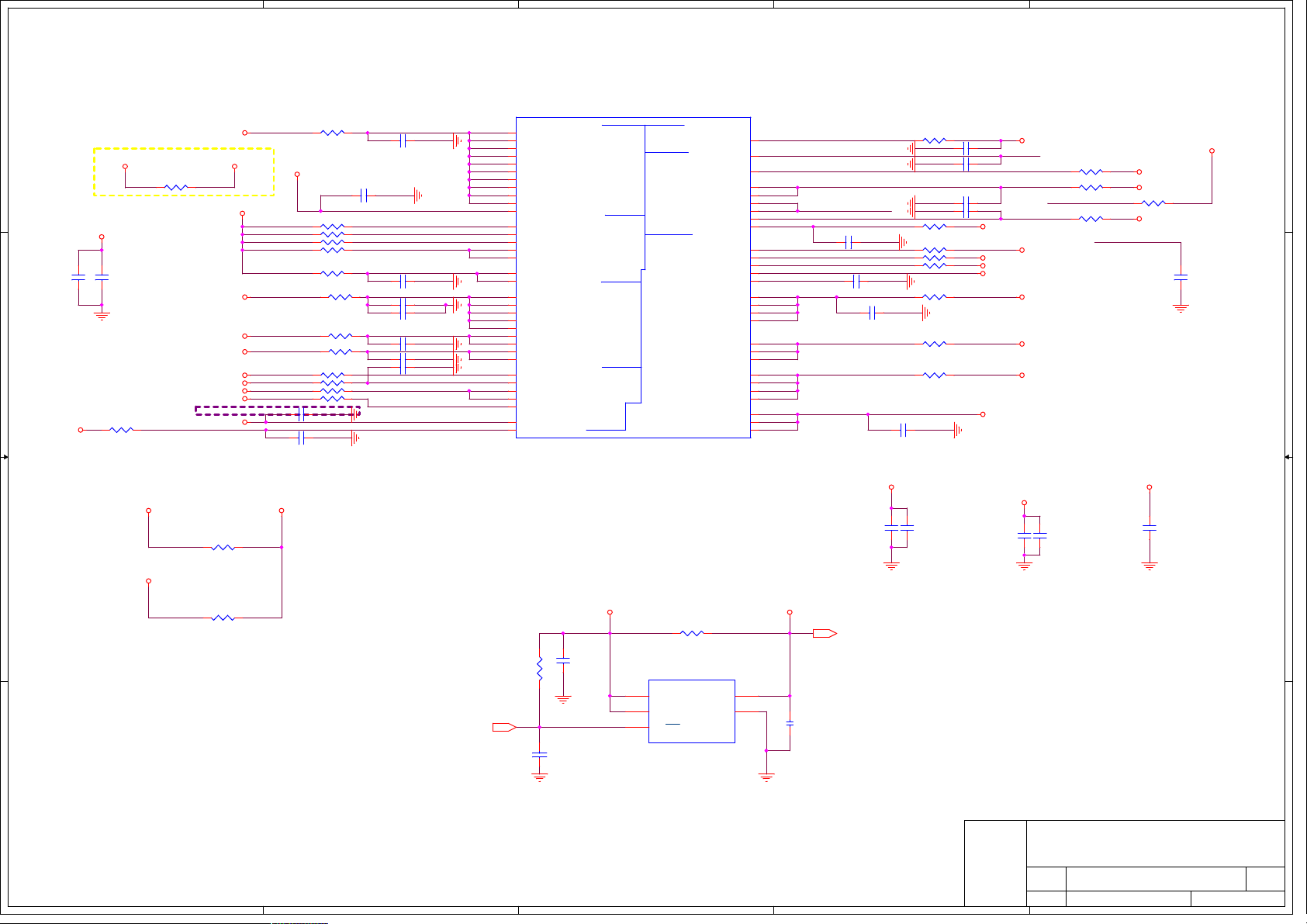

Acer aspire V5-591G Schematic

1

V/+5V S5

+3

PG.39

+1

A A

.05V/+1.5V

PG.40/45

CP

U Core

PG.42~

43

DDR4

PG.41

Cha

rge

PG.38

VGA POWER

47

PG.46~

B B

VC

CGT/VCCSA

PG.44

2

IN

SOD

IMM1

Max. 16GB

STD

SOD

STD

HDD

PG.17

IMM2

Max. 16GB

PG.18

PG.33

3

4

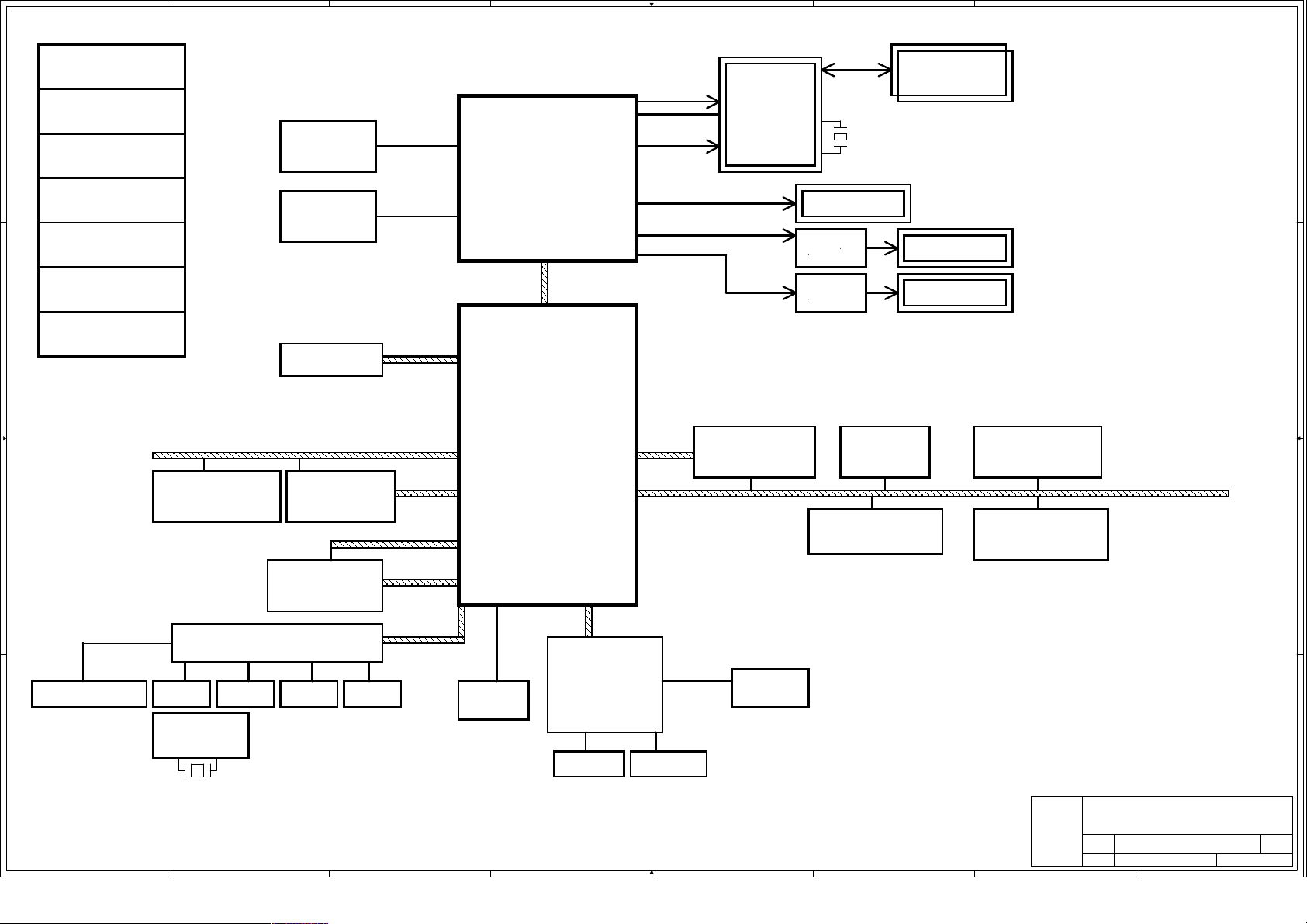

TEL SYSTEM DIAGRAM

PEG

2400MT/s

L

DDR4

Channel A

2400MT/s

DDR4

L

Channel B

SATA2 6GB/s

INTEL

Sky

Lake-H

Processor : Daul / Quad Core

Power : 45 (Watt)

Package : BGA1400

Size : 42 x 28 (mm)

PG.2~8

I

DM

eDP (5.4Gb/s)

DDI

DDI

eD

2

1

5

U

GP

6P-GT

N1

P1

9~P23

P

eD

P Conn.

IT

E6515

PS8

407

P28

P30

TAL 27MHz

X'

P29

6

VR

AM

DDR3

A Conn.

VG

DMI Conn.

H

P24~P27

P29

P3

7

8

01

0

INTEL PCH

US

nx Point

Ly

PCI-E x 1

Port4

LA

N

RTL8111GSH

10/

100/1000

Port3

WLA

COMBO

BT

N

B 2.0

US

PORT7

PG.34PG.31

PCI-E x 4

C C

PG.34

PG.37

FA

SATA0~1 6GB/s

LPC

NROM

G- Sensor

FF SSD

NG

KBC

E IT8987E/BX

IT

LPC Interface

TPM

PAGE 33 NPCT650

SLG3NB3454

L

D D

GreenCLK

25MHz

TPKB

PG.35PG.35 PG.35PG.12

PAGE 33

Power : Watt

Package : FCBGA837

Size : 23 x 23 (mm)

PG.9~

DIO

AU

CO

DEC

AL

P3

5

C255

Speaker

15

PAGE 32

Az

alia

US

PG.32

Dual Digital MIC

B 3.0

PORT1,2

US

PAGE 32

B3-1 & USB3-2

B 2.0

US

B3.0 Ports

Un

X2

PG.36

PORT1,2

iversal HP

We

bcam

PG.29

PORT9

PORT5

DB IO Port

PG.36

P3

2

Ca

rd Reader

To

uch Screen

PG.36

PORT10

PORT8

PG.29

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

1

2

3

4

5

6

7

OCK DIAGRAM

OCK DIAGRAM

OCK DIAGRAM

BL

BL

BL

Date: Sheet of

Date: Sheet of

Date: Sheet of

8

1A

1A

1A

149Monday, September 07, 2015

149Monday, September 07, 2015

149Monday, September 07, 2015

5

4

3

2

1

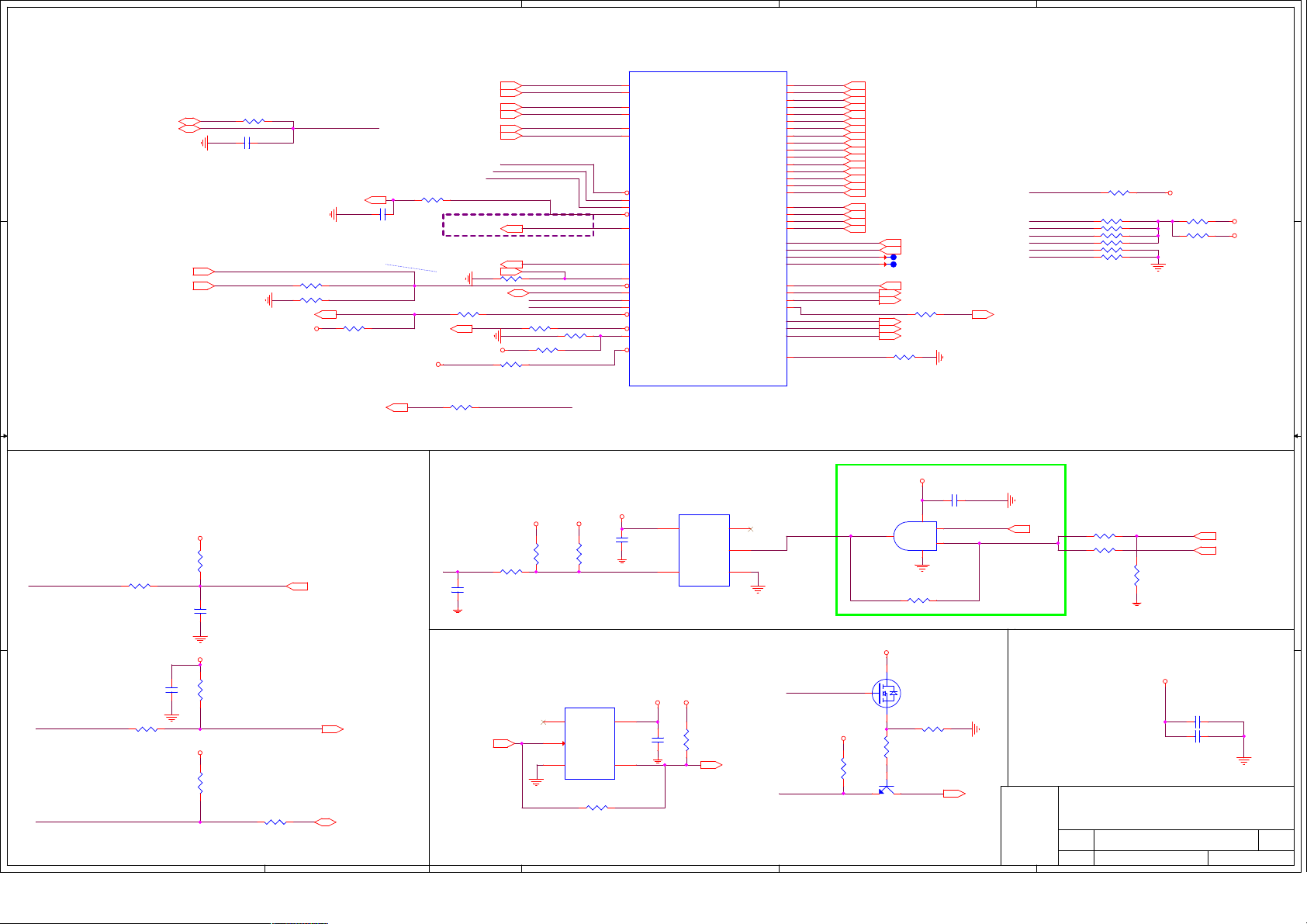

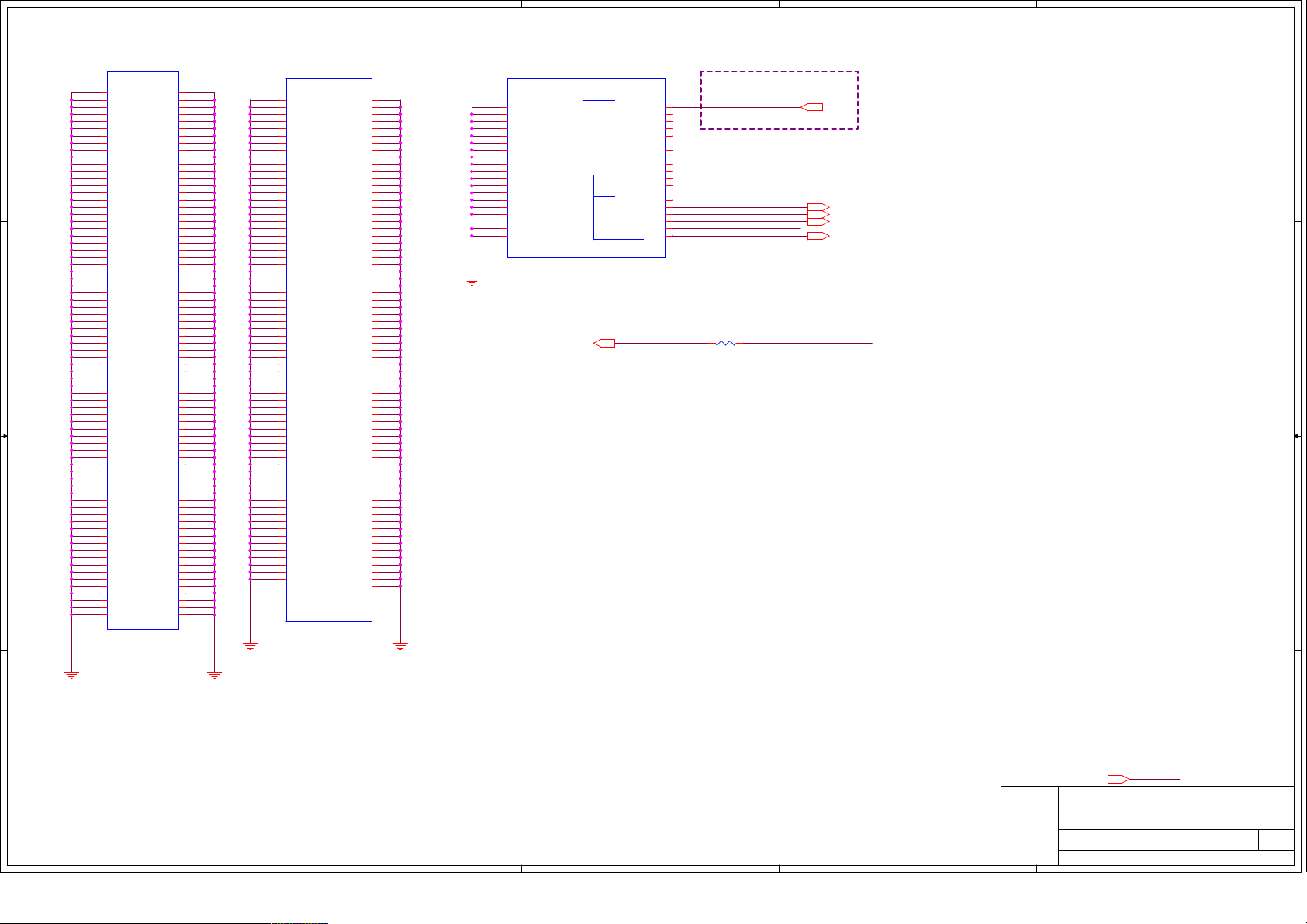

Host CLK:

Trace length < 11000 MILS

Trace spacing = 15 ,20 MILS, Impendence 90 ohm

K_CPU_BCLKP11

CL

K_CPU_BCLKN11

CL

U_PCI_BCLKP11

D D

H_

PECI (50ohm)

Route on micro strip only

Spacing > 18 mils

Trace Length: 15 inch

CP

U RESET#

C C

HPECI Ra,Ca n eed placement close to EC.

H_PECI11

PC

_PECI37

EC

U_PLTRST#R11

CP

TRST#12,16,19,31,33,34,37

PL

CP

U_PLTRST# (50o hm)

Trace Length: 10~17 inches

R563 13/F_4

02 *47P/50V_4

C8

PROCHOT# (50ohm)

Trace Length <11 inches

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

Ra

Ca

PROCHOT#37,38,42

H_

Ch

ange net name_20141203

PM

_SYNC (50ohm)

Trace Length: 1~11.25 inches

R5

41 *1.5K/F_4

R5

42 *750/F_4

_THRMTRIP#5,11,17,18

PM

+V

CCSTPLL

R6

26 1K_4

Rb need placment near PCH

_PECI

EC

07

C8

Cb

47P/50V_4

_THRMTRIP#

PM

Rb

+V

CP

U_PCI_BCLKN11

CP

CL

K_DPLL_NSCCLKP11

K_DPLL_NSCCLKN11

CL

R5

67 499/F_4

Cb need placment near VR

DDR_VTT_CNTL17

PROCPWRGD (50ohm)

Trace Length: 1~11.25 inches

CST_PWRGD16

VC

OCPWRGD10

PR

R553 *SHORT_4

CCSTPLL

+V

SKT

SKT

CCSTPLL

OCC_N_R13

H_

R5

PM

_SYNC11

OCC_N_R

R5

71 49.9/F_4

New CN to PCH pin Y44_20141203

R5

PM_DOWN11

H_

59 20_4

R14 need change to 20ohm

PD

HW

CPU CORE SVID

Layout note: need routing together and ALERT need between CLK and DATA.

B B

A A

OSE TO CPU

CL

PLACE THE PU RESISTORS

H_

CPU_SVIDALRT#

ACE THE PU RESISTORS

PL

CLOSE TO V R

PULL UP IS IN THE VR MODULE

_SVID_CLK_R

VR

OSE TO CPU

CL

PLACE THE PU RESISTORS

CPU_SVIDDAT

H_

R5

45 220/F_4

R540 *SHORT_4

5

CCSTPLL

+V

38

R5

56.2/F_4

55

C7

*0.1U/16V_4

CCSTPLL

+V

5

C8

R5

39

*54.9/F_4

*1000p/50V_4

CCSTPLL

+V

44

R5

100/F_4

SVI

SVI

43 *SHORT_4

R5

D ALERT

VR

_SVID_ALERT# 42

D CLK

SVI

_SVID_CLK 42

VR

D DATA

_SVID_DATA 42

VR

4

VC

CST_PWRGD

R1

17

C4

*0.1u/16V_4

CPU thermal trip

VP_PWR GD42

IM

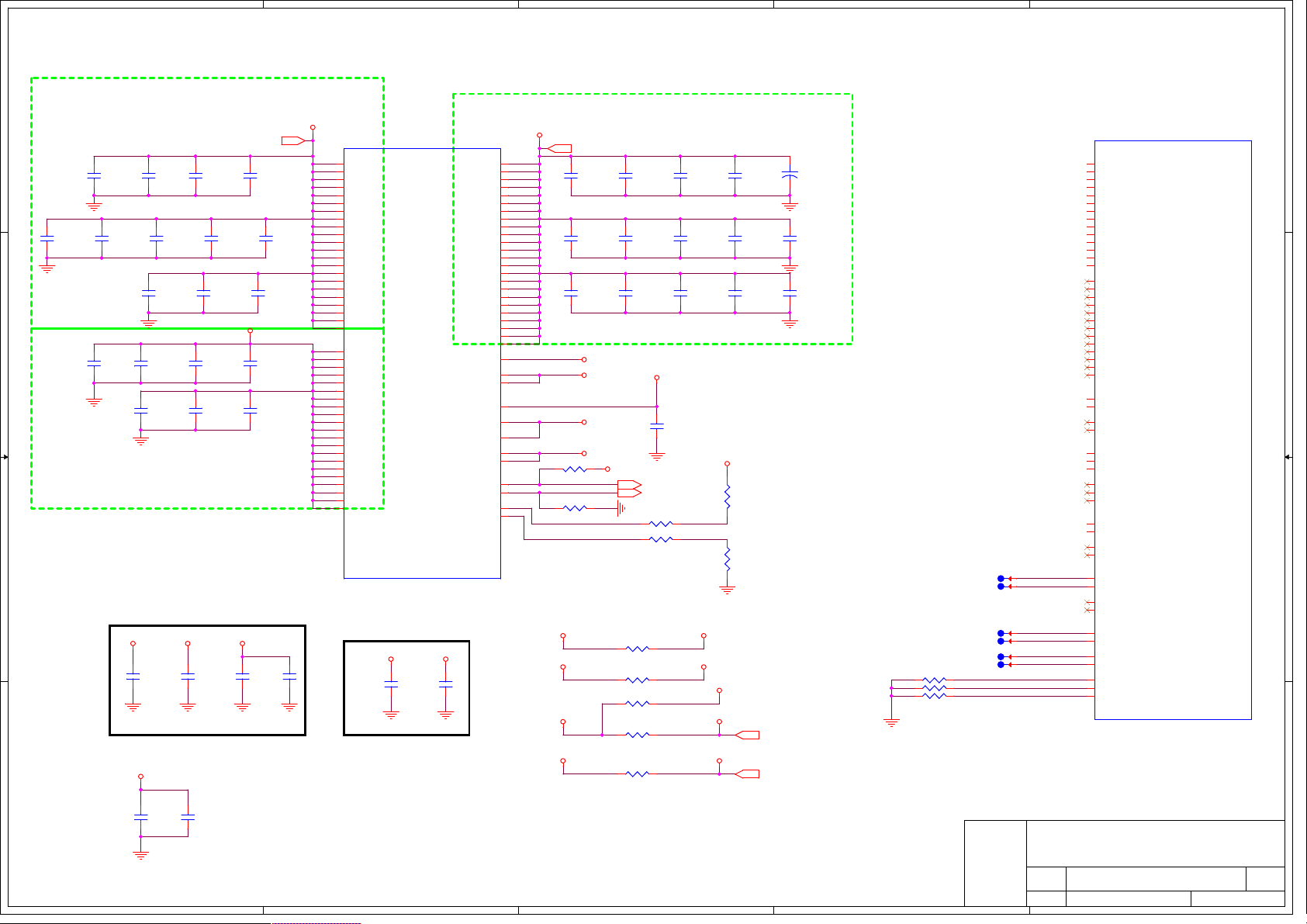

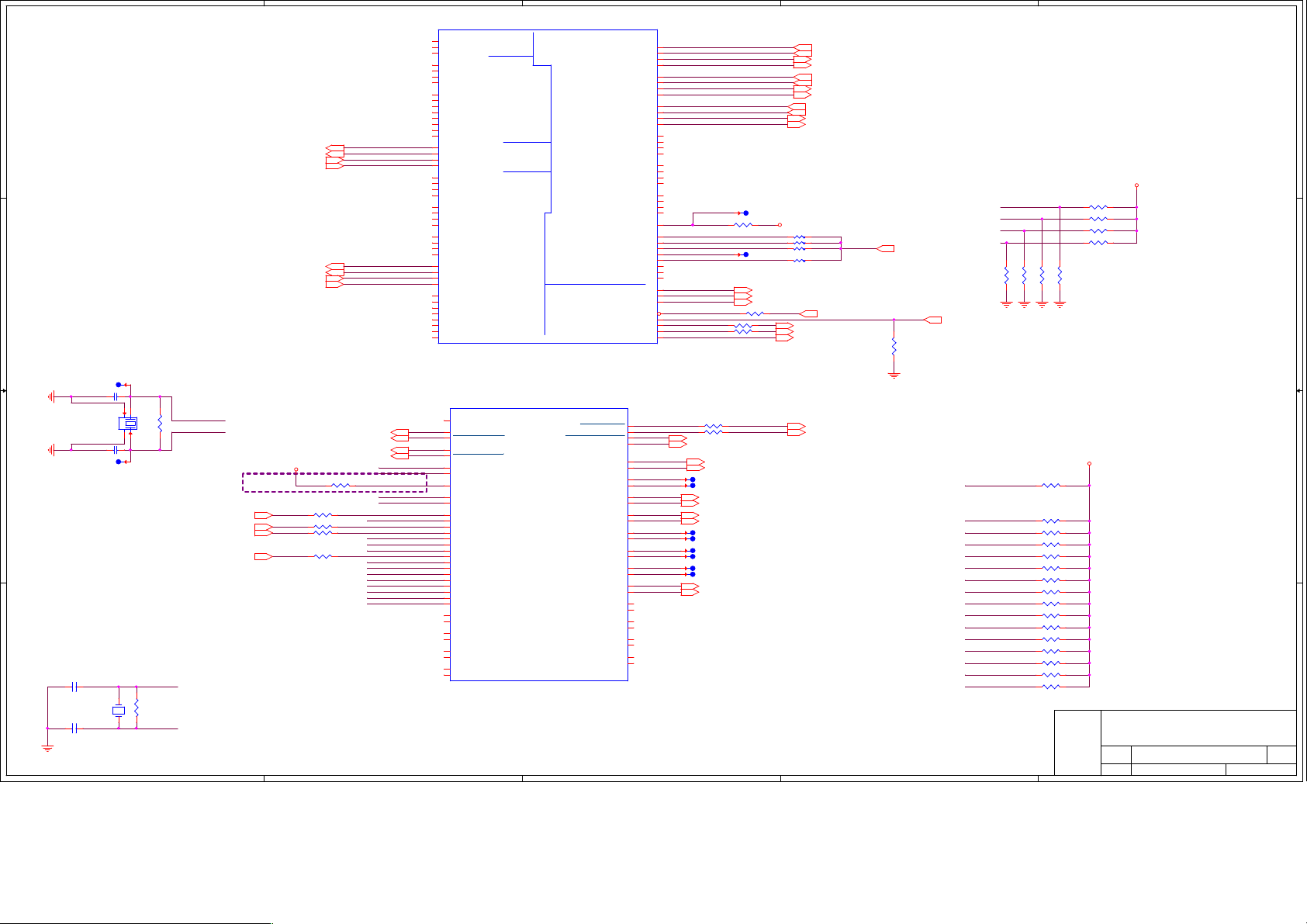

SKYLAKE Processor (CLK,MISC,JTAG)

AKE_HALO

SKYL

U41E

BCLKP

LKN

BC

I_BCLKP

PC

PCI_BCLKN

CLK24P

CL

K24N

DALERT#

VI

DSCK

VI

DSOUT

VI

OCHOT#

PR

DDR_

VTT_CNTL

VC

CST_PWRGD

PR

OCPWRGD

RE

SET#

PM

_SYNC

_DOWN

PM

PEC

I

ERMTRIP#

TH

OCC#

SKT

PROC_SELECT#

CATERR#

SKL_H_BGA_BGA

CRB is via +1.05V PGVCCST PWRGD

5

20

4

+VCCSTPLL

12

41

3

BGA1440

5

OF 14

U2

1

VC

C

GN

Y

74AUP1G07GW

V

+3

R2

00

*10K_4

PR

PR

PR

PR

PR

OC_TRST#

OC_PREQ#

PR

PROC_PRDY#

G_RCOMP

CF

1

NC

2

A

3

D

VP_PWR GD_3V 10

IM

CFG[0]

G[1]

CF

CFG[2]

G[3]

CF

CFG[4]

CF

G[5]

CFG[6]

CF

G[7]

CFG[8]

CF

G[9]

G[10]

CF

CF

G[11]

G[12]

CF

CF

G[13]

G[14]

CF

G[15]

CF

G[17]

CF

G[16]

CF

G[19]

CF

CF

G[18]

BPM

BPM

BPM

BPM

OC_TDO

OC_TDI

OC_TMS

OC_TCK

#[0]

#[1]

#[2]

#[3]

H_

VR

_SVID_CLK_R

H_CPU_SVIDDAT

PROCHOT#_R

60 *10K_4

R5

80 *100K/F_4

R1

H_

PM_DOWN_R

CCSTPLL

+V

79 60.4/F_4

K_CPU_BCLKP

CL

K_CPU_BCLKN

CL

CP

U_PCI_BCLKP

U_PCI_BCLKN

CP

K_DPLL_NSCCLKP

CL

CL

K_DPLL_NSCCLKN

CPU_SVIDALRT#

VTT_CNTL

DDR_

CST_PWRGD

VC

OCPWRGD

PR

PM_DOWN_R

H_

EC

_PECI

56 *SHORT_4

81 *0_4

R1

CA

R1

78

*1K_4

Shortpad change

to 60.4 ohm. 11/6

U2

NC1VCC

2

A

GND3Y

*74AUP1G07GW

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

SKT

OCC_N

BM30

TERR#

.0V

+1

R2

03

1K_4

VC

2

82 *SHORT_4

R1

B31

A32

D35

C36

E31

D31

H13

J31

BN1

+3

V_S5

C4

0.1u/16V_4

CST_PWRGD_R

5

C4

*0.1u/16V_4

4

BN25

G0

CF

BN27

G1

CF

BN26

CF

G2

BN28

CF

G3

BR20

G4

CF

BM20

G5

CF

BT20

G6

CF

BP20

CF

G7

BR23

CF

G8

BR22

CF

G9

BT23

G10

CF

BT22

G11

CF

BM19

CF

G12

BR19

CFG13

BP19

CF

G14

BT19

G15

CF

BN23

CFG17

BP23

G16

CF

BP22

CF

G18

BN22

G19

CF

BR27

P_BPM0

XD

BT27

P_BPM1

XD

BM31

XD

P_BPM2

BT30

P_BPM3

XD

BT28

P_TDO_CPU

XD

BL32

XD

P_TDI_CPU

BP28

P_TMS_CPU

XD

BR28

P_TRST#_CPU

XD

BP30

P_TRST#

XD

BL30

XD

P_PREQ#

BP27

XD

P_PRDY#

BT25

G_RCOMP

CF

VC

CST_PWRGD_EN_L

IM

VP_PWR GD_3V

+V

PM

_THRMTRIP#

CCSTPLL

R1

*1K_4

+V

2

86

CF

G0 16

CF

G1 16

G2 8,16

CF

G3 8,16

CF

G4 8,16

CF

CF

G5 8,16

CF

G6 8,16

G7 16

CF

G8 16

CF

G9 16

CF

CF

G10 8,16

CF

G11 16

CF

G12 8,16

G13 8,16

CF

G14 16

CF

CF

G15 16

CF

G17 16

G16 16

CF

G18 16

CF

CFG19 16

TP

TP

XD

XD

XD

R300 *0_4

XD

XD

XD

R1

4

3

U5

TC7SH08FU

R9

69 *0_4

CCSTPLL

3

Q2

FDV301N

1

R191

1K_4

2

1 3

Q2

3 MMBT3904 -7-F

2

XD

P_BPM0 16

P_BPM1 16

XD

17

18

CP

U XDP

P_TDO_CPU 16

P_TDI_CPU 16

P_TMS_CPU 16

P_TRST# 15,16

P_PREQ# 15,16

P_PRDY# 15,16

2949.9/F_4

V_S5

+3

C8

12 0.1u/16V_4

2

1

3 5

0

R1

84

1 2

*100K_4

JT

AGX_PCH 10,16

SB#

SU

CST_PWRGD_EN

VC

No

SYS_SHDN# 39,45

02

ocessor pull-up (CPU)

Pr

PROCHOT#

H_

XD

P_TDO_CPU

P_TMS_CPU

XD

P_TDI_CPU

XD

P_PREQ#

XD

P_TRST#_CPU

XD

XD

P_TRST#

SB# 10,16,37,39

SU

CPU VDDQ

Del R2574_20141217

te: please keep plane is enough for VDDQ 2. 8A

66 1K_4

R5

R5

78 51_4

77 *51_4

R5

R5

58 *51_4

R5

72 *51_4

R5

79 *51_4

R5

64 51_4

A

B2

S0->S5 & S0->S3

Power of sequence 1us

SUSB# -> VCCST_PWRGD

R204 *0_4

R2

02 *SHORT_4

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Cu

Cu

Cu

stom

stom

stom

Date: Sheet

Date: Sheet

Date: Sheet

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

PC

H_PWROK

HW

R2

10K_4

+1

.0V

+1

65 *SHORT_4

R5

R5

70 *0_4

PG

05

.2VSUS

03 0.1U/16V_4

C4

C4

02 *0.1U/16V_4

1

Pl

PC

HW

acement close to CPU.

+1

.0V

CCSTPLL

+V

H_PWROK 10,37

PG 10,37

1A

1A

1A

of

of

of

249Monday, September 07, 2015

249Monday, September 07, 2015

249Monday, September 07, 2015

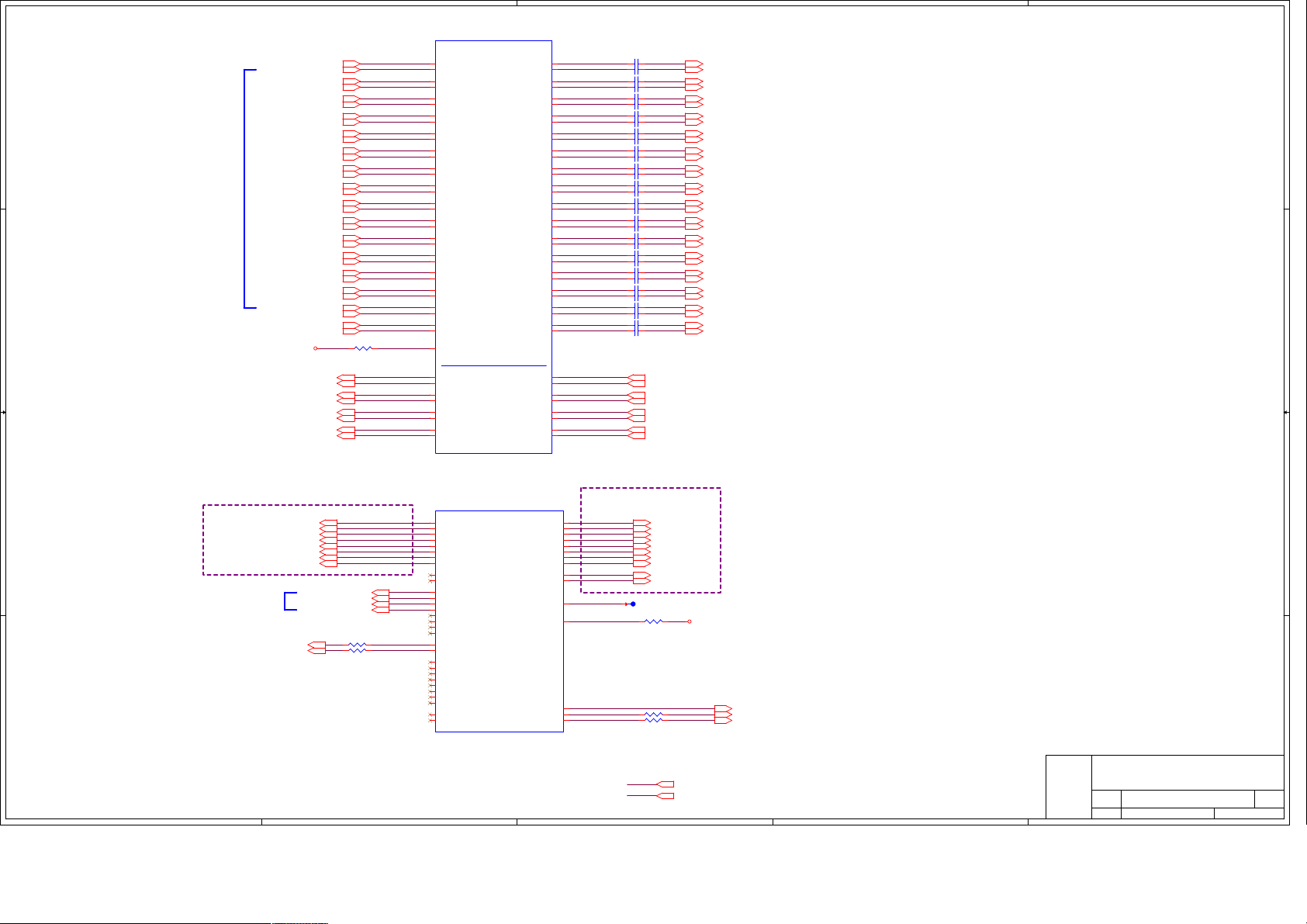

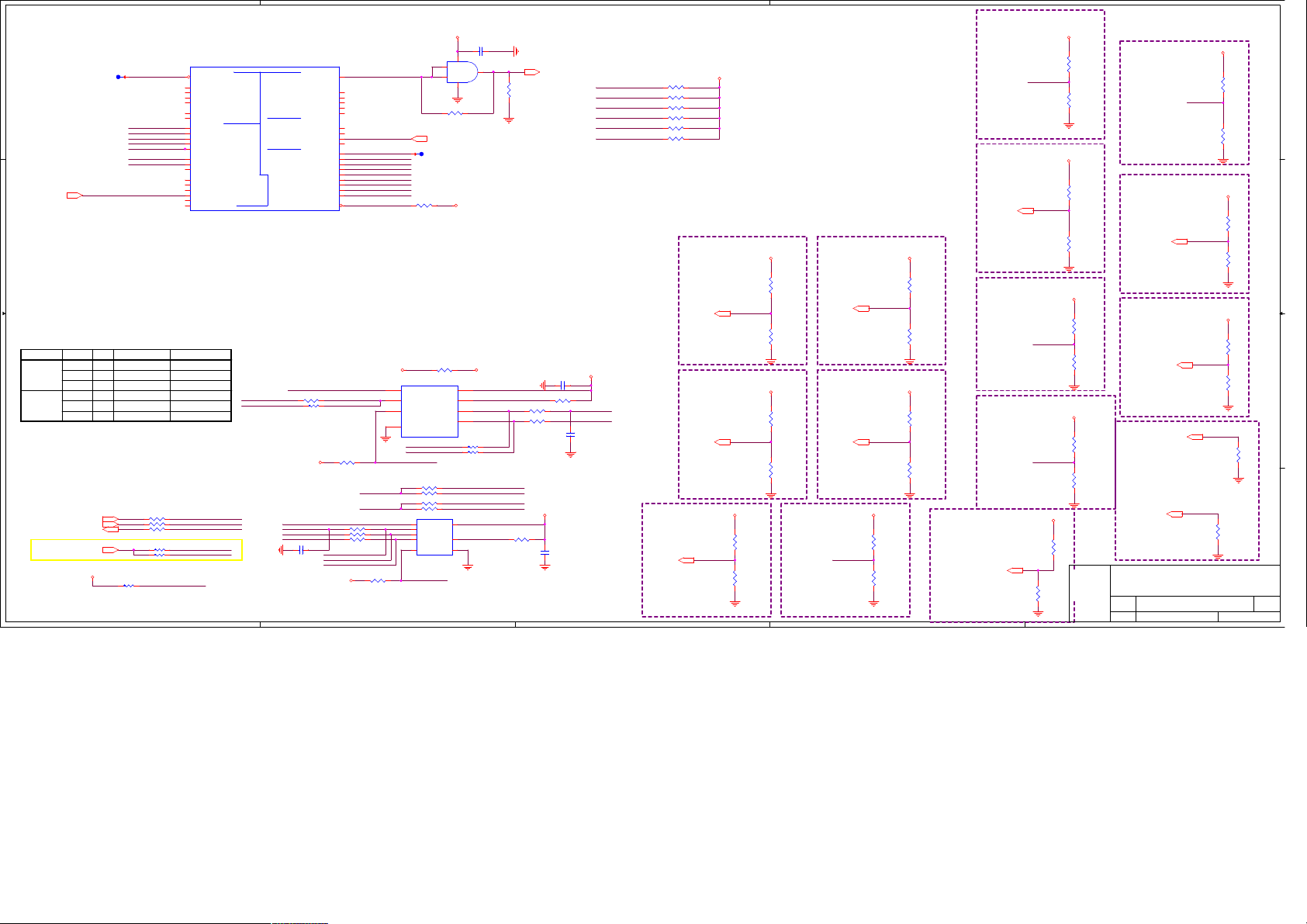

5

PEG_RX1519

_RX#1519

PEG

_RX1419

PEG

_RX#1419

PEG

PEG

_RX1319

_RX#1319

D D

Lane Reversed

C C

dGPU PEG*16

PEG

_RCOMP

Trace length < 400 MILS

Trace width = 12 MILS

Trace spacing = 15 MILS

DM

I

PEG

PEG

_RX1219

PEG

_RX#1219

PEG

_RX1119

PEG_RX#1119

_RX1019

PEG

_RX#1019

PEG

_RX919

PEG

PEG

_RX#919

PEG

_RX819

PEG

_RX#819

PEG_RX719

_RX#719

PEG

_RX619

PEG

_RX#619

PEG

PEG

_RX519

PEG

_RX#519

PEG

_RX419

PEG

_RX#419

_RX319

PEG

PEG_RX#319

_RX219

PEG

_RX#219

PEG

_RX119

PEG

PEG

_RX#119

PEG

_RX019

PEG_RX#019

CCIO

+V

DM

I_RXP09

DM

I_RXN09

DM

I_RXP19

DMI_RXN19

I_RXP29

DM

I_RXN29

DM

I_RXP39

DM

DM

I_RXN39

4

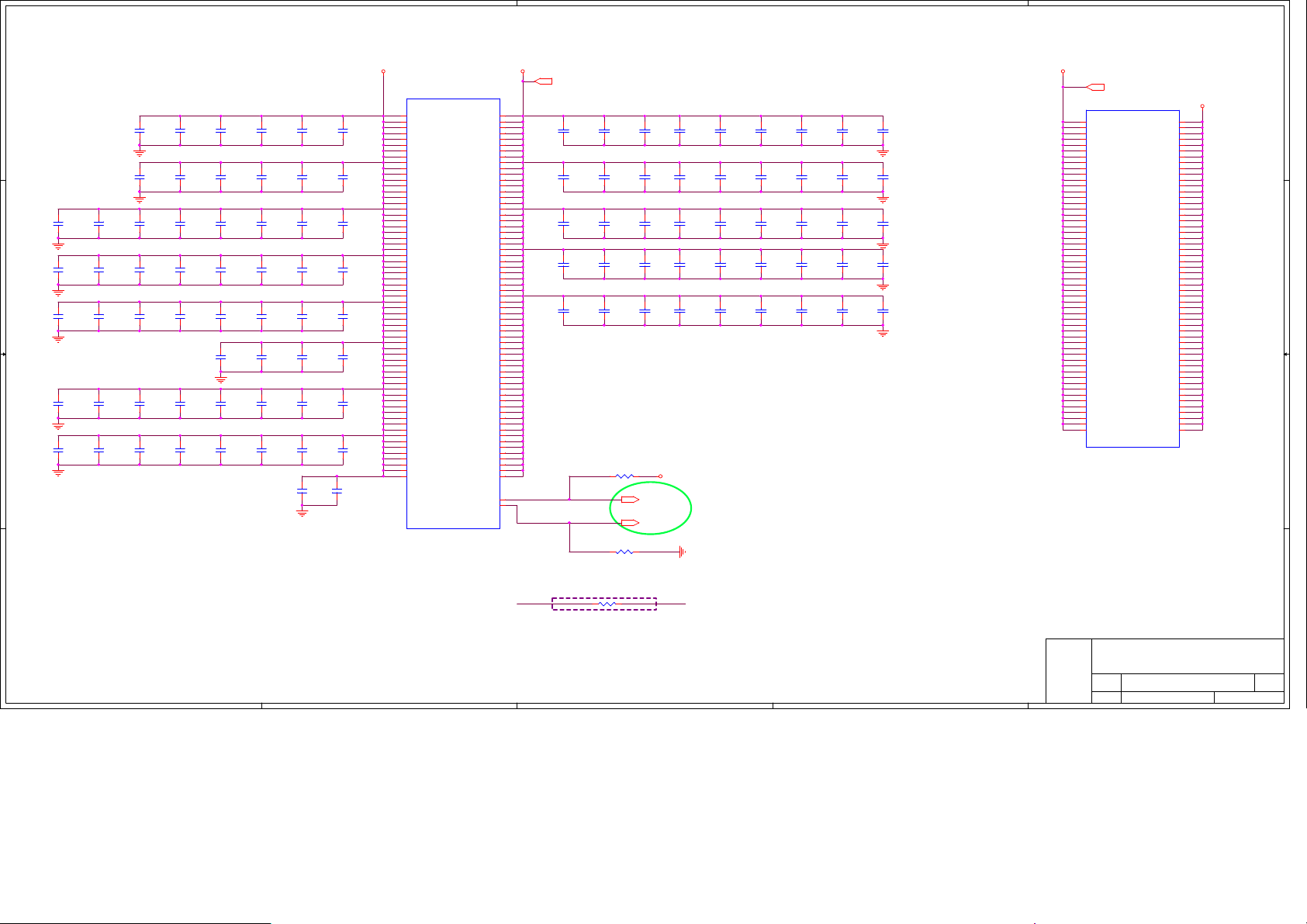

SKYLAKE Processor (DMI,PEG,FDI)

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

PEG

R1

94 24.9/F_4

_COMP

G2

D8

E8

E6

F6

D5

E5

J8

J9

PEG

PEG

PEG

PEG

PEG

PEG_RXN[2]

PEG_RXP[3]

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG

PEG_RXN[10]

PEG_RXP[11]

PEG

PEG

PEG

PEG

PEG

PEG_RXP[14]

PEG

PEG

PEG

PEG

DM

DMI_RXN[0]

DM

DM

DM

DM

DM

DM

SKYL

U41C

_RXP[0]

_RXN[0]

_RXP[1]

_RXN[1]

_RXP[2]

_RXN[3]

_RXP[4]

_RXN[4]

_RXP[5]

_RXN[5]

_RXP[6]

_RXN[6]

_RXP[7]

_RXN[7]

_RXP[8]

_RXN[8]

_RXP[9]

_RXN[9]

_RXP[10]

_RXN[11]

_RXP[12]

_RXN[12]

_RXP[13]

_RXN[13]

_RXN[14]

_RXP[15]

_RXN[15]

_RCOMP

I_RXP[0]

I_RXP[1]

I_RXN[1]

I_RXP[2]

I_RXN[2]

I_RXP[3]

I_RXN[3]

SKL_H_BGA_BGA

BGA1440

AKE_HALO

3

OF 14

_TXP[0]

PEG

_TXN[0]

PEG

_TXP[1]

PEG

PEG

_TXN[1]

PEG

_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

_TXN[3]

PEG

_TXP[4]

PEG

_TXN[4]

PEG

PEG

_TXP[5]

PEG

_TXN[5]

PEG

_TXP[6]

PEG

_TXN[6]

_TXP[7]

PEG

_TXN[7]

PEG

_TXP[8]

PEG

_TXN[8]

PEG

PEG

_TXP[9]

PEG

_TXN[9]

PEG

_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

_TXN[11]

PEG

_TXP[12]

PEG

PEG

_TXN[12]

PEG

_TXP[13]

PEG

_TXN[13]

PEG_TXP[14]

PEG

_TXN[14]

_TXP[15]

PEG

_TXN[15]

PEG

DM

I_TXP[0]

DMI_TXN[0]

I_TXP[1]

DM

I_TXN[1]

DM

I_TXP[2]

DM

DM

I_TXN[2]

DM

I_TXP[3]

DM

I_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

C_

PEG_TX15

C_

PEG_TX#15

C_

PEG_TX14

C_PEG_TX#14

PEG_TX13

C_

PEG_TX#13

C_

PEG_TX12

C_

C_

PEG_TX#12

C_

PEG_TX11

C_

PEG_TX#11

C_PEG_TX10

PEG_TX#10

C_

PEG_TX9

C_

PEG_TX#9

C_

C_

PEG_TX8

C_

PEG_TX#8

C_

PEG_TX7

C_

PEG_TX#7

PEG_TX6

C_

C_PEG_TX#6

PEG_TX5

C_

PEG_TX#5

C_

PEG_TX4

C_

C_

PEG_TX#4

C_

PEG_TX3

C_PEG_TX#3

C_PEG_TX2

PEG_TX#2

C_

PEG_TX1

C_

PEG_TX#1

C_

C_

PEG_TX0

C_

PEG_TX#0

3

194 EV@0.22u/10V_4

C1

C1

195 EV@0.22u/10V_4

C1

200 EV@0.22u/10V_4

C1

198 EV@0.22u/10V_4

C1197 EV@0.22u/10V_4

196 EV@0.22u/10V_4

C1

201 EV@0.22u/10V_4

C1

199 EV@0.22u/10V_4

C1

C1

202 EV@0.22u/10V_4

C1

203 EV@0.22u/10V_4

C1

208 EV@0.22u/10V_4

C1

206 EV@0.22u/10V_4

205 EV@0.22u/10V_4

C1

C1204 EV@0.22u/10V_4

209 EV@0.22u/10V_4

C1

207 EV@0.22u/10V_4

C1

13 EV@0.22u/10V_ 4

C8

C8

11 EV@0.22u/10V_ 4

C8

14 EV@0.22u/10V_ 4

C815 EV@0.22u/10V _4

C817 EV@0.22u/10V _4

16 EV@0.22u/10V_ 4

C8

19 EV@0.22u/10V_ 4

C8

18 EV@0.22u/10V_ 4

C8

C8

22 EV@0.22u/10V_ 4

C8

20 EV@0.22u/10V_ 4

C8

23 EV@0.22u/10V_ 4

C8

25 EV@0.22u/10V_ 4

27 EV@0.22u/10V_ 4

C8

26 EV@0.22u/10V_ 4

C8

28 EV@0.22u/10V_ 4

C8

30 EV@0.22u/10V_ 4

C8

DM

I_TXP0 9

DM

I_TXN0 9

DM

I_TXP1 9

DMI_TXN1 9

I_TXP2 9

DM

I_TXN2 9

DM

I_TXP3 9

DM

DM

I_TXN3 9

PEG_TX15 19

_TX#15 19

PEG

_TX14 19

PEG

_TX#14 19

PEG

PEG

_TX13 19

_TX#13 19

PEG

PEG

_TX12 19

PEG_TX#12 19

PEG

_TX11 19

PEG_TX#11 19

_TX10 19

PEG

_TX#10 19

PEG

_TX9 19

PEG

PEG

_TX#9 19

PEG

_TX8 19

PEG

_TX#8 19

PEG_TX7 19

_TX#7 19

PEG

_TX6 19

PEG

_TX#6 19

PEG

PEG

_TX5 19

PEG

_TX#5 19

PEG

_TX4 19

PEG_TX#4 19

_TX3 19

PEG

PEG_TX#3 19

_TX2 19

PEG

_TX#2 19

PEG

_TX1 19

PEG

PEG

_TX#1 19

PEG

_TX0 19

PEG

_TX#0 19

Lane

Reversed

2

1

03

SKYL

AKE_HALO

U41D

B B

A A

5

HDM

I

CRT

CRT

CRT

CRT

CRT

4

_AUX_C

_AUX#_C

K36

K37

J35

J34

H37

H36

J37

J38

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

DDI1_TXP[0]

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI2_AUXN

DDI3_TXP[0]

DDI

DDI

DDI

DDI

DDI

DDI

DDI

DDI3_AUXP

DDI

_D2

IN

_D230

IN

IN

_D2#30

IN

IN_D130

_D1#30

IN

IN_D030

IN

_D0#30

IN

_CLK30

_CLK#30

IN

_AUXP28

_AUXN28

_D2#

_D1

IN

_D1#

IN

_D0

IN

_D0#

IN

IN_CLK

IN

_CLK#

_TXP028

CRT

_TXN028

CRT

_TXP128

CRT

CRT_TXN128

R998*short_4

R9

99*short_4

1_TXN[0]

1_TXP[1]

1_TXN[1]

1_TXP[2]

1_TXN[2]

1_TXP[3]

1_TXN[3]

1_AUXP

1_AUXN

2_TXP[0]

2_TXN[0]

2_TXP[1]

2_TXN[1]

2_TXP[2]

2_TXN[2]

2_TXP[3]

2_TXN[3]

2_AUXP

3_TXN[0]

3_TXP[1]

3_TXN[1]

3_TXP[2]

3_TXN[2]

3_TXP[3]

3_TXN[3]

3_AUXN

SKL_H_BGA_BGA

BGA1440

4 OF 14

PR

EDP_TXP[0]

ED

P_TXN[0]

ED

P_TXP[1]

P_TXN[1]

ED

ED

P_TXN[2]

P_TXP[2]

ED

ED

P_TXN[3]

P_TXP[3]

ED

P_AUXP

ED

P_AUXN

ED

ED

P_DISP_UTIL

ED

P_RCOMP

OC_AUDIO_CLK

PR

PROC_AUDIO_SDI

OC_AUDIO_SDO

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

D37

G27

G25

G29

eDP

P_TXP0 29

ED

P_TXN0 29

ED

EDP_TXP1 29

P_TXN1 29

ED

EDP_TXN2 29

ED

P_TXP2 29

ED

P_TXN3 29

P_TXP3 29

ED

P_AUXP 29

ED

ED

P_AUXN 29

ED

P_DISP_UTIL

EDP_RCOMP

DP

P_RCOMP

eD

Trace length < 100 Mils

Trace Width 20 Mils Trace Spacing 25 Mils

D_AZACPU_SO

AU

TP87

1624.9/F_4

R1

+V

& PEG Compensation

R1

27 *SHORT_4

R1

26 20_4

CCIO 6 ,16,38,40,42, 45

+V

.0V 2,5,6,10,1 6,40,45

+1

3

CCIO

D_AZACPU_SCLK 10

AU

AU

D_AZACPU_SDO 10

D_AZACPU_SDI 10

AU

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

2

B 1/5 (PCIE&DMI&FDI)

B 1/5 (PCIE&DMI&FDI)

B 1/5 (PCIE&DMI&FDI)

SN

SN

SN

Date: Sheet

Date: Sheet

Date: Sheet

1

1A

1A

1A

349Tuesday, Augu st 25, 2015

349Tuesday, Augu st 25, 2015

349Tuesday, Augu st 25, 2015

of

of

of

5

4

3

2

1

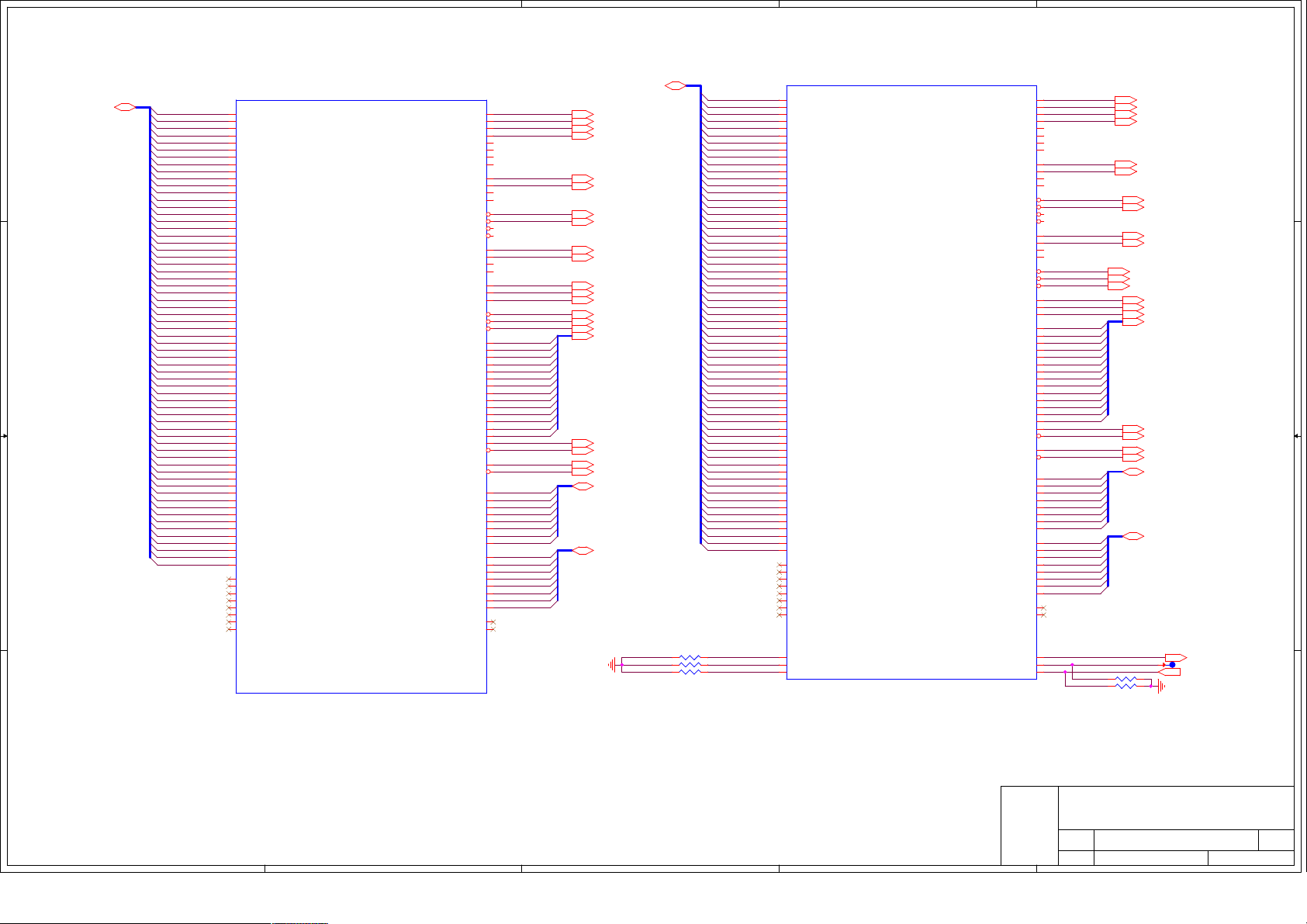

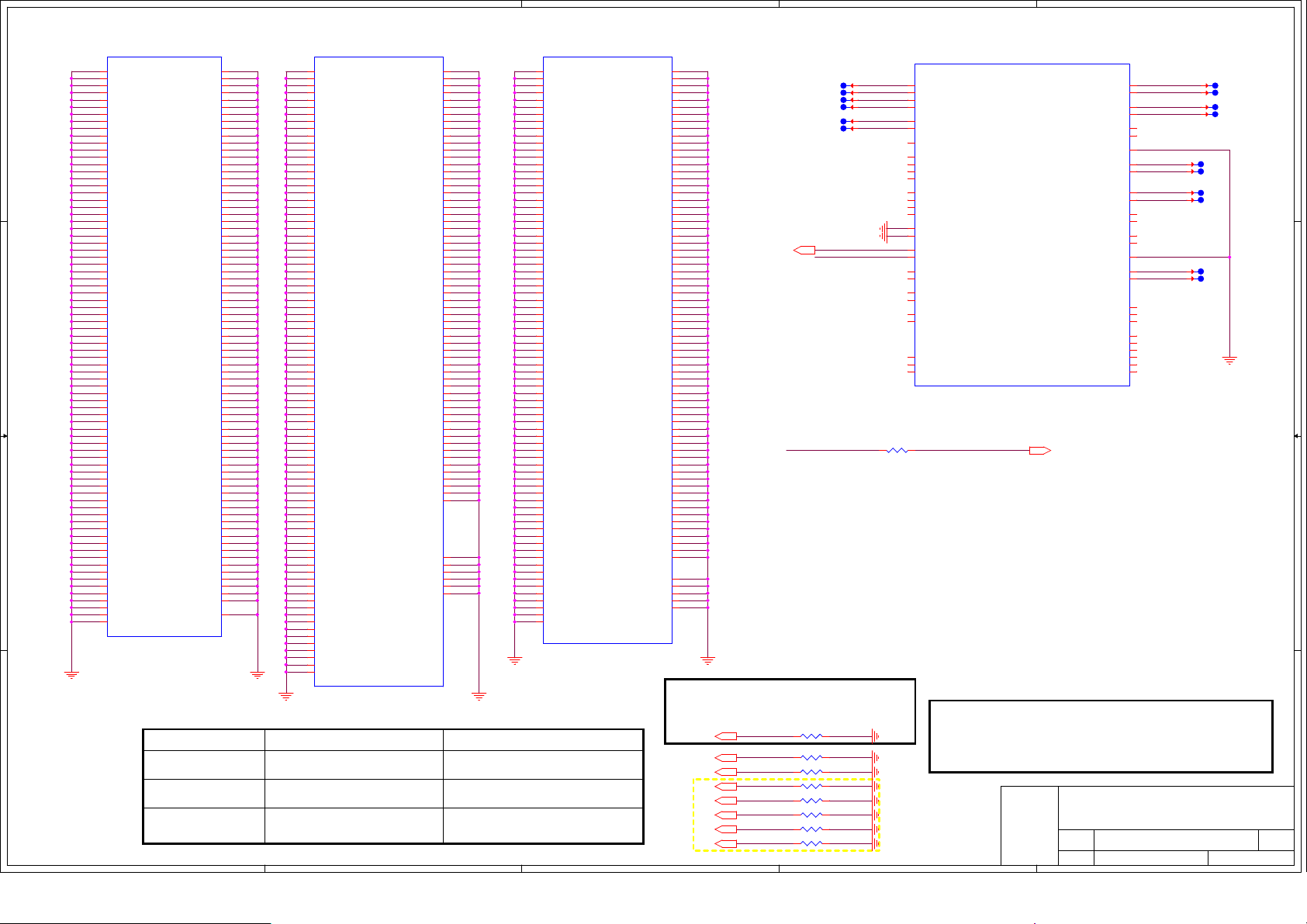

SK

YLAKE Processor (DDR3)

CHANNEL B

SKYLAKE_HALO

BGA1440

DDR1

_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1

_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1

_CAS#/DDR1_CAB[1]/DDR1_MA[15]

_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1

DDR1

_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1

_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1

_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1

_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1

_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1

DDR1

_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1

DDR1

_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1

OF 14

2

DDR1_CKP[0]

_CKN[0]

DDR1

DDR1_CKN[1]

DDR1

_CKP[1]

DDR1_CLKP[2]

DDR1

_CLKN[2]

DDR1_CLKP[3]

DDR1

_CLKN[3]

DDR1

_CKE[0]

_CKE[1]

DDR1

DDR1

_CKE[2]

_CKE[3]

DDR1

_CS#[0]

DDR1

_CS#[1]

DDR1

_CS#[2]

DDR1

_CS#[3]

DDR1

_ODT[0]

DDR1

DDR1

_ODT[1]

_ODT[2]

DDR1

DDR1

_ODT[3]

DDR1_MA[3]

_MA[4]

DDR1

_PAR

DDR1

_ALERT#

DDR1

_DQSN[0]/DDR0_DQSN[2]

_DQSN[1]/DDR0_DQSN[3]

_DQSN[2]/DDR0_DQSN[6]

_DQSN[3]/DDR0_DQSN[7]

_DQSN[4]/DDR1_DQSN[2]

_DQSN[5]/DDR1_DQSN[3]

DDR1

_DQSN[6]

DDR1

_DQSP[0]/DDR0_DQSP[2]

_DQSP[1]/DDR0_DQSP[3]

_DQSP[2]/DDR0_DQSP[6]

_DQSP[3]/DDR0_DQSP[7]

_DQSP[4]/DDR1_DQSP[2]

_DQSP[5]/DDR1_DQSP[3]

_DQSN[7]

DDR1_DQSP[6]

_DQSP[7]

DDR1

_DQSP[8]

DDR1

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

B_BA#0

M_

M_

B_BA#1

B_BG#0

M_

M_

B_A0

M_

B_A1

M_

B_A2

B_A3

M_

B_A4

M_

M_

B_A5

M_

B_A6

M_

B_A7

B_A8

M_

B_A9

M_

M_B_A10

M_

B_A11

M_

B_A12

B_A13

M_

B_BG#1

M_

B_ACT#

M_

M_

B_PARITY

B_ALERT#

M_

M_

B_DQSN0

M_

B_DQSN1

M_

B_DQSN2

B_DQSN3

M_

B_DQSN4

M_

M_

B_DQSN5

M_

B_DQSN6

B_DQSN7

M_

B_DQSP0

M_

M_

B_DQSP1

M_

B_DQSP2

M_

B_DQSP3

M_

B_DQSP4

B_DQSP5

M_

M_

B_DQSP6

M_B_DQSP7

_VREF

SM

SM

DDR_VREF_DQ0_M3

DDR_VREF_DQ1_M3

SM

M_

M_

M_

M_

M_

M_

B_RAS# 18

M_

B_WE# 18

M_

B_CAS# 18

M_

M_

M_

R1

46*1K _4

R154*1K _4

M_

M_B_CS#1 18

M_

M_

M_

B_CLKP0 18

B_CLKN0 18

B_CLKN1 18

B_CLKP1 18

B_CKE0 18

B_CKE1 18

B_CS#0 18

B_ODT0_CPU 18

B_ODT1_CPU 18

B_BA#0 18

M_

B_BA#1 18

M_

M_

B_BG#0 18

B_A[13:0] 18

M_

B_BG#1 18

M_

B_ACT# 18

B_PARITY 18

M_

B_ALERT# 18

M_

B_DQSN[7:0] 18

B_DQSP[7:0] 18

M_

AKE_HALO

A_DQ[63:0]17

D D

C C

B B

M_

VD_V10 must be grounded

RS

A_DQ0

M_

A_DQ1

M_

A_DQ2

M_

M_

A_DQ3

M_

A_DQ4

M_

A_DQ5

A_DQ6

M_

A_DQ7

M_

M_

A_DQ8

M_A_DQ9

M_

A_DQ10

A_DQ11

M_

A_DQ12

M_

M_A_DQ13

A_DQ14

M_

M_

A_DQ15

A_DQ16

M_

A_DQ17

M_

A_DQ18

M_

A_DQ19

M_

M_

A_DQ20

A_DQ21

M_

A_DQ22

M_

A_DQ23

M_

A_DQ24

M_

M_

A_DQ25

A_DQ26

M_

M_

A_DQ27

A_DQ28

M_

A_DQ29

M_

M_

A_DQ30

M_

A_DQ31

M_

A_DQ32

A_DQ33

M_

A_DQ34

M_

M_

A_DQ35

M_

A_DQ36

M_

A_DQ37

A_DQ38

M_

A_DQ39

M_

M_A_DQ40

M_

A_DQ41

M_

A_DQ42

A_DQ43

M_

A_DQ44

M_

A_DQ45

M_

M_

A_DQ46

M_

A_DQ47

A_DQ48

M_

M_

A_DQ49

A_DQ50

M_

M_

A_DQ51

M_

A_DQ52

M_

A_DQ53

A_DQ54

M_

A_DQ55

M_

M_

A_DQ56

M_

A_DQ57

A_DQ58

M_

M_

A_DQ59

A_DQ60

M_

M_

A_DQ61

M_

A_DQ62

M_

A_DQ63

U41A

BR6

DDR0_DQ[0]

BT6

DDR0

_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0

_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0

_DQ[5]

BP2

_DQ[6]

DDR0

BN3

DDR0

_DQ[7]

BL4

_DQ[8]

DDR0

BL5

DDR0

_DQ[9]

BL2

_DQ[10]

DDR0

BM1

_DQ[11]

DDR0

BK4

_DQ[12]

DDR0

BK5

_DQ[13]

DDR0

BK1

_DQ[14]

DDR0

BK2

_DQ[15]

DDR0

BG4

DDR0

_DQ[16]/DDR0_DQ[32]

BG5

_DQ[17]/DDR0_DQ[33]

DDR0

BF4

DDR0

_DQ[18]/DDR0_DQ[34]

BF5

_DQ[19]/DDR0_DQ[35]

DDR0

BG2

DDR0

_DQ[20]/DDR0_DQ[36]

BG1

DDR0

_DQ[21]/DDR0_DQ[37]

BF1

DDR0

_DQ[22]/DDR0_DQ[38]

BF2

DDR0

_DQ[23]/DDR0_DQ[39]

BD2

DDR0

_DQ[24]/DDR0_DQ[40]

BD1

DDR0

_DQ[25]/DDR0_DQ[41]

BC4

_DQ[26]/DDR0_DQ[42]

DDR0

BC5

DDR0

_DQ[27]/DDR0_DQ[43]

BD5

_DQ[28]/DDR0_DQ[44]

DDR0

BD4

DDR0

_DQ[29]/DDR0_DQ[45]

BC1

_DQ[30]/DDR0_DQ[46]

DDR0

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

_DQ[32]/DDR1_DQ[0]

DDR0

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

_DQ[34]/DDR1_DQ[2]

DDR0

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0

_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0

_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0

_DQ[40]/DDR1_DQ[8]

V2

_DQ[41]/DDR1_DQ[9]

DDR0

U1

DDR0

_DQ[42]/DDR1_DQ[10]

U2

_DQ[43]/DDR1_DQ[11]

DDR0

V1

DDR0

_DQ[44]/DDR1_DQ[12]

V4

_DQ[45]/DDR1_DQ[13]

DDR0

U5

_DQ[46]/DDR1_DQ[14]

DDR0

U4

_DQ[47]/DDR1_DQ[15]

DDR0

R2

_DQ[48]/DDR1_DQ[32]

DDR0

P5

_DQ[49]/DDR1_DQ[33]

DDR0

R4

_DQ[50]/DDR1_DQ[34]

DDR0

P4

DDR0

_DQ[51]/DDR1_DQ[35]

R5

_DQ[52]/DDR1_DQ[36]

DDR0

P2

DDR0

_DQ[53]/DDR1_DQ[37]

R1

_DQ[54]/DDR1_DQ[38]

DDR0

P1

DDR0

_DQ[55]/DDR1_DQ[39]

M4

DDR0

_DQ[56]/DDR1_DQ[40]

M1

DDR0

_DQ[57]/DDR1_DQ[41]

L4

DDR0

_DQ[58]/DDR1_DQ[42]

L2

DDR0

_DQ[59]/DDR1_DQ[43]

M5

DDR0

_DQ[60]/DDR1_DQ[44]

M2

_DQ[61]/DDR1_DQ[45]

DDR0

L5

DDR0

_DQ[62]/DDR1_DQ[46]

L1

_DQ[63]/DDR1_DQ[47]

DDR0

BA2

_ECC[0]

DDR0

BA1

DDR0_ECC[1]

AY4

_ECC[2]

DDR0

AY5

DDR0_ECC[3]

BA5

_ECC[4]

DDR0

BA4

DDR0_ECC[5]

AY1

DDR0

_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

SKL_H_BGA_BGA

SKYL

BGA1440

DDR0

_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0

_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0

_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0

DDR0

_WE#/DDR0_CAB[2]/DDR0_MA[14]

_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0

_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0

_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0

_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0

DDR0

_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0

DDR0

_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0

_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0

_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0

OF 14

1

DDR0_CKP[0]

DDR0

_CKN[0]

DDR0_CKP[1]

DDR0

_CKN[1]

DDR0_CLKP[2]

DDR0

_CLKN[2]

_CLKP[3]

DDR0

DDR0

_CLKN[3]

DDR0

_CKE[0]

_CKE[1]

DDR0

_CKE[2]

DDR0

_CKE[3]

DDR0

_CS#[0]

DDR0

_CS#[1]

DDR0

DDR0

_CS#[2]

_CS#[3]

DDR0

_ODT[0]

DDR0

DDR0

_ODT[1]

DDR0

_ODT[2]

DDR0

_ODT[3]

DDR0_MA[3]

DDR0

_MA[4]

_PAR

DDR0

_ALERT#

DDR0

DDR0

_DQSN[0]

_DQSN[1]

DDR0

_DQSN[2]/DDR0_DQSN[4]

_DQSN[3]/DDR0_DQSN[5]

_DQSN[4]/DDR1_DQSN[0]

_DQSN[5]/DDR1_DQSN[1]

_DQSN[6]/DDR1_DQSN[4]

_DQSN[7]/DDR1_DQSN[5]

DDR0

_DQSP[0]

_DQSP[1]

DDR0

_DQSP[2]/DDR0_DQSP[4]

_DQSP[3]/DDR0_DQSP[5]

_DQSP[5]/DDR1_DQSP[1]

_DQSP[7]/DDR1_DQSP[5]

DDR0

_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK2

AK1

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AA3

U3

P3

L3

BP5

BK3

BF3

BC3

AB3

V3

R3

M3

AY3

BA3

A_BA#0

M_

M_

A_BA#1

A_BG#0

M_

M_

A_A0

A_A1

M_

A_A2

M_

M_

A_A3

M_

A_A4

M_

A_A5

A_A6

M_

A_A7

M_

M_A_A8

M_

A_A9

M_

A_A10

A_A11

M_

A_A12

M_

A_A13

M_

M_

A_BG#1

M_

A_ACT#

M_

A_PARITY

A_ALERT#

M_

M_

A_DQSN0

A_DQSN1

M_

A_DQSN2

M_

M_

A_DQSN3

M_

A_DQSN4

A_DQSN5

M_

M_

A_DQSN6

A_DQSN7

M_

M_

A_DQSP0

M_

A_DQSP1

M_

A_DQSP2

A_DQSP3

M_

M_

A_DQSP4

M_A_DQSP5

M_

A_DQSP6

M_

A_DQSP7

B_DQ[63:0]18

A_CLKP0 17

M_

A_CLKN0 17

M_

A_CLKP1 17

M_

M_

A_CLKN1 17

M_A_CKE0 17

M_

A_CKE1 17

A_CS#0 17

M_

M_

A_CS#1 17

A_ODT0_CPU 17

M_

M_

A_ODT1_CPU 17

A_BA#0 17

M_

A_BA#1 17

M_

A_BG#0 17

M_

A_RAS# 17

M_

A_WE# 17

M_

M_

A_CAS# 17

M_

A_A[13:0] 17

A_BG#1 17

M_

A_ACT# 17

M_

M_

A_PARITY 17

M_

A_ALERT# 17

M_

A_DQSN[7:0] 17

A_DQSP[7:0] 17

M_

R1

R1

R1

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_B_DQ11

M_

M_

M_

M_B_DQ15

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_B_DQ42

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

SM

95121/F_4

SM

9375/F_4

SM

92100/F_4

B_DQ0

B_DQ1

B_DQ2

B_DQ3

B_DQ4

B_DQ5

B_DQ6

B_DQ7

B_DQ8

B_DQ9

B_DQ10

B_DQ12

B_DQ13

B_DQ14

B_DQ16

B_DQ17

B_DQ18

B_DQ19

B_DQ20

B_DQ21

B_DQ22

B_DQ23

B_DQ24

B_DQ25

B_DQ26

B_DQ27

B_DQ28

B_DQ29

B_DQ30

B_DQ31

B_DQ32

B_DQ33

B_DQ34

B_DQ35

B_DQ36

B_DQ37

B_DQ38

B_DQ39

B_DQ40

B_DQ41

B_DQ43

B_DQ44

B_DQ45

B_DQ46

B_DQ47

B_DQ48

B_DQ49

B_DQ50

B_DQ51

B_DQ52

B_DQ53

B_DQ54

B_DQ55

B_DQ56

B_DQ57

B_DQ58

B_DQ59

B_DQ60

B_DQ61

B_DQ62

B_DQ63

_RCOMP_0

_RCOMP_1

_RCOMP_2

U41B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

_DQ[1]/DDR0_DQ[17]

DDR1

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1

_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1

_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1

_DQ[7]/DDR0_DQ[23]

BL12

_DQ[8]/DDR0_DQ[24]

DDR1

BL11

DDR1

_DQ[9]/DDR0_DQ[25]

BL8

_DQ[10]/DDR0_DQ[26]

DDR1

BJ8

DDR1

_DQ[11]/DDR0_DQ[27]

BJ11

_DQ[12]/DDR0_DQ[28]

DDR1

BJ10

_DQ[13]/DDR0_DQ[29]

DDR1

BL7

_DQ[14]/DDR0_DQ[30]

DDR1

BJ7

_DQ[15]/DDR0_DQ[31]

DDR1

BG11

_DQ[16]/DDR0_DQ[48]

DDR1

BG10

_DQ[17]/DDR0_DQ[49]

DDR1

BG8

DDR1

_DQ[18]/DDR0_DQ[50]

BF8

_DQ[19]/DDR0_DQ[51]

DDR1

BF11

DDR1

_DQ[20]/DDR0_DQ[52]

BF10

_DQ[21]/DDR0_DQ[53]

DDR1

BG7

DDR1

_DQ[22]/DDR0_DQ[54]

BF7

DDR1

_DQ[23]/DDR0_DQ[55]

BB11

DDR1

_DQ[24]/DDR0_DQ[56]

BC11

DDR1

_DQ[25]/DDR0_DQ[57]

BB8

DDR1

_DQ[26]/DDR0_DQ[58]

BC8

DDR1

_DQ[27]/DDR0_DQ[59]

BC10

_DQ[28]/DDR0_DQ[60]

DDR1

BB10

DDR1

_DQ[29]/DDR0_DQ[61]

BC7

_DQ[30]/DDR0_DQ[62]

DDR1

BB7

DDR1

_DQ[31]/DDR0_DQ[63]

AA11

_DQ[32]/DDR1_DQ[16]

DDR1

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

_DQ[34]/DDR1_DQ[18]

DDR1

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

_DQ[36]/DDR1_DQ[20]

DDR1

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1

_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1

_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1

_DQ[42]/DDR1_DQ[26]

V11

_DQ[43]/DDR1_DQ[27]

DDR1

W11

DDR1

_DQ[44]/DDR1_DQ[28]

W10

_DQ[45]/DDR1_DQ[29]

DDR1

V7

DDR1

_DQ[46]/DDR1_DQ[30]

V8

_DQ[47]/DDR1_DQ[31]

DDR1

R11

_DQ[48]

DDR1

P11

_DQ[49]

DDR1

P7

_DQ[50]

DDR1

R8

_DQ[51]

DDR1

R10

_DQ[52]

DDR1

P10

DDR1

_DQ[53]

R7

_DQ[54]

DDR1

P8

DDR1

_DQ[55]

L11

_DQ[56]

DDR1

M11

DDR1

_DQ[57]

L7

DDR1

_DQ[58]

M8

DDR1

_DQ[59]

L10

DDR1

_DQ[60]

M10

DDR1

_DQ[61]

M7

DDR1

_DQ[62]

L8

_DQ[63]

DDR1

AW11

_ECC[0]

DDR1

AY11

DDR1

_ECC[1]

AY8

_ECC[2]

DDR1

AW8

DDR1_ECC[3]

AY10

_ECC[4]

DDR1

AW10

DDR1_ECC[5]

AY7

_ECC[6]

DDR1

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL_H_BGA_BGA

DDR

04

_VREF 17

SM

TP

74

DDR_VREF_DQ1_M3 18

SM

A A

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

Si

Cu

Cu

Cu

stom

stom

stom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

B 2/5 (DDR3 I/F)

B 2/5 (DDR3 I/F)

B 2/5 (DDR3 I/F)

SN

SN

SN

1

1A

1A

1A

of

of

of

449Tuesday, August 25, 2015

449Tuesday, August 25, 2015

449Tuesday, August 25, 2015

5

4

3

2

1

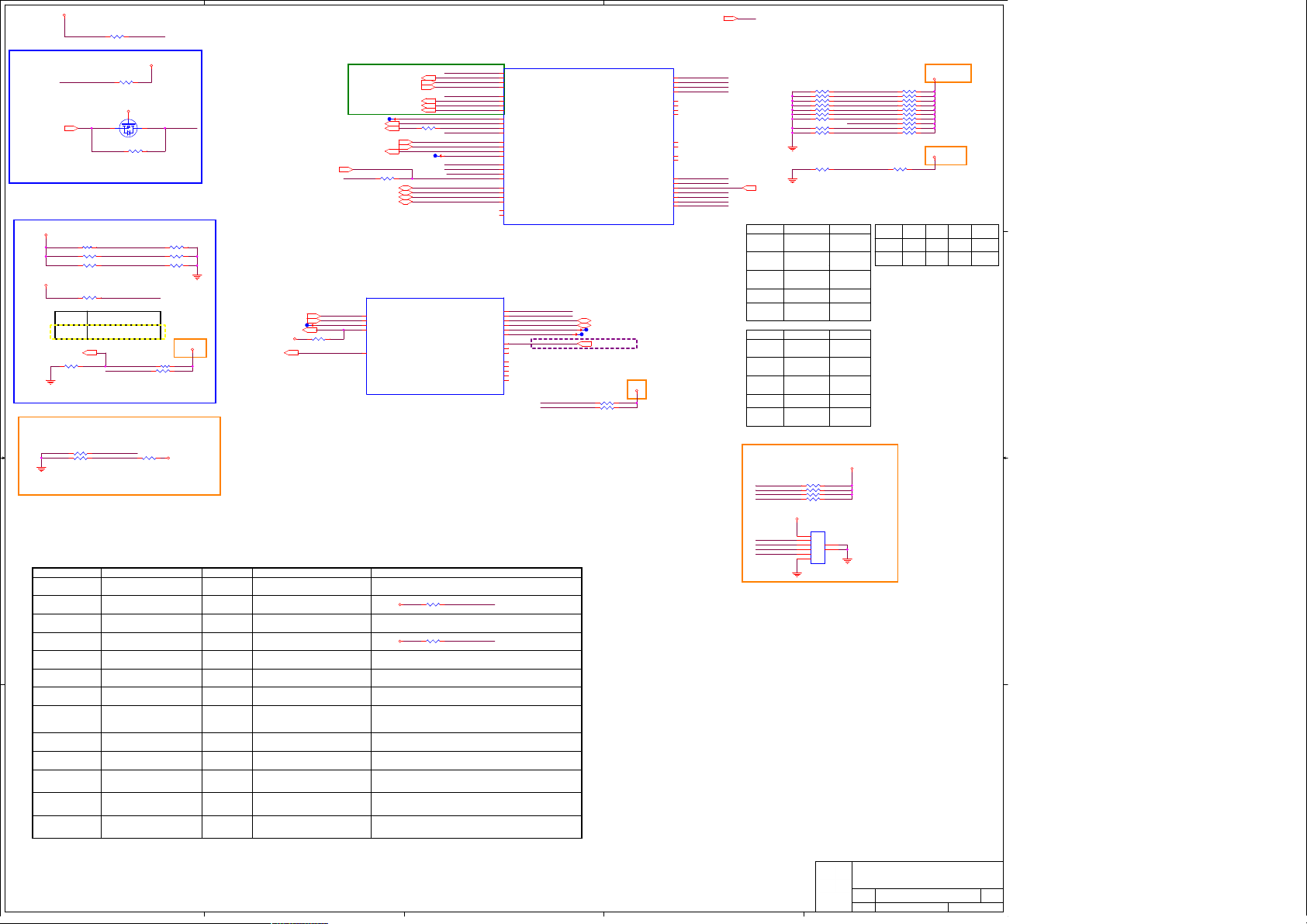

SKYLAKE Processor (POWER)

.5V 14,30,32,34,45

+1

low SKL H EDS page 133 to 45W(GT4+OPC): +VCCGT=104A/12A (GTx)

Fol

Follow SKL H EDS page 133 to 45W(GT2): +VCCGT=55A

Follow SKL H DG page 574 to place Cap

D D

+

C C

B B

22uF x 14, 10uF x 35, 1uF x 68

C3

C2

00

197

PC

330u/2V_7343

22U/6.3V_6

C7

52

22U/6.3V_6

C7

62

22U/6.3V_6

94

C1

10U/6.3V_6

26

C3

10U/6.3V_6

27

C3

10U/6.3V_6

C3

61

1U/6.3V_4

C3

83

1U/6.3V_4

C2

02

1U/6.3V_4

22U/6.3V_6

C7

22U/6.3V_6

C7

22U/6.3V_6

C7

10U/6.3V_6

C2

10U/6.3V_6

C3

10U/6.3V_6

C2

1U/6.3V_4

C2

1U/6.3V_4

C2

1U/6.3V_4

C3

C1

10

22U/6.3V_6

C7

53

22U/6.3V_6

C2

63

22U/6.3V_6

65

C2

10U/6.3V_6

09

C2

10U/6.3V_6

28

C7

10U/6.3V_6

C2

18

1U/6.3V_4

C1

89

1U/6.3V_4

C7

51

1U/6.3V_4

C3

29

91

22U/6.3V_6

C7

75

50

22U/6.3V_6

C3

24

55

22U/6.3V_6

13

21

C2

10U/6.3V_6

42

07

C3

10U/6.3V_6

64

88

C1

10U/6.3V_6

C3

27

64

1U/6.3V_4

C3

94

93

1U/6.3V_4

C2

91

52

1U/6.3V_4

07

22U/6.3V_6

C7

51

22U/6.3V_6

C3

52

22U/6.3V_6

76

C7

10U/6.3V_6

39

C3

10U/6.3V_6

74

C7

10U/6.3V_6

C2

16

1U/6.3V_4

C3

63

1U/6.3V_4

C3

51

1U/6.3V_4

C1

95

22U/6.3V_6

C3

08

22U/6.3V_6

C3

53

22U/6.3V_6

73

C7

10U/6.3V_6

40

C3

10U/6.3V_6

60

C7

10U/6.3V_6

41

C7

47U/6.3VS_8

C3

17

1U/6.3VS_4

C3

81

1U/6.3VS_4

C7

82

1U/6.3VS_4

+V

CCGT7,42,44

47U/6.3VS_8

C7

49

22U/6.3V_6

C3

09

22U/6.3V_6

C3

54

22U/6.3V_6

25

C2

10U/6.3V_6

41

C3

10U/6.3V_6

72

C7

10U/6.3V_6

42

C7

C2

29

1U/6.3V_4

C7

83

1U/6.3V_4

C2

79

1U/6.3V_4

+V

CCGT

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

U41N

CGT

VC

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

CGT

VC

VCCGT

VCCGT

VC

CGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VCCGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

VCCGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

VCCGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

CGT

VC

VCCGT

VCCGT

VC

CGT

VC

CGT

VC

CGT

CGT

VC

VC

CGT

VCCGT

CGT

VC

CGT

VC

VC

CGT

VC

CGT

SKL_H_BGA_BGA

SKY

LAKE_HALO

BGA1440

14

OF 14

VCCGTX

VCCGTX

VC

CGTX

VC

CGTX

CGTX

VC

CGTX

VC

CGTX

VC

VCCGTX

VCCGTX

VC

CGTX

CGTX

VC

CGTX

VC

CGTX

VC

CGTX

VC

VCCGTX

VC

CGTX

VC

CGTX

VC

CGTX

VC

CGTX

CGTX

VC

VCCGTX

VCCGTX

VC

CGT_SENSE

VSSG

TX_SENSE

T_SENSE

VSSG

VCCGTX_SENSE

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH35

AH37

AH36

R5

*100/F_4

R5

*100/F_4

4+4e, Support eDRAM Only, GTX 12A

ed c aps.. .

Ne

CCGT

+V

50

VC

CGT_SENSE 42

86

TP

VCCGTSS_SENSE 42

85

TP

49

VPCU

+3

CCGT

+V

C785

C287

1U/6.3V_4

92

C2

1U/6.3V_4

28

C2

1U/6.3V_4

76

C2

1U/6.3V_4

99

C3

1U/6.3V_4

C7

94

1U/6.3V_4

C385

1U/6.3V_4

46

C3

1U/6.3V_4

66

C2

1U/6.3V_4

95

C3

1U/6.3V_4

03

C2

1U/6.3V_4

C3

60

1U/6.3V_4

1U/6.3V_4

32

C3

1U/6.3V_4

74

C2

1U/6.3V_4

93

C7

1U/6.3V_4

26

C2

1U/6.3V_4

C3

62

1U/6.3V_4

+1

.2VSUS 2,6,10,17,18,41

Thrm Protect

IO

R2

15

*16.5K/F_4

RM_MOINTOR

TH

R2

31

*3.3K/F_4

For

75 degree, 1.2 v limit, (HW)

41

R2

1 2

00K_4 NTC

*1

C325

1U/6.3VS_4

54

C2

1U/6.3VS_4

17

C2

1U/6.3VS_4

96

C3

1U/6.3VS_4

78

C2

1U/6.3VS_4

C3

97

1U/6.3VS_4

68

C4

*0.1U/16V_4

C275

1U/6.3V_4

84

C7

1U/6.3V_4

77

C2

1U/6.3V_4

50

C2

1U/6.3V_4

15

C2

1U/6.3V_4

C7

92

1U/6.3V_4

1 2

05

C4

53

*0.1U/16V_4

TH

RM_MOINTOR1 37

C288

1U/6.3VS_4

53

C2

1U/6.3VS_4

92

C1

1U/6.3VS_4

04

C2

1U/6.3VS_4

80

C3

1U/6.3VS_4

C3

82

1U/6.3VS_4

C290

1U/6.3V_4

91

C2

1U/6.3V_4

49

C2

1U/6.3V_4

84

C3

1U/6.3V_4

65

C3

1U/6.3V_4

C3

98

1U/6.3V_4

Local CPU Thermal Sensor

U4

0

B_RUN_CLK10, 16,17,18,35

VC

C Output Decoupli ng Recommendations

A A

5

4

3

SM

SM

B_RUN_DAT10,16,17, 18,35

CPU_THRMTRIP#

R5

55 10K/F_4

+3

V

+1

.0V

PM_THRMTRIP#2,11,17,18

R562*4.7K_4

1 3

*METR3904-G

8

VC

SC

LK

7

DX

SD

A

6

ERT#

DX

AL

4

GN

OV

ERT#

*TMP431ADGKR

2

8

Q3

U_THRMTRIP#

CP

2

C8

06 0.01U/50 V_4

1

C

2

CP

P

3

N

5

D

U_THERMDA

09

C8

2200P/50V_4

CP

U_THERMDC

AL000431014

V

+3

CP

U Thermal Sensor

9

Q3

2

*METR3904-G

1 3

TMP431ADGKR(98h)

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

SNB 3/5 (POWER)

SNB 3/5 (POWER)

SNB 3/5 (POWER)

Date: Sheet

Date: Sheet

Date: Sheet

1

549Monday, S eptember 07, 2015

549Monday, S eptember 07, 2015

549Monday, S eptember 07, 2015

1A

1A

1A

of

of

of

5

4

3

2

1

06

Fol

low SKL H EDS page 135 to 45W(GT2): VCCSA=11.1A (GTx)

D D

+VCCSA42,

44

C1

22U/6.3V_6

C7

10U/6.3V_6

C C

C2

87

10U/6.3V_6

C3

22u/6.3V_6

C7

90

22U/6.3V_6

05

C7

1U/6.3V_4

57

C3

22u/6.3V_6

C3

1U/6.3V_4

88

C7

86

10U/6.3V_6

66

50

73

C2

19

22U/6.3VS_6

C7

78

10U/6.3V_6

C2

08

1U/6.3V_4

18

C3

22U/6.3VS_6

C3

93

1U/6.3V_4

+VCCI

Follow SKL H EDS P136 to 45W: VCCIO

+VCCIO = 0.95V

B B

+VDDQC+VCCSTG+VCCPLL_O

86

73

C3

C2

10U/6.3V_6

+VCCI

O

A A

5

C3

56

*1U/6.3V_ 4

C4

1U/6.3V_4

C3

59

*22U/6.3V _6

01

1U/6.3V_4

C7

89

22U/6.3VS_6

C1

81

10U/6.3V_6

C2

96

1U/6.3V_4

O

31

C3

22U/6.3VS_6

C3

44

10U/6.3V_6

C

00

C4

+VCCSA

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

SKYLAKE_HALO

U41I

VC

CSA

11.1 A

CSA

VC

CSA

VC

VC

CSA

VC

CSA

CSA

VC

CSA

VC

VC

CSA

VCCSA

CSA

VC

VC

CSA

VC

CSA

CSA

VC

CSA

VC

VC

CSA

VC

CSA

CSA

VC

CSA

VC

VC

CSA

VC

CSA

CSA

VC

CSA

VC

CIO

VC

5.5 A

CIO

VC

VC

CIO

VCCIO

CIO

VC

VC

CIO

VC

CIO

CIO

VC

CIO

VC

VC

CIO

VC

CIO

CIO

VC

CIO

VC

VC

CIO

VC

CIO

CIO

VC

CIO

VC

VC

CIO

VC

CIO

CIO

VC

VC

CIO

SKL_H_BGA_BGA

C2

98

1U/6.3V_4

Close CPUUnder CPU

4

BG

A1440

O

1U/6.3V_4

0.26 A

9

C2

97

2.8 A

0.12 A

0.145 A

VC

VSSSA_

VC

VSSI

OF 14

+VCCPLL+VCCI

VD

VD

VD

VD

VD

VD

VD

VD

VDDQ

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

VD

DQC

VD

VCCPLL_OC

CPLL_OC

VC

CST

VC

VC

CSTG

CSTG

VC

VC

CPLL

VC

CPLL

CSA_SENSE

SENSE

CIO_SENSE

O_SENSE

Follow SKL H EDS page 135 45W: VDDQ=2.8A

+1.

2VSUS

+1.

AA6

DQ

AE12

DQ

AF5

DQ

AF6

DQ

AG5

DQ

AG9

DQ

AJ12

DQ

AL11

DQ

AP6

AP7

DQ

AR12

DQ

AR6

DQ

AT12

DQ

AW6

DQ

AY6

DQ

J5

DQ

J6

DQ

K12

DQ

K6

DQ

L12

DQ

L6

DQ

R6

DQ

T6

DQ

W6

DQ

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

2VSUS 2,10,17,18,41

47

59

40

PLL

C2

1U/6.3V_4

ohm near CPU

100

VSA_

SENSE 42

VSASS_

SENSE 42

R151*SHORT_6

56*SH ORT_6

R1

R1

15*SHORT_6

R1

18*0_ 6

23*SH ORT_6

R1

3

C4

22U/6.3VS_6

C4

10U/6.3V_6

C4

10U/6.3V_6

60

+1.

+1.

52

49

51

2VSUS

2VSUS

+VCCST

+1.0V

C4

22U/6.3VS_6

C4

10U/6.3V_6

C4

10U/6.3V_6

+VDDQ

+VCCPLL_O

+VCCST

+VCCPLL

51 *100/F_4

R5

R5

46 *100/F_4

VCCI

O_VCCSENSE

O_VSSSENSE

VSSI

C

+VDDQ

C

+VCCPLL_O

+VCCSTG

+VCCPLL +VCCST

C4

21

22U/6.3VS_6

C4

60

10U/6.3V_6

C4

50

10U/6.3V_6

C

+VCCST

C

G

+VCCSA

R1

44 *SHORT_4

42 *SHORT_4

R1

+VCCI

C4

44

22U/6.3VS_6

C4

22

10U/6.3V_6

C4

34

10U/6.3V_6

O

45

R1

100_4

43

R1

100_4

PLL

PLL

+1.

+VCCST

+

C5

02

*330U/2V _7343

C4

32

10U/6.3V_6

C4

16

10U/6.3V_6

0V 2,5,10,16,40,45

PLL 2,10,40,42

EDRAM Only, PLACE CAPS IN ACK SIDE

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

91

TP

TP

24

29

TP

28

TP

TP

30

TP

27

OPC_COMP

76*49.9/F_4

CPU_

R5

CPU_

R1

R1

2

OPCE_COMP

33*49.9/F_4

CPU_

OPCE_COMP2

32*49.9/F_4

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Si

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

SNB 4/5 (POWER & GND)

SNB 4/5 (POWER & GND)

SNB 4/5 (POWER & GND)

Date: Sheet

Date: Sheet

Date: Sheet

SKYLAKE_HALO

U41J

BG

VC

COPC

3.8 A

COPC

VC

COPC

VC

VC

COPC

VC

COPC

COPC

VC

COPC

VC

VC

COPC

VCCOPC

COPC

VC

VC

COPC

VC

COPC

COPC

VC

COPC

VC

RS

VD

VD

RS

VD

RS

RS

VD

RS

VD

VD

RS

VD

RS

RS

VD

RS

VD

VD

RS

VD

RS

RS

VD

RSVD

VC

COPC_SENSE

PC_SENSE

VSSO

RS

VD

RS

VD

VC

CEOPIO

2.8 A

VC

CEOPIO

CEOPIO

VC

RS

VD

RS

VD

VD

RS

VCCEOPIO_SENSE

PIO_SENSE

VSSEO

RS

VD

VD

RS

VC

C_OPC_1P8

C_OPC_1P8

VC

RS

VD

RS

VD

ZV

M#

MS

M#

ZV

M2#

MS

M2#

C_RCOMP

OP

CE_RCOMP

OP

OP

CE_RCOMP2

SKL_H_BGA_BGA

A1440

0.05 A

10

1

OF 14

1A

1A

1A

of

of

of

9Monday, September 07, 2015

9Monday, September 07, 2015

64

64

64

9Monday, September 07, 2015

5

4

3

2

1

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

+V

CCGT

07

n

et name

C_SENSE

SENSE

CCCORE

+V

CCCORE 42,43

+V

Follow SKL H DG page 573 to place Cap

V32

VCC

V33

C

VC

V34

C

VC

V35

C

VC

V36

C

VC

V37

C

VC

V38

VC

C

W13

VC

C

W14

VC

C

W29

VC

C

W30

VC

C

W31

VCC

W32

C

VC

W35

C

VC

W36

C

VC

W37

C

VC

W38

C

VC

Y29

VC

C

Y30

VC

C

Y31

VC

C

Y32

VC

C

Y33

VC

C

Y34

VCC

Y35

C

VC

Y36

VCC

L14

C

VC

P29

C

VC

P30

C

VC

P31

VC

C

P32

C

VC

P33

VC

C

P34

VC

C

P35

VC

C

P36

VCC

R13

VC

C

R31

VCC

R32

C

VC

R33

C

VC

R34

C

VC

R35

C

VC

R36

C

VC

R37

VC

C

R38

VC

C

T29

VC

C

T30

VC

C

T31

VC

C

T32

VCC

T35

C

VC

T36

C

VC

T37

C

VC

T38

C

VC

U29

C

VC

U30

VC

C

U31

VC

C

U32

VC

C

U33

VC

C

U34

VC

C

U35

VCC

U36

C

VC

V13

VCC

V14

C

VC

V31

C

VC

P14

C

VC

AG37

AG38

22uF x 12, 10uF x 28, 1uF x 63

C3

C3

0.1U/10V_4

1 2

C2

0.1U/10V_4

1 2

C180

0.1U/10V_4

1 2

C2

0.1U/10V_4

1 2

C2

0.1U/10V_4

1 2

69

82

44

45

88

0.1U/10V_4

1 2

81

C2

0.1U/10V_4

1 2

C739

0.1U/10V_4

1 2

76

C3

0.1U/10V_4

1 2

91

C3

0.1U/10V_4

1 2

R5

48 *100_4

R5

47 *100_4

C3

87

0.1U/10V_4

1 2

71

C3

0.1U/10V_4

1 2

C283

0.1U/10V_4

1 2

79

C3

0.1U/10V_4

1 2

48

C2

0.1U/10V_4

1 2

CCCORE

+V

ORE_SENSE 42

VC

ORESS_SENSE 42

VC

C2

C2

0.1U/10V_4

1 2

C2

0.1U/10V_4

1 2

C370

0.1U/10V_4

1 2

C7

0.1U/10V_4

1 2

C3

0.1U/10V_4

1 2

47

70

0.1U/10V_4

1 2

1 2

84

82

C1

0.1U/10V_4

1 2

1 2

C745

0.1U/10V_4

1 2

1 2

40

69

C2

0.1U/10V_4

1 2

1 2

92

90

C3

0.1U/10V_4

1 2

1 2

Se

nse resistor should be placed within 2

inches (50.8 mm) o f the processor soc ket

Trace Impendence 50 ohm

C3

78

0.1U/10V_4

67

C2

0.1U/10V_4

C375

0.1U/10V_4

95

C7

0.1U/10V_4

06

C2

0.1U/10V_4

1 2

1 2

1 2

1 2

1 2

C2

71

0.1U/10V_4

77

C3

0.1U/10V_4

C286

0.1U/10V_4

75

C1

0.1U/16V_4

67

C3

0.1U/10V_4

C3

0.1U/10V_4

1 2

C3

0.1U/10V_4

1 2

C214

0.1U/10V_4

1 2

C2

0.1U/10V_4

1 2

C3

0.1U/10V_4

1 2

C3

89

74

0.1U/10V_4

1 2

72

66

C2

0.1U/10V_4

1 2

C246

0.1U/10V_4

1 2

68

87

C1

0.1U/10V_4

1 2

68

85

C2

0.1U/10V_4

1 2

CCCORE

+V

U41G

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_HALO

BG

VCC

C

VC

C

VC

C

VC

C

VC

C

VC

VC

C

VC

C

VC

C

VC

C

VC

C

VCC

C

VC

C

VC

C

VC

C

VC

C

VC

VC

C

VC

C

VC

C

VC

C

VC

C

VCC

C

VC

VCC

C

VC

C

VC

C

VC

VC

C

C

VC

VC

C

VC

C

VC

C

VCC

VC

C

VCC

C

VC

C

VC

C

VC

C

VC

C

VC

VC

C

VC

C

VC

C

VC

C

VC

C

VCC

C

VC

C

VC

C

VC

C

VC

C

VC

VC

C

VC

C

VC

C

VC

C

VC

C

VCC

C

VC

VCC

C

VC

C

VC

C

VC

SKL_H_BGA_BGA

A1440

VC

VSS_

7 OF 14

D D

C757

C211

22U/6.3V_6

22U/6.3V_6

C C

B B

C1

85

22U/6.3V_6

48

C3

10U/6.3V_6

83

C1

1U/6.3V_4

43

C3

1U/6.3V_4

C7

70

22U/6.3V_6

37

C3

10U/6.3V_6

89

C1

1U/6.3V_4

69

C7

1U/6.3V_4

Follow SKL H EDS page 131 to 45W(GT2): VCC_CORE=68A

C3

23

22U/6.3V_6

86

C1

22U/6.3V_6

C324

22U/6.3V_6

C3

47

22U/6.3V_6

58

C7

10U/6.3V_6

43

C7

1U/6.3V_4

01

C2

1U/6.3V_4

C7

48

22U/6.3V_6

97

C1

22U/6.3V_6

C759

22U/6.3V_6

C7

77

22U/6.3V_6

61

C7

10U/6.3V_6

99

C1

1U/6.3V_4

90

C7

1U/6.3V_4

C3

22

22U/6.3V_6

84

C1

22U/6.3V_6

C223

22U/6.3V_6

C7

47

22U/6.3V_6

12

C3

10U/6.3V_6

C7

67

10U/6.3V_6

79

C1

1U/6.3V_4

81

C7

1U/6.3V_4

C3

13

22U/6.3V_6

76

C1

22U/6.3V_6

C212

22U/6.3V_6

C3

36

22U/6.3V_6

10

C2

10U/6.3V_6

C3

49

10U/6.3V_6

80

C7

1U/6.3V_4

30

C3

1U/6.3V_4

C7

44

22U/6.3V_6

98

C1

22U/6.3V_6

C314

22U/6.3V_6

C2

22

22U/6.3V_6

71

C7

10U/6.3V_6

C3

38

10U/6.3V_6

15

C3

1U/6.3VS_4

21

C3

1U/6.3VS_4

C1

78

47U/6.3VS_8

C1

96

22U/6.3V_6

46

C7

22U/6.3V_6

C220

22U/6.3V_6

C7

56

22U/6.3V_6

68

C7

10U/6.3V_6

C7

54

10U/6.3V_6

74

C1

1U/6.3V_4

79

C7

1U/6.3V_4

C1

77

47U/6.3VS_8

CCGT

+V

CCGT 5,42,44

+V

U41H

SKYLAKE_HALO

A1440

BJ37

BJ38

BL36

BL37

BT37

BG

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

VCCGT

CGT

VC

CGT

VC

CGT

VC

VC

CGT

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VCCGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

SKL_H_BGA_BGA

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

VCCGT

CGT

VC

CGT

VC

CGT

VC

VC

CGT

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VCCGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VCCGT

CGT

VC

CGT

VC

CGT

VC

CGT

VC

CGT

VC

VC

CGT

VC

CGT

VC

CGT

8

OF 14

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

Ch

ange R2053 to NI_20141203

VC

ORE_SENSE

A A

5

4

VC

R5

ORESS_SENSE

52*49.9/F_4

PROJECT :ZRY

PROJECT :ZRY

PROJECT :ZRY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Si

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

SN

SN

SN

B 4/5 (POWER & GND)

B 4/5 (POWER & GND)

B 4/5 (POWER & GND)

Date: Sheet

Date: Sheet

3

2

Date: Sheet

1

1A

1A

1A

749Tuesday, Augu st 25, 2015

749Tuesday, Augu st 25, 2015

749Tuesday, Augu st 25, 2015

of

of

of

5

4

3

2

1

Haswell Processor (GND)

AW

AW

AW

BA38

BA3

BA12

BA1

BA10

AY3

AY3

AY1

AY1

AW

AW

AW

AW

AW

AV3

AV3

AU

AU

AU

AU

AU

AT30

AT

AR

AR37

AR

AR13

AP3

AP3

AP1

AP1

AP1

AN

AN

AN

AM

AM

AM

AM

AM

AM

AM

AM

AL

AL

AL

AL12

AL

BB4

BB3

BB2

BB1

BA9

BA8

BA7

BA6

AU

AU

AU

AU

AT6

AR

AR4

AR

AR

AR

AP9

AP8

AN

AN

AL9

AL

AL7

AL

U41M

VSS

VSS

VSS

VSS

VSS

7

VSS

VSS

1

VSS

VSS

VSS

VSS

VSS

VSS

B9

VSS

4

VSS

3

VSS

4

VSS

2

VSS

30

VSS

29

VSS

12

VSS

5

VSS

4

VSS

3

VSS

2

VSS

1

VSS

8

VSS

7

VSS

34

VSS

33

VSS

12

VSS

11

VSS

10

VSS

9

VSS

8

VSS

7

VSS

6

VSS

VSS

29

VSS

VSS

38

VSS

VSS

14

VSS

VSS

5

VSS

VSS

3

VSS

2

VSS

1

VSS

4

VSS

3

VSS

2

VSS

1

VSS

0

VSS

VSS

VSS

30

VSS

29

VSS

12

VSS

6

VSS

5

VSS

38

VSS

37

VSS

12

VSS

5

VSS

4

VSS

3

VSS

2

VSS

1

VSS

34

VSS

33

VSS

14

VSS

VSS

10

VSS

VSS

8

VSS

VSS

4

VSS

SKL_H_BGA_BGA

SKYL

AKE_HALO

BGA1440

13 OF 14

0

AK3

VSS

9

AK2

VSS

AK4

VSS

38

AJ

VSS

AJ37

VSS

6

AJ

VSS

AJ5

VSS

4

AJ

VSS

AJ3

VSS

2

AJ

VSS

AJ1

VSS

34

AH

VSS

33

AH

VSS

12

AH

VSS

6

AH

VSS

30

AG

VSS

29

AG

VSS

11

AG

VSS

10

AG

VSS

8

AG

VSS

7

AG

VSS

6

AG

VSS

AF

14

VSS

13

AF

VSS

AF

12

VSS

4

AF

VSS

AF

3

VSS

2

AF

VSS

AF

1

VSS

4

AE3

VSS

AE3

3

VSS

AE6

VSS

30

AD

VSS

29

AD

VSS

12

AD

VSS

11

AD

VSS

10

AD

VSS

AD9

VSS

8

AD

VSS

AD7

VSS

6

AD

VSS

AC38

VSS

37

AC

VSS

AC12

VSS

6

AC

VSS

AC5

VSS

4

AC

VSS

3

AC

VSS

2

AC

VSS

1

AC

VSS

4

AB3

VSS

3

AB3

VSS

AB6

VSS

0

AA3

VSS

9

AA2

VSS

2

AA1

VSS

0

A3

VSS

A2

8

VSS

6

A2

VSS

A2

4

VSS

2

A2

VSS

A2

0

VSS

8

A1

VSS

A1

6

VSS

4

A1

VSS

A1

2

VSS

0

A1

VSS

A9

VSS

A6

VSS

B37

FVSS

NCT

B3

NCTFVSS

A34

FVSS

NCT

A4

NCTFVSS

A3

FVSS

NCT

CF

G[3] (PHYSICAL_DEBUG_ENABLED (DFX PRIVACY))

Enable; SET DFX ENABLED BIT IN DEBUG

0

1 , Disable;

3

H_2_CPU_TRIG15

PC

CF