ZILOG Z86E74, Z86E73, Z86L74, Z86L73 Datasheet

FEATURES

PRELIMINARY

P

RELIMINARY

C

USTOMER PROCUREMENT SPECIFICATION

Z86E73/E74 32K OTP

Z86L73/L74 32K ROM

INFRARED REMOTE CONTROLLERS

Z86E73/E74/L73/L74

CP95LVO0801

ROM RAM* One-Time Speed

Part (Kbyte) (Kbyte) Programmable (MHz)

Z86E73 32 1004 Yes 8

Z86L73 32 492 No 8

Z86E74 32 1004 Yes 8

Z86L74 32 1004 No 8

* General-Purpose

■ 40-Pin DIP, 44-Pin PLCC/QFP Packages (E73/L73)

64-Pin DIP, 68-Pin PLCC Packages (E74/L74)

■ 2.0V to 3.9V Operating Range (L73/L74)

4.5V to 5.5V Operating Range (E73/E74)

■ Low-Power Consumption

(Typical: 40 mw for L73/L74)

(Typical: 60 mw for E73/E74)

■ 0°C to +70°C Temperature Range

■ Expanded Register Files (ERF)

■ 31 Input/Output Lines (E73/L73)

51 Input/Output Lines (E74/L74*)

*Note: With Auto Latch on Port 4, 5 and 6.

■ Five Prioritized Interrupts with Programmable Polarity

■ Two Comparators

■ 8-Bit Counter/Timer with Two Capture Registers and

16-Bit Counter/Timer with One Capture Register

■ Watch-Dog Timer (WDT)/Power-On Reset (POR)

■ On-Chip Oscillator that Accepts a Crystal, Ceramic

Resonator, LC, RC, or External Clock Drive

■ Low-Voltage Detection and Protection

■ 32-KHz Mask Option to Disable Internal Feedback

Resistor (L73/L74)

GENERAL DESCRIPTION

The Z86E73/L73/E74/L74 are ROM-based members of

Zilog's Z8® single-chip microcontroller family of infrared

(IR) consumer controller processors featuring fast and

flexible code execution. The Z86E73/E74 devices offer a

one-time programmable (OTP) option.

For applications demanding powerful I/O capabilities, the

Z86E73/L73's dedicated input and output lines are grouped

into four ports, and into seven ports for the Z86E74/L74.

They are configurable under software control to provide

timing, status signals, or parallel I/O.

Four address spaces, the Program Memory, Register File,

Data Memory, and Expanded Register File (ERF) support

a wide range of memory configurations. Through the ERF

the designer has access to three additional control registers

that provide extra peripheral devices, I/O ports, and register

addresses.

CP95LVO0801

Two on-chip counter/timers, with a large number of

selectable modes, offload the system of administering

real-time tasks such as counting/timing and I/O

datacommunications.

Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.,

B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

Power V

Ground GND V

CC

V

DD

SS

1

PRELIMINARY

GENERAL DESCRIPTION (Continued)

Z86E73/E74/L73/L74

CP95LVO0801

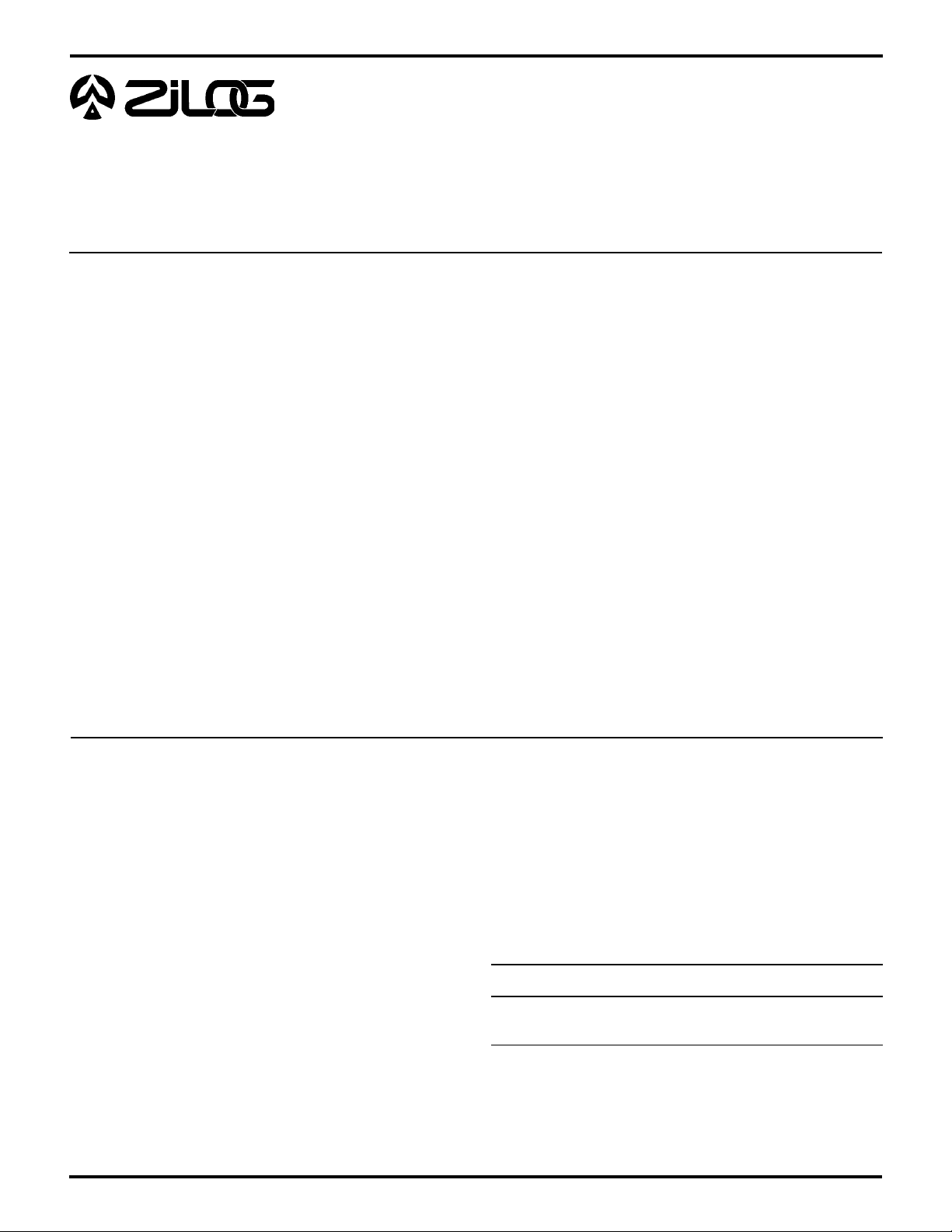

I/O Bit

Programmable

P00

P01

P02

P03

P04

P05

P06

P07

P10

P11

P12

P13

P14

P15

P16

P17

P20

P21

P22

P23

P24

P25

P26

P27

Register File

4

Port 0

4

8

Port 1

Port 2

Register Bus

ROM

16K/32K x 8

512 or 1K x 8-bit

Address Bus

Internal Data Bus

Extended

Register

File

Counter/Timer 8

8-Bit

Internal

Extended

Register Bus

Counter/Timer 16

Port 3

Z8 Core

Machine

Timing

&

Instruction

Control

Power

16-Bit

P31

P32

P33

P34

P35

P36

P37

XTAL

/AS

/DS

R/W

/RESET

VDD

VSS

Port 4

8

Z86E74/L74

Port 5

8

Port 6

4

version only

Functional Block Diagram

2

PIN DESCRIPTION

PRELIMINARY

Z86E73/E74/L73/L74

CP95LVO0801

R//W

P25

P26

P27

P04

P05

P06

P14

P15

P07

VDD

P16

P17

XTAL2

XTAL1

P31

P32

P33

P34

/AS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

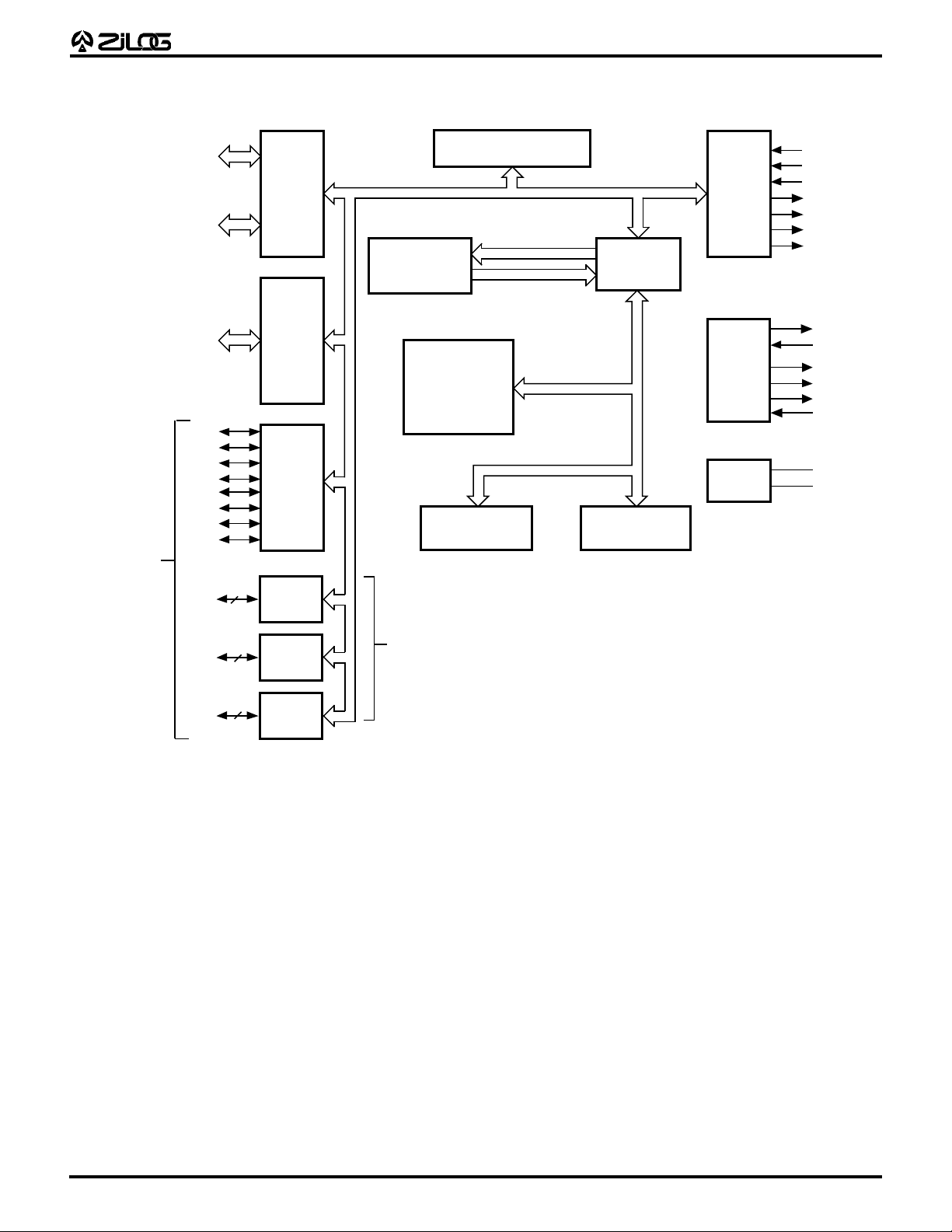

Z86E73/L73

DIP

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

Z86E73 (Standard Mode)

Z86L73 40-Pin DIP

Pin Assignments

/DS

P24

P23

P22

P21

P20

P03

P13

P12

VSS

P02

P11

P10

P01

P00

Pref1

P36

P37

P35

/RESET

P56

R/W

P25

P26

P27

P04

P05

P06

P14

P15

P07

VDD

VDD

P40

P41

P42

P43

P44

P45

P16

P17

XTAL2

XTAL1

P31

P32

P33

P34

P60

P61

/AS

P63

P55

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Z86E74/L74

DIP

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

R//RL

P54

P53

/DS

P51

P50

P24

P23

P22

P21

P20

P03

P13

P12

VSS

VSS

P52

P57

P02

P46

P47

P11

P10

P01

P00

PREF1

P36

P37

P35

/RESET

VSS

P62

Z86E74 (Standard Mode)

Z86L74 64-Pin DIP

Pin Assignments

3

PIN DESCRIPTION

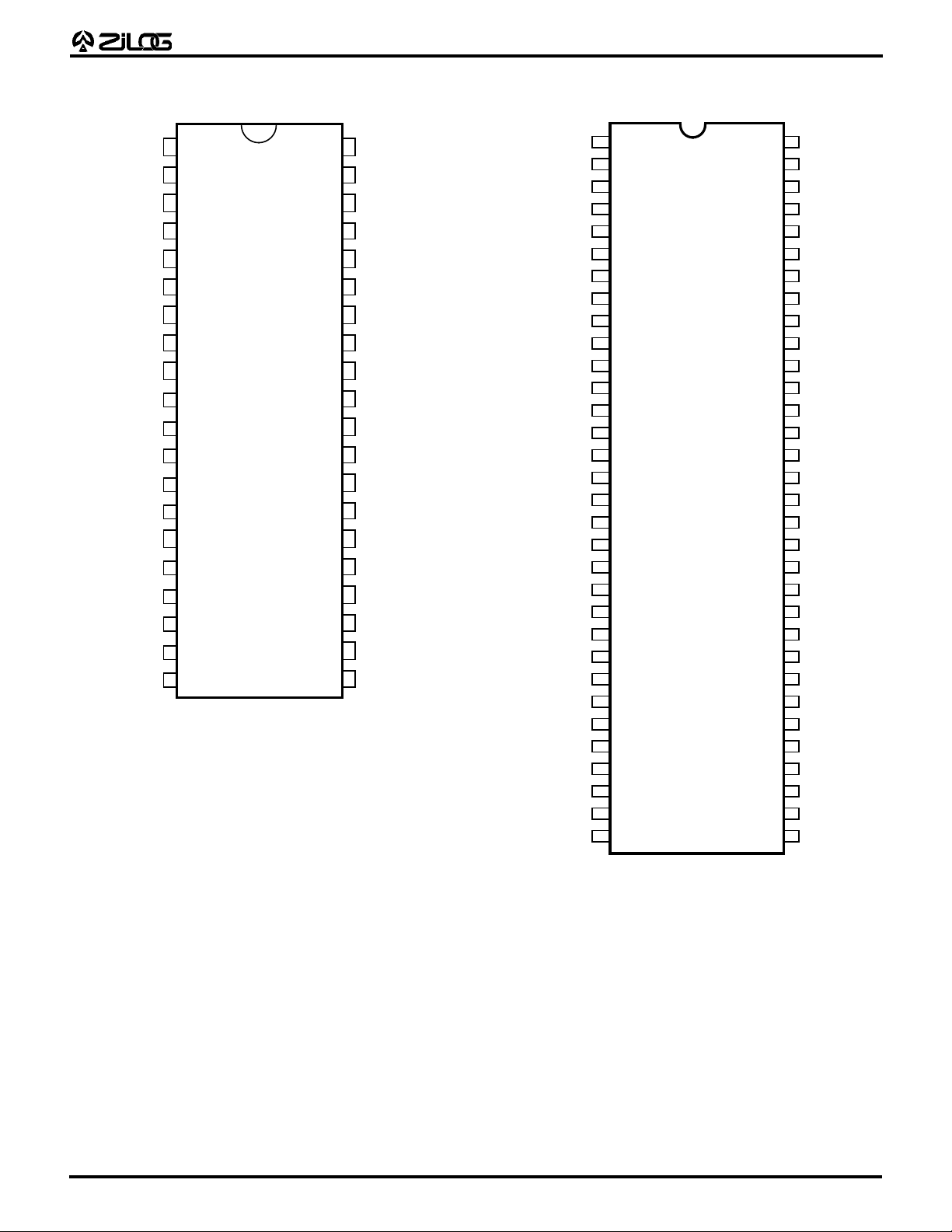

P21

P22

P23

P24

/DS

R//RL

R//W

P25

P26

P27

P04

PRELIMINARY

P20

P03

P13

P12

VSS

VSS

P02

P11

P10

P01

6543214443424140

7

8

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

P05

P06

P14

Z86E73/L73

PLCC

P15

P07

VDD

VDD

P16

P17

XTAL2

P00

39

38

37

36

35

34

33

32

31

30

29

XTAL1

Z86E73/E74/L73/L74

CP95LVO0801

Pref1

P36

P37

P35

/RESET

VSS

/AS

P34

P33

P32

P31

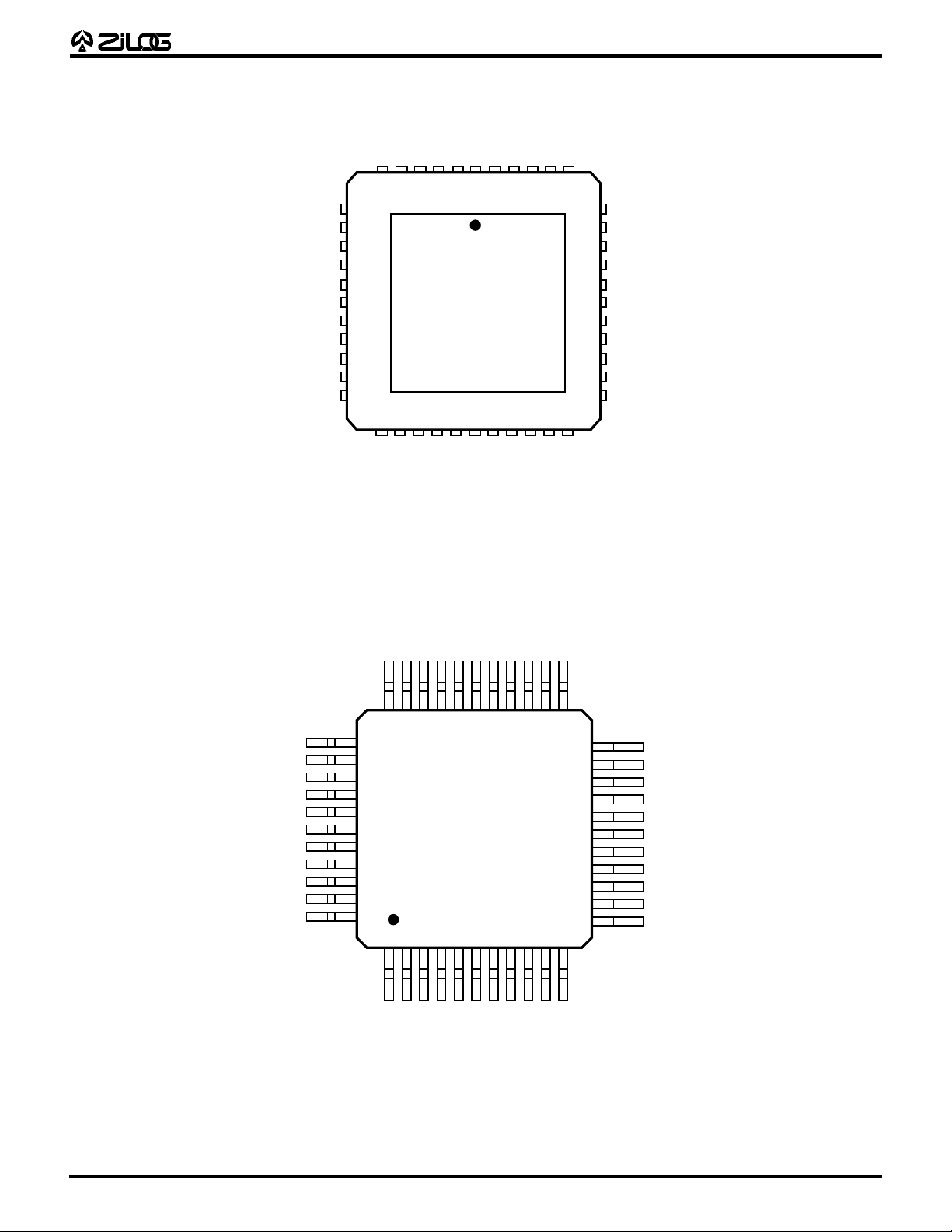

P21

P22

P23

P24

/DS

R//RL

R//W

P25

P26

P27

P04

Z86E73 (Standard Mode)

Z86L73 44-Pin PLCC

Pin Assignments

P20

P03

P13

P12

VSS

VSS

P02

P11

P10

33 32 31 30 29 2827 26 25 24 23

34

35

36

37

38

39

40

41

42

43

44

1234567891011

Z86E73/L73

QFP

P01

P00

22

21

20

19

18

17

16

15

14

13

12

Pref1

P36

P37

P35

/RESET

VSS

/AS

P34

P33

P32

P31

P05

P06

P14

P15

P07

VDD

VDD

P16

P17

XTAL2

XTAL1

Z86E73 (Standard Mode)

Z86L73 44-Pin QFP

Pin Assignments

4

PIN DESCRIPTION (Continued)

10

P21

11

P22

12

P23

13

P24

14

P50

15

P51

16

/DS

17

P53

18

P54

P56

R//W

N/C

P25

P26

P27

P04

19

20

21

22

23

24

25

26

R//RL

PRELIMINARY

P02

P57

P13

P20

P03

P12

VSS

VSS

789 6543216867666564636261

N/C

N/C

P52

P46

P47

Z86E74/L74

PLCC

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

P06

P14

P15

P05

P07

VDD

VDD

P40

P41

P42

P43

P44

P45

P01

P10

P11

P16

P17

XTAL2

P00

XTAL1

Z86E73/E74/L73/L74

CP95LVO0801

60

PREF1

59

P36

58

P37

57

P35

56

/RESET

55

VSS

54

P62

53

P55

52

N/C

51

P63

50

/AS

49

P61

48

P60

47

P34

46

P33

45

P32

44

P31

Z86E74 (Standard Mode)

Z86L74 68-Pin PLCC Pin Assignments

5

ABSOLUTE MAXIMUM RATINGS

PRELIMINARY

Z86E73/E74/L73/L74

CP95LVO0801

Symbol Description Min Max Units

V

CC

T

STG

T

A

Notes:

* Voltage on all pins with respect to GND.

† See Ordering Information.

Supply Voltage (*) –0.3 +7.0 V

Storage Temp. –65° +150° C

Oper. Ambient Temp. † C

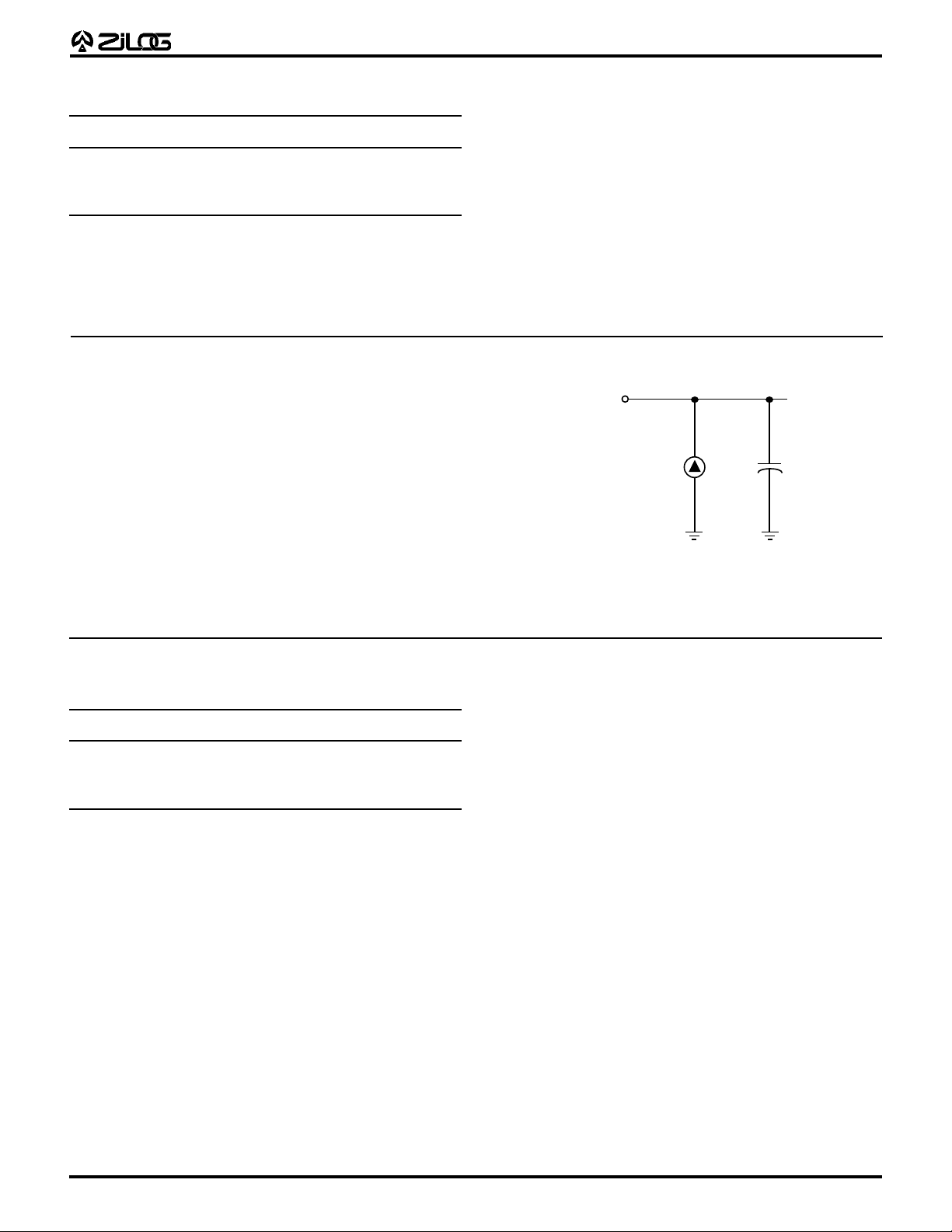

STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test

conditions as noted. All voltages are referenced to GND.

Positive current flows into the referenced pin (Test Load).

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at

any condition above those indicated in the operational

sections of these specifications is not implied. Exposure to

absolute maximum rating conditions for an extended

period may affect device reliability.

From Output

Under Test

I

150 pF

CAPACITANCE

TA = 25°C, VCC = GND = 0V, f = 1.0 MHz, unmeasured pins returned to GND.

Parameter Max

Input capacitance 12 pF

Output capacitance 12 pF

I/O capacitance 12 pF

Test Load Diagram

6

Loading...

Loading...