GENERAL DESCRIPTION

PRELIMINARY

P

RELIMINARY

C

USTOMER PRODUCT SPECIFICATION

Z86E47 OTP ROM

CMOS Z8

MICROCONTROLLER

®

8-BIT

Z86E47-ROM

CPS DC-4157-01

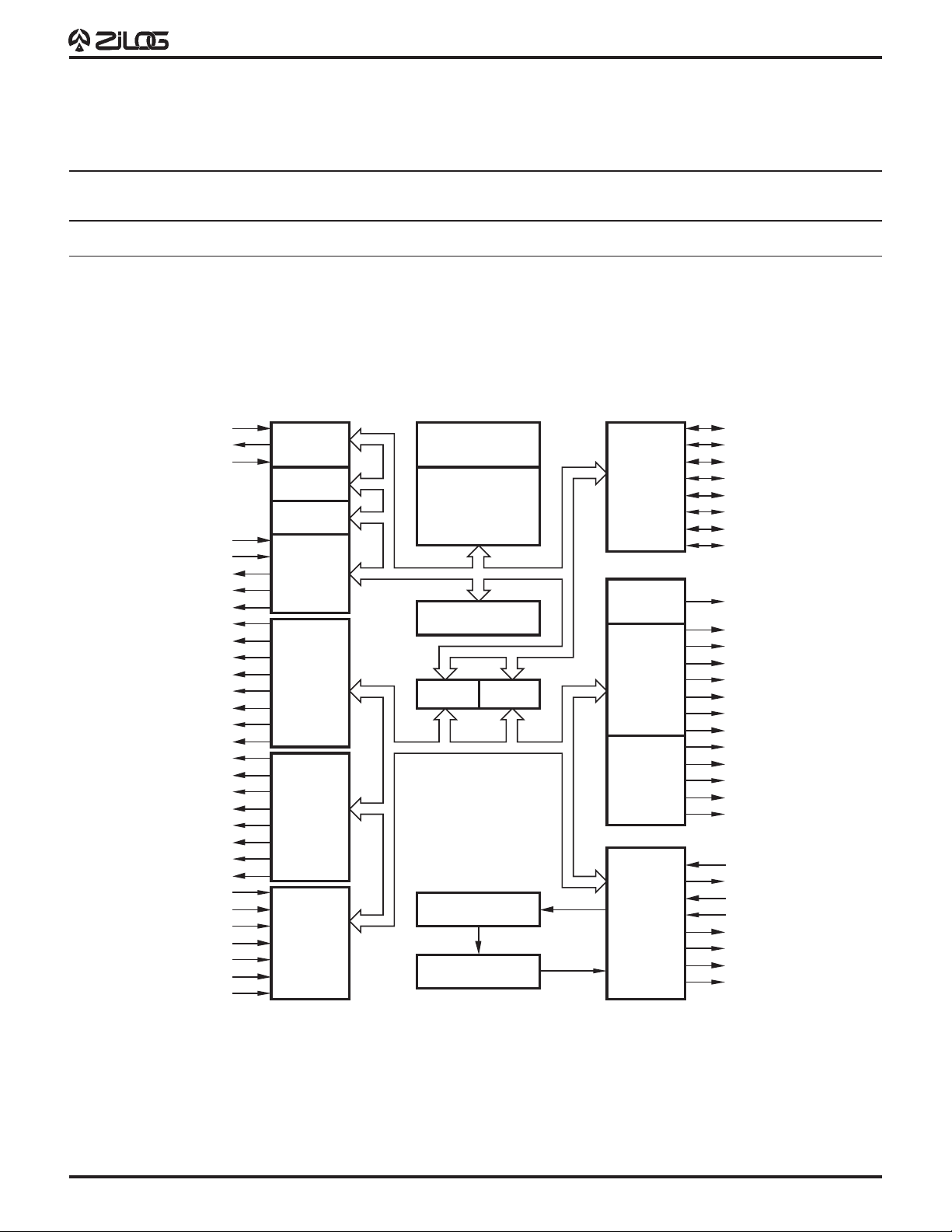

The Z86E47 Digital Television Controller (DTC) introduce

a new level of sophistication to single-chip architecture.

The Z86E47 is a member of the Z8 single-chip

microcontroller family with 16 Kbytes of OTP (One-TimeProgrammable) ROM and 236 bytes of RAM. The device

is housed in a 64-pin DIP package, and is CMOS compatible. The part features ROMs for program storage and

character generation. The Z86E47 microcontroller may be

used in prototyping, low volume applications or where

code development is required. Zilog’s DTC offers fast

execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy

hardware/software system expansion along with low cost

and low power consumption. The device provides an ideal

performance and reliability solution for consumer and

industrial television applications.

The Z86E47 architecture utilizes Zilog’s advanced

Superintegration™ design methodology. The device has

an 8-bit internal data path controlled by a Z8 microcontroller,

On-Screen Display (OSD) logic circuits/Pulse Width Modulators (PWM). On-chip peripherals include five register/

memory mapped I/O ports (Ports 2, 3, 4, 5, and 6), Interrupt

control logic (1 software, 2 external and 3 internal interrupts) and a standby mode recovery input port (Port 3, pin

P30).

The OSD control circuits support eight rows by 20 columns

for 128 kinds of characters. The character color is specified by row. One of the eight rows is assigned to show two

kinds of colors for bar type displays such as volume

control. The OSD is capable of displaying high resolution

(11x15 dot pattern) characters.

A 14-bit PWM port provides enough voltage resolution for

a voltage synthesizer tuning system. Seven 6-bit PWM

ports are used for controlling audio signal level. Five 8-bit

PWM ports are used to vary picture levels.

DTC applications demand powerful I/O capabilities. The

Z86E47 fulfills this with 35 I/O pins dedicated to input and

output. These lines are grouped into five ports, and are

configurable under software control to provide timing,

status signals, parallel I/O and an address/data bus for

interfacing to external memory.

There are three basic address spaces available to support

this wide range of configurations: Program Memory, Register File and Data Memory. The Data Memory address

space contains a number of control registers for the

PWMs, OSD, and I/O Ports 4, 5, and 6. Specifically, there

are 13 PWM and eight OSD control registers mapped into

the external memory address space. Three I/O registers

for Ports 4, 5, and 6 reside in data memory space as well.

The Register File is composed of 236 bytes of general

purpose register, two I/O Port registers and 15 control and

status registers.

To unburden the program from coping with the real-time

problems such as counting/timing and data communication, the DTC’s offer two on-chip counter/timers with a large

number of user selectable modes (see block diagram).

Note: All Signals with a preceding front slash, "/", are active

Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is

active Low, only).

DC-4157-01 (2-18-94)

1

PRELIMINARY

PRODUCT RECOMMENDATIONS

Zilog recommends the following programming equipment

for use with this one-time-programmable product.

Recommended

Device Zilog Support Tool Hardware

Z86E4700ZDP Z86E47 Programming Adapter A

Z86E47-ROM

CPS DC-4157-01

Some non-Zilog programmers may have different programming waveforms, voltages and timings and not all

programmers may meet the programming requirements of

Zilog's one-time-programmable products.

XTAL1

XTAL2

/RESET

P30

P31

P34

P35

P36

P40

P41

P42

P43

P44

P45

P46

P47

P50

P51

P52

P53

P54

P55

P56

P57

P60

P61

P62

P63

P64

P65

AFCIN

RESET

Oscillator

WDT

Counter

Timer

Counter

Timer

Port 3/

Interrupt

Port4

Port 5

Port 6

16K Byte

Program ROM

Port 0

Character RAM

Character ROM

If difficulty is encountered in programming a Zilog OTP

product, please contact your local Zilog sales office.

P27

P26

P25

Z8 CPU

Core

256 Byte

Register File

Port 1

A8:15 AD0:7

160 Byte

4 KByte

Port 2

PWM 1

14 -bit

PWM 2

to

PWM 8

6-bit

PWM 9

to

PWM 13

8-bit

On Screen

Display

P24

P23

P22

P21

P20

PWM 1

PWM 2

PWM 3

PWM 4

PWM 5

PWM 6

PWM 7

PWM 8

PWM 9

PWM 10

PWM 11

PWM 12

PWM 13

OSCIN

OSCOUT

HSYNC

VSYNC

VRED

VGREEN

VBLUE

VBLANK

Functional Block Diagram

2

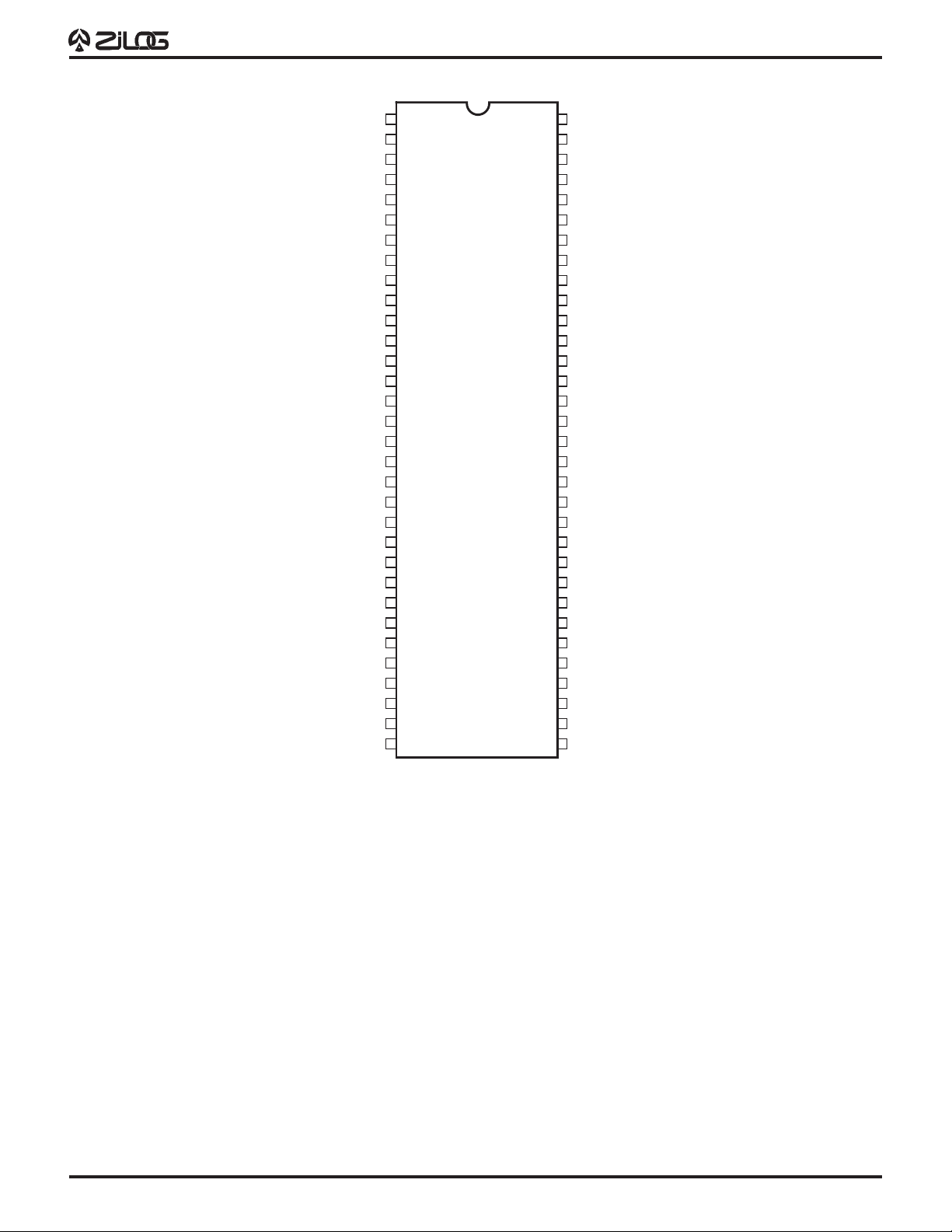

PIN CONFIGURATION

PRELIMINARY

Z86E47-ROM

CPS DC-4157-01

PWM5

PWM4

PWM3

PWM2

PWM1

P35

P36

P34

P31

P30

XTAL1

XTAL2

/RESET

P60

GND

P61

P62

VCC

P63

P64

P65

AFCIN

P50

P51

P52

P53

P54

P55

P56

P57

OSCIN

OSCOUT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Z86E47

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PWM6

PWM7

PWM8

PWM9

PWM10

PWM11

PWM12

PWM13

P27

P26

P25

P24

P23

GND

P22

P21

VCC

P20

P47

P46

P45

P44

P43

P42

P41

P40

VBLANK

VBLUE

VGREEN

VRED

VSYNC

HSYNC

Z86E47 OTP ROM Plastic DIP

3

Loading...

Loading...