Page 1

Z8018x

Family MPU

User Manual

UM005003-0703

ZiLOG WORLDWIDE HEADQUARTERS • 532 Race Street • SAN JOSE, CA 95126-3432

T

ELEPHONE: 408.558.8500 • FAX: 408.558.8300 • WWW.ZILOG.COM

Page 2

Z8018x

Family MPU User Manual

This publication is subject to replacement by a later edition. To determine whether a later edition

exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters

532 Race Street

San Jose, CA 95126-3432

Telephone: 408.558.8500

Fax: 408.558.8300

www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

Document Disclaimer

© 2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices,

applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG,

INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF

THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG

ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT

RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY

DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of

information, devices, or technology as critical components of life support systems is not authorized. No

licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property

rights.

UM005003-0703

Page 3

MANUAL OBJECTIVES

This user manual describes the features of the Z8018x MPUs.This manual

provides basic programming information for the Z80180/Z8S180/

Z8L180. These cores and base peripheral sets are used in a large family of

ZiLOG products. Below is a list of ZiLOG products that use this class of

processor, along with the associated processor family. This document is

also the core user manual for the following products:

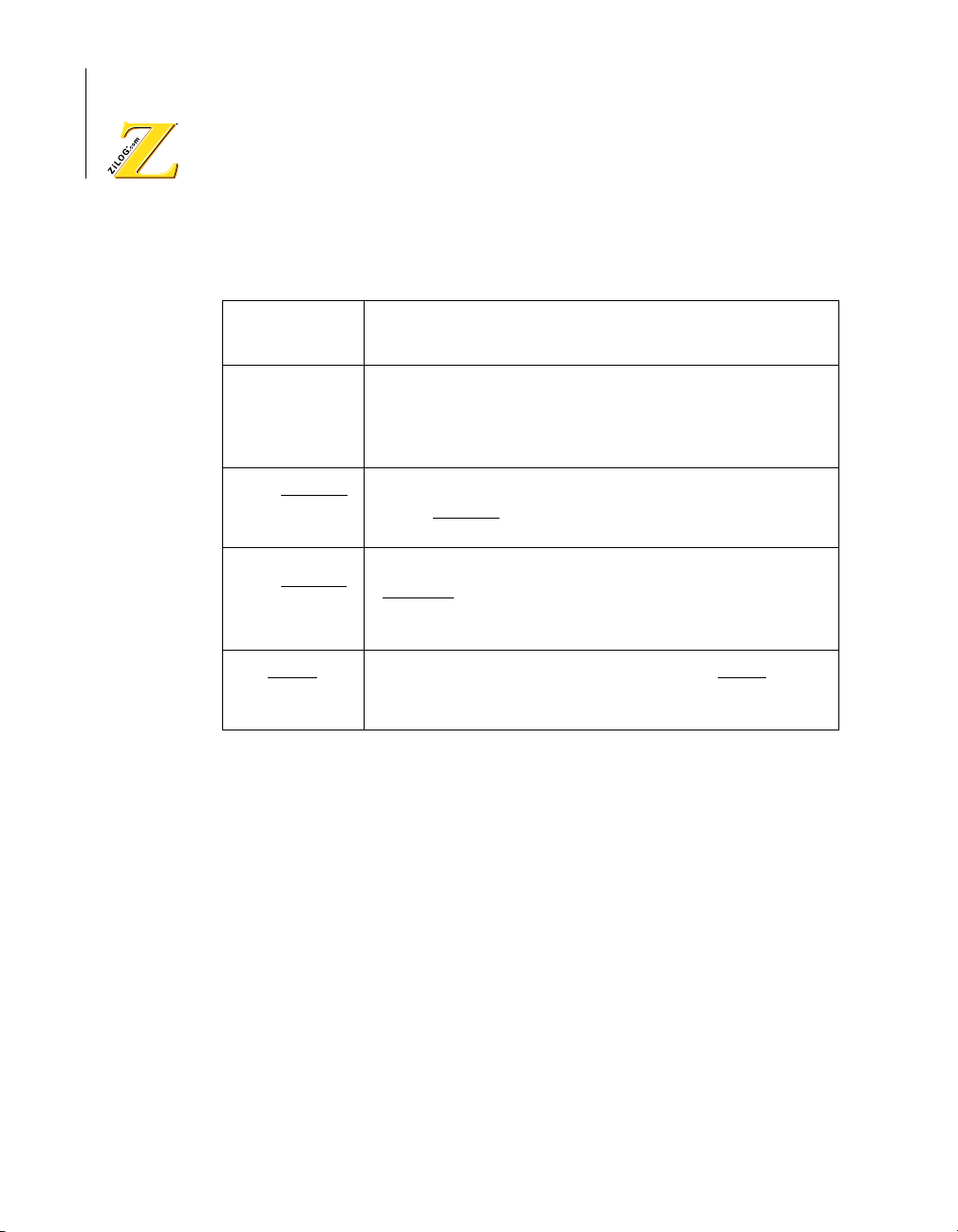

Part Family

Z80180 Z80180

Z8S180 Z8S180

Z8L180 Z8L180

Z8018x

Family MPU User Manual

iii

Z80181 Z80180

Z80182 Z80180, Z8S180*

Z80S183 Z8S180

Z80185/195 Z8S180

Z80189 Z8S180

* Part number-dependant

Intended Audience

This manual is written for those who program the Z8018x.

Manual Organization

The Z8018x User Manual is divided into five sections, seven appendices,

and an index.

UM005003-0703

Page 4

Z8018x

Family MPU User Manual

iv

Sections

Z8018X MPU Operation

Presents features, a general description, pins descriptions, block

diagrams, registers, and details of operating modes for the Z8018x MPUs.

Software Architecture

Provides instruction sets and CPU registers for the Z8018x MPUs.

DC Characteristics

Presents the DC parameters and absolute maximum ratings for the

Z8X180 MPUs.

AC Characteristics

Presents the AC parameters for the Z8018x MPUs.

Timing Diagrams

Contains timing diagrams and standard test conditions for the Z8018x

MPUs.

Appendices

The appendixes in this manual provide additional information applicable

to the Z8018x family of ZiLOG MPUs:

•

Instruction set

•

Instruction summary table

•

Op Code map

•

Bus Control signal conditions in each machine cycle and interrupt

conditions

•

Operating mode summary

•

Status signals

•

I/O registers and ordering information

UM005003-0703

Page 5

Z8018x

Family MPU User Manual

Table of Contents

Z80180, Z8S180, Z8L180 MPU Operation . . . . . . . . . . . . . . . . . . . .1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

CPU Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Wait State Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

HALT and Low Power Operation Modes

(Z80180-Class Processors Only) . . . . . . . . . . . . . . . . . . . . . . . .31

Low Power Modes

(Z8S180/Z8L180 only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Add-On Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

STANDBY Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

STANDBY Mode Exit wiht BUS REQUEST . . . . . . . . . . . . . . . . .38

STANDBY Mode EXit with External Interrupts . . . . . . . . . . . . . . .39

IDLE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

STANDBY-QUICK RECOVERY Mode . . . . . . . . . . . . . . . . . . . .41

Internal I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

MMU Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Interrupt Acknowledge Cycle Timings . . . . . . . . . . . . . . . . . . . . . .82

Interrupt Sources During RESET . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Dynamic RAM Refresh Control . . . . . . . . . . . . . . . . . . . . . . . . . . .86

DMA Controller (DMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Asynchronous Serial Communication Interface (ASCI) . . . . . . . .115

v

UM005003-0703

Page 6

Z8018x

Family MPU User Manual

vi

Baud Rate Generator

(Z8S180/Z8L180-Class Processors Only) . . . . . . . . . . . . . . . 143

Clocked Serial I/O Port (CSI/O) . . . . . . . . . . . . . . . . . . . . . . . . . . 146

CSI/O Registers Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Programmable Reload Timer (PRT) . . . . . . . . . . . . . . . . . . . . . . . 156

Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Software Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Absolute Maximum Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Z80180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Z8S180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Z8L180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

AC Characteristics—Z8S180 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Standard Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Restart Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

UM005003-0703

Page 7

Z8018x

Family MPU User Manual

Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .210

Data Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .211

Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

Program and Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

Special Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .235

Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

Op Code Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .247

Bus Control Signal Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

Bus and Control Signal Condition in each Machine Cycle . . . . . . . . .251

vii

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

Operating Modes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .281

Request Acceptances in Each Operating Mode . . . . . . . . . . . . . . . . . .281

Request Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .282

Operation Mode Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

Other Operation Mode Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . .285

Status Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287

Pin Outputs in Each Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . .287

Pin Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .288

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .293

Internal I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .293

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .303

UM005003-0703

Page 8

Z8018x

Family MPU User Manual

List of Figures

Z80180, Z8S180, Z8L180 MPU Operation . . . . . . . . . . . . . . . . . . . .1

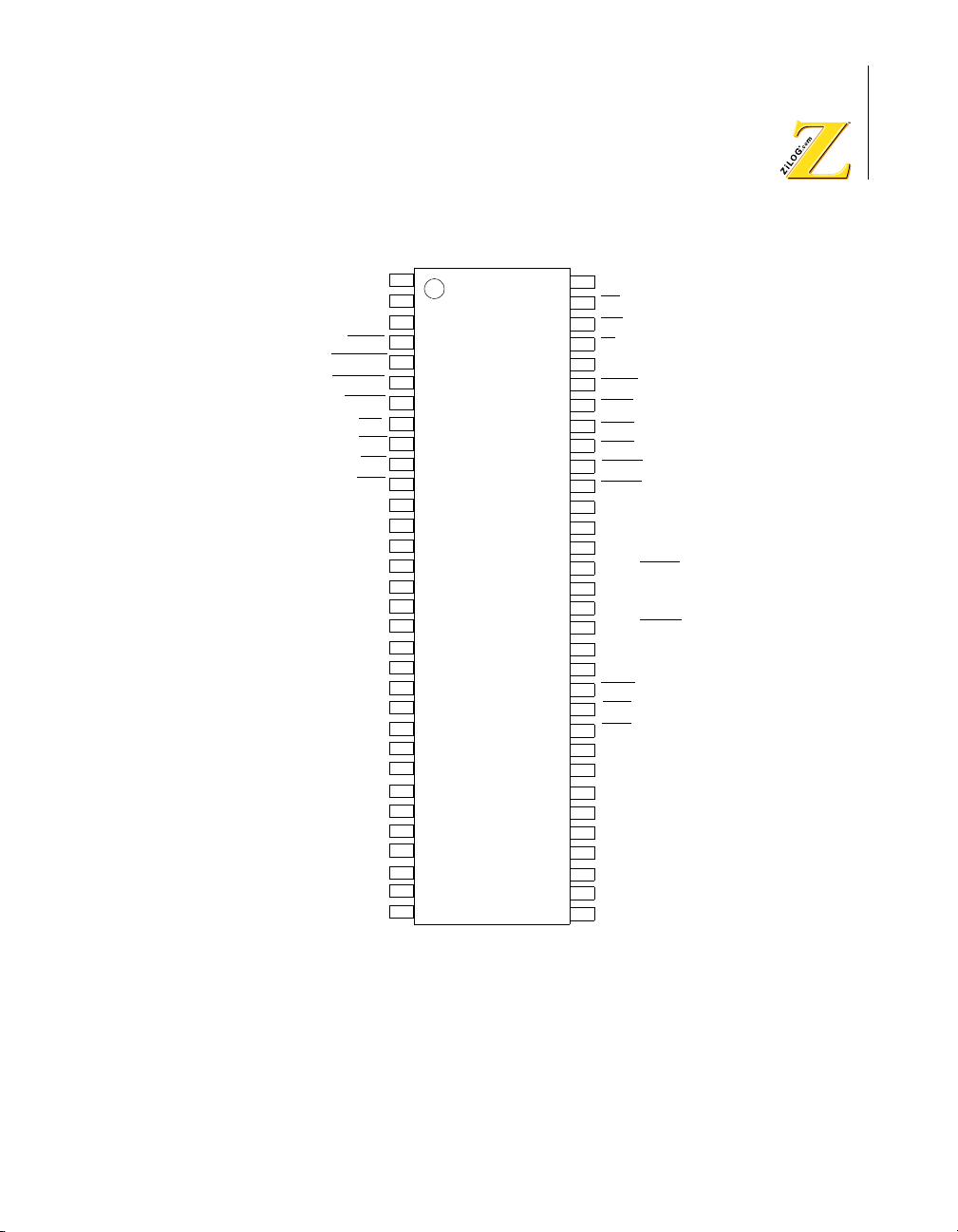

Figure 1. 64-Pin DIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

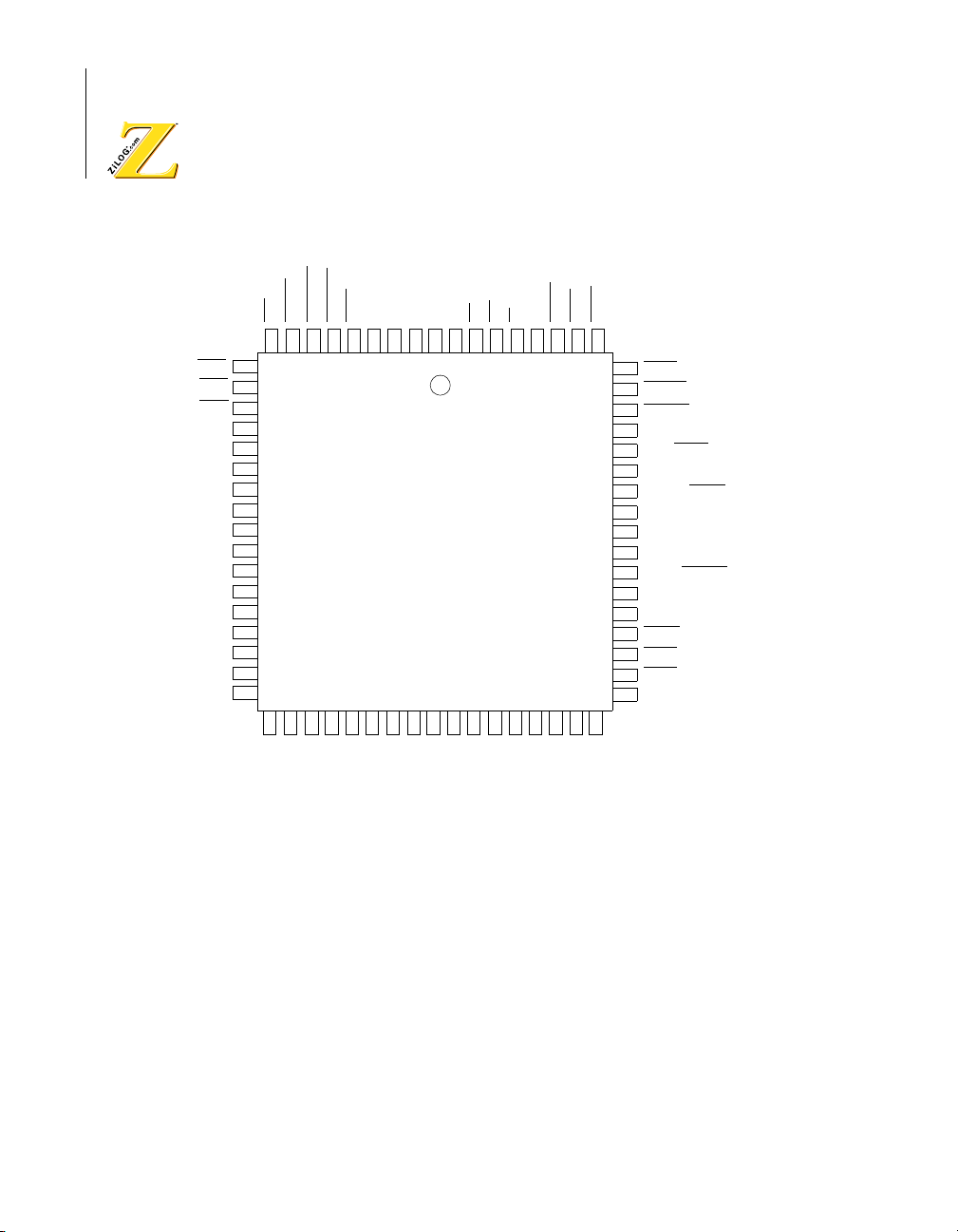

Figure 2. 68-Pin PLCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

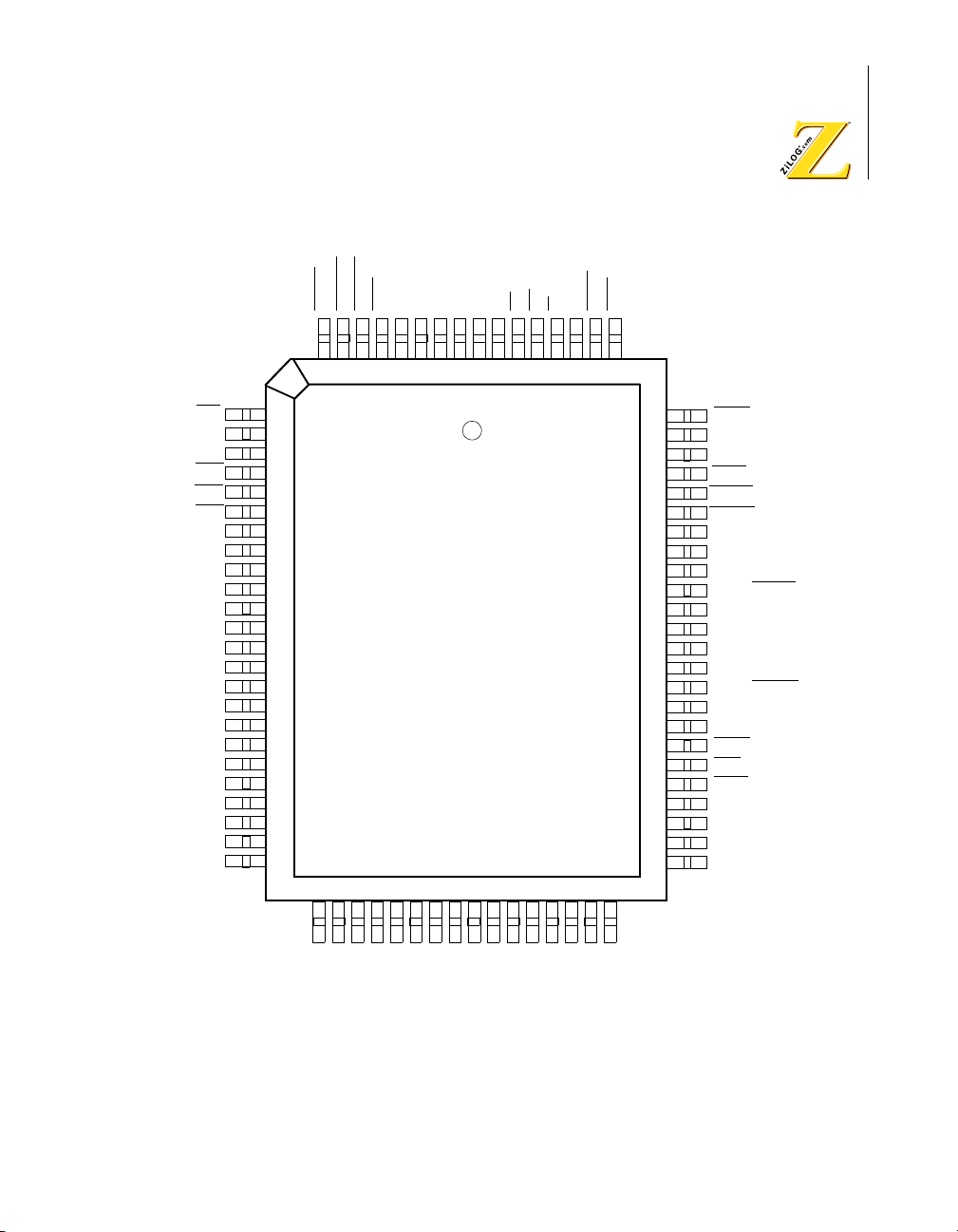

Figure 3. 80-Pin QFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

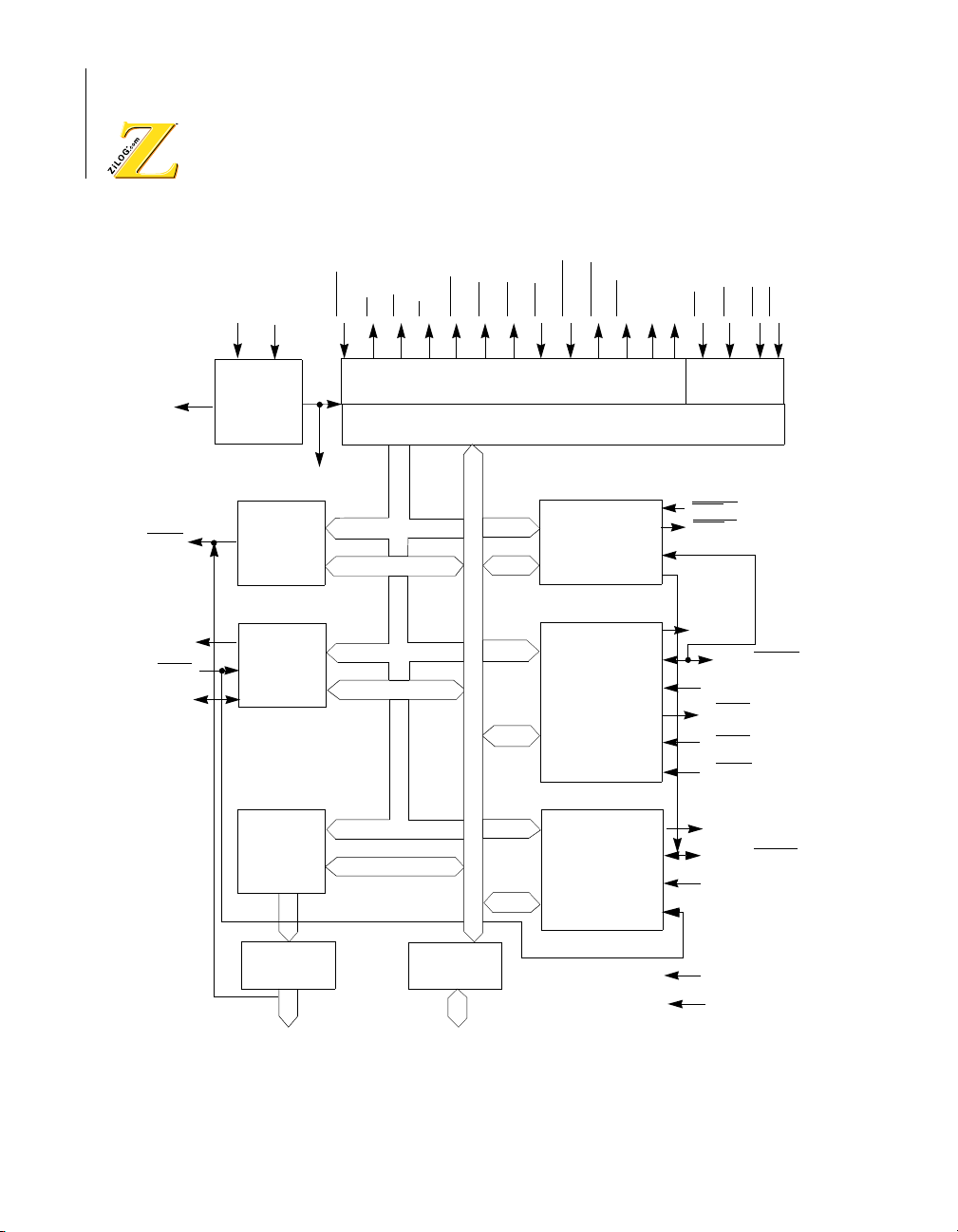

Figure 4. Z80180/Z8S180/Z8L180 Block Diagram . . . . . . . . . . . . . . .6

Figure 5. Operation Mode Control Register . . . . . . . . . . . . . . . . . . . .15

Figure 6. M1 Temporary Enable Timing . . . . . . . . . . . . . . . . . . . . . .16

Figure 7. I/O Read and Write Cycles with IOC = 1

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 8. I/O Read and Write cycles with IOC = 0

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 9. Op Code Fetch (without Wait State) Timing Diagram . . . .19

Figure 10. Op Code Fetch (with Wait State) Timing Diagram . . . . . .20

Figure 11. Memory Read/Write (without Wait State)

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Figure 12. Memory Read/Write (with Wait State)

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Figure 13. I/O Read/Write Timing Diagram . . . . . . . . . . . . . . . . . . . .23

Figure 14. Instruction Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . .24

Figure 15. RESET Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Figure 16. Bus Exchange Timing During Memory Read . . . . . . . . . . .26

Figure 17. Bus Exchange Timing During CPU Internal Operation . . .27

Figure 18. WAIT Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 19. Memory and I/O Wait State Insertion

(DCNTL – DMA/Wait Control Register) . . . . . . . . . . . . . .29

Figure 20. HALT Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .33

ix

UM005003-0703

Page 9

Z8018x

Family MPU User Manual

x

Figure 21. SLEEP Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 22. I/O Address Relocation . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 23. Logical Address Mapping Examples . . . . . . . . . . . . . . . . . 55

Figure 24. Physical Address Transition . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 25. MMU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 26. I/O Address Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 27. Logical Memory Organization . . . . . . . . . . . . . . . . . . . . . 58

Figure 28. Logical Space Configuration . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 29. Physical Address Generation . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 30. Physical Address Generation 2 . . . . . . . . . . . . . . . . . . . . . 64

Figure 31. Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 32. TRAP Timing Diagram -2nd Op Code Undefined . . . . . . 71

Figure 33. TRAP Timing - 3rd Op Code Undefined . . . . . . . . . . . . . 72

Figure 34. NMI Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 35. NMI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 36. INT0 Mode 0 Timing Diagram . . . . . . . . . . . . . . . . . . . . . 76

Figure 37. INT0 Mode 1 Interrupt Sequence . . . . . . . . . . . . . . . . . . . 77

Figure 38. INT0 Mode 1 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 39. INT0 Mode 2 Vector Acquisition . . . . . . . . . . . . . . . . . . . 79

Figure 40. INT0 Interrupt Mode 2 Timing Diagram . . . . . . . . . . . . . 80

Figure 41. INT1, INT2 Vector Acquisition . . . . . . . . . . . . . . . . . . . . 81

Figure 42. RETI Instruction Sequence . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 43. INT1, INT2 and Internal Interrupts Timing Diagram . . . . 86

Figure 44. Refresh Cycle Timing Diagram . . . . . . . . . . . . . . . . . . . . . 87

Figure 45. DMAC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure 46. DMA Timing Diagram-CYCLE STEAL Mode . . . . . . . 106

Figure 47. CPU Operation and DMA Operation DREQ0

Figure 48. CPU Operation and DMA Operation DREQ0

is Programmed for Level-Sense . . . . . . . . . . . . . . . . . . . 107

is Programmed for Edge-Sense . . . . . . . . . . . . . . . . . . . . 108

UM005003-0703

Page 10

Z8018x

Family MPU User Manual

Figure 49. TEND0 Output Timing Diagram . . . . . . . . . . . . . . . . . . .108

Figure 50. DMA Interrupt Request Generation . . . . . . . . . . . . . . . . .114

Figure 51. NMI and DMA Operation Timing Diagram . . . . . . . . . . .115

Figure 52. ASCI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

Figure 53. DCD0 Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . .139

Figure 54. RTS0 Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .140

Figure 55. ASCI Interrupt Request Circuit Diagram . . . . . . . . . . . . .140

Figure 56. ASCI Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

Figure 57. CSI/O Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

Figure 58. CSI/O Interrupt Request Generation . . . . . . . . . . . . . . . . .151

Figure 59. Transmit Timing Diagram–Internal Clock . . . . . . . . . . . .153

Figure 60. Transmit Timing–External Clock . . . . . . . . . . . . . . . . . . .154

Figure 61. CSI/O Receive Timing–Internal Clock . . . . . . . . . . . . . . .155

Figure 62. CSI/O Receive Timing–External Clock . . . . . . . . . . . . . .156

Figure 63. PRT Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

Figure 64. Timer Initialization, Count Down, and Reload

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163

Figure 65. Timer Output Timing Diagram . . . . . . . . . . . . . . . . . . . . .164

Figure 66. PRT Interrupt Request Generation . . . . . . . . . . . . . . . . . .164

Figure 67. E Clock Timing Diagram (During Read/Write Cycle

and Interrupt Acknowledge Cycle . . . . . . . . . . . . . . . . . .167

Figure 68. E Clock Timing in BUS RELEASE Mode . . . . . . . . . . . .167

Figure 69. E Clock Timing in SLEEP Mode and

SYSTEM STOP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . .168

Figure 70. External Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . .169

Figure 71. Clock Generator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . .170

Figure 72. Circuit Board Design Rules . . . . . . . . . . . . . . . . . . . . . . .170

Figure 73. Example of Board Design . . . . . . . . . . . . . . . . . . . . . . . . .171

xi

UM005003-0703

Page 11

Z8018x

Family MPU User Manual

xii

Software Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Figure 74. CPU Register Configurations . . . . . . . . . . . . . . . . . . . . . 176

Figure 75. Register Direct — Bit Field Definitions . . . . . . . . . . . . . 181

Figure 76. Register Indirect Addressing . . . . . . . . . . . . . . . . . . . . . . 181

Figure 77. Indexed Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Figure 78. Extended Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Figure 79. Immediate Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Figure 80. Relative Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Figure 81. AC Timing Diagram 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Figure 82. AC Timing Diagram 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Figure 83. CPU Timing (IOC = 0) (I/O Read Cycle,

I/O Write Cycle) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Figure 84. DMA Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Figure 85. E Clock Timing (Memory R/W Cycle) (I/O R/W Cycle) 201

Figure 86. E Clock Timing (BUS RELEASE Mode, SLEEP Mode, and

SYSTEM STOP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 87. E Clock Timing (Minimum Timing Example of PWEL and

PWEH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Figure 88. Timer Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Figure 89. SLP Execution Cycle Timing Diagram . . . . . . . . . . . . . . 203

Figure 90. CSI/O Receive/Transmit Timing Diagram . . . . . . . . . . . 204

Figure 91. External Clock Rise Time and Fall Time . . . . . . . . . . . . 204

Figure 92. Input Rise Time and Fall Time

(Except EXTAL, RESET) . . . . . . . . . . . . . . . . . . . . . . . . 204

Figure 93. Test Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

UM005003-0703

Page 12

Z8018x

Family MPU User Manual

List of Tables

Z80180, Z8S180, Z8L180 MPU Operation . . . . . . . . . . . . . . . . . . . .1

Table 1. Status Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Table 2. Multiplexed Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . .12

Table 3. Memory Wait States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Table 4. Wait State Insertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Table 5. Power-Down Modes

(Z8S180/Z8L180-Class Processor Only) . . . . . . . . . . . . . .37

Table 6. I/O Address Map for Z80180-Class Processors Only . . . . .44

Table 7. I/O Address Map

(Z8S180/Z8L180-Class Processors Only) . . . . . . . . . . . . .48

Table 8. State of IEF1 and IEF2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Table 9. Vector Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Table 10. RETI Control Signal States . . . . . . . . . . . . . . . . . . . . . . . . .85

Table 11. DRAM Refresh Intervals . . . . . . . . . . . . . . . . . . . . . . . . . .89

Table 12. Channel 0 Destination . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

Table 13. Channel 0 Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Table 14. Transfer Mode Combinations . . . . . . . . . . . . . . . . . . . . . . .99

Table 15. Channel 1 Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 16. DMA Transfer Request . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Table 17. Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

Table 18. Divide Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

Table 19. ASCI Baud Rate Selection. . . . . . . . . . . . . . . . . . . . . . . . .142

Table 20. Clock Mode Bit Values . . . . . . . . . . . . . . . . . . . . . . . . . . .144

Table 21. 2^ss Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

Table 22. CSI/O Baud Rate Selection . . . . . . . . . . . . . . . . . . . . . . . .150

xiv

UM005003-0703

Page 13

Z8018x

Family MPU User Manual

Table 23. Timer Output Control . . . . . . . . . . . . . . . . . . . . . . . . . . . .163

Table 24. E Clock Timing in Each Condition . . . . . . . . . . . . . . . . . .166

Table 25. Z8X180 Operating Frequencies . . . . . . . . . . . . . . . . . . . .169

Software Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Table 26. Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . .173

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

Table 27. Absolute Maximum Rating . . . . . . . . . . . . . . . . . . . . . . . .185

Table 28. Z80180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . .186

Table 29. Z8S180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . .187

Table 30. Z8L180 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . .189

xv

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

Table 31. Z8S180 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . 193

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

Table 32. Register Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

Table 33. Bit Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

Table 34. Instruction Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

Table 35. Address Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

Table 36. Flag Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

Table 37. Operations Mnemonics . . . . . . . . . . . . . . . . . . . . . . . . . . .210

Table 38. Arithmetic and Logical Instructions (8-bit) . . . . . . . . . . . .211

Table 39. Rotate and Shift Instructions . . . . . . . . . . . . . . . . . . . . . . .216

Table 40. Arithmetic Instructions (16-bit) . . . . . . . . . . . . . . . . . . . . .221

Table 41. 8-Bit Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

Table 42. 16-Bit Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

UM005003-0703

Page 14

Z8018x

Family MPU User Manual

xvi

Table 43. Block Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Table 44. Stock and Exchange . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Table 45. Program Control Instructions . . . . . . . . . . . . . . . . . . . . . . 229

Table 46. I/O Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Table 47. Special Control Instructions . . . . . . . . . . . . . . . . . . . . . . . 235

Op Code Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Table 48. 1st Op Code Map Instruction Format: XX . . . . . . . . . . . 247

Table 49. 2nd Op Code Map Instruction Format: CB XX . . . . . . . 249

Table 50. 2nd Op Code Map Instruction Format: ED XX . . . . . . . 250

Bus Control Signal Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Table 51. Bus and Control Signal Condition in Each

Machine Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Table 52. Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Operating Modes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

Table 53. Request Acceptances in Each Operating Mode . . . . . . . . 281

Table 54. The Z80180 Types of Requests . . . . . . . . . . . . . . . . . . . . 282

Status Signals 287

Table 55. Pin Outputs in Each Operating Mode. . . . . . . . . . . . . . . . 287

Table 56. Pin Status During RESET and

LOW POWER OPERATION Modes. . . . . . . . . . . . . . . . 289

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

Table 57. Internal I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

UM005003-0703

Page 15

Z8018x

Family MPU User Manual

xv

UM005003-0703

Page 16

Family MPU User Manual

Z80180, Z8S180, Z8L180 MPU Operation

FEATURES

•

Operating Frequency to 33 MHz

•

On-Chip MMU Supports Extended Address Space

•

Two DMA Channels

•

On-Chip Wait State Generators

•

Two Universal Asynchronous Receiver/Transmitter (UART) Channels

•

Two 16-Bit Timer Channels

Z8018x

1

•

On-Chip Interrupt Controller

•

On-Chip Clock Oscillator/Generator

•

Clocked Serial I/O Port

•

Code Compatible with ZiLOG Z80 CPU

•

Extended Instructions

GENERAL DESCRIPTION

Based on a microcoded execution unit and an advanced CMOS

manufacturing technology, the Z80180, Z8S180, Z8L180 (Z8X180) is an

8-bit MPU which provides the benefits of reduced system costs and low

power operation while offering higher performance and maintaining

compatibility with a large base of industry standard software written

around the ZiLOG Z8X CPU.

Higher performance is obtained by virtue of higher operating frequencies,

reduced instruction execution times, an enhanced instruction set, and an

UM005003-0703

Page 17

Z8018x

Family MPU User Manual

2

on-chip memory management unit (MMU) with the capability of

addressing up to 1 MB of memory.

Reduced system costs are obtained by incorporating several key system

functions on-chip with the CPU. These key functions include I/O devices

such as DMA, UART, and timer channels. Also included on-chip are

several glue functions such as dynamic RAM refresh control, wait state

generators, clock oscillator, and interrupt controller.

Not only does the Z8X180 consume a low amount of power during

normal operation, but processors with Z8S180 and Z8L180 class

processors also provides two operating modes that are designed to

drastically reduce the power consumption even further. The SLEEP mode

reduces power by placing the CPU into a stopped state, thereby

consuming less current, while the on-chip I/O device is still operating.

The SYSTEM STOP mode places both the CPU and the on-chip

peripherals into a stopped state, thereby reducing power consumption

even further.

When combined with other CMOS VLSI devices and memories, the

Z8X180 provides an excellent solution to system applications requiring

high performance, and low power operation.

Figures 1 through 3 illustrate the three pin packages in the Z8X180 MPU

family:

•

64-Pin Dual In-line Package (DIP), Figure 1

•

68-Pin Plastic Leaded Chip Carrier (PLCC), Figure 2

•

80-Pin Quad Flat Pack (QFP), Figure 3

Pin out package descriptions for other Z8X180-based products are

covered in their respective product specifications.

Figure 4 depicts the block diagram that is shared throughout all

configurations of the Z8X180.

UM005003-0703

Page 18

V

XTAL

EXTAL

WAIT

BUSACK

BUSREQ

RESET

NMI

INT0

INT1

INT2

ST

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18/TOUT

V

CC

Z8018x

Family MPU User Manual

3

1

SS

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Z8X180

64

Phi

RD

63

62

WR

61

MI

E

60

59

MREQ

58

IORQ

57

RFSH

56

HALT

55

TEND1

54

DREQ1

53

CKS

52

RXS/CTS1

51

TXS

50

CKA1/TEND0

RXA1

49

48

TXA1

CKA0/DREQ0

47

46

RXA0

45

TXA0

44

DCO0

CTS0

43

RTS0

42

D7

41

40

D6

D5

39

38

D4

37

D3

36

D2

D1

35

34

D0

33

V

SS

Figure 1. 64-Pin DIP

UM005003-0703

Page 19

Z8018x

Family MPU User Manual

4

10

INT0

INT1

11

INT2

12

ST

13

A0

14

A1

15

A2

16

17

A3

18

V

SS

A4

19

20

A5

A6

21

A7

22

A8

23

A9

24

A10

25

26

A11

NMI

9

27

A12

RESET

8

28

A13

BUSREQ

7

29

A14

BUSACK

6

30

A15

WAIT

5

A16

EXTAL

XTAL

432

Z8X180

33

32

A17

VSS

VLS

PhiRDWRMIE

1

68676665646362

35

34

363137383940414243

SS

CC

D0

D2

D1

V

A19

V

D3

D4

MREQ

IORQ

RFSH

61

60

HALT

TEND1

59

58

DREQ1

57

CKS

RXS/CTS1

56

55

TXS

54

CKA1/TEND0

53

RXA1

52

TEST

51

TXA1

50

CKA0/DREQ0

49

RXA0

48

TXA0

47

DCD0

46

CTS0

RTS0

45

44

D7

D6

D5

A18/TOUT

Figure 2. 68-Pin PLCC

UM005003-0703

Page 20

SSVSS

K

RESET

BUSREQBUSAC

8079787776757473727170

EXTALNCWAIT

XTAL

V

Phi

RD

WR

69

Family MPU User Manual

MREQ

MI

686766

IORQ

E

65

Z8018x

5

NMI

NC

NC

INT0

INT1

INT2

ST

A0

A1

A2

A3

V

SS

A4

NC

A5

A6

A7

A8

A9

A10

A11

NC

NC

A12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

10111213141516

A13

A14

A15

A16

Z8X180

NC

A17

17

CC

V

181920

SS

A19

V

D0

21

D1

222324

D2D3D4

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

25

D5

RFSH

NC

NC

HALT

TEND1

DREQ1

CKS

RXS/CTS1

TXS

CKA1/TEND0

RXA1

TEST

TXA1

NC

CKA0/DREQ0

RXA0

TXA0

DCD0

CTS

RTS0

D7

NC

NC

D6

Figure 3. 80-Pin QFP

A18/TOUT

UM005003-0703

Page 21

Z8018x

Family MPU User Manual

6

XTAL

EXTAL

RESETRDWRMIMREQ

IORQ

HALT

WAIT

BUSREQ

BUSACK

RFSH

STENMI

INT0

INT1

INT2

Phi

A18/TOUT

TXS

RXS/CTS1

CKS

Timing

Generator

16-bit

Programmable

Reload

Timers

Clocked

Serial I/O

Port

MMU

(16-bit)

Address Bus

Bus State Control

CPU

Data Bus (8-bit)

DMACs

(2)

Asynchronous

SCI

(Channel 0)

Asynchronous

SCI

(channel 1)

Interrupt

DREQ1

TEND1

TXA0

CKA0/DREQ0

RXA0

RTS0

CTS0

DCD0

TXA1

CKA1/TEND0

RXA1

Address

Buffer

–

A0

A19

Data

Buffer

D0

–

DF

Figure 4. Z80180/Z8S180/Z8L180 Block Diagram

UM005003-0703

V

CC

V

SS

Page 22

PIN DESCRIPTION

A0–A19. Address Bus (Output, Active High, 3-state). A0–A19 form a 20-

bit address bus. The Address Bus provides the address for memory data

bus exchanges, up to 1 MB, and I/O data bus exchanges, up to 64K. The

address bus enters a high impedance state during RESET and external bus

acknowledge cycles. Address line A18 is multiplexed with the output of

PRT channel 1 (TOUT, selected as address output on RESET) and address

line A19 is not available in DIP versions of the Z8X180.

Z8018x

Family MPU User Manual

7

BUSACK

that the requesting device, the MPU address and data bus, and some

control signals, have entered their high impedance state.

BUSREQ

external devices (such as DMA controllers) to request access to the

system bus. This request has a higher priority than NMI

recognized at the end of the current machine cycle. This signal stops the

CPU from executing further instructions and places the address and data

buses, and other control signals, into the high impedance state.

CKA0, CKA1. Asynchronous Clock 0 and 1 (Bidirectional, Active High).

These pins are the transmit and receive clocks for the ASCI channels.

CKA0, is multiplexed with DRE

TEND

CKS. Serial Clock (Bidirectional, Active High). This line is the clock for

the CSIO channel.

CLOCK (PHI). System Clock (Output, Active High). The output is used

as a reference clock for the MPU and the external system. The frequency

of this output is equal to one-half that of the crystal or input clock

frequency.

CTS

modem control signals for the ASCI channels. CTS

. Bus Acknowledge (Output, Active Low). BUSACK indicates

. Bus Request (Input, Active Low). This input is used by

and is always

Q0 and CKA1 is multiplexed with

0.

0, CTS1. Clear to Send 0 and 1 (Inputs, Active Low). These lines are

1 is multiplexed with RXS.

UM005003-0703

Page 23

Z8018x

Family MPU User Manual

8

D0–D7. Data Bus (Bidirectional, Active High, 3-state). D0-D7 constitute

an 8-bit bidirectional data bus, used for the transfer of information to and

from I/O and memory devices. The data bus enters the high impedance

state during RESET and external bus acknowledge cycles.

DCD

programmable modem control signal for ASCI channel 0.

0. Data Carrier Detect 0 (Input, Active Low). This input is a

DREQ

0, DREQ1. DMA Request 0 and 1 (Input, Active Low). DREQ is

used to request a DMA transfer from one of the on-chip DMA channels.

The DMA channels monitor these inputs to determine when an external

device is ready for a read or write operation. These inputs can be

programmed to be either level- or edge-sensed. DREQ

0 is multiplexed

with CKA0.

E. Enable Clock (Output, Active High). Synchronous machine cycle clock

output during bus transactions.

EXTAL. External Clock/Crystal (Input, Active High). Crystal oscillator

connection. An external clock can be input to the Z8X180 on this pin

when a crystal is not used. This input is Schmitt-triggered.

HALT

after the CPU has executed either the HALT

. Halt/Sleep Status (Output, Active Low). This output is asserted

or SLP instruction, and is

waiting for either non-maskable or maskable interrupt before operation

can resume. HALT

is also used with the M1 and ST signals to decode

status of the CPU machine cycle.

0. Maskable Interrupt Request 0 (Input, Active Low). This signal is

INT

generated by external I/O devices. The CPU honors this request at the end

of the current instruction cycle as long as the NMI

and BUSREQ signals

are inactive. The CPU acknowledges this interrupt request with an

interrupt acknowledge cycle. During this cycle, both the M

1 and IORQ

signals become Active.

1, INT2. Maskable Interrupt Requests 1 and 2 (Inputs, Active Low).

INT

This signal is generated by external I/O devices. The CPU honors these

requests at the end of the current instruction cycle as long as the NMI

UM005003-0703

,

Page 24

Z8018x

Family MPU User Manual

BUSREQ, and INT0 signals are inactive. The CPU acknowledges these

interrupt requests with an interrupt acknowledge cycle. Unlike the

acknowledgment for INT

0, during this cycle neither the M1 or IORQ

signals become Active.

. I/O Request (Output, Active Low, 3-state). IORQ indicates that the

IORQ

address bus contains a valid I/O address for an I/O read or I/O write

operation. IORQ

acknowledgment of the INT

is also generated, along with M1, during the

0 input signal to indicate that an interrupt

response vector can be placed onto the data bus. This signal is analogous

to the IOE

1. Machine Cycle 1 (Output, Active Low). Together with MR EQ , M1

M

signal of the Z64180.

indicates that the current cycle is the Op Code fetch cycle of an

instruction execution. Together with IORQ

cycle is for an interrupt acknowledge. It is also used with the HALT

, M1 indicates that the current

and

ST signal to decode status of the CPU machine cycle. This signal is

analogous to the LIR

signal of the Z64180.

9

MREQ

. Memory Request (Output, Active Low, 3-state). MREQ indicates

that the address bus holds a valid address for a memory read or memory

write operation. This signal is analogous to the ME

. Non-maskable Interrupt (Input, negative edge triggered). NMI has

NMI

a higher priority than INT

and is always recognized at the end of an

signal of the Z64180.

instruction, regardless of the state of the interrupt enable flip-flops. This

signal forces CPU execution to continue at location

. Read (Output active Low, 3-state). RD indicates that the CPU wants

RD

0066H.

to read data from memory or an I/O device. The addressed I/O or memory

device must use this signal to gate data onto the CPU data bus.

. Refresh (Output, Active Low). Together with MREQ, RFSH

RFSH

indicates that the current CPU machine cycle and the contents of the

address bus must be used for refresh of dynamic memories. The low order

8 bits of the address bus (A7–A0) contain the refresh address.

This signal is analogous to the REF

signal of the Z64180.

UM005003-0703

Page 25

10

Z8018x

Family MPU User Manual

RTS0. Request to Send 0 (Output, Active Low). This output is a

programmable modem control signal for ASCI channel 0.

RXA0, RXA1. Receive Data 0 and 1 (Inputs, Active High). These signals

are the receive data to the ASCI channels.

RXS. Clocked Serial Receive Data (Input, Active High). This line is the

receiver data for the CSIO channel. RXS is multiplexed with the CTS

signal for ASCI channel 1.

1

ST. Status (Output, Active High). This signal is used with the M1

HALT

output to decode the status of the CPU machine cycle. Table 1

and

provides status summary.

Table 1. Status Summary

ST HALT

0 1 0 CPU operation (1st Op Code fetch)

1 1 0 CPU operation (2nd Op Code and 3rd Op Code fetch)

1 1 1 CPU operation (MC

0X

0 0 0 HALT mode

1 0 1 SLEEP mode (including SYSTEM STOP mode)

1

M1 Operation

1 DMA operation

2

except for Op Code fetch)

1. X = Don't care

2. MC = Machine cycle

TEND

0, TEND1. Transfer End 0 and 1 (Outputs, Active Low). This

output is asserted active during the last write cycle of a DMA operation. It

is used to indicate the end of the block transfer. TEND

0 in multiplexed

with CKA1.

TEST. Test (Output, not on DIP version). This pin is for test and must be

left open.

UM005003-0703

Page 26

Z8018x

Family MPU User Manual

TOUT. Timer Out (Output, Active High). TOUT is the pulse output from

PRT channel 1. This line is multiplexed with A18 of the address bus.

TXA0, TXA1. Transmit Data 0 and 1 (Outputs, Active High). These

signals are the transmitted data from the ASCI channels. Transmitted data

changes are with respect to the falling edge of the transmit clock.

TXS. Clocked Serial Transmit Data (Output, Active High). This line is

the transmitted data from the CSIO channel.

. Wait (Input; Active Low). WAIT indicates to the CPU that the

WAIT

addressed memory or I/O devices are not ready for a data transfer. This

input is used to induce additional clock cycles into the current machine

cycle. The WAIT

input is sampled on the falling edge of T2 (and

subsequent Wait States). If the input is sampled Low, then additional Wait

States are inserted until the WAIT

input is sampled High, at which time

execution continues.

11

. Write (Output, Active Low, 3-state). WR indicates that the CPU data

WR

bus holds valid data to be stored at the addressed I/O or memory location.

XTAL. Crystal (Input, Active High). Crystal oscillator connection. This

pin must be left open if an external clock is used instead of a crystal. The

oscillator input is not a TTL level (reference DC characteristics).

Multiplexed pins are described in Table 2.

UM005003-0703

Page 27

12

Z8018x

Family MPU User Manual

Table 2. Multiplexed Pin Descriptions

Multiplexed

Pins Descriptions

A18/TOUT

CKA0/

DREQ0

TEND0

CKA1/

During RESET, this pin is initialized as A18 pin. If either

TOC1 or TOC0 bit of the Timer Control Register (TCR) is set

to 1, TOUT function is selected. If TOC1 and TOC0 bits are

cleared to 0, A18 function is selected.

During RESET, this pin is initialized as CKA0 pin.

If either DM1 or SM1 in DMA Mode Register (DMODE) is

set to 1,

During RESET, this pin is initialized as CKA1 pin. If

CKA1D bit in ASCI control register ch 1 (CNTLA1) is set to

1,

CKA1 function is selected.

DREQ0 function is always selected.

TEND0 function is selected. If CKA1D bit is set to 0,

During RESET, this pin is initialized as RXS pin. If CTS1E bit

RXS/

CTS1

in ASCI status register ch 1 (STAT1) is set to 1,

is selected. If CTS1E bit is 0, RXS function is selected.

ARCHITECTURE

The Z8X180 combines a high performance CPU core with a variety of

system and I/O resources useful in a broad range of applications. The CPU

core consists of five functional blocks: clock generator, bus state controller

(including dynamic memory refresh), interrupt controller, memory

management unit (MMU), and the central processing unit (CPU). The

integrated I/O resources make up the remaining four functional blocks:

•

Direct Memory Access (DMA) Control (2 channels)

•

Asynchronous Serial Communications Interface (ASCI, 2 channels),

UM005003-0703

CTS1 function

Page 28

Z8018x

Family MPU User Manual

•

Programmable Reload Timers (PRT, 2 channels)

•

Clock Serial I/O (CSIO) channel.

Other Z8X180 family members (such as Z80183, Z80S183, Z80185/195)

feature, in addition to these blocks, additional peripherals and are covered

in their associated Product Specification

Clock Generator

This logic generates the system clock from either an external crystal or

clock input. The external clock is divided by two and provided to both

internal and external devices.

Bus State Controller

13

This logic performs all of the status and bus control activity associated

with both the CPU and some on-chip peripherals. This includes Wait State

timing, RESET cycles, DRAM refresh, and DMA bus exchanges.

Interrupt Controller

This block monitors and prioritizes the variety of internal and external

interrupts and traps to provide the correct responses from the CPU. To

remain compatible with the Z80 CPU, three different interrupt modes are

supported.

Memory Management Unit

The MMU allows the user to map the memory used by the CPU (logically

only 64K) into the 1MB addressing range supported by the Z8X180. The

organization of the MMU object code features compatibility with the Z80

CPU while offering access to an extended memory space. This capability

is accomplished by using an effective common area - banked area

scheme.

UM005003-0703

Page 29

14

Z8018x

Family MPU User Manual

Central Processing Unit

The CPU is microcoded to provide a core that is object code compatible

with the Z80 CPU. It also provides a superset of the Z80 instruction set,

including 8-bit multiply and divide. This core has been enhanced to allow

many of the instructions to execute in fewer clock cycles.

DMA Controller

The DMA controller provides high speed transfers between memory and

I/O devices. Transfer operations supported are memory-to-memory,

memory to/from I/O and I/O to I/O. Transfer modes supported are

REQUEST, BURST, and CYCLE STEAL. DMA transfers can access the

full 1MB addressing range with a block length up to 64KB, and can cross

over 64K boundaries.

Asynchronous Serial Communications Interface (ASCI)

The ASCI logic provides two individual full-duplex UARTs. Each

channel includes a programmable baud rate generator and modem control

signals. The ASCI channels can also support a multiprocessor

communications format.

Programmable Reload Timer (PRT)

This logic consists of two separate channels, each containing a 16-bit

counter (timer) and count reload register. The time base for the counters is

derived from the system clock (divided by 20) before reaching the

counter. PRT channel 1 provides an optional output to allow for

waveform generation.

Clocked Serial I/O (CSIO)

The CSIO channel provides a half-duplex serial transmitter and receiver.

This channel can be used for simple high-speed data connection to

another microprocessor or microcomputer.

UM005003-0703

Page 30

Z8018x

Family MPU User Manual

OPERATION MODES

The Z8X180 can be configured to operate like the Hitachi HD64180. This

functionality is accomplished by allowing user control over the M

IORQ

, WR, and RD signals. The Operation Mode Control Register

(OMCR), illustrated in Figure 5, determines the M

the IORQ

, RD, and WR signals, and the RETI operation.

1 options, the timing of

Operation Mode Control Register

Bit 7654 0

Bit/Field M1E M1TE

R/W R/W W R/W –

Reset 1 1 1 –

Note: R = Read W = Write X = Indeterminate? = Not Applicable

IOC Reserved

1,

15

Figure 5. Operation Mode Control Register

M1E (M1 Enable): This bit controls the M1 output and is set to a 1 during

RESET.

When M1E is

1, the M1 output is asserted Low during the Op Code fetch

cycle, the INT0 acknowledge cycle, and the first machine cycle of the

acknowledge. This action also causes the M1 signal to be Active

NMI

during both fetches of the RETI instruction sequence, and may cause

corruption of the external interrupt daisy chain. Therefore, this bit must be

0 for the Z8X180. When M1E is 0 the M1 output is normally inactive and

asserted Low only during the refetch of the RETI instruction sequence

and the INT

0 acknowledge cycle (Figure 6).

UM005003-0703

Page 31

16

Z8018x

Family MPU User Manual

Phi

WR

M1

T1

Write into OMCR

Figure 6. M1 Temporary Enable Timing

T2

T3

T1

Op Code Fetch

T2

T3

M1TE (M1 Temporary Enable): This bit controls the temporary assertion

of the M1

signal. It is always read back as a 1 and is set to 1 during

RESET. This function is used to arm the internal interrupt structure of the

Z80PIO. When a control word is written to the Z80PIO to enable

interrupts, no enable actually takes place until the PIO sees an active M

signal. When M1TE

signal and M1E controls its function. When M1TE

is 1, there is no change in the operation of the M1

is 0, the M1 output is

1

asserted during the next Op Code fetch cycle regardless of the state

programmed into the M1E bit. This situation is only momentary (one

time) and the user need not reprogram a

1 to disable the function (See

Figure 7).

: This bit controls the timing of the IORQ and RD signals. IOC is set

IOC

to

1 by RESET.

When IOC

is 1, the IORQ and RD signals function the same as the

HD64180.

UM005003-0703

Page 32

Z8018x

Family MPU User Manual

17

T1

Phi

IORQ

RD

WR

T2

TW

T3

Figure 7. I/O Read and Write Cycles with IOC = 1 Timing Diagram

When IOC is 0, the timing of the IORQ and RD signals match the timing

required by the Z80 family of peripherals. The IORQ

and RD signals go

active as a result of the rising edge of T2. This timing allows the Z8X180

to satisfy the setup times required by the Z80 peripherals on those two

signals (Figure ).

T1

Phi

T2

TW

T3

IORQ

RD

WR

Figure 8. I/O Read and Write cycles with IOC = 0 Timing Diagram

For the remainder of this document, assume that M1E is 0 and IOC is 0.

UM005003-0703

Page 33

18

Z8018x

Family MPU User Manual

Note:

The user must program the Operation Mode Control Register

before the first I/O instruction is executed.

CPU Timing

This section explains the Z8X180 CPU timing for the following operations:

•

Instruction (Op Code) fetch timing

•

Operand and data read/write timing

•

I/O read/write timing

•

Basic instruction (fetch and execute) timing

•

RESET timing

•

BUSREQ/BUSACK bus exchange timing

The basic CPU operation consists of one or more Machine Cycles (MC).

A machine cycle consists of three system clocks, T1, T2, and T3 while

accessing memory or I/O, or it consists of one system clock (T1) during

CPU internal operations. The system clock is half the frequency of the

Crystal oscillator (that is, an 8-MHz crystal produces 4 MHz or 250 nsec).

For interfacing to slow memory or peripherals, optional Wait States (TW)

may be inserted between T2 and T3.

Instruction (Op Code) Fetch Timing

Figure 9 illustrates the instruction (Op Code) fetch timing with no Wait

States. An Op Code fetch cycle is externally indicated when the M

output pin is Low.

In the first half of T1, the address bus (A0–A19) is driven from the

contents of the Program Counter (PC). This address bus is the translated

address output of the Z8X180 on-chip MMU.

In the second half of T1, the MREQ

signals are asserted Low, enabling the memory.

UM005003-0703

. (Memory Request) and RD (Read)

1

Page 34

Z8018x

Family MPU User Manual

The Op Code on the data bus is latched at the rising edge of T3 and the

bus cycle terminates at the end of T3.

T1 T3 T1 T2T2

Phi

–

A19

A0

D0

–

D7

WAIT

M1

MREQ

RD

19

Figure 9. Op Code Fetch (without Wait State) Timing Diagram

Figure 10 illustrates the insertion of Wait States (TW) into the Op Code

fetch cycle. Wait States (TW) are controlled by the external WAIT

input

combined with an on-chip programmable Wait State generator.

At the falling edge of T2 the combined WAIT

input is sampled. If WAIT

input is asserted Low, a Wait State (TW) is inserted. The address bus,

MREQ

, RD and M1 are held stable during Wait States. When WAIT is

sampled inactive High at the falling edge of TW, the bus cycle enters T3

and completes at the end of T3.

UM005003-0703

Page 35

20

Z8018x

Family MPU User Manual

Phi

A0

–

A19

–

D7

D0

WAIT

M1

MREQ

RD

T1 T2T2 TW TW T3 T1

Op Code

Figure 10. Op Code Fetch (with Wait State) Timing Diagram

Operand and Data Read/Write Timing

The instruction operand and data read/write timing differs from Op Code

fetch timing in two ways:

•

The M1 output is held inactive

•

The read cycle timing is relaxed by one-half clock cycle because data

is latched at the falling edge of T3

Instruction operands include immediate data, displacement, and extended

addresses, and contain the same timing as memory data reads.

During memory write cycles the MREQ

signal goes active in the second

half of T1. At the end of T1, the data bus is driven with the write data.

At the start of T2, the WR

MREQ

and WR go inactive in the second half of T3 followed by

signal is asserted Low enabling the memory.

disabling of the write data on the data bus.

UM005003-0703

Page 36

Z8018x

Family MPU User Manual

Wait States (TW) are inserted as previously described for Op Code fetch

cycles. Figure 11 illustrates the read/write timing without Wait States

(Tw), while Figure 12 illustrates read/write timing with Wait States (TW).

21

–

A0

D0–D7

WAIT

MREQ

Phi

A19

RD

WR

Read Cycle

T1 T1T2 T3 T1 T2 T3

Memory address

Read data

Write Cycle

Memory address

Write data

Figure 11. Memory Read/Write (without Wait State) Timing Diagram

UM005003-0703

Page 37

22

Z8018x

Family MPU User Manual

Phi

A0–A19

D0–D7

WAIT

MREQ

RD

WR

Read Cycle

T1 T1T2 TW T3 T2 T3

Read data

Figure 12. Memory Read/Write (with Wait State) Timing Diagram

Write Cycle

TW

Write data

I/O Read/Write Timing

I/O Read/Write operations differ from memory Read/Write operations in

the following three ways:

•

The IORQ (I/O Request) signal is asserted Low instead of the MREQ

signal

•

The 16-bit I/O address is not translated by the MMU

•

A16–A19 are held Low

At least one Wait State (TW) is always inserted for I/O read and write

cycles (except internal I/O cycles).

Figure 13 illustrates I/O read/write timing with the automatically inserted

Wait State (TW).

UM005003-0703

Page 38

Z8018x

Family MPU User Manual

23

A0

D0

Phi

–

A19

–

D7

WAIT

IORQ

RD

WR

I/O Read Cycle

T1 T1T2 TW T3 T2 T3

I/O address

Read data

I/O Write Cycle

TW

I/O address

Write data

Figure 13. I/O Read/Write Timing Diagram

Basic Instruction Timing

An instruction may consist of a number of machine cycles including Op

Code fetch, operand fetch, and data read/write cycles. An instruction may

also include cycles for internal processes which make the bus IDLE. The

example in Figure 14 illustrates the bus timing for the data transfer

instruction LD (IX+d),g.

UM005003-0703

Page 39

24

Z8018x

Family MPU User Manual

Phi

–

A19

A0

D0–D7

M1

MREQ

RD

WR

Machine Cycle

1st Op Code

Fetch Cycle

2nd Op Code

Fetch Cycle

Displacement

Read Cycle

CPU internal

Operation

Memory

Write Cycle

T1 T2 T3 T1 T3 T1T2 T2 T3 T1 T1 T1 T1 T1T2 T3 T2

PC

(DDH)

MC1 MC2 MC3 MC4 MC5 MC6 MC7

NOTE: d = displacement

g = register contents

PC+1

(7OH

–

77H)

PC+2

d

IX+d

Next instruction

Fetch Cycle

PC+3

g

Figure 14. Instruction Timing Diagram

This instruction moves the contents of a CPU register (g) to the memory

location with address computed by adding a signed 8-bit displacement (d)

to the contents of an index register (IX).

The instruction cycle begins with the two machine cycles to read the two

byte instruction Op Code as indicated by M

operand (d) is fetched.

UM005003-0703

1 Low. Next, the instruction

Page 40

Z8018x

Family MPU User Manual

The external bus is IDLE while the CPU computes the effective address.

Finally, the computed memory location is written with the contents of the

CPU register (g).

RESET Timing

25

Figure 15 depicts the Z8X180 hardware RESET timing. If the RESET

is Low for six or more clock cycles, processing is terminated and the

Z8X180 restarts execution from (logical and physical) address

RESET

T1 T2

Phi

RESET

–

A19

A0

Figure 15. RESET Timing Diagram

6 or more clocks

High impedance

RESET Start

Op Code Fetch Cycle

Restart address (00000H)

00000H.

BUSREQ/BUSACK Bus Exchange Timing

The Z8X180 can coordinate the exchange of control, address and data bus

ownership with another bus master. The alternate bus master can request

the bus release by asserting the BUSREQ

(Bus Request) input Low. After

the Z8X180 releases the bus, it relinquishes control to the alternate bus

master by asserting the BUSACK

(Bus Acknowledge) output Low.

pin

The bus may be released by the Z8X180 at the end of each machine cycle.

In this context, a machine cycle consists of a minimum of three clock

cycles (more if wait states are inserted) for Op Code fetch, memory read/

write, and I/O read/write cycles. Except for these cases, a machine cycle

corresponds to one clock cycle.

UM005003-0703

Page 41

26

Z8018x

Family MPU User Manual

When the bus is released, the address (A0–A19), data (D0–D7), and

control (MREQ

impedance state.

Dynamic RAM refresh is not performed when the Z8X180 has released

the bus. The alternate bus master must provide dynamic memory

refreshing if the bus is released for long periods of time.

, IORQ, RD, and WR) signals are placed in the high

Figure 16 illustrates BUSREQ

/BUSACK bus exchange during a memory

read cycle. Figure 17 illustrates bus exchange when the bus release is

requested during a Z8X180 CPU internal operation. BUSREQ

at the falling edge of the system clock prior to T3, T1 and Tx (BUS

RELEASE state). If BUSREQ

is asserted Low at the falling edge of the

clock state prior to Tx, another Tx is executed.

CPU memory read cycle Bus release cycle CPU cycle

T1 T1TXTXT3TWT2 T1

Phi

A0

–

A19

D0–D7

MREQ

IORQ

, WR

RD

BUSREQ

BUSACK

is sampled

Figure 16. Bus Exchange Timing During Memory Read

UM005003-0703

Page 42

Phi

A0

–

A19

D0–D7

MREQ

IORQ

RD

, WR

BUSREQ

BUSACK

Z8018x

Family MPU User Manual

27

CPU Internal Operation Bus Release Cycle CPU Cycle

T1 T1 T1 TX T1TXT1 TX

Figure 17. Bus Exchange Timing During CPU Internal Operation

Wait State Generator

To ease interfacing with slow memory and I/O devices, the Z8X180 uses

Wait States (TW) to extend bus cycle timing. A Wait State(s) is inserted

based on the combined (logical OR) state of the external WAIT

an internal programmable wait state (TW) generator. Wait States (TW)

can be inserted in both CPU execution and DMA transfer cycles.

When the external WAIT

inserted between T2 and T3 to extend the bus cycle duration. The WAIT

input is sampled at the falling edge of the system clock in T2 or TW. If the

WAIT

input is asserted Low at the falling edge of the system clock in TW,

another TW is inserted into the bus cycle.

Note:

WAI T

input transitions must meet specified setup and hold

times. This specification can easily be accomplished by

input is asserted Low, Wait State(s) (TW) are

UM005003-0703

input and

Page 43

28

Z8018x

Family MPU User Manual

externally synchronizing WAIT input transitions with the rising

edge of the system clock.

Dynamic RAM refresh is not performed during Wait States (TW) and thus

system designs which use the automatic refresh function must consider

the affects of the occurrence and duration of wait states (TW). Figure 18

depicts WAIT

timing.

T1

Phi

WAIT

Figure 18. WAIT Timing Diagram

T2 TW TW T3 T1

Programmable Wait State Insertion

In addition to the WAIT

input, Wait States (TW) can also be inserted by

program using the Z8X180 on-chip Wait State generator (see Figure 19.

Wait State (TW) timing applies for both CPU execution and on-chip

DMAC cycles.

By programming the four significant bits of the DMA/Wait Control

Register (DCNTL) the number of Wait States, (TW) automatically

inserted in memory and I/O cycles, can be separately specified. Bits 4 and

5 specify the number of Wait States (TW) inserted for I/O access and bits

6 and 7 specify the number of Wait States (TW) inserted for memory

access. These bit pairs all 0–3 programmed Wait States for either I/O or

memory access.

UM005003-0703

Page 44

Z8018x

Family MPU User Manual

Bit 7 6 5 4

MWI1 MWI0 MWI1 MWI0

R/W R/W R/W R/W

Figure 19. Memory and I/O Wait State Insertion (DCNTL – DMA/Wait

Control Register)

The number of Wait States (TW) inserted in a specific cycle is the

maximum of the number requested by the WAIT

input, and the number

automatically generated by the on-chip Wait State generator.

Bit 7, 6: MWI1 MWI0, (Memory Wait Insertion)

29

For CPU and DMAC cycles which access memory (including memory

mapped I/O), zero to three Wait States may be automatically inserted

depending on the programmed value in MWI1 and MWI0 as depicted in

Table 3

Table 3. Memory Wait States

MW11 MWI0 The Number of Wait States

00 0

01 1

10 2

11 3

Bit 5, 4: IWI1, IWI0 (I/O Wait Insertion)

For CPU and DMA cycles which access external I/O (and interrupt

acknowledge cycles), one to six Wait States (TW) may be automatically

UM005003-0703

Page 45

Z8018x

Family MPU User Manual

30

inserted depending on the programmed value in IWI1 and IWI0. Refer to

Table 4.

Table 4. Wait State Insertion

For external

I/O registers

IWI1 IWI0

accesses

The Number of Wait States

For internal

I/0

registers

accesses

For INT0

interrupt

acknowledge

cycles when

M1

is Low

For INT1

INT2

,

and

internal

interrupts

acknowledge

cycles

(Note 2)

For NMI

interrupt

acknowledge

cycles

when M1

is

Low

(Note 2)

00 1 0

01 2 4

(Note 1)

22 0

10 3 5

11 4 6

Note:

1. For Z8X180 internal I/O register access (I/O addresses

determine wait state (TW) timing. For ASCI, CSI/O and PRT Data Register accesses, 0 to 4 Wait States

(TW) are generated. The number of Wait States inserted during access to these registers is a function of

internal synchronization requirements and CPU state. All other on-chip I/O register accesses (that is,

MMU, DMAC, ASCI Control Registers, for instance.) have no Wait States inserted and thus require only

three clock cycles.

2. For interrupt acknowledge cycles in which M

stacking cycle, memory access timing applies.

1 is High, such as interrupt vector table read and PC

0000H-003FH), IWI1 and IWI0 do not

WAIT Input and RESET

During RESET, MWI1, MWI0 IWI1 and IWI0, are all

1, selecting the

maximum number of Wait States (TW) (three for memory accesses, four

for external I/O accesses).

UM005003-0703

Page 46

Z8018x

Family MPU User Manual

Also, the WAIT input is ignored during RESET. For example, if RESET

is detected while the Z8X180 is in a Wait State (TW), the Wait Stated

cycle in progress is aborted, and the RESET sequence initiated. Thus,

RESET

has higher priority than WAIT.

HALT and Low Power Operation Modes (Z80180-Class

Processors Only)

The Z80180 can operate in two different modes:

•

HALT mode

•

IOSTOP mode

31

and two low-power operation modes:

•

SLEEP

•

SYSTEM STOP

In all operating modes, the basic CPU clock (XTAL, EXTAL) must

remain active.

HALT Mode

HALT mode is entered by execution of the HALT instruction (Op Code

76H) and has the following characteristics:

•

The internal CPU clock remains active

•

All internal and external interrupts can be received

•

Bus exchange (BUSREQ and BUSACK) can occur

•

Dynamic RAM refresh cycle (RFSH) insertion continues at the

programmed interval

•

I/O operations (ASCI, CSI/O and PRT) continue

•

The DMAC can operate

UM005003-0703

Page 47

32

Z8018x

Family MPU User Manual

•

The HALT output pin is asserted Low

•

The external bus activity consists of repeated dummy fetches of the

Op Code following the HALT instruction.

Essentially, the Z80180 operates normally in HALT mode, except that

instruction execution is stopped.

HALT mode can be exited in the following two ways:

•

RESET Exit from HALT Mode

If the RESET

HALT mode is exited and the normal RESET

address

•

Interrupt Exit from HALT mode

When an internal or external interrupt is generated, HALT mode is

exited and the normal interrupt response sequence is initiated.

00000H) is initiated.

input is asserted Low for at least six clock cycles,

sequence (restart at

If the interrupt source is masked (individually by enable bit, or globally

by IEF1 state), the Z80180 remains in HALT mode. However, NMI

interrupt initiates the normal NMI

independent of the state of IEF1.

HALT timing is illustrated in Figure 20.

UM005003-0703

interrupt response sequence

Page 48

Z8018x

Family MPU User Manual

33

.

HALT Op Code

Fetch Cycle

HALT mode

Interrupt

acknowledge cycle

T1

Phi

, NMI

INT1

–

A19

A0

HALT

MREQ

Figure 20. HALT Timing Diagram

HALT Op Code address HALT Op Code address + 1

M1

RD

T3 T1 T2 T3 T1 T2

SLEEP Mode

SLEEP mode is entered by execution of the 2-byte SLP instruction.

SLEEP mode contains the following characteristics:

•

The internal CPU clock stops, reducing power consumption

•

The internal crystal oscillator does not stop

•

Internal and external interrupt inputs can be received

•

DRAM refresh cycles stop

•

I/O operations using on-chip peripherals continue

•

The internal DMAC stop

•

BUSREQ can be received and acknowledged

•

Address outputs go High and all other control signal outputs become

inactive High

UM005003-0703

Page 49

34

Z8018x

Family MPU User Manual

•

Data Bus, 3-state

SLEEP mode is exited in one of two ways as described below.

•

RESET Exit from SLEEP mode. If the RESET input is held Low for

at least six clock cycles, it exits SLEEP mode and begins the normal

RESET sequence with execution starting at address (logical and

physical)

•

Interrupt Exit from SLEEP mode. The SLEEP mode is exited by

detection of an external (NMI

CSI/O, PRT) interrupt.

00000H.

, INT0, INT2) or internal (ASCI,

In case of NMI

NMI

interrupt response sequence.

In the case of all other interrupts, the interrupt response depends on the

state of the global interrupt enable flag IEF1 and the individual interrupt

source enable bit.

If the individual interrupt condition is disabled by the corresponding

enable bit, occurrence of that interrupt is ignored and the CPU remains in

the SLEEP mode.

Assuming the individual interrupt condition is enabled, the response to

that interrupt depends on the global interrupt enable flag (IEF1). If

interrupts are globally enabled (IEF1 is

interrupt occurs, SLEEP mode is exited and the appropriate normal

interrupt response sequence is executed.

If interrupts are globally disabled (IEF1 is

interrupt occurs, SLEEP mode is exited and instruction execution begins

with the instruction following the SLP instruction. This feature provides a

technique for synchronization with high speed external events without

incurring the latency imposed by an interrupt response sequence.

Figure 21 depicts SLEEP timing.

, SLEEP mode is exited and the CPU begins the normal

1) and an individually enabled

0) and an individually enabled

UM005003-0703

Page 50

Z8018x

t

Family MPU User Manual

35

Op Code Fetch or Interrup

Acknowledge Cycle

Phi

INT1, NMI

A0

–

A19

HALT

M1

SLP 2nd Op Code

Fetch Cycle

T2

T3

SLP 2nd Op Code address

SLEEP mode

T1 T2 TS TS T1 T2 T3

FFFFFH

Figure 21. SLEEP Timing Diagram

IOSTOP Mode

IOSTOP mode is entered by setting the IOSTOP bit of the I/O Control

Register (ICR) to

1. In this case, on-chip I/O (ASCI, CSI/O, PRT) stops

operating. However, the CPU continues to operate. Recovery from

IOSTOP mode is by resetting the IOSTOP bit in ICR to

0.

SYSTEM STOP Mode

SYSTEM STOP mode is the combination of SLEEP and IOSTOP modes.

SYSTEM STOP mode is entered by setting the IOSTOP bit in ICR to

1

followed by execution of the SLP instruction. In this mode, on-chip I/O

and CPU stop operating, reducing power consumption. Recovery from

SYSTEM STOP mode is the same as recovery from SLEEP mode, noting

that internal I/O sources, (disabled by IOSTOP) cannot generate a

recovery interrupt.

UM005003-0703

Page 51

36

Z8018x

Family MPU User Manual

Low Power Modes (Z8S180/Z8L180 only)

The following section is a detailed description of the enhancements to the

Z8S180/L180 from the standard Z80180 in the areas of STANDBY, IDLE

and STANDBY QUICK RECOVERY modes.

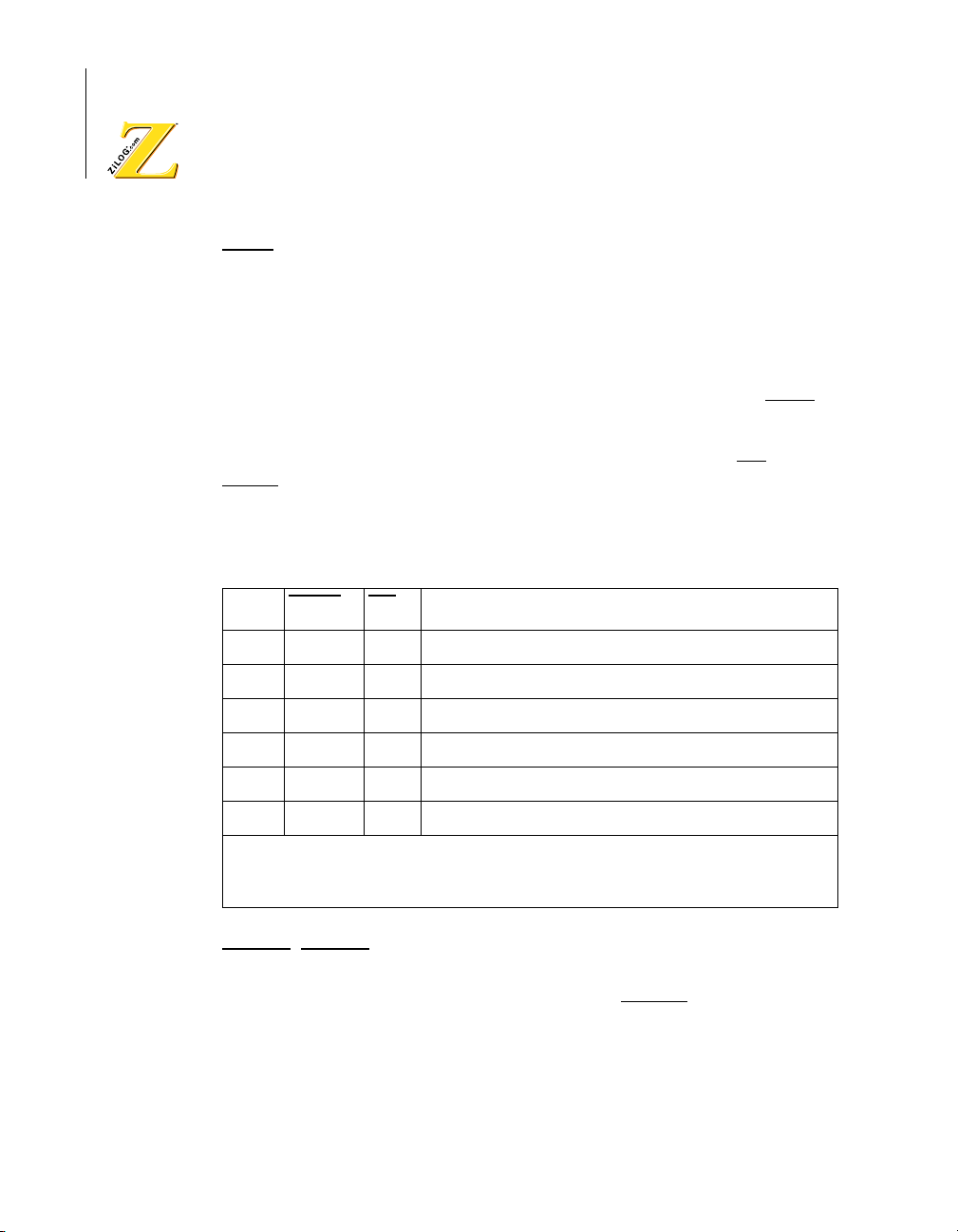

Add-On Features

There are five different power-down modes. SLEEP and SYSTEM STOP

are inherited from the Z80180. In SLEEP mode, the CPU is in a stopped

state while the on-chip I/Os are still operating. In I/O STOP mode, the onchip I/Os are in a stopped state while leaving the CPU running. In

SYSTEM STOP mode, both the CPU and the on-chip I/Os are in the

stopped state to reduce current consumption. The Z8S180 features two

additional power-down modes, STANDBY and IDLE, to reduce current

consumption even further. The differences in these power-down modes

are summarized in Table 5.

UM005003-0703

Page 52

Family MPU User Manual

Table 5. Power-Down Modes (Z8S180/Z8L180-Class Processors Only)

PowerDown

Modes CPU Core

On-Chip

I/O Osc. CLKOUT

Recovery

Source

Z8018x

37

Recovery Time

(Minimum)

SLEEP Stop Running Running Running RESET,

Interrupts

I/O STOP Running Stop Running Running By

Programming

SYSTEM

STOP

IDLE † Stop Stop Running Stop RESET,

STANDBY † Stop Stop Stop Stop RESET,

† IDLE and STANDBY modes are only offered in the Z8S180. The minimum recovery time can

be achieved if INTERRUPT is used as the Recovery Source.

Stop Stop Running Running RESET,

Interrupts

Interrupts,

BUSREQ

Interrupts,

BUSREQ

1.5 Clock

–

1.5 Clock

8 + 1.5 Clock

17

+ 1.5 Clock

2

(Normal

Recovery)

6

2

+ 1.5 Clock

(Quick Recovery)

STANDBY Mode

The Z8S180/Z8L180 is designed to save power. Two low-power

programmable power-down modes have been added:

•

STANDBY mode

•

IDLE mode

The STANDBY/IDLE mode is selected by multiplexing bits 1 and 3 of

the CPU Control Register (CCR, I/O Address =

1FH).

To enter STANDBY mode:

UM005003-0703

Page 53

38

Z8018x

Family MPU User Manual

1. Set bits 6 and 3 to 1 and 0, respectively.

2. Set the I/O STOP bits (bit 5 of ICR, I/O Address =

3. Execute the SLEEP instruction.

When the device is in STANDBY mode, it performs similar to the

SYSTEM STOP mode as it exists on the Z80180-class processors, except

that the STANDBY mode stops the external oscillator, internal clocks and

reduces power consumption to 50 mA (typical).

Because the clock oscillator has been stopped, a restart of the oscillator

requires a period of time for stabilization. An 18-bit counter has been

added in the Z8S180Z8L180 to allow for oscillator stabilization. When

the part receives an external IRQ or BUSREQ during STANDBY mode,

the oscillator is restarted and the timer counts down 2

acknowledgment is sent to the interrupt source.