Page 1

High-Performance 16-Bit Microcontrollers

ZNEO® CPU Core

User Manual

UM018809-0611

Copyright ©2011 Zilog®, Inc. All rights reserved.

www.zilog.com

Page 2

ZNEO® CPU Core

Warning:

User Manual

ii

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or

to request copies of publications, visit www.zilog.com

.

DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE

SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF

THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b)

support or sustain life and whose failure to perform when properly used in accordance with instructions for

use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any componen t in a li fe supp ort device o r syste m whose failure to p erform ca n be re asonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

Document Disclaimer

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications,

or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES

NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE

INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO

DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED

IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED

HEREIN OR OTHERWISE. The information contained within this document has been verified according

to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, eZ80, and ZNEO are trademarks or registered trademarks

of Zilog, Inc. All other product or service names are the property of their respective owners.

UM018809-0611

Page 3

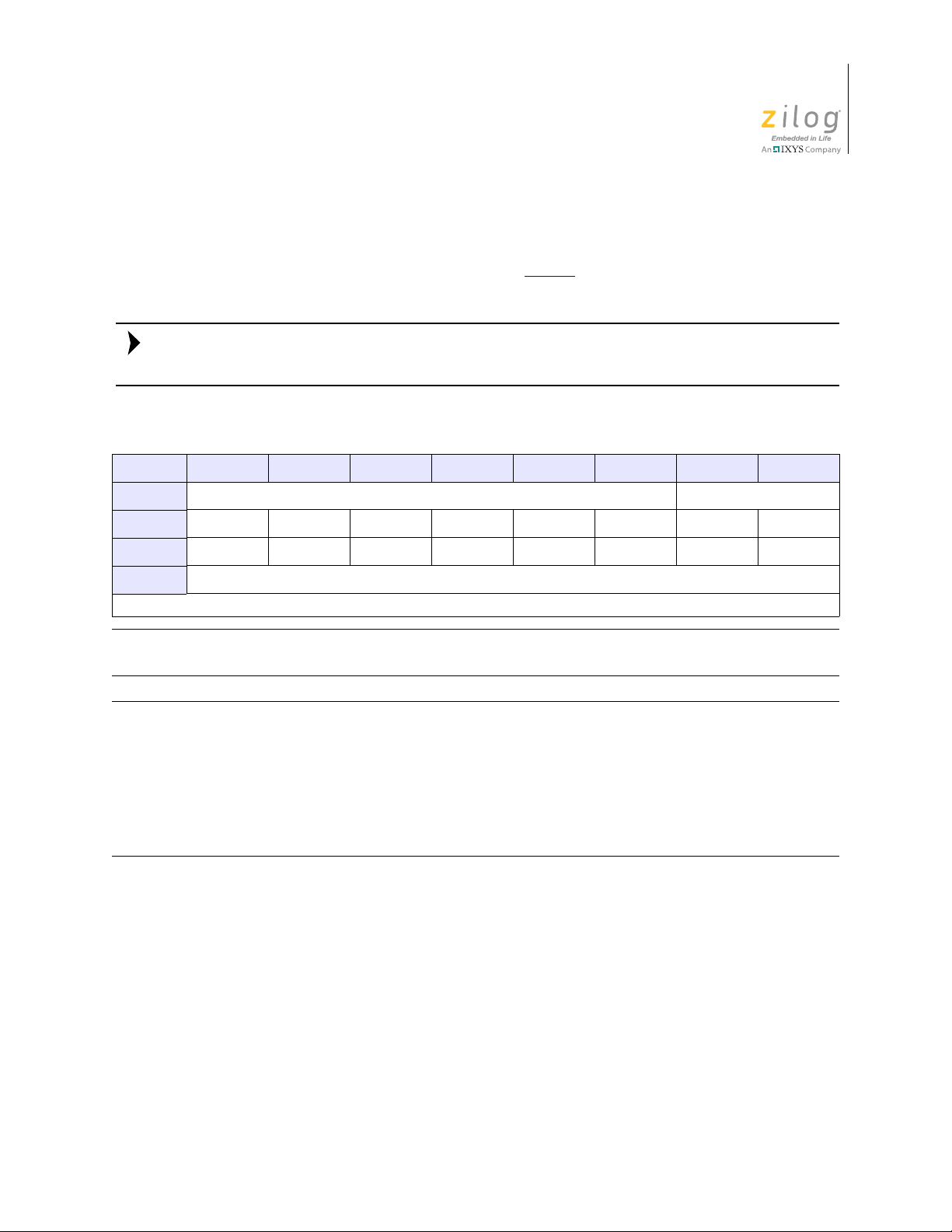

Revision History

Each instance in the Revision History table below reflects a change to this document from

its previous version. For more details, click the appropriate links in the table.

Revision

Date

May

2011

Aug

2010

Feb

2008

Sep

2007

Mar

2007

May

2006

Level Section Description Page

09 All Updated for style. All

Using the Program Counter as

a Base Address

LEA

SDIV Corrected After address in Example. 152

08 ADC, ADD Updated Syntax and Opcodes table. 68, 71

07 Flags Register (FLAGS) Updated User Flag description. 9

Loading an Effective Address Updated example. 33

System Exceptions Updated first paragraph. 49

Stack Overflow Updated second step for Stack Overflow

06 Instruction Set Reference Updated Examples for DEC Instruction. 65

05 Loading an Effective Address Change in instruction. 33

Flags Register (FLAGS), Vectored Interrupts, Instruction Set

Reference

04 Multiple Updated ZNEO trademark issues. Applied

Features, Control Registers,

Address Space, I/O Memory,

Direct Memory Addressing

CPU Control Register

(CPUCTL)

Memory Map, Jump Addressing

Internal Nonvolatile Memory,

Internal RAM

Direct Memory Addressing 16-bit address range is in highest and low-

®

ZNEO

Added note. 34

Added addressing mode offset description.

protection.

Updated with CIRQE bit. 9, 41, 65

current publications template.

Clarified size of address space. 1, 8, 15,

Clarified section. 13

Jump addresses FF_E000H and above

are reserved.

Clarified use of assembler address

ranges.

est 32K blocks, not 8K blocks.

CPU Core

User Manual

122

50

All

18, 29

16, 39

17, 17

29

iii

UM018809-0611 Revision History

Page 4

ZNEO® CPU Core

User Manual

iv

Date

Jan

2006

Revision

Level Section Description Page

03 Multiple Updated ZNEO trademark. All

02 Instruction Opcodes Moved opcodes beginning 0000 1011

and 0001 001+ to correct listing order.

(Opcode-to-instruction relationship is not

changed); corrected sequence of unimplemented opcodes and removed duplicate

row.

UDIV64 Corrected “After” register in example. 182

55

Revision History UM018809-0611

Page 5

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .iii

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ix

List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xi

Manual Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xiii

About This Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xiii

Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xiii

Manual Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xiii

Manual Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xiv

Safeguards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xvi

ZNEO

®

CPU Core

User Manual

v

Architectural Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Program Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Fetch Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Instruction Cycle Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Instruction Fetch Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Execution Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Program Counter Overflow Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Stack Pointer Overflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Flags Register (FLAGS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CPU Control Register (CPUCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Address Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Internal Nonvolatile Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Internal RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

I/O Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

I/O Memory Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

External Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Endianness . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Bus Widths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Assembly Language Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

ZNEO CPU Instruction Classes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

UM018809-0611 Table of Contents

Page 6

ZNEO® CPU Core

User Manual

vi

Operand Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Immediate Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Direct Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Memory Data Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Resizing Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Register-Indirect Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Loading an Effective Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Using the Program Counter as a Base Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Memory Address Decrement and Increment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Using the Stack Pointer (R15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Using the Frame Pointer (R14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Bit Manipulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Clearing Bits (Masked AND) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Setting Bits (Masked OR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Testing Bits (TM and TCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Jump Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Vectored Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Interrupt Enable and Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Returning From a Vectored Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Interrupt Priority and Nesting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Software Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Polled Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

System Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Program Counter Overflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Stack Overflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Divide-by-Zero . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Divide Overflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Illegal Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Software Traps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Instruction Opcodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Instruction Set Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Instruction Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Numerical and Expression Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Miscellaneous Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Example Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Mnemonic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table of Contents UM018809-0611

Page 7

®

ZNEO

CPU Core

User Manual

ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

ADD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

ATM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

BRK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

CALL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

CALLA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

CLR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

COM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

CP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

CPC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

CPCZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

CPZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

DEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

DI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

DJNZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

EI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

EXT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

HALT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

ILL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

INC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

IRET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

JP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

JPA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

JP cc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

LD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

LD cc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

LDES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

LEA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

LINK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

MUL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

NEG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

NOFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

NOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

POP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

POPF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

POPMLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

POPMHI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

PUSH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

PUSHF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

vii

UM018809-0611 Table of Contents

Page 8

ZNEO® CPU Core

User Manual

viii

PUSHMHI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

PUSHMLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

RET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

RL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

SBC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

SDIV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

SLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

SLLX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

SMUL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

SRA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

SRAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

SRL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

SRLX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

SUB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

TCM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

TM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

TRAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

UDIV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

UDIV64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

UMUL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

UNLINK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

WDT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

XOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Customer Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table of Contents UM018809-0611

Page 9

List of Figures

Figure 1. ZNEO CPU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 2. Flags Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 3. ZNEO CPU Memory Map (24 Significant Address Bits) . . . . . . . . . . . . . . 16

Figure 4. Endianness of Words and Quads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 5. Alignment of 16-Bit and 32-Bit Operations on 16-Bit Memories . . . . . . . . 20

Figure 6. Example Assembly Language Statement . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 7. Mapping of Register to Memory Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

ZNEO

®

CPU Core

User Manual

ix

Figure 8. Register-Indirect Memory Addressing Example . . . . . . . . . . . . . . . . . . . . . 33

Figure 9. Masked Logic Example: Clearing a Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 10. Effects of an Interrupt on the Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 11. Interrupt Vectoring Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

UM018809-0611 List of Figures

Page 10

ZNEO® CPU Core

User Manual

x

List of Figures UM018809-0611

Page 11

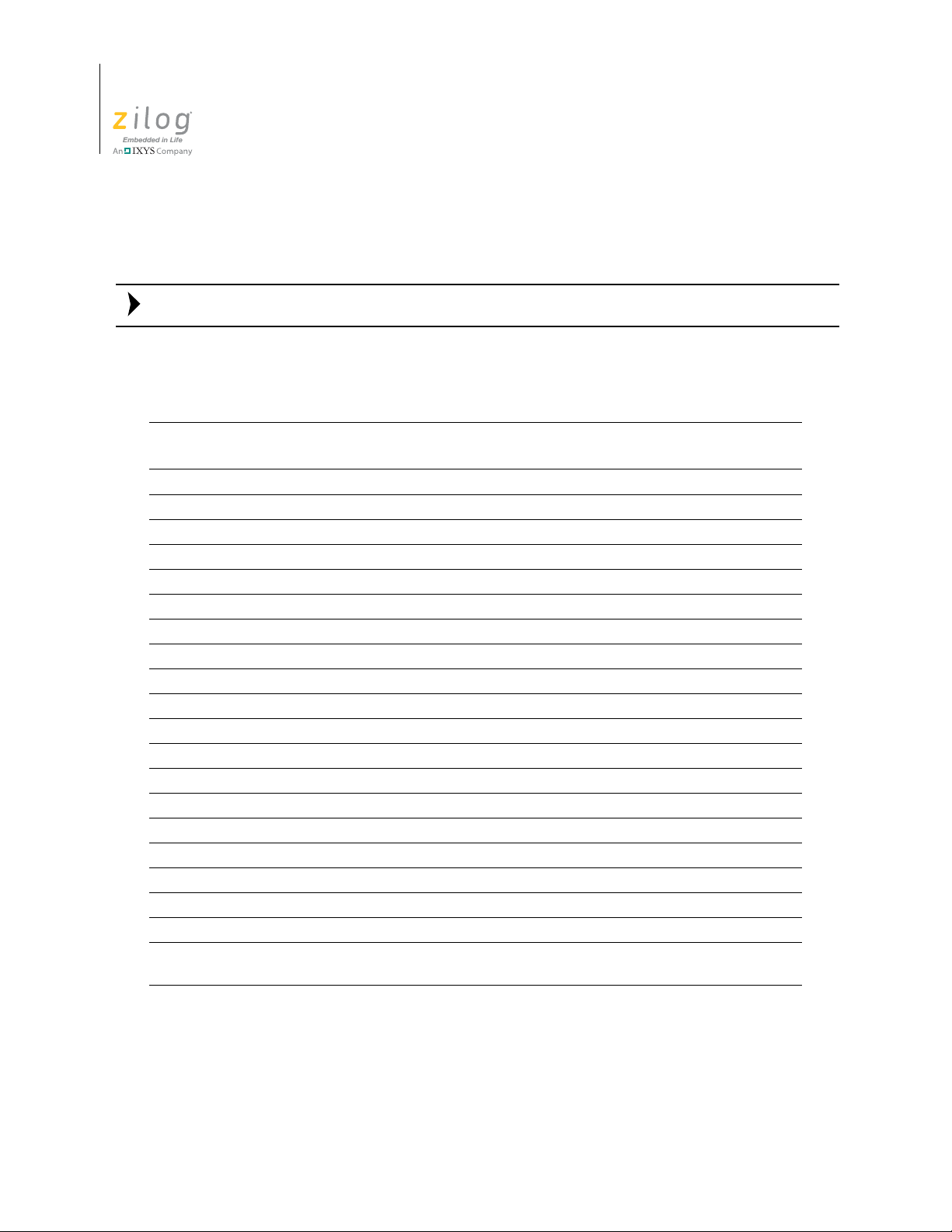

List of Tables

Table 1. Instruction Execution Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2. Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 3. Condition Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 4. CPU Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 5. Reserved Memory Map Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 6. Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 7. Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 8. Bit Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 9. Rotate and Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 10. Load Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 11. CPU Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 12. Program Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 13. 16-Bit Addressing (Object Code Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 14. Data Sizes for Memory Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 15. Relative Jump Offset Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 16. Bit Field Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 17. Operand Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 18. ZNEO CPU Instructions Listed by Opcode . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 19. Symbols Used in Expressions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 20. Abbreviations Used in Text and Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 21. Truth Table for AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 22. Truth Table for OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Table 23. Truth Table for XOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

ZNEO

®

CPU Core

User Manual

xi

UM018809-0611 List of Tables

Page 12

ZNEO® CPU Core

User Manual

xii

List of Tables UM018809-0611

Page 13

Manual Objectives

ZNEO

User Manual

®

CPU Core

xiii

This user manual describes the CPU architecture and instruction set common to all Zilog

devices that incorporate the ZNEO

internal peripherals and memory, and I/O registers for each device, refer to the device-specific Product Specification.

About This Manual

Zilog® recommends you to read and understand everything in this manual before setting

up and using the product. We have designed this manual to be used either as an instructional manual or a reference guide to important data.

Intended Audience

This document is written for Zilog customers with experience in writing microprocessor,

assembly code, and compilers. Some introductory material is included to help new customers who are less familiar with this device.

Manual Organization

®

CPU. For complete information about interfaces,

This user manual is divided into nine chapters to describe the following device characteristics:

Architectural Overview

Describes the ZNEO CPU’s features and benefits, architecture, and control registers.

Address Space

Introduces the ZNEO CPU’s unified memory address space, with a memory map illustrating how the available memory areas are addressed.

Assembly Language Introduction

Briefly introduces some of the assembly language terminology used in the following chapters and lists ZNEO CPU instructions in functional groups.

Operand Addressing

Explains ZNEO CPU operand addressing and data sizes.

UM018809-0611 Manual Objectives

Page 14

ZNEO® CPU Core

User Manual

xiv

Interrupts

Introduces the use of vectored and polled interrupts to service interrupt requests from

peripherals or external devices.

System Exceptions

Explains system exceptions and the events which cause the processor overflow, stack

overflow, divide-by-zero, divide overflow, and illegal instruction.

Software Traps

Explains the software trap instruction.

Instruction Opcodes

Numerical list of ZNEO CPU instruction opcodes and syntax.

Instruction Set Reference

Alphabetical list of ZNEO CPU instruction descriptions, with syntax and opcodes.

Manual Conventions

The following manual conventions provide clarity and ease of use.

Notations specific to assembly language, address operands, opcodes, and instruction

descriptions are explained in the chapters discussing those topics.

Courier Typeface

User-typed commands, code lines and fragments, bit names, equations, hexadecimal

addresses, and executable items are distinguished from general text by the use

Courier typeface. Where the use of the font is not indicated (for example, Index)

of the

the name of the entity is presented in upper case.

For example, Internal RAM begins at

Binary Values

Binary values are designated by an uppercase ‘B’ suffix. For readability, underscore ‘_’

characters separate large values into four-digit groups, except in program statements.

For example, 8-bit binary value

FFFF_0000H.

0100_0010B.

Hexadecimal Values

Hexadecimal values are designated by an uppercase ‘H’ and appear in the Courier typeface. For readability, underscore ‘_’ characters separate lar ge values into four-digit groups,

except in program statements as illustrated in the below examples:

Manual Objectives UM018809-0611

Page 15

®

ZNEO

Example 1: R1 is set to F8H.

Example 2: 32-bit hexadecimal value 1234_5678H

CPU Core

User Manual

Bit Numbering

Bits are numbered in order of significance, from 0 to n–1 where 0 indicates the least significant bit and n indicates the total number of bits.

For example, 8 bits of a memory byte are numbered from 0 to 7.

Registers, memory bytes, and binary values are illustrated with the highest-numbered bit

on the left and the lowest-numbered bit on the right.

xv

For example, Bit 6 of the value

0100_0000B is 1.

Brackets

In text, square brackets, [ ], indicate one or more bits of a register, memory location, or

bus. A colon between bit numbers indicates a range of bits. A comma between bit numbers

indicates individual bits as given below:

Example 1: ADDR[31:0] refers to bit 31 through bit 0 of the ADDR bus or memory loca-

tion. ADDR[31] is the most significant bit (msb), and ADDR[0] is the least significant bit

(lsb). ADDR[31:24] is the most significant byte (MSB), and ADDR[7:0] is the least significant byte (LSB).

Example 2: If the value of R1[7:0] is 0100_0010B, the bits R1[6,2] are both 1.

Braces

The curly braces, { }, indicate a single register, memory address or bus created by concatenating combination of smaller registers, addresses, buses or individual bits.

For example, the 32-bit effective address {

hexadecimal value (

FFFFH) and a 16-bit direct address. FFFFH is the most significant

FFFFH, ADDR[15:0]} consists of a 16-bit

word (16 bits) and ADDR[16:0] is the least significant word of the resulting 32-bit

address.

Use of the Words Set, Reset and Clear

The word set indicates a 1 is stored in a register or memory bit or flag. The words reset or

clear indicates a 0 is stored in a register or memory bit or flag.

Use of the Terms LSB, MSB, lsb and msb

In this document, the terms LSB and MSB, when appearing in upper case, mean least significant byte and most significant byte, respectively. The lowercase forms (lsb and msb)

mean least significant bit and most significant bit, respectively.

UM018809-0611 Manual Objectives

Page 16

ZNEO® CPU Core

Caution:

Warning:

User Manual

xvi

Use of Initial Uppercase Letters

Initial uppercase letters designate settings, modes, and conditions in general text:

Example 1: Stop mode.

Example 2: The receiver forces the SCL line to Low.

Example 3: The Master can generate a Stop condition to abort the transfer.

Use of All Uppercase Letters

The use of all uppercase letters designates assembly mnemonics or the names of states and

hardware commands.

Example 1: The bus is considered BUSY after the Start condition.

Example 2: A START command triggers the processing of the initialization sequence.

Safeguards

It is important to understand the following safety terms:

Indicates that a procedure or file may become corrupted if you do not follow directions.

Indicates that you are in a situation that could cause bodily injury. Before you work on

any equipment, be aware of the hazards involved with electrical circuitry and be familiar with standard practices for preventing accidents.

Manual Objectives UM018809-0611

Page 17

Architectural Overview

Zilog’s ZNEO CPU meets the continuing demand for faster and more code-efficient

microcontrollers. ZNEO CPU’s architecture greatly improves the execution

code developed using higher-level programming languages like ‘C’ language

Features

The key features of ZNEO CPU architecture include:

•

Highly efficient register-based architecture with sixteen 32-bit registers. All register

operations are 32 bits wide

ZNEO

User Manual

efficiency of

.

®

CPU Core

1

•

Up to 4 GB linear address space (16 MB on current devices) with multiple internal

and external memory and I/O buses

•

Short 16-bit addressing for internal RAM, I/O, and 32K of nonvolatile memory

•

Instructions using memory can operate on 8-bit, 16-bit, or 32-bit values

•

Support for 16-bit memory paths (internal and external)

•

Pipelined instruction fetch, decode, and execution

•

Bus arbiter supports simultaneous instruction and memory access (when possible)

Other features of the ZNEO CPU include:

•

Direct register-to-register architecture allows each 32-bit register to function as an

accumulator. This improves the execution time and decreases the memory required for

programs.

•

Expanded stack support:

– Push/Pop instructions use one 32-bit register as Stack Pointer

– Single-instruction push and pop of multiple registers

– Stack Pointer overflow protection

– Predecrement/postincrement Load instructions simplify the use of multiple stacks

– Link and Unlink operations with enhanced Frame Pointer-based instructions for

efficient access to arguments and local variables in subroutines

•

Program Counter overflow protection

•

User-selectable bus bandwidth control for DMA and CPU sharing

UM018809-0611 Architectural Overview

Page 18

ZNEO® CPU Core

User Manual

2

Program Control

ZNEO CPU is controlled by a program stored in memory as object code. An object code is

a sequence of numerical opcode and operand bytes. An opcode specifies an instruction to

perform while operands specify the data addresses to be operated upon. Numerical object

code is rarely used to write programs. Instead, programs is written in a symbolic assembly

language using easily remembered (mnemonic) instructions. A program called an assembler translates assembly language into object code.

This user manual provides details about using ZNEO CPU instructions in both object code

and assembly language. Those interested in writing assembly language can skip object

code details handled by the assembler.

Programmers using high-level languages like ‘C’ require this manual while writing optimized routines in assembly language. Otherwise, the compiler or interpreter’s documentation should describe processor-specific details affecting program operation.

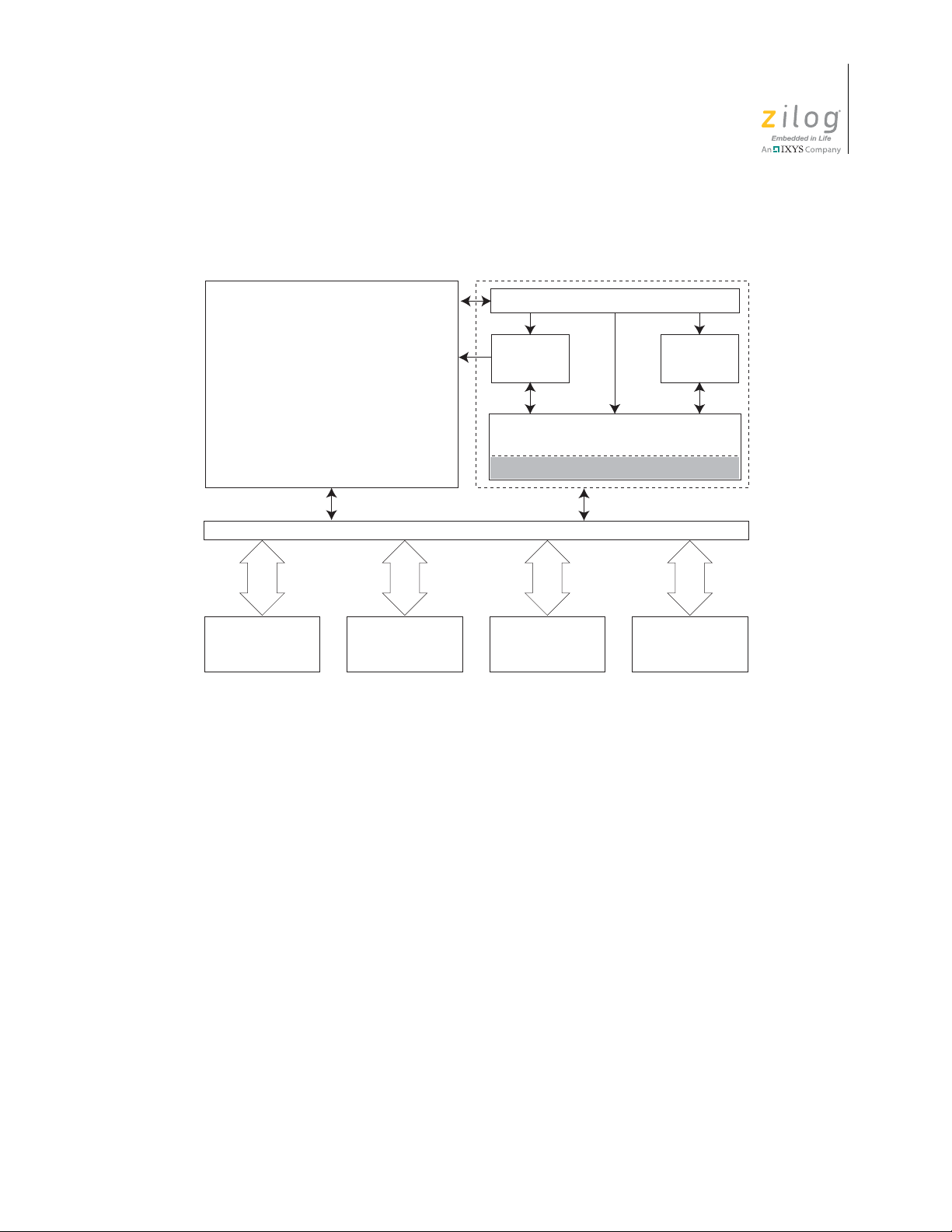

Processor Block Diagram

The ZNEO CPU consists of following two major functional blocks:

•

Fetch Unit

•

Execution Unit

The Fetch and Execution units access memory through a bus arbiter. The Execution Unit

is subdivided into the Instruction State Machine, Program Counter, Arithmetic Logic Unit

(ALU), and ALU registers. Figure 1 on page 3 displays the ZNEO CPU architecture.

Architectural Overview UM018809-0611

Page 19

ZNEO

Fetch Unit

Instruction and

Operand Fetch

Instruction State Machine

Arithmetic Logic Unit (ALU)

32-bit ALU Registers, R0-R15

Bus Arbiter

16

Internal

Non-volatile

Memory

16

Internal

RAM

8/16

Internal I/O

8/16

External

Memory

Interface

Program

Counter

Control

Registers

Execution Unit

User Manual

®

CPU Core

3

Fetch Unit

The Fetch Unit’s primary function is to fetch opcodes and operand words (including

immediate data) from memory. The Fetch Unit also fetches interrupt vectors. The Fetch

Unit is pipelined and operates semi-independently from the execution unit. This Unit performs a partial decoding of the opcode to determine the number of bytes to fetch for the

operation.

The Fetch Unit operation sequence functions as follows:

1. Fetch the first 2-byte opcode word.

2. Determine number of remaining opcode and operand words (one or two).

3. Fetch the remaining opcode and operand words.

4. Present the opcode and operands to the Instruction State Machine.

A ZNEO CPU instruction is always 1, 2, or 3 words long, including operands, and must be

aligned on an even address.

Figure 1. ZNEO CPU Block Diagram

UM018809-0611 Architectural Overview

Page 20

ZNEO® CPU Core

Note:

User Manual

4

Execution Unit

The Execution Unit performs the processing functions required by the instruction opcodes

and operands which it receives from the Fetch Unit.

Instruction State Machine

The Instruction State Machine is the controller for the ZNEO CPU Execution Unit. After

the initial operation decode by the Fetch Unit, the Instruction State Machine takes over

and completes the instruction. The Instruction State Machine generates effective addresses

and controls memory read and write operations.

Program Counter

The Program Counter contains a counter and adder to monitor the address of the current

instruction and calculates the next instruction address. According to the number of bytes

fetched by the Fetch Unit, the Program Counter increments automatically. The adder

increments and handles Program Counter jumps for relative addressing. The initial value

of the program counter is programmable through the RESET vector.

refer to the ZNEO product specification that is specific to your device for the RESET vector location.

Programs cannot address the Program Counter directly but the instruction

LEA Rd, 4(PC) can be used to load the current Program Counter value (the next instruc-

tion address) into an ALU Register. The JP, CALL, and related instructions are used to

alter the program counter value.

The I/O memory register described in Program Counter Overflow Register on page 9 provides access to the program counter overflow feature.

Arithmetic Logic Unit

The Arithmetic Logic Unit (ALU) performs arithmetic and logical operations on data.

arithmetic operations including addition, subtraction, and multiplication. Logical operations include binary logic operations, bit shifting, and bit rotation.

ALU Registers

The ZNEO CPU provides 16 highly efficient 32-bit registers associated with the ALU.

The 16 ALU registers are named from R0 to R15.

These registers have the following characteristics:

•

The CPU can access ALU registers more quickly than ordinary internal or external

memory.

Architectural Overview UM018809-0611

Page 21

®

Note:

ZNEO

•

All 32 bits of a source or destination ALU Register are used for arithmetic and logical

operations.

•

When an 8-bit or 16-bit memory read is performed, the value is extended to 32-bits in

the destination register. Unsigned (zero) or Signed extension can be specified.

•

When an 8-bit or 16-bit memory write is performed, the source register’ s value is trun-

cated (only the least significant 8 or 16 bits are stored in memory.)

•

The CALL, IRET, LINK, POP, POPM, PUSH, PUSHM, RET, TRAP, and UNLINK

instructions; system interrupts; and exceptions use Register R15 as the Stack Pointer.

If not used, R15 behaves like any other ALU Register.

•

The LINK, UNLINK, and some LD operations use Register R14 as a Frame Pointer. If

not used, R14 behaves like any other ALU Register.

CPU Core

User Manual

5

Instruction Cycle Time

Instruction cycle times vary from instruction to instruction. Instructions are pipelined

which means the current instruction executes while the next instruction is being fetched.

This allows higher performance at a specific clock speed.

Instruction Fetch Cycles

The following equation is used to calculate the minimum number of cycles required to

fetch an instruction into the CPU:

Fetch Cycles = (bus_wait_states + 1) opcode_bytes/bus_bytes

In the above equation, the following points are true:

•

Bus wait states is configured on a bus to accommodate memory specifications. The

number of wait states is added to each memory read or write on that bus.

For details about wait states, refer to the ZNEO product specification that is specific to

your device .

•

The opcode bytes value can be 2, 4 or 6, depending on the instruction. Immediate

operands, if any, are included in the opcode fetch, so they do not affect execution

cycles.

•

The bus bytes value can be 1 or 2, for fetches from an 8-bit or 16-bit bus, respectively.

For more details, see the Bus Widths

UM018809-0611 Architectural Overview

section on page 19.

Page 22

ZNEO® CPU Core

Note:

User Manual

6

Execution Cycles

Instructions always begin at an even address; therefore, instruction fetches are not subject

to uneven alignment delays.

An instruction fetch delay cycle can occur if the Fetch and Execution Units request access

to the same bus on the same cycle. In this case, the bus arbiter gives precedence to the

Execution Unit. This kind of delay can be avoided by storing instructions and data in different memory spaces; for example, instructions in ROM or Flash and data in RAM.

The minimum instruction execution time for most CPU instructions is one system clock

cycle. Additional cycles are required for shift, multiply, divide operations, and operations

which read or write memory locations. Table 1 lists minimum Execution Unit cycle times

for the various instructions. The symbol bus_time is described in the text following the

table, as other factors that affect execution of some instructions.

Table 1. Instruction Execution Cycles

Instruction Operand Types Minimum Execution Unit Cycles

LD, LEA Immediate, Register-to-Reg-

ister

To or From Memory 1

EXT, LDES, ATM, BRK, DI, DJNZ,

EI, HALT, IRET, NOP, RET, STOP

PUSH, POP,

PUSHF, POPF

PUSHM, POPM — Variable

CLR Register 1

CP, CPZ, TM, TCM Immediate, Register-to-Reg-

ADC, ADD, AND, COM, CPC,

CPCZ, DEC, INC, NEG, OR, SBC,

SUB, XOR

—1

—1

Memory 1

ister

To or From Memory 1 +

Immediate, Register-to-Reg-

ister

Memory to Register 1 +

1

bus_time

bus_time

bus_time

1

bus_time

1

bus_time

Register to Memory 2 bus_time

Architectural Overview UM018809-0611

Page 23

®

ZNEO

Table 1. Instruction Execution Cycles (Continued)

Instruction Operand Types Minimum Execution Unit Cycles

MUL, SMUL, UMUL Operands 1_0000H 10

Operands 1_0000H 18

SDIV Destination 1_0000H 17 if result is positive, 18 if negative

Destination 1_0000H 33 if result is positive, 34 if negative

UDIV Destination 1_0000H 17

Destination 1_0000H 33

UDIV64 — 34

SRA, SRL, SLL, RL — (src/8) + (src % 8)

CPU Core

User Manual

7

SRAX, SRLX, SLLX — src + 1

JP, JP cc, CALL, NOFLAGS, Extend

Prefix

ILL, TRAP — 1 + 4

—0

IROM_bus_time

stack_bus_time

+ 6

+ next_instruction_words

LINK — 2 + 4 stack_bus_time

UNLINK — 1 + 4 stack_bus_time

Execution cycles can be affected by the following factors:

•

The symbol bus_time stands for the time to read or write a value to the addressed

memory bus, as given by the formula below:

(bus_wait_states + 1) ceiling(data_bytes/bus_bytes)

In the above equation, the following points can be considered:

– Bus wait states is configured for a bus to accommodate memory specifications.

The number of wait states is added to each memory read or write on that bus.

–The ceiling function rounds up to the nearest integer. This accounts for a 1-byte

access on a 2-byte bus, which takes a full memory access cycle, not 1/2 cycle.

–The data bytes value can be 1, 2 or 4, depending on the size of the addressed data

(for direct or register-indirect addressed memory).

–The bus bytes value can be 1 or 2, for fetches from an 8-bit or 16-bit bus, respec-

tively.

An unaligned 16-bit or 32-bit read or write requires additional cycles. For more

details, see the Bus Widths

section on page 19.

UM018809-0611 Architectural Overview

Page 24

ZNEO® CPU Core

Note:

Note:

Note:

User Manual

8

•

•

For details about wait states, refer to the ZNEO product specification that is specific to

your device .

Control Registers

For LD and LEA instructions, a delay cycle is inserted if a register is loaded immediately before it is used for the base address in a register-indirect instruction.

If execution of an instruction ends before all the next instruction words are fetched,

the Execution Unit delays for the number of cycles required by the Fetch unit to complete the instruction fetch. After an ILL or TRAP instruction executes, the entire next

instruction must be fetched.

The ZNEO CPU and internal peripheral control registers are accessed in the I/O memory

space starting at

FF_E000H (24-bit address space devices). Table 2 lists control registers

common to all Zilog devices that incorporate the ZNEO CPU. In this table, “X” indicates

an undefined hex digit value.

For complete information about peripheral control registers for a particular device, refer to

the device specific Product Specification.

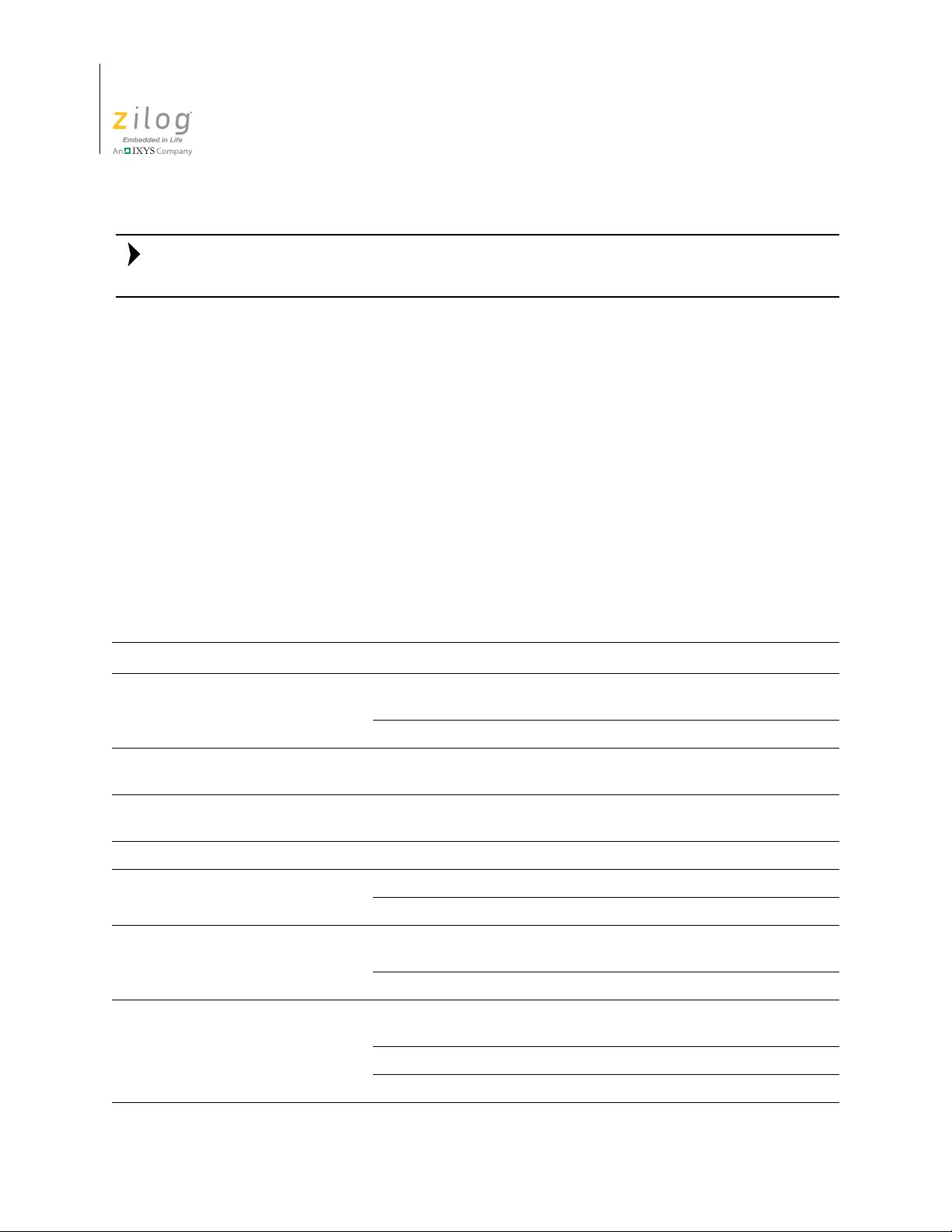

Table 2. Control Registers

Reset Value

Address (Hex) Register Description Mnemonic

FF_E004–FF_E007 Program Counter Overflow PCOV FFFFFFFF

FF_E008–FF_E00B Reserved — xxxxxxxx

FF_E00C–FF_E00F Stack Pointer Overflow SPOV 00000000

FF_E010 Flags FLAGS xx

FF_E011 Reserved — xx

FF_E012 CPU Control CPUCTL FF

(Hex)

I/O memory locations can be accessed using a 16 bit address operand. For more details, see

the Direct Memory Addressing section on page 29.

Architectural Overview UM018809-0611

Page 25

Program Counter Overflow Register

CZSVBF1 CIRQE IRQE Flags Register

Bit

0

Bit

7

Master Interrupt Enable

Chained Interrupt Enable

User Flag 1

Blank Flag

Overflow Flag

Sign Flag

Zero Flag

Carry Flag

The Program Counter Overflow Register (PCOV) implements program counter overflow

protection. For more details, see the Program Counter Overflow

Stack Pointer Overflow

The Stack Pointer Overflow Register (SPOV) is used to provide stack pointer overflow

protection. For more details, see the Stack Overflow

IRET, POP, PUSH, RET and TRAP instructions, system interrupts and exceptions use the

ALU Register. R15 is used as the Stack Pointer.

Flags Register (FLAGS)

®

ZNEO

section on page 50.

section on page 50. CALL, ILL,

CPU Core

User Manual

9

This byte register contains the status information regarding the most recent arithmetic,

logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits

of status information that are set or cleared by CPU operations. Five of the bits (C, Z, S, V

and B) can be tested with conditional jump instructions. The

rupt Enable flag, and the CIRQE bit is the Chained Interrupt Enable flag. Figure 2 displays

the flags and their bit positions in the Flags Register.

IRQE bit is the Master Inter-

Figure 2. Flags Register

Interrupts, System Exceptions, and the software Trap (TRAP) instruction write the value

of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction

restores the value saved on the stack into the Flags Register.

UM018809-0611 Architectural Overview

Page 26

ZNEO® CPU Core

User Manual

10

Flag settings depend on the data size of the result, which can be 8 bits (Byte), 16 bits

(Word), or 32 bits (Quad, the default). For instructions with destinations in memory, the

mnemonic suffix determines the destination size. If the destination is a register, Flags are

based on the 32-bit result. For more information, see the Memory Data Size

section on

page 30.

Carry Flag

The Carry (C) flag is 1 when the result of an arithmetic operation generates a carry out of

or a borrow into the most significant bit (msb) of the data. Otherwise, the Carry flag is 0.

Some bit rotate or shift instructions also affect the Carry flag. Bit [31] is considered msb

for register destinations; the msb for a memory destination depends on the data size.

Zero Flag

For arithmetic and logical operations, Zero (Z) flag is 1 if the result is 0. Otherwise, the

Zero flag is 0. If the result of testing bits is

0, Zero flag is 1; otherwise, the Zero flag is 0.

Also, if the result of a rotate or shift operation is

0, the Zero flag is 1; otherwise, the Zero

flag is 0. The test considers 32 bits for a register destination or the destination size for a

memory destination.

Sign Flag

The Sign (S) flag stores the value of the most significant bit (msb) of a result following an

arithmetic, logical, rotate, or shift operation. For signed numbers, the ZNEO CPU uses

binary two’s complement to represent the data and perform the arithmetic operations. A 0

in the msb position identifies a positive number; therefore, the Sign flag is also 0. A 1 in

the most significant position identifies a negative number; therefore, the Sign flag is also

1. Bit [31] is considered msb for register destinations; the msb for a memory destination

depends on the data size.

Overflow Flag

For signed arithmetic, rotate or shift operations, the Overflow (V) flag is 1 when the result

is greater than the maximum possible number or less than the minimum possible number

which is represented with the specified data size in signed (two’s complement) form. For

signed data size ranges, see Table 14

occurs. Following logical operations, the Overflow flag is 0.

Following addition operations, the Overflow flag is 1 when the operands have the same

sign, but the result has the opposite sign. Following subtraction operations, the Overflow

flag is 1 if the two operands are of opposite sign and the sign of the result is same as the

sign of the source operand. Following shift/rotation operations, the Overflow flag is 1 if

the sign bit of the destination changed during the last bit shift iteration.

on page 32. The Overflow flag is 0 if no overflow

Architectural Overview UM018809-0611

Page 27

®

ZNEO

CPU Core

User Manual

Blank Flag

For some arithmetic, logical, and load operations, the Blank (B) flag is set to 1 if a tested

operand value is 0 before the operation. Otherwise,

operands might be tested, but which operands are tested depends on the operation being

performed. See the instruction descriptions for details.

B is 0. Both source and destination

11

Unlike other flags, the

B flag can be altered by POP and some LD instructions. 8-bit or 16-

bit memory operands are tested after unsigned or signed extension, depending on the

instruction

The

the following statement executes,

. For more information, see the Resizing Data section on page 31.

B flag is useful for operations involving a null-terminated strings. For example, after

Z is set if the tested byte is a carriage return (0DH), or B

is set if the byte is zero.

CP.B (R6), #0DH

User Flag

The User Flag (F1) are available as general-purpose status bits. The User Flag is unaffected by arithmetic operations and must be set or cleared by instructions. The User Flag

must not be used with conditional Jumps. The User Flag is 0 after initial power-up or

Reset.

Chained Interrupt Enable Flag

The Chained Interrupt Enable flag (CIRQE) is used to enable or disable chained-interrupt

optimization, which allows program control to pass directly from one interrupt service

routine to another while omitting unneeded stack operations. For more information, see

the Returning From a Vectored Interrupt

Whenever a vectored interrupt or system exception occurs, the previous state of the

flag is copied to

CIRQE after the Flags Register is pushed onto the stack. This disables

interrupt chaining if interrupts are globally disabled (

rupt or system exception occurs.

section on page 44.

IRQE

IRQE=0) when a nonmaskable inter-

The

CIRQE flag is unaffected by other operations, but it may be set or cleared by instruc-

tions, if desired. The

CIRQE flag cannot be used with conditional Jumps. The CIRQE flag

is 0 after initial power-up or Reset.

Master Interrupt Enable Flag

The Master Interrupt Enable bit (IRQE) globally enables or disables interrupts. For more

information, see the Interrupts

chapter on page 41.

Condition Codes

The C, Z, S, V, and B flags control the operation of the conditional jump (JP cc) instruc-

tions. Sixteen frequently useful functions of the flag settings are encoded in a 4-bit field

UM018809-0611 Architectural Overview

Page 28

ZNEO® CPU Core

Note:

User Manual

12

called the condition code (cc), which are assembled into each conditional jump opcode.

Table 3 summarizes condition codes and their assembly language mnemonics.

Some binary condition codes are expressed by more than one mnemonic.

The result of the flag test operation determines if the conditional jump executes.

Table 3. Condition Codes

Assembly

Binary Hex

0000 0 B Blank B = 1

0001 1 LT Less Than (S XOR V) = 1

0010 2 LE Less Than or Equal (Z OR (S XOR V)) = 1

0011 3 ULE Unsigned Less Than or Equal (C OR Z) = 1

0100 4 OV Overflow V = 1

0101 5 MI Minus S = 1

0110 6 ZZero Z = 1

0110 6 EQ Equal Z = 1

0111 7 CCarry C = 1

0111 7 ULT Unsigned Less Than C = 1

1000 8 NB Not Blank B = 0

1001 9 GE Greater Than or Equal (S XOR V) = 0

1010 A GT Greater Than (Z OR (S XOR V)) = 0

1011 B UGT Unsigned Greater Than (C OR Z) = 0

1100 C NOV No Overflow V = 0

1101 D PL Plus S = 0

1110 E NZ Non-Zero Z = 0

1110 E NE Not Equal Z = 0

1111 F NC No Carry C = 0

1111 F UGE Unsigned Greater Than or

Mnemonic Definition

Equal

Flag Test Operation

(Jump if T rue)

C = 0

Architectural Overview UM018809-0611

Page 29

®

Note:

ZNEO

CPU Core

User Manual

CPU Control Register (CPUCTL)

Bits [1:0] of the CPU Control Register (see Table 4 on page 13) control access to the

ZNEO CPU buses through DMA bandwidth selection.

For more details about the available peripheral control and data registers, and additional

information about DMA operation, refer to the device specific Product Specification.

Table 4. CPU Control Register

Bit 7 6 5 4 3 2 1 0

Field

Reset

R/W

Address

Note: R = Read-only; R/W = Read/Write; R/W0 = Read/Write to 0.

11111111

RRRRRRR/WR/W

Reserved DMABW

FFFF_E012H

13

Bit

Position Description

[7:2] Reserved; must be zero.

[1:0] DMA Bandwidth Selection (DMABW)

The ZNEO CPU can be configured to support four levels of Direct Memory Access (DMA) Con troller bus bandwidth. Write one of the fo llowing values to DMABW[1:0] to se lect the portion of

bus bandwidth allocated to DMA operations:

00 = DMA can consume 100% of the bus bandwidth

01 = DMA is allowed one transaction for each CPU operation

10 = DMA is allowed one transaction for every two CPU operations

11 = DMA is allowed one transaction for every three CPU operations

UM018809-0611 Architectural Overview

Page 30

ZNEO® CPU Core

User Manual

14

Architectural Overview UM018809-0611

Page 31

Address Space

The ZNEO CPU has a unique memory architecture with a unified address space. It supports memory and I/O up to four buses:

•

Internal Non-Volatile Memory (Flash, EEPROM, EPROM, or ROM)

•

Internal RAM

•

Internal I/O Memory (internal peripherals)

•

External Memory (and/or memory-mapped peripherals)

The ZNEO CPU Fetch Unit and Execution Unit can access separate buses at the same

time. The CPU can access memories with either 8-bit or 16-bit bus widths. ZNEO CPU

uses 32-bit addressing internally. Therefore, the CPU is capable of addressing up to 4 GB

of addresses.

ZNEO

User Manual

®

CPU Core

15

Current ZNEO CPU products ignore address bits [31:24], providing a 24-bit address space

with 16 MB (16,777,216 bytes) of unique memory addresses. Address bits [31:24] must

be written appropriately for the addressed space to allow for possible future expansion.

The CPU also provides instructions which use 16-bit addressing. 16-bit addresses are sign

extended by the CPU to access the highest and lowest 32 KB of the available address

space.

Example: The 16-bit address FEFFH resolves to FF_FEFFH in the 24-bit address space.

Most CPU instructions also use Arithmetic and Logic Unit (ALU) registers for either

source or destination data. See the ALU Registers

The ZNEO CPU address space includes the following features:

•

Memory Map

•

Internal Nonvolatile Memory

•

Internal RAM

•

I/O Memory

•

External Memory

•

Endianness

•

Bus Widths

section on page 4.

UM018809-0611 Address Space

Page 32

ZNEO® CPU Core

Internal Non-Volatile

External Memory Interface

00_0000H

FF_8000H

FF_E000H

FF_FFFFH

FF_xxxxH

Data Addresses

Jump Addresses

(Execution Unit)

(Fetch Unit)

Internal Bus (One of Three)

External Bus

00_xxxxH

00_0xxxH

FF_xxxxH

xxxxH

Device-Specific Boundary

16-Bit Address Sp ace

00_7FFFH

Internal I/O &

Control Registers

Option Bits and Vectors

Memory

External Memory Interface

Internal RAM

Reserved

User Manual

16

Memory Map

Figure 3 displays a memory map of the ZNEO CPU. It displays the location of internal

nonvolatile memory, internal RAM, and internal I/O Memory. External memory can be

accessed at addresses not occupied by internal memory or I/O.

Figure 3. ZNEO CPU Memory Map (24 Significant Address Bits)

Address Space UM018809-0611

Page 33

To determine the amount of internal RAM and internal nonvolatile memory available for

Note:

Note:

the specific device and for details about the available option bits and vectors, refer to the

ZNEO product specification that is specific to your device .

Internal Nonvolatile Memory

Internal nonvolatile memory consists of executable program code, constants, and data.

The ZNEO CPU assembler provides configurable address range mnemonics (ROM and

EROM) that can be specified to locate data and program elements in nonvolatile memory.

ROM selects nonvolatile memory in the 16-bit address space, while EROM selects nonvolatile memory in the 32-bit address space. For more details about data space and segment definitions, refer to the assembler documentation.

ZNEO

User Manual

®

CPU Core

17

For each product within the ZNEO CPU family, a block of memory beginning at address

00_0000H is reserved for option bits and system vectors (RESET, trap, interrupts, System

Exceptions; etc.). Table 5 provides an example reserved memory map for a ZNEO CPU

product with 24 interrupt vectors.

Internal RAM

Internal RAM is employed for data and stacks. However, internal RAM can also contain

program code for execution. Most ZNEO CPU devices contain some internal RAM. The

base (lowest address) and top (highest address) of internal RAM are a function of the

amount of internal RAM available.

Table 5. Reserved Memory Map Example

Memory Address (Hex) Description

00_0000–00_0003 Option Bits

00_0004–00_0007 RESET Vector

00_0008

00_000C–00_000F Reserved

00_0010–00_006F Interrupt Vectors

–

00_000B System Exception Vector

To determine the amount and location of internal RAM, refer to the ZNEO product specification that is specific to your device .

UM018809-0611 Address Space

Page 34

ZNEO® CPU Core

Note:

User Manual

18

I/O Memory

The ZNEO CPU assembler provides a configurable address range mnemonic (RAM) that

can be specified to locate data and (possibly) program elements in the RAM space

accessed using 16-bit addressing. For more details about data space and segment definitions, refer to the assembler documentation.

ZNEO CPU supports 8 KB (8,192 bytes) of internal I/O Memory space located at

addresses

addresses are reserved for control of the ZNEO CPU, the on-chip peripherals, and the I/O

ports.

For descriptions of the peripheral and I/O control registers, refer to the ZNEO product

specification that is specific to your device . Attempts to read from unavailable I/O Memory addresses return

no effect.

FF_E000H through FF_FFFFH (in the 24-bit address space). The I/O Memory

FFH. Attempts to write to unavailable I/O Memory addresses produce

The ZNEO CPU assembler provides a configurable address range mnemonic, IODATA,

that can be specified to locate an address in the reserved I/O Memory space or (if present)

external I/O configured in the adjacent 16-bit addressable memory space. For more details

about data space and segment definitions, refer to the assembler documentation.

I/O Memory Precautions

Some control registers within the I/O Memory provide read-only or write-only access.

When accessing these read-only or write-only registers, ensure that the instructions do not

attempt to read from a write-only register or, conversely, write to a read-only register.

External Memory

ZNEO CPU products support external data and address buses for connecting to additional

external memories and/or memory-mapped peripherals. The external addresses can be

used for storing program code, data, constants, stack, etc. The results of reading from or

writing to unavailable external addresses are undefined.

The ZNEO CPU assembler’s EROM and ERAM address range mnemonics can be configured to include external memory configured in 32-bit addressed memory. These mnemonics can be used to locate data and program elements in nonvolatile or RAM memory, as

required. For more information about data space and segment definitions, refer to the

assembler documentation.

Address Space UM018809-0611

Page 35

Endianness

FF_0080H

FF_0081H

FF_0082H

FF_0083H

MSB

LSB

Address

of Quad

FF_0080H

FF_0081H

MSB

LSB

Address

of Word

The ZNEO CPU accesses data in Big Endian order; which means the address of a multibyte Word or Quad points to the most significant byte (MSB). Figure 4 displays the Endianness of the ZNEO CPU.

ZNEO

User Manual

®

CPU Core

19

Figure 4. Endianness of Words and Quads

Bus Widths

The ZNEO CPU can access 8-bit or 16-bit wide memories. The data buses of the internal

nonvolatile memory and internal RAM are 16-bits wide. The internal peripherals are a mix

UM018809-0611 Address Space

of 8-bit and 16-bit peripherals. The external memory bus can be configured as an 8-bit or

16-bit memory bus.

If a 16-bit or 32-bit operation is performed on a 16-bit wide memory, the number of memory accesses depends on the alignment of the address. If the address is even, a 16-bit operation takes one memory access and a 32-bit operation takes two memory accesses. If the

address is odd (unaligned), a 16-bit operation takes two memory accesses and a 32-bit

operation takes three memory accesses. Figure 5 displays this behavior for 16-bit and 32bit access.

Page 36

ZNEO® CPU Core

MSB

LSB

FF_0080H FF_0081H

MSB

LSB

FF_0082H

FF_0081H

Aligned 16-Bit Access

Unaligned 16-Bit Access

MSB

LSB

FF_0080H FF_0081H

FF_0082H FF_0083H

MSB

LSB

FF_0081H

FF_0082H

FF_0083H

FF_0084H

Aligned 32-Bit Access

Unaligned 32-Bit Access

FF_0080H

FF_0083H

FF_0085H

FF_0080H

User Manual

20

Figure 5. Alignment of 16-Bit and 32-Bit Operations on 16-Bit Memories

Address Space UM018809-0611

Page 37

Assembly Language Introduction

LOOP: SUB R5, R7 ;Subtract

Label

(Optional)

Instruction

Mnemonic

Destination

Operand

Source

Operand

Comment

(Optional)

Assembly language uses mnemonic symbols to represent instruction opcodes. Operands

such as register names and immediate data is represented symbolically, numerically, as

expressions, or by labels defined elsewhere in the program.

Figure 6 displays a typical assembly language statement.

ZNEO

User Manual

®

CPU Core

21

Figure 6. Example Assembly Language Statement

An assembly statement can include one or more the following elements:

Label. An optional text string used to refer to this statement elsewhere in the program. A

string is considered a label definition if it is not an assembler keyword, and it either begins

a line or is followed by a colon. The label definition identifies the address of the instruction that follows it.

Instruction Mnemonic. The mnemonic code for the desired operation.

Destination Operand. The destination location for the operation. In assembly, the desti-

nation operand is always first if both operands are specified.

Source Operand. The source location or immediate data for the operation.

Comment. An optional text field ignored by the assembler. Comments are used to

describe the flow of a program so it is easier to understand and maintain later.

Instead of instruction mnemonics, some assembly statements contain assembler directives

(also called pseudo-ops), which are not translated into object code. Directives are used to

select memory segments, allocate storage in memory, define macros, and control the

assembly process.

Example Assembly Language Source

An assembly language program is written in a plain text file called as source file, which

contains a sequence of assembly language statements and directives.

Below is an example of an assembly source file:

SEGMENT NEAR_TEXT ; Directive to place the following statements

UM018809-0611 Assembly Language Introduction

Page 38

ZNEO® CPU Core

User Manual

22

; in data (RAM space) memory

Str_Data: ; Make Str_Data label equal to current addr.

DB "NEVAR" ; Directive to allocate and initialize data

; bytes

Str_Length EQU $ - Str_Data ; Equate Str_Length to current

assembly

; address ("$") minus Str_Data address.

Blank_Data: ; Allocate an uninitialized data block

DS Str_Length ; that is the same size as the Str_Data block.

SEGMENT CODE ; Directive to put the following statements in

; instruction (ROM space) memory

REVERSE: ; Routine to reverse a block of data

LD R8, #Str_Data ; Load R8 with 1st address in Str_Data block

LD R12, #Blank_Data+Str_Length ;Next addr. after Blank_Data

LOOP: ; Start of loop

LD.UB R5,(R8++) ; Load byte pointed to by R8 into R5 LSB

; Increment R8 after load.

LD.B (--R12),R5 ; Decrement R12, then

; Load byte pointed to by R12 with R5 LSB

CP R12, #Blank_Data ; Did we write all the bytes?

JP NZ,LOOP ; Repeat until Blank_Data block contains

; reversed copy of Str_Data bytes

For details about assembly instructions, see the Instruction Set Reference chapter on

page 65. For details about operand addressing and data sizes, see the Operand Addressing

chapter on page 27.

For information about how program flow can be interrupted, see the Interrupts

chapter on

page 41, System Exceptions on page 49, and Software Traps on page 53.

For details about assembly language syntax, expressions, directives, and using the assem-

bler, refer to the Zilog Developer Studio II – ZNEO User Manual (UM0171)

.

ZNEO CPU Instruction Classes

ZNEO CPU instructions can be divided functionally into the following groups:

•

Arithmetic

•

Logical

•

Bit Manipulation

•

Rotate and Shift

Assembly Language Introduction UM018809-0611

Page 39

®

•

Load

•

CPU Control

•

Program Control

ZNEO

CPU Core

User Manual

Tables 6 through 12 list the instructions for each of the above groups and the number of

operands required for each instruction. Some instructions appear in more than one table as

these instructions can be considered members of more than one category. The abbreviations dst and src refer to destination and source operands, respectively.

Table 6. Arithmetic Instructions

Mnemonic Operands Instruction Page

ADC dst, src Add with Carry 68

ADD dst, src Add 71

CP dst, src Compare 86

CPC dst, src Compare with Carry 89

CPCZ dst Compare to Zero with Carry 92

CPZ dst Compare to Zero 94

DEC dst Decrement 96

INC dst Increment 108

MUL dst, src Multiply (32 bit) 125

NEG dst Negate 127

SBC dst, src Subtract with Carry 149

SDIV dst, src Signed Divide (32 bit) 152

SMUL dst, src Signed Multiply (64 bit) 158

SUB dst, src Subtract 169

UDIV dst, src Unsigned Divide (32 bit) 180

UDIV64 dst, src Unsigned Divide (64 bit) 182

UMUL dst, src Unsigned Multiply (64 bit) 184

23

Table 7. Logical Instructions

Mnemonic Operands Instruction Page

AND dst, src Logical AND 74

COM dst Complement 84

OR dst, src Logical OR 131

XOR dst, src Logical Exclusive OR 188

UM018809-0611 Assembly Language Introduction

Page 40

ZNEO® CPU Core

User Manual

24

Table 8. Bit Manipulation Instructions

Mnemonic Operands Instruction Page

TCM dst, src Test Complement Under Mask 172

TM dst, src Test Under Mask 175

Table 9. Rotate and Shift Instructions

Mnemonic Operands Instruction Page

RL dst Rotate Left 147

SLL dst, src Shift Left Logical 154

SLLX dst, src Shift Left Logical, Extended 156

SRA dst, src Shift Right Arithmetic 160

SRAX dst, src Shift Right Arithmetic,

Extended

SRL dst, src Shift Right Logical 164

SRLX dst, src Shift Right Logical, Extended 166

162

Table 10. Load Ins truct io n s

Mnemonic Operands Instruction Page

CLR dst Clear Value 82

EXT dst, src Extend Value 103

LD dst, src Load 115

LD cc dst Load Condition Code 120

LDES dst Load and Extend Sign Flag 121

LEA dst Load Effective Address 122

LINK src Link Frame Pointer 124

POP dst Pop 134

POPF dst Pop Flags 136

POPM mask Pop Multiple 137

PUSH src Push 140

PUSHF src Push Flags 142

PUSHM mask Push Multiple 143

UNLINK Unlink Frame Pointer 186

Assembly Language Introduction UM018809-0611

Page 41

Table 11. CPU Control Instructions

Mnemonic Operands Instruction Page

ATM — Atomic Operation Modifier 77

DI — Disable Interrupts 98

EI — Enable Interrupts 102

HALT — Halt Mode 105

NOFLAGS — No Flags Modifier 129

NOP — No Operation 130

STOP — Stop Mode 168

Table 12. Program Control Instructions

ZNEO

User Manual

®

CPU Core

25

Mnemonic Operands Instruction Page

BRK — On-Chip Debugger Break 78

CALL dst Call 79

CALLA dst Call Absolute 81

DJNZ dst, src Decrement, Jump if Nonzero 100

IRET — Interrupt Return 110

JP dst Jump 112

JPA dst Jump Absolute 113

JP cc dst Jump Conditional 114

RET — Return from Call 146

TRAP vector Software Trap 178

UM018809-0611 Assembly Language Introduction

Page 42

ZNEO® CPU Core

User Manual

26

Assembly Language Introduction UM018809-0611

Page 43

Operand Addressing

Most ZNEO CPU instructions operate on one or two registers, or one register and one

memory address. Operands following the instruction specify which register or memory

address to use.

Example. The assembly language statement below loads one 32-bit register with data

from another:

LD R7, R8

The first operand almost always specifies the destination, and the second operand (if any)

specifies the source for the operation. In this example, the R7 register is loaded with the

value from R8 register.

ZNEO

User Manual

®

CPU Core

27

There are four kinds of operand addressing, each of which is described in this chapter:

•

Immediate Data, in which the value specified by the operand is used for operation.

•

Register Addressing, in which the specified 32-bit register is used for operation.

•

Direct Memory Addressing, in which the value specified by the operand addresses a

memory location that is used for the operation. This section introduces the following

topics:

– Memory Data Size

– Resizing Data

These topics also apply to Register-Indirect memory addressing.

•

Register-Indirect Memory Addressing, in which the specified 32-bit register and

optional offset point to a memory location that is used for the operation. This section

covers the following topics specific to register-indirect addressing:

– Loading an Effective Address

– Using the Program Counter as a Base Address