Page 1

eZ80L92

Product Specification

PRELIMINARY

PS013011-0204

ZiLOG Worldwide Headquarters • 532 Race Street • San Jose, CA 95126

Telephone: 408.558.8500 • Fax: 408.558.8300 • www.ZiLOG.com

Page 2

ii

T

©

eZ80L92 Product Specification

This publication is subject to replacement by a later edition. T o determine whether

a later edition exists, or to request copies of publications, contact:

ZiLOG W orldwide Headquarters

532 Race Street

San Jose, CA 95126

elephone: 408.558.8500

Fax: 408.558.8300

www .ZiLOG.com

PS013011-0204

Document Disclaimer

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other

products and/or service names mentioned herein may be trademarks of the companies with which

they are associated.

2004 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices,

applications, or technology described is intended to suggest possible uses and may be superseded.

ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENT A TION OF

ACCURACY OF THE INFORMA TION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS

DOCUMENT . ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPER TY

INFRINGEMENT RELA TED IN ANY MANNER T O USE OF INFORMA TION, DEVICES, OR

TECHNOLOGY DESCRIBED HEREIN OR OTHER WISE. Devices sold by ZiLOG, Inc. are covered

by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. T erms and Conditions of

Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except with the

express written approval of ZiLOG, use of information, devices, or technology as critical components

of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this

document under any intellectual property rights.

PRELIMINARY

Page 3

able of Contents

ist of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Pin Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

®

eZ80

PU Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

New and Improved Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

T

L

C

eZ80L92 Product Specification

iii

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

RESET Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

SLEEP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

HALT Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Clock Peripheral Power-Down Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 36

General-Purpose Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

GPIO Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

GPIO Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

GPIO Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

GPIO Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Nonmaskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Chip Selects and Wait States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Memory and I/O Chip Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Memory Chip Select Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

I/O Chip Select Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Wait States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

WAIT Input Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Chip Selects During Bus Request/Bus Acknowledge Cycles . . . . . . . . . . . 52

Bus Mode Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

eZ80 Bus Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

PS013011-0204

PRELIMINARY

Table of Content s

Page 4

eZ80L92 Product Specification

Z80 Bus Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Intel Bus Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Motorola Bus Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Chip Select Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Watch-Dog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Watch-Dog Timer Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Watch-Dog Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Watch-Dog Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Programmable Reload Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Programmable Reload Timers Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Programmable Reload Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Programmable Reload Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Real-Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Real-Time Clock Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Real-Time Clock Alarm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Real-Time Clock Oscillator and Source Selection . . . . . . . . . . . . . . . . . . . . 87

Real-Time Clock Battery Backup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Real-Time Clock Recommended Operation . . . . . . . . . . . . . . . . . . . . . . . . 87

Real-Time Clock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

iv

Universal Asynchronous Receiver/Transmitter . . . . . . . . . . . . . . . . . . . . . . . . 102

UART Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

UART Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

UART Recommended Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

BRG Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

UART Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Infrared Encoder/Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Infrared Encoder/Decoder Signal Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Loopback Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Serial Peripheral Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

SPI Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

SPI Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

SPI Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

SPI Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Data Transfer Procedure with SPI Configured as the Master . . . . . . . . . . 130

PS013011-0204 PRELIMINARY Table of Contents

Page 5

eZ80L92 Product Specification

Data Transfer Procedure with SPI Configured as a Slave . . . . . . . . . . . . 130

SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

I2C Serial I/O Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

I2C General Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Transferring Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

I2C Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

ZiLOG Debug Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

ZDI-Supported Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

ZDI Clock and Data Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

ZDI Start Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

ZDI Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

ZDI Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

ZDI Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Operation of the eZ80L92 during ZDI BREAKpoints . . . . . . . . . . . . . . . . . 163

Bus Requests During ZDI Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 163

ZDI Write-Only Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

ZDI Read-Only Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

ZDI Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

v

On-Chip Instrumentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Introduction to On-Chip Instrumentation . . . . . . . . . . . . . . . . . . . . . . . . . . 182

OCI Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

OCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

OCI Information Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

eZ80® CPU Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Op-Code Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

On-Chip Oscillators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

20 MHz Primary Crystal Oscillator Operation . . . . . . . . . . . . . . . . . . . . . . 196

50 MHz Primary Crystal Oscillator Operation . . . . . . . . . . . . . . . . . . . . . . 197

32 KHz Real-Time Clock Crystal Oscillator Operation . . . . . . . . . . . . . . . 199

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

External Memory Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

External Memory Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

PS013011-0204 PRELIMINARY Table of Contents

Page 6

eZ80L92 Product Specification

External I/O Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

External I/O Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Wait State Timing for Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Wait State Timing for Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

General Purpose I/O Port Input Sample Timing . . . . . . . . . . . . . . . . . . . . 213

General Purpose I/O Port Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . 213

External Bus Acknowledge Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

External System Clock Driver (PHI) Timing . . . . . . . . . . . . . . . . . . . . . . . 214

Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Part Number Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Precharacterization Product . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Document Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Document Number Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Change Log . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

vi

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Customer Feedback Form . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

PS013011-0204 PRELIMINARY Table of Contents

Page 7

List of Figures

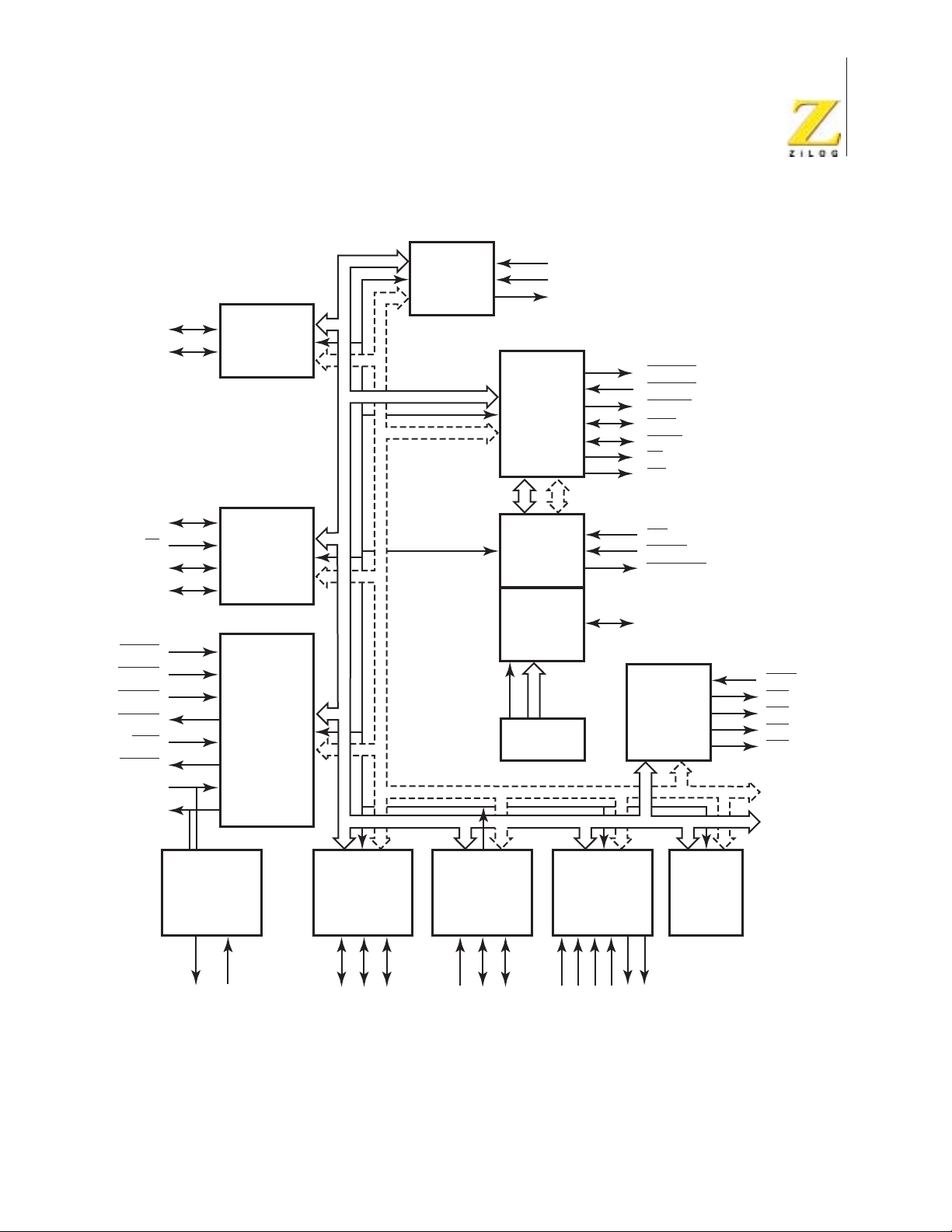

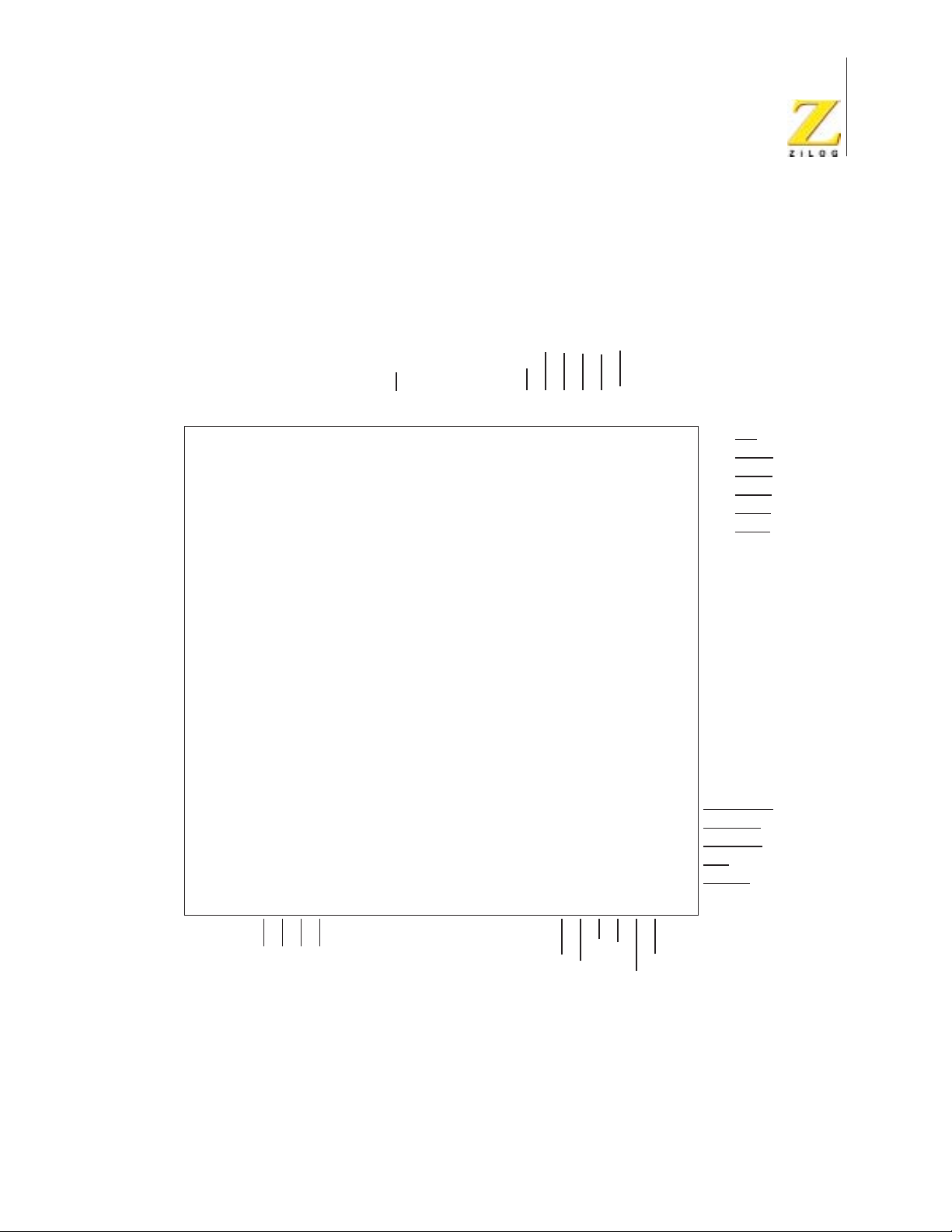

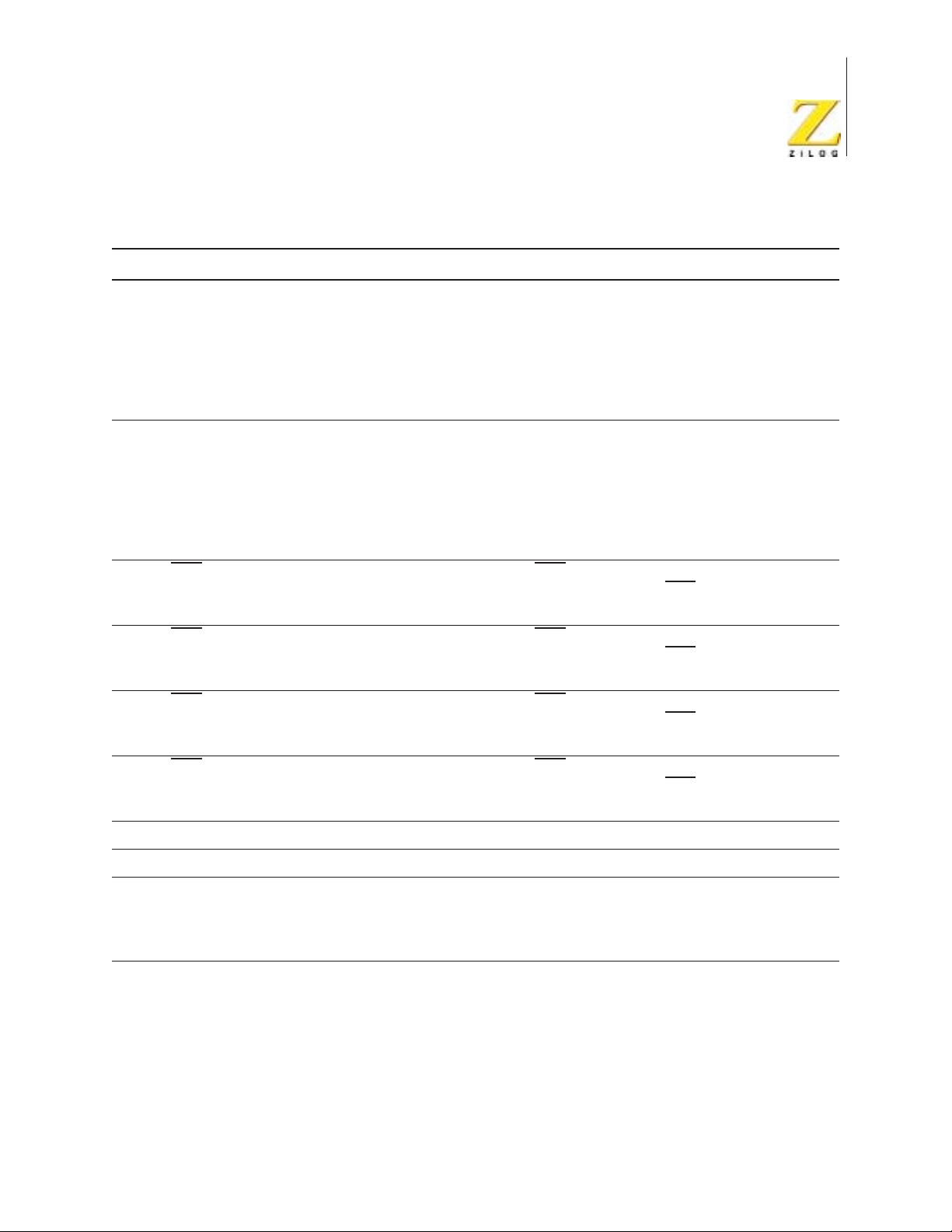

Figure 1. eZ80L92 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

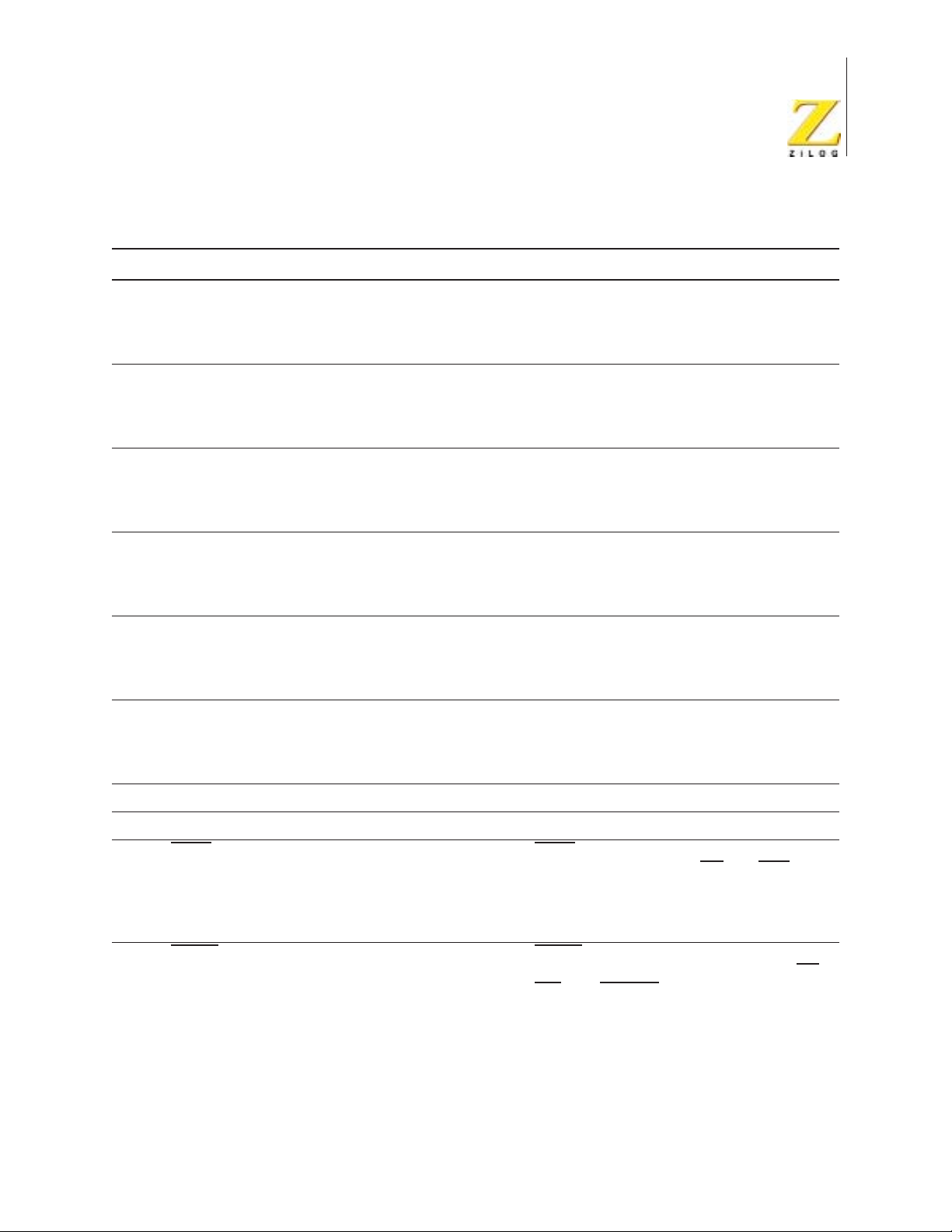

Figure 2. 100-Pin LQFP Configuration of the eZ80L92 . . . . . . . . . . . . . . . . . . 4

Figure 3. GPIO Port Pin Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 4. Memory Chip Select Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 5. Wait Input Sampling Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 6. Wait State Operation Example (Read Operation) . . . . . . . . . . . . . . 52

Figure 7. Z80 Bus Mode Read Timing Example . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 8. Z80 Bus Mode Write Timing Example . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 9. IntelTM Bus Mode Signal and Pin Mapping . . . . . . . . . . . . . . . . . . . 56

Figure 10. Intel™ Bus Mode Read Timing Example (Separate Address and

Data Buses) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 11. Intel™ Bus Mode Write Timing Example (Separate Address and

Data Buses) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 12. Intel™ Bus Mode Read Timing Example (Multiplexed Address

and Data Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 13. IntelTM Bus Mode Write Timing Example (Multiplexed Address

and Data Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 14. Motorola Bus Mode Signal and Pin Mapping . . . . . . . . . . . . . . . . . 63

Figure 15. Motorola Bus Mode Read Timing Example . . . . . . . . . . . . . . . . . . . 65

Figure 16. Motorola Bus Mode Write Timing Example . . . . . . . . . . . . . . . . . . . 66

Figure 17. Watch-Dog Timer Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 18. Programmable Reload Timer Block Diagram . . . . . . . . . . . . . . . . . 75

Figure 19. PRT Single Pass Mode Operation Example . . . . . . . . . . . . . . . . . . 77

Figure 20. PRT Continuous Mode Operation Example . . . . . . . . . . . . . . . . . . 78

Figure 21. PRT Timer Output Operation Example . . . . . . . . . . . . . . . . . . . . . . 80

Figure 22. Real-Time Clock and 32KHz Oscillator Block Diagram . . . . . . . . . . 86

Figure 23. UART Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 24. Infrared System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 25. Infrared Data Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 26. Infrared Data Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 27. SPI Master Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 28. SPI Slave Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 29. SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 30. I2C Clock and Data Relationship . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Figure 31. START and STOP Conditions In I2C Protocol . . . . . . . . . . . . . . . . 136

Figure 32. I2C Frame Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

eZ80L92 Product Specification

vii

PS013011-0204 PRELIMINARY List of Figures

Page 8

eZ80L92 Product Specification

Figure 33. I2C Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Figure 34. Clock Synchronization In I2C Protocol . . . . . . . . . . . . . . . . . . . . . . 139

Figure 35. Typical ZDI Debug Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Figure 36. Schematic For Building a Target Board ZPAK II Connector . . . . . 157

Figure 37. ZDI Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 38. ZDI Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 39. ZDI Address Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Figure 40. ZDI Single-Byte Data Write Timing . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 41. ZDI Block Data Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 42. ZDI Single-Byte Data Read Timing . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 43. ZDI Block Data Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 44. Recommended Crystal Oscillator Configuration

(20MHz operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Figure 45. Recommended Crystal Oscillator Configuration

(50MHz operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Figure 46. Recommended Crystal Oscillator Configuration

(32KHz operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Figure 47. ICC vs. Frequency (Typical @ 3.3 V, 25ºC) . . . . . . . . . . . . . . . . . . 203

Figure 48. ICC vs. WAIT (Typical @ 3.3 V, 25ºC) . . . . . . . . . . . . . . . . . . . . . . 203

Figure 49. External Memory Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 50. External Memory Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Figure 51. External I/O Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Figure 52. External I/O Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Figure 53. Wait State Timing for Read Operations . . . . . . . . . . . . . . . . . . . . . 211

Figure 54. Wait State Timing for Write Operations . . . . . . . . . . . . . . . . . . . . . 212

Figure 55. Port Input Sample Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 56. GPIO Port Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 57. 100-Lead Plastic Low-Profile Quad Flat Package (LQFP) . . . . . . 215

viii

PS013011-0204 PRELIMINARY List of Figures

Page 9

List of Tables

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device . . . . . . . . . . . . 5

Table 2. Pin Characteristics of the eZ80L92 . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 3. Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 4. Clock Peripheral Power-Down Register 1 . . . . . . . . . . . . . . . . . . . . . . 37

Table 5. Clock Peripheral Power-Down Register 2 . . . . . . . . . . . . . . . . . . . . . . 38

Table 6. GPIO Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 7. Port x Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 8. Port x Data Direction Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 9. Port x Alternate Registers 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 10. Port x Alternate Registers 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 11. Interrupt Vector Sources by Priority . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 12. Vectored Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 13. Register Values for Memory Chip Select Example . . . . . . . . . . . . . . 50

Table 14. Z80 Bus Mode Read States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 15. Z80 Bus Mode Write States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 16. Intel™ Bus Mode Read States (Separate Address and Data Buses) 56

Table 17. Intel™ Bus Mode Write States (Separate Address and Data Buses) 57

Table 18. Intel™ Bus Mode Write States (Multiplexed Address and Data Bus). 60

Table 19. Intel™ Bus Mode Read States (Multiplexed Address and Data Bus) 60

Table 20. Motorola Bus Mode Read States . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 21. Motorola Bus Mode Write States . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 22. Chip Select x Lower Bound Registers . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 23. Chip Select x Upper Bound Registers . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 24. Chip Select x Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 25. Chip Select x Bus Mode Control Registers . . . . . . . . . . . . . . . . . . . . 69

Table 26. Watch-Dog Timer Approximate Time-Out Delays . . . . . . . . . . . . . . . 72

Table 27. Watch-Dog Timer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 28. Watch-Dog Timer Reset Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 29. PRT Single Pass Mode Operation Example . . . . . . . . . . . . . . . . . . . 77

Table 30. PRT Continuous Mode Operation Example . . . . . . . . . . . . . . . . . . . . 78

Table 31. PRT Timer Out Operation Example . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 32. Timer Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 33. Timer Data Registers—Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 34. Timer Data Registers—High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 35. Timer Reload Registers—Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . 83

eZ80L92 Product Specification

ix

PS013011-0204 PRELIMINARY List of Tables

Page 10

eZ80L92 Product Specification

Table 36. Timer Reload Registers—High Byte . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 37. Timer Input Source Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 38. Real-Time Clock Seconds Register . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 39. Real-Time Clock Minutes Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 40. Real-Time Clock Hours Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 41. Real-Time Clock Day-of-the-Week Register . . . . . . . . . . . . . . . . . . . 91

Table 42. Real-Time Clock Day-of-the-Month Register . . . . . . . . . . . . . . . . . . . 92

Table 43. Real-Time Clock Month Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 44. Real-Time Clock Year Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 45. Real-Time Clock Century Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 46. Real-Time Clock Alarm Seconds Register . . . . . . . . . . . . . . . . . . . . . 96

Table 47. Real-Time Clock Alarm Minutes Register . . . . . . . . . . . . . . . . . . . . . 97

Table 48. Real-Time Clock Alarm Hours Register . . . . . . . . . . . . . . . . . . . . . . . 98

Table 49. Real-Time Clock Alarm Day-of-the-Week Register . . . . . . . . . . . . . . 99

Table 50. Real-Time Clock Alarm Control Register . . . . . . . . . . . . . . . . . . . . . 100

Table 51. Real-Time Clock Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 52. UART Baud Rate Generator Registers—Low Byte . . . . . . . . . . . . . 108

Table 53. UART Baud Rate Generator Registers—High Byte . . . . . . . . . . . . . 108

Table 54. UART Transmit Holding Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 55. UART Receive Buffer Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 56. UART Interrupt Enable Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 57. UART Interrupt Identification Registers . . . . . . . . . . . . . . . . . . . . . . 111

Table 58. UART Interrupt Status Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 59. UART FIFO Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 60. UART Line Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 61. UART Character Parameter Definition . . . . . . . . . . . . . . . . . . . . . . . 114

Table 62. UART Modem Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 63. UART Line Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 64. UART Modem Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 65. UART Scratch Pad Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 66. GPIO Mode Selection when using the IrDA Encoder/Decoder . . . . 123

Table 67. Infrared Encoder/Decoder Control Register . . . . . . . . . . . . . . . . . . . 124

Table 68. SPI Clock Phase (CPHA) and Clock Polarity Operation . . . . . . . . . 127

Table 69. SPI Baud Rate Generator Register—High Byte. . . . . . . . . . . . . . . . 131

Table 70. SPI Baud Rate Generator Register—Low Byte . . . . . . . . . . . . . . . . 131

Table 71. SPI Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 72. SPI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 73. SPI Receive Buffer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

x

PS013011-0204 PRELIMINARY List of Tables

Page 11

eZ80L92 Product Specification

Table 74. SPI Transmit Shift Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 75. I2C Master Transmit Status Codes. . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 76. I2C 10-Bit Master Transmit Status Codes . . . . . . . . . . . . . . . . . . . . 142

Table 77. I2C Master Transmit Status Codes For Data Bytes . . . . . . . . . . . . . 143

Table 78. I2C Master Receive Status Codes . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 79. I2C Master Receive Status Codes For Data Bytes. . . . . . . . . . . . . . 145

Table 80. I2C Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 81. I2C Slave Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 82. I2C Extended Slave Address Register . . . . . . . . . . . . . . . . . . . . . . . 149

Table 83. I2C Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 84. I2C Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 85. I2C Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 86. I2C Status Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 87. I2C Clock Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 88. I2C Software Reset Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Table 89. Recommended ZDI Clock vs. System Clock Frequency . . . . . . . . . 157

Table 90. ZDI Write-Only Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 91. ZDI Read-Only Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 92. ZDI Address Match Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Table 93. ZDI BREAK Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 94. ZDI Master Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 95. ZDI Write Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Table 96. ZDI Read/Write Control Register Functions . . . . . . . . . . . . . . . . . . . 172

Table 97. ZDI Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 98. Instruction Store 4:0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 99. ZDI Write Memory Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Table 100. eZ80® Product ID Low Byte Register. . . . . . . . . . . . . . . . . . . . . . . 176

Table 101. eZ80® Product ID Revision Register . . . . . . . . . . . . . . . . . . . . . . . 177

Table 102. eZ80® Product ID High Byte Register . . . . . . . . . . . . . . . . . . . . . . 177

Table 103. ZDI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Table 104. ZDI Read Registers—Low, High and Upper . . . . . . . . . . . . . . . . . 179

Table 105. ZDI Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Table 106. ZDI Read Memory Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Table 107. OCI Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 108. Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 109. Bit Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 110. Block Transfer and Compare Instructions . . . . . . . . . . . . . . . . . . . 185

Table 111. Exchange Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

xi

PS013011-0204 PRELIMINARY List of Tables

Page 12

eZ80L92 Product Specification

Table 112. Input/Output Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 113. Load Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Table 114. Logical Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Table 115. Processor Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Table 116. Program Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 117. Rotate and Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 118. Op Code Map—First Op Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 119. Op Code Map—Second Op Code after 0CBh . . . . . . . . . . . . . . . . 190

Table 120. Op Code Map—Second Op Code After 0DDh . . . . . . . . . . . . . . . . 191

Table 121. Op Code Map—Second Op Code After 0EDh . . . . . . . . . . . . . . . . 192

Table 122. Op Code Map—Second Op Code After 0FDh . . . . . . . . . . . . . . . . 193

Table 123. Op Code Map—Fourth Byte After 0DDh, 0CBh, and dd . . . . . . . . 194

Table 124. Op Code Map—Fourth Byte After 0FDh, 0CBh, and dd* . . . . . . . . 195

Table 125. Recommended Crystal Oscillator Specifications

(20 MHz Operation). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 126. Recommended Crystal Oscillator Specifications

(50MHz Operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Table 127. Recommended Crystal Oscillator Specifications

(32 KHz Operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 128. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Table 129. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 130. AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 131. External Read Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Table 132. External Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Table 133. External I/O Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 134. External I/O Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Table 135. GPIO Port Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Table 136. Bus Acknowledge Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Table 137. PHI System Clock Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Table 138. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

xii

PS013011-0204 PRELIMINARY List of Tables

Page 13

Architectural Overview

The eZ80L92 microprocessor is a high-speed single-cycle instruction-fetch microprocessor with a maximum clock speed of 50 MHz. The eZ80L92 is a member of

ZiLOG’s new eZ80® product family. It can operate in Z80-compatible addressing

mode (64 KB) or full 24-bit addressing mode (16 MB). The rich peripheral set of the

eZ80L92 makes it suitable for a variety of applications including industrial control,

embedded communication, and point-of-sale terminals.

Features

• Single-cycle instruction fetch, high-performance, pipelined eZ80® CPU core

• Low power features including SLEEP mode, HALT mode, and selective

peripheral power-down control

eZ80L92 Product Specification

1

1

• Two UARTs with independent baud rate generators

• SPI with independent clock rate generator

• I2C with independent clock rate generator

• Infrared Data Association (IrDA)-compliant infrared encoder/decoder

• New DMA-like eZ80® instructions for efficient block data transfer

• Glueless external peripheral interface with 4 Chip Selects, individual Wait

State generators, and an external WAIT input pin—supports Intel-and Motorola-style buses

• Fixed-priority vectored interrupts (both internal and external) and interrupt

controller

• Real-time clock with on-chip 32 KHz oscillator, selectable 50/60Hz input, and

separate VDD pin for battery backup

• Six 16-bit Counter/Timers with prescalers and direct input/output drive

• Watch-Dog Timer

• 24 bits of General-Purpose I/O

• JTAG and ZDI debug interfaces

• 100-pin LQFP package

• 3.0–3.6 V supply voltage with 5 V tolerant inputs

1. For simplicity, the term eZ80® CPU is referred to as CPU for the bulk of this document.

PS013011-0204 PRELIMINARY Architectural Overview

Page 14

• Operating Temperature Range

–

Standard: 0ºC to +70ºC

–

Extended: –40ºC to +105ºC

eZ80L92 Product Specification

2

Note:

All signals with an overline are active Low. For example, B/W, for which

WORD is active Low, and B/W, for which BYTE is active Low.

Power connections follow these conventional descriptions:

Connection Circuit Device

Power V

Ground GND V

Block Diagram

Figure 1 illustrates a block diagram of the eZ80L92 microprocessor.

CC

V

DD

SS

PS013011-0204 PRELIMINARY Architectural Overview

Page 15

eZ80L92 Product Specification

3

SCL

SDA

SCK

SS

MISO

MOSI

CTS0/1

CD0/1

DSR0/1

DTR0/1

RI0/1

RTS0/1

RxD0/1

TxD0/1

2

I C

Serial

Interface

Serial

Peripheral

Interface

(SPI)

Universal

Asynchronous

Receiver/

Transmitter

(UART)

Real-Time

Clock and

32 KHz

Oscillator

RTC_V

RTC_X

RTC_X

Bus

Controller

eZ80

CPU

ZiLOG

Debug

Interface

(JTAG/ZDI)

Interrupt

Vector

[7:0]

Interrupt

Controller

DD

IN

OUT

BUSACK

BUSREQ

INSTRD

IORQ

MREQ

RD

WR

NMI

RESET

HALT_SLP

JTAG/ZDI Signals (5)

Chip

Select

and

Wait State

Generator

WAIT

CS0

CS1

CS2

CS3

DATA[7:0]

ADDR[23:0]

IrDA

Encoder/

Decoder

IR_TxD

IR_RxD

8-Bit

General

Purpose

I/O Port

(GPIO)

PB[7:0]

PC[7:0]

PD[7:0]

Crystal

Oscillator

and

System Clock

Generator

IN

X

OUT

X

PHI

Programmable

Reload

Timer/Counters

(6)

T0_IN

T1_IN

T2_IN

T3_IN

T4_OUT

T5_OUT

Watch-Dog

Timer

(WDT)

Figure 1. eZ80L92 Block Diagram

PS013011-0204 PRELIMINARY Architectural Overview

Page 16

Pin Description

Figure 2 illustrates the pin layout of the eZ80L92 in the 100-pin LQFP package.

Table 1 describes the pins and their functions.

eZ80L92 Product Specification

4

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

V

DD

V

SS

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

V

DD

V

SS

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

PHI

SCL

99

100

262728

ADDR21

ADDR22

ADDR23

DD

SDA

VSSPB7/MOSI

V

95

96

97

98

PB6/MISO

PB5/T5_OUT

PB4/T4_OUT

92

93

94

PB3/SCK

PB2/SS

PB1/T1_IN

90

91

89

OUTXINVSS

PB0/T0_IN

VDDX

86

87

88

85

84

PC7/RI1

83

PC6/DCD1

PC5/DSR1

81

82

PC4/DTR1

PC3/CTS1

79

80

100-Pin LQFP

30

313233343536373839

29

SS

DD

V

CS2

CS3

V

CS0

CS1

DATA0

DATA1

DATA2

4050414243444546474849

SS

DD

V

V

DATA3

DATA4

DATA5

DATA6

DATA7

IORQ

RD

MREQ

Figure 2. 100-Pin LQFP Configuration of the eZ80L92

PC2//RTS1

PC1/RxD1

77

78

WR

INSTRD

PC0/TxD1

76

75

PD7/RI0

74

PD6/DCD0

73

PD5/DSR0

72

PD4/DTR0

71

PD3/CTS0

70

PD2/RTS0

69

PD1/RxD0/IR_RXD

68

PD0/TxD0/IR_TXD

67

V

DD

66

TDO

65

TDI

64

TRIGOUT

63

TCK

62

TMS

61

V

SS

60

RTC_V

59

RTC_XOUT

58

RTC_XIN

57

V

SS

56

V

DD

55

HALT_SLP

54

BUSACK

53

BUSREQ

52

NMI

51

RESET

WAIT

DD

PS013011-0204 PRELIMINARY Architectural Overview

Page 17

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device

Pin # Symbol Function Signal Direction Description

1 ADDR0 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

2 ADDR1 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

5

3 ADDR2 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

4 ADDR3 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

5 ADDR4 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

6 ADDR5 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

PS013011-0204 PRELIMINARY Architectural Overview

Page 18

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

6

7 V

8 V

DD

SS

Power Supply Power Supply.

Ground Ground.

9 ADDR6 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

10 ADDR7 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

11 ADDR8 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

12 ADDR9 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

13 ADDR10 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

PS013011-0204 PRELIMINARY Architectural Overview

Page 19

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

14 ADDR11 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

15 ADDR12 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

7

16 ADDR13 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

17 ADDR14 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

18 V

19 V

DD

SS

Power Supply Power Supply.

Ground Ground.

20 ADDR15 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

PS013011-0204 PRELIMINARY Architectural Overview

Page 20

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

21 ADDR16 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

22 ADDR17 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

8

23 ADDR18 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

24 ADDR19 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

25 ADDR20 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

26 ADDR21 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

PS013011-0204 PRELIMINARY Architectural Overview

Page 21

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

27 ADDR22 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

28 ADDR23 Address Bus Bidirectional Configured as an output in normal opera-

tion. The address bus selects a location in

memory or I/O space to be read or written.

Configured as an input during bus

acknowledge cycles. Drives the Chip

Select/Wait State Generator block to generate Chip Selects.

9

29 CS0 Chip Select 0 Output, Active Low CS0 Low indicates that an access is occur-

ring in the defined CS0 memory or I/O

address space.

30 CS1 Chip Select 1 Output, Active Low CS1 Low indicates that an access is occur-

ring in the defined CS1 memory or I/O

address space.

31 CS2 Chip Select 2 Output, Active Low CS2 Low indicates that an access is occur-

ring in the defined CS2 memory or I/O

address space.

32 CS3 Chip Select 3 Output, Active Low CS3 Low indicates that an access is occur-

ring in the defined CS3 memory or I/O

address space.

33 V

34 V

DD

SS

Power Supply Power Supply.

Ground Ground.

35 DATA0 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

36 DATA1 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

PS013011-0204 PRELIMINARY Architectural Overview

Page 22

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

37 DATA2 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

38 DATA3 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

39 DATA4 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

10

40 DATA5 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

41 DATA6 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

42 DATA7 Data Bus Bidirectional The data bus transfers data to and from I/O

and memory devices. The eZ80L92 drives

these lines only during write cycles when

the eZ80L92 is the bus master.

43 V

44 V

DD

SS

45 IORQ Input/Output

Power Supply Power Supply.

Ground Ground.

Request

Bidirectional, Active

Low

IORQ indicates that the CPU is accessing

a location in I/O space. RD and WR indicate the type of access. The eZ80L92 does

not drive this line during RESET. It is an

input in bus acknowledge cycles.

46 MREQ Memory

Request

Bidirectional, Active

Low

MREQ Low indicates that the CPU is

accessing a location in memory. The RD,

WR, and INSTRD signals indicate the type

of access. The eZ80L92 does not drive this

line during RESET. It is an input in bus

acknowledge cycles.

PS013011-0204 PRELIMINARY Architectural Overview

Page 23

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

47 RD Read Output, Active Low RD Low indicates that the eZ80L92 is

reading from the current address location.

This pin is tristated during bus acknowledge cycles.

48 WR Write Output, Active Low WR indicates that the CPU is writing to the

current address location. This pin is

tristated during bus acknowledge cycles.

11

49 INSTRD Instruction

Read Indicator

50 WAIT WAIT Request Input, Active Low Driving the WAIT pin Low forces the CPU

51 RESET Reset Schmitt Trigger Input,

52 NMI Nonmaskable

Interrupt

53 BUSREQ Bus Request Input, Active Low External devices can request the eZ80L92

Output, Active Low INSTRD (with MREQ and RD) indicates

the eZ80L92 is fetching an instruction from

memory. This pin is tristated during bus

acknowledge cycles.

to wait additional clock cycles for an external peripheral or external memory to complete its Read or Write operation.

This signal is used to initialize the

Active Low

Schmitt Trigger Input,

Active Low

eZ80L92. This input must be Low for a

minimum of 3 system clock cycles, and

must be held Low until the clock is stable.

This input includes a Schmitt trigger to

allow RC rise times.

The NMI input is a higher priority input than

the maskable interrupts. It is always recognized at the end of an instruction, regardless of the state of the interrupt enable

control bits. This input includes a Schmitt

trigger to allow RC rise times.

to release the memory interface bus for

their use, by driving this pin Low.

54 BUSACK Bus Acknowl-

edge

55 HALT_SLP HALT and

SLEEP Indicator

PS013011-0204 PRELIMINARY Architectural Overview

Output, Active Low The eZ80L92 responds to a Low on BUS-

REQ, by tristating the address, data, and

control signals, and by driving the

BUSACK line Low. During bus acknowledge cycles ADDR[23:0], IORQ, and

MREQ are inputs.

Output, Active Low A Low on this pin indicates that the CPU

has entered either HALT or SLEEP mode

because of execution of either a HALT or

SLP instruction.

Page 24

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

12

56 V

57 V

DD

SS

Power Supply Power Supply.

Ground Ground.

58 RTC_XIN Real-Time

Clock Crystal

Input

59 RTC_XOUT Real-Time

Clock Crystal

Output

60 RTC_

V

DD

Real-Time

Clock Power

Supply

61 V

SS

Ground Ground.

62 TMS JTAG Test

Mode Select

63 TCK JTAG Test

Clock

Input This pin is the input to the low-power

32KHz crystal oscillator for the Real-Time

Clock.

Bidirectional This pin is the output from the low-power

32KHz crystal oscillator for the Real-Time

Clock. This pin is an input when the RTC is

configured to operate from 50/60 Hz input

clock signals and the 32 KHz crystal oscillator is disabled.

Power supply for the Real-Time Clock and

associated 32KHz oscillator. Isolated from

the power supply to the remainder of the

chip. A battery can be connected to this pin

to supply constant power to the Real-Time

Clock and 32KHz oscillator.

Input JTAG Mode Select Input.

Input JTAG and ZDI clock input.

64 TRIGOUT JTAG Test

Output Active High trigger event indicator.

Trigger Output

65 TDI JTAG Test

Data In

66 TDO JTAG Test

Bidirectional JTAG data input pin. Functions as ZDI data

I/O pin when JTAG is disabled.

Output JTAG data output pin.

Data Out

67 V

PS013011-0204 PRELIMINARY Architectural Overview

DD

Power Supply Power Supply.

Page 25

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

13

68 PD0 GPIO Port D Bidirectional

TxD0 UART Trans-

mit Data

IR_TXD IrDA Transmit

Data

69 PD1 GPIO Port D Bidirectional This pin can be used for general-purpose

RxD0 Receive Data Input This pin is used by the UART to receive

Output This pin is used by the UART to transmit

Output This pin is used by the IrDA encoder/

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

asynchronous serial data. This signal is

multiplexed with PD0.

decoder to transmit serial data. This signal

is multiplexed with PD0.

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

asynchronous serial data. This signal is

multiplexed with PD1.

IR_RXD IrDA Receive

Data

70 PD2 GPIO Port D Bidirectional This pin can be used for general-purpose

RTS0 Request to

Send

PS013011-0204 PRELIMINARY Architectural Overview

Input This pin is used by the IrDA encoder/

decoder to receive serial data. This signal

is multiplexed with PD1.

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

Output, Active Low Modem control signal from UART. This sig-

nal is multiplexed with PD2.

Page 26

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

71 PD3 GPIO Port D Bidirectional This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

CTS0 Clear to Send Input, Active Low Modem status signal to the UART. This

signal is multiplexed with PD3.

14

72 PD4 GPIO Port D Bidirectional

DTR0 Data Terminal

Ready

73 PD5 GPIO Port D Bidirectional

DSR0 Data Set

Ready

74 PD6 GPIO Port D Bidirectional

Output, Active Low Modem control signal to the UART. This

Input, Active Low Modem status signal to the UART. This

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

signal is multiplexed with PD4.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

signal is multiplexed with PD5.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

DCD0 Data Carrier

Detect

PS013011-0204 PRELIMINARY Architectural Overview

Input, Active Low Modem status signal to the UART. This

signal is multiplexed with PD6.

Page 27

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

15

75 PD7 GPIO Port D Bidirectional

RI0 Ring Indicator Input, Active Low Modem status signal to the UART. This

76 PC0 GPIO Port C Bidirectional

TxD1 Transmit Data Output This pin is used by the UART to transmit

77 PC1 GPIO Port C Bidirectional

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port D

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port D is multiplexed with

one UART.

signal is multiplexed with PD7.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

asynchronous serial data. This signal is

multiplexed with PC0.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

RxD1 Receive Data Input This pin is used by the UART to receive

asynchronous serial data. This signal is

multiplexed with PC1.

PS013011-0204 PRELIMINARY Architectural Overview

Page 28

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

16

78 PC2 GPIO Port C Bidirectional

RTS1 Request to

Send

79 PC3 GPIO Port C Bidirectional

CTS1 Clear to Send Input, Active Low Modem status signal to the UART. This

80 PC4 GPIO Port C Bidirectional

Output, Active Low Modem control signal from UART. This sig-

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

nal is multiplexed with PC2.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

signal is multiplexed with PC3.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

DTR1 Data Terminal

Ready

81 PC5 GPIO Port C Bidirectional

DSR1 Data Set

Ready

PS013011-0204 PRELIMINARY Architectural Overview

Output, Active Low Modem control signal to the UART. This

signal is multiplexed with PC4.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

Input, Active Low Modem status signal to the UART. This

signal is multiplexed with PC5.

Page 29

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

17

82 PC6 GPIO Port C Bidirectional

DCD1 Data Carrier

Input, Active Low Modem status signal to the UART. This

Detect

83 PC7 GPIO Port C Bidirectional

RI1 Ring Indicator Input, Active Low Modem status signal to the UART. This

84 V

85 X

SS

IN

Ground Ground.

System Clock

Input This pin is the input to the onboard crystal

Oscillator Input

86 X

OUT

System Clock

Output This pin is the output of the onboard crystal

Oscillator Output

87 V

DD

Power Supply Power Supply.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

signal is multiplexed with PC6.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port C

pin, when programmed as output, can be

selected to be an open-drain or opensource output. Port C is multiplexed with

one UART.

signal is multiplexed with PC7.

oscillator for the primary system clock. If an

external oscillator is used, its clock output

should be connected to this pin. When a

crystal is used, it should be connected

between XIN and X

OUT

.

oscillator. When used, a crystal should be

connected between XIN and X

OUT

.

PS013011-0204 PRELIMINARY Architectural Overview

Page 30

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

18

88 PB0 GPIO Port B Bidirectional

T0_IN Timer 0 In Input Alternate clock source for Programmable

89 PB1 GPIO Port B Bidirectional

T1_IN Timer 1 In Input Alternate clock source for Programmable

90 PB2 GPIO Port B Bidirectional

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

Reload Timers 0 and 2. This signal is multiplexed with PB0.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

Reload Timers 1 and 3. This signal is multiplexed with PB1.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

SS Slave Select Input, Active Low The slave select input line is used to select

a slave device in SPI mode. This signal is

multiplexed with PB2.

91 PB3 GPIO Port B Bidirectional

SCK SPI Serial

Clock

PS013011-0204 PRELIMINARY Architectural Overview

Bidirectional SPI serial clock. This signal is multiplexed

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

with PB3.

Page 31

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

19

92 PB4 GPIO Port B Bidirectional

T4_OUT Timer 4 Out Output Programmable Reload Timer 4 timer-out

93 PB5 GPIO Port B Bidirectional

T5_OUT Timer 5 Out Output Programmable Reload Timer 5 timer-out

94 PB6 GPIO Port B Bidirectional

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

signal. This signal is multiplexed with PB4.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

signal. This signal is multiplexed with PB5.

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

MISO Master In

Slave Out

PS013011-0204 PRELIMINARY Architectural Overview

Bidirectional The MISO line is configured as an input

when the eZ80L92 is an SPI master device

and as an output when eZ80L92 is an SPI

slave device. This signal is multiplexed

with PB6.

Page 32

eZ80L92 Product Specification

Table 1. 100-Pin LQFP Pin Identification of the eZ80L92 Device (Continued)

Pin # Symbol Function Signal Direction Description

20

95 PB7 GPIO Port B Bidirectional

MOSI Master Out

Slave In

96 V

97 V

98 SDA I2C Serial Data Bidirectional This pin carries the I2C data signal.

99 SCL I2C Serial

100 PHI System Clock Output This pin is an output driven by the internal

DD

SS

Power Supply Power Supply.

Ground Ground.

Clock

Bidirectional The MOSI line is configured as an output

Bidirectional This pin is used to receive and transmit the

This pin can be used for general-purpose

I/O. It can be individually programmed as

input or output and can also be used individually as an interrupt input. Each Port B

pin, when programmed as output, can be

selected to be an open-drain or opensource output.

when the eZ80L92 is an SPI master device

and as an input when the eZ80L92 is an

SPI slave device. This signal is multiplexed

with PB7.

I2C clock.

system clock.

Pin Characteristics

Table 2 describes the characteristics of each pin in the eZ80L92’s 100-pin LQFP

package.

Table 2. Pin Characteristics of the eZ80™ Webserver-i

Schmitt

Reset

Pin # Symbol Direction

1 ADDR0

2 ADDR1

3 ADDR2

4 ADDR3

5 ADDR4

6 ADDR5

7 V

PS013011-0204 PRELIMINARY Architectural Overview

DD

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

Direction

Active

Low/High

Tristate

Output

Pull

Up/Down

Trigger

Input

Open

Drain/Source

Page 33

Table 2. Pin Characteristics of the eZ80™ Webserver-i (Continued)

Pin # Symbol Direction

Reset

Direction

Active

Low/High

Tristate

Output

eZ80L92 Product Specification

Schmitt

Pull

Up/Down

Trigger

Input

Open

Drain/Source

21

8 V

SS

9 ADDR6

10 ADDR7

11 ADDR8

12 ADDR9

13 ADDR10

14 ADDR11

15 ADDR12

16 ADDR13

17 ADDR14

18 V

19 V

DD

SS

20 ADDR15

21 ADDR16

22 ADDR17

23 ADDR18

24 ADDR19

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

25 ADDR20

26 ADDR21

27 ADDR22

28 ADDR23

29 CS0

30 CS1

31 CS2

32 CS3

33 V

34 V

DD

SS

35 DATA0

PS013011-0204 PRELIMINARY Architectural Overview

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

I/O O N/A Yes No No No

O O Low No No No No

O O Low No No No No

O O Low No No No No

O O Low No No No No