Page 1

eZ80F92 Development Kit

User Manual

UM013911-0607

Copyright ©2007 by ZiLOG, Inc. All rights reserved.

www.zilog.com

Page 2

eZ80F92 Development Kit

User Manual

ii

Safeguards

The following precautions must be observed when working with the

devices described in this document.

Caution:

Always use a grounding strap to prevent damage resulting from

electrostatic discharge (ESD).

Safeguards UM013911-0607

Page 3

Table of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Kit Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Hardware Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

eZ80F92 Development Board Revision History . . . . . . . . . . . . . . . .3

eZ80Acclaim!

eZ80Acclaim!

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

eZ80F92 Flash Module Interface . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Application Module Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

I/O Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Embedded Modem Socket Interface . . . . . . . . . . . . . . . . . . . . . . . .29

eZ80Acclaim!

LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Push Buttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Console . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2

I

C Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

eZ80F92 Flash Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

eZ80F92 Flash Module Memory . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Reset Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

IrDA Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

®

Development Platform Overview . . . . . . . . . . . . . . . . .4

®

Development Platform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

®

Development Platform Memory . . . . . . . . . . . . . .31

eZ80F92 Development Kit

User Manual

iii

UM013911-0607 Table of Contents

Page 4

eZ80F92 Development Kit

User Manual

iv

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Flash Loader Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Mounting the Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Changing the Power Supply Plug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

ZPAK II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

ZDI Target Interface Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Application Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

ZDS II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Cannot Download Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

No Output on Console Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

IrDA Port Not Working . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Schematic Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Appendix A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

General Array Logic Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

eZ80Acclaim!

®

Development Platform . . . . . . . . . . . . . . . . . . . . . 61

eZ80F92 Flash Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

U10 Address Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

U15 Address Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table of Contents UM013911-0607

Page 5

Introduction

The eZ80F92 Development Kit provides a general-purpose platform for

evaluating the capabilities and operation of ZiLOG’s eZ80F92 microcontroller. The eZ80F92 is a member of ZiLOG’s eZ80Acclaim!

line, which offers on-chip Flash capability. The eZ80F92 Development

Kit features two primary boards: the eZ80Acclaim!

form and the eZ80F92 Flash Module. This arrangement provides a full

development platform when using both boards. It can also provide a

smaller-sized reference platform with the eZ80F92 Flash Module as a

stand-alone development tool.

Kit Features

eZ80F92 Development Kit

User Manual

1

®

product

®

Development Plat-

1

The key features of the eZ80F92 Development Kit are:

•

eZ80Acclaim!® Development Platform:

– Up to 2 MB fast SRAM (12 ns access time; 1 MB factory-

installed, with 512 KB on module, 512 KB on platform)

– Embedded modem socket with a U.S. telephone line interface

2

C EEPROM

–I

2

C configuration register

–I

– GPIO, logic circuit, and memory headers

– Supported by ZiLOG Developer Studio II and the eZ80Acclaim!

C-Compiler

– LEDs, including a 7 x 5 LED matrix

– Platform configuration jumpers

1. Other members of the eZ80Acclaim!® product line include the eZ80F91 and eZ80F93 microcontrollers. A scaled-down eZ80F92 Ethernet Module is also available. Contact your local ZiLOG

Sales Office for more information.

UM013911-0607 Introduction

®

Page 6

eZ80F92 Development Kit

User Manual

2

– Two RS232 connectors—console, modem

– RS485 connector with cable assembly

– ZiLOG Debug Interface (ZDI)

– JTAG Debug Interface

– 9 VDC power connector

– Telephone jack

•

eZ80F92 Flash Module:

– eZ80F92 microcontroller

– 512 KB off-chip SRAM

– Real-Time Clock with Battery Back-Up

•

ZPAK II Debug Interface

2

operating at 20 MHz, with

128 KB + 256 bytes internal Flash and 8 KB internal SRAM

•

eZ80F92 Development Kit Software and Documentation CD-ROM

Hardware Specifications

Table 1 lists the specifications of the eZ80Acclaim!® Development Platform.

Table 1. eZ80Acclaim!

Hardware Specifications

Operating Temperature: 20ºC ±5ºC

Operating Voltage: 9 VDC

2. Also available is the eZ80F93 microcontroller, which features 64 KB of internal Flash memory

and 4 KB of internal SRAM. Please contact your local ZiLOG Sales Office

Introduction UM013911-0607

®

Development Platform

for details.

Page 7

eZ80F92 Development Kit

eZ80F92 Development Board Revision History

99C0858-001 Rev C or later:

10/20/03 - Updated layout and added reset fix.

05/30/06 - The following components are not populated on the board:

– U11: Triac, SCR Phone Line D0-214

– U26 and U27: IC RS485, XCVR, Low PWR, 8-SOIC

– C3 and C4: CAP 1000pF Ceramic Disc 1KV

– D1 and D3: Diode LED Amber 0805 SMT

– T1: Inductor Ferrite Bead, 2x15 Turns

– J1: Conn HDR/Pin 1x32 2mm socket

– J5: Conn HDR/Pin 1x2 2mm socket

– J9: Conn HDR/Pin 1x9 2mm socket

– P4: Conn RJ14 Jack 6-Pos 4-CKT

– P5: Conn 9-CKT Cir rt-angl PC Mount

User Manual

3

UM013911-0607 Kit Features

Page 8

eZ80F92 Development Kit

User Manual

4

eZ80Acclaim!® Development Platform Overview

The purpose of the eZ80Acclaim!® Development Platform is to provide

the developer with a set of tools for evaluating the features of the

eZ80Acclaim!

cation before building application hardware.

®

family of devices, and to be able to develop a new appli-

The eZ80F92 Development Kit features two primary boards: the

eZ80Acclaim!

®

Development Platform and the eZ80F92 Flash Module.

This arrangement provides a full development platform when using both

boards. It can also provide a smaller-sized reference platform with the

eZ80F92 Flash Module as a stand-alone development tool.

The eZ80Acclaim!

ber of application-specific modules and Z8- and eZ80Acclaim!

®

Development Platform is designed to accept a num-

®

-based

add-on modules, including the eZ80F92 Flash Module, which features a

real-time clock, an IrDA transceiver, and the eZ80F92 microcontroller.

®

The eZ80Acclaim!

Development Platform, together with its plugged-in

eZ80F92 Flash Module, can operate in stand-alone mode with Flash

memory, or interface via the ZPAK II emulator to a host PC running

ZiLOG Developer Studio II Integrated Development Environment (ZDS

IDE) software.

The address bus, data bus, and all eZ80F92 Flash Module control signals

are buffered on the eZ80Acclaim!

®

Development Platform to provide suf-

ficient drive capability.

Introduction UM013911-0607

Page 9

eZ80F92 Development Kit

User Manual

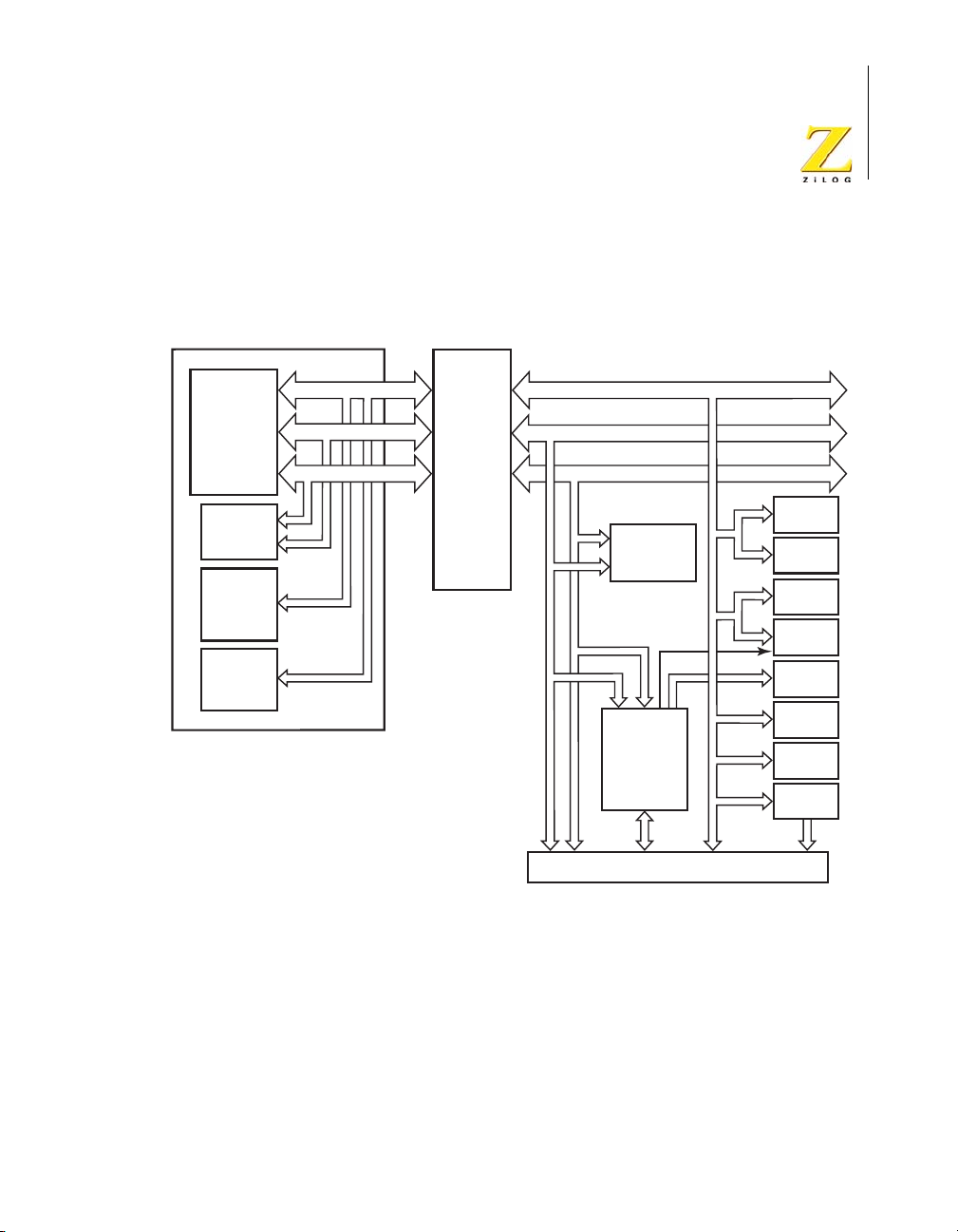

A block diagram of the eZ80Acclaim!® Development Platform and the

eZ80F92 Flash Module is shown in Figure 1.

5

eZ80F92

SRAM

(512 KB)

Battery &

Oscillator

for RTC

IrDA

Transceiver

Peripheral Device Signals

Address Bus

Data Bus

eZ80“

Flash MPU

Module

Interface

Peripheral Device Signals

Address Bus

Data Bus

SRAM

(512 KB

up to 2 MB)

GPIO

and

Address

Decoder

Application Module Headers

Figure 1. eZ80Acclaim!® Development Platform Block Diagram

with eZ80F92 Flash Module

RS232-0

(Console)

RS485

RS232-1

(Modem)

Embedded

Modem

LED

(7x5 matrix)

Push-

buttons

2

I C

EEPROM

2

I C

Register

UM013911-0607 eZ80Acclaim!® Development Platform Overview

Page 10

eZ80F92 Development Kit

User Manual

6

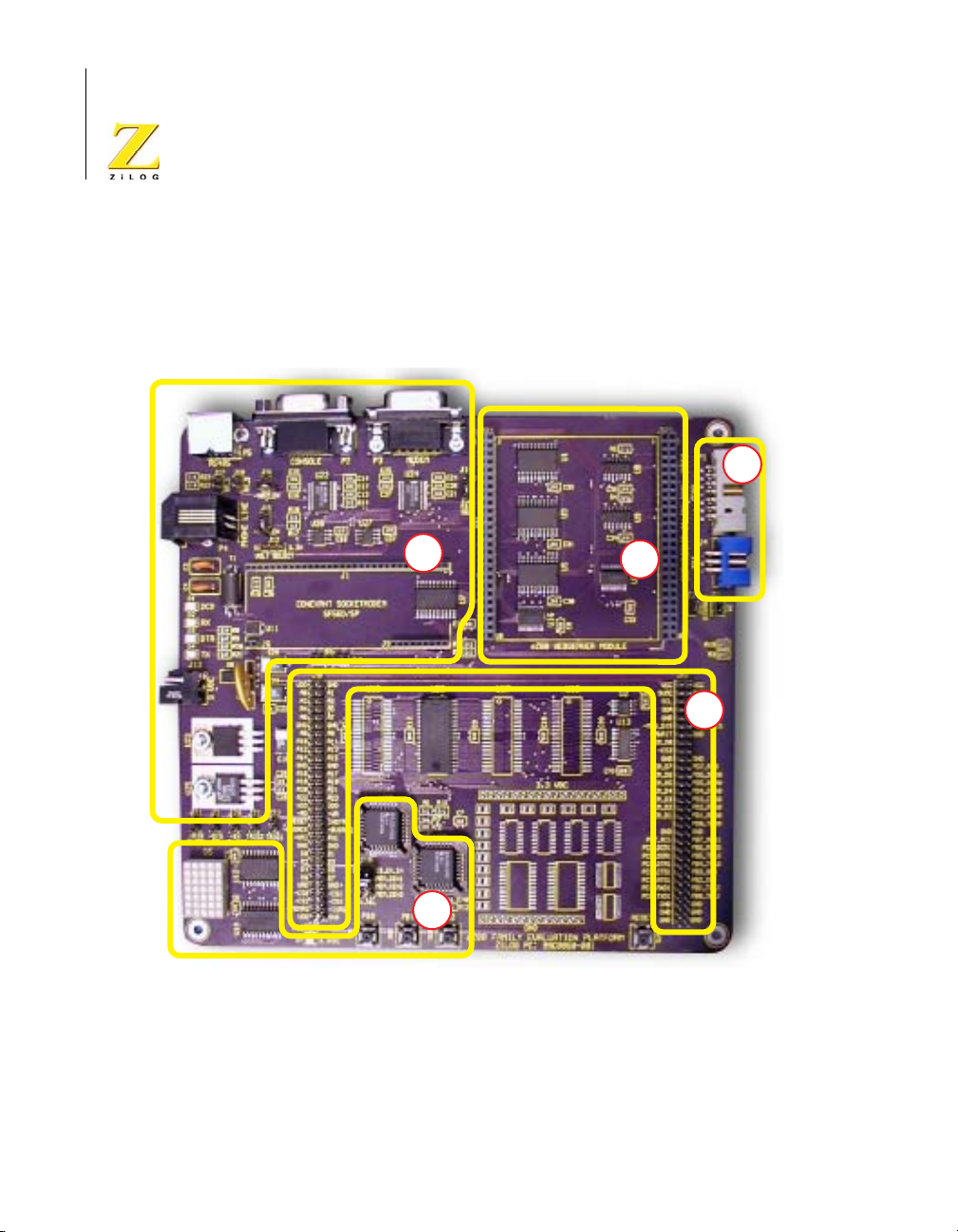

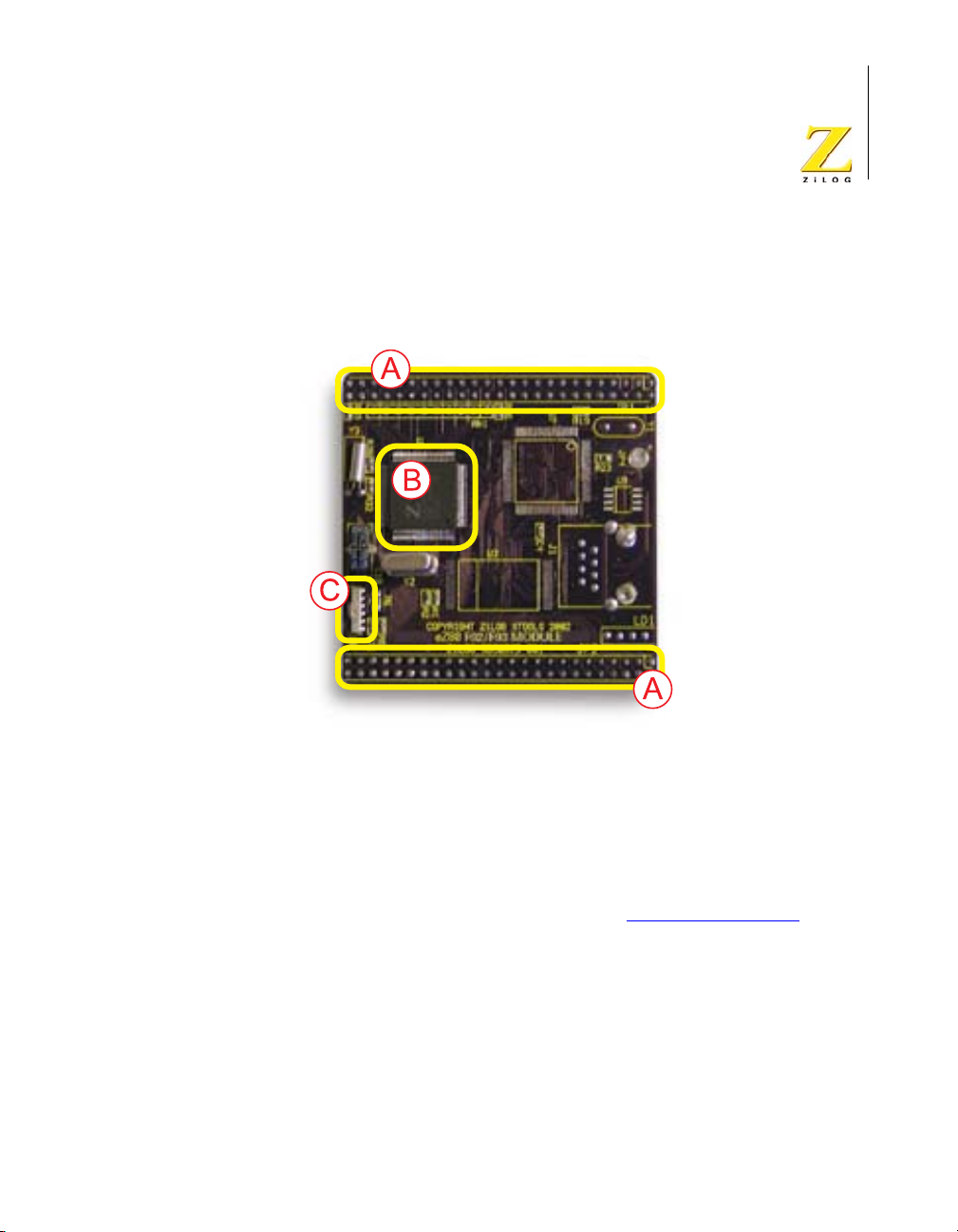

Figure 2 is a photographic representation of the eZ80Acclaim!® Development Platform segmented into its key blocks, as shown in the legend for

the figure.

C

Note: Key to blocks A–E.

A. Power and serial communications.

B. eZ80F92 Flash Module interface.

C. Debug interface.

Figure 2. The eZ80Acclaim!® Development Platform

A

B

D

E

D. Application module interfaces.

E. GPIO and LED with Address Decoder.

Introduction UM013911-0607

Page 11

eZ80F92 Development Kit

User Manual

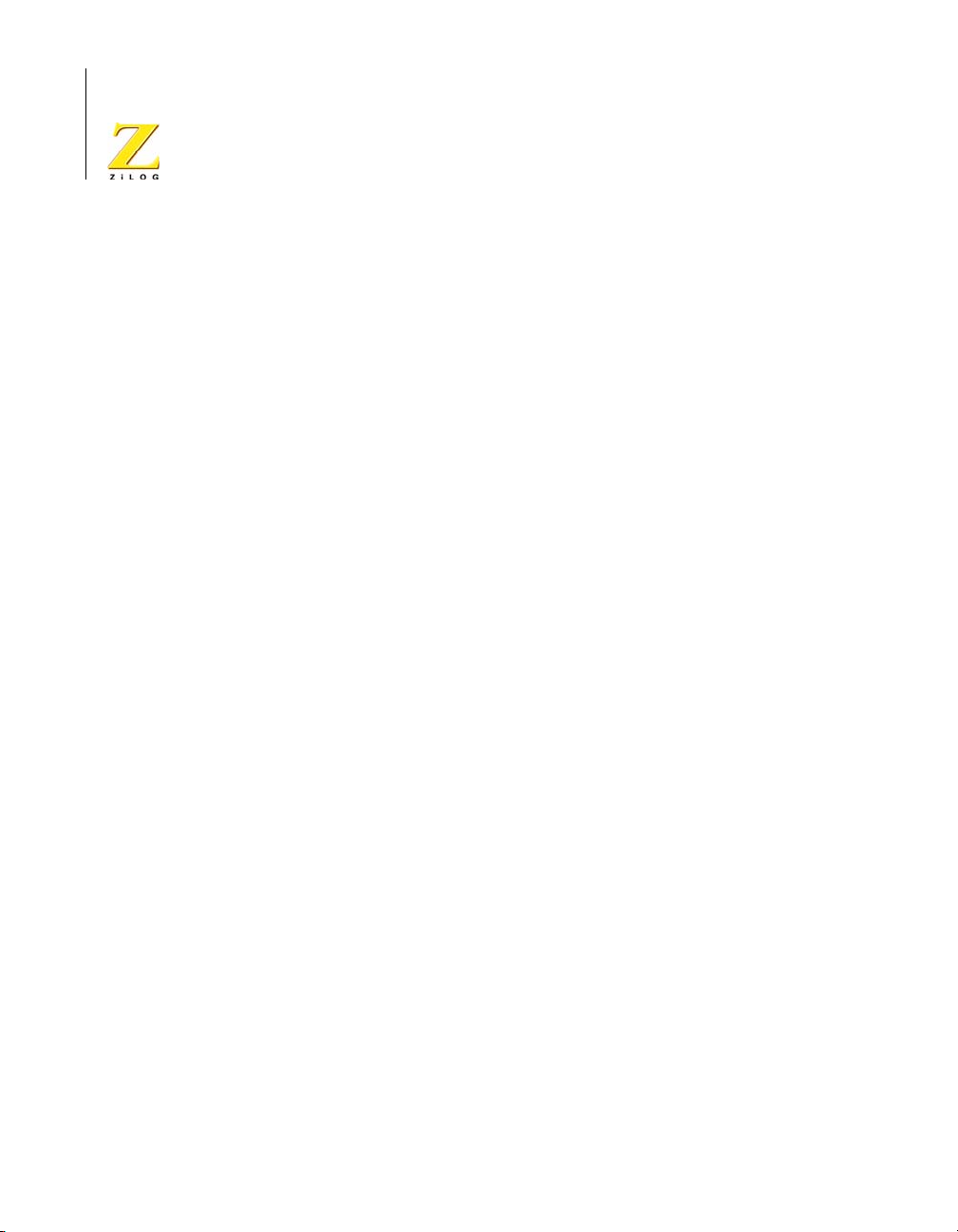

Figure 3 is a photographic representation of the eZ80F92 Flash Module

segmented into its key blocks, as shown in the legend for the figure.

7

Note: Key to blocks A–C.

A. eZ80F92 Flash Module interfaces.

B. CPU.

C. IrDA transceiver.

Figure 3. The eZ80F92 Flash Module

The structures of the eZ80Acclaim!

eZ80F92 Flash Module are illustrated in the Schematic Diagrams

®

Development Platform and the

starting

on page 61.

UM013911-0607 eZ80Acclaim!® Development Platform Overview

Page 12

eZ80F92 Development Kit

User Manual

8

eZ80Acclaim!® Development Platform

This section describes the eZ80Acclaim!® Development Platform hardware, its key components and its interfaces, including detailed programmer interface information such as memory maps, register definitions, and

interrupt usage.

Functional Description

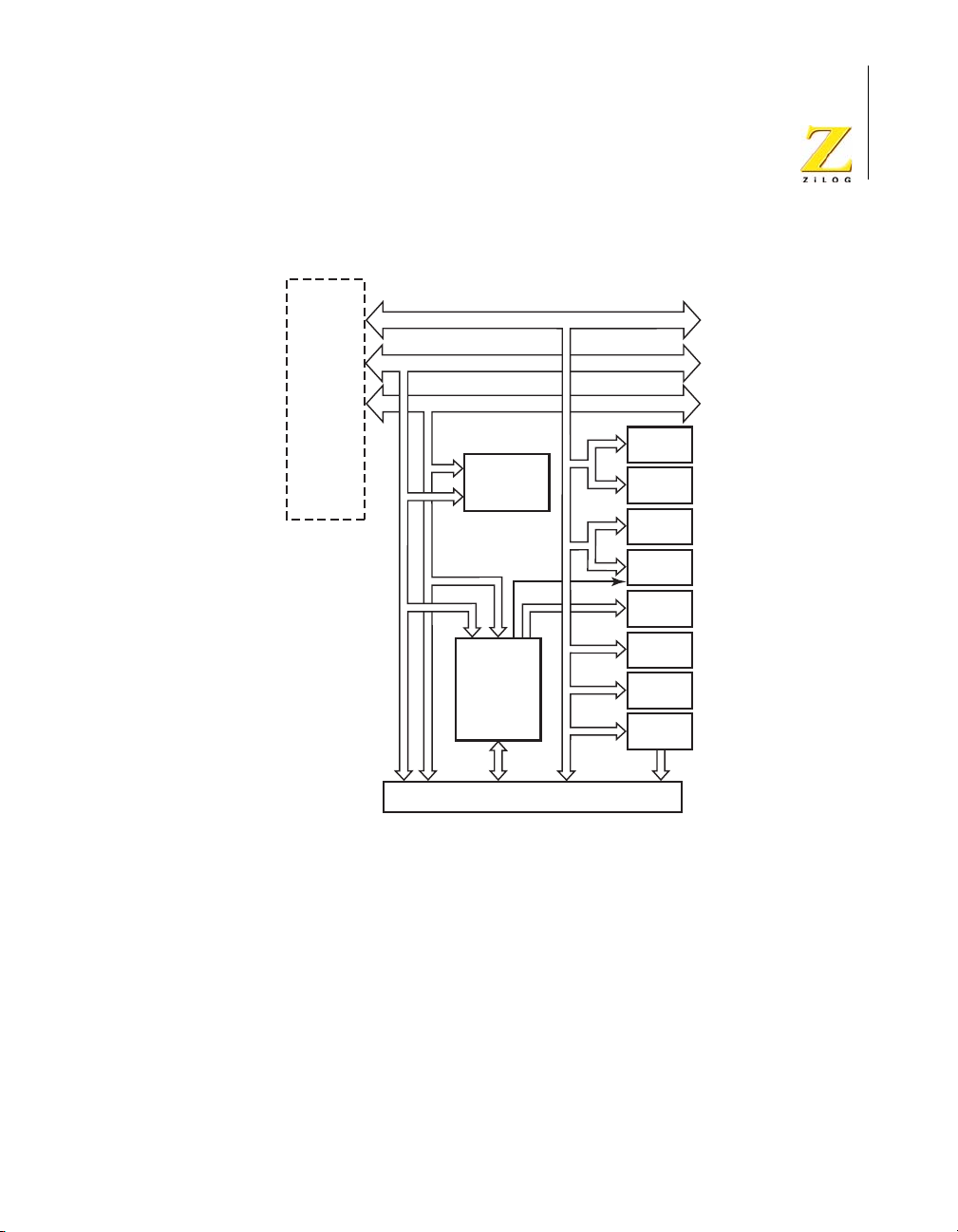

The eZ80Acclaim!® Development Platform consists of seven major hardware blocks. These blocks, listed below, are diagrammed in Figure 4.

•

eZ80F92 Flash Module interface (2 female headers)

•

Power supply for the eZ80Acclaim!® Development Platform, the

eZ80F92 Flash Module, and application modules

•

Application Module interface (2 male headers)

•

GPIO and LED matrix

•

RS232 serial communications ports

•

Embedded modem interface

•

I2C devices

eZ80Acclaim!® Development Platform UM013911-0607

Page 13

Peripheral Device Signals

eZ80F92 Development Kit

User Manual

9

eZ80“

Flash MPU

Module

Interface

Address Bus

Data Bus

SRAM

(512 KB

up to 2 MB)

GPIO

and

Address

Decoder

RS232-0

(Console)

RS485

RS232-1

(Modem)

Embedded

Modem

LED

(7x5 matrix)

Push-

buttons

2

I C

EEPROM

2

I C

Register

Application Module Headers

Figure 4. Basic eZ80Acclaim!® Development Platform Block Diagram

UM013911-0607 Functional Description

Page 14

eZ80F92 Development Kit

User Manual

10

Physical Dimensions

The dimensions of the eZ80Acclaim!® Development Platform PCB is

177.8 mm x 182.9 mm. The overall height is 38.1 mm. See Figure 5.

175.3 mm

43.2 mm

96.5 mm 55.9 mm

114.3 mm

157.5 mm

167.6 mm

5.1 mm

165.1 mm

5.1 mm

Figure 5. Physical Dimensions of the eZ80Acclaim!® Development Platform

eZ80Acclaim!® Development Platform UM013911-0607

Page 15

Operational Description

eZ80F92 Development Kit

User Manual

11

The eZ80Acclaim!® Development Platform can accept any

®

eZ80Acclaim!

correctly to the eZ80Acclaim!

the eZ80Acclaim!

-core-based modules, provided that the module interfaces

®

®

Development Platform is to provide the application

Development Platform. The purpose of

developer with a tool to evaluate the features of the eZ80F92 Flash MCU,

and to develop an application without building additional hardware.

eZ80F92 Flash Module Interface

The eZ80F92 Flash Module interface provides easy connection of the

eZ80F92 Flash Module. It also provides easy connection for any

eZ80Acclaim!

modules using future eZ80Acclaim!

ules using current eZ80Acclaim!

The eZ80F92 Flash Module interface consists of two 50-pin receptacles,

JP1 and JP2.

Peripheral Bus Connector

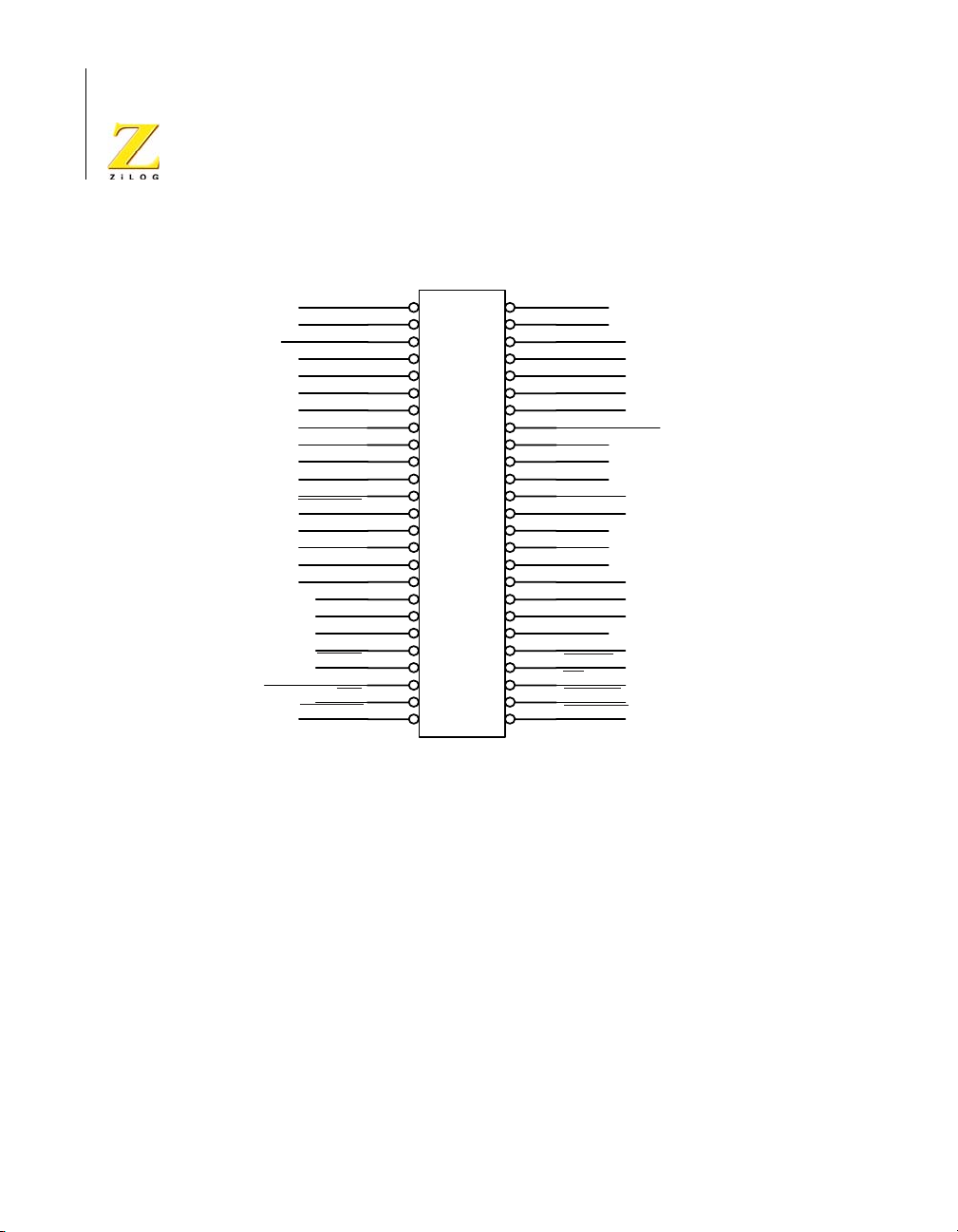

Figure 6 illustrates the pin layout of the Peripheral Bus Connector in the

50-pin header, located at position JP1 on the eZ80Acclaim!

ment Platform. Table 2 describes the pins and their functions.

®

-based module designed to this interface. This includes

®

devices.

®

devices, and user-developed mod-

®

Develop-

UM013911-0607 Operational Description

Page 16

eZ80F92 Development Kit

User Manual

12

A6

A10

GND_EXT

A8

A13

A15

A18 A1 6

A19

A2

A11

A4

A5

DIS_ETH

A21

A22

CS0

CS2

D1

D3

D5

D7

MREQ

GND_EXT

WR

BUSACK

JP1

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

HEADER 25X2

IDC50

A0

A3

V3.3_EXT

A7

A9

A14

GND_EXT

A1

A12

A20

A17

DIS_FLASH

V3.3_EXT

A23

CS1

D0

D2

D4

GND_EXT

D6

IOREQ

RD

INSTRD

BUSREQ

Figure 6. eZ80Acclaim!® Development Platform

Peripheral Bus Connector Pin Configuration—JP1

eZ80Acclaim!® Development Platform UM013911-0607

Page 17

eZ80F92 Development Kit

Table 2. eZ80Acclaim!® Development Platform

Peripheral Bus Connector Identification—JP1*

User Manual

13

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

1 A6 Bidirectional Yes

2 A0 Bidirectional Yes

3 A10 Bidirectional Yes

4 A3 Bidirectional Yes

5GND

6V

DD

7 A8 Bidirectional Yes

8 A7 Bidirectional Yes

9 A13 Bidirectional Yes

10 A9 Bidirectional Yes

11 A15 Bidirectional Yes

12 A14 Bidirectional Yes

13 A18 Bidirectional Yes

14 A16 Bidirectional Yes

15 A19 Bidirectional Yes

2

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

3. External capacitive loads on RD

to satisfy the timing requirements for the eZ80

either V

reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in

the eZ80F92’s Peripheral Power-Down Register.

or GND, depending on their inactive levels to reduce power consumption and to

DD

, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF

®

CPU. All unused inputs should be pulled to

UM013911-0607 Operational Description

Page 18

eZ80F92 Development Kit

User Manual

14

Table 2. eZ80Acclaim!

®

Development Platform

Peripheral Bus Connector Identification—JP1* (Continued)

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

16 GND

17 A2 Bidirectional Yes

18 A1 Bidirectional Yes

19 A11 Bidirectional Yes

20 A12 Bidirectional Yes

21 A4 Bidirectional Yes

22 A20 Bidirectional Yes

23 A5 Bidirectional Yes

24 A17 Bidirectional Yes

25 DIS_ETH

26 EN_FLASH

Output Low No

Output Low No

27 A21 Bidirectional Yes

28 V

DD

29 A22 Bidirectional Yes

2

30 A23 Bidirectional Yes

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

3. External capacitive loads on RD

to satisfy the timing requirements for the eZ80

either V

reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in

the eZ80F92’s Peripheral Power-Down Register.

or GND, depending on their inactive levels to reduce power consumption and to

DD

, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF

®

CPU. All unused inputs should be pulled to

eZ80Acclaim!® Development Platform UM013911-0607

Page 19

eZ80F92 Development Kit

User Manual

15

Table 2. eZ80Acclaim!

®

Development Platform

Peripheral Bus Connector Identification—JP1* (Continued)

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

31 CS0 Input Low Yes

32 CS1 Input Low Yes

33 CS2 Input Low Yes

34 D0 Bidirectional Yes

35 D1 Bidirectional Yes

36 D2 Bidirectional No

37 D3 Bidirectional Yes

38 D4 Bidirectional Yes

39 D5 Bidirectional Yes

40 GND

41 D7 Bidirectional Yes

42 D6 Bidirectional Yes

43 MREQ

Bidirectional Low Yes

2

44 IORQ

Bidirectional Low Yes

45 GND

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

3. External capacitive loads on RD

to satisfy the timing requirements for the eZ80

either V

reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in

the eZ80F92’s Peripheral Power-Down Register.

or GND, depending on their inactive levels to reduce power consumption and to

DD

, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF

®

CPU. All unused inputs should be pulled to

UM013911-0607 Operational Description

Page 20

eZ80F92 Development Kit

User Manual

16

Peripheral Bus Connector Identification—JP1* (Continued)

Table 2. eZ80Acclaim!

®

Development Platform

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

2

46 RD Bidirectional Low Yes

47 WR

48 INSTRD

49 BUSACK

50 BUSREQ

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

3. External capacitive loads on RD

to satisfy the timing requirements for the eZ80® CPU. All unused inputs should be pulled to

either V

reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in

the eZ80F92’s Peripheral Power-Down Register.

or GND, depending on their inactive levels to reduce power consumption and to

DD

Bidirectional Low Yes

Input Low Yes

Input Pull-Up 10 KΩ; Low Yes

Output Pull-Up 10 KΩ; Low Yes

, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF

eZ80Acclaim!® Development Platform UM013911-0607

Page 21

I/O Connector

eZ80F92 Development Kit

User Manual

17

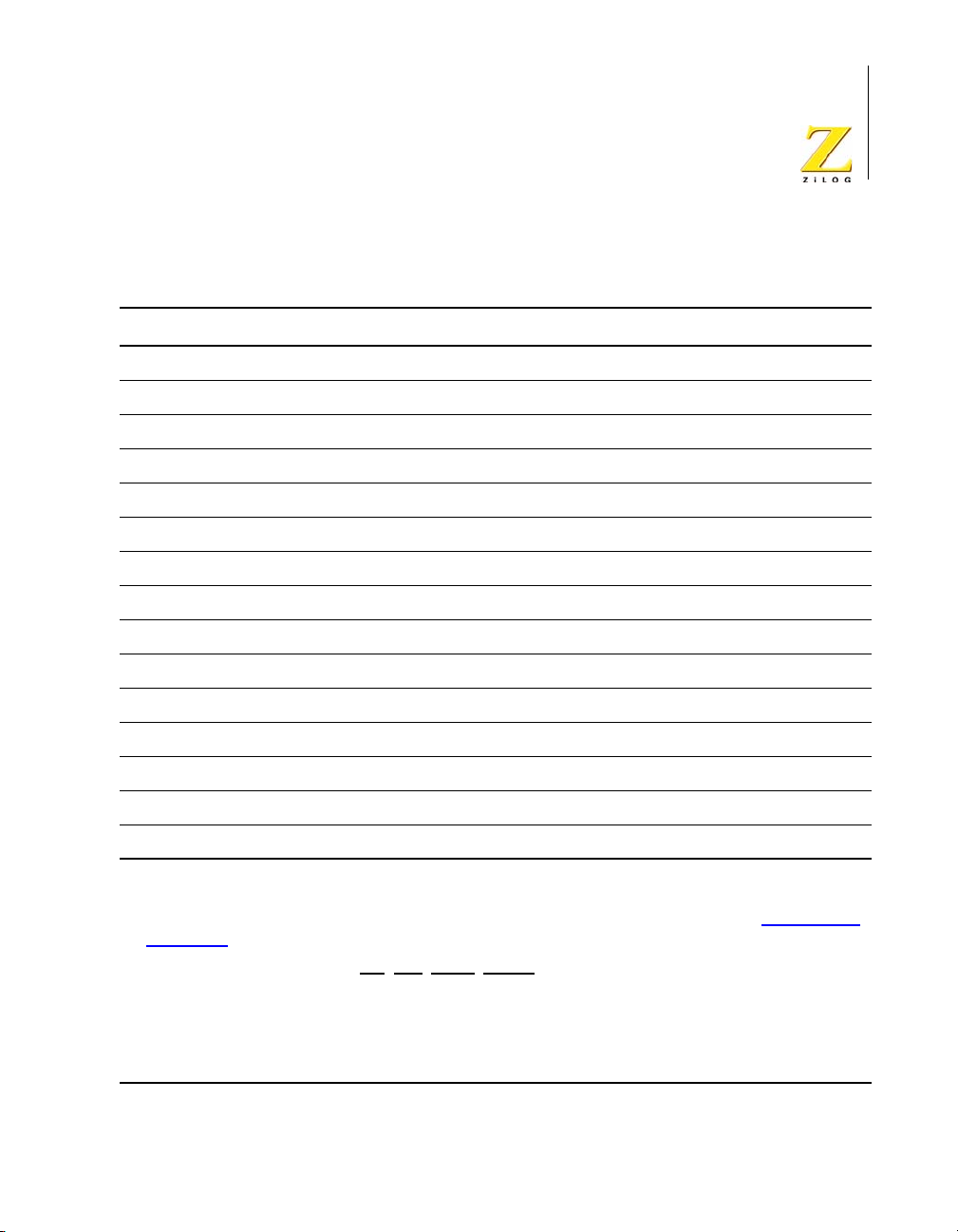

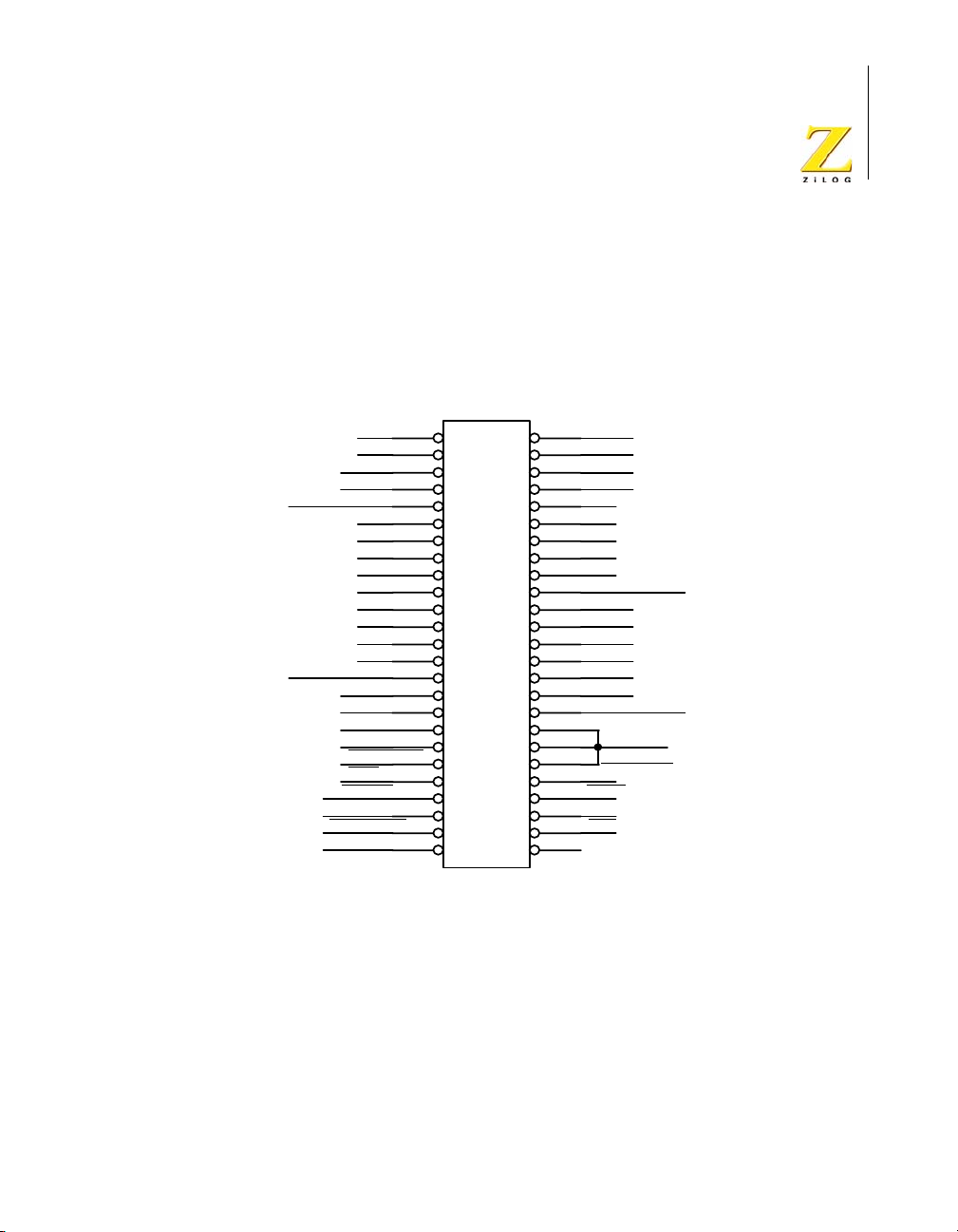

Figure 7 illustrates the pin layout of the I/O Connector in the 50-pin

header, located at position JP2 on the eZ80Acclaim!

®

Development Plat-

form. Table 3 describes the pins and their functions.

PB7

PB5

PB3

PB1

GND_EXT

PC6

PC4

PC2

PC0

PD6

PD5

PD3

PD1

GND_EXT

TCK TMS

RTC_VDD

IICSCL

IICSDA

FLASHWE

CS3

RESET

V3.3_EXT

HALT_SLP

V3.3_EXT

JP2

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

HEADER 25X2

IDC50

PB6

PB4

PB2

PB0

PC7

PC5

PC3

PC1

PD7

GND_EXT

PD4

PD2

PD0

TDITDO

TRIGOUT

EZ80CLK

GND_EXT

DIS_IRDA

WAIT

GND_EXT

NMI

Figure 7. eZ80Acclaim!® Development Platform

I/O Connector Pin Configuration—JP2

UM013911-0607 Operational Description

Page 22

eZ80F92 Development Kit

User Manual

18

Table 3. eZ80Acclaim!® Development Platform

I/O Connector Identification—JP2*

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

1 PB7 Bidirectional Yes

2 PB6 Bidirectional Yes

3 PB5 Bidirectional Yes

4 PB4 Bidirectional Yes

5 PB3 Bidirectional Yes

6 PB2 Bidirectional Yes

7 PB1 Bidirectional Yes

8 PB0 Bidirectional Yes

9GND

10 PC7 Bidirectional Yes

11 PC6 Bidirectional Yes

12 PC5 Bidirectional Yes

13 PC4 Bidirectional Yes

14 PC3 Bidirectional Yes

15 PC2 Bidirectional Yes

2

16 PC1 Bidirectional Yes

17 PC0 Bidirectional Yes

18 PD7 Bidirectional Yes

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

eZ80Acclaim!® Development Platform UM013911-0607

Page 23

eZ80F92 Development Kit

User Manual

19

Table 3. eZ80Acclaim!

®

Development Platform

I/O Connector Identification—JP2* (Continued)

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

19 PD6 Bidirectional

20 GND

21 PD5 Bidirectional Yes

22 PD4 Bidirectional Yes

23 PD3 Bidirectional Yes

24 PD2 Bidirectional Yes

25 PD1 Bidirectional Yes

26 PD0 Bidirectional Yes

27 TDO Input Yes

28 TDI/ZDA Output Yes

29 GND

30 TRIGOUT Input High

31 TCK/ZCL Output Yes

2

32 TMS Output High Yes

33 RTC_V

DD

34 EZ80CLK Input Yes

35 SCL Bidirectional Yes

36 GND

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

UM013911-0607 Operational Description

Page 24

eZ80F92 Development Kit

User Manual

20

Table 3. eZ80Acclaim!

®

Development Platform

I/O Connector Identification—JP2* (Continued)

Pin # Symbol Signal Direction Active Level eZ80F92 Signal

37 SDA Bidirectional Yes

38 GND

39 FlashWE

Output Low No

40 GND

41 CS3

42 DIS_IrDA

43 RESET

44 WAIT

45 V

DD

Input Low Yes

Output Low No

Bidirectional Low Yes

Output Pull-Up 10 KΩ; Low Yes

46 GND

47 HALT_SLP

48

49 V

NMI

DD

Input Low Yes

Output Low Yes

50 Reserved

2

Notes:

1. For the sake of simplicity in describing the interface, Power and Ground nets are omitted from

this table. The entire interface is represented in the eZ80F92 Module Schematics on pages 65

through 67.

2. The Power and Ground nets are connected directly to the eZ80F92 device.

Almost all of the connectors’ signals are received directly from the CPU.

Three input signals, in particular, offer options to the application developer by disabling certain functions of the eZ80F92 Flash Module.

eZ80Acclaim!® Development Platform UM013911-0607

Page 25

These three inputs are:

•

Enable Flash (EN_FLASH)*

•

Flash Write Enable (FlashWE)*

•

Disable IrDA (DIS_IrDA)

These three signals are described below.

Enable Flash*

eZ80F92 Development Kit

User Manual

21

When active Low, the EN_FLASH

the eZ80F92 Flash Module.

Flash Write Enable*

When active Low, the FlashWE

the Flash boot block of the eZ80F92 Flash Module.

Disable IrDA

When the DIS_IrDA

input signal is pulled Low, the IrDA transceiver,

located on the eZ80F92 Flash Module, is disabled. As a result, UART0

can be used with the RS232 or the RS485 interfaces on the

®

Development Platform.

Note:

eZ80Acclaim!

*These inputs are only used if external Flash is present on the eZ80F92

Flash Module (as shipped from the factory, external Flash is not

installed).

Application Module Interface

An Application Module Interface is provided to allow the user to add an

application-specific module to the eZ80Acclaim!

form. ZiLOG’s Thermostat Application Module (not provided in the kit)

is an example application-specific module that demonstrates an HVAC

control system. Implementing an application module with the Application

Module Interface requires that the eZ80F92 Flash Module also be

input signal enables the Flash chip on

input signal enables Write operations on

®

Development Plat-

UM013911-0607 Operational Description

Page 26

eZ80F92 Development Kit

User Manual

22

mounted on the eZ80Acclaim!® Development Platform, because the

eZ80F92 Flash Module features the eZ80F92 microcontroller. To mount

an application module, use the two male headers J6 and J8.

Jumper J6 carries the General Purpose Input/Output ports (GPIO), and

jumper J8 carries memory and control signals. To design an application

module, the user should be familiar with the architecture and features of

the eZ80F92 Flash Module currently installed. Tables 4 and 5 list the signals and functions related to each of these jumpers by pin. Power and

ground signals are omitted for the sake of simplicity.

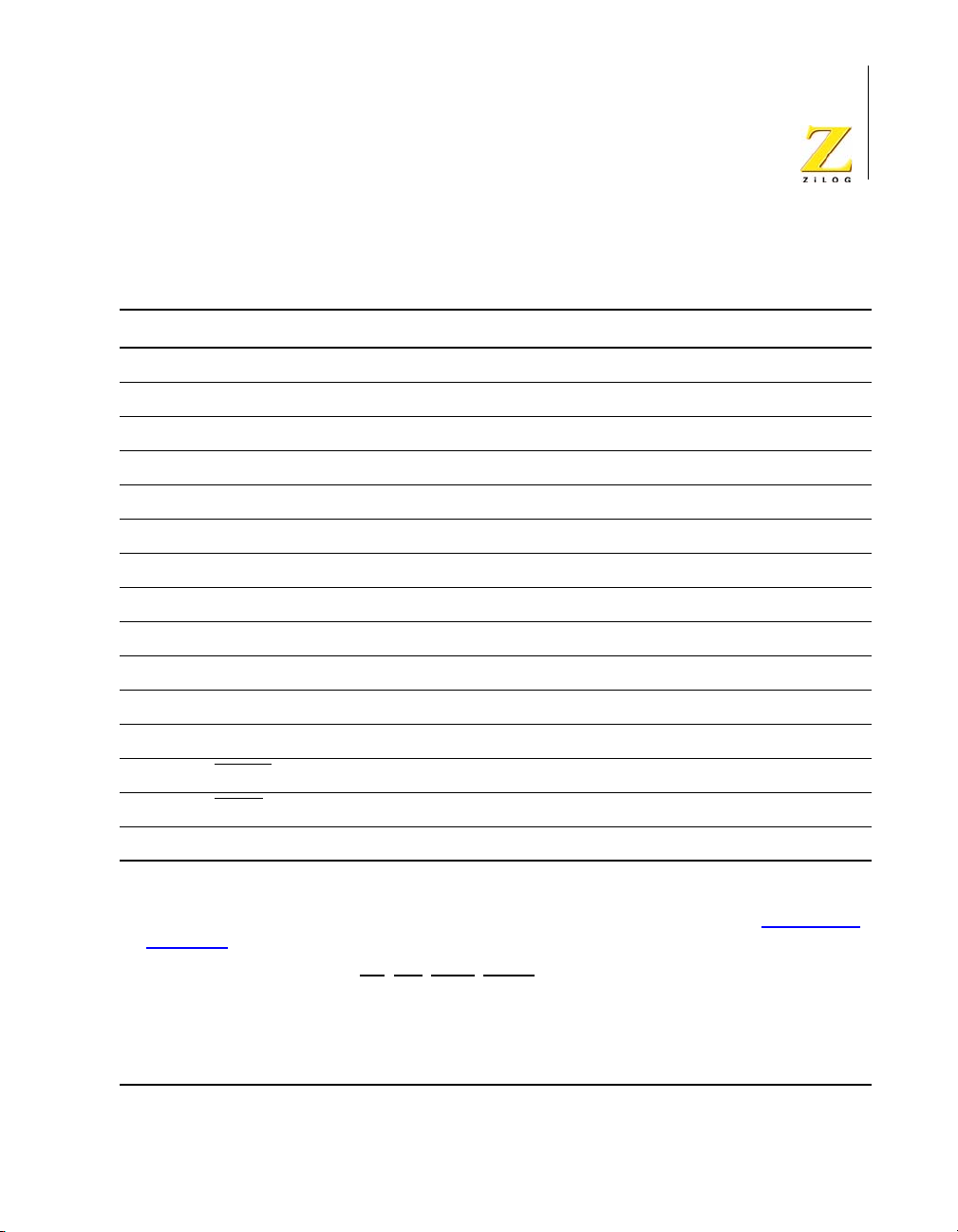

Table 4. GPIO Connector J6*

Signal Pin # Function Direction Notes

SCL 5 I

SDA 7 I

2

C Clock Bidirectional

2

C Data Bidirectional

MOD_DIS 9 Modem Disable Input If a shunt is installed between

pins 6 and 9, the modem

function on the eZ80Acclaim!

Development Platform is

disabled.

MWAIT 13 Wait signal for the

CPU

EM_D0 15 Emulated Port A,

Bit 0

CS3 17 Chip Select 3 of

the CPU

EM_D[7:1] 21,23,25,

27,29,31,

33

Reserved 35

Note: *All of the signals are driven directly by the CPU.

eZ80Acclaim!® Development Platform UM013911-0607

Emulated Port A,

Bit [7:1]

Input

Bidirectional

Output This signal is also present on

the J8.

Bidirectional

®

Page 27

eZ80F92 Development Kit

Table 4. GPIO Connector J6* (Continued)

Signal Pin # Function Direction Notes

User Manual

23

PC[7:0] 39,41,43,

Port C, Bit [7:0] Bidirectional

45,47,49,

51,53

®

ID_[2:0] 6,8,10 eZ80Acclaim!

Output

Development

Platform ID

CON_DIS 12 Console Disable Input If a shunt is installed between

pins 12 and 14, the Console

function on the eZ80Acclaim!

Development Platform is

disabled.

Reserved 16,18

PD[7:0] 22,24,26,

Port D, Bit[7:0] Bidirectional

28,30,32,

34,36

PB[7:0] 40,42,44,

Port B, Bit[7:0] Bidirectional

46,48,50,

52,54

Note: *All of the signals are driven directly by the CPU.

®

UM013911-0607 Operational Description

Page 28

eZ80F92 Development Kit

User Manual

24

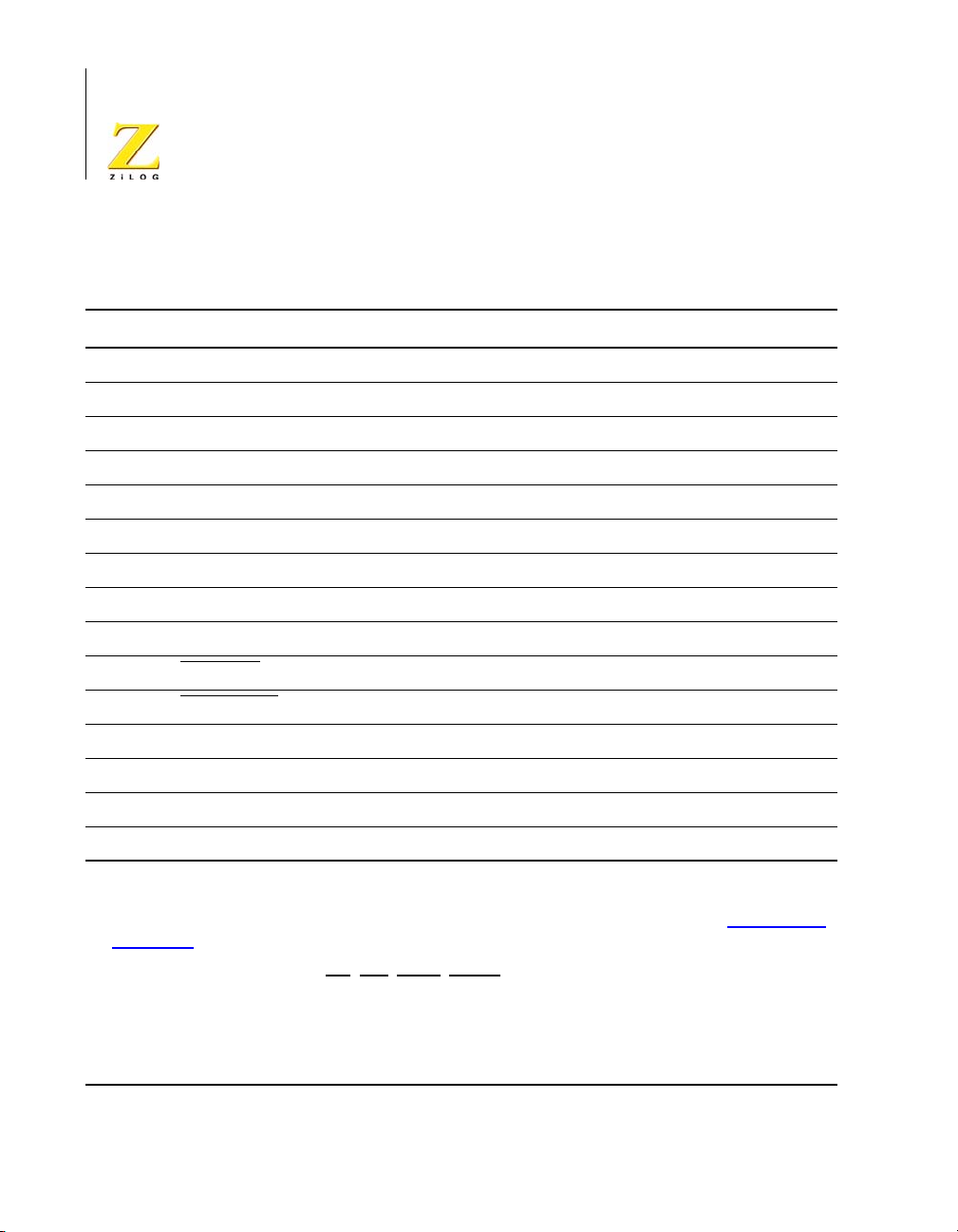

Signal Pin # Function Direction

A[0:7] 3–10 Address Bus, Low Byte Output

A[8:15] 13–20 Address Bus, High Byte Output

A[16:23] 23–30 Address Bus, Upper Byte Output

RD 33 Read Signal Output

Table 5. CPU Bus Connector J8*

RESET

BUSACK

NMI

D[0:7] 43–50 Data Bus Bidirectional

CS[0:3] 53–56 Chip Selects

MREQ

WR

INSTRD

BUSREQ

PHI 40 Clock output of the CPU Output

Note: *All of the signals except BUSACK and INSTRD are driven by low-voltage

CMOS technology (LVC) drivers.

35 Push Button Reset Output

37 CPU Bus Acknowledge Signal Output

39 Nonmaskable Interrupt Input

57 Memory Request Output

34 WRITE Signal Output

36 Instruction Fetch Output

38 CPU Bus Request signal

I/O Functionality

The eZ80190 microprocessor features General-Purpose I/O functionality

at Port A. The eZ80F92 device does not incorporate this Port A feature.

The eZ80Acclaim!

tionality, featuring GPIO for devices without Port A, an LED matrix, a

modem reset, and two user triggers.

®

Development Platform provides additional I/O func-

eZ80Acclaim!® Development Platform UM013911-0607

Page 29

eZ80F92 Development Kit

User Manual

These functions are memory-mapped with an address decoder based on

the Generic Array Logic GAL22lV10D (U15) device manufactured by

Lattice Semiconductor, and a bidirectional latch (U16). Additionally, U15

is used to decode addresses for access to the 7 x 5 LED matrix.

Table 6 lists the memory map addresses to registers that allow access to

the above functions. The register at address

800000h controls GPIO Port

A Output Control and LED Anode register functions. The register at

address

modem reset, and user triggers. Address

800001h controls the register functions for the LED cathode,

800002h controls GPIO Port A

data.

Table 6. LED and Port Emulation Addresses

Address Register Function Access

800000h LED Anode/GPIO Port output control WR

800001h LED Cathode/Modem/Trig WR

800002h GPIO Data RD/WR

25

Port A Emulation

GPIO Port A is emulated with the use of the GPIO Output Control Register and the GPIO Data Register. If bit 7 in the GPIO Output Control Register is 1, all of the lines on GPIO Port A are configured as input ports. If

this bit is 0, all of the lines on Port A are configured as output ports.

Table 7 lists the multiple functions of the register.

Table 7. LED Anode/GPIO Port A Output Control Register

Bit #

Function

Anode Col 1 X

Anode Col 2 X

Anode Col 3 X

UM013911-0607 Operational Description

76543210

Page 30

eZ80F92 Development Kit

User Manual

26

Table 7. LED Anode/GPIO Port A Output Control Register (Continued)

Bit #

Function

Anode Col 4 X

Anode Col 5 X

Anode Col 6 X

Anode Col 6 X

GPIO Output X

76543210

The GPIO Data Register receives inputs or provides outputs for each of

the seven GPIO Port A lines, depending on the configuration of the port.

See Table 8.

Table 8. GPIO Data Register

Function/Bit # 76543210

GPIO D0 X

GPIO D1 X

GPIO D2 X

GPIO D3 X

GPIO D4 X

GPIO D5 X

GPIO D6 X

GPIO D7 X

LED Matrix

The one 7 x 5 LED matrix device on the eZ80Acclaim!

®

Development

Platform is a memory-mapped device that can be used to display information, such as programmed alphanumeric characters. For example, the

eZ80Acclaim!® Development Platform UM013911-0607

Page 31

eZ80F92 Development Kit

User Manual

LED display sample program that is shipped with this kit displays the

alphanumeric message:

eZ80

To illuminate any LED in the matrix, its respective anode bit must be set

to 1 and its corresponding cathode bit must be set to 0.

Bits 0–6 in Table 7 are LED anode bits. They must be set High (1) and

their corresponding cathode bits, bits 0–4 in Table 9, must be set Low (0)

to illuminate each of the LED’s, respectively.

Bit 7 in Table 7 does not carry any significance within the LED matrix. It

is used for GPIO as a Port A control bit.

Table 9 indicates the multiple register functions of the LED cathode,

modem, and triggers. This table shows the bit configuration for each cathode bit. Bits 5, 6, and 7 do not carry any significance within the LED

matrix. These three bits are control bits for the modem reset, Trig1, and

Trig2 functions, respectively.

27

Table 9. Bit Access to the LED Cathode, Modem, and Triggers

Bit #

Function

Cathode Row 5 X

Cathode Row 4 X

Cathode Row 3 X

Cathode Row 2 X

Cathode Row 1 X

Modem RST X

Trig 1 X

Trig 2 X

UM013911-0607 Operational Description

76543210

Page 32

eZ80F92 Development Kit

User Manual

28

An LED display sample program is shipped with the eZ80F92 Development Kit. Please refer to the eZ80Acclaim!™ Development Kits Quick

Start Guide (QS0020) or to the Tutorial section in the ZiLOG Developer

Studio—eZ80Acclaim!™ User Manual (UM0144).

Modem Reset

The Modem Reset signal, MRESET, is used to reset an optional socket

modem. This signal is controlled by bit 5 in the register shown in Table 9.

The MRESET signal is available at the embedded modem socket interface (J9, Pin 1). Setting this bit Low places the optional socket modem

into a reset state. The user must pull this bit High again to enable the

socket modem. Reference the appropriate documentation for the socket

modem to reset timing requirements.

User Triggers

Two general-purpose trigger output pins are provided on the

eZ80Acclaim!

®

Development Platform. Labeled J21 (Trig2) and J22

(Trig1), these pins allow the user a way to trigger external equipment to

aid in the debug of the system. See Figure 8 for trigger pin details.

J21

Trig2

Figure 8. Trigger Pins J21 and J22

J22

Ground

Trigger output

Trig1

Bits 6 and 7 in Table 9 are the control bits for the user triggers. If either bit

is a 1, the corresponding Trig1 and Trig2 signals are driven High. If either

bit is 0, the corresponding Trig1 and Trig2 signals are driven Low.

eZ80Acclaim!® Development Platform UM013911-0607

Page 33

Embedded Modem Socket Interface

The eZ80Acclaim!® Development Platform features a socket for an

optional 56K modem (a modem is not included in the kit).

Connectors J1, J5, and J9 provide connection capability. The modem

socket interface provided by these three connectors is shown in Figure 9.

Tables 10 through 12 identify the pins for each connector. The embedded

modem utilizes UART1, which is available via the Port C pins.

eZ80F92 Development Kit

User Manual

29

J5

12

2

J9

1

3

6

7

8

9

J1

4

24

25

26

27

28

29

30

31

32

Figure 9. Embedded Modem Socket Interface—J1, J5, and J9

Table 10. Connector J5

Pin Symbol Description

1 M-TIP Telephone Line Interface—TIP.

2 M-RING Telephone Line Interface—RING.

UM013911-0607 Operational Description

Page 34

eZ80F92 Development Kit

User Manual

30

Table 11. Connector J9

Pin Symbol Description

1 MRESET Reset, active Low, 50–100 ms. Closure to GND for reset.

3 GND Ground.

6 D1 DCD indicator; can drive an LED anode without additional circuitry.

7 D2 RxD indicator; can drive an LED anode without additional circuitry.

8 D3 DTR indicator; can drive an LED anode without additional circuitry.

9 D4 TxD indicator; can drive an LED anode without additional circuitry.

Table 12. Connector J1

Pin Symbol Description

2 MOD_DIS Modem disable, active Low.

4V

24 GND Ground.

25 PC4_DTR1 DTR interface; TTL levels.

26 PC6_DCD1 DCD interface; TTL levels.

27 PC3_CTS1 CTS interface; TTL levels.

28 PC5_DSR1 DSR interface; TTL levels.

29 PC7_RI1 Ring Indicator interface; TTL levels.

30 PC0_TXD1 TxD interface; TTL levels.

31 PC1_RXD1 RxD interface; TTL levels.

32 PC2_RTS1 RTS interface; TTL levels.

eZ80Acclaim!® Development Platform UM013911-0607

CC

+5 VDC or +3.3 VDC input.

Page 35

eZ80F92 Development Kit

User Manual

31

Components P4, T1, C3, C4, and U11 provide the phone line interface to

the modem. On the eZ80Acclaim!

®

Development Platform, LEDs D1,

D2, D3, and D4 function as status indicators for this optional modem.

The phone line connection for the modem is for the United States only.

Connecting the modem outside of the U.S. requires modification.

The tested modem for this eZ80F92 Development Kit is a MultiTech Systems (formerly Conexant) socket modem, part number SC56H1. Either

the 3.3 V or the 5.0 V version of the modem can be used. However, jumper

J12 should be configured accordingly—see Table 17. Information about

this modem and its interface is available in the SocketModem data sheet

from www.multitech.com

.

eZ80Acclaim!® Development Platform Memory

Memory space on the eZ80Acclaim!® Development Platform consists of

onboard SRAM and additional SRAM footprints.

Onboard SRAM

The eZ80Acclaim!

U20. This SRAM provides the basic memory requirement for small applications development. This SRAM is in the address range

BFFFFFh. With the 512 KB of SRAM on the eZ80F92 Flash Module, this

addressing structure provides 1 MB of contiguous SRAM for immediate

use. Chip Select 2 is used to access the 512 KB of SRAM on the

eZ80Acclaim!

®

Development Platform features 512 KB SRAM at

®

Development Platform.

B80000h–

Additional SRAM

The amount of eZ80Acclaim!

®

Development Platform memory can be

extended if required by adding SRAM devices. U19, U18, and U17 provide this capability. However, the user should be aware that additional

SRAM must be installed in the following order:

1. U19, address range

UM013911-0607 Operational Description

B00000h–B7FFFFh

Page 36

eZ80F92 Development Kit

User Manual

32

2. U18, address range A80000h–AFFFFFh

3. U17, address range A00000h–A7FFFFh

If SRAM memory is installed in a different order than the above

sequence, SRAM will not be contiguous unless the user is able to change

the address decoder, U10. Memory access decoding is performed by this

address decoder, implemented in the Generic Array Logic device,

GAL22LV10D (U10).

On-Chip SRAM

The eZ80F92 device on the eZ80F92 Flash Module contains 8 KB of onchip SRAM. Upon power-up, this SRAM is enabled and mapped to the

top 8 KB of memory address space. Using the RAM Address Register,

this 8 KB memory can be mapped to the top of any 64 KB block. It can

also be disabled. Please see the eZ80F92/eZ80F92 Product Specification

(PS0153) for more information.

Flash Memory

The eZ80F92 Development Kit allows off-chip Flash memories between

1 MB and 4 MB. This Flash memory is entirely located on the eZ80F92

Flash Module (in footprint only; as shipped from the factory, external

Flash is not installed).

Memory Map

A memory map of the eZ80

®

CPU is illustrated in Figure 10. Flash memory and SRAM on the eZ80F92 Flash Module are addressed when CS0

and CS1 are active Low. SRAM on the eZ80Acclaim!

®

Development

Platform is addressed when CS2 is active Low.

The location of on-chip SRAM is programmable by setting the RAM

address upper byte register. The upper 8 KB of any 64 KB memory page

can be selected. Addresses to enabled on-chip memories assume priority

over all chip selects. Please refer to the eZ80F92/eZ80F92 Product Specification (PS0153) for more details.

eZ80Acclaim!® Development Platform UM013911-0607

Page 37

eZ80F92 Development Kit

User Manual

33

On-chip

SRAM

Off-chip

Flash memory

Off-chip

Flash memory

FFFFFFh

FFE000h

Available

Address Space

DFFFFFh

SRAM Memory

up to 2 MB

C7FFFFh

C00000h

BFFFFFh

B80000h

Platform Expansion

SRAM Memory up to 4 MB

80FFFFh

800000h

7FFFFFh

Expansion Module:

Flash Memory up to 4 MB

400000h

3FFFFFh

Module Expansion

Flash Memory up to 4 MB

120000h

11FFFFh

Flash Memory

8 KB

CS1

Module SRAM

Platform SRAM (512 KB)

CS2

LED & GPIO

Up to 4 MB

CS0 (8 MB)

Up to 4 MB

1 MB

020000h

On-chip

Flash memory

01FFFFh

000000h

128 KB

Figure 10. Memory Map of the eZ80Acclaim!® Development Platform

and eZ80F92 Flash Module

UM013911-0607 Operational Description

Page 38

eZ80F92 Development Kit

User Manual

34

LEDs

As stated earlier, LEDs D1, D2, D3, and D4 function as status indicators

for an optional modem. This section describes each LED and the LED

matrix device.

Data Carrier Detect

The Data Carrier Detect (DCD) signal at D1 indicates that a good carrier

signal is being received from the remote modem.

RX

The RX signal at D2 indicates that data is received from the modem.

Data Terminal Ready

The Data Terminal Ready (DTR) signal at D3 informs the modem that the

PC is ready.

TX

The TX signal at D4 indicates that data is transmitted to the modem.

Push Buttons

The eZ80Acclaim!® Development Platform provides user controls in the

form of push buttons. These push buttons serve as input devices to the

eZ80F92 microcontroller. The programmer can use them as necessary for

application development. All push buttons are connected to the GPIO

Port B pins.

PB0

The PB0 push button switch, SW1, is connected to bit 0 of GPIO Port B.

This switch can be used as the port input if required by the user.

eZ80Acclaim!® Development Platform UM013911-0607

Page 39

PB1

The PB1 push button switch, SW2, is connected to bit 1 of GPIO Port B.

This switch can be used as the port input if required by the user.

PB2

The PB2 push button switch, SW3, is connected to bit 2 of GPIO Port B.

This switch can be used as the port input if required by the user.

RESET

The Reset push button switch, SW4, resets the eZ80

eZ80Acclaim!

Jumpers

The eZ80Acclaim!® Development Platform provides a number of jumpers that are used to enable or disable functionality on the platform, enable

or disable optional features, or to provide protection from inadvertent use.

®

Development Platform.

eZ80F92 Development Kit

User Manual

®

CPU and the

35

Jumper J2

The J2 jumper connection enables/disables IrDA transceiver functionality. When the shunt is placed, IrDA communication is disabled. See

Table 13.

Table 13. J2—DIS_IrDA

Shunt

Status Function Affected Device

In IrDA interface disabled UART0 is configured to work with the RS232 or the

RS485 interfaces.

Out IrDA interface enabled The IrDA and UART0 interfaces on the eZ80F92 Flash

Module perform their functions.

UM013911-0607 Operational Description

Page 40

eZ80F92 Development Kit

User Manual

36

Jumper J3

The J3 jumper connection controls Port A emulation mode and communication with the 7 x 5 LED. When the shunt is placed, Port A emulation is

disabled. See Table 14.

Table 14. J3—DIS_EM

Shunt

Status Function Affected Device

In Application Module

Hardware Disabled

Out Application Module

Hardware Enabled

Communication with 7 x 5 LED and Port emulation

circuit is disabled.

Communication with 7 x 5 LED and Port A emulation

circuit is enabled.

Jumper J7

The J7 jumper connection controls Flash boot loader programming. When

the shunt is placed, overwriting of the Flash boot loader program is

enabled. See Table 15.

Table 15. J7—FlashWE

Shunt

Status Function Affected Device

Out The Flash boot sector of the eZ80F92

Flash Module is write-protected.

In The Flash boot sector of the eZ80F92

Flash Module is enabled for writing or

overwriting.

Note: As shipped from the factory, external Flash memory is not installed.

(Off-Chip)*

Flash boot sector of the eZ80F92 Flash

Module.

Flash boot sector of the eZ80F92 Flash

Module.

eZ80Acclaim!® Development Platform UM013911-0607

Page 41

eZ80F92 Development Kit

User Manual

Jumper J11

The J11 jumper connection controls access to the off-chip Flash memory

device. When the shunt is placed, access to this Flash device is enabled.

See Table 16.

Note:

The silk-screened label on the eZ80Acclaim!

®

Development Platform for

jumper J11 is incorrect. Currently, it reads DIS_FLASH. The correct label

is EN_FLASH.

Table 16. J11—EN_FLASH (Off-Chip)*

Shunt

Status Function Affected Device

IN All access to external Flash memory on the

eZ80190 Module is enabled.

OUT All access to external Flash memory on the

eZ80F92 Module is disabled.

Note: As shipped from the factory, external Flash memory is not installed.

External Flash memory on the

eZ80190 Module.

External Flash memory on the

eZ80190 Module.

37

Jumper J12

The J12 jumper connection controls the selection of a 5 V or 3 VDC power

supply to the embedded modem, if an embedded modem is used. See

Table 17.

Table 17. J12—5VDC/3.3VDC for an Embedded Modem

Shunt

Status Function Affected Device

1–2 5 VDC is provided to power the embedded modem. Embedded modem.

2–3 3.3 VDC is provided to power the embedded modem. Embedded modem.

UM013911-0607 Operational Description

Page 42

eZ80F92 Development Kit

User Manual

38

Jumper J14

The J14 jumper connection controls the polarity of the Ring Indicator. See

Table 18.

Table 18. J14—RI

Shunt

Status Function Affected Device

1–2 The Ring Indicator for UART1 is inverted. UART1.

2–3 The Ring Indicator for UART1 is not inverted. UART1.

Jumper J15

The J15 jumper connection controls the selection RS485 circuit along

with UART0. When the shunt is placed, the RS485 circuit is enabled. See

Table 19. RS485 functionality will be available in future eZ80Acclaim!

devices.

®

Table 19. J15—RS485_1_EN*

Shunt

Status Function Affected Device

In The RS485 circuit is enabled on UART0.

The UART0 CONSOLE interface and IrDA are

disabled.

Out The RS485 circuit is disabled on UART0. IrDA, UART0 CONSOLE

Note: *To enable the RS485 circuit, the corresponding IrDA/RS232 circuit must be disabled.

eZ80Acclaim!® Development Platform UM013911-0607

IrDA, UART0 CONSOLE

interface, RS485 interface.

interface, RS485 interface.

Page 43

eZ80F92 Development Kit

User Manual

Jumper J16

The J16 jumper connection controls the selection of the RS485 circuit.

However, UART1 MODEM interface and the socket modem interface are

disabled if the RS485 circuit is enabled. When the shunt is placed, the

RS485 circuit is enabled. See Table 20.

Table 20. J16—RS485_2_EN

Shunt

Status Function Affected Device

39

In The RS485 circuit is enabled on UART1.

The UART1 MODEM interface and the

Socket Modem interface are disabled.

Out The RS485 circuit is disabled on UART1. UART1 MODEM interface,

UART1 MODEM interface,

Socket Modem Interface, and

RS485 interface.

Socket Modem Interface, and

RS485 interface.

Jumper J17

The J17 jumper connection controls the selection of the RS485 termination resistor circuit. When the shunt is placed, the RS485 termination

resistor circuit is enabled. See Table 21.

Table 21. J17—RT_1*

Shunt

Status Function Affected Device

In The Termination Resistor for RS485_1 is IN. RS485 interface.

Out The Termination Resistor for RS485_1 is OUT. RS485 interface.

Note: *Before enabling the termination resistor, ensure that the device is located at the end of the

interface line.

UM013911-0607 Operational Description

Page 44

eZ80F92 Development Kit

User Manual

40

Jumper J18

The J18 jumper connection controls the selection of the RS485 termination resistor circuit. When the shunt is placed, the RS485 termination

resistor circuit is enabled. See Table 22.

Table 22. J18—RT_2*

Shunt

Status Function Affected Device

In The Termination Resistor for RS485_2 is IN. RS485 interface.

Out The Termination Resistor for RS485_2 is OUT. RS485 interface.

Note: *Before enabling the termination resistor, ensure that the device is located at the end of the

interface line.

Jumper J19

The J19 jumper connection selects the range of memory addresses for the

external chip select signal, CS_EX

, to the application module. See

Table 23.

Table 23. J19—EX_SEL

Shunt

Status Function Affected Device

1–2 CS_EX

located in the address range 400000h–7FFFFFh.

3–4 CS_EX

located in the address range A00000h–A7FFFFh.

5–6 CS_EX

located in the address range A80000h–AFFFFFh.

7–8 CS_EX

located in the address range B00000h–B7FFFFh.

eZ80Acclaim!® Development Platform UM013911-0607

is decoded in the CS0 memory space and is

is decoded in the CS2 memory space and is

is decoded in the CS2 memory space and is

is decoded in the CS2 memory space and is

Application module

addressing.

Application module

addressing.

Application module

addressing.

Application module

addressing.

Page 45

eZ80F92 Development Kit

User Manual

Jumper J20

The J20 jumper connection controls the selection of the external chip

select in the external application module. When the shunt is placed, the

external chip select signal, CS_EX

Table 24. J20—EX_FL_DIS

Shunt

Status Function Affected Device

IN The jumper for EX_FL_DIS is IN. The chip select on the application module

, is disabled. See Table 24.

is disabled.

41

OUT

The jumper for EX_FL_DIS is OUT.

Connectors

A number of connectors are available for connecting external devices

such as the ZPAK II emulator, PC serial ports, external modems, the console, and LAN/telephone lines.

J6 and J8 are the headers, or connectors, that provide pin-outs to connect

any external application module, such as ZiLOG’s Thermostat Application Module.

Connector J6

The J6 connector provides pin-outs to make use of GPIO functionality.

Connector J8

The J8 connector provides pin-outs to access memory and other control

signals.

The chip select on the application module

is enabled.

UM013911-0607 Operational Description

Page 46

eZ80F92 Development Kit

User Manual

42

Console

Connector P2 is the RS232 terminal, which can be used for observing the

console output. P2 can be connected to the HyperTerminal if required.

Modem

Connector P3 provides a terminal for connecting an external modem, if

used with the eZ80F92 Development Kit. RS485 functionality will be

available in future eZ80Acclaim!

I2C Devices

The two I2C devices on the eZ80Acclaim!® Development Platform are the

U2 EEPROM and the U13 Configuration register. The EEPROM provides 16 KB of memory. The Configuration register provides access to

control the configuration of an application-specific function at the Application Module Interface. Neither device is utilized by the eZ80F92 Development Kit software. The user is free to develop proprietary software for

these two devices. The addresses for accessing these devices are listed in

Table 25.

®

devices.

Table 25. I2C Addresses

Device/Bit # 76543210

EEPROM (U10)* 10100A1A0R/W

Configuration Register (U13)1001110R/W

Note: *EEPROM address bits A0 and A1 are configured for 0s.

eZ80Acclaim!® Development Platform UM013911-0607

Page 47

DC Characteristics

Understanding proper DC current requirements for the eZ80Acclaim!®

Development Platform when application modules are plugged into it is

very important for developing applications. This section provides an estimate of the average current requirement when different combinations of

these application modules are plugged in to the eZ80Acclaim!

ment Platform.

The receiver supply current is 90–150 µA and the transmitter supply current is 260 mA when the LED is active. The measurements of current that

are shown in Table 26 are for the user’s reference. These values can vary

depending on the type of application that is developed to run with the

platform.

Table 26. DC Current Characteristics of the

eZ80Acclaim!

®

Development Platform with Different Module Loads

eZ80F92 Development Kit

User Manual

®

Develop-

43

Current

Platform/Modules Configurations

eZ80Acclaim!

and eZ80F92 Flash Module

eZ80Acclaim!

eZ80F92 Flash Module, and Modem

Module

eZ80Acclaim!

eZ80F92 Flash Module, and

Thermostat Application Module

eZ80Acclaim!

eZ80F92 Flash Module, Modem

Module, and Thermostat Application

Module

UM013911-0607 DC Characteristics

®

Development Platform

®

Development Platform,

®

Development Platform,

®

Development Platform,

Requirement (mA) Status

173 When connected only to a

power supply, and when

no program is running.

174 When connected only to a

power supply, and when

no program is running.

195 When connected only to a

power supply, and when

no program is running.

203 When connected only to a

power supply, and when

no program is running.

Page 48

eZ80F92 Development Kit

User Manual

44

Table 26. DC Current Characteristics of the

eZ80Acclaim!

Platform/Modules Configurations

®

Development Platform with Different Module Loads (Continued)

Current

Requirement (mA) Status

eZ80Acclaim!® Development Platform

and eZ80F92 Flash Module

eZ80Acclaim!

®

Development Platform,

eZ80F92 Flash Module, and Modem

Module

eZ80Acclaim!

®

Development Platform,

eZ80F92 Flash Module, and

Thermostat Application Module

®

eZ80Acclaim!

Development Platform,

eZ80F92 Flash Module, Modem

Module, and Thermostat Application

Module

325 When the LED demo is

running.

325 When the LED demo is

running.

350 When the LED demo is

running.

360 When the LED demo is

running.

eZ80Acclaim!® Development Platform UM013911-0607

Page 49

eZ80F92 Flash Module

This section describes the eZ80F92 Flash Module hardware, its interfaces

and key components, including the CPU, real-time clock, IrDA transceiver, and memory.

Functional Description

The eZ80F92 Flash Module is a compact, high-performance module specially designed for the rapid development and deployment of embedded

systems. Additional devices such as serial ports, LED matrices, GPIO

ports, and I

eZ80Acclaim!

both of these boards is shown in Figure 1

2

C devices are supported when connected to the

®

Development Platform. A block diagram representing

eZ80F92 Development Kit

User Manual

45

on page 5.

The eZ80F92 Flash Module is developed to be a plug-in module to the

eZ80Acclaim!

vides a CPU, RAM, an IrDA transceiver, and a real-time clock. This lowcost, expandable module is powered by the eZ80F92 microcontroller,

members of ZILOG’s new eZ80Acclaim!

also contains a battery and an oscillator in support of the on-chip RealTime Clock (RTC). The eZ80F92 Flash Module can also be used as a

stand-alone development tool when provided with an external power

source.

UM013911-0607 eZ80F92 Flash Module

®

Development Platform. This small-footprint module pro-

®

product family. The module

Page 50

eZ80F92 Development Kit

User Manual

46

Physical Dimensions

The dimensions of the eZ80F92 Flash Module PCB is 64 x 64mm. With an

RJ-45 Ethernet connector, the overall height is 25 mm. See Figure 11.

8.3 mm

max.

2.54 mm

63.5 mm

8.5 mm

1

1

64 mm

Bus Connector

Top View

2.7 mm

6.2 mm

55.88 mm

I/O Connector

9 mm

IrDA

7 mm

Figure 11. Physical Dimensions of the eZ80F92 Flash Module

eZ80F92 Flash Module UM013911-0607

Page 51

eZ80F92 Development Kit

User Manual

Figure 12 illustrates the top layer silkscreen of the eZ80F92 Flash Module.

47

Figure 12. eZ80F92 Flash Module—Top Layer

UM013911-0607 Functional Description

Page 52

eZ80F92 Development Kit

User Manual

48

Figure 13 illustrates the bottom layer silkscreen of the eZ80F92 Flash

Module.

Figure 13. eZ80F92 Flash Module—Bottom Layer

eZ80F92 Flash Module UM013911-0607

Page 53

Operational Description

The purpose of the eZ80F92 Flash Module as a feature of the eZ80F92

Development Kit is to provide the application developer with a plug-in

tool to evaluate the memory, IrDA, and other features of the eZ80F92

device.

eZ80F92 Flash Module Memory

The eZ80F92 Flash Module comprises both off-chip SRAM and on-chip

Flash memory, which are described below.

Static RAM

The eZ80F92 Flash Module features 512 KB of fast SRAM. Access speed

is typically 50 ns, allowing zero-wait-state operation at 20 MHz. With the

CPU at 20 MHz, SRAM can be accessed with zero wait states in eZ80

mode. CS1_CTL (chip select CS1

eZ80F92 Development Kit

User Manual

49

) can be set to 08h (no wait states).

Flash Memory

The eZ80F92 Flash Module features 128 KB of Flash memory. This onchip memory can be programmed a single byte at a time, or in bursts of up

to 128 bytes. Write operations can be performed using either memory or I/

O instructions. Erasing bytes in Flash memory returns them to a value of

FFh. Both the MASS ERASE and PAGE ERASE operations are self-

timed by the Flash controller, leaving the CPU free to execute other operations in parallel. Upon power-up, the on-chip Flash memory is located in

the address range

in Flash control register

On-chip Flash memory is prioritized over all external Chip Selects, can be

enabled or disabled (power-on enabled), and can be programmed within

any 128 KB address space in the 16 MB address range.

The eZ80F92 Flash Module features the following memory configurations:

UM013911-0607 Operational Description

000000h–01FFFFh. Four wait states are programmed

F8h.

Page 54

eZ80F92 Development Kit

User Manual

50

•

•

•

Reset Generator

The onboard Reset Generator Chip is connected to the eZ80F92 Reset

input pin. It performs reliable Power-On Reset functions, generating a

reset pulse with a duration of 200 ms if the power supply drops below

2.93 V. This reset pulse ensures that the board always starts in a defined

condition. The RESET pin on the I/O connector reflects the status of the

RESET line. It is a bidirectional pin for resetting external peripheral components or for resetting the eZ80F92 Development Kit with a low-impedance output (e.g. a 100-Ohm push button).

On-chip SRAM: 8 KB

Off-chip SRAM: 512 KB

On-chip Flash: 128 KB

IrDA Transceiver

An onboard IrDA transceiver (ZiLOG ZHX1810) is connected to PD0

(TX), PD1 (RX), and PD2 (Shutdown, IR_SD). The IrDA transceiver is

of the LED type 870 nm Class 1.

The IrDA transceiver is accessible via the IrDA controller attached to

UART0 on the eZ80F92 device. The UART0 console and the IrDA transceiver cannot be used simultaneously.

To use the UART0 for console or to save power, the transceiver can be

disabled by the software or by an off-board signal when using the proper

jumper selection. The transceiver is disabled by setting PD2 (IR_SD)

High or by pulling the DIS_IRDA

shutdown feature is used for power savings. To enable the IrDA transceiver, DIS_IRDA

The eZ80F92 Flash Module contains a ZiLOG IrDA transceiver that is

connected to the UART0 port. This port can be used as a wireless connection into the eZ80F92 Flash Module. The UART0 can connect to a standard RS232 port, or it can be configured to control the IrDA transceiver;

eZ80F92 Flash Module UM013911-0607

is left floating and PD2 is set to Low.

pin on the I/O connector Low. The

Page 55

eZ80F92 Development Kit

User Manual

however, it cannot do both at the same time. Only a few registers are

required to configure the UART0 port to send and receive IrDA data.

The RxD and TxD signals on the transceiver perform the same functions

as a standard RS232 port. However, these signals are processed as IrDA

3/16 coding pulses (sometimes called IrDA encoder/decoder pulses).

When the IrDA function is enabled, the final output to the RxD and TxD

pins are routed through the 3/16 pulse generator.

Another signal that is used in the eZ80F92 Flash Module’s IrDA system is

Shut_Down (SD). The SD pin is connected to PD2 on the eZ80F92 Flash

Module. The IrDA control software on the user’s wireless device must

enable this pin to wake the IrDA transceiver. The SD pin must be set Low

to enable the IrDA transceiver. On the eZ80F92 Flash Module, a twoinput OR gate is used to allow an external pin to shut down the IrDA

transceiver. Both pins must be set Low to enable this function.

51

Figure 14 highlights the eZ80F92 Flash Module IrDA hardware connections.

External Disable

IrDA

eZ80L92

Device

PD2(IR_SD)

PD1(RxD)

PD0(TxD)

Figure 14. IrDA Hardware Connections

SD

RD

TD

The eZ80F92 Flash Module features an Infrared Encoder/Decoder register that configures the IrDA function. This register is located at address

0BFh in the internal I/O register map.

The Infrared Encoder/Decoder register contains three control bits. Bit 0

enables or disables the IrDA encoder/decoder block. Bit 1, if it is set,

UM013911-0607 Operational Description

Page 56

eZ80F92 Development Kit

User Manual

52

enables received data to pass into the UART0 Receive FIFO data buffer.

Bit 2 is a test function that provides a loopback sequence from the TxD

pin to the RxD input.

Bit 1, the Receive Enable bit, is used to block data from filling up the

Receive FIFO when the eZ80F92 Flash Module is transmitting data.

Because IrDA data passes through the air as a light source, transmitted

data can also be received. This Receive Enable bit prevents this data from

being received. After the eZ80F92 Flash Module completes transmitting,

this bit is changed to allow for incoming messages.

The code that follows provides an example of how this function is

enabled on the eZ80F92 Flash Module.

//Init_IRDA

// Ensure to first set PD2 as a port bit, an output and set it

Low.

PD_ALT1 &= 0xFC; // PD0 = uart0tx, PD1 = uart0_rx

PD_ALT2 |= 0x03; // Enable alternate function

UART_LCTL0= 0x80; // Select dlab to access baud rate

generator

BRG_DLRL0=0x2F; // Baud rate Masterclock/(16*baudrate)

BRG_DLRH0=0x00; // High byte of baud rate

UART_LCTL0=0x00; // Disable dlab

UART_FCTL0=0xC7; // Clear tx fifo, enable fifo

UART_LCTL0=0x03; // 8bit, N, 1 stop

IR_CTL = 0x03; // enable IRDA Encode/decode and Receive

// enable bit.

//IRDA_Xmit

IR_CTL = 0x01; //Disable receive

Putchar(0xb0); //Output a byte to the uart0 port.

eZ80F92 Flash Module UM013911-0607

Page 57

DC Characteristics

eZ80F92 Development Kit

User Manual

53

As different combinations of application modules are loaded onto the

®

eZ80Acclaim!

Development Platform, current requirements change.

Please see Table 26

for these different module combinations.

A 0.1-Farad capacitor is provided on the eZ80F92 Flash Module as a

short-term battery backup for the RTC (see the Schematic Diagrams

page 61). The part number of the capacitor made by Panasonic is

EECS0HDV. The capacitor is connected to RTC_VDD to provide power

to the RTC when main power to the chip is removed; it is also connected

to the 3.3 V supply to the chip for recharging. The RTC can operate down

to 3.0 V; it requires 10 µA of current. The (keep alive) time this capacitor

can supply power to the RTC, from 3.3 V to 3.0 V, is approximately 3000

seconds, or 50 minutes.

Flash Loader Utility

The Flash Loader utility allows the user a convenient way to program onchip Flash memory. Please refer to the External Flash Loader Product

User Guide (PUG0016) for more details.

Mounting the Module

on page 43 to reference current consumption values

on

When mounting the eZ80F92 Flash Module onto the eZ80Acclaim!®

Development Platform, check its orientation to the platform to ensure a

correct fit. Pin 1 of JP1 on the eZ80Acclaim!

must align with pin 1 of JP1 on the eZ80Acclaim!

®

Development Platform

®

Development Platform; Pin 1 of JP2 on the eZ80F92 Flash Module must align with pin 1 of

JP2 on the eZ80Acclaim!

UM013911-0607 DC Characteristics

®

Development Platform, etc.

Page 58

eZ80F92 Development Kit

User Manual

54

Changing the Power Supply Plug

The universal 9VDC power supply offers three different plug configurations and a tool that aids in removing one plug configuration to insert

another, as shown in Figure 15.

Figure 15. 9VDC Universal Power Supply Components

To exchange one plug configuration for another, perform the following

steps:

1. Place the tip of the removal tool into the round hole at the top of the

current plug configuration.

2. Press down to disengage the keeper tab and push the plug configuration out of its slot.

3. Select the plug configuration appropriate for your location, and insert

it into the slot formerly occupied by the previous plug configuration.

4. Push the new plug configuration down until it snaps into place, as

indicated in Figure 16.

eZ80F92 Flash Module UM013911-0607

Page 59

eZ80F92 Development Kit

User Manual

55

Figure 16. Inserting a New Plug Configuration

UM013911-0607 Changing the Power Supply Plug

Page 60

eZ80F92 Development Kit

User Manual

56

ZPAK II

ZPAK II is a debug tool used to develop and debug hardware and software. It is a networked device featuring an Ethernet interface and an

RS232 console port. ZPAK II is shipped with a preconfigured IP address

that can be changed to suit the user on a local network. For more information about using and configuring ZPAK II, please refer to the

eZ80Acclaim! Development Kits Quick Start Guide (QS0020) and the

ZPAK II Product User Guide (PUG0015).

ZDI Target Interface Module

The ZDI Target Interface Module provides a physical interface between

ZPAK II and the eZ80Acclaim!

ule supports ZDI functions. For more information on using the TIM module or ZDI, please refer to the eZ80Acclaim!

Start Guide (QS0019), the eZ80F92 Ethernet Module Product Specification (PS0186), and the eZ80F92 Flash Module Product Specification

(PS0189).

JTAG

Connector P1 is the JTAG connector on the eZ80Acclaim!® Development

Platform. JTAG will be supported in the next offering of eZ80Acclaim!

products.

Application Modules

ZiLOG offers the Thermostat Application module, which can be used for

evaluating and developing process control and simple I/O applications.

The Thermostat Application module is equipped with an LCD display

that can be used to display process control and other physical parameters.

®

Development Platform. The TIM mod-

®

Development Kits Quick

®

ZPAK II UM013911-0607

Page 61

eZ80F92 Development Kit

User Manual

For additional reading about the Thermostat application, please see the

Java Thermostat Demo Application Note (AN0104) on zilog.com

.

57

UM013911-0607 Application Modules

Page 62

eZ80F92 Development Kit

User Manual

58

ZDS II

ZiLOG Developer Studio II (ZDS II) Integrated Development Environment is a complete stand-alone system that provides a state-of-the-art

development environment. Based on the Windows

Win2000-SP4/WinXP Professional user interfaces, ZDS II integrates a

language-sensitive editor, project manager, C-Compiler, assembler,

linker, librarian, and source-level symbolic debugger that supports the

eZ80F92.

For further details about ZDS II for eZ80Acclaim!

to the ZiLOG Developer Studio—eZ80Acclaim!

(UM0144).

®

Vista/Win 98SE/

®

products, please refer

®

User Manual

ZDS II UM013911-0607

Page 63

Troubleshooting

Overview

Before contacting ZiLOG Customer Support to submit a problem report,

please follow these simple steps. If a hardware failure is suspected, contact a local ZiLOG representative for assistance.

Cannot Download Code

eZ80F92 Development Kit

User Manual

59

If you are unable to download code to RAM using ZDS, make sure to

press and release the Reset button on the eZ80Acclaim!

Platform prior to selecting

ZDS.

No Output on Console Port

The eZ80F92 Development Kit is shipped with a Flash Loader utility that

is loaded in the protected boot sector of Flash memory (U3). Upon powerup of the eZ80Acclaim!

MCU Module, the eZ80F92 device on the module starts running code

from this Flash memory area. This code enables the Console port with

settings of 57.6 kbps, 8, N, 1.

The Console checks the Receive buffer. If a space character is received on

the Console port, the Flash Loader utility is enabled and a boot message

should be displayed on your connected device. If no message is displayed,

check the following:

•

Jumper J2 must be ON (IrDA is disabled)

•

On Connector J6, the jumper must be removed from pins 6 and 9 (pin

names con_dis and GND).

®

Development Platform and the eZ80F92 Flash

Debug

→

Reset

and then

®

Development

Debug → Go

in

UM013911-0607 Troubleshooting

Page 64

eZ80F92 Development Kit

User Manual

60

IrDA Port Not Working

If you plan on using the IrDA transceiver on the eZ80F92 Flash Module,

make sure the hardware is set up as follows:

•

Jumper J2 must be OFF (to enable the control gate that drives the

IrDA device)

•

Set port pin PD2 Low. When this port pin and Jumper J2 are turned

OFF, the IrDA device is enabled.

•

Install a jumper on connector J6 across pin names con_dis and GND

to disable the console serial port driver

Troubleshooting UM013911-0607

Page 65

e

Z80F9

2 D

Ki

t

MA10

MA

3

A[23:0]

12

evelopment

User Manual

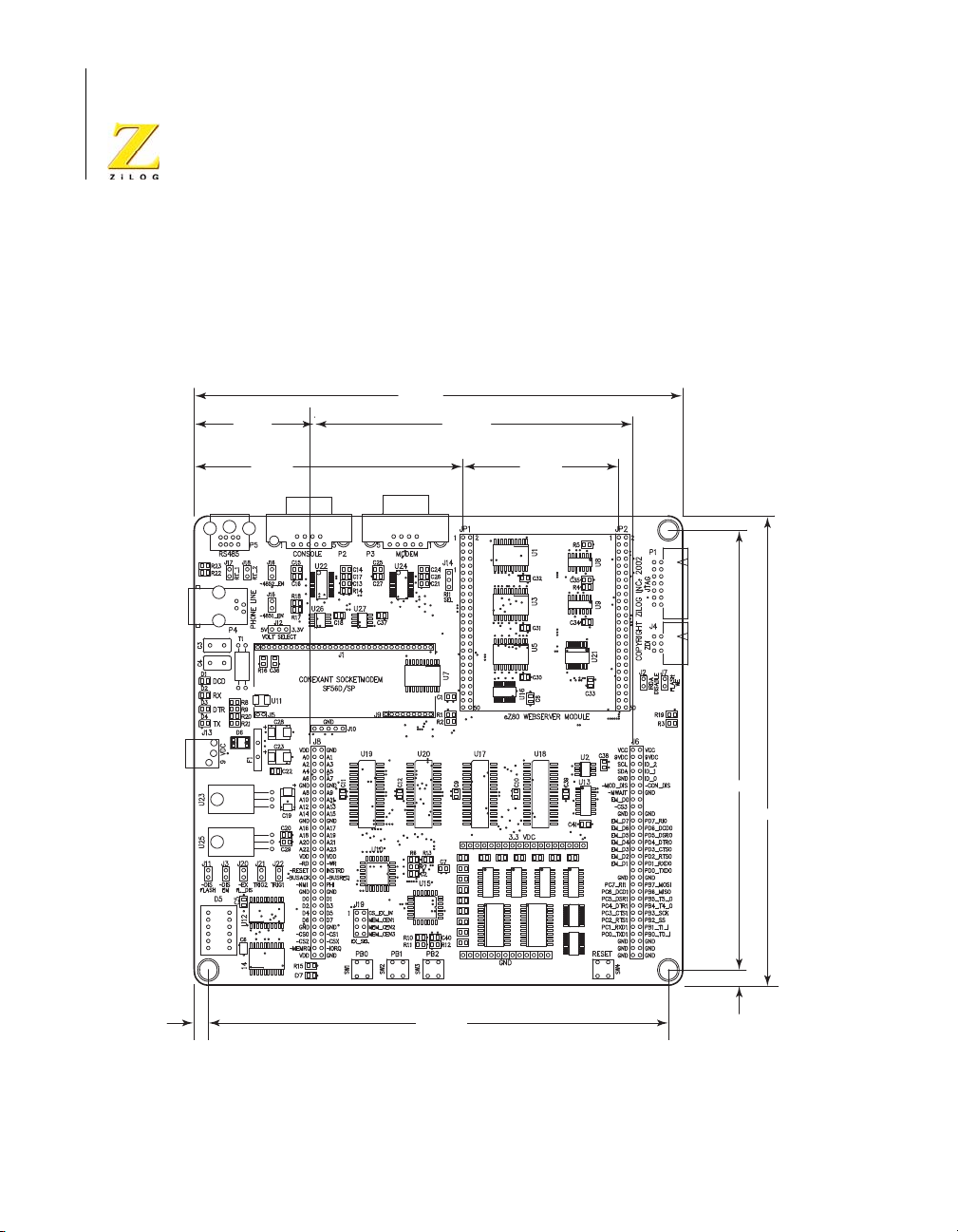

Schematic Diagrams

eZ80Acclaim!® Development Platform

Figures 17 through 20 diagram the layout of the eZ80Acclaim!® Development Platform.

GND

-RESE

GND

VDD

J6

12

34

56

78

9

10

11 12

13 14

15 16

17 18

19 20

21 22