AV RECEIVER

RX-V673/HTR-6065/

RX-A720

SERVICE MANUAL

When the DIGITAL P.C.B. or IC82 on DIGITAL P.C.B. is replaced, this unit will display “Internal Error”

Note:

and will not operate at all without additional setting.

In such a case, report the serial number of this unit to the following e-mail address.

Yamaha Corporation will reply providing the setting procedure to make this unit operate properly.

E-mail: ycav-ysiss@gmx.yamaha.com

IMPORTANT NOTICE

This manual has been provided for the use of authorized YAMAHA Retailers and their service personnel.

It has been assumed that basic service procedures inherent to the industry, and more specifi cally YAMAHA Products, are already known

and understood by the users, and have therefore not been restated.

WARNING:

IMPORTANT:

The data provided is believed to be accurate and applicable to the unit(s) indicated on the cover. The research, engineering, and service

departments of YAMAHA are continually striving to improve YAMAHA products. Modifications are, therefore, inevitable and

specifi cations are subject to change without notice or obligation to retrofi t. Should any discrepancy appear to exist, please contact the

distributor's Service Division.

WARNING:

IMPORTANT:

Failure to follow appropriate service and safety procedures when servicing this product may result in personal injury,

destruction of expensive components, and failure of the product to perform as specifi ed. For these reasons, we advise

all YAMAHA product owners that any service required should be performed by an authorized YAMAHA Retailer or

the appointed service representative.

The presentation or sale of this manual to any individual or fi rm does not constitute authorization, certifi cation or

recognition of any applicable technical capabilities, or establish a principle-agent relationship of any form.

Static discharges can destroy expensive components. Discharge any static electricity your body may have

accumulated by grounding yourself to the ground buss in the unit (heavy gauge black wires connect to this buss).

Turn the unit OFF during disassembly and part replacement. Recheck all work before you apply power to the unit.

RX-V673/HTR-6065/

■ CONTENTS

TO SERVICE PERSONNEL ............................................2

FRONT PANELS ......................................................... 3–4

REAR PANELS ...........................................................5–8

REMOTE CONTROL PANEL .......................................... 9

SPECIFICATIONS ................................................... 10–15

INTERNAL VIEW .................................................... 16–17

SERVICE PRECAUTIONS ............................................ 17

DISASSEMBLY PROCEDURES ............................. 18–23

UPDATING FIRMWARE ..........................................24–25

SELF-DIAGNOSTIC FUNCTION ............................26–64

POWER AMPLIFIER ADJUSTMENT ............................65

101237

Copyright © 2012 All rights reserved.

This manual is copyrighted by YAMAHA and may not be copied or

redistributed either in print or electronically without permission.

RX-A720

DISPLAY DATA .......................................................66–69

IC DATA ...................................................................70–89

PIN CONNECTION DIAGRAMS .............................90–91

BLOCK DIAGRAMS ................................................92–95

PRINTED CIRCUIT BOARDS ...............................96–128

SCHEMATIC DIAGRAMS ................................... 129–148

REPLACEMENT PARTS LIST ............................ 149–171

REMOTE CONTROL ........................................... 172–174

ADVANCED SETUP ............................................ 175–176

FIRMWARE UPDATING PROCEDURE .............. 177–188

P.O.Box 1, Hamamatsu, Japan

'12.05

RX-V673/HTR-6065/RX-A720

■ TO SERVICE PERSONNEL

1. Critical Components Information

Components having special characteristics are marked ⚠ and

must be replaced with parts having specifications equal to those

originally installed.

2. Leakage Current Measurement (For 120V Models Only)

When service has been completed, it is imperative to verify

that all exposed conductive surfaces are properly insulated

from supply circuits.

• Meter impedance should be equivalent to 1500 ohms shunted

by 0.15 F.

For U model

“CAUTION”

“F3702: FOR CONTINUED PROTECTION AGAINST RISK OF FIRE, REPLACE ONLY WITH SAME TYPE 8A,

125V FUSE.”

For C model

CAUTION

F3702: REPLACE WITH SAME TYPE 8A, 125V FUSE.

ATTENTION

F3702: UTILISER UN FUSIBLE DE RECHANGE DE MÉME TYPE DE 8A, 125V.

WALL

OUTLET

• Leakage current must not exceed 0.5mA.

• Be sure to test for leakage with the AC plug in both polarities.

EQUIPMENT

UNDER TEST

INSULATING

TABLE

AC LEAKAGE

TESTER OR

EQUIVALENT

WARNING: CHEMICAL CONTENT NOTICE!

This product contains chemicals known to the State of California to cause cancer, or birth defects or other reproductive

harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON

WHATSOEVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or

expose eyes to solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before

handling food.

RX-A720

About lead free solder

RX-V673/HTR-6065/

All of the P.C.B.s installed in this unit and solder joints are soldered using the lead free solder.

Among some types of lead free solder currently available, it is recommended to use one of the following types for the

repair work.

• Sn + Ag + Cu (tin + silver + copper)

• Sn + Cu (tin + copper)

• Sn + Zn + Bi (tin + zinc + bismuth)

Caution:

As the melting point temperature of the lead free solder is about 30°C to 40°C (50°F to 70°F) higher than that of the lead

solder, be sure to use a soldering iron suitable to each solder.

2

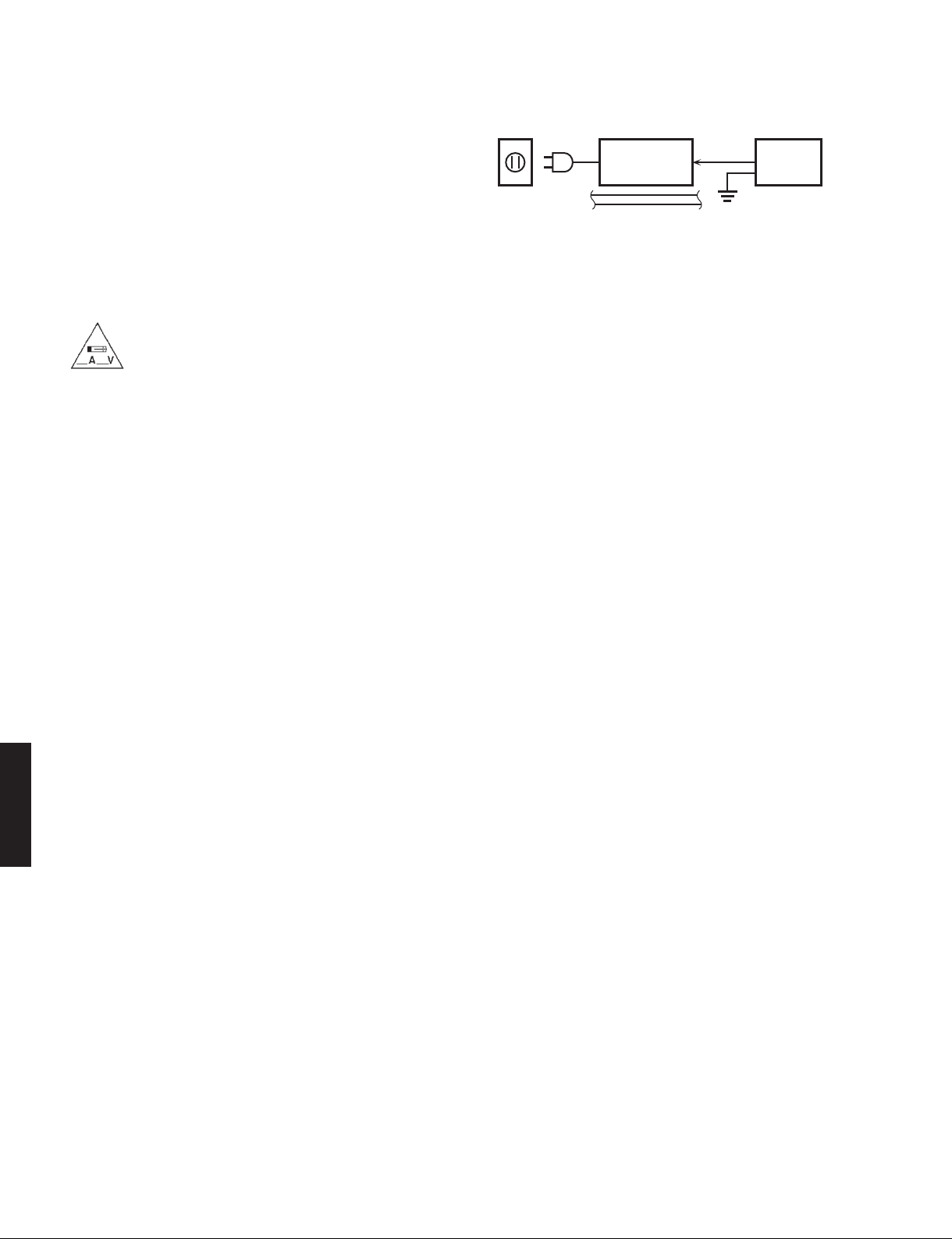

■ FRONT PANELS

RX-V673 (U, C, R, T, K, A, B, G, F, L, S, H models)

RX-V673/HTR-6065/RX-A720

HTR-6065 (A, F models)

RX-V673/HTR-6065/

RX-A720

3

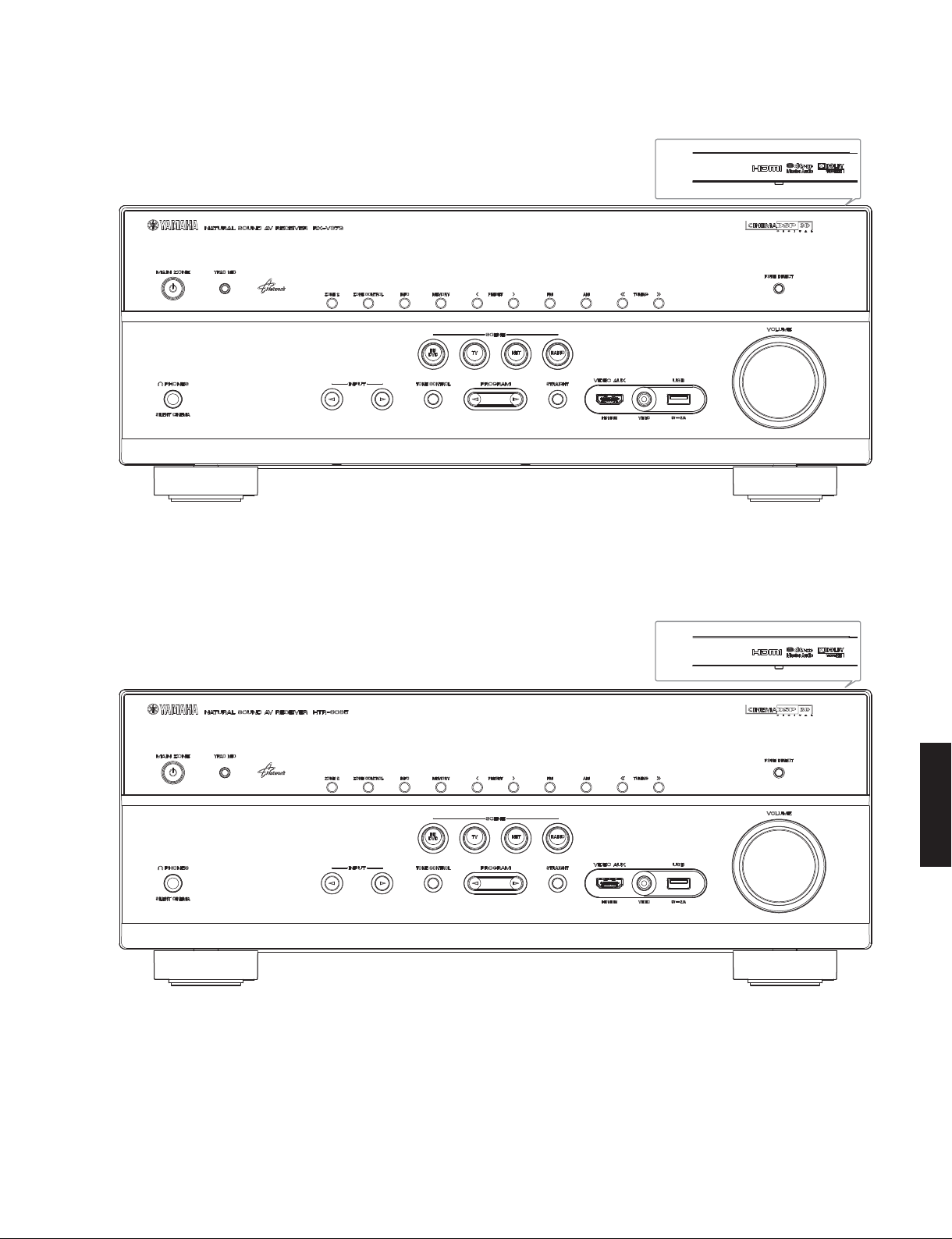

RX-V673/HTR-6065/RX-A720

RX-A720 (U, C, A models)

RX-A720

RX-V673/HTR-6065/

4

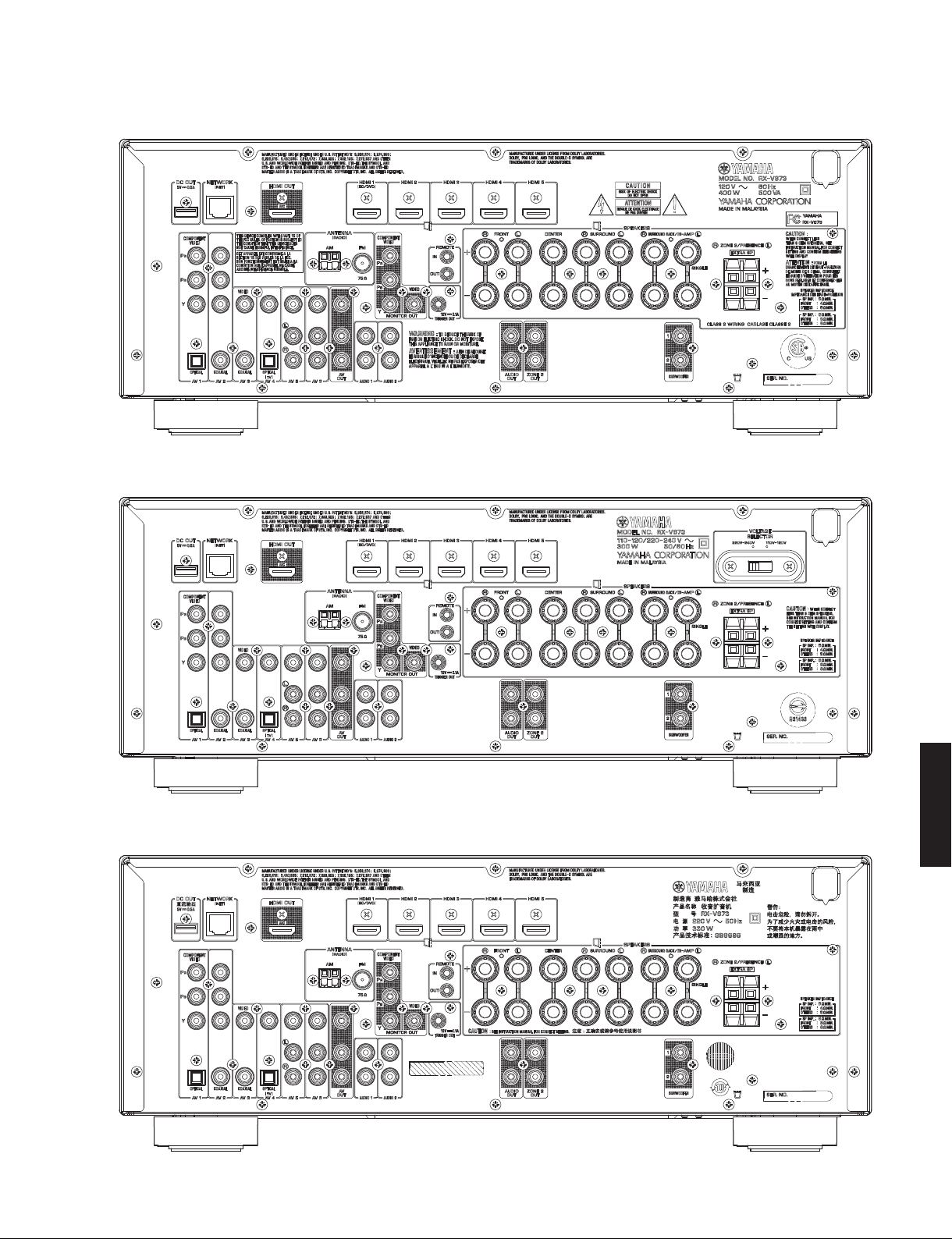

■ REAR PANELS

RX-V673 (U, C models)

RX-V673 (R, S models)

RX-V673/HTR-6065/RX-A720

RX-V673 (T model)

RX-V673/HTR-6065/

RX-A720

5

RX-V673/HTR-6065/RX-A720

RX-V673 (K model)

RX-V673 (A model)

RX-A720

RX-V673/HTR-6065/

RX-V673 (B, G, F models)

6

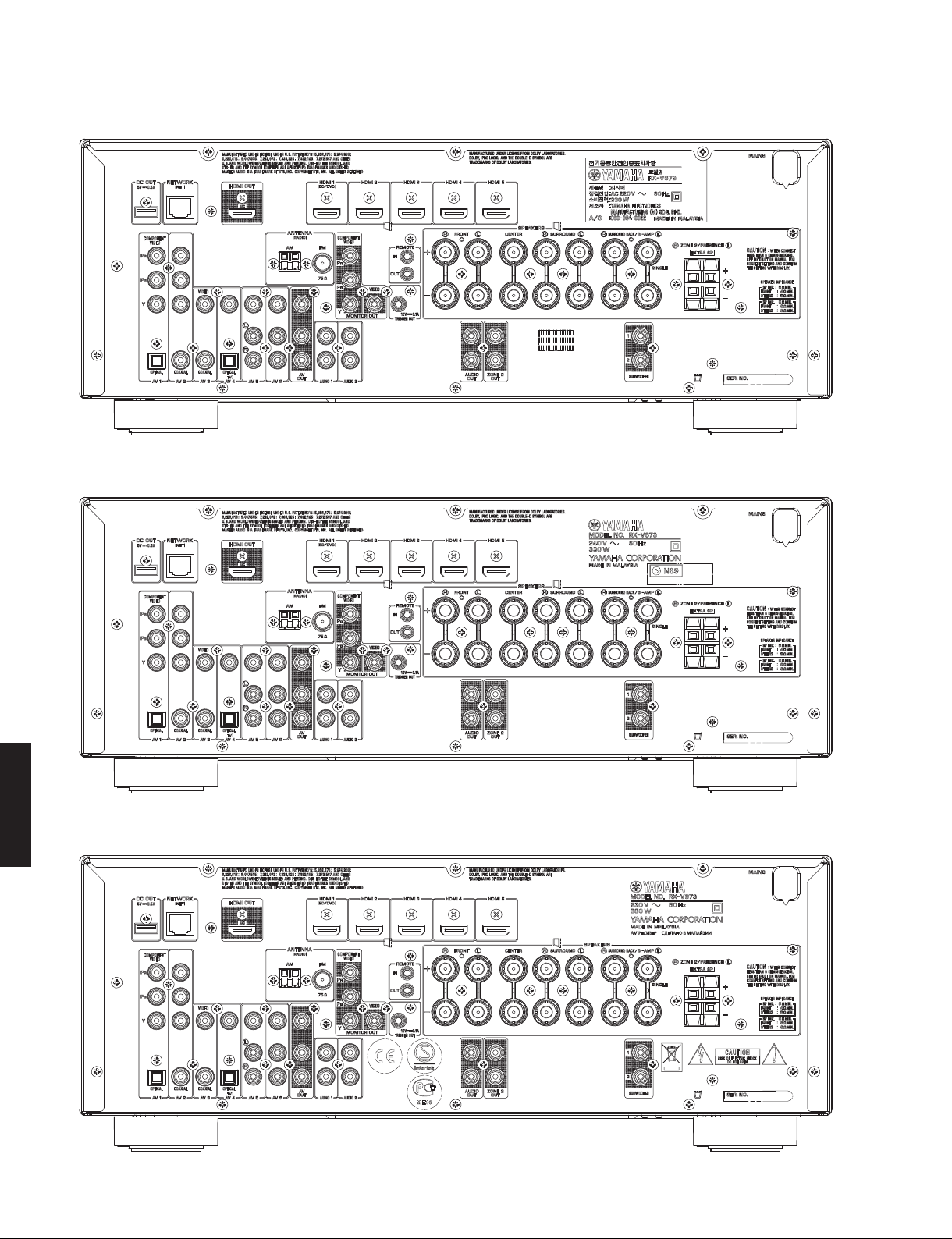

RX-V673 (L, H models)

HTR-6065 (A model)

RX-V673/HTR-6065/RX-A720

H model

HTR-6065 (F model)

RX-V673/HTR-6065/

RX-A720

7

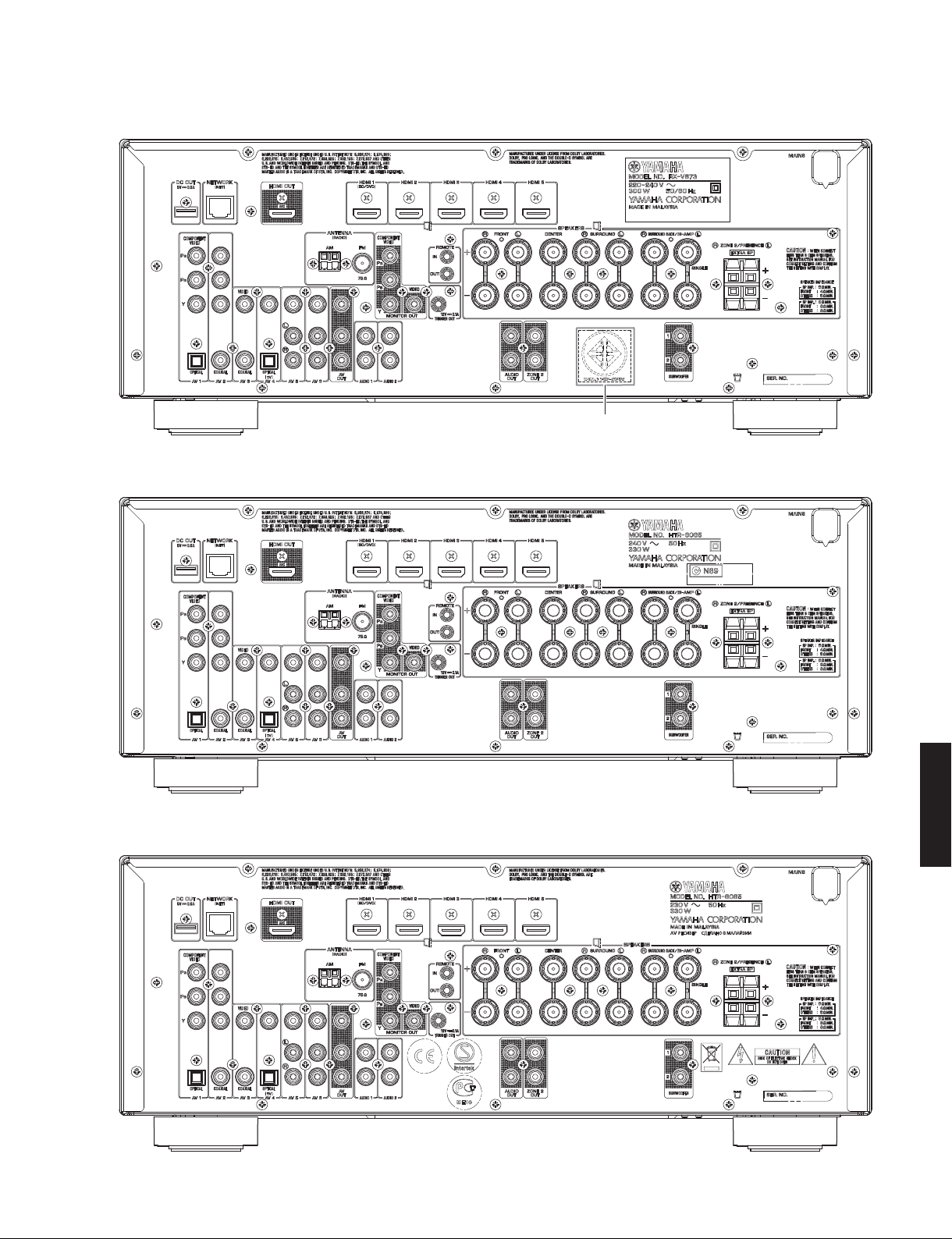

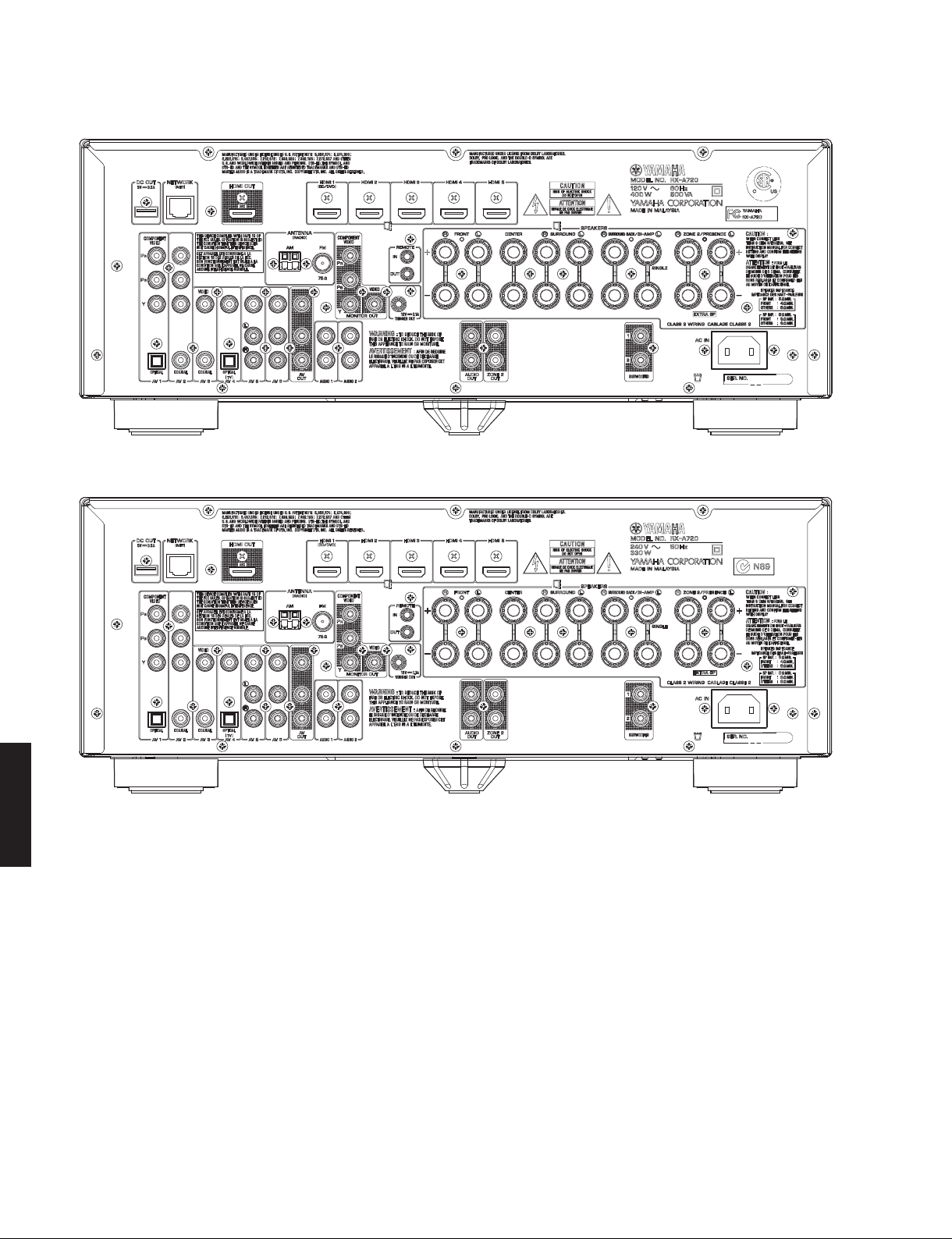

RX-V673/HTR-6065/RX-A720

RX-A720 (U, C models)

RX-A720 (A model)

RX-A720

RX-V673/HTR-6065/

8

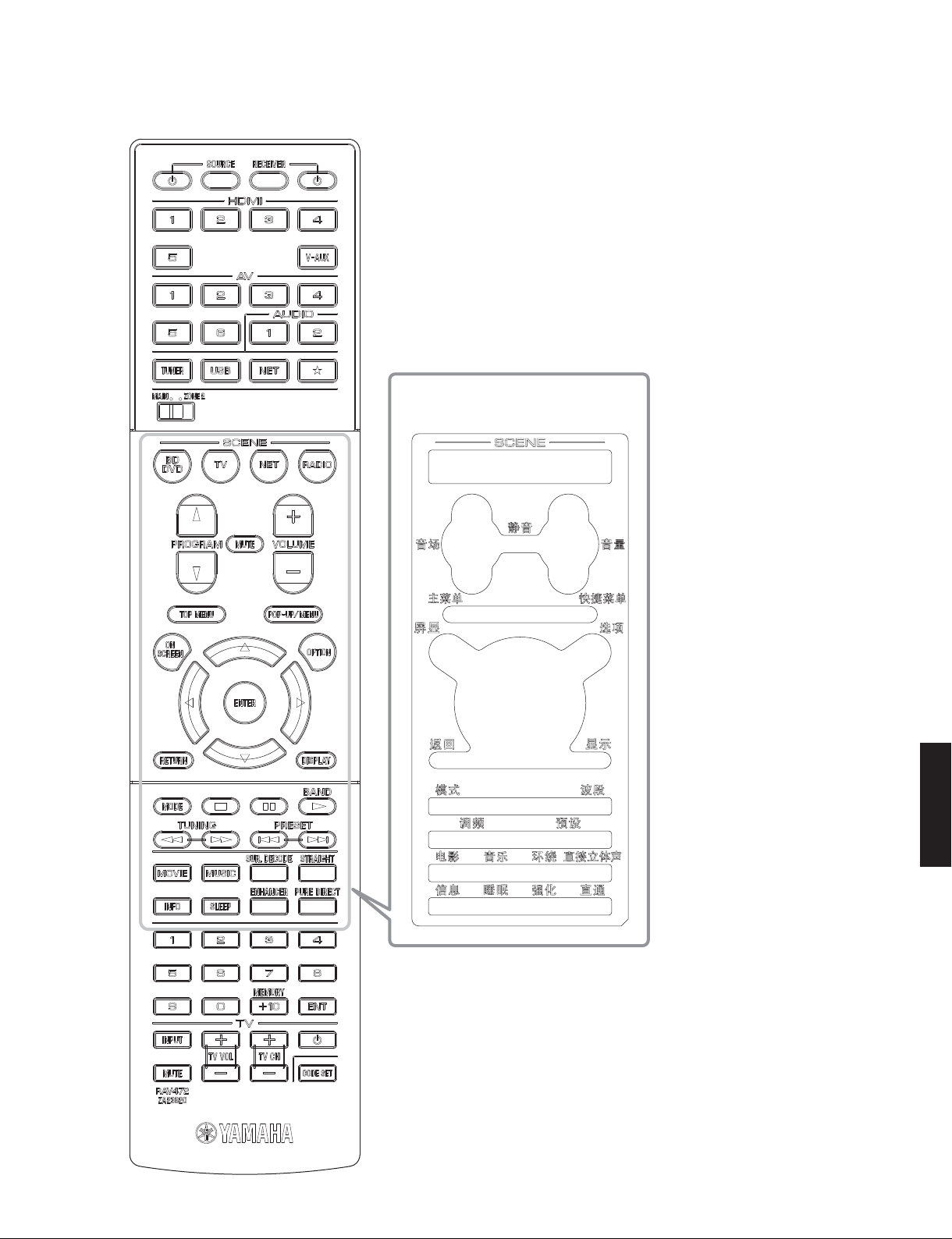

■ REMOTE CONTROL PANEL

RAV472

RX-V673/HTR-6065/RX-A720

Remote control sheet

(T model)

RX-V673/HTR-6065/

RX-A720

9

RX-V673/HTR-6065/RX-A720

■ SPECIFICATIONS

■ Audio Section

Rated Output Power (Power Amp. Section)

(1 kHz, 0.9 % THD)

– 1 channel driven –

U, C, R, T, K, A, B, G, F, L, S, H models (8 ohms)

FRONT L/R ................................................................ 125 W/ch

CENTER .......................................................................... 125 W

SURROUND L/R ........................................................ 125 W/ch

SURROUND BACK L/R .............................................125 W/ch

B, G, F models (4 ohms)

FRONT L/R ................................................................ 150 W/ch

– 2 channels driven simultaneously –

U, C, R, T, K, A, B, G, F, L, S, H models (8 ohms)

FRONT L/R .......................................................105 W + 105 W

CENTER .......................................................................... 105 W

SURROUND L/R ...............................................105 W + 105 W

SURROUND BACK L/R ....................................105 W + 105 W

(20 Hz to 20 kHz, 0.09 % THD)

– 2 channels driven simultaneously –

U, C, R, T, K, A, B, G, F, L, S, H models (8 ohms)

FRONT L/R ...........................................................90 W + 90 W

Maximum Effective Output Power (JEITA) [R, T, K, L, S, H models]

(1 channel driven, 1 kHz, 10 % THD, 8 ohms)

FRONT L/R ......................................................................... 150 W/ch

CENTER .................................................................................. 150 W

SURROUND L/R ................................................................150 W/ch

SURROUND BACK L/R .....................................................150 W/ch

Dynamic Power Per Channel (IHF)

FRONT L/R (1 channel driven)

(8 / 6 / 4 / 2 ohms) ..................................... 130 / 170 / 200 / 240 W

Damping Factor (20 Hz to 20 kHz, 8 ohms)

FRONT L/R to SPEAKER-A ............................................100 or more

Input Sensitivity/Input Impedance (1 kHz, 100 W/8 ohms)

AV5 etc. ............................................................200 mV / 47 k-ohms

Maximum Input Signal (1 kHz, 0.5 % THD)

AV5 etc. (EFFECT ON) .............................................................. 2.3 V

Output Level/Output Impedance

AUDIO OUT ..................................................... 200 mV / 1.2 k-ohms

RX-A720

RX-V673/HTR-6065/

SUBWOOFER (2 ch stereo and FRONT SP: small)

.............................................................................. 1 V / 1.2 k-ohms

ZONE2 OUT ..................................................... 200 mV / 1.2 k-ohms

Headphone Jack Rated Output/Output Impedance

(1 kHz, 50 mV, 8 ohms)

AV5 etc. input .....................................................100 mV / 560 ohms

Frequency Response (10 Hz to 100 kHz)

AV5 etc., FRONT ..................................................................0 / -3 dB

Total Harmonic Distortion (20 Hz to 20 kHz, 50 W/8 ohms)

AV5 etc. (PURE DIRECT) to FRONT SP OUT .............0.06 % or less

Signal to Noise Ratio (IHF-A Network) (Input shorted 250 mV)

AV5 etc. (PURE DIRECT) to SP OUT ....................... 100 dB or more

Residual Noise (IHF-A Network)

FRONT L/R to SP OUT ................................................150 V or less

Channel Separation (1 kHz / 10 kHz)

AV5 etc. (Input 5.1 k-ohms shorted)

...................................................... 60 dB or more / 45 dB or more

Volume Control/Step

......................................... MUTE / -80 dB to +16.5 dB / 0.5 dB step

Tone Control Characteristics

Bass

Boost/Cut ........................................ ±6 dB / 0.5 dB step, at 50 Hz

Turnover frequency .............................................................350 Hz

Treble

Boost/Cut .......................................±6 dB / 0.5 dB step, at 20 kHz

Turnover frequency ............................................................ 3.5 kHz

Filter Characteristics

FRONT, CENTER, SURROUND, SURROUND BACK small (H.P.F.)

....................fc=40/60/80/90/100/110/120/160/200 Hz, 12 dB/oct.

SUBWOOFER small (L.P.F.)

....................fc=40/60/80/90/100/110/120/160/200 Hz, 24 dB/oct.

Optical Jack, Coaxial Jack Support Frequencies

............................................................................... 32 kHz to 96 kHz

■ Video Section

Video Signal Type

Monitor out (Wall paper)

U, C, R, K models .................................................................NTSC

T, A, B, G, F, L, S, H models ..................................................... PAL

Video conversion

.......................................................................................NTSC/PAL

Composite Video Signal Level

...............................................................................1 Vp-p / 75 ohms

Component Video Signal Level

Y .............................................................................1 Vp-p / 75 ohms

Pb/Pr ...................................................................0.7 Vp-p / 75 ohms

Video Maximum Input Level (VIDEO Conversion Off)

................................................................................ 1.5 Vp-p or more

Video Signal to Noise Ratio

................................................................................... 50 dB or more

Monitor Out Frequency Response (VIDEO Conversion Off)

Component video signal level .......................5 Hz to 60 MHz, -3 dB

■ FM Section

Tuning Range

U, C models ......................................................... 87.5 to 107.9 MHz

R, L, S, H models ..................... 87.5 to 108.0 / 87.50 to 108.00 MHz

T, K, A, B, G, F models ....................................87.50 to 108.00 MHz

50 dB Quieting Sensitivity (IHF) (1 kHz, 100 % MOD.)

Mono ......................................................................... 3 µV (20.8 dBf)

Signal to Noise Ratio (IHF)

Mono ........................................................................................71 dB

Stereo ......................................................................................69 dB

Harmonic Distortion (1 kHz)

Mono ........................................................................................ 0.3 %

Stereo ......................................................................................0.5 %

Antenna Input

......................................................................... 75 ohms unbalanced

10

■ AM Section

Tuning Range

U, C models ........................................................... 530 to 1,710 kHz

R, L, S, H models ............................ 530 to 1,710 / 531 to 1,611 kHz

T, K, A, B, G, F models ..........................................531 to 1,611 kHz

Antenna

..................................................................................... Loop antenna

■ General

Power Supply

U, C models ............................................................ AC 120 V, 60 Hz

R, S models .................................AC 110–120/220–240 V, 50/60 Hz

T model ................................................................... AC 220 V, 50 Hz

K model .................................................................. AC 220 V, 60 Hz

A model .................................................................. AC 240 V, 50 Hz

B, G, F models ........................................................ AC 230 V, 50 Hz

L, H models ............................................... AC 220–240 V, 50/60 Hz

Power Consumption

U, C models ..............................................................400 W / 500 VA

R, L, S, H models .................................................................... 300 W

T, K, A, B, G, F models ...........................................................330 W

Standby Power Consumption (reference data)

HDMI control: OFF / Standby through: OFF

................................................................................ 0.1 W (typical)

HDMI control: ON / Standby through: ON

INPUT: HDMI1(HDMI no signal)

.............................................................................3.0 W (typical)

Network standby: ON

................................................................................ 2.0 W (typical)

Maximum Power Consumption [R, L, S, H models]

................................................................................................ 590 W

Dimensions (W x H x D)

[RX-V673/HTR-6065]

............................ 435 x 171 x 364 mm (17-1/8" x 6-3/4" x 14-3/8")

[RX-A720]

............................ 435 x 171 x 367 mm (17-1/8" x 6-3/4" x 14-1/2")

Weight

[RX-V673/HTR-6065]

........................................................................... 10.2 kg (22.5 lbs.)

[RX-A720]

........................................................................... 10.7 kg (23.6 lbs.)

Finish

[RX-V673]

T model ..........................................................................Gold color

U, C, R, T, K, A, B, G, F, L, S, H models ....................... Black color

R, B, G, F, L, H models .............................................Titanium color

[HTR-6065]

A, F models .................................................................. Black color

[RX-A720]

U, C, A models ............................................................. Black color

RX-V673/HTR-6065/RX-A720

Accessories

Remote control ..............................................................................x 1

Batteries (R03, AAA, UM-4) ..........................................................x 2

FM antenna (1.4 m) ......................................................................x 1

AM antenna (1.0 m) ......................................................................x 1

YPAO microphone (6.0 m) ............................................................x 1

Remote control sheet (T model) ...................................................x 1

Power cable (2.0 m) (RX-A720) ....................................................x 1

* Specifications are subject to change without notice.

U ........................U.S .A. model

C ..................Canadian model

R .....................General model

T..................... Chinese model

K ...................... Korean model

A .................Australian model

Manufactured under license from Dolby Laboratories. Dolby, Pro Logic and

the double-D symbol are trademarks of Dolby Laboratories.

DTS-HD, the Symbol, & DTS-HD and the Symbol together are registered

trademarks & DTS-HD Master Audio is a trademark of DTS, Inc.

Product includes software. © DTS, Inc. All Rights Reserved.

AirPlay, the AirPlay logo, iPad, iPhone, iPod, iPod nano, and iPod touch are

trademarks of Apple Inc., registered in the U.S. and other countries.

MPEG Layer-3 audio coding technology licensed from Fraunhofer IIS and

Thomson.

This receiver supports network connections.

“HDMI,” the “HDMI” logo and “High-Definition Multimedia Interface” are

trademarks, or registered trademarks of HDMI Licensing LLC.

“x.v.Color” is a trademark of Sony Corporation.

B .......................British model

G ..................European model

F..................... Russian model

L..................Singapore model

S ...................Brazirian model

H ...........................Thai model

RX-V673/HTR-6065/

RX-A720

11

RX-V673/HTR-6065/RX-A720

“SILENT CINEMA” is a trademark of Yamaha Corporation.

DLNA™ and DLNA CERTIFIED™ are trademarks or registered trademarks

of Digital Living Network Alliance. All rights reserved. Unauthorized use is

strictly prohibited.

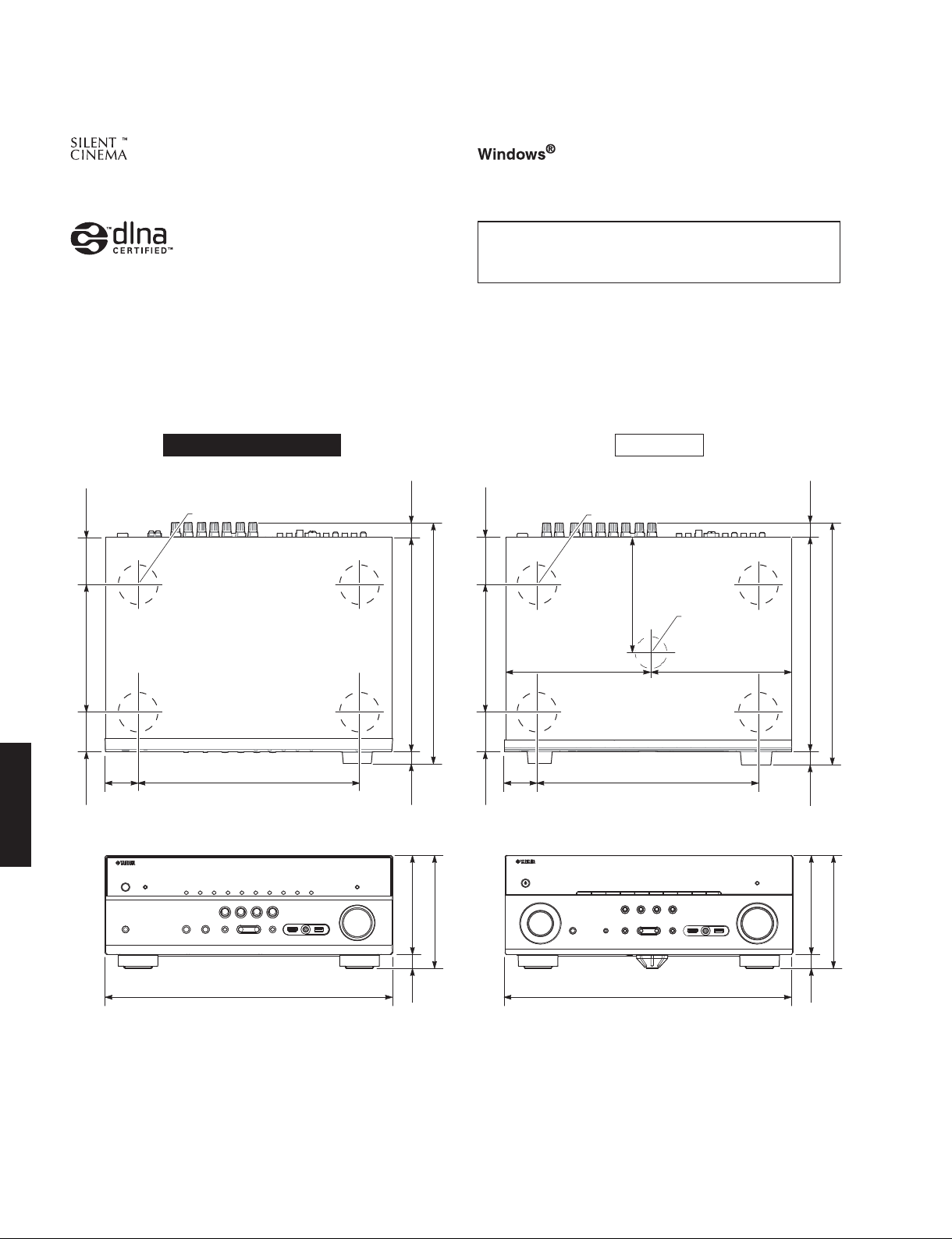

• DIMENSIONS

RX-V673/HTR-6065 RX-A720

72

Top view

(2-7/8")

ø 60

22

(7/8")

Windows is a registered trademark of Microsoft Corporation in the United

States and other countries.

Windows XP, Windows Vista, Windows 7, Windows Media Audio, Windows

Media Connect and Windows Media Player are either registered trademarks

or trademarks of Microsoft Corporation in the United States and/or other

countries.

72

Top view

(2-7/8")

ø 60

173 (6-3/4")

ø 48/18

22

(7/8")

193 (7-5/8")

59

(2")

(2-1/4")

RX-A720

Front view

RX-V673/HTR-6065/

50

335 (13-1/4")

435 (17-1/8")

364 (14-3/8")

324 (12-3/4")

18

(3/4")

150 (5-7/8")

171 (6-3/4")

21

(7/8")

193 (7-5/8")

50

59

(2")

(2-1/4")

Front view

222.5 (8-3/4") 212.5 (8-3/8")

335 (13-1/4")

435 (17-1/8")

Unit: mm (inch)Unit: mm (inch)

367 (14-1/2")

324 (12-3/4")

21

(7/8")

150 (5-7/8")

171 (6-3/4")

21

(7/8")

12

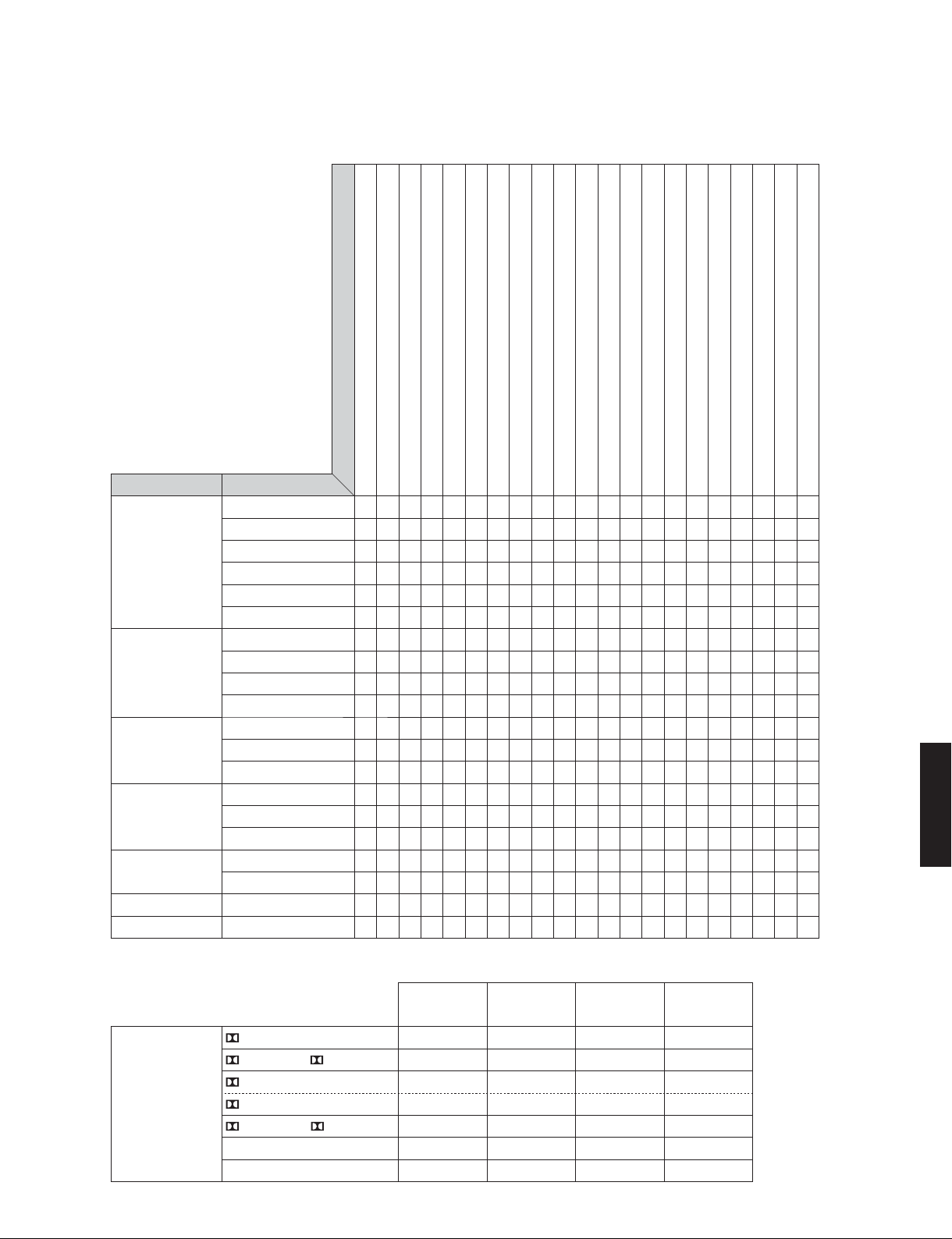

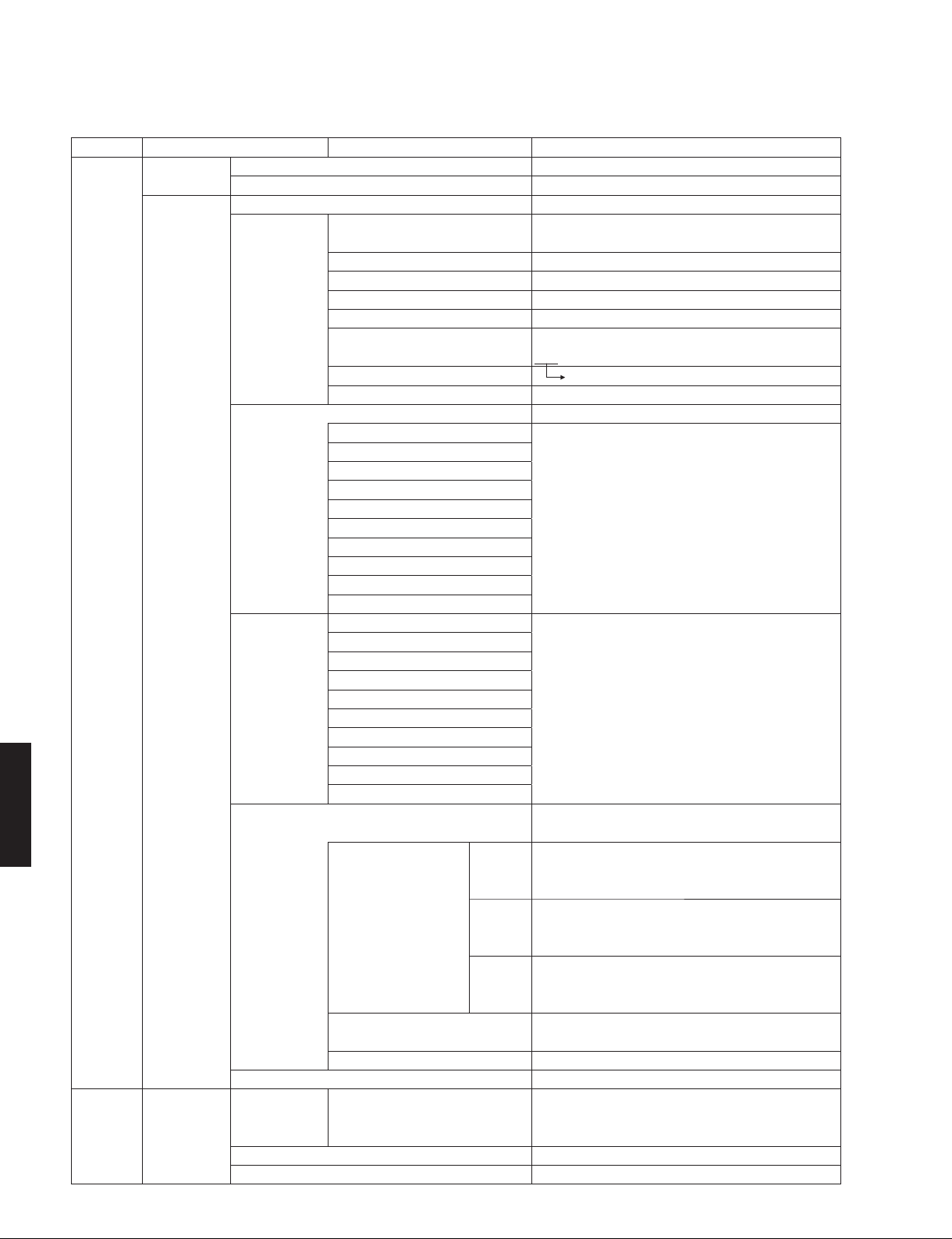

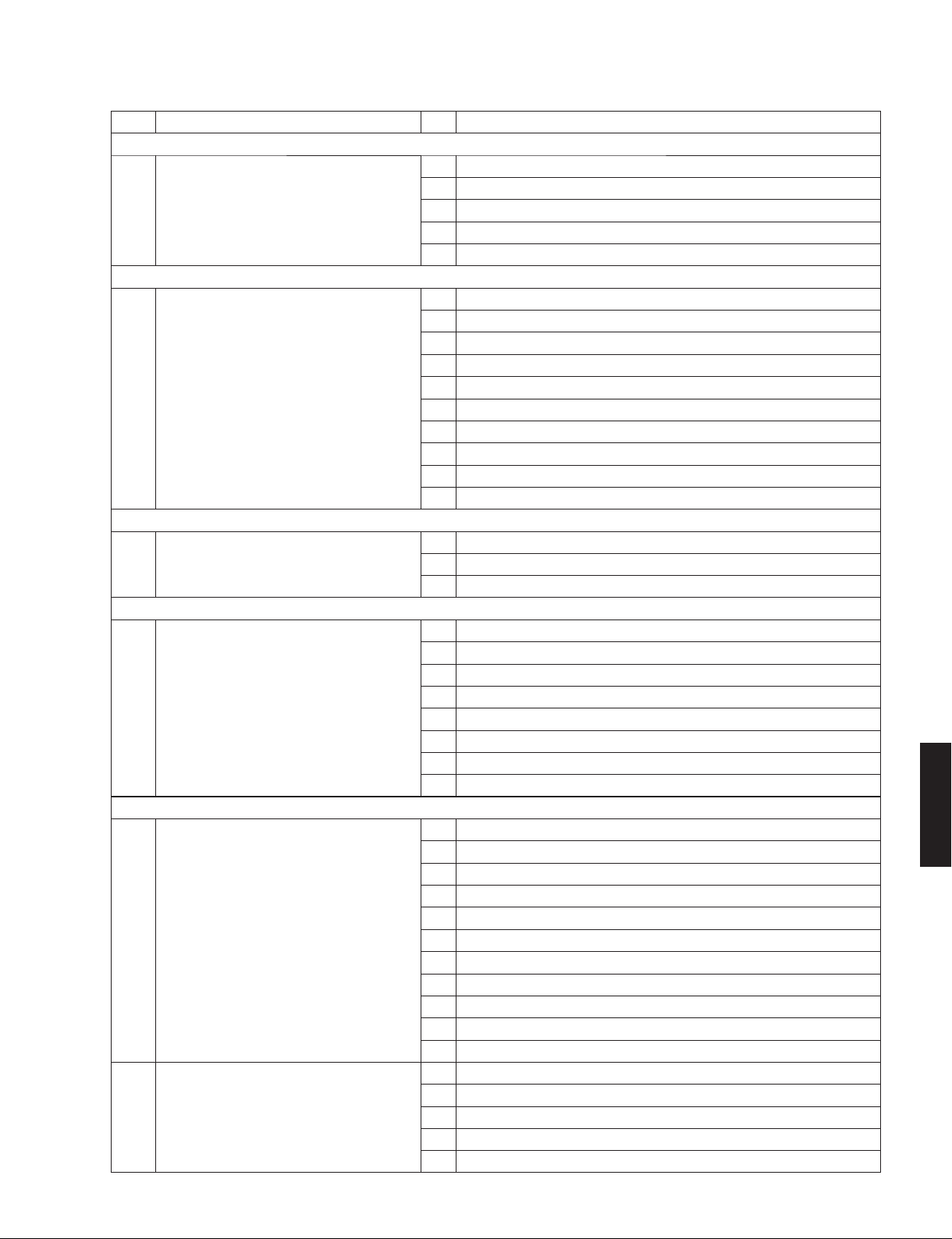

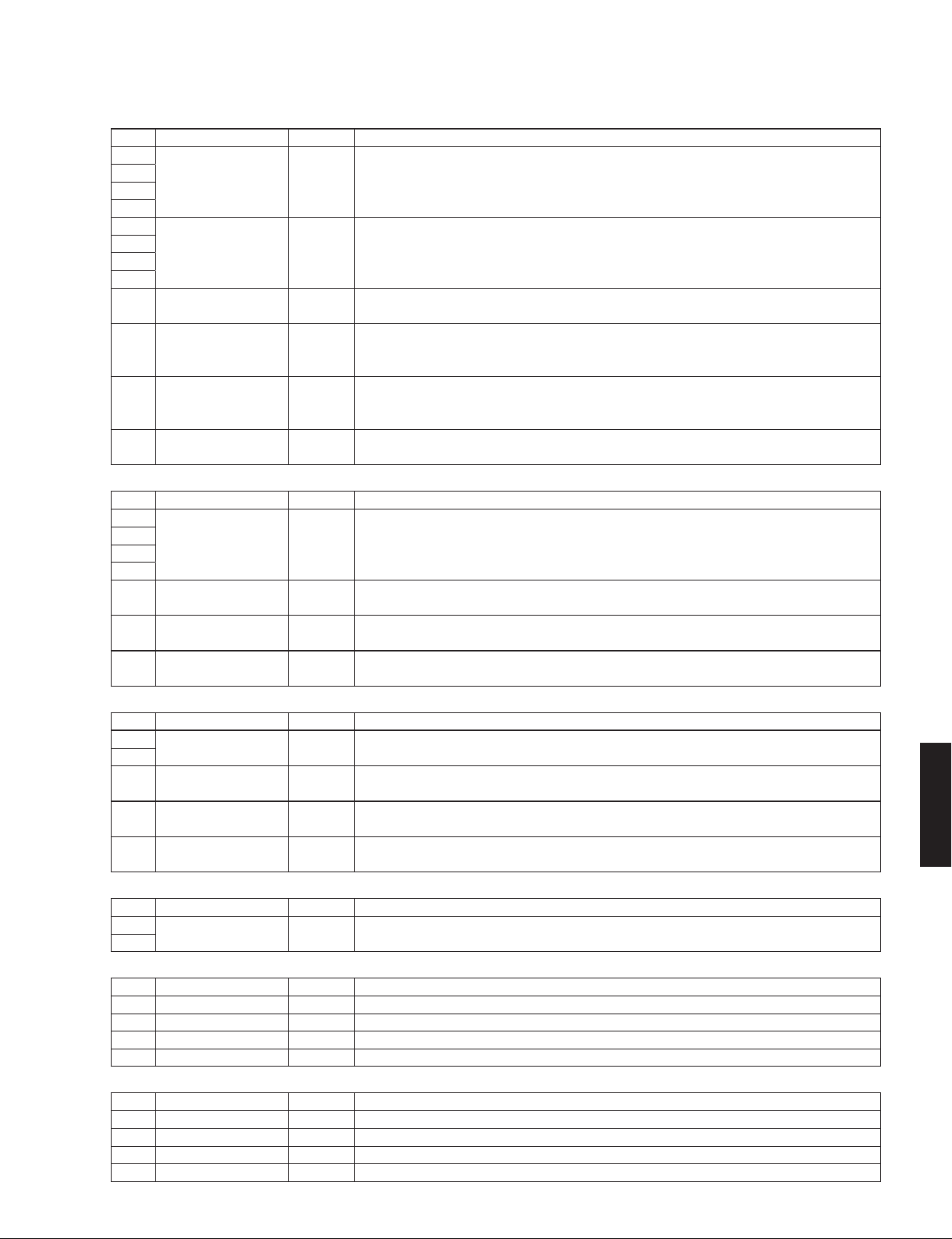

• SELECT MENU

Sound field parameters

RX-V673/HTR-6065/RX-A720

Parameter

Category Program

MOVIE THEATER Standard

Spectacle

Sci-Fi

Adventure

Drama

Mono Movie

ENTERTAINMENT Sports

Action Game

Roleplaying Game

Music Video

CLASSICAL Hall in Munich

Hall in Vienna

Chamber

LIVE/CLUB Cellar Club

The Roxy Theatre

The Bottom Line

STEREO 2ch Stereo

7ch Stereo

SUR. DECODE SURROUND DECODER

STRAIGHT

Decode Type (*1)

DSP Level: -6 to +3 dB, [0]

Initial Delay: 1 to 99 ms

Surround Initial Delay: 1 to 49 ms

Surround Back Initial Delay: 1 to 49 ms

Room Size: 0.1 to 2.0

Surround Room Size: 0.1 to 2.0

Surround Back Room Size: 0.1 to 2.0

Liveness: 0 to 10

Surround Liveness: 0 to 10

Surround Back Liveness: 0 to 10

Reverb Time: 1.0 to 5.0 s

Reverb Delay: 0 to 250 ms

Reverb Level: 0 to 100 %

Direct: Auto / Off, [Auto]

Level: -5 to +5, [0]

Front/Rear Balance: -5 to +5, [0]

Left/Right Balance: -5 to +5, [0]

Height Balance: 0 to 10, [5]

Monaural Mix: Off / On, [Off]

Reset

●● ●○ ●○ ●○ ●

●●●●○●●○ ●

●●●●○●●○ ●

●●●●○●●○ ●

●●●●○●●○ ●

●● ● ● ●●● ●

●●●○●●○ ●

●●●○●●○ ●

●●●○●●○ ●

●●●○●●○ ●

●● ● ● ●

●● ● ● ●

●● ● ●●● ●

●● ● ● ●

●● ● ● ●●● ●

●● ● ● ●

●●

●●●●●●

● ●

RX-V673/HTR-6065/

RX-A720

*1 Surround Decoder

Decode Type

Pro Logic

PL IIx Movie / PL II Movie

PL IIx Music /

PL II Music

PL IIx Game / PL II Game

Neo:6 Cinema

Neo:6 Music

Panorama Center Width Dimension Center Image

Off / On, [Off] 0 to 7, [3] -3 to +3, [0] 0.0 to 1.0, [0.3]

●●●

●

13

RX-V673/HTR-6065/RX-A720

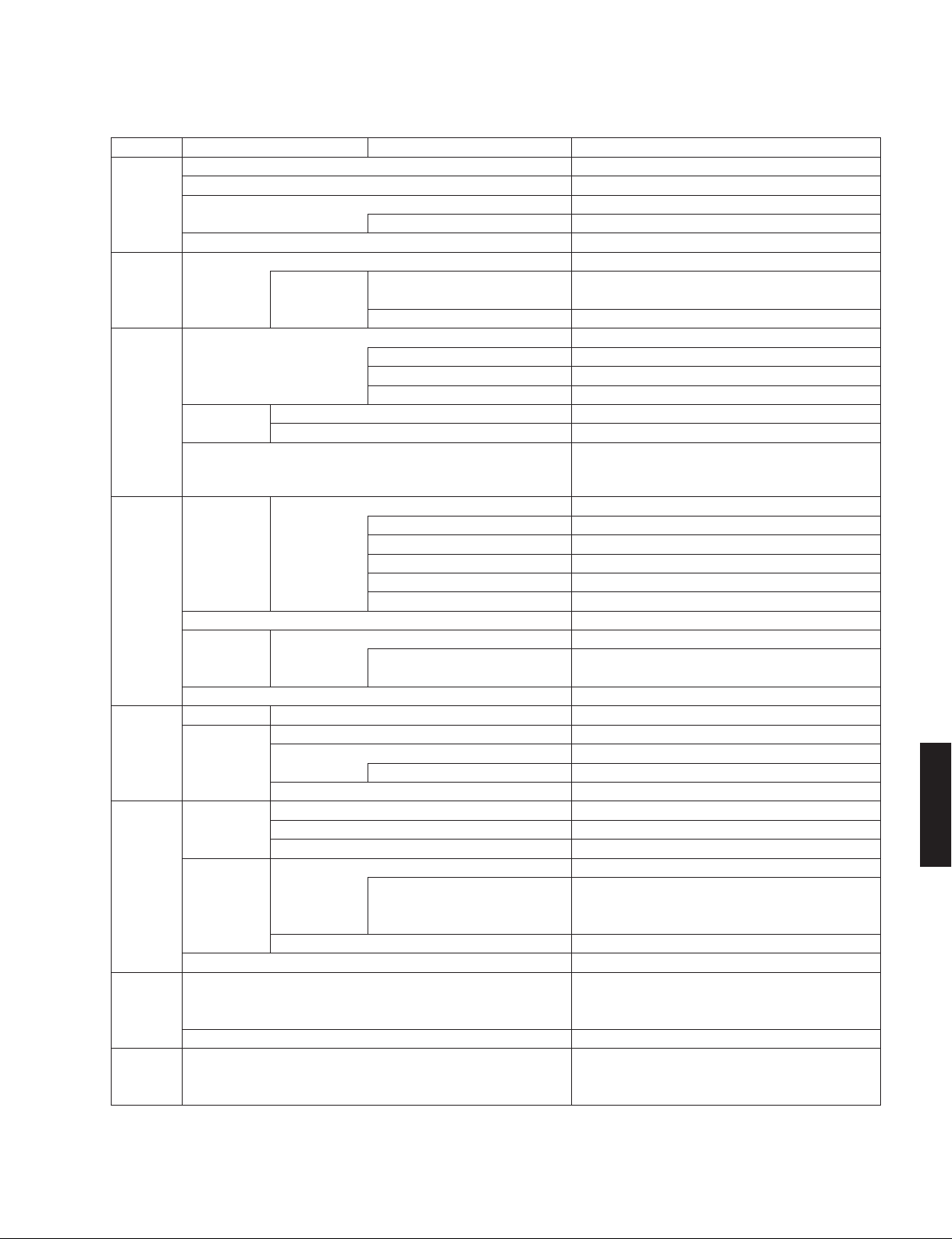

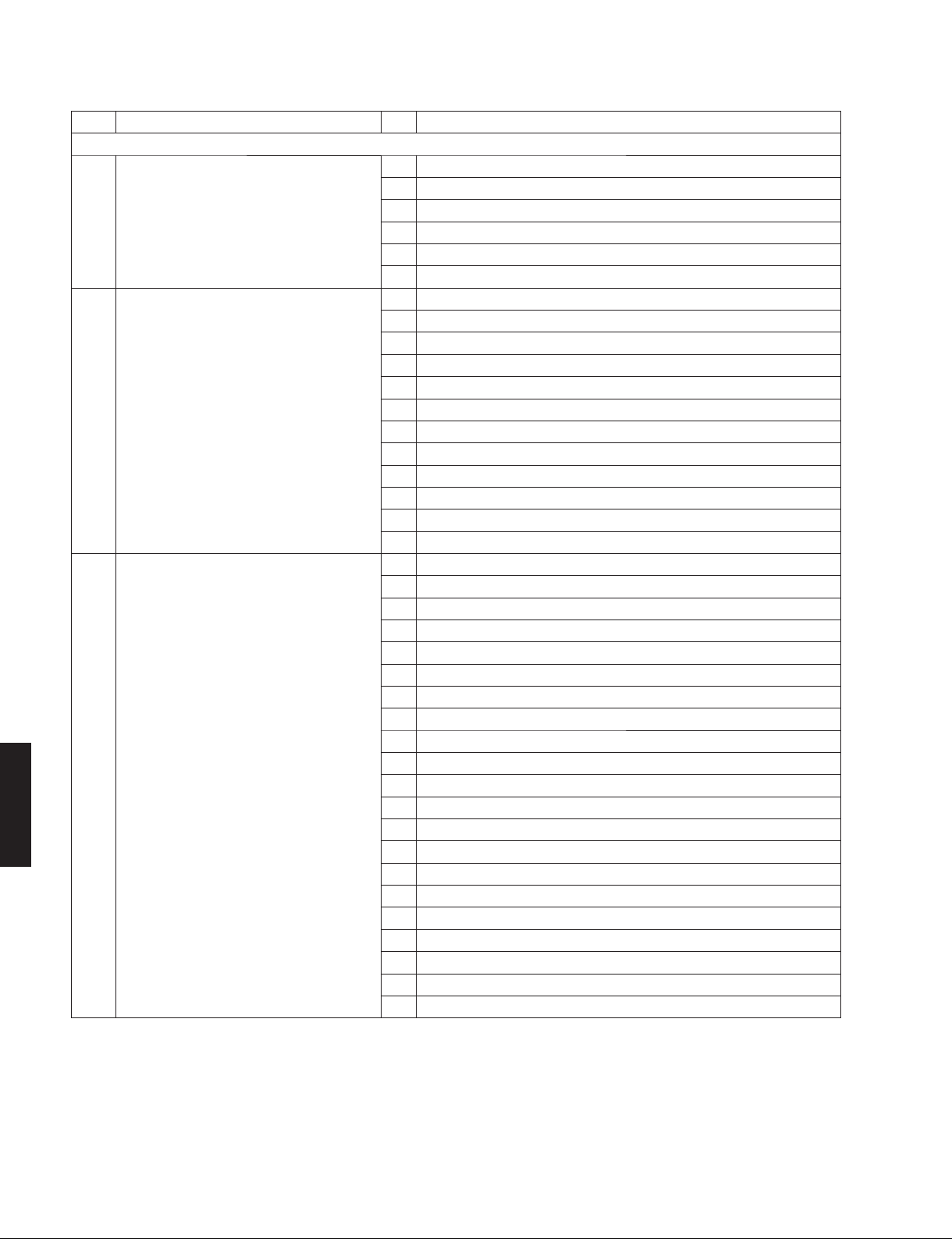

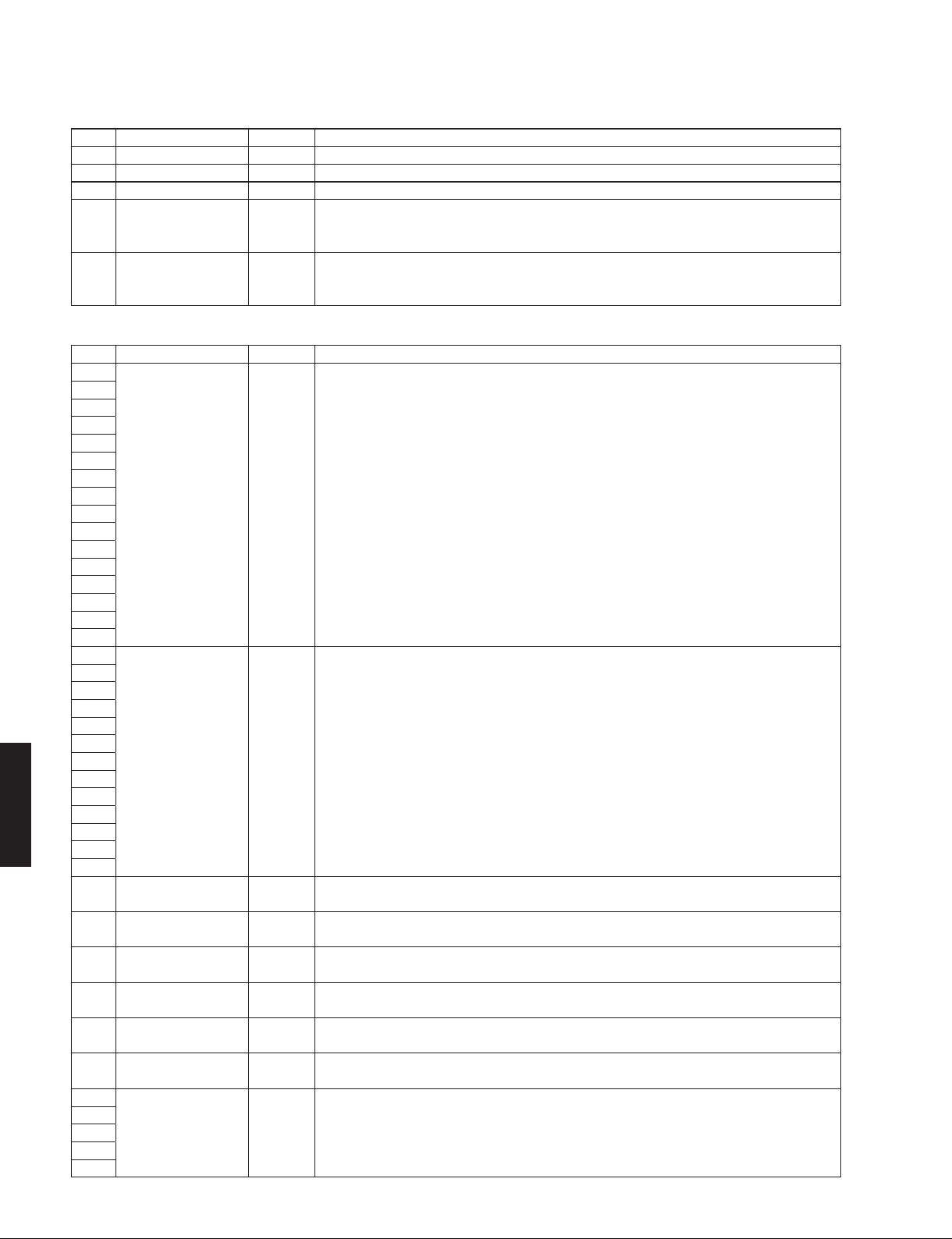

• SET MENU TABLE

MAIN MENU SUB-MENU PARAMETER VALUE [INITIAL VALUE]

Speaker Auto Measure Optimizes the speaker configuration automatically using YPAO.

Setup Result Not Available

Manual Power Amp Assign [Basic] / 7ch +1ZONE / 5ch BI-AMP

RX-A720

RX-V673/HTR-6065/

Sound Setup Lipsync Delay Enable HDMI1 / HDMI2 / HDMI3 / HDMI4 /

Configuration Front Large / [Small]

* When “Subwoofer” is set to “None”, “Front” is disabled.

Center Large / [Small] / None

Surround Large / [Small] / None

Surround Back Large x1 / Large x2 / Small x1 / [Small x2] / None

Front Presence [Use] / None

Subwoofer [Use] / None

[Normal] / Reverse

Extra Bass Not Available

Bass Cross Over 40 / 60 / [80] / 90 / 100 / 110 / 120 / 160 / 200 Hz

Distance Meter / Feet

Front L

Front R

Center

Surround L

Surround R 0.30 to 24.00 m, [3.00 m], 0.05 m step

Surround Back L 1.0 to 80.0 ft, [10.0 ft], 0.2 ft step

Surround Back R

Front Presence L

Front Presence R

Subwoofer

Level Front L

Front R

Center

Surround L

Surround R -10.0 to +10.0 dB, [0.0 dB], 0.5 dB step

Surround Back L

Surround Back R

Front Presence L

Front Presence R

Subwoofer

Parametric EQ Manual / YPAO : Flat / YPAO : Front / YPAO : Natural / [Through]

* Select “ENTER”

Front L Band

Front R / Gain▲ Gain: -20.0 to +6.0 dB, [0.0 dB], 0.5 dB step

Center

Surround L Frequency▶ Frequency: 31.3 Hz to 16.0 kHz, [62.5 Hz]

Surround R / Gain▲ Gain: -20.0 to +6.0 dB, [0.0 dB], 0.5 dB step

Surround Back L

Surround Back R Q

Front Presence L / Gain▲ Gain: -20.0 to +6.0 dB, [0.0 dB], 0.5 dB step

Front Presence R

PEQ Data Copy Flat > Manual / Front > Manual / Natural > Manual

PEQ Data Clear OK / CANCEL * Select “ENTER”

Test Tone [Off] / On

HDMI5 / AV1 / AV2 / AV3 / AV4 / AV5 / Disable / [Enable]

AV6 / AUDIO1 / AUDIO2

Auto/Manual Select [Auto] / Manual

Adjustment 0 to 500 ms, [0 ms], 1 ms step

Band: #1 to #7

▶

Q: 0.500 to 10.080, [1.000]

▶

* Select “ENTER”

14

RX-V673/HTR-6065/RX-A720

MAIN MENU SUB-MENU PARAMETER VALUE [INITIAL VALUE]

Sound Setup Dynamic Range [Maximum] / Standard / Minimum/Auto

Max. Volume -30.0 to +16.5 dB (Maximum volume), [+16.5 dB], 5.0 dB step

Initial Volume [Off] / On

Select “On” Mute, -80 to +16.5 dB, 0.5 dB step

Adaptive DSP Level Off / [On]

Video Setup Video Mode [Direct] / Processing

Select Resolution Through / [Auto] / 576p / 720p / 1080i / 1080p / 4K

“Processing” * Select “ENTER”

Aspect [Through] / 16:9 Normal

HDMI Setup HDMI Control [Off] / On

TV Audio Input AV1 / AV2 / AV3 / [AV4] / AV5 / AV6 / AUDIO1 / AUDIO2

ARC (Audio Return Channel) Off / [On]

Standby Sync Off / On / [Auto]

Audio Output Amp Off / [On]

HDMI OUT (TV) [Off] / On

Standby Through [Off] / On

* When HDMI Control is set to “On”, “Standby Through” is

disabled.

Network IP Address DHCP [Off] / On

Setup IP Address xxx.xxx.xxx. x

Subnet Mask xxx.xxx.xxx. x

Default Gateway xxx.xxx.xxx. x

DNS Server (P) Primary x. x. x. x

DNS Server (S) Secondary x. x. x. x

Network Standby [Off] / On

MAC Address Filter [Off] / On

Filter MAC Address 1–5 xx : xx : xx : xx : xx : xx

6–10

Network Name Input is possible to 15 characters

Multi Zone Main Zone Set Zone Rename Input is possible to 9 characters

Setup Zone2 Set Max. Volume -30.0 to +16.5 dB (Maximum volume), [+16.5 dB], 5.0dB step

Initial Volume [Off] / On

Select “On” Mute, -80 to +16.5 dB, 0.5 dB step

Zone Rename Input is possible to 9 characters

Function Display Set Dimmer (Front Display) -4 to 0

Setup Short Message [On] / Off

Wall Paper Picture1 / Picture2 / Picture3 / Gray

Trigger Output Trigger Mode [Power] / Source / Manual

Select “Source” HDMI1–5, AV1–6, V-AUX, AUDIO1–2, TUNER, AirPlay,

SERVER, NET RADIO, USB

Low / [High]

Target Zone Main / Zone2 / [All]

Memory Guard [Off] / On

ECO Setup Auto Power Down Off / 2 Hours / 4 Hours / 8 Hours / 12 Hours

U, C, R, T, K, A, L, S, H models: [Off]

B, G, F models: [8 Hours]

ECO Mode [Off] / On

Language [English (English)] /

Setup Deutsch (German) / Español (Spanish) / Рyccкий (Russian) /

(Chinese)

中文

(Japanese) / Français (French) /

日本語

RX-V673/HTR-6065/

RX-A720

15

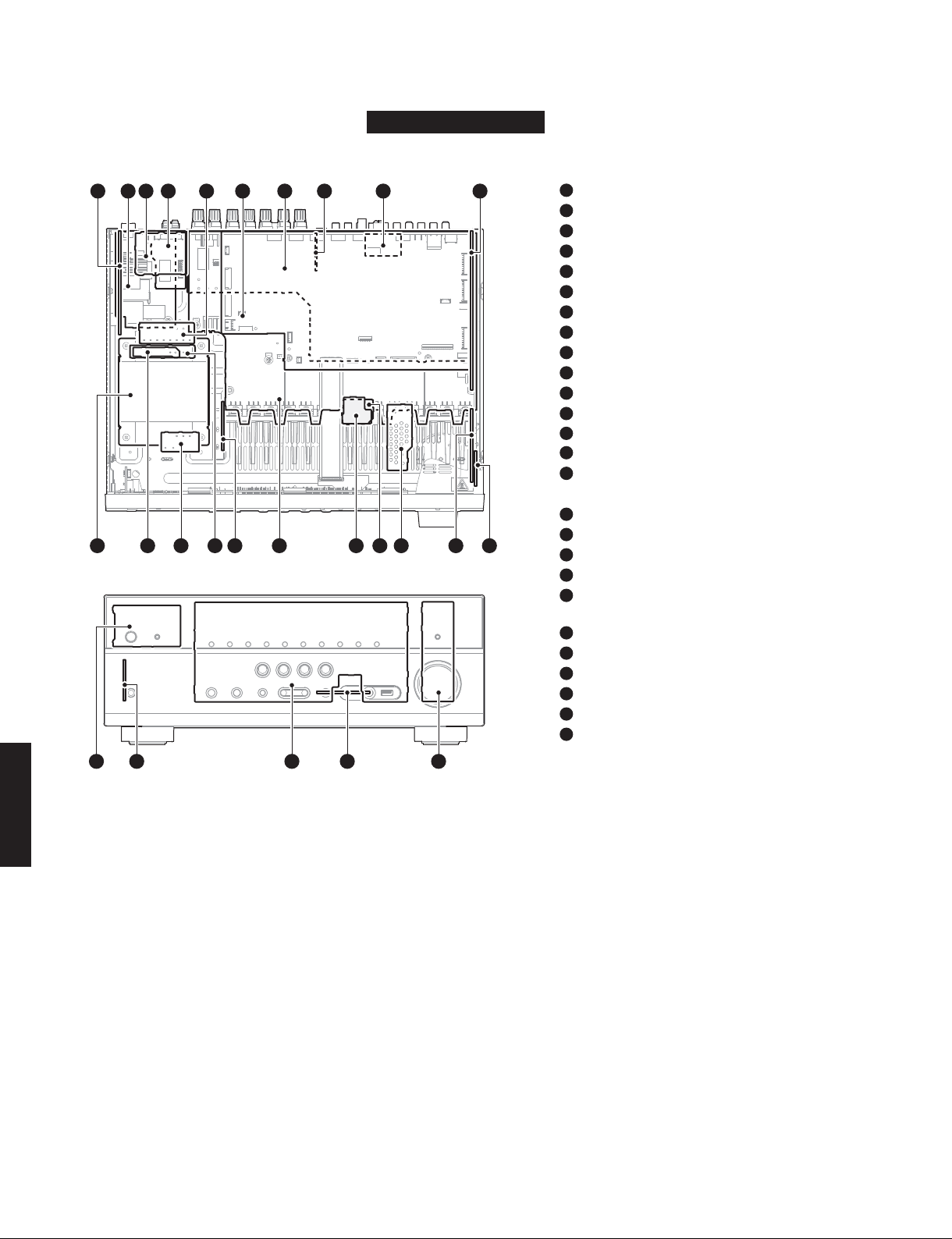

RX-V673/HTR-6065/RX-A720

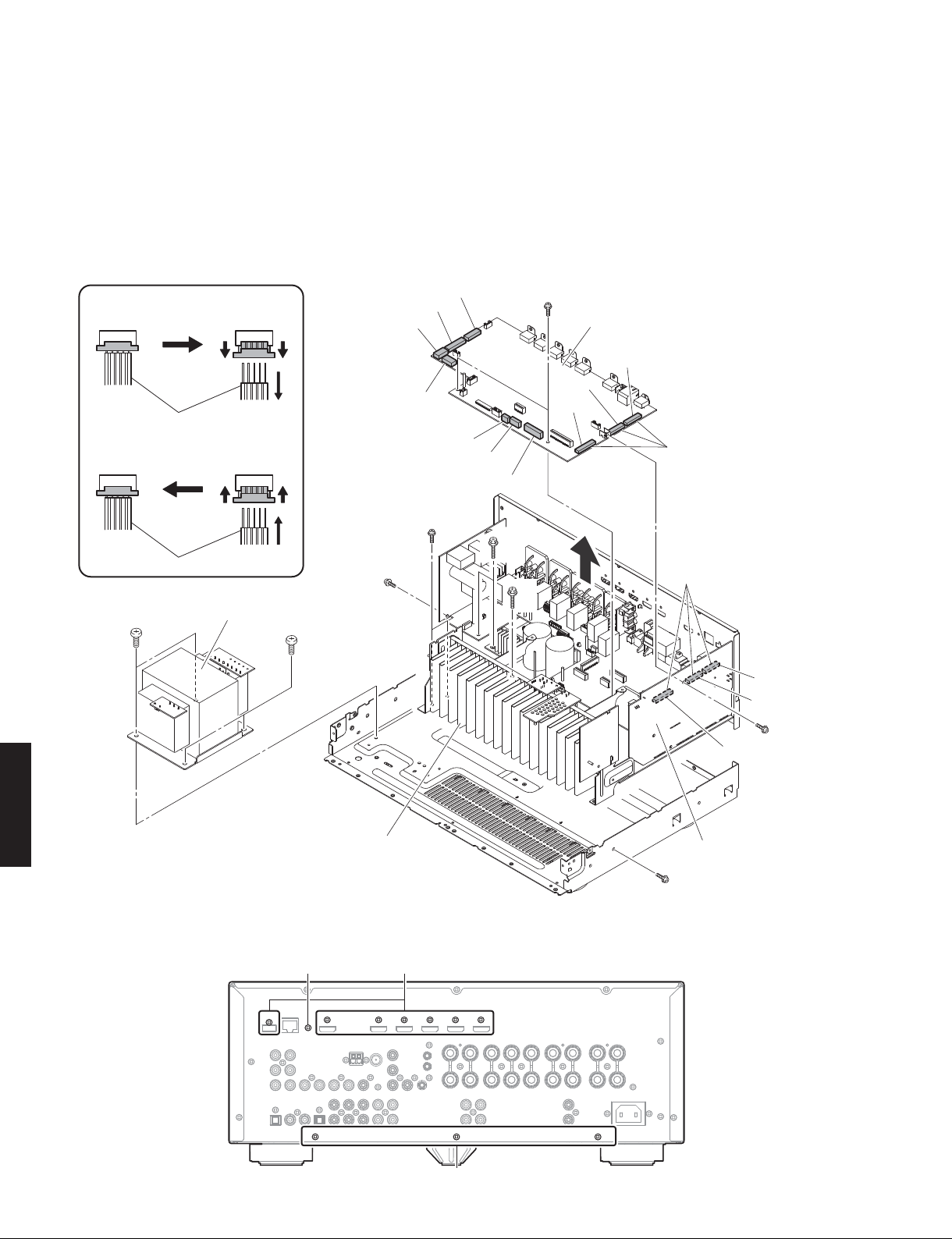

■ INTERNAL VIEW

RX-V673/HTR-6065

Top view

18

523 4 6 7 9

1516 131920

Front view

10

111421 1218 17

1

VIDEO (2) P.C.B.

2

VIDEO (3) P.C.B.

3

VIDEO (8) P.C.B. (R, S models)

4

OPERATION (8) P.C.B.

5

MAIN (2) P.C.B.

6

DIGITAL (1) P.C.B.

7

VIDEO (1) P.C.B.

8

VIDEO (4) P.C.B.

9

AM/FM TUNER

10

OPERATION (2) P.C.B.

11

OPERATION (12) P.C.B.

12

OPERATION (7) P.C.B.

13

OPERATION (11) P.C.B.

14

OPERATION (9) P.C.B. (U, C models)

15

OPERATION (10) P.C.B.

(R, T, K, A, B, G, F, L, S, H models)

6

MAIN (1) P.C.B.

16

MAIN (6) P.C.B.

17

VIDEO (9) P.C.B. (R, S models)

18

VIDEO (7) P.C.B.

19

VIDEO (6) P.C.B.

20

(U, C, T, K, A, B, G, F, L, H models)

POWER TRANSFORMER

21

OPERATION (4) P.C.B.

22

OPERATION (3) P.C.B.

23

OPERATION (1) P.C.B.

24

DIGITAL (2) P.C.B.

25

OPERATION (5) P.C.B.

26

22 23 24 25 26

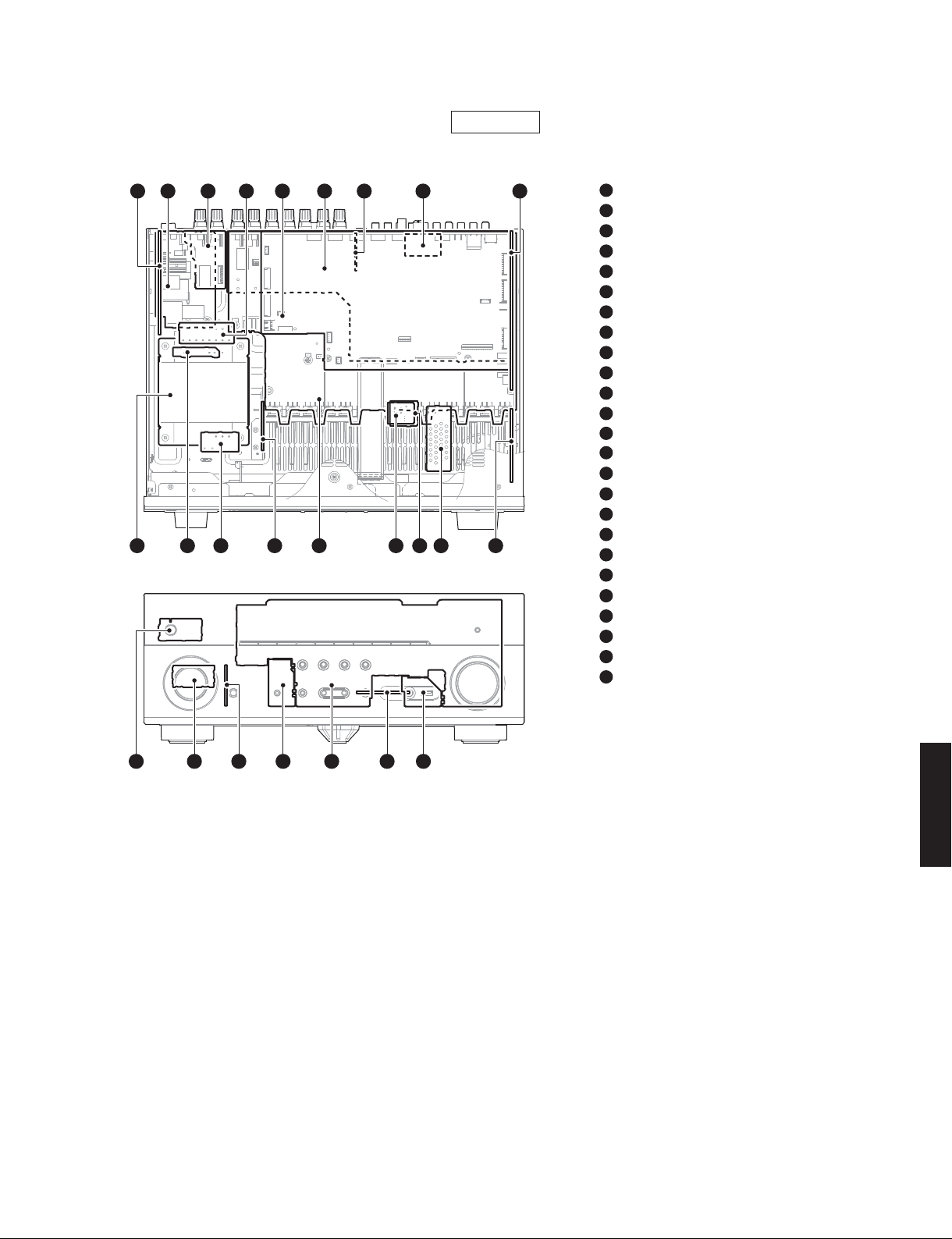

RX-A720

RX-V673/HTR-6065/

16

RX-A720

Top view

17

423 5 6 8

1218 1015

1314 111617

9

Front view

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

RX-V673/HTR-6065/RX-A720

VIDEO (2) P.C.B.

VIDEO (3) P.C.B.

OPERATION (8) P.C.B.

MAIN (2) P.C.B.

DIGITAL (1) P.C.B.

VIDEO (1) P.C.B.

VIDEO (4) P.C.B.

AM/FM TUNER

OPERATION (2) P.C.B.

OPERATION (7) P.C.B.

OPERATION (11) P.C.B.

OPERATION (9) P.C.B. (U, C models)

OPERATION (10) P.C.B. (A model)

MAIN (1) P.C.B.

MAIN (6) P.C.B.

VIDEO (7) P.C.B.

VIDEO (6) P.C.B.

POWER TRANSFORMER

OPERATION (5) P.C.B.

OPERATION (6) P.C.B.

OPERATION (3) P.C.B.

OPERATION (4) P.C.B.

OPERATION (1) P.C.B.

DIGITAL (2) P.C.B.

OPERATION (12) P.C.B.

19 21 232220 24 25

■ SERVICE PRECAUTIONS

Safety measures

• Some internal parts in this product contain high voltages and are dangerous.

Be sure to take safety measures during servicing, such as wearing insulating gloves.

• Note that the capacitors indicated below are dangerous even after the power is turned off because an electric charge

remains and a high voltage continues to exist there.

Before starting any repair work, connect a discharging resistor (5 k-ohms/10 W) to the terminals of each capacitor

indicated below to discharge electricity.

The time required for discharging is about 30 seconds per each.

C1082–C1085 on MAIN P.C.B.

C3706 on VIDEO (2) P.C.B.

For details, refer to “PRINTED CIRCUIT BOARDS”.

RX-V673/HTR-6065/

RX-A720

17

RX-V673/HTR-6065/RX-A720

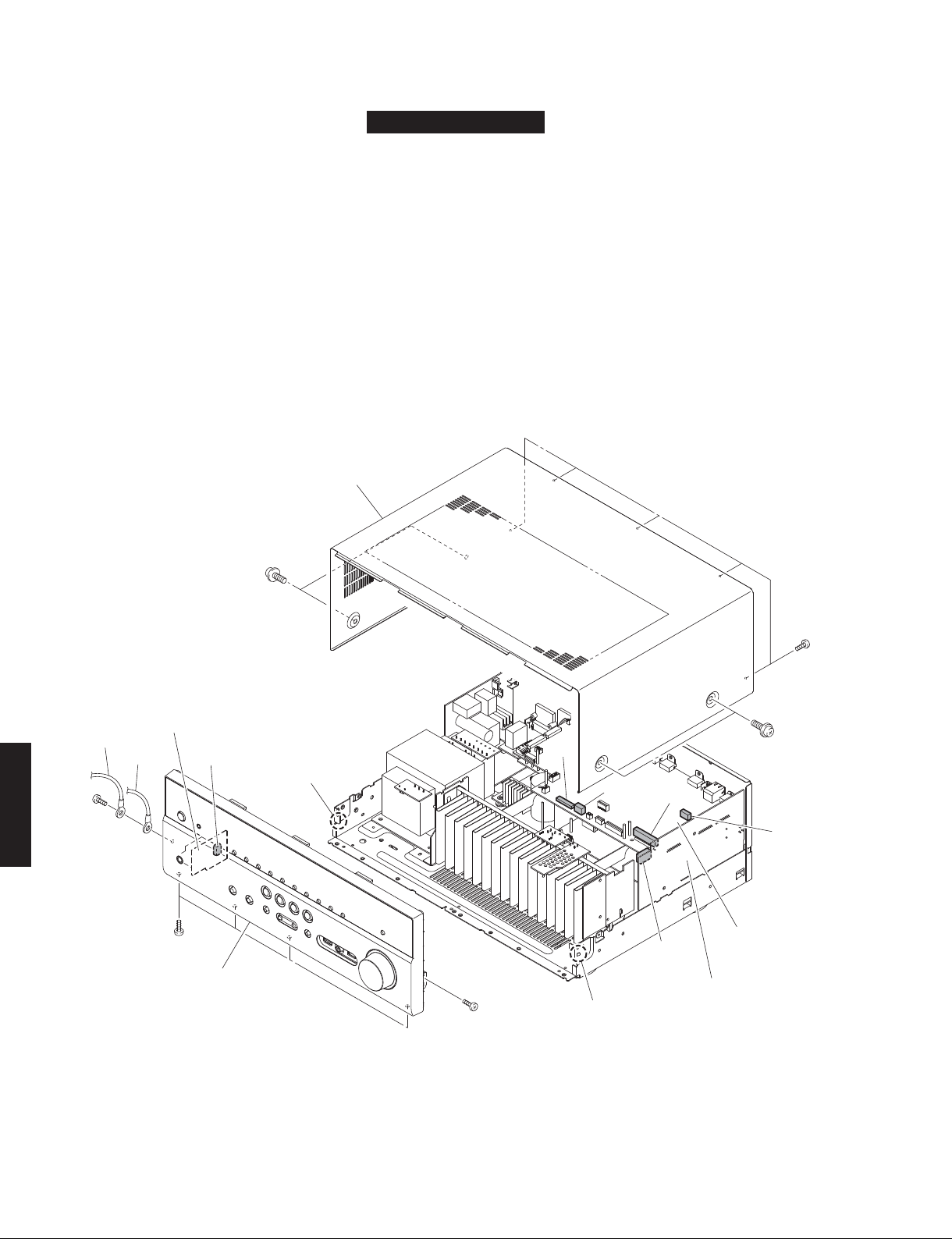

■ DISASSEMBLY PROCEDURES

RX-V673/HTR-6065

(Remove parts in the order as numbered.)

Disconnect the power cable from the AC outlet.

1. Removal of Top Cover

a. Remove 4 screws (①) and 5 screws (②). (Fig. 1)

b. Lift the rear of the top cover to remove it. (Fig. 1)

2. Removal of Front Panel Unit

a. Remove 6 screws (③), and remove W4401 and W4421. (Fig. 1)

b. Remove CB8, CB82, CB458, CB472, CB947 and CB952. (Fig. 1)

c. Release 2 hooks, and remove the front panel unit. (Fig. 1)

Top cover

W4401

RX-A720

RX-V673/HTR-6065/

③

OPERATION (3) P.C.B.

W4421

CB472

③

Front panel unit

①

Hook

③

CB8

Hook

CB947

②

①

CB82

CB952

DIGITAL (1) P.C.B.

CB458

OPERATION (2) P.C.B.

18

Fig. 1

RX-V673/HTR-6065/RX-A720

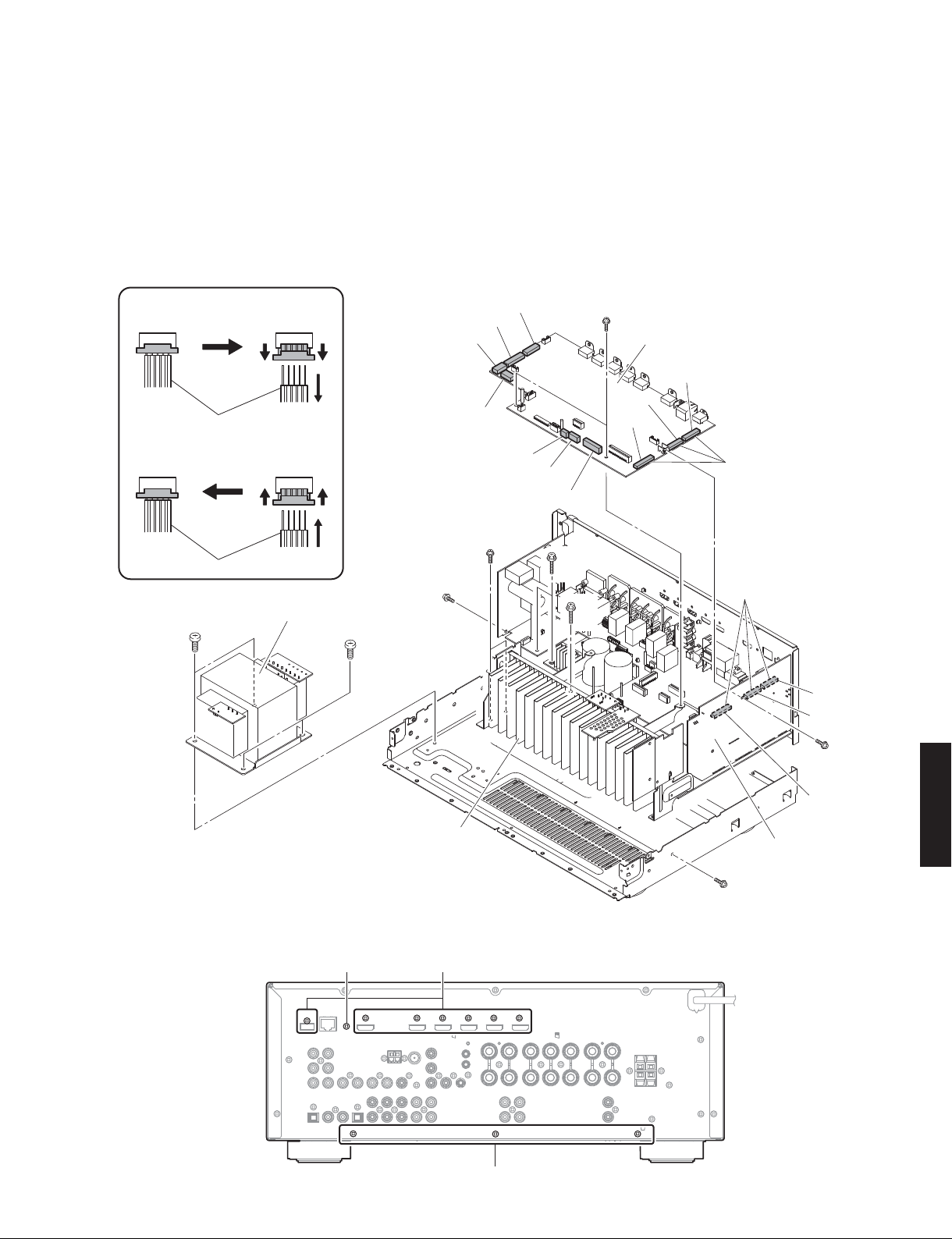

3. Removal of DIGITAL (1) P.C.B.

a. Remove screw (④) and 7 screws (⑤). (Fig. 3)

b. Remove 3 screws. (⑥). (Fig. 2)

c. Remove CB21, CB76, CB81 and CB942. (Fig. 2)

d. Unlock and remove CB78, CB79 and CB944. (Fig. 2)

e. Remove the DIGITAL (1) P.C.B. which is connected

directly to the OPERATION (2) P.C.B. with board-toboard connectors. (Fig. 2)

Remove CB78, CB79 and CB944

Connected

Cable

Connect CB78, CB79 and CB944

Connected

Cable

Unlock the connector

①

Remove the cable

②

①①

②

Lock the connector

①

Insert the cable

②

①①

②

CB942

CB944

⑦

⑩

Power transformer

⑩

4. Removal of AMP Unit and Power Transformer

a. Remove screw (⑦), 3 screws (⑧), 3 screws (⑨) and

4 screws (⑩). (Fig. 2)

b. Remove 3 screws (⑪). (Fig. 3)

c. Remove the AMP unit together with the power

transformer. (Fig. 2)

CB21

CB76

CB81

CB79

⑥

DIGITAL (1) P.C.B.

CB945

CB946

CB948

Board-to-board connectors

CB78

⑨

⑧

Board-to-board connectors

⑧

AMP unit

⑤④

Fig. 2

Rear view

CB459

CB460

CB461

OPERATION (2) P.C.B.

⑨

⑥

RX-V673/HTR-6065/

RX-A720

⑪

Fig. 3

19

RX-V673/HTR-6065/RX-A720

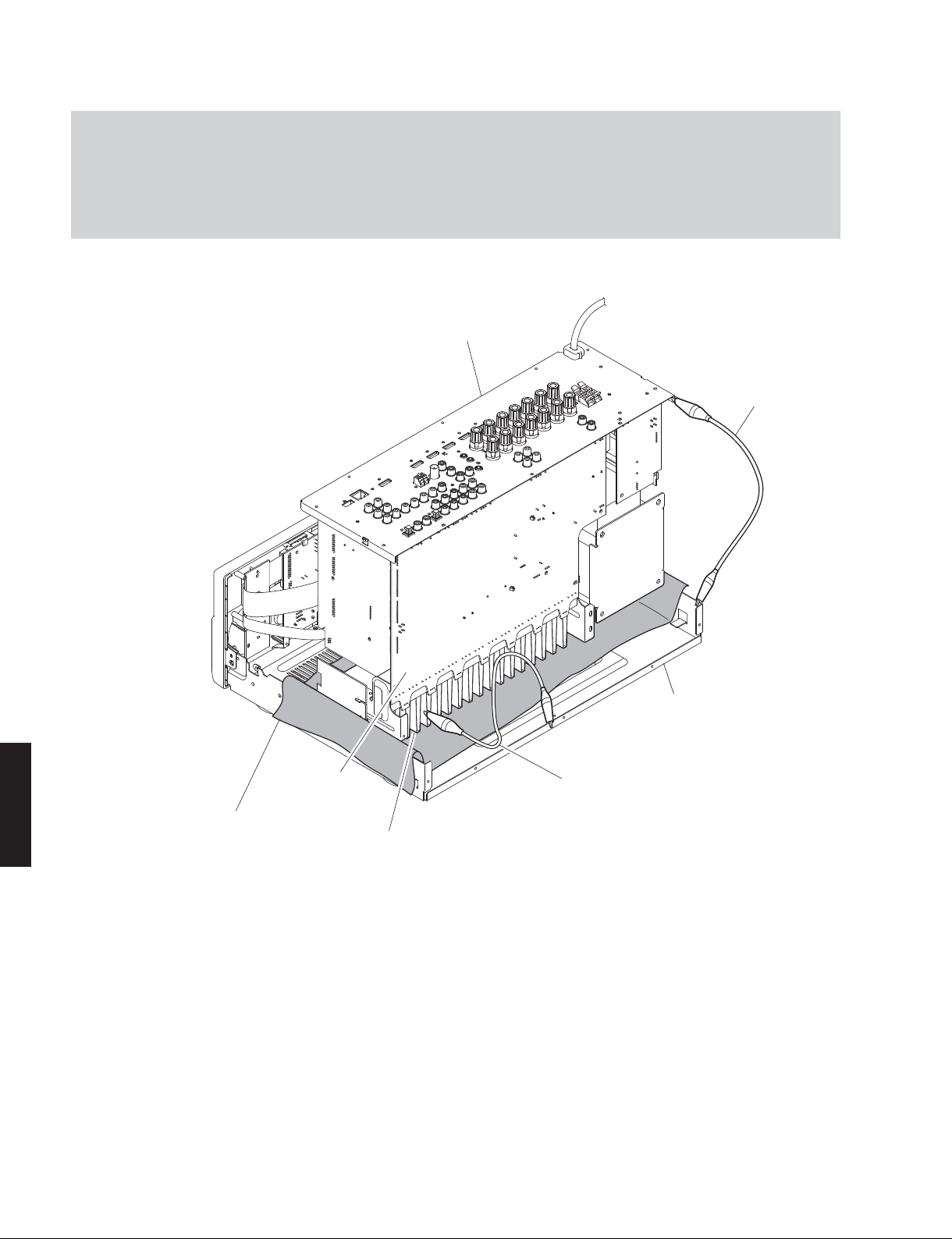

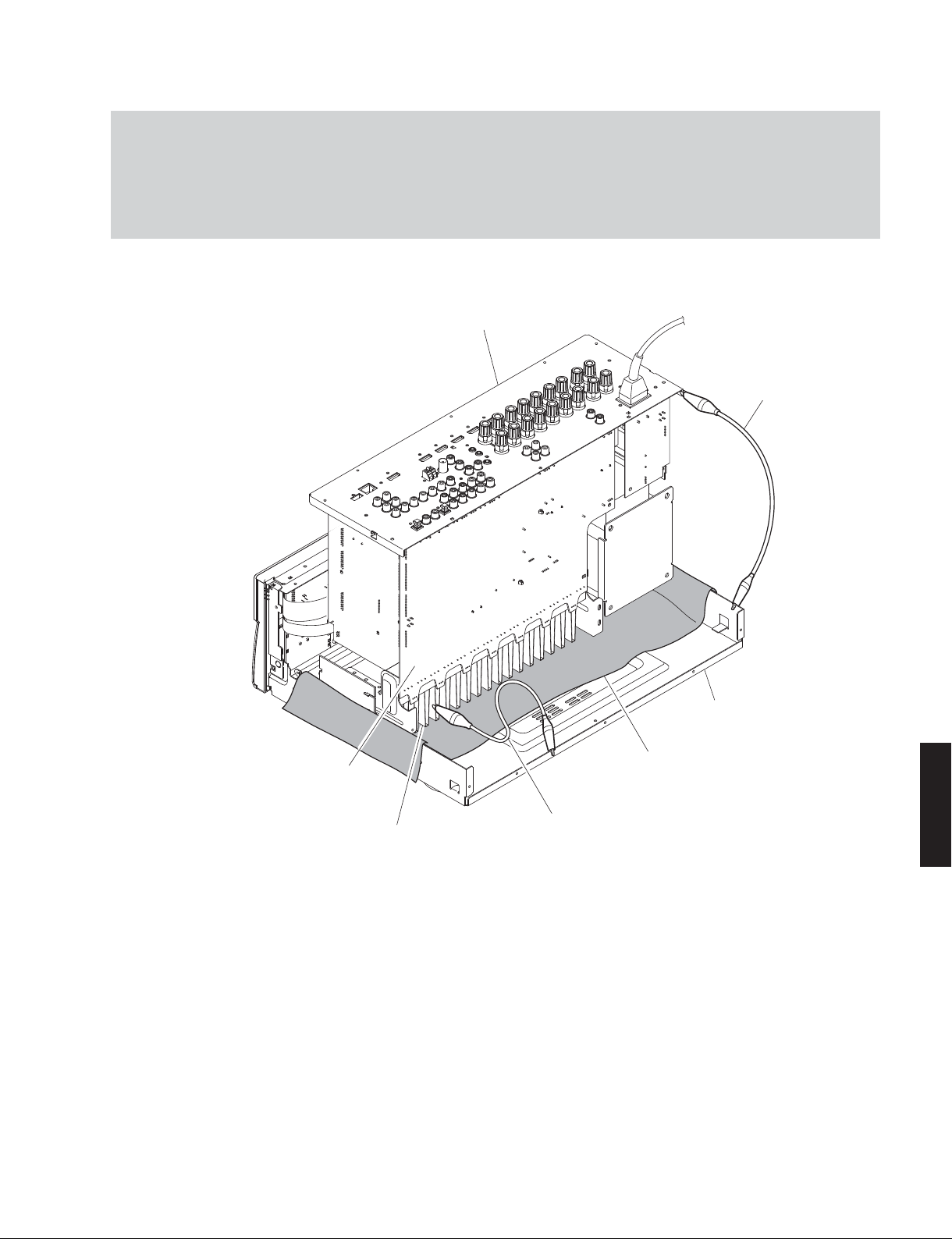

When checking the P.C.B.s:

• Place the P.C.B.s (with rear panel) upright. (Fig. 4)

• Connect the heatsink and rear panel to the chassis with a ground lead. (Fig. 4)

• Reconnect all cables (connectors) that have been disconnected.

• When connecting the flexible flat cable, be careful with polarity.

Rear panel

Ground lead

RX-A720

RX-V673/HTR-6065/

MAIN (1) P.C.B.

Rubber sheet and cloth

Chassis

Ground lead

Heatsink

Fig. 4

20

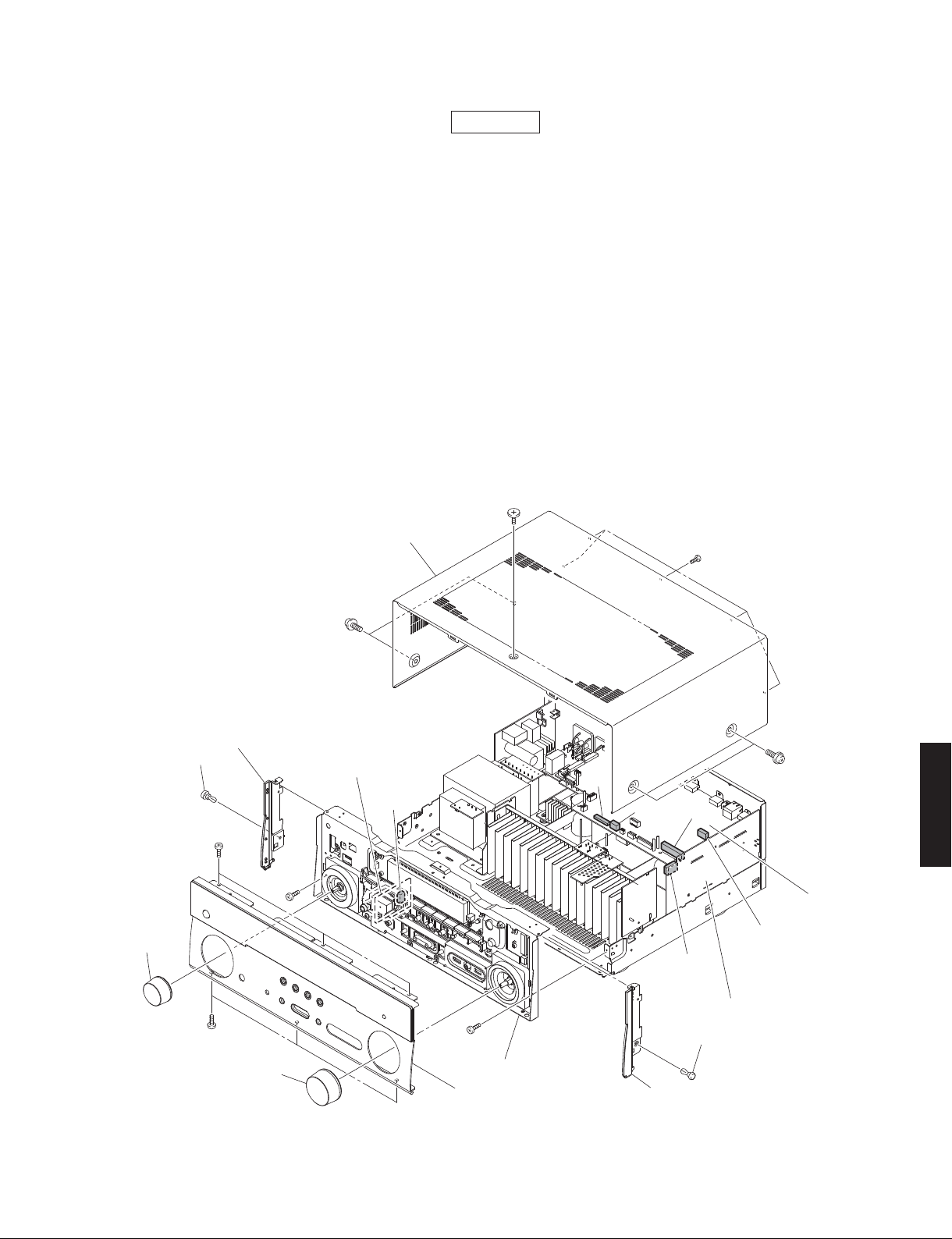

RX-A720

(Remove parts in the order as numbered.)

Disconnect the power cable from the AC outlet.

1. Removal of Top Cover

a. Remove 4 screws (①), 5 screws (②) and screw (③). (Fig. 1)

b. Lift the rear of the top cover to remove it. (Fig. 1)

2. Removal of Front Panel Unit and Sub-Chassis Unit

a. Remove knob (INPUT) and knob (VOLUME). (Fig. 1)

b. Remove 6 screws (④) and then remove the front panel unit. (Fig. 1)

c. Remove 2 push rivets and then remove the side plate (L) and side plate (R). (Fig. 1)

d. Remove CB8, CB82, CB458, CB471, CB947 and CB952. (Fig. 1)

e. Remove 2 screws (⑤) and then remove the sub-chassis unit. (Fig. 1)

RX-V673/HTR-6065/RX-A720

Knob

(INPUT)

Side plate (L)

Push rivet

④

①

OPERATION (3) P.C.B.

⑤

Top cover

CB471

③

CB8

CB947

CB82

CB458

②

①

DIGITAL (1) P.C.B.

CB952

RX-V673/HTR-6065/

RX-A720

④

(VOLUME)

Knob

⑤

Sub-chassis unit

Front panel unit

Fig. 1

OPERATION (2) P.C.B.

Push rivet

Side plate (R)

21

RX-V673/HTR-6065/RX-A720

3. Removal of DIGITAL (1) P.C.B.

a. Remove screw (⑥) and 7 screws (⑦). (Fig. 3)

b. Remove 3 screws. (⑧). (Fig. 2)

c. Remove CB21, CB76, CB81 and CB942. (Fig. 2)

d. Unlock and remove CB78, CB79 and CB944. (Fig. 2)

e. Remove the DIGITAL (1) P.C.B. which is connected

directly to the OPERATION (2) P.C.B. with board-toboard connectors. (Fig. 2)

Remove CB78, CB79 and CB944

Connected

Cable

Connect CB78, CB79 and CB944

Connected

Cable

⑫

Unlock the connector

①

Remove the cable

②

①①

Lock the connector

①

Insert the cable

②

①①

Power transformer

②

②

⑨

⑫

CB76

CB942

CB944

⑪

4. Removal of AMP Unit and Power Transformer

a. Remove screw (⑨), 3 screws (⑩), 3 screws (⑪) and

4 screws (⑫). (Fig. 2)

b. Remove 3 screws (⑬). (Fig. 3)

c. Remove the AMP unit together with the power

transformer. (Fig. 2)

CB21

CB81

CB79

CB78

⑧

DIGITAL (1) P.C.B.

CB945

CB946

CB948

Board-to-board connectors

⑩

Board-to-board connectors

⑩

RX-A720

RX-V673/HTR-6065/

AMP unit

CB459

CB460

⑧

CB461

OPERATION (2) P.C.B.

⑪

Fig. 2

⑦⑥

Rear view

22

⑬

Fig. 3

When checking the P.C.B.s:

• Place the P.C.B.s (with rear panel) upright. (Fig. 4)

• Connect the heatsink and rear panel to the chassis with a ground lead. (Fig. 4)

• Reconnect all cables (connectors) that have been disconnected.

• When connecting the flexible flat cable, be careful with polarity.

Rear panel

RX-V673/HTR-6065/RX-A720

Ground lead

MAIN (1) P.C.B.

Heatsink

Fig. 4

Ground lead

Chassis

Rubber sheet and cloth

RX-V673/HTR-6065/

RX-A720

23

RX-V673/HTR-6065/RX-A720

■ UPDATING FIRMWARE

When the following parts are replaced, the firmware must be updated to the latest version.

DIGITAL P.C.B.

FPGA Flash ROM: IC77 on DIGITAL P.C.B.

DSP(TI) Flash ROM: IC923 on DIGITAL P.C.B.

NETWORK Flash ROM: IC953 on DIGITAL P.C.B.

● Confirmation of firmware version and checksum

Before and after updating the firmware, check the firmware version and checksum by using the self-diagnostic

function menu.

Start up the self-diagnostic function and select “S4. ROM VERSION/CHECKSUM” menu.

Using the sub-menu, have the firmware version and checksum displayed, and note them down.

(See “SELF-DIAGNOSTIC FUNCTION”)

* When the firmware version is different from written one after updating, perform the updating procedure again from

the beginning again.

● Initializing the back-up IC (EEPROM: IC82 on DIGITAL P.C.B.)

After updating the firmware, the back-up IC MUST be initialized by the following procedure to store the setting

information (soundfield parameters, system memory and tuner presetting, etc.) properly.

Start up the self-diagnostic function and select “S3. FACTORY PRESET” menu. (See “SELF-DIAGNOSTIC FUNCTION”)

Select “PRESET RSRV”, press the “MAIN ZONE

the back-up IC is initialized.

● Required Tools

• USB storage device

• Firmware

● Preparation

RX-A720

RX-V673/HTR-6065/

1. Download the latest firmware from the specified download source to the folder of the PC.

2. Copy the latest firmware from the PC to the root folder of the USB storage device.

Note) When the latest firmware is copied to a sub-folder of the USB storage device, the update will not proceed.

” key to turn off the power once and turn on the power again. Then

RX-V673/HTR-6065/RX-A720: R0309-xxxx.bin

24

RX-V673/HTR-6065/RX-A720

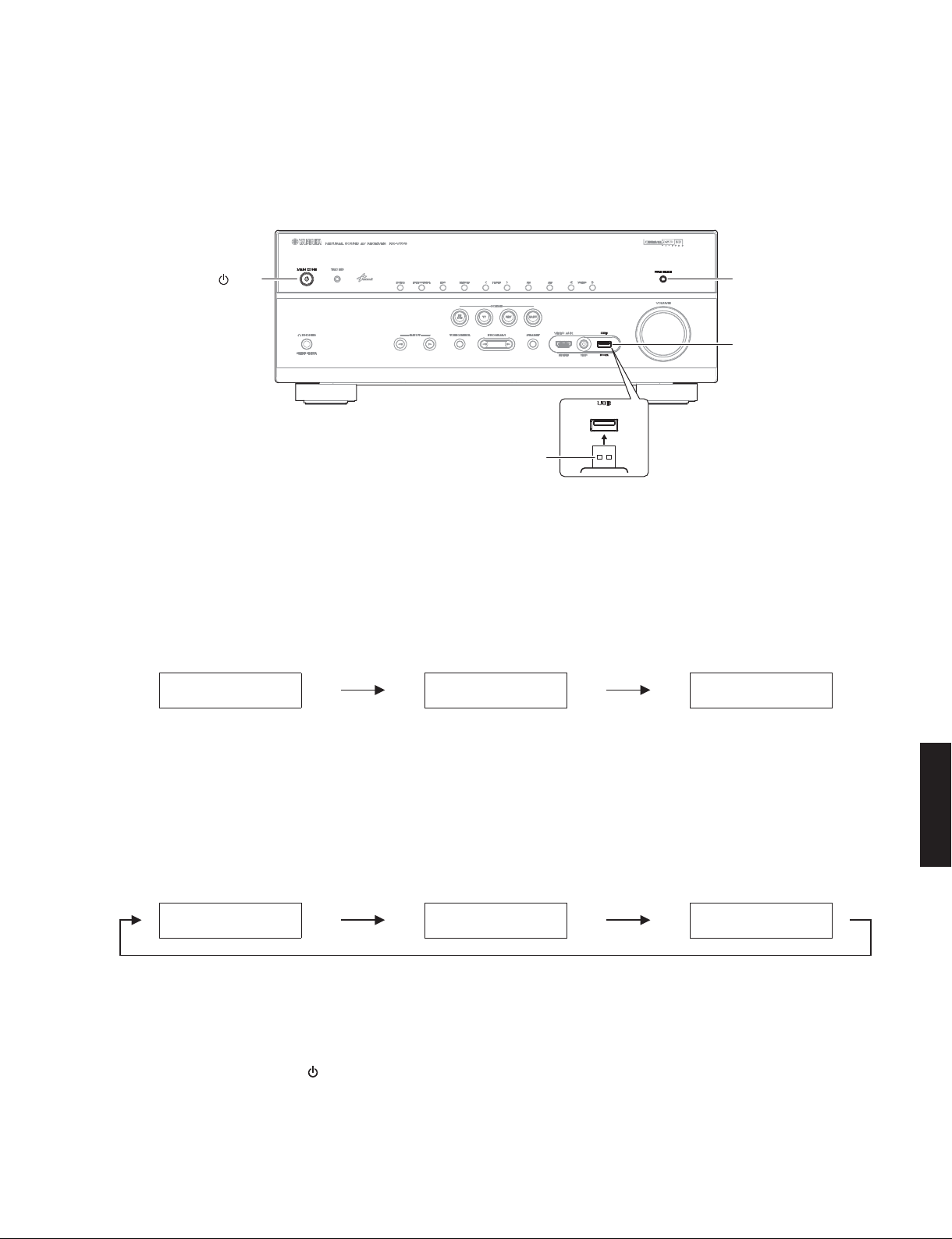

● Operation Procedures

1. Insert the USB storage device to the USB jack. (Fig. 1)

2. While pressing the “PURE DIRECT” key, connect the power cable to the AC outlet. (Fig. 1)

"MAIN ZONE " key "PURE DIRECT" key

USB jack

USB storage device

Fig. 1

3. The USB UPDATE mode is activated and “USB UPDATE” is displayed. Writing of the firmware starts automatically.

(Fig. 2)

Writing is started.

USBUPDATE

VERIFYING...

Writing being executed.

Sx-x:xx%

Fig. 2

4. When writing of the firmware is completed, “UPDATE SUCCESS”, “PLEASE...” and “POWER OFF!” are displayed

repeatedly. (Fig. 3)

Writing is completed.

UPDATESUCCESS

PLEASE...

POWEROFF!

RX-V673/HTR-6065/

RX-A720

Fig. 2

5. Press the “MAIN ZONE

” key to turn off the power. (Fig. 1)

6. Remove the USB storage device from the USB jack. (Fig. 1)

7. Start up the self-diagnostic function and check that the firmware version and checksum are the same as written

ones. (See “Confirmation of firmware version and checksum”)

25

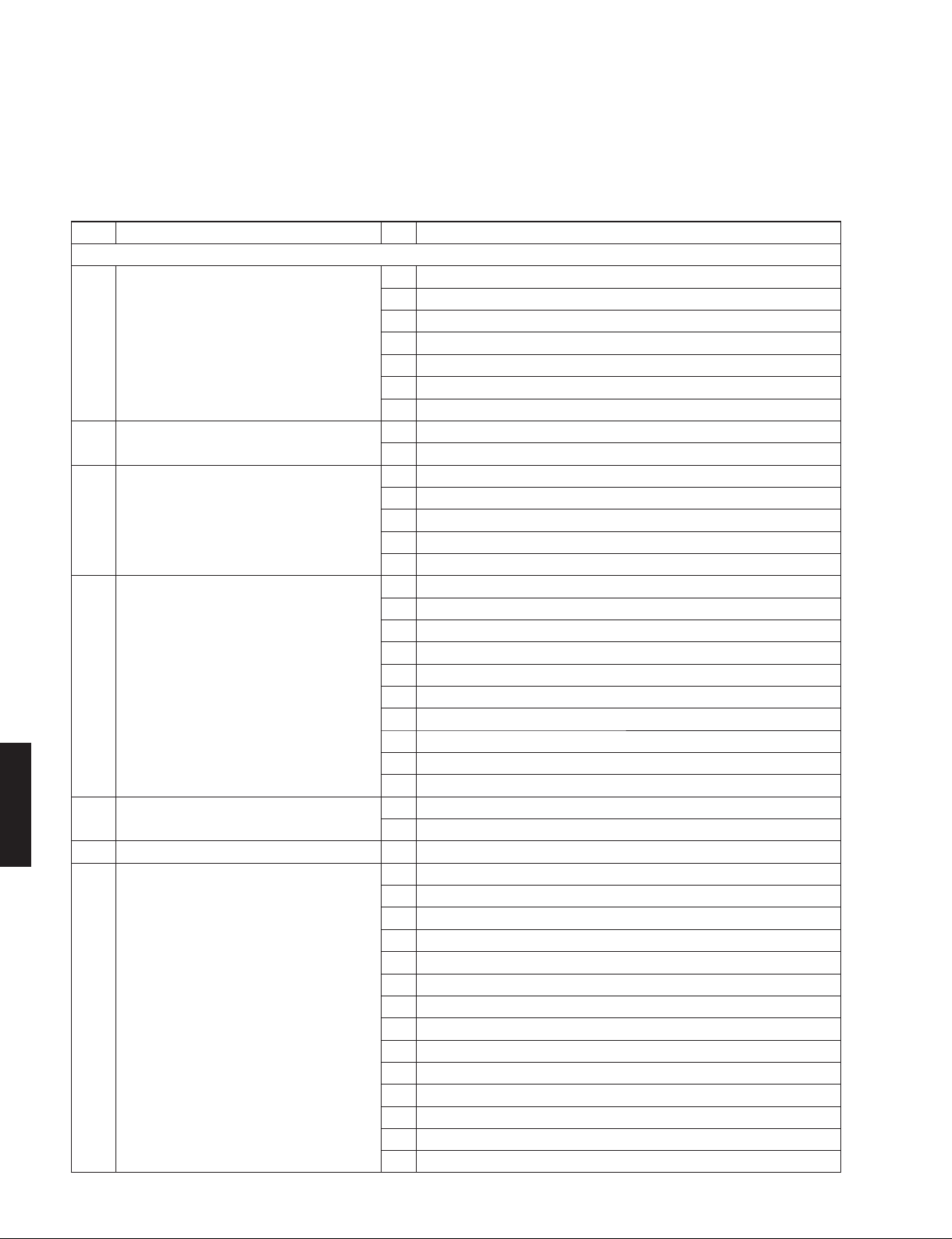

RX-V673/HTR-6065/RX-A720

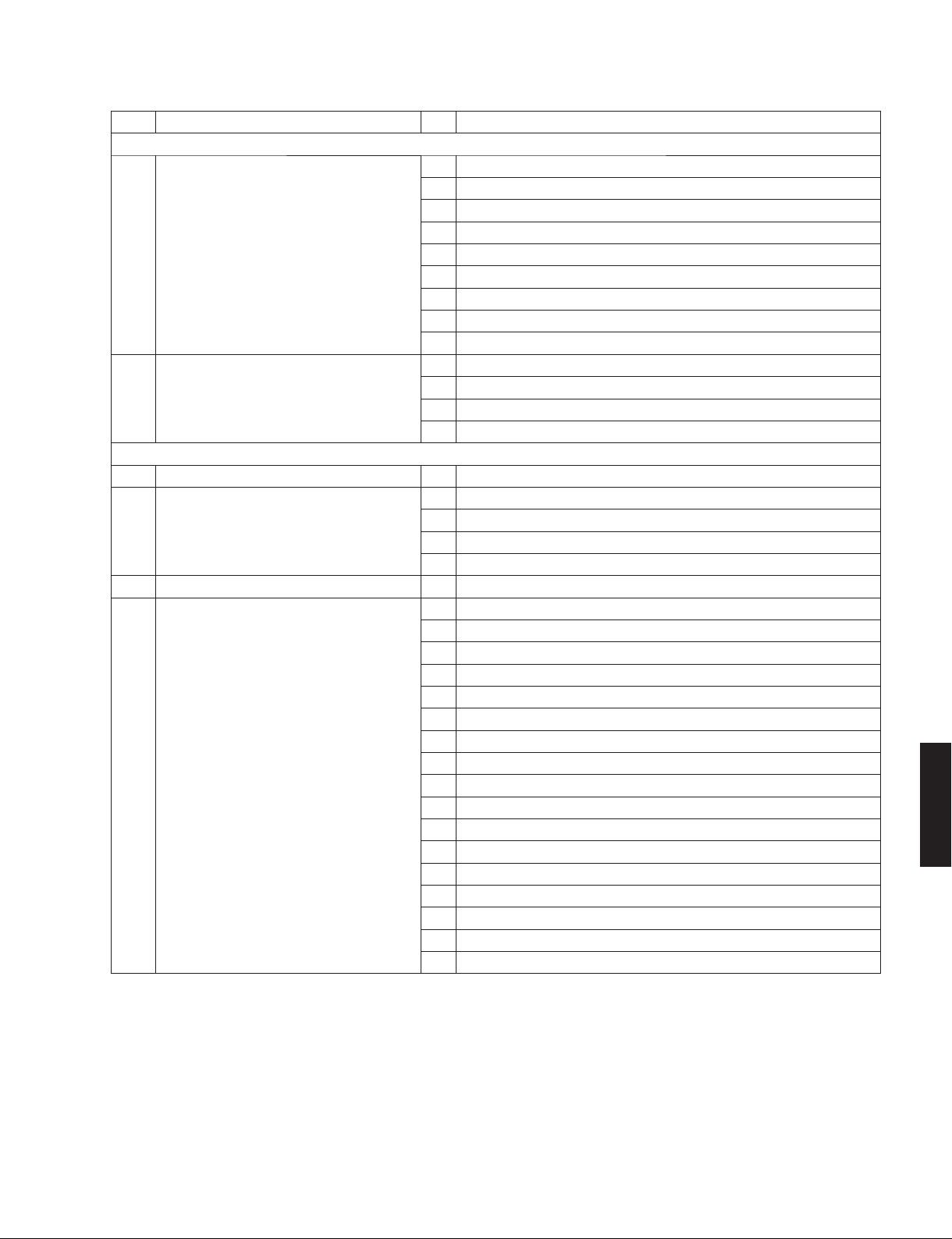

■ SELF-DIAGNOSTIC FUNCTION

This unit has self-diagnostic functions that are intended for inspection, measurement and location of faulty point.

There are 22 main menu items, each of which has sub-menu items.

Listed in the table below are main menu items and sub-menu items.

Note: Some of the menu items listed below may not apply to the models covered in this service manual.

No. Main menu No. Sub-menu

A: Audio system

A1 DSP AUDIO 1 DSP MARGIN

A2 DIRECT AUDIO 1 ANALOG DIRECT VH

A3 HDMI AUDIO 1 HDMI AUTO

A4 SPEAKERS SET 1 BI-AMP

A5 MULTI CHANNEL INPUT 1 MULTI CHANNEL INPUT 8 ohms

RX-A720

RX-V673/HTR-6065/

(Not for service)

A6 MIC CHECK 1 MIC ROUTE CHECK

A7 MANUAL TEST 1 TEST ALL

2 DSP NON MARGIN

3 INVALID ITEM

(Not for service)

4 DSP FULL CENTER

5 DSP FULL SURROUND

6 DSP FULL SURROUND BACK

7 DSP FULL SUBWOOFER

2 ANALOG DIRECT VL

2 INVALID ITEM

(Not for service)

3 ARC1

4 INVALID ITEM

5 INVALID ITEM

(Not for service)

(Not for service)

2 ZONE/TONE=MAX

3 ZONE/TONE=MIN

4 INVALID ITEM

5 INVALID ITEM

(Not for service)

(Not for service)

6 D-PARTY MODE

7 FULL MUTE

8 INVALID ITEM

9 INVALID ITEM

10 INVALID ITEM

(Not for service)

(Not for service)

(Not for service)

2 MULTI CHANNEL INPUT 6 ohms

2 TEST FRONT L

3 TEST CENTER

4 TEST FRONT R

5 TEST SURROUND R

6 TEST SURROUND BACK R

7 TEST SURROUND BACK L

8 TEST SURROUND L

9 TEST FRONT PRESENCE L

10 TEST FRONT PRESENCE R

11 INVALID ITEM

12 INVALID ITEM

(Not for service)

(Not for service)

13 TEST LFE 1

14 INVALID ITEM

(Not for service)

26

No. Main menu No. Sub-menu

D: Display system

D1 FL CHECK 1 FL CHECK

2 ALL SEGMENT OFF

3 ALL SEGMENT ON

4 CHECK PATTERN 1

5 CHECK PATTERN 2

Z: Zone system

Z1 ZONE TEST 1 AV1

2AV2

3AV3

4AV4

(Not for service)

(Not for service)

(Not for service)

(Not for service)

5AV5

6AV6

7 AUDIO1

8 AUDIO2

9 V-AUX

10 PHONO

(Not for service)

(Not for service)

U: Universal system

U1 USB 1 USB FRONT 1 TRACK

2 USB FRONT 2 TRACK

3 USB_VBUS HIGH POWER

N: Network system

N1 NETWORK 1 IP ADDRESS CHECK

2 MAC ADDRESS CHECK

3 LINE NOISE 100 MDI

4 LINE NOISE 100 MDIX

5 LINE NOISE 10 MDI

6 LINE NOISE 10 MDIX

(Not for service)

(Not for service)

(Not for service)

(Not for service)

7 EXT TEST

8 MAC ADDRESS

C: Communication system

C1 DIGITAL PCB CHECK 1 ALL

2 BUS FLASH ROM

3 BUS FPGA

4 I2C

5 FPGA RAM

6 BUS DIR1

7 BUS DSP1

8 EEPROM

9 INVALID ITEM

10 INVALID ITEM

11 INVALID ITEM

(Not for service)

(Not for service)

(Not for service)

C2 NETWORK IC CHECK 1 ALL

2 LINK CHECK

3

PHY TEST

4 BUS RAM

5 APL ID CHECK

RX-V673/HTR-6065/RX-A720

RX-V673/HTR-6065/

RX-A720

27

RX-V673/HTR-6065/RX-A720

No. Main menu No. Sub-menu

V: Video system

V1 ANALOG VIDEO CHECK

V2 DIGITAL VIDEO CHECK 1 LOOPBACK TEST 1

V3 TEST PATTERN 1 480i

RX-A720

RX-V673/HTR-6065/

1 ANALOG BYPASS

2 INVALID ITEM

3 INVALID ITEM

(Not for service)

(Not for service)

4 MUTE CHECK

5 TEST PATTERN

(Not for service)

6 VIDEO IN

2 LOOPBACK TEST 2

3 LOOPBACK TEST 3

4 INVALID ITEM

5 INVALID ITEM

6 INVALID ITEM

(Not for service)

(Not for service)

(Not for service)

7 HDMI REPEAT

8 DIGITAL CVBS

9 INVALID ITEM

(Not for service)

10 DIGITAL COMPONENT

11 DIGITAL COMPONENT SC

12 GUI-VIDEO OUT

2 480p

3 720p 60Hz

4 1080i 60Hz

5 1080p 60Hz

6 576i

7 576p

8 720p 50Hz

9 1080i 50Hz

10 1080p 50Hz

11 1080p 24Hz

12 1080p 24Hz 3D/FP

13 720p 60Hz 3D/FP

14 720p 50Hz 3D/FP

15 1080i 60Hz 3D/FP

16 1080i 60Hz 3D/SS

17 1080i 50Hz 3D/SS

18 720p 60Hz 3D/TB

19 720p 50Hz 3D/TB

20 1080p 24Hz 3D/TB

21 4k 24Hz

28

No. Main menu No. Sub-menu

P: Power and protection system

P1 SYSTEM MONITOR 1 DC

2 PS1/PS2/PS3

3 THM

4 INVALID ITEM

(Not for service)

5 OUTPUT LEVEL

6 LIMITER CONTROL

7 L3 (J model)

(Not for service)

8 KEY1/KEY2

9 USB-VBUS

(Not for service)

P2 PROTECTION HISTORY 1 HISTORY 1

2 HISTORY 2

3 HISTORY 3

4 HISTORY 4

S: System and version system

S1 FIRMWARE UPDATE 1 FIRMWARE UPDATE

(Not for service)

S2 SET INFORMATION 1 MODEL

2 DESTINATION

3 DEBUG

4 NET RESTART COUNTER

(Not for service)

(Not for service)

S3 FACTORY PRESET 1 PRESET INHIBIT/RESERVE

S4 ROM VERSION/CHECKSUM 1 SYSTEM VERSION

2 MICROPROCESSOR VERSION

3 MICROPROCESSOR CHECKSUM

4 FLASH ROM VERSION

5 FLASH ROM CHECKSUM

6 NETWORK MICROPROCESSOR VERSION

7 NETWORK MICROPROCESSOR CHECKSUM

8 DSP1 VERSION

9 DSP1 CHECKSUM

10 INVALID ITEM

11 INVALID ITEM

(Not for service)

(Not for service)

12 GUI VERSION

13 FPGA GUI VERSION

14 FPGA SD VERSION

15 FPGA HD VERSION

16 INVALID ITEM

17 INVALID ITEM

(Not for service)

(Not for service)

RX-V673/HTR-6065/RX-A720

RX-V673/HTR-6065/

RX-A720

29

RX-V673/HTR-6065/RX-A720

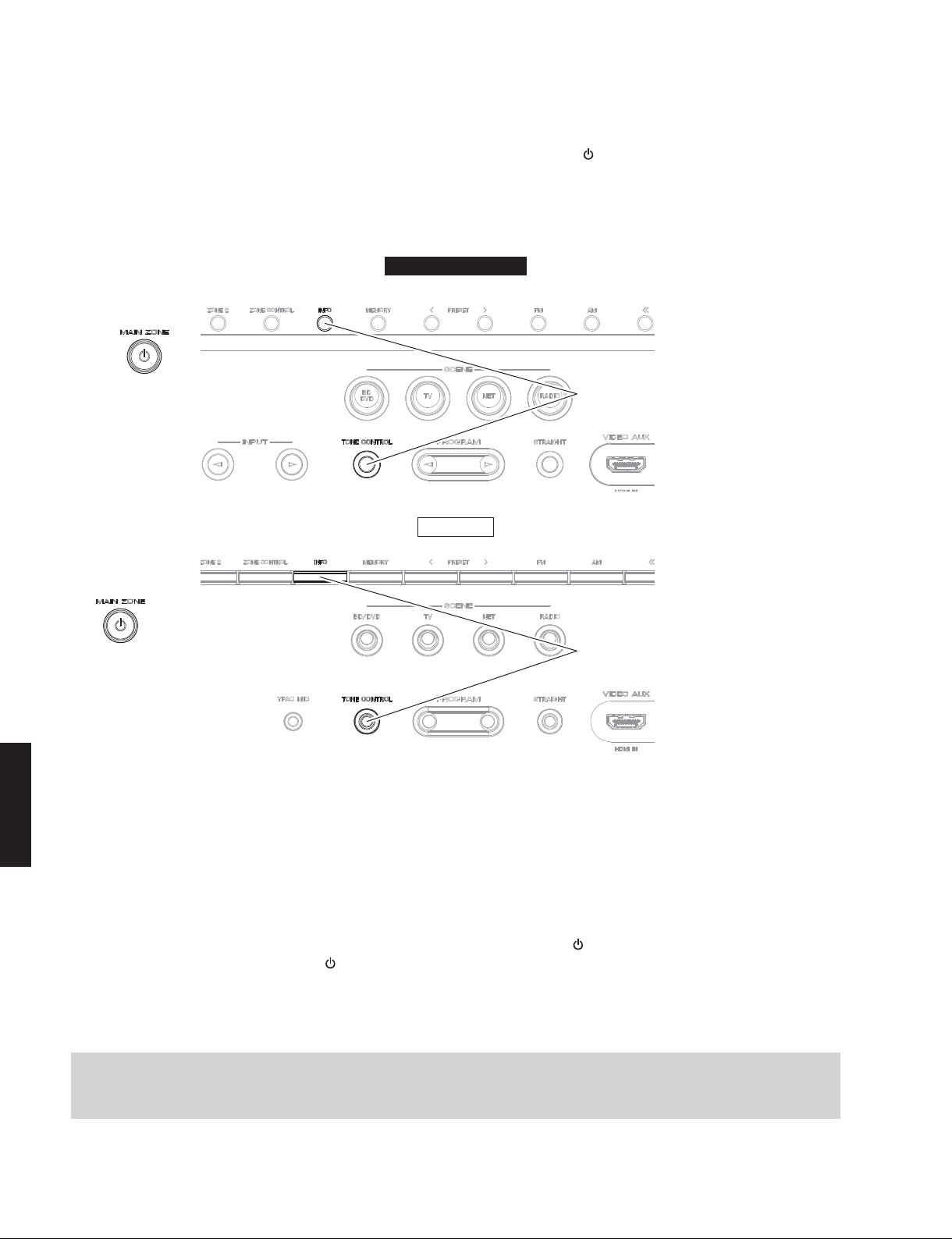

● Starting Self-Diagnostic Function

While pressing the “TONE CONTROL” and “INFO” keys, press the “MAIN ZONE ” key to turn on the power, and release

those 2 keys.

The self-diagnostic function mode is activated.

Keys of this unit

RX-V673/HTR-6065

While pressing these keys, turn on the power.

RX-A720

RX-V673/HTR-6065/

● Starting Self-Diagnostic Function in the protection cancel mode

If the protection function works and causes hindrance to troubleshooting, cancel the protection function by the procedure

below, and it will be possible to enter the self-diagnostic function mode. (The protection functions other than the excess

current detect function will be disabled.)

While pressing the “TONE CONTROL” and “INFO” keys, press the “MAIN ZONE

pressing those 2 keys and “MAIN ZONE

The self-diagnostic function mode is activated with the protection functions disabled.

In this mode, the “SLEEP” segment of the FL display flashes to indicate that the mode is self-diagnostic function mode with the

protection functions disabled.

RX-A720

While pressing these keys, turn on the power.

” key to turn on the power and keep

” key for 3 seconds or longer.

CAUTION!

Using this unit with the protection function disabled may cause further damage to this unit. Use special care for this point

when using this mode.

30

RX-V673/HTR-6065/RX-A720

● Canceling Self-Diagnostic Function

1. Before canceling self-diagnostic function, execute setting for “S3. FACTORY PRESET” menu. (Memory initialization

inhibited or Memory initialized).

* In order to keep the user memory preserved, be sure to select PRESET INHIBIT (Memory initialization inhibited).

2. Press the “MAIN ZONE

” key to turn off the power.

● Display provided when Self-Diagnostic Function started

The display is as described below depending on the situation when the power to this unit is turned off.

1. When the power is turned off by usual operation:

“NO PROTECT” is displayed. Then “A1-1. DSP MARGIN” is displayed in a few seconds.

Main menu displayOpening message

After a few seconds

A1-1

NOPROTECT

DSPMARGIN

2. When the protection function worked to turn off the power:

The information of protection function which worked at that time is displayed. Then “A1-1. DSP MARGIN” is displayed in

a few seconds.

Note: At that time if you restart the self-diagnostic function after turning off the power once, “NO PROTECT” will be

displayed. That is because that situation is equal to “1. When the power is turned off by usual operation:”.

However history of the protection function is stored in memory as backup data. For details, refer to “P2.

PROTECTION HISTORY” menu.

2-1. When there is a history of protection function due to excess current.

IPROTECT

Cause: An excessive current flowed through the power amplifier.

Supplementary information: As over current of the power amplifier is detected, check condition of each power transistor.

Turning on the power without correcting the abnormality will cause the protection function to work immediately and the

power supply will instantly be shut off.

RX-V673/HTR-6065/

RX-A720

Notes:

• Applying the power to this unit without correcting the abnormality can be dangerous and cause additional

circuit damage. To avoid this, if “I PROTECT” protection function works 1 time, the power will not turn on even

when the “MAIN ZONE

function.

• The output transistors in each amplifier channel should be checked for damage before applying power to this

unit.

• Amplifier current should be monitored by measuring DC voltage across the emitter resistors for each channel.

” key is pressed. In order to turn on the power again, start up the self-diagnostic

31

RX-V673/HTR-6065/RX-A720

2-2. When the protection function worked due to abnormal DC output.

H: Displayed when the voltage is HIGHER than upper limit

L: Displayed when the voltage is LOWER than lower limit

DCPRT:xxxH

xxx: A/D conversion value of voltage at the moment when the protection function worked

(Reference voltage: 3.3 V=255)

Cause: DC output of the power amplifier is abnormal.

Supplementary information: The protection function worked due to a DC voltage appearing at the speaker terminal. A

cause could be a defect in the amplifier.

Turning on the power without correcting the abnormality will cause the protection function to work in 5 seconds and the

power supply will be shut off.

2-3. When the protection function worked due to abnormal voltage in the power supply section.

Cause: The voltage in the power supply section is abnormal.

Supplementary information: The protection function worked due to a defect or overload in the power supply.

Turning on the power without correcting the abnormality will cause the protection function to work in 1 seconds and the

power supply will be shut off.

Notes:

RX-A720

RX-V673/HTR-6065/

• Applying the power to this unit without correcting the abnormality can be dangerous and cause additional

circuit damage. To avoid this, if “PS” and “DC” protection function works 3 times consecutively, the power will

not turn on even when the “MAIN ZONE

diagnostic function.

• The output transistors in each amplifier channel should be checked for damage before applying power to this

unit.

• Amplifier current should be monitored by measuring DC voltage across the emitter resistors for each channel.

H: Displayed when the voltage is HIGHER than upper limit

L: Displayed when the voltage is LOWER than lower limit

PSxPRT:xxxL

xxx: A/D conversion value of voltage at the moment when the protection function worked

(Reference voltage: 3.3 V=255)

PS1/PS2/PS3

” key is pressed. In order to turn on the power again, start up the self-

32

RX-V673/HTR-6065/RX-A720

2-4. When the protection function worked due to excessive heatsink temperature.

H: Displayed when the voltage is HIGHER than upper limit

L: Displayed when the voltage is LOWER than lower limit

TMPPRT:xxxL

xxx: A/D conversion value of voltage at the moment when the protection function worked

(Reference voltage: 3.3 V=255)

Cause: The temperature of the heatsink is excessive.

Supplementary information: The protection function worked due to the temperature limit being exceeded. Causes could

be poor ventilation or a defect related to the thermal sensor.

Turning on the power without correcting the abnormality will cause the protection function to work in 1 seconds and the

power supply will be shut off.

● History of protection function

When the protection function has worked, its history is stored in memory as backup data.

Even if no abnormality is noted while servicing the unit, an abnormality which has occurred previously can be defined

as long as the backup data has been stored.

For details, refer to “P2. PROTECTION HISTORY” menu.

RX-V673/HTR-6065/

RX-A720

33

RX-V673/HTR-6065/RX-A720

● Operation procedure of Main menu and Sub-menu

There are 22 main menu items, each of which has sub-menu items.

Main menu selection

Select the main menu using “SCENE TV” (forward) and “SCENE BD/DVD” (reverse) keys.

Sub-menu selection

Select the sub-menu using “SCENE RADIO” (forward) and “SCENE NET” (reverse) keys.

Keys of this unit

Main menu selection

Reverse Forward

Sub-menu selection

Reverse Forward

● Functions in Self-Diagnostic Function mode

In addition to the self-diagnostic function menu items, functions listed below are available.

• Power ON/OFF

• Master volume

• Muting

• Input selection

• Zone control

* Functions related to the tuner and the set menu are not available.

RX-A720

RX-V673/HTR-6065/

● Initial settings when Self-Diagnostic Function started

The following initial settings are used when self-diagnostic function is started.

• Master volume: -20 dB / Zone volume: +2.5dB

• Input: HDMI1 / Zone input: AUDIO1

• Main menu: A1-1. DSP MARGIN

• Speaker setting: LARGE, Bass out to SWFR (All channels)

• HDMI Control: Off

• Zone 2: On

* When self-diagnostic function is canceled, these settings are restored to those before starting self-diagnostic function.

34

● Details of Self-Diagnostic Function menu

A1. DSP AUDIO

This menu is used to check audio signal route via DSP.

A1-1. DSP MARGIN

The audio signal is output including the head margin via DSP.

* When input source is stereo, signal is assigned as below.

Front L: Front L, Center, Surround L, Surround Back L

Front R: Front R, Surround R, Surround Back R

Front L +10 dB: Subwoofer

A1-1

DSPMARGIN

A1-2. DSP NON MARGIN

The SUBWOOFER signal is output including the head margin via DSP.

The audio signal other than SUBWOOFER is output without including the head margin via DSP.

RX-V673/HTR-6065/RX-A720

A1-2

DSPNONMARGIN

A1-3. INVALID ITEM

Not for service.

A1-3

INVALIDITEM

A1-4. DSP FULL CENTER

The audio signal is output to only CENTER channel in digital full bit without including the head margin.

A1-4

DSPFULLC

A1-5. DSP FULL SURROUND

The audio signal is output to only SURROUND L/R channels in digital full bit without including the head margin.

RX-V673/HTR-6065/

RX-A720

A1-5

DSPFULLSUR

35

RX-V673/HTR-6065/RX-A720

A1-6. DSP FULL SURROUND BACK

The audio signal is output to only SURROUND BACK L/R channel in digital full bit without including the head

margin.

A1-7. DSP FULL SUBWOOFER

The audio signal is output to only SUBWOOFER channel in digital full bit without including the head margin.

A1-6

DSPFULLSB

A1-7

DSPFULLSW

A2. DIRECT AUDIO

This menu is used to check audio signal route of PURE DIRECT mode.

A2-1. DIRECT VH

RX-A720

RX-V673/HTR-6065/

A2-2. DIRECT VL

The analog input audio signal is output to FRONT L/R in PURE DIRECT mode.

VH: Voltage High, RY101 on MAIN P.C.B.: Off

A2-1

DIRECT:VH

The analog input audio signal is output to FRONT L/R in PURE DIRECT mode.

VL: Voltage Low, RY101 on MAIN P.C.B.: On

A2-2

DIRECT:VL

36

RX-V673/HTR-6065/RX-A720

A3. HDMI AUDIO

This menu is used to check the route of audio signal input to HDMI IN/OUT jack.

* Before check using “A3-3. ARC 1” menu, be sure to connect a TV monitor equipped with Audio Return Channel

function to this unit in advance.

A3-1

HDMIAUTO

A3-2

INVALIDITEM

A3-3

ARC1

A3-4

INVALIDITEM

A3-5

INVALIDITEM

A3-1. HDMI AUTO

The audio signal input to selectedHDMI IN jack is output.

A3-2. INVALID ITEM

Not for service.

A3-3. ARC 1 (Audio Return Channel function)

The audio signal input to HDMI OUT jack is output.

A3-4. INVALID ITEM

Not for service.

A3-5. INVALID ITEM

Not for service.

RX-V673/HTR-6065/

RX-A720

37

RX-V673/HTR-6065/RX-A720

A4. SPEAKERS SET

This menu is used to check the speaker output.

A4-1

BI-AMP

A4-2

ZONE/TONE=MAX

A4-3

ZONE/TONE=MIN

A4-4

INVALIDITEM

A4-5

INVALIDITEM

A4-6

D-PARTYMODE

A4-1. BI-AMP

The FRONT L/R signal is distributed to SURROUND BACK L/R terminals.

A4-2. ZONE/TONE=MAX

The audio signal is output to FRONT L/R, CENTER and SURROUND L/R terminals with the tone control

“BASS +6 dB”, “TREBLE +6 dB”.

A4-3. ZONE/TONE=MIN

The audio signal is output to FRONT L/R, CENTER and SURROUND L/R terminals with the tone control

“BASS -6 dB”, “TREBLE -6 dB”.

A4-4. INVALID ITEM

Not for service.

A4-5. INVALID ITEM

Not for service.

A4-6. D-PARTY MODE

The FRONT L/R signal is distributed to ZONE2 L/R terminals.

ZONE2 volume: -3.5 dB

A4-7

FULLMUTE

RX-A720

A4-8

INVALIDITEM

RX-V673/HTR-6065/

A4-9

INVALIDITEM

A4-10

INVALIDITEM

A4-7. FULL MUTE

The audio signals are muted at all channels.

A4-8. INVALID ITEM

Not for service.

A4-9. INVALID ITEM

Not for service.

A4-10. INVALID ITEM

Not for service.

38

A5. MULTI CHANNEL INPUT

Not for service.

RX-V673/HTR-6065/RX-A720

A6. MIC CHECK

A6-1. MIC ROUTE CHECK

The audio signal input to the YPAO MIC jack is output to FRONT L and FRONT R channels via A/D-D/A.

A5-1

8ohmMULTICH

A5-2

6ohmMULTICH

A6-1

MICROUTE

RX-V673/HTR-6065/

RX-A720

39

RX-V673/HTR-6065/RX-A720

A7. MANUAL TEST

The test noise generated by built-in noise generator in DSP is output to the channels specified by the sub-menu.

Test noise Test tone

for SUBWOOFER

for other than SUBWOOFER

30 Hz to 80 Hz 50 Hz

pink noise sine wave

500 Hz to 2 kHz 1 kHz

pink noise sine wave

A7-1

TESTALL

A7-2

TESTFRNTL

A7-3

TESTCENTER

A7-4

TESTFRNTR

A7-5

TESTSURRR

A7-1. TEST ALL

The test noise is output to FRONT L/R, CENTER, SURROUND L/R, SURROUND BACK L/R and LFE 1

channels.

A7-2. TEST FRONT L

The test tone is output to FRONT L channel.

A7-3. TEST CENTER

The test tone is output to CENTER channel.

A7-4. TEST FRONT R

The test tone is output to FRONT R channel.

A7-5. TEST SURROUND R

The test tone is output to SURROUND R channel.

A7-6

TESTSBR

RX-A720

RX-V673/HTR-6065/

A7-7

TESTSBL

A7-8

TESTSURRL

A7-9

TESTFPL

40

A7-6. TEST SURROUND BACK R

The test tone is output to SURROUND BACK R channel.

A7-7. TEST SURROUND BACK L

The test tone is output to SURROUND BACK L channel.

A7-8. TEST SURROUND L

The test tone is output to SURROUND L channel.

A7-9. TEST FRONT PRESENCE L

The test tone is output to FRONT PRESENCE L channel.

RX-V673/HTR-6065/RX-A720

A7-10

TESTFPR

A7-11

INVALIDITEM

A7-12

INVALIDITEM

A7-13

TESTLFE1

A7-14

INVALIDITEM

A7-10. TEST FRONT PRESENCE R

The test tone is output to FRONT PRESENCE R channel.

A7-11. INVALID ITEM

Not for service.

A7-12. INVALID ITEM

Not for service.

A7-13. TEST LFE 1 (SUBWOOFER)

The test tone is output to LFE 1 channel.

A7-14. INVALID ITEM

Not for service.

RX-V673/HTR-6065/

RX-A720

41

RX-V673/HTR-6065/RX-A720

D1. FL CHECK

This menu is used to check operation of the FL display.

D1-1. INITIAL DISPLAY

D1-2. ALL SEGMENT OFF

FL display

RX-A720

RX-V673/HTR-6065/

D1-3. ALL SEGMENT ON

* After check, change to next menu at once.

D1-4. CHECK PATTERN 1

Example

Lighting on segments in lattice.

D1-5. CHECK PATTERN 2

NormalShort

42

Segment conditions of the FL tube is checked by turning ON and OFF all segments.

Next, a short between segments next to each other is checked by turning ON and OFF all segments alternately (in

lattice).

(In the above example, the segments in the second row from the top are shorted.)

Z1. ZONE TEST

This menu is used to check audio signal route to ZONE2 OUT jack.

RX-V673/HTR-6065/RX-A720

Z1-1

AV1

Z1-2

AV2

Z1-3

AV3

Z1-4

AV4

Z1-5

AV5

Z1-6

AV6

Z1-1. AV1

Not for service.

Z1-2. AV2

Not for service.

Z1-3. AV3

Not for service.

Z1-4. AV4

Not for service.

Z1-5. AV5

The audio signal input to AV5 jack is output to ZONE 2 OUT jack.

Z1-6. AV6

The audio signal input to AV6 jack is output to ZONE 2 OUT jack.

Z1-7

AUDIO1

Z1-8

AUDIO2

Z1-9

V-AUX

Z1-10

PHONO

Z1-7. AUDIO1

The audio signal input to AUDIO1 jack is output to ZONE 2 OUT jack.

Z1-8. AUDIO2

The audio signal input to AUDIO2 jack is output to ZONE 2 OUT jack.

Z1-9. V-AUX

Not for service.

Z1-10. PHONO

Not for service.

RX-V673/HTR-6065/

RX-A720

43

RX-V673/HTR-6065/RX-A720

U1. USB

This menu is used to check the audio signal route from USB storage device.

U1-1. USB FRONT 1 TRACK

The 1st music file stored in the USB storage device connected to the USB jack is reproduced.

* Copy 2 or more music files from PC to the root folder of the USB storage device in advance.

U1-1

USBF1TRACK

U1-2. USB FRONT 2 TRACK

The 2nd music file stored in the USB storage device connected to the USB jack is reproduced.

U1-2

USBF2TRACK

U1-3. USB_VBUS HIGH POWER

The output current (USB_VBUS) of USB jack is output at up to 2.1A/5V.

N1. NETWORK

This menu is used to check functions related to NETWORK.

Connect between LAN port of broadband router and NETWORK jack of this unit with a network cable.

* When the network condition varies while sub-menu is displayed (e.g., the network is deactivated once), the correct

RX-A720

RX-V673/HTR-6065/

N1-1. IP ADDRESS CHECK

U1-3

USBVBUSHPWR

result will not be displayed.

In that case, once turn off the power to this unit, then start up the self-diagnostic function again and select this

menu.

This menu is used to check that IP address can be obtained.

N1-1

IPADCHK:OK

OK: Connected (IP address obtained)

NG: No traffic / Disconnected

44

N1-2. MAC ADDRESS CHECK

This menu is used to check that MAC address is written.

N1-2

MACADCHK:OK

OK: Normal

NG: Unwritten

N1-3. LINE NOISE 100 MDI

Not for service.

N1-4. LINE NOISE 100 MDIX

Not for service.

N1-5. LINE NOISE 10 MDI

Not for service.

RX-V673/HTR-6065/RX-A720

N1-3

LNMDI100

N1-4

LNMDIX100

N1-5

LNMDI10

N1-6. LINE NOISE 10 MDIX

Not for service.

N1-6

LNMDIX10

N1-7. EXT TEST

Transmission/reception of the NETWORK jack is checked.

With the power turned off, short the pins of the NETWORK jack as shown in the figure below.

Start up the self-diagnostic function and select this menu.

Transmission/reception test is executed and its result is displayed.

Note: Be sure to return the shorted pins to their original condition after executing this test.

12345678

N1-7

EXTTEST:OK

OK: Normal

NG: Abnormal

--: Checking

RX-V673/HTR-6065/

RX-A720

NETWORK jack

N1-8. MAC ADDRESS

Written MAC address is displayed.

N1-8

00A0DExxxxxx

45

RX-V673/HTR-6065/RX-A720

C1. DIGITAL P.C.B. CHECK

This menu is used to check the communication and bus line connection between devices on DIGITAL P.C.B.

C1-1. ALL

The synthetic judgment result of sub-menu C1-2 to C1-8 is displayed.

C1-1

ALL:OK

OK: No error detected

NG: An error is detected

C1-2. BUS FLASH ROM

FLASH ROM (IC77)’s reading/writing are checked.

C1-2

BUSFROM:OK

OK: No error detected

NG: An error is detected

C1-3. BUS FPGA

C1-4. I2C

RX-A720

RX-V673/HTR-6065/

Communication and bus line connection between microprocessor (IC83) and FPGA (IC50) are checked.

C1-3

BUSFPGA:OK

OK: No error detected

NG: An error is detected

The I2C (Inter integrated circuit) bus line connection is checked.

C1-4

0-00---0--0

Error detection of Front HDMI equalizer (IC30)

Error detection of Video decoder (IC21)

0 : No error detected

1 : An error is detected

46

Error detection of HDMI transmitter (IC61)

Error detection of HDMI receiver (IC3)

Error detection of HDMI switcher 1 (IC1)

RX-V673/HTR-6065/RX-A720

C1-5. FPGA RAM

SDRAM (IC53)’s reading/writing are checked.

C1-5

FPGARAM:OK

OK: No error detected

NG: An error is detected

C1-6. BUS DIR1

Communication and bus line connection between microprocessor (IC83) and DIR1 (IC924) are checked.

C1-6

DIR1BUS:OK

OK: No error detected

NG: An error is detected

C1-7. BUS DSP1

Communication and bus line connection between microprocessor (IC83) and DSP1 (IC921) are checked.

C1-8. EEPROM

EEPROM (IC82)'s reading is checked.

C1-9. INVALID ITEM

Not for service.

C1-10. INVALID ITEM

Not for service.

C1-7

DSP1BUS:OK

C1-8

EEPROM:OK

C1-9

INVALIDITEM

OK: No error detected

NG: An error is detected

OK: No error detected

NG: An error is detected

RX-V673/HTR-6065/

RX-A720

C1-11. INVALID ITEM

Not for service.

C1-10

INVALIDITEM

C1-11

INVALIDITEM

47

RX-V673/HTR-6065/RX-A720

C2. NETWORK IC CHECK

This menu is used to check the communication and bus line connection between devices related to network.

C2-1. ALL

The synthetic judgment result of sub-menu C2-2 to C2-5 is displayed.

C2-1

ALL:OKExt.JIG

OK: No error detected

NG: An error is detected

--: Checking

C2-2. LINK CHECK

LAN cable connection is checked.

Connect between NETWORK jack of this unit and LAN port of broadband router with a network cable.

* When the network condition varies while sub-menu is displayed (e.g., the network is deactivated once), the

correct result will not be displayed. In that case, once turn off the power to this unit, then start up the selfdiagnostic function again and select this menu.

When test result using the “C2-2. LINK CHECK” menu is

NG, the sub-menu C2-2 is NG, “Ext. JIG” is displayed.

C2-3. PHY (Ethernet PHYceiver) TEST

RX-A720

RX-V673/HTR-6065/

C2-4. BUS RAM

C2-2

LINKCHK:OK

OK: Normal

NG: Disconnected

--: Checking

Communication and bus line connection between PHY (IC955) and NETWORK microprocessor (IC951) are

checked.

C2-3

PHYTEST:OK

OK: No error detected

NG: An error is detected

--: Checking

Communication and bus line connection between SDRAM (IC952) and NETWORK microprocessor (IC951) are

checked.

48

C2-4

RAMBUS:OK

OK: No error detected

NG: An error is detected

--: Checking

C2-5. APL (Apple) ID CHECK

Apple authentication IC (IC956) device ID is checked.

V1. ANALOG VIDEO CHECK

This menu is used to check the analog video signal route.

RX-V673/HTR-6065/RX-A720

C2-5

APLID:OK

OK: No error detected

NG: An error is detected

--: Checking

V1-1. ANALOG BYPASS

The video signal is converted and output as shown below.

V1-1

ANALOGBYPASS

ANALOG BYPASS

HDMI IN

Component In

Composite In

DIGITAL

IC3

HDMI

Receiver

VIDEO

IC303

Component

Selector

VIDEO

IC307

Composite

Selector

DIGITAL

IC21

VIDEO

Decoder

V1-2. INVALID ITEM

Not for service.

DIGITAL

IC64

FPGA

MUTE

VDEC_N_RST

Transmitter

VIDEO

IC302

Video Driver

VIDEO

IC301

Video Driver

DIGITAL

IC61

HDMI

HDMI OUT

Component Out

RX-V673/HTR-6065/

RX-A720

Composite Out

V1-3. INVALID ITEM

Not for service.

V1-2

INVALIDITEM

V1-3

INVALIDITEM

49

RX-V673/HTR-6065/RX-A720

V1-4. MUTE CHECK

The video signal is muted.

MUTE CHECK

HDMI IN

Component In

DIGITAL

IC3

HDMI

Receiver

VIDEO

IC303

Component

Selector

V1-4

MUTECHECK

DIGITAL

IC21

VIDEO

Decoder

DIGITAL

IC64

FPGA

MUTE

VDEC_N_RST

MUTE

CPNT_N_VMT

Transmitter

VIDEO

IC302

Video Driver

DIGITAL

IC61

HDMI

HDMI OUT

Component Out

V1-5. TEST PATTERN

V1-6. VIDEO INFORMATION

RX-A720

RX-V673/HTR-6065/

VIDEO

IC307

Composite

Composite In

Selector

Not for service.

V1-5

TESTPATTERN

The information of input analog video signals is displayed.

V1-6

VIDIN:480i60

MUTE

VID_N_MMT

VIDEO

IC301

Video Driver

Composite Out

50

V2. DIGITAL VIDEO CHECK

This menu is used to check the digital video signal route.

V2-1. LOOPBACK TEST 1

Execute the test for all HDMI IN jacks by repeating the procedure below.

1. Select sub-menu other than V2-1.

2. Connect between any of the HDMI IN jacks and HDMI OUT jack with an HDMI cable.

3. Select V2-1. The test result is displayed in a few seconds.

CB5

CB4

CB30

HDMI IN

Front

HDMI

IN5

HDMI

IN4

CB3

HDMI

IN3

V2-1

TEST1:OK

HDMI Cable for Loopback

CB2

HDMI

IN2

CB1

HDMI

IN1

RX-V673/HTR-6065/RX-A720

OK: No error detected

NG: An error is detected

--: Checking

CB61

HDMI

OUT1

IC30

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

Y,CbCr

Y,C

CVBS

IC2

HDMI SWITCHER 2

Sii9589-3

IC21

VIDEO DECODER

ADV7180BSTZ

IC3

HDMI RECEIVER

ADV7619

IC1

HDMI SWITCHER 1

Sii9589-3

IC53

128Mbit

SDRAM

IC50

FPGA

EP4CE15F23C6N

IC61

HDMI

TRANSMITTER

Sii9136-3

RX-V673/HTR-6065/

RX-A720

51

RX-V673/HTR-6065/RX-A720

V2-2. LOOPBACK TEST 2

Execute the test for all HDMI IN jacks by repeating the procedure below.

1. Select sub-menu other than V2-2.

2. Connect between any of the HDMI IN jacks and HDMI OUT jack with an HDMI cable.

3. Select the input source corresponding to the connected HDMI IN jack by using “INPUT

keys (RX-V673/HTR-6065) / “INPUT” knob (RX-A720).

4. Select V2-2. The test result is displayed in a few seconds.

Select the input source Result

HDMI1 V-AUX

” and “INPUT ”

V2-2

TEST2:OK

OK: No error detected

NG: An error is detected

--: Checking

HDMI Cable for Loopback

RX-A720

RX-V673/HTR-6065/

CB30

HDMI IN

Front

IC30

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

Y,CbCr

Y,C

CVBS

IC2

HDMI SWITCHER 2

Sii9589-3

IC21

VIDEO DECODER

ADV7180BSTZ

CB5

HDMI

IN5

IC3

HDMI RECEIVER

ADV7619

CB4

HDMI

CB3

HDMI

IN4

IN3

IC1

HDMI SWITCHER 1

Sii9589-3

CB2

HDMI

IN2

CB1

HDMI

IN1

EP4CE15F23C6N

IC53

128Mbit

SDRAM

IC50

FPGA

CB61

HDMI

OUT1

IC61

HDMI

TRANSMITTER

Sii9136-3

4K test pattern 3840x2160/24Hz

52

V2-3. LOOPBACK TEST 3

Execute the test for all HDMI IN jacks by repeating the procedure below.

1. Select sub-menu other than V2-3.

2. Connect between any of the HDMI IN jacks and HDMI OUT jack with an HDMI cable.

3. Select the input source corresponding to the connected HDMI IN jack by using “INPUT

keys (RX-V673/HTR-6065) / “INPUT” knob (RX-A720).

4. Select V2-3. The test result is displayed in a few seconds.

Select the input source Result

HDMI1 V-AUX

RX-V673/HTR-6065/RX-A720

” and “INPUT ”

V2-3

TEST3:OK

OK: No error detected

NG: An error is detected

--: Checking

HDMI Cable for Loopback

CB30

HDMI IN

Front

IC30

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

HDMI SWITCHER 2

Y,CbCr

Y,C

CVBS

VIDEO DECODER

V2-4. INVALID ITEM

Not for service.

IC2

Sii9589-3

IC21

ADV7180BSTZ

CB5

HDMI

IN5

IC3

HDMI RECEIVER

ADV7619

CB4

CB3

HDMI

HDMI

IN4

IN3

IC1

HDMI SWITCHER 1

Sii9589-3

CB2

HDMI

IN2

CB1

HDMI

IN1

EP4CE15F23C6N

IC53

128Mbit

SDRAM

IC50

FPGA

1080/60Hz 12bit

CB61

HDMI

OUT1

IC61

HDMI

TRANSMITTER

Sii9136-3

RX-V673/HTR-6065/

RX-A720

V2-5. INVALID ITEM

Not for service.

V2-6. INVALID ITEM

Not for service.

V2-4

INVALIDITEM

V2-5

INVALIDITEM

V2-6

INVALIDITEM

53

RX-V673/HTR-6065/RX-A720

V2-7. HDMI REPEAT

The video/audio signals input to HDMI IN jack are output to HDMI OUT jack.

V2-7

HDMIREPEAT**

The Deep Color video signals is input, “30” bit or

“36” bit is displayed.

CB30

HDMI IN

Front

IC30

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

Y,CbCr

Y,C

CVBS

HDMI output

HDMI

IC2

HDMI SWITCHER 2

Sii9589-3

IC21

VIDEO DECODER

ADV7180BSTZ

BD/DVD player

CB5

HDMI

IN5

IC3

HDMI RECEIVER

ADV7619

CB4

HDMI

CB3

HDMI

IN4

IN3

IC1

HDMI SWITCHER 1

Sii9589-3

CB2

HDMI

IN2

CB1

HDMI

IN1

EP4CE15F23C6N

IC53

128Mbit

SDRAM

IC50

FPGA

HDMI

TV

CB61

HDMI

OUT1

IC61

HDMI

TRANSMITTER

Sii9136-3

V2-8. DIGITAL CVBS

RX-A720

RX-V673/HTR-6065/

Video output

VIDEO

BD/DVD player

The video (CVBS) signal is converted and output as shown below.

V2-8

DIGITALCVBS

CB5

CB4

CB3

CB2

IN2

CB1

HDMI

IN1

CB30

HDMI IN

Front

IC30

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

Y,CbCr

Y,C

CVBS

IC2

HDMI SWITCHER 2

Sii9589-3

IC21

VIDEO DECODER

ADV7180BSTZ

HDMI

IN5

IC3

HDMI RECEIVER

ADV7619

HDMI

HDMI

IN4

IN3

IC1

HDMI SWITCHER 1

Sii9589-3

HDMI

IC53

128Mbit

SDRAM

IC50

FPGA

EP4CE15F23C6N

HDMI

TV

CB61

HDMI

OUT1

IC61

HDMI

TRANSMITTER

Sii9136-3

54

V2-9. INVALID ITEM

Not for service.

V2-9

INVALIDITEM

V2-10. DIGITAL COMPONENT

The component video (Y, Cb, Cr) signal is converted and output as shown below.

V2-10

DIGITALCmp

RX-V673/HTR-6065/RX-A720

TV

HDMI

HDMI IN

Front-HDMI-Board

HDMI EQUALIZER

TMDS261

Component video output

COMPONENT

BD/DVD player

CB30

Front

IC30

Y,CbCr

Y,C

CVBS