Vishay VS-ST700CL Series Data Sheet

www.vishay.com

TO-200AC (B-PUK)

PRODUCT SUMMARY

Package TO-200AC (B-PUK)

Diode variation Single SCR

I

T(AV)

V

DRM/VRRM

V

TM

I

GT

T

J

1200 V, 1600 V, 1800 V, 2000 V

Phase Control Thyristors

(Hockey PUK Version), 910 A

FEATURES

• Center amplifying gate

• Metal case with ceramic insulator

• International standard case TO-200AC (B-PUK)

• Designed and qualified for industrial level

• Material categorization: For definitions of compliance

please see www.vishay.com/doc?99912

TYPICAL APPLICATIONS

• DC motor controls

• Controlled DC power supplies

• AC controllers

910 A

1.80 V

100 mA

-40 °C to 125 °C

VS-ST700CL Series

Vishay Semiconductors

MAJOR RATINGS AND CHARACTERISTICS

PARAMETER TEST CONDITIONS VALUES UNITS

I

T(AV)

I

T(RMS)

I

TSM

2

t

I

V

DRM/VRRM

t

q

T

J

T

hs

T

hs

50 Hz 15 700

60 Hz 16 400

50 Hz 1232

60 Hz 1125

Typical 150 μs

910 A

55 °C

1857 A

25 °C

A

kA2s

1200 to 2000 V

-40 to 125 °C

VOLTAGE RATINGS

TYPE

NUMBER

VS-ST700CL

V

VOLTAGE

CODE

12 1200 1300

16 1600 1700

18 1800 1900

20 2000 2100

DRM/VRRM

PEAK AND OFF-STATE VOLTAGE

, MAXIMUM REPETITIVE

NON-REPETITIVE PEAK VOLTAGE

V

V

RSM

, MAXIMUM

V

I

DRM/IRRM

T

= TJ MAXIMUM

J

MAXIMUM AT

mA

80

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

1

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Document Number: 94413

VS-ST700CL Series

www.vishay.com

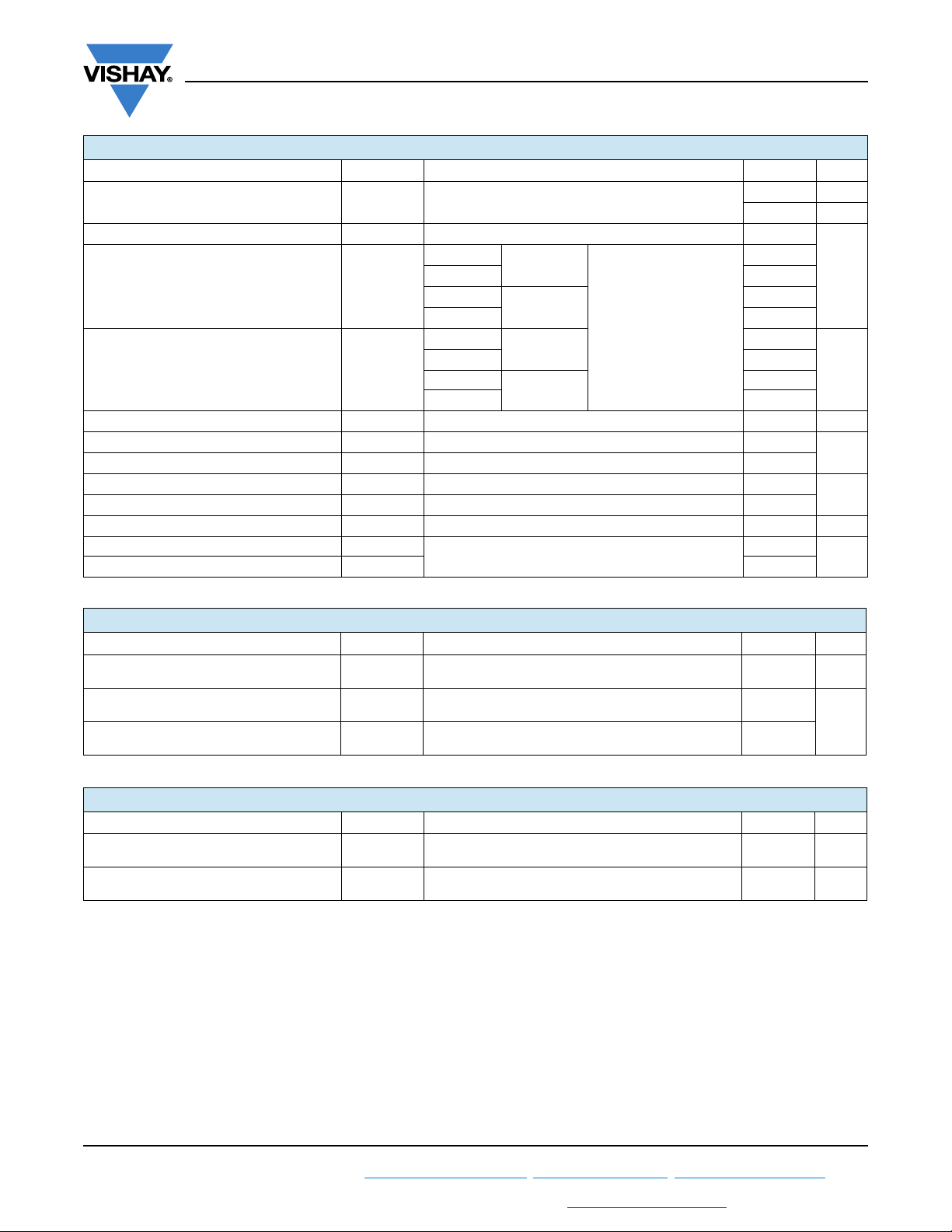

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum average on-state current

at heatsink temperature

Maximum RMS on-state current I

T(RMS)

Maximum peak, one-cycle

non-repetitive surge current

Maximum I

Maximum I

2

t for fusing I2t

2

√t for fusing I2√t t = 0.1 to 10 ms, no voltage reapplied 12 321 kA2√s

Low level value of threshold voltage V

High level value of threshold voltage V

Low level value of on-state slope resistance r

High level value of on-state slope resistance r

Maximum on-state voltage V

Maximum holding current I

Typical latching current I

I

T(AV)

I

TSM

T(TO)1

T(TO)2

t1

t2

TM

H

L

180° conduction, half sine wave

double side (single side) cooled

DC at 25 °C heatsink temperature double side cooled 1857

t = 10 ms

t = 8.3 ms 16 400

t = 10 ms

t = 8.3 ms 13 800

t = 10 ms

t = 8.3 ms 1125

t = 10 ms

t = 8.3 ms 795

(16.7 % x π x I

(I > π x I

(16.7 % x π x I

(I > π x I

No voltage

reapplied

100 % V

RRM

reapplied

No voltage

reapplied

100 % V

RRM

reapplied

< I < π x I

T(AV)

), TJ = TJ maximum 1.13

T(AV)

< I < π x I

T(AV)

), TJ = TJ maximum 0.35

T(AV)

Ipk = 2000 A, TJ = TJ maximum, tp = 10 ms sine pulse 1.80 V

TJ = 25 °C, anode supply 12 V resistive load

Vishay Semiconductors

Sinusoidal half wave,

initial T

= TJ maximum

J

), TJ = TJ maximum 1.00

T(AV)

), TJ = TJ maximum 0.40

T(AV)

910 (355) A

55 (85) °C

15 700

13 200

1232

871

kA2s

mΩ

600

1000

mA

A

V

SWITCHING

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum non-repetitive rate of rise

of turned-on current

Typical delay time t

Typical turn-off time t

dI/dt

d

q

Gate drive 20 V, 20 Ω, t

T

= TJ maximum, anode voltage ≤ 80 % V

J

Gate current 1 A, dIg/dt = 1 A/μs

V

= 0.67 % V

d

DRM

ITM = 750 A, TJ = TJ maximum, dI/dt = 60 A/μs,

V

= 50 V, dV/dt = 20 V/μs, gate 0 V 100 Ω, tp = 500 μs

R

≤ 1 μs

r

, TJ = 25 °C

DRM

1000 A/μs

1.0

μs

150

BLOCKING

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum critical rate of rise of

off-state voltage

Maximum peak reverse and

off-state leakage current

dV/dt T

I

,

RRM

I

DRM

= TJ maximum linear to 80 % rated V

J

TJ = TJ maximum, rated V

DRM/VRRM

DRM

500 V/μs

applied 50 mA

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

2

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

Document Number: 94413

VS-ST700CL Series

www.vishay.com

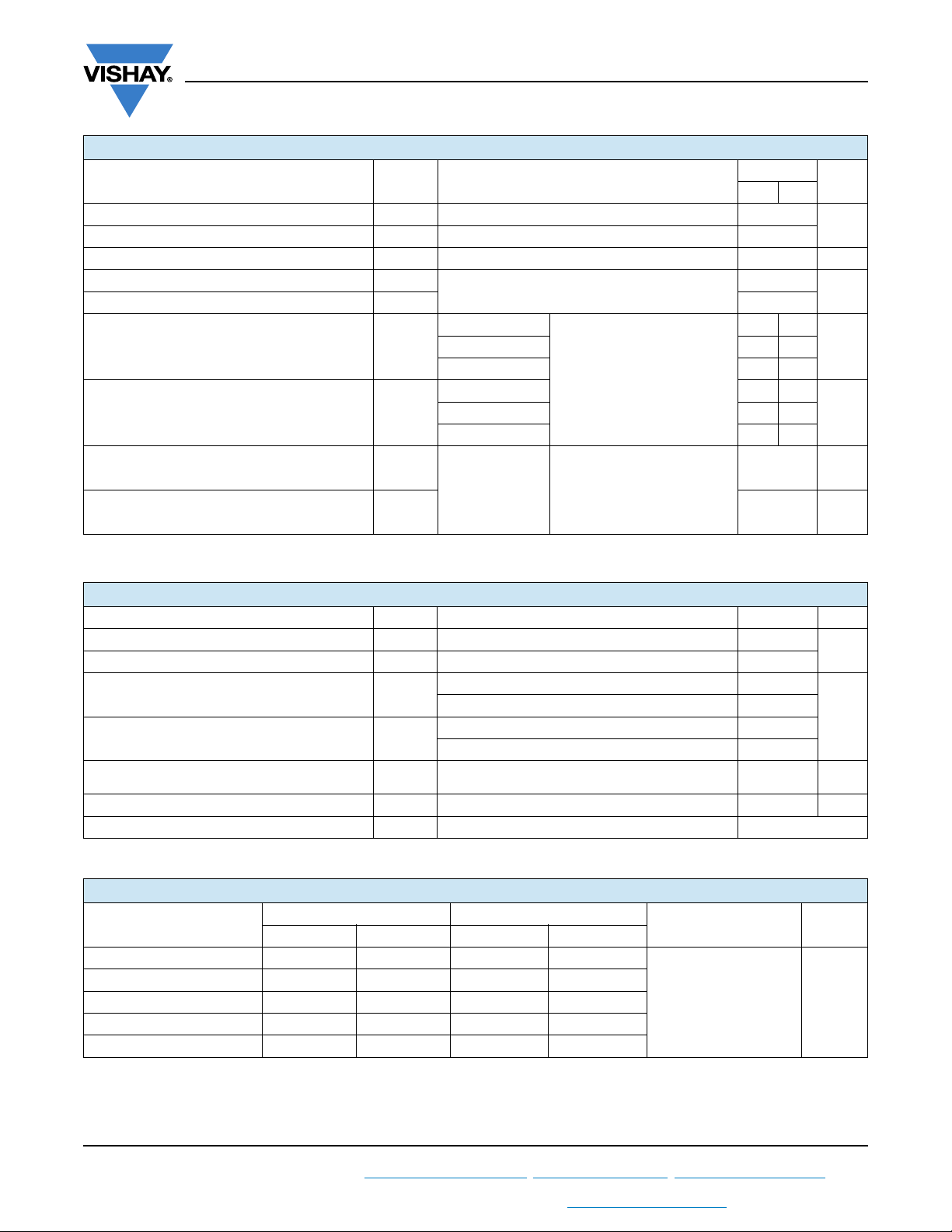

TRIGGERING

PARAMETER SYMBOL TEST CONDITIONS

Maximum peak gate power P

Maximum average gate power P

Maximum peak positive gate current I

Maximum peak positive gate voltage + V

Maximum peak negative gate voltage - V

DC gate current required to trigger I

DC gate voltage required to trigger V

DC gate current not to trigger I

DC gate voltage not to trigger V

GM

G(AV)

GM

GT

GD

GD

TJ = TJ maximum, tp ≤ 5 ms 10.0

TJ = TJ maximum, f = 50 Hz, d% = 50 2.0

TJ = TJ maximum, tp ≤ 5 ms 3.0 A

GM

TJ = TJ maximum, tp ≤ 5 ms

GM

TJ = -40 °C

= 25 °C 100 200

J

= 125 °C 50 -

T

J

TJ = -40 °C 2.5 -

GT

= 25 °C 1.8 3.0

J

T

= 125 °C 1.1 -

J

Maximum required gate

trigger/

current/voltage are the lowest

value which will trigger all units

12 V anode to cathode applied

Maximum gate current/voltage

not to trigger is the maximum

TJ = TJ maximum

value which will not trigger any

unit with rated V

cathode applied

Vishay Semiconductors

anode to

DRM

VALUES

Typ. Max.

20

5.0

200 -

10 mA

0.25 V

UNITS

W

V

mAT

VT

THERMAL AND MECHANICAL SPECIFICATIONS

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum operating junction temperature range T

Maximum storage temperature range T

Maximum thermal resistance, junction to heatsink R

Maximum thermal resistance, case to heatsink R

J

Stg

thJ-hs

thC-hs

DC operation single side cooled 0.073

DC operation double side cooled 0.031

DC operation single side cooled 0.011

DC operation double side cooled 0.006

Mounting force, ± 10 %

Approximate weight 255 g

Case style See dimensions - link at the end of datasheet TO-200AC (B-PUK)

ΔR

CONDUCTION ANGLE

CONDUCTION

thJ-hs

SINUSOIDAL CONDUCTION RECTANGULAR CONDUCTION

SINGLE SIDE DOUBLE SIDE SINGLE SIDE DOUBLE SIDE

TEST CONDITIONS UNITS

180° 0.009 0.009 0.006 0.006

120° 0.011 0.011 0.011 0.011

T

90° 0.014 0.014 0.015 0.015

= TJ maximum K/W

J

60° 0.020 0.020 0.021 0.021

30° 0.036 0.036 0.036 0.036

Note

• The table above shows the increment of thermal resistance R

when devices operate at different conduction angles than DC

thJ-hs

-40 to 125

-40 to 150

14 700

(1500)

°C

K/W

N

(kg)

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

3

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

Document Number: 94413

Loading...

Loading...