TOSHIBA Original CMOS 16-Bit Microcontroller

TLCS-900/L1 Series

TMP91FY42FG

Semiconductor Company

Preface

Thank you very much for making use of Toshiba microcomputer LSIs.

Before use this LSI, refer the section, “Points of Note and Restrictions”.

Especially, take care below cautions.

1. Outline and Features

TMP91FY42F is a high-speed 16-bit microcontroller designed for the control of various mid- to

large-scale equipment.

TMP91FY42FG comes in a 100-pin flat package.

Listed below are the features.

(1) High-speed 16-bit CPU (900/L1 CPU)

• Instruction mnemonics are upward-compatible with TLCS-90/900

• General-purpose registers and register banks

• 16 Mbytes of linear address space

• 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

• Micro DMA: 4-channels (593 ns/2 bytes at 27 MHz)

(2) Minimum instruction execution time: 148 ns (at 27 MHz)

TMP91FY42

CMOS 16-Bit Microcontrollers

TMP91FY42FG

RESTRICTIONS ON PRODUCT USE

• The information contained herein is subject to change without notice. 021023_D

• TOSHIBA is continually working to improve the quality and reliabil ity of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity an d vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as

set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and

conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability

Handbook” etc.

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer,

personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These

TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high

quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury

(“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship

instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical

instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall

be made at the customer’s own risk.

• The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106_Q

021023_A

021023_B

060925EBP

• The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under an y patent or patent rights of TOSHIBA or others.

021023_C

• The products described in this document are subject to foreign exchange and foreign trade control laws. 060925_E

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter

entitled Quality and Reliability Assurance/Handling Precautions. 030619_S

This product uses the Super Flash® technology under the license of Silicon Storage Technology,Inc.

Super Flash® is a registered trademark of Silicon Storage Technology,Inc.

91FY42-1 2006-11-08

TMP91FY42

(3) Built-in RAM: 16 Kbytes

Built-in ROM: 256 Kbytes Flash memory

4 Kbytes mask ROM (used for booting)

(4) External memory expansion

• Expandable up to 16 Mbytes (shared program/data area)

• Can simultaneously support 8-/16-bit width external data bus

… Dynamic data bus sizing

(5) 8-bit timers: 8 channels

(6) 16-bit timer/event counter: 2 channels

(7) General-purpose serial interface: 2 channels

• UART/ Synchronous mode: 2 channels

• IrDA ver1.0 (115.2 kbps) supported: 1 channel

(8) Serial bus interface: 1 channel

2

C bus mode/clock synchronous Select mode

• I

(9) 10-bit AD converter (built-in sample hold circuit) : 8 channels

(10) Watchdog timer

(11) Special timer for clock

(12) Chip Select/Wait controller: 4 channels

(13) Interrupts: 45 interrupts

• 9 CPU interrupts: Software interrupt instruction and illegal instruction

• 26 internal interrupts:

Seven selectable priority levels

• 10 external interrupts:

(14) Input/Output ports: 81 pins

(15) Standby function

Three HALT modes: IDLE2 (programmable), IDLE1, STOP

(16) Clock controller

• Clock Gear function: Select a high-frequency clock (fc to fc/16)

• Special timer for CLOCK (fs = 32.768 kHz)

(17) Operating voltage

• V

• V

= 2.7 V to 3.6 V (fc max = 27 MHz, flash memory read operation)

CC

= 3.0 V to 3.6 V (fc max = 27 MHz, flash memory erase/program operations)

CC

(18) Package

• 100-pin LQFP: LQFP100-P-1414-0.50F

Note: This LSI does not build in Clock doubler (DFM.)

91FY42-2 2006-11-08

(

(

(

TMP91FY42

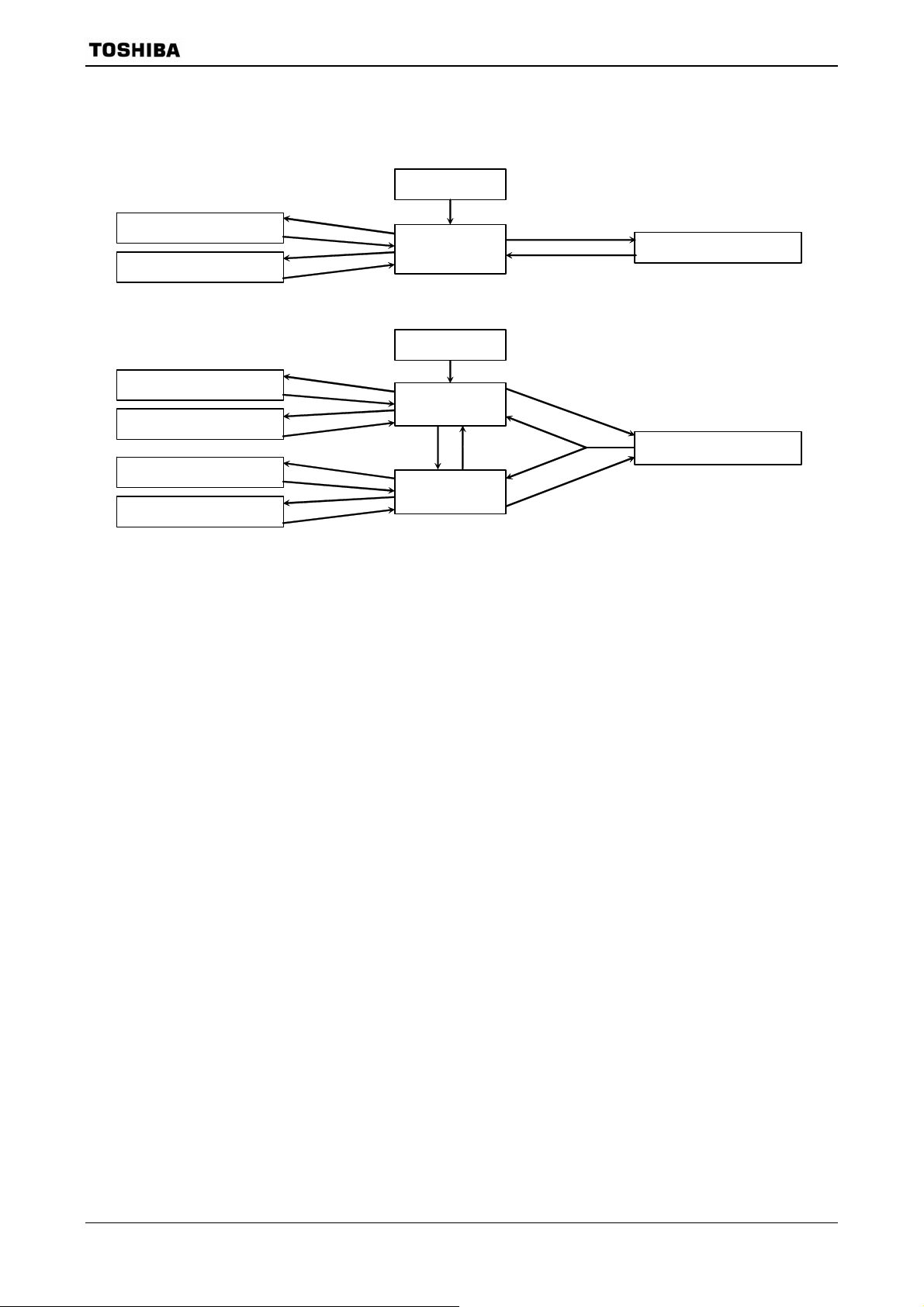

ADTRG (P53)

(P50 to P57)

AVCC, AVSS

VREFH, VREFL

RXD0 (P91)

SCLK0/

RXD1 (P94)

SCLK1/

CTS1 (P95)

SO/SDA (P61)

SI / SCL (P62)

TA0IN (P70)

TA1OUT (P71)

TA3OUT (P72)

TA4IN (P73)

TA5OUT (P74)

TA7OUT (P75)

AN0 to AN7

TXD0 (P90)

0CTS (P92)

TXD1 (P93)

SCK (P60)

10-Bit 8CH

AD

Converter

SIO/UART/IrDA

(SIO0)

SIO/UART

(SIO1)

Serial Bus

Interface

SBI)

8-Bit Timer

(TMRA0)

8-Bit Timer

(TMRA1)

8-Bit Timer

(TMRA2)

8-Bit Timer

(TMRA3)

8-Bit Timer

(TMRA4)

8-Bit Timer

(TMRA5)

8-Bit Timer

(TMRA6)

8-Bit Timer

(TMRA7)

CPU (TLCS-900/L1)

XWA

XBC

XDE

XHL

XIX

XIY

XIZ

XSP

16-KB RAM

W A

B C

D E

H L

IX

IY

IZ

SP

32 bits

PC

Watchdog

Timer (WDT)

Special timer

for CLOCK

256-KB FLASH

2

PROM

E

4-KB BOOT ROM

FSR

H-OSC

Clock Gear

Clock doubler

L-OSC

Port 0

Port 1

Port 2

Port 3

Port 6

Port A

CS/WAIT

Controller

(4-BLOCK)

Interrupt

Controller

16-Bit Timer

(TMRB0)

16-Bit Timer

(TMRB1)

DVCC [3]

DVSS [3]

X1

X2

EMU0

EMU1

XT1 (P96)

XT2 (P97)

RESET

AM0

AM1

ALE

(P00 to P07)

AD0 to AD7

(P10 to P17)

AD8/A8 to AD15/A15

(P20 to P27)

A0/A16 to A7/A23

RD (P30)

WR (P31)

HWR (P32)

BUSRQ (P34)

BUSAK (P35)

WR/ (P36)

BOOT

SCOUT(P64), P65, P66

PA4 to PA7

(P40 to P43)

CS0 to CS3

WAIT

NMI

INT0 (P64)

INT1 to INT4

(PA0 to PA3)

TB0IN0/INT5 (P80)

TB0IN1/INT6 (P81)

TB0OUT0 (P82)

TB0OUT1 (P83)

TB1IN0/INT7 (P84)

TB1IN1/INT8 (P85)

TB1OUT0 (P86)

TB1OUT1 (P87)

P37)

P33)

( ): Initial function after reset

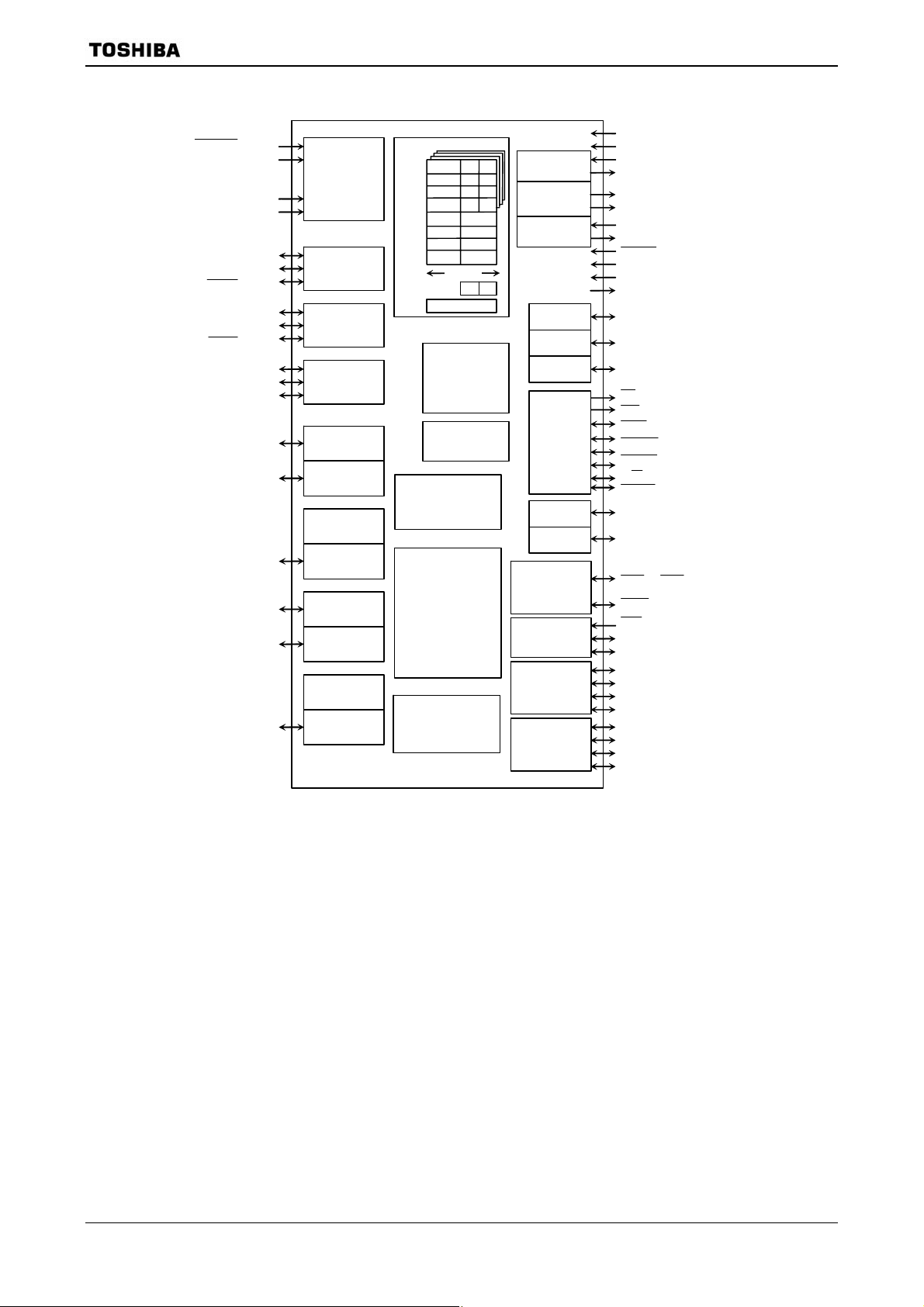

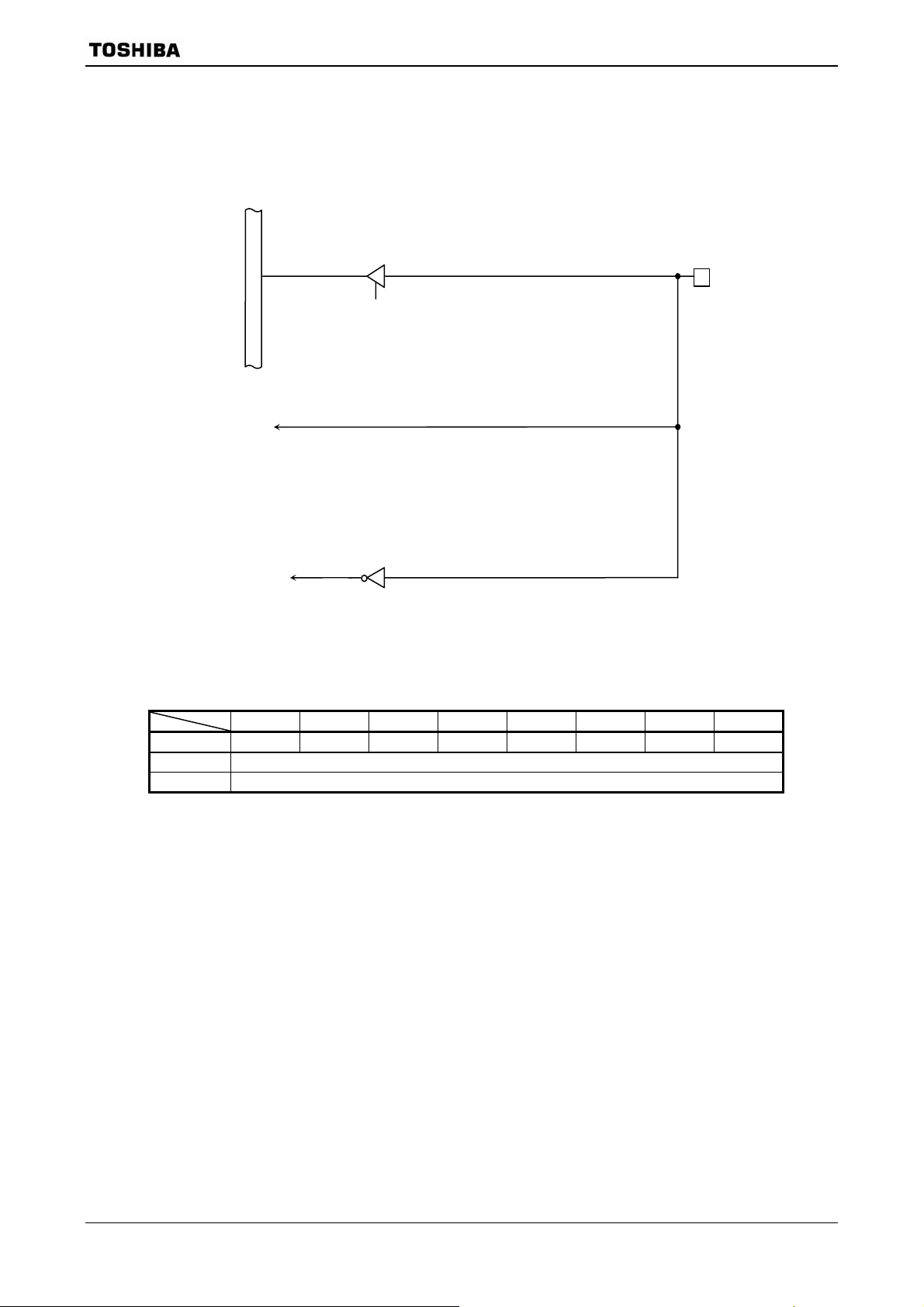

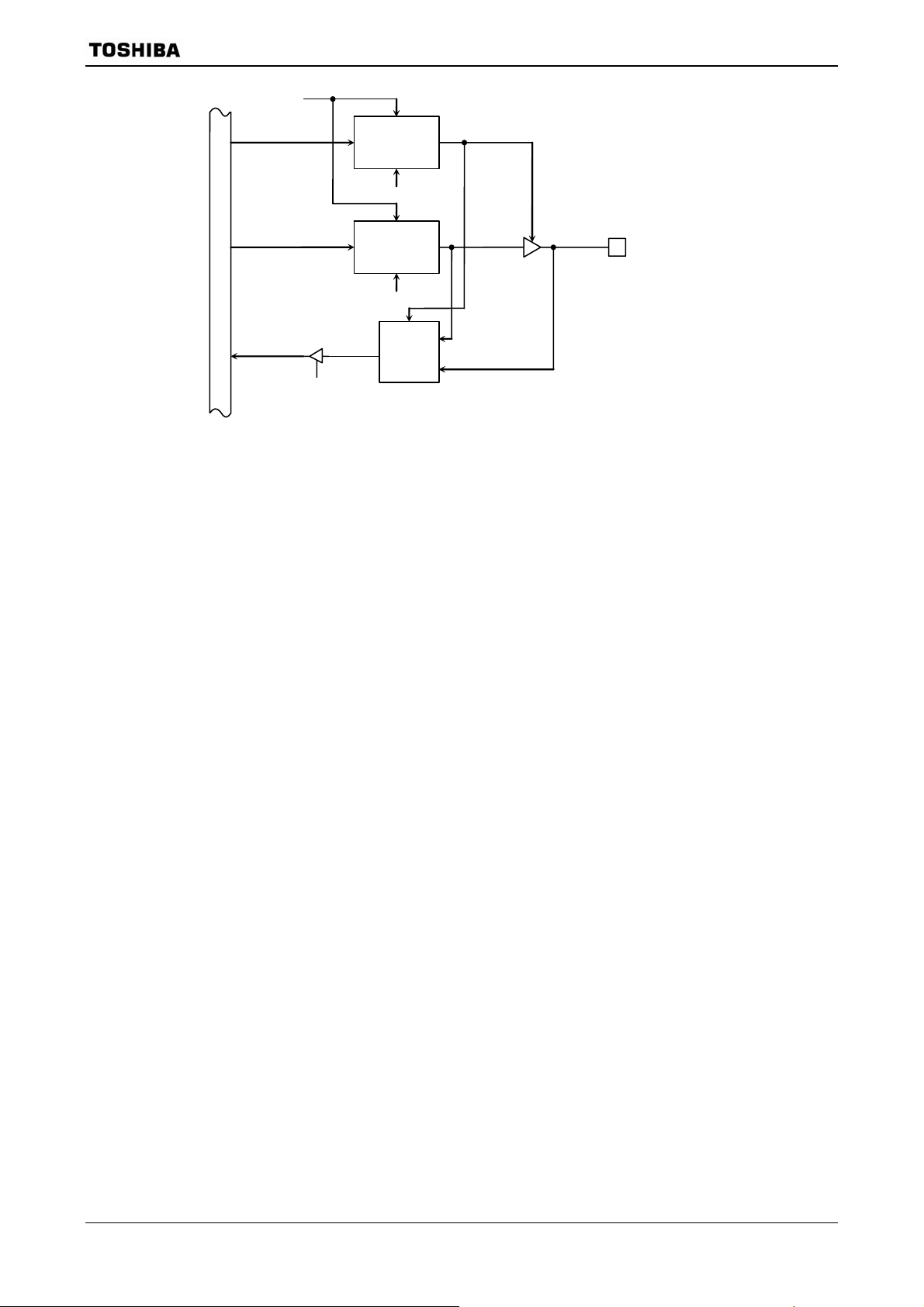

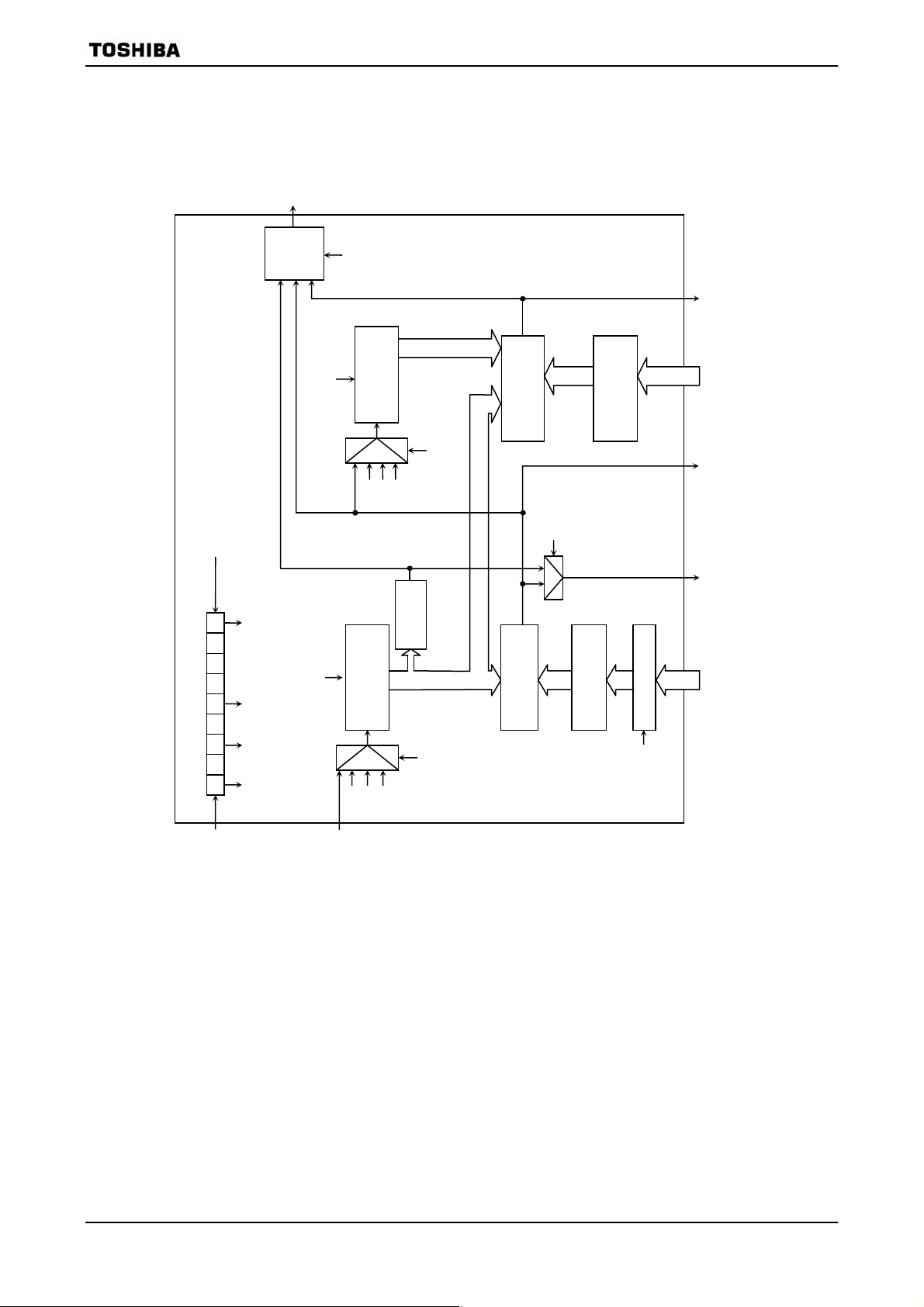

Figure 1.1 TMP91FY42F Block Diagram

91FY42-3 2006-11-08

2. Pin Assignment and Pin Functions

The assignment of input/output pins for the TMP91FY42, their names and functions are as

follows:

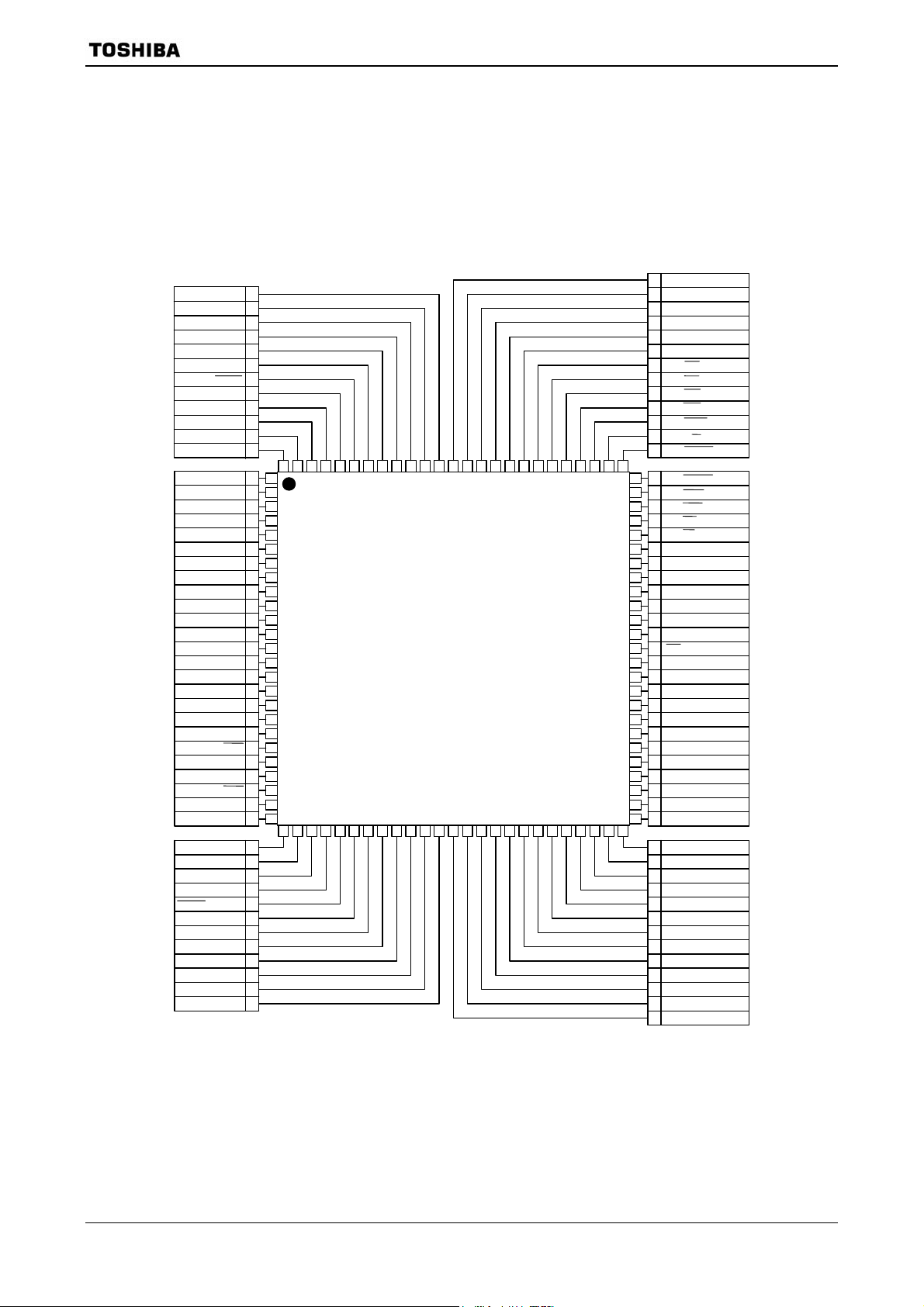

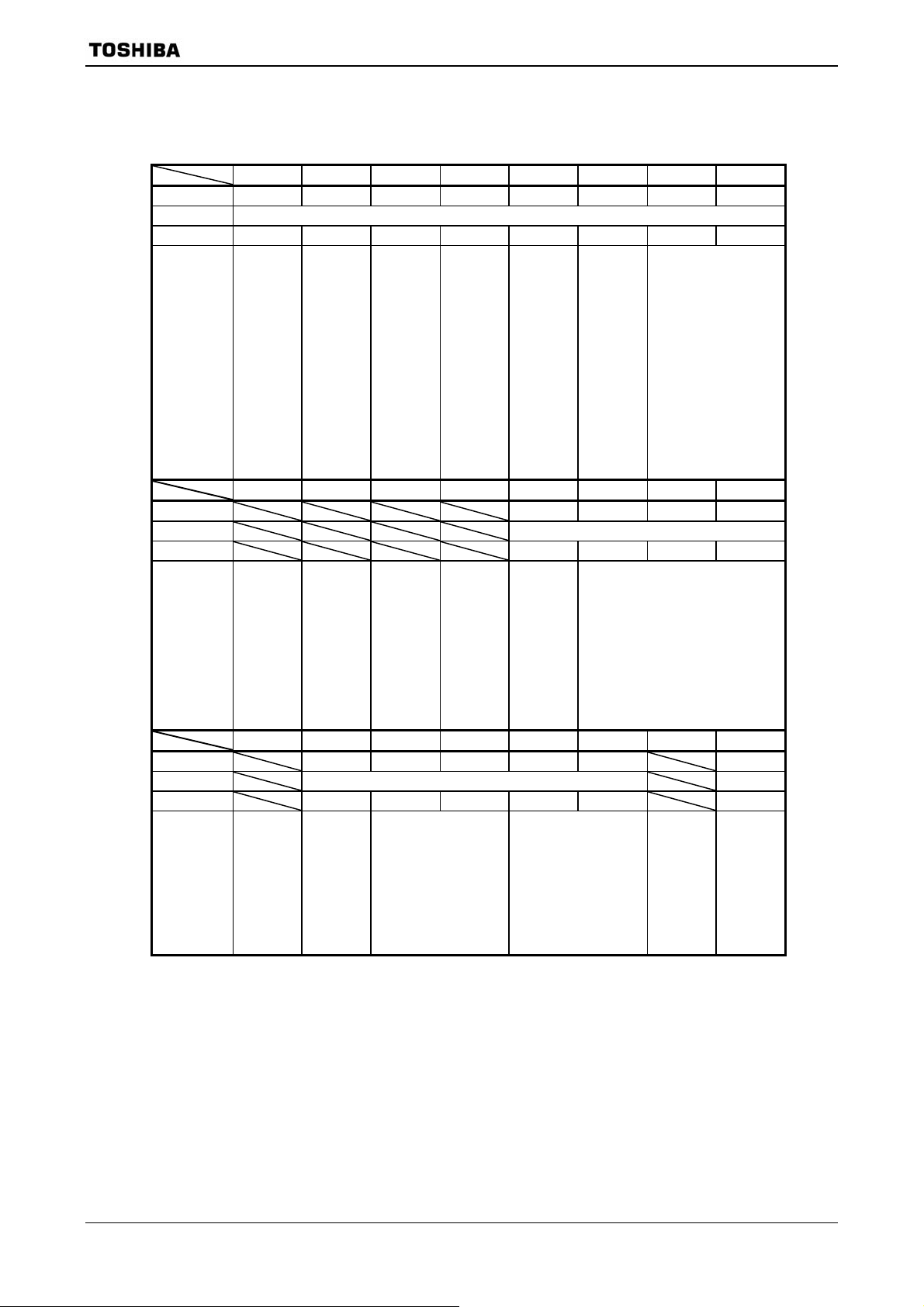

2.1 Pin Assignment Diagram

Figure 2.1.1 shows the pin assignment of the TMP91FY42.

DVCC 89

P66 90

DVSS 91

P50/AN0 92

P51/AN1 93

P52/AN2 94

P53/AN3/ADTRG 95

P54/AN4 96

P55/AN5 97

P56/AN6 98

P57/AN7 99

VREFH 100

VREFL 1

AVSS 2

AVCC 3

P70/TA0IN 4

P71/TA1OUT 5

P72/TA3OUT 6

P73/TA4IN 7

P74/TA5OUT 8

P75/TA7OUT 9

P80/TB0IN0/INT5 10

P81/TB0IN1/INT6 11

P82/TB0OUT0 12

P83/TB0OUT1 13

P84/TB1IN0/INT7 14

P85/TB1IN1/INT8 15

P86/TB1OUT0 16

P87/TB1OUT1 17

P90/TXD0 18

P91/RXD0 19

P92/SCLK0/CTS0 20

P93/TXD1 21

P94/RXD1 22

P95/SCLK1/CTS1 23

AM0 24

DVCC 25

X2 26

DVSS 27

X1 28

AM1 29

RESET 30

P96/XT1 31

P97/XT2 32

EMU0 33

EMU1 34

PA0/INT1 35

PA1/INT2 36

PA2/INT3 37

Top view

QFP100

TMP91FY42

88 P65

87 P64/SCOUT

86 P63/INT0

85 P62/SI/SCL

84 P61/SO/SDA

83 P60/SCK

82 P43/CS3

81 P42/CS2

80 P41/CS1

79 P40/CS0

78 P37/BOOT

77 P36/R/W

76 P35/BUSAK

75 P34/BUSRQ

74 P33/WAIT

73 P32/HWR

72 P31/WR

71 P30/RD

70 P27/A7/A23

69 P26/A6/A22

68 P25/A5/A21

67 P24/A4/A20

66 P23/A3/A19

65 P22/A2/A18

64 DVCC

63 NMI

62 DVSS

61 P21/A1/A17

60 P20/A0/A16

59 P17/AD15/A15

58 P16/AD14/A14

57 P15/AD13/A13

56 P14/AD12/A12

55 P13/AD11/A11

54 P12/AD10/A10

53 P11/AD9/A9

52 P10/AD8/A8

51 P07/AD7

50 P06/AD6

49 P05/AD5

48 P04/AD4

47 P03/AD3

46 P02/AD2

45 P01/AD1

44 P00/AD0

43 ALE

42 PA7

41 PA6

40 PA5

39 PA4

38 PA3/INT4

Figure 2.1.1 Pin assignment diagram (100-pin LQFP)

91FY42-4 2006-11-08

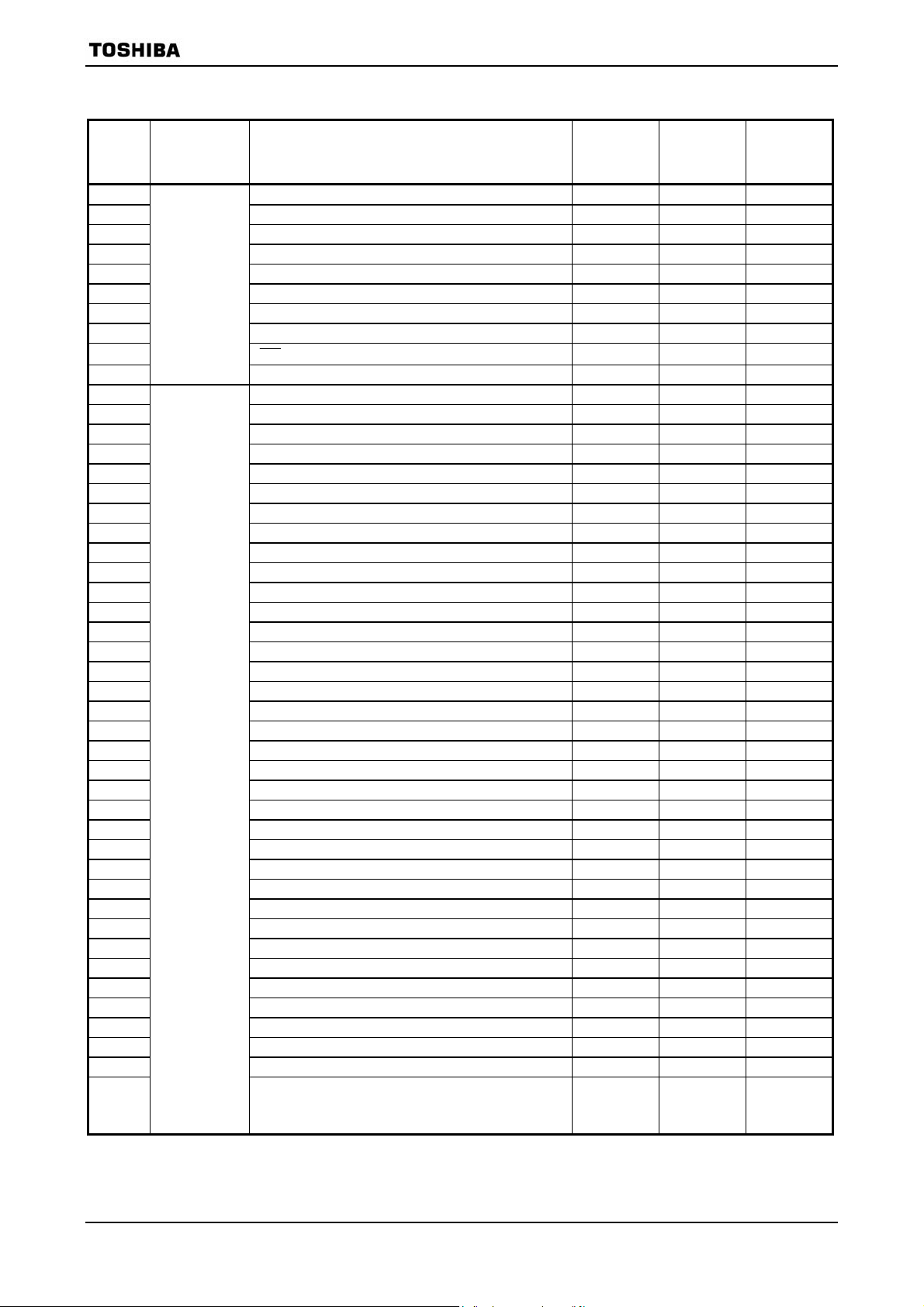

TMP91FY42

2.2 Pin Names and Functions

The names of the input/output pins and their functions are described below.

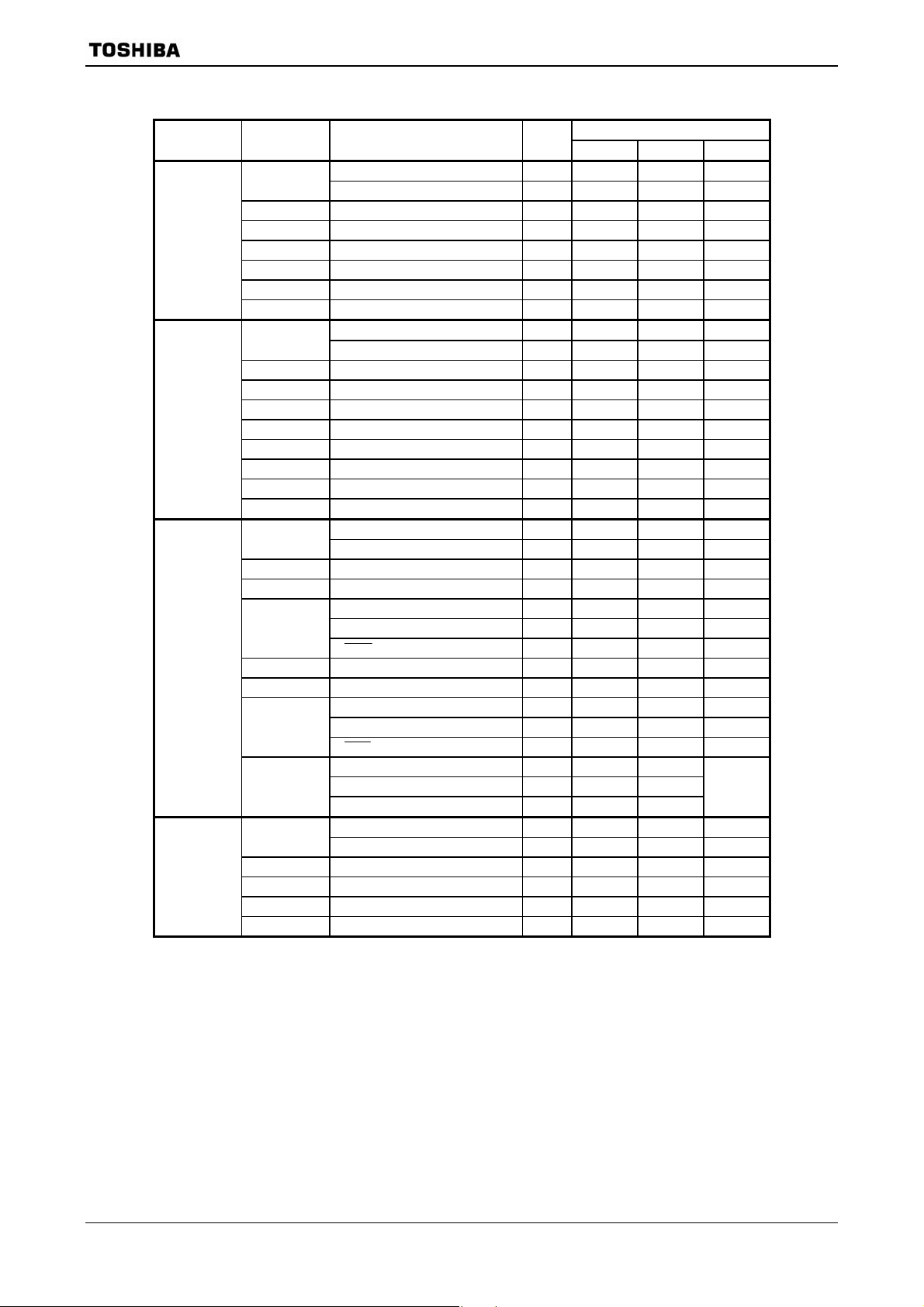

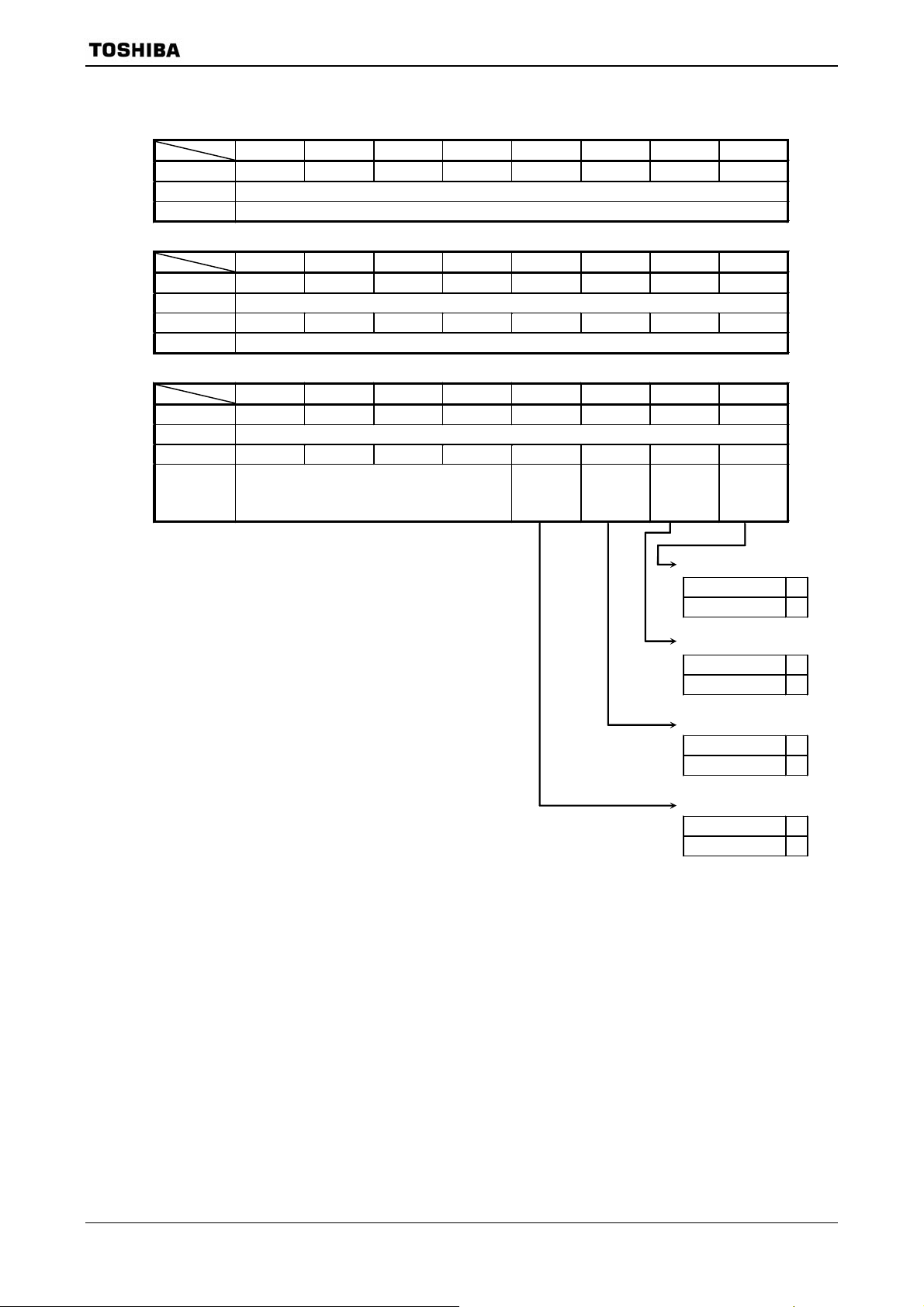

Table 2.2.1 Pin names and functions.

Table 2.2.1 Pin names and functions (1/3)

Pin Name

P00∼P07

AD0∼AD7

P10∼P17

AD8∼AD15

A8∼A15

P20∼P27

A0∼A7

A16∼A23

P30

RD

P31

WR

P32

HWR

P33

WAIT

P34

BUSRQ

P35

BUSAK

P36

W/R

P37

BOOT

P40

CS0

P41

CS1

P42

CS2

P43

CS3

P50∼P57

∼AN7

AN0

ADTRG

Number

of Pins

8 I/O

8 I/O

8 I/O

1 Output

1 Output

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

8 Input

I/O Functions

Port 0: I/O port that allows I/O to be selected at the bit level

I/O

Address and data (lower): Bits 0 to 7 of address and data bus

Port 1: I/O port that allows I/O to be selected at the bit level

I/O

Address and data (upper): Bits 8 to 15 for address and data bus

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Address: Bits 8 to 15 of address bus

Port 2: I/O port that allows I/O to be selected at the bit level

Address: Bits 0 to 7 of address bus

Address: Bits 16 to 23 of address bus

Port 30: Output port

Read: Strobe signal for reading external memory

This port output RD signal also case of reading internal-area by setting P3

<P30> = 0 and P3FC <P30F> = 1.

Port 31: Output port

Write: Strobe signal for writing data to pins AD0 to AD7

Port 32: I/O port (with pull-up resistor)

High Write: Strobe signal for writing data to pins AD8 to AD15

Port 33: I/O port (with pull-up resistor)

Input

Wait: Pin used to request CPU bus wait

((1+N) WAIT mode)

Port 34: I/O port (with pull-up resistor)

Input

Bus Request: Signal used to request Bus Release

Port 35: I/O port (with pull-up resistor)

Bus Acknowledge: Signal used to acknowledge Bus Release

Port 36: I/O port (with pull-up resistor)

Read/Write: 1 represents Read or Dummy cycle; 0 represents Write cycle.

Port 36: I/O port (with pull-up resistor)

Input

This pin sets single boot mode.

When released reset, Single boot mode is started at P37

Port 40: I/O port (with pull-up resistor)

Chip Select 0: Outputs 0 when address is within specified address area

Port 41: I/O port (with pull-up resistor)

Chip Select 1: Outputs 0 if address is within specified address area

Port 42: I/O port (with pull-up resistor)

Chip Select 2: Outputs 0 if address is within specified address area

Port 43: I/O port (with pull-up resistor)

Chip Select 3: Outputs 0 if address is within specified address area

Port 5: Pin used to input port

Input

Analog input: Pin used to input to AD converter

Input

AD Trigger: Signal used to request start of AD converter (Shared with53 pin)

=Low level.

91FY42-5 2006-11-08

TMP91FY42

Table 2.2.1 Pin names and functions (2/3)

Pin Name

P60

SCK

P61

SO

SDA

P62

SI

SCL

P63

INT0

P64

SCOUT

P65 1 I/O Port 65 I/O port

P66 1 I/O Port 66 I/O port

P70

TA0IN

P71

TA1OUT

P72

TA3OUT

P73

TA4IN

P74

TA5OUT

P75

TA7OUT

P80

TB0IN0

INT5

P81

TB0IN1

INT6

P82

TB0OUT0

P83

TB0OUT1

P84

TB1IN0

INT7

P85

TB1IN1

INT8

P86

TB1OUT0

P87

TB1OUT1

Number

of Pins

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

I/O Functions

Port 60: I/O port

I/O

Serial bus interface clock in SIO Mode

Port 61: I/O port

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Serial bus interface send data at SIO mode

I/O

Serial bus interface send/recive data at I

Open-drain output mode by programmable

Port 62: I/O port

Input

Serial bus interface recive data at SIO mode

I/O

Serial bus interface clock I/O data at I

Open-drain output mode by programmable

Port 63: I/O port

Input

Interrupt Request Pin 0: Interrupt request pin with

rising edge / falling edge

Port 64: I/O port

System Clock Output: Outputs f

Port 70I/O port

Input

8bitt timer 0 input:: Timer 0 input

Port 71I/O port

8-bit timer 1 output: Timer 0 or Timer 1 output

Port 72I/O port 8bit

8-bit timer 3 output: Timer 2 or Timer 3 output

Port 73: I/O port

Input

8-bit timer 4 input: Timer 4 input

Port 74: I/O port

8-bit timer 5 output: Timer 4 or Timer 5 output

Port 75: I/O port

88-bit timer 7 output: Timer 6 or Timer 7 output

Port 80: I/O port

Input

16bit timer 0 input 0: 16bit Timer 0 count / capture trigger input

Input

Interrupt Request Pin 5: Interrupt request pin with programmable rising edge

/ falling edge.

Port 81: I/O port

Input

16bit timer 0 input 1: 16bit Timer 0 count / capture trigger input

Input

Interrupt Request Pin 6: Interrupt request on rising edge

Port 82: I/O port

16bit timer 0 output 0: 16bit Timer 0 output

Port 83: I/O port

16bit timer 0 output 1: 16bit Timer 0 output

Port 84: I/O port

Input

16bit timer 1 input 0: 16bit Timer 1 count / capture trigger input

Input

Interrupt Request Pin 7: Interrupt request pin with programmable rising edge

/ falling edge.

Port 85: I/O port

Input

16bit timer 1 input 1: 16bit Timer 1 count / capture trigger input

Input

Interrupt Request Pin 8: Interrupt request on rising edge

Port 86: I/O port

16bit timer 1 output 0: 16bit Timer 1 output 16bit

Port 87: I/O port

16bit timer 1 output 1: 16bit Timer 1 output 16bit 16bit

2

or fs clock.

FPH

2

C bus mode

C bus mode

programmable level /

91FY42-6 2006-11-08

TMP91FY42

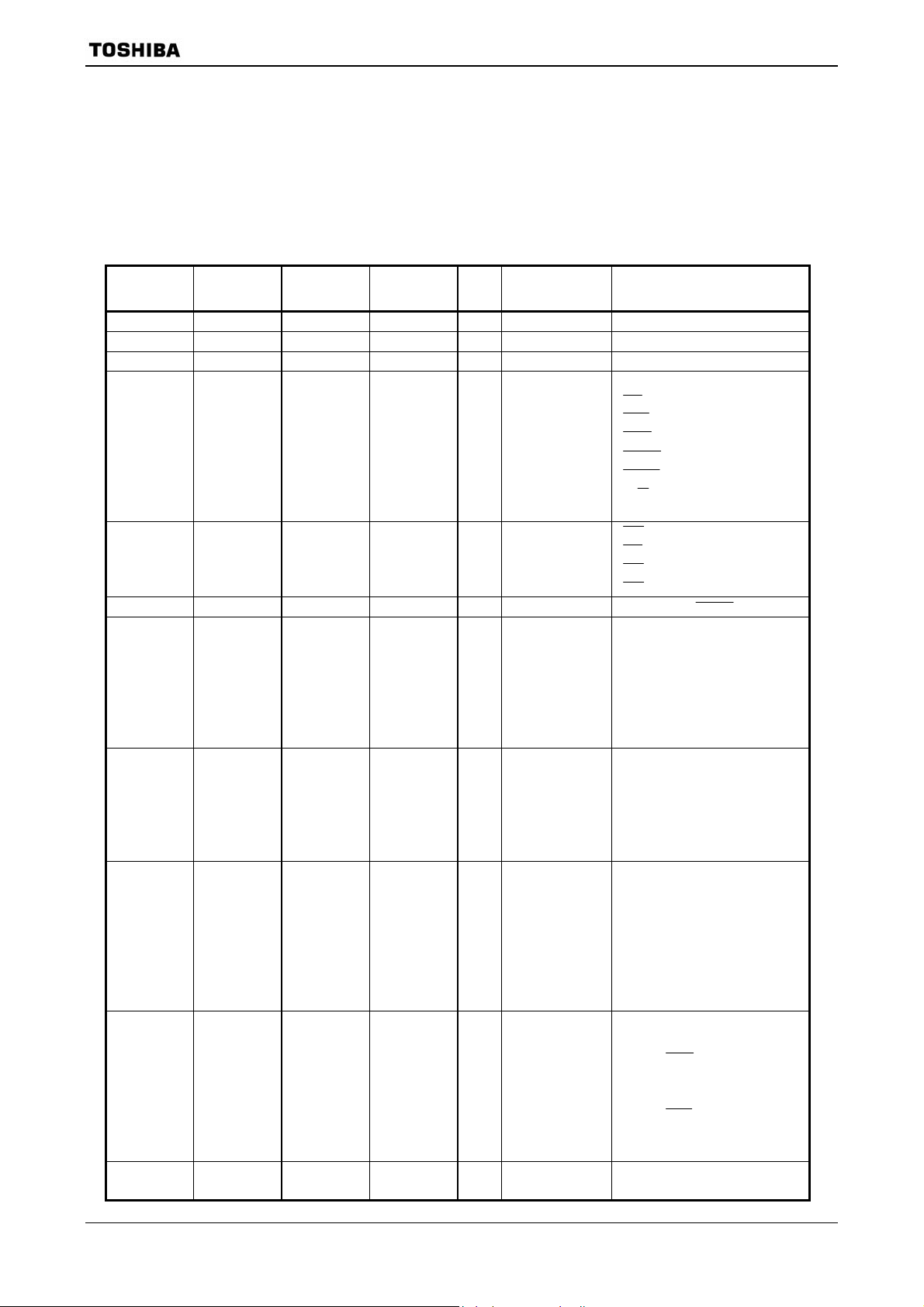

Table 2.2.1 Pin names and functions (3/3)

Pin Name

P90

TXD0

P91

RXD0

P92

SCLK0

0CTS

P93

TXD1

P94

RXD1

P95

SCLK1

CTS1

P96

XT1

P97

XT2

PA0∼PA3

INT1

∼INT4

PA4∼PA7 4 I/O Ports A4 to A7: I/O ports

ALE 1 Output Address Latch Enable

NMI

AM0∼1

EMU0 1 Output Open pin

EMU1 1 Output Open pin

RESET

VREFH 1 Input Pin for reference voltage input to AD converter (H)

VREFL 1 Input Pin for reference voltage input to AD converter (L)

AVCC 1 Power supply pin for AD converter

AVSS 1 GND pin for AD converter (0 V)

X1/X2 2 I/O High-frequency oscillator connection pins

DVCC 3 Power supply pins (All DVCC pins should be connected with the power supply pin.)

DVSS 3 GND pins (0 V) (All DVSS pins should be connected with the power supply pin.)

Number

of Pins

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

4 I/O

1 Input Non-Maskable Interrupt Request Pin: Interrupt request pin with programmable

2 Input

1 Input Reset: initializes TMP91FY42. (With pull-up resistor)

I/O Functions

Port 90: I/O port

Output

Output

Output

Serial Send Data 0 (programmable open-drain)

Port 91: I/O port

Input

Serial Receive Data 0

Port 92: I/O port

I/O

Serial Clock I/O 0

Input

Serial Data Send Enable 0 (Clear to Send)

Port 93: I/O port

Serial Send Data 1 (programmable open-drain)

Port 94: I/O port (with pull-up resistor)

Input

Serial Receive Data 1

Port 95: I/O port (with pull-up resistor)

I/O

Serial Clock I/O 1

Input

Serial Data Send Enable 1 (Clear to Send)

Port 96: I/O port (open-drain output)

Input

Low-frequency oscillator connection pin

Port 97: I/O port (open-drain output)

Low-frequency oscillator connection pin

Ports A0 to A3: I/O ports

Input

Interrupt Request Pins 1 to 4: Interrupt request pins with programmable rising

edge / falling edge.

Can be disabled to reduce noise.

falling edge or both edge.

Operation mode:

Fixed to AM1

= 1, AM0 = 1

Note: An external DMA controller cann ot access the device’s built-in memory or built-in I/O devices using

the

BUSRQ

and

BUSAK

signal.

91FY42-7 2006-11-08

3. Operation

This following describes block by block the functions and operation of the TMP91FY42.

Notes and restrictions for eatch book are outlined in 7 “Points of Note and Restrictions” at the

end of this manual.

3.1 CPU

The TMP91FY42 incorporates a high-performance 16-bit CPU (The 900/L1 CPU). For CPU

operation, see the “TLCS-900/L1 CPU”.

The following describe the unique function of the CPU used in the TMP91FY42; these

functions are not covered in the TLCS-900/L1 CPU section.

3.1.1 Reset

When resetting the TMP91FY42 microcontroller, ensure that the power supply voltage is

within the operating voltage range, and that the internal high-frequency oscillator has

stabilized. Then hold the

27MHz).

Thus, when turn on the switch, be set to the power supply voltage is within the operating

voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the

RESET input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock

mode f

SYS

When the reset is accept, the CPU:

• Sets as follows the program counter (PC) in accordance with the reset vector stored

at address FFFF00H to FFFF02H:

TMP91FY42

RESET

is set to fc/32 (= fc/16 × 1/2).

PC<7:0> ← Value at FFFF00H address

input to low level for at least 10 system clocks (12μs at

PC<15:8> ← Value at FFFF01H address

PC<23:16> ← Value at FFFF02H address

• Sets the stack pointer (XSP) to 100H.

• Sets bits <IFF2:0> of the status register (SR) to 111 (Sets the interrupt level mark

register to level 7).

• Sets the <MAX> bit of the status register to 1 (MAX mode).

(Note: As this product does not support MIN mode, do not write a 0 to the <MAX>.)

• Clears bits <RFP2:0> of the status register to 000 (Sets the register bank to 0).

When reset is released,the CPU starts executing instructions in accordance with the

program counter settings. CPU internal registers not mentioned above do not change

when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports, and other pins as

follows.

• Initializes the internal I/O registers.

• Sets the port pins, including the pins that also act as internal I/O, to

general-purpose input or output port mode.

• Sets ALE pin to “High-Z"

Note: The CPU internal register (except to PC, SR, XSP) and internal RAM data do not

change by resetting.

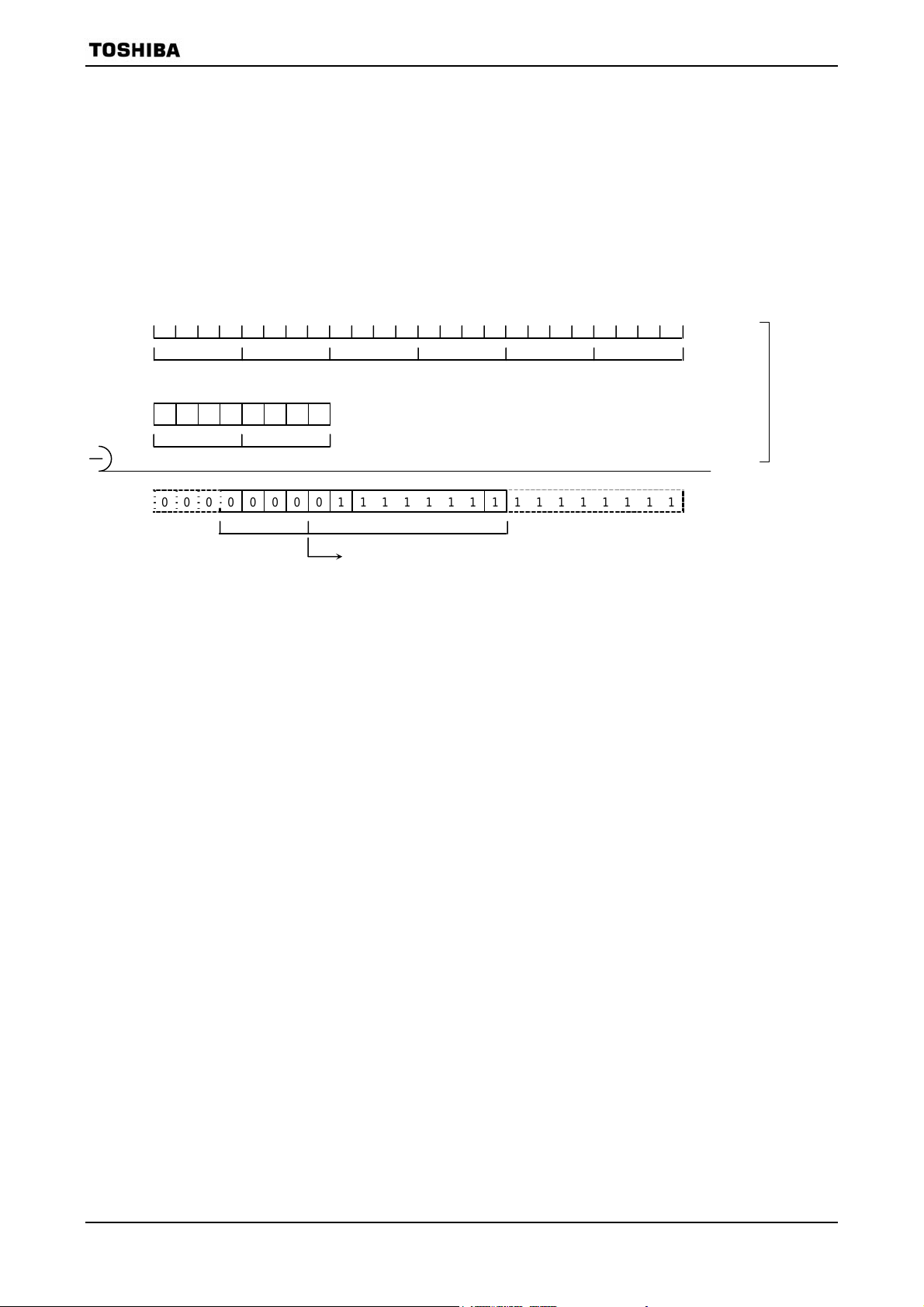

Figure 3.1.1 is a reset timing of the TMP91FY42.

91FY42-8 2006-11-08

TMP91FY42

Read

(After reset is released, startting 0

wait read cycle)

Write

Sampling

(P32 imput mode)

(P20~P27 imput mode)

(P40~P43 imput mode)

Sampling

FPH

f

RESET

A16~A23

(P36 imput mode)

R/W

CS0∼CS3

(P00~P07, P10~P17 imput mode)

(P30 output mode)

Address

Address

ALE

AD0~AD15

RD

(P00~P07, P10~P17 imput mode)

Address

Data-out

Address

AD0~AD15

(P31 output mode)

WR

(Output mode)

(Imput mode)

(Imput mode)

: Pull-up (Internal)

: High-Z

HWR

P30∼P31

P32~P37, P40~P43

P00~P07, P10~P17,

P20~P27, P60~P66,

P70~P75, P80~P87,

P90~P97, PA0~PA7

Figure 3.1.1 TMP91FY42 Reset Timing Example

91FY42-9 2006-11-08

3.1.2 Outline of Operation Modes

There are single-chip and single-boot modes. Which mode is selected depends on the device’s

pin state after a reset.

• Single-chip mode: The device normally operations in this mode. After a reset, the device starts

executing the internal memory program.

• Single-boot mode: This mode is used to rewrite the internal flash memory by serial transfer

(UART).

After a reset, internal boot program starts up, executing an on-board rewrite

program.

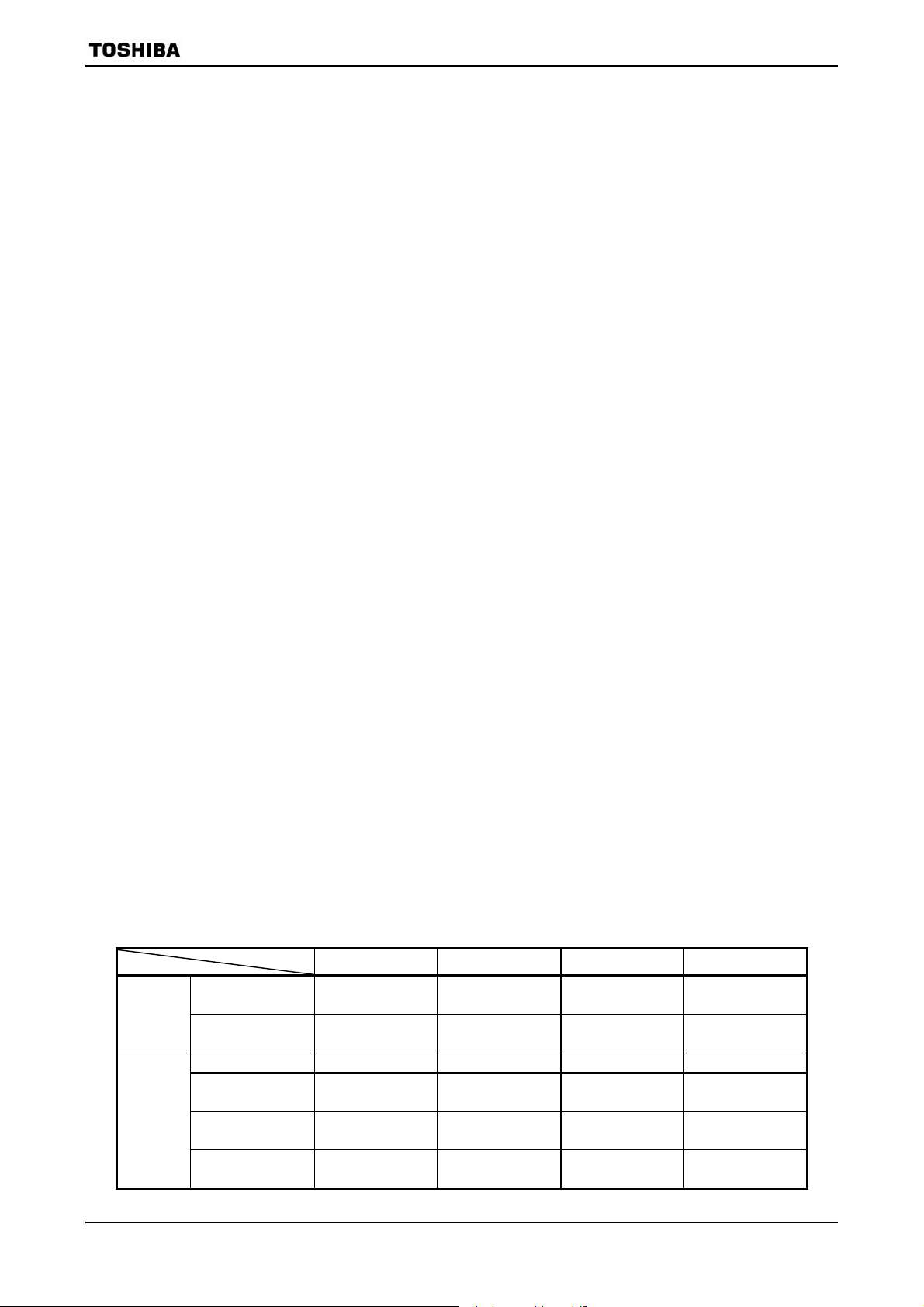

Table 3.1.1 Operation Mode Setup Table

TMP91FY42

Operation Mode

Mode Setup Input Pin

RESET BOOT (P37)

Single-chip mode H

Single-boot mode

L

AM0 AM1

H H

91FY42-10 2006-11-08

3.2 Memory Map

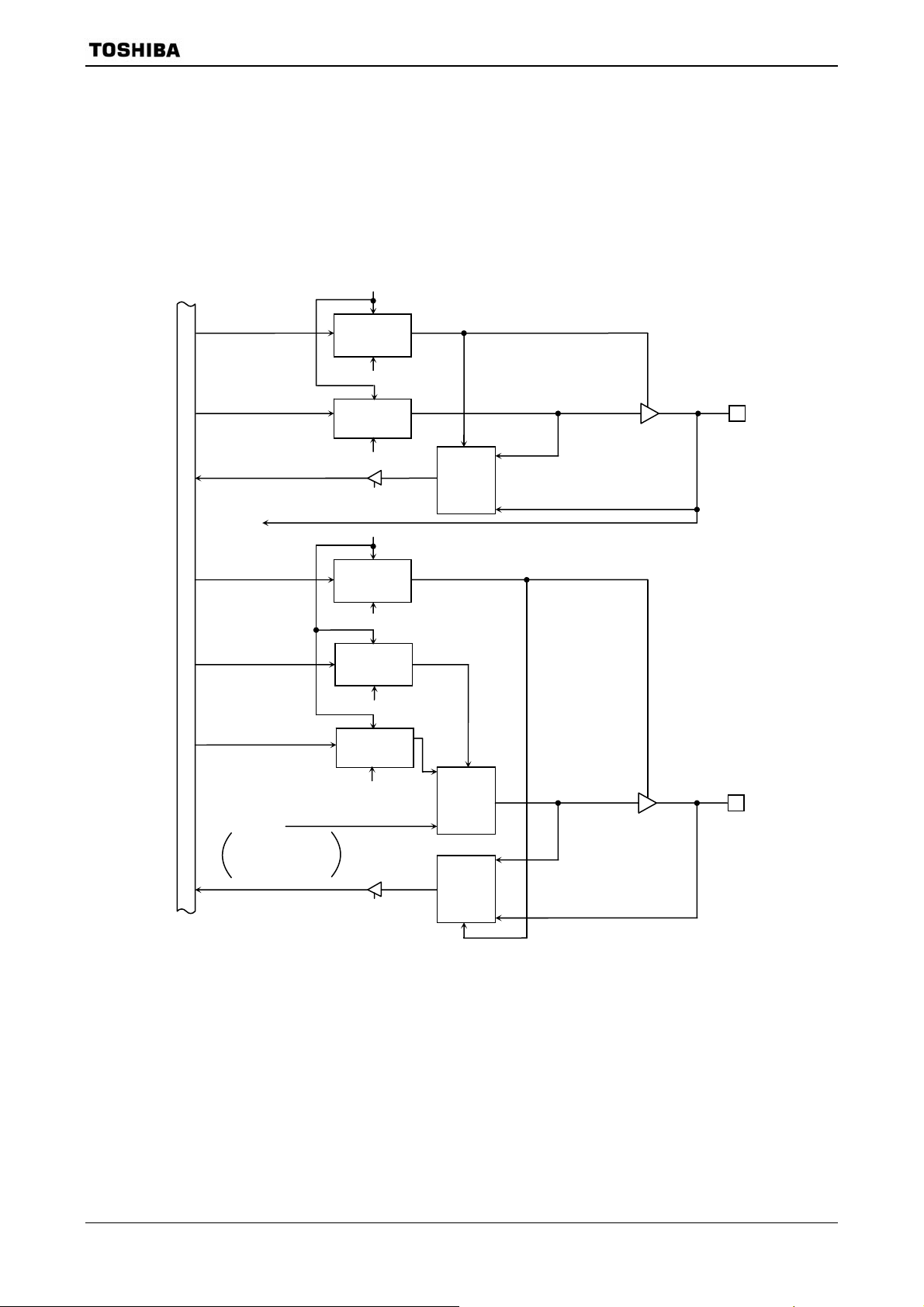

Figure 3.2.1 is a memory map of the TMP91FY42.

000000H

000100H

Internal I/O

(4 Kbytes)

TMP91FY42

Direct area

(n)

001000H

005000H

010000H

FC0000H

Internal R A M

(16 Kbyte)

External memory

256 Kbyte

Internal ROM

64 Kbyte area

(nn)

16 Mbyte area

(R)

(−R)

(R+)

(R + R8/16)

(R + d8/16)

(nnn)

FFFF00H

FFFFFFH

Vector table (256 byte)

( = Internal area)

Figure 3.2.1 Memory Map

91FY42-11 2006-11-08

3.3 Triple Clock Function and Standby Function

TMP91FY42 contains (1) Clock gear, (2) Standby controller, and (3) Noise-reducing circuit. It

is used for low-power, low-noise systems.

This chapter is organized as follows:

• 3.3.1 Block Diagram of System Clock

• 3.3.2 SFRs

• 3.3.3 System Clock Controller

• 3.3.4 Prescaler Clock Controller

• 3.3.5 Noise Reduction Circuits

• 3.3.6 Standby Controller

TMP91FY42

91FY42-12 2006-11-08

TMP91FY42

The clock operating modes are as follows: (a) Single clock mode (X1, X2 pins only), (b) Dual

clock mode (X1, X2, XT1 and XT2 pins).

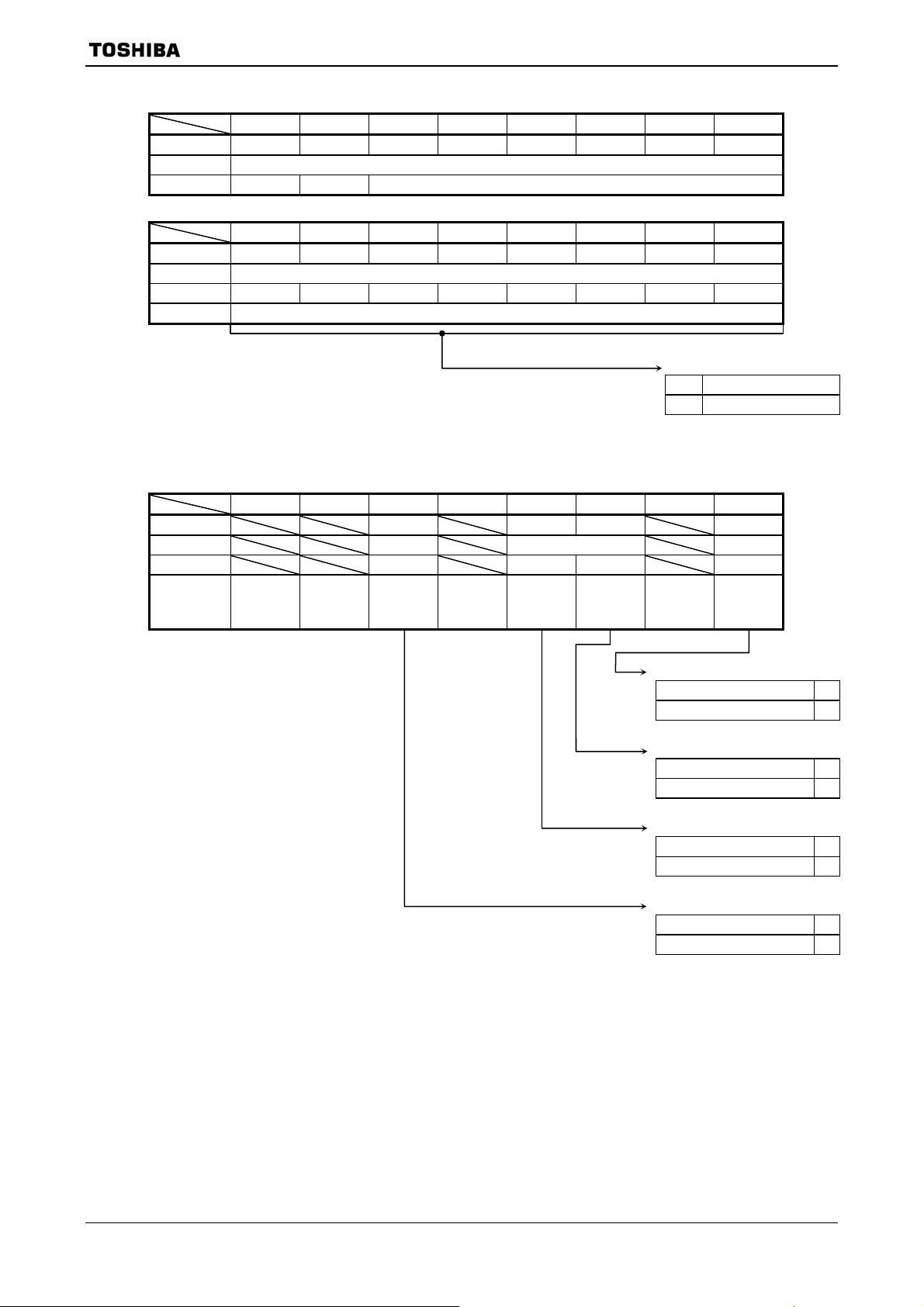

Figure 3.3.1 shows a transition figure.

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

Instruction

Interrupt

Instruction

Interrupt

(a) Single clock mode transition figure

Instruction

Interrupt

Instruction

Interrupt

Instruction

Interrupt

Instruction

Interrupt

(b) Dual clock mode transition fiigure

Reset

/32)

(f

OSCH

Release reset

NORMAL mode

/gear value/2)

(f

OSCH

Reset

/32)

(f

OSCH

Release reset

NORMAL mode

/gear value/2)

(f

OSCH

SLOW mode

(fs/2)

Instruction

Instruction

Interrupt

Instruction

Interrupt

STOP mode

(Stops all circuits)

STOP mode

(Stops all circuits)

Figure 3.3.1 System Clock Block Diagram

The clock frequency input from the X1 and X2 pins is called fc and the clock frequency input

from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is

called the system clock f

one cycle of f

is defined to as one state.

SYS

. The system clock f

FPH

is defined as the divided clock of f

SYS

FPH

, and

TMP91FY42 does not built-in Clock Doubler (DFM).

91FY42-13 2006-11-08

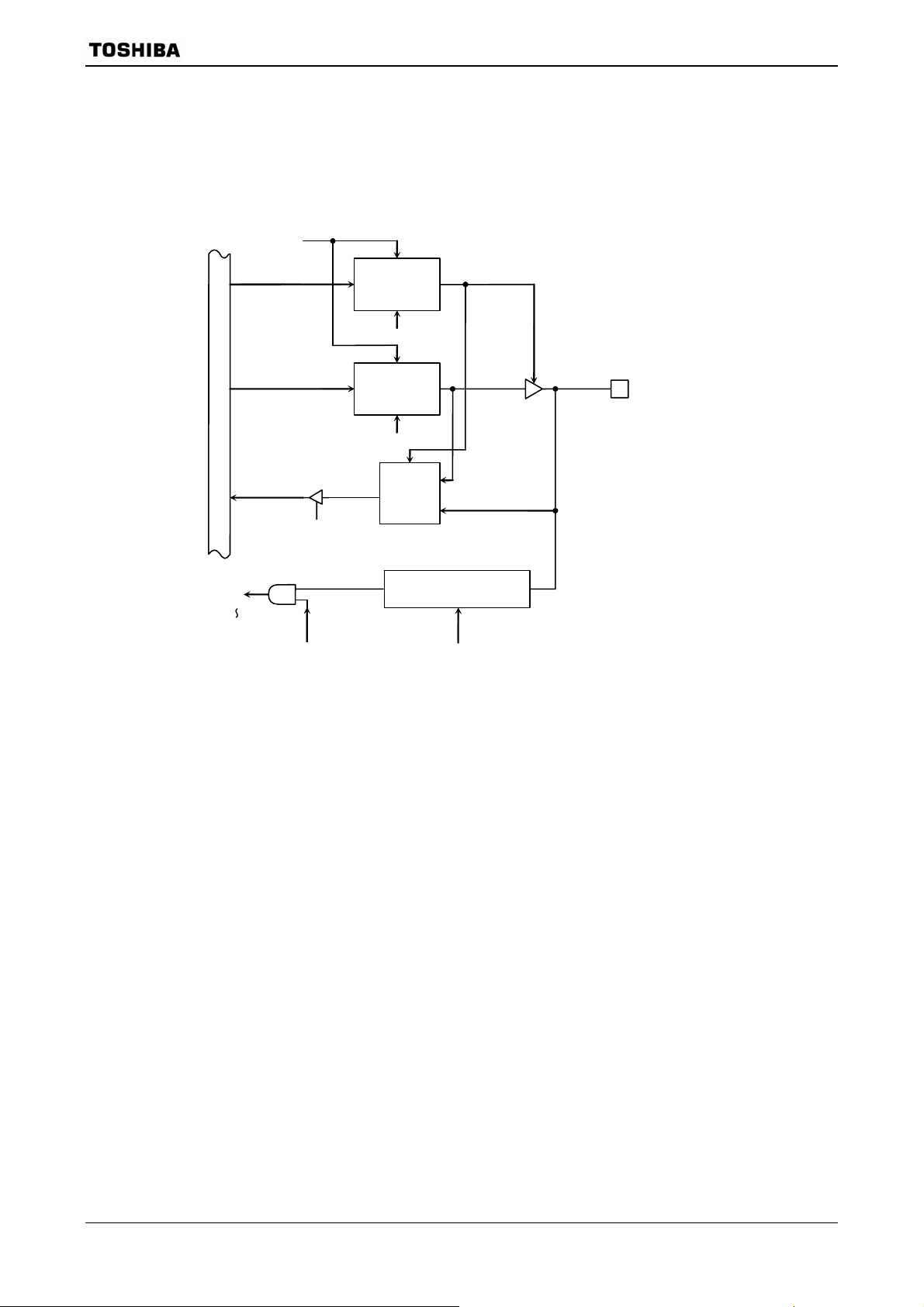

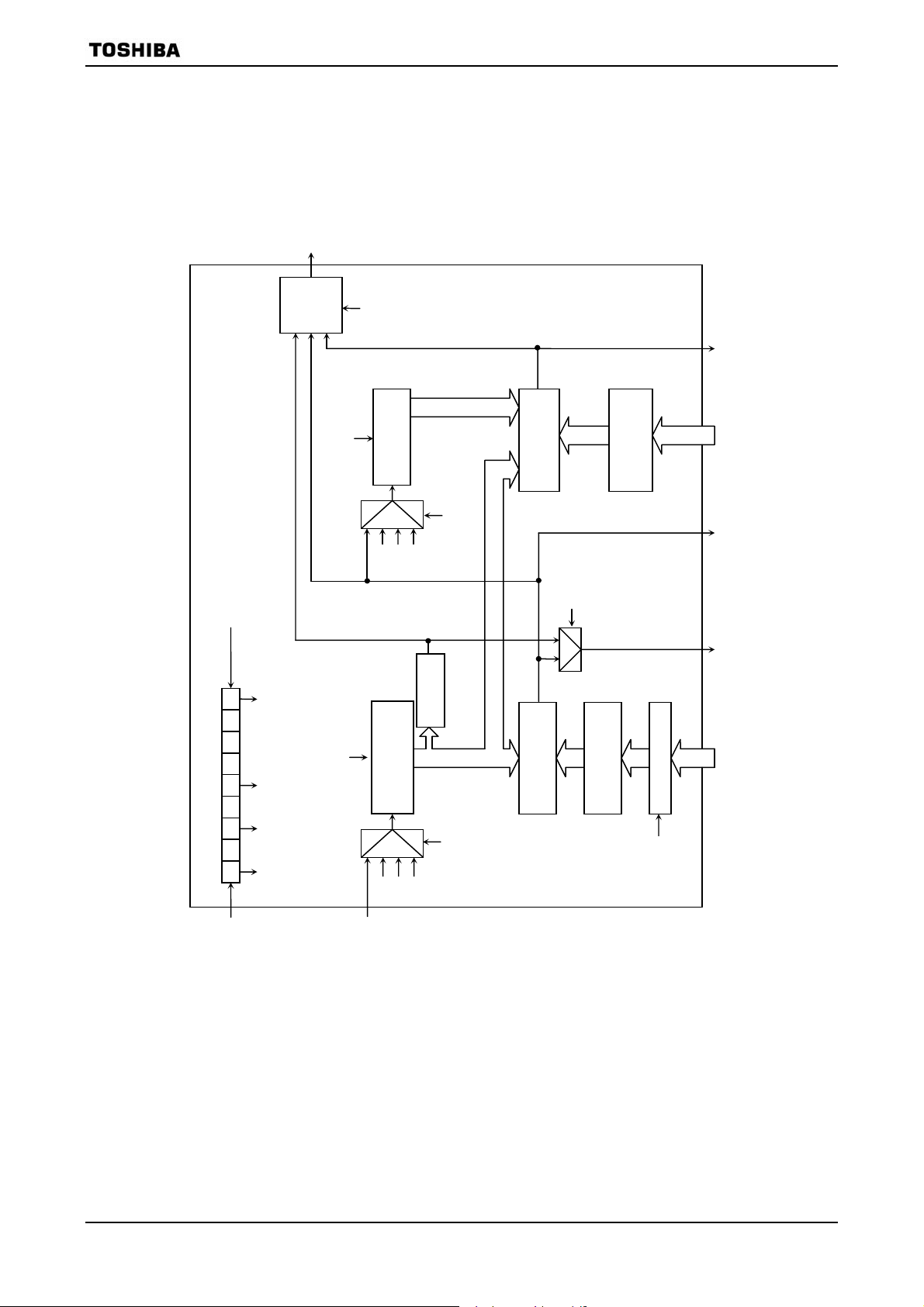

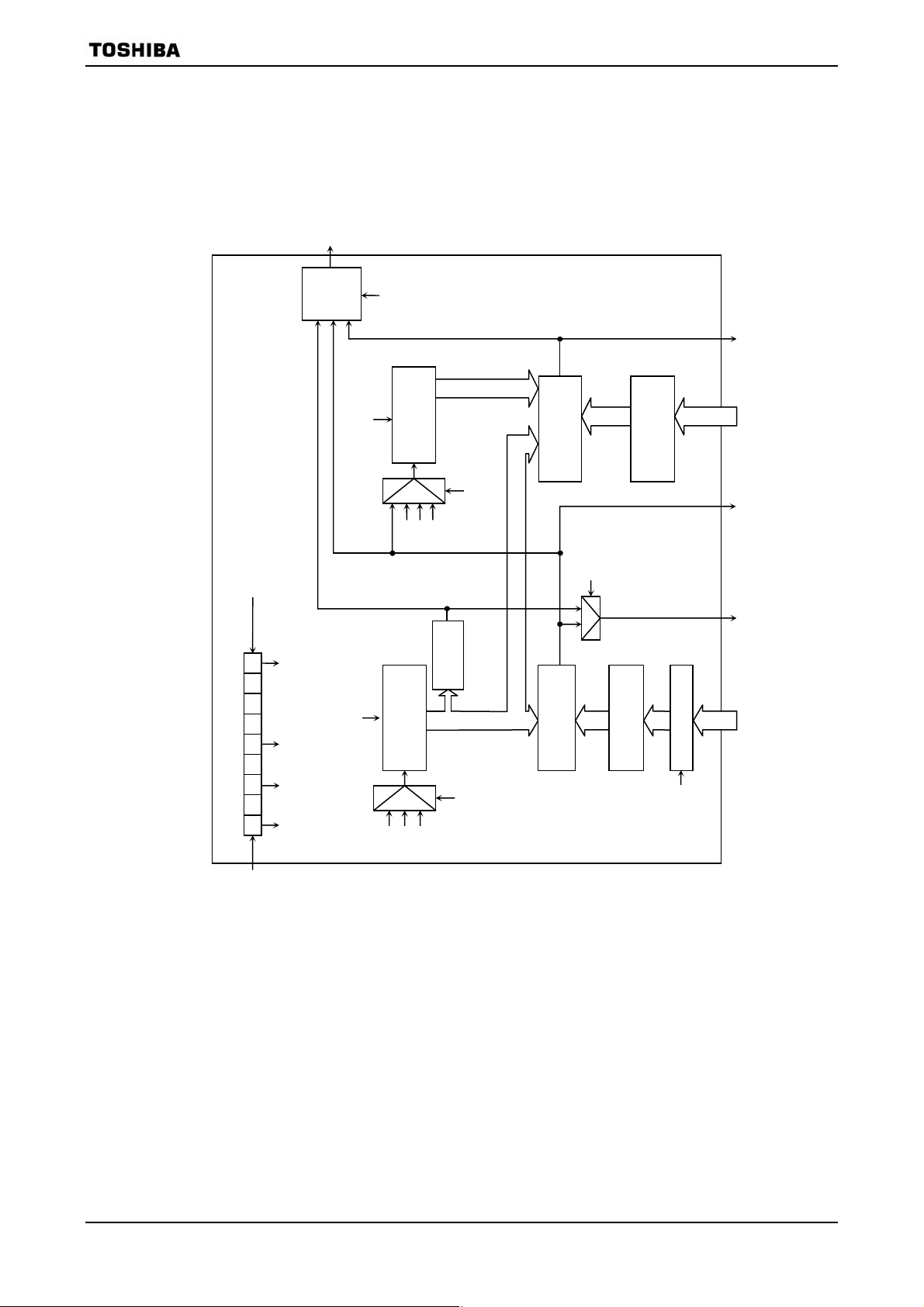

3.3.1 Block Diagram of System Clock

SYSCR0<WUEF>

SYSCR2<WUPTM1:0>

Warm-up timer (High-/low-frequencyoscillator)

SYSCR0

<XTEN, RXTEN>

f

OSCH

fs

XT1

XT2

X1

X2

Low-frequency

oscillator

SYSCR0

<XEN, RXEN>

High-frequency

oscillator

fc

fc/2

÷2 ÷16 ÷4 ÷8

Clock gear

TMP91FY42

SYSCR0

<PRCK1:0>

fc/4

fc/8

fc/16

SYSCR1<GEAR2:0>

fc/16

f

FPH

SYSCR1<SYSCK>

÷2 ÷4

÷2

φT

φT0

fs

f

FPH

f

SYS

f

SYS

φT0

f

FPH

φT

TMRA01 toTMRA67

Prescaler

TMRB0 to TMRB1

Prescaler

SIO0~SIO1

Prescaler

SBI

Prescaler

Special timer for CLOCK

fs

Binary counter

SYSCR2<SCOSEL>

CPU

ROM

RAM

Interrupt

controller

CS/WAIT

controller

ADC

WDT

I/O ports

SCOUT

Figure 3.3.2 Block Diagram of System Clock

Note: TMP91FY42 does not built-in Clock Doubler (DFM).

91FY42-14 2006-11-08

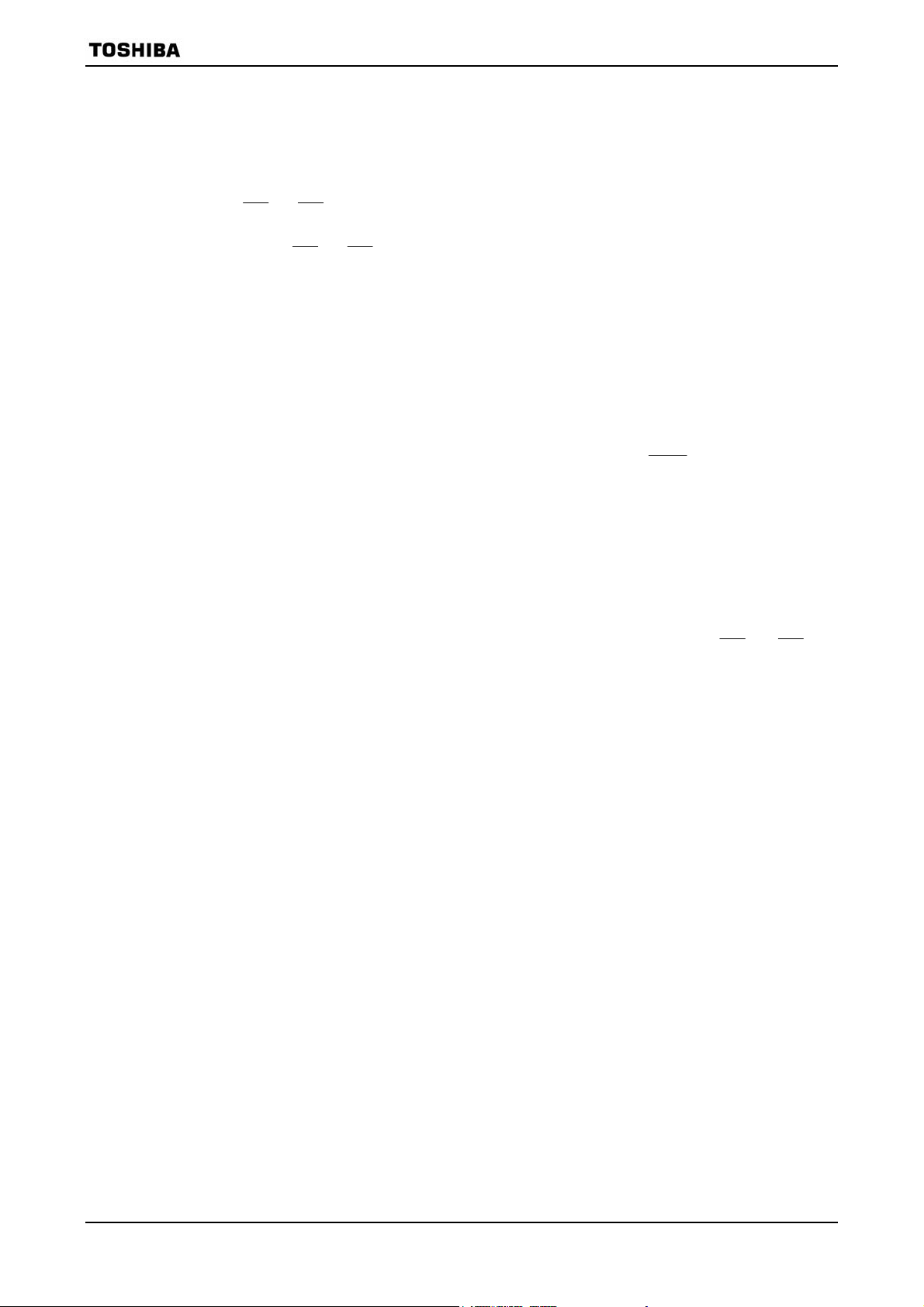

3.3.2 SFRs

SYSCR0

(00E0H)

SYSCR1

(00E1H)

SYSCR2

(00E2H)

Bit symbol XEN XTEN RXEN RXTEN RSYSCK WUEF PRCK1 PRCK0

Read/Write R/W

After reset 1 1 1 0 0 0 0 0

Function

7 6 5 4 3 2 1 0

Bit symbol SYSCK GEAR2 GEAR1 GEAR0

Read/Write R/W

After reset 0 1 0 0

Function

7 6 5 4 3 2 1 0

Bit symbol SCOSEL WUPTM1 WUPTM0 HALTM1 HALTM0 DRVE

Read/Write R/W R/W

After reset 0 1 0 1 1 0

Function Selects

Note 1: SYSCR1<bit7:4>,SYSCR2<bit7,1> are read as undefined value.

Note 2:In case of using built-in SBI circuit, it must set SYSCR0<PRCK1:0> to 00.

TMP91FY42

7 6 5 4 3 2 1 0

Highfrequency

oscillator (fc)

0: Stop

1: Oscillation

Lowfrequency

oscillator (fs)

0: Stop

1: Oscillation

(Note 1)

SCOUT

0: fs

1: f

FPH

Highfrequency

oscillator (fc)

after release

of STOP

mode

0: Stop

1: Oscillation

Warm-up timer

00: Reserved

8

01: 2

/inputted frequency

14

10:2

/inputted frequency

16

11:2

/inputted frequency

Lowfrequency

oscillator (fs)

after release

of STOP

mode

0: Stop

1: Oscillation

Select

Selects clock

after release

of STOP

mode

0: fc

1: fs

system clock

0: fc

1: fs

HALT mode

00: Reserved

01: STOP mode

10: IDLE1 mode

11: IDLE2 mode

Warm-up

timer

0: Write

don’t

care

1: Write

start

timer

0: Read

end

warm up

1: Read do

not end

warm up

Select gear value of high frequency (fc)

000: fc

001: fc/2

010: fc/4

011: fc/8

100: fc/16

101: (Reserved)

110: (Reserved)

111: (Reserved)

Select prescaler clock

00: f

(Note 2)

FPH

01: Reserved

10: fc/16

11: Reserved

Pin state

control in

STOP/IDLE1

mode

0: I/O off

1: Remains

the state

before

halt

Figure 3.3.3 SFR for System Clock

91FY42-15 2006-11-08

TMP91FY42

DFMCR0

(00E8H)

Bit symbol ACT1 ACT10 DLUPFG DLUPTM

Read/Write R/W R R/W

After reset 0 0 0 0

Function

7 6 5 4 3 2 1 0

Always write “0”

DFMCR1

(00E9H)

Bit symbol – – – – – – – –

Read/Write R/W

After reset 0 0 0 1 0 0 1 1

Function

7 6 5 4 3 2 1 0

Don’t access this register

Figure 3.3.4 SFR for DFM

Note: TMP91FY42 does not built-in Clock Doubler (DFM).

7 6 5 4 3 2 1 0

EMCCR0

(00E3H)

EMCCR1

(00E4H)

Bit symbol PROTECT – – – ALEEN EXTIN DRVOSCH DRVOSCL

Read/Write R R/W

After reset 0 0 1 0 0 0 1 1

Function

Bit symbol

Read/Write

After reset

Function

Note1: When restarting the oscillator from the stop oscil latio n sta te (e .g. r estar ting the o scillato r in STO P mo de), set

Protect flag

0: OFF

1: ON

EMCCR0<DRVOSCH>, <DRVOSCL>

Always

write “0”

Always

write “1”

Writing 1FH turns protections off.

Writing any value other than 1FH turns protection on.

=”1”..

Always

write “0”

0: ALE output

disable

1: ALE output

enable

1: fc external

clock

fc oscillator

driver ability

1: Normal

0: Weak

fs oscillator

driver ability

1: Normal

0: Weak

Figure 3.3.5 SFR for Noise Reducing

91FY42-16 2006-11-08

3.3.3 System Clock Controller

TMP91FY42

The system clock controller generates the system clock signal (f

) for the CPU core and

SYS

internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency

(fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs,

SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator,

and SYSCR1<GEAR0:2> sets the high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2,

fc/4, fc/8 or fc/16). These functions can reduce the power consumption of the equipment in

which the device is installed.

The combination of settings <XEN> = 1, <XTEN> = 0, <SYSCK> = 0 and <GEAR0:2> =

100 will cause the system clock (f

For example, f

is set to 0.84 MHz when the 27-MHz oscillator is connected to the X1

SYS

) to be set to fc/32 (fc/16 × 1/2) after a reset.

SYS

and X2 pins.

(1) Switching from NORMAL mode to SLOW mode

When the resonator is connected to the X1 and X2 pins, or to the XT1 and XT2 pins,

the warm-up timer can be used to change the operation frequency after stable

oscillation has been attained.

The warm-up time can be selected using SYSCR2<WUPTM0:1>.

This warm-up timer can be programmed to start and stop as shown in the following

examples 1 and 2.

Table 3.3.1 shows the warm-up times.

Note 1: When using an oscillator (Other than a resonator) with stable oscillation, a

warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some

variation in warm-up time.

Note 2: Note on using low-frequency oscillation circuit

To connect the low-frequency resonator to port 96, 97, it is necessary to set the

following to reduce the power consumption.

(connecting with resonators)

P9CR<P96C:97C> = 11, P9<P96:97> = 00

(connection with oscillators)

P9CR<P96C:97C> = 11, P9<P96:97> = 10

Table 3.3.1 Warm-up Tim es

Warm-up Time

SYSCR2

<WUPTM1:0>

01 (28/frequency) 9.0 [μs] 7.8 [ms]

10 (214/frequency) 0.607 [ms] 500 [ms]

11 (216/frequency) 2.427 [ms] 2000 [ms]

Change to

NORMAL Mode

Change to

SLOW Mode

at f

OSCH

fs

= 32.768 kHz

= 27 MHz,

91FY42-17 2006-11-08

Example 1: Setting the clock

Changing from high frequency (fc) to low frequency (fs).

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

LD (SYSCR2),

SET 6, (SYSCR0) ; Enables low-frequency oscillation.

SET 2, (SYSCR0) ; Clears and starts warm-up timer.

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

SET 3, (SYSCR1) ; Changes f

RES 7, (SYSCR0) ; Disables high-frequency oscillation.

X: Don’t care,

−: No change

−X11− − X −B ; Sets warm-up time to 2

TMP91FY42

Detects stopping of warm-up timer.

from fc to fs.

SYS

<XEN>

X1, X2 pins

<XTEN>

XT1, XT2 pins

16

/fs.

Warm-up timer

End of warm-up timer

<SYSCK>

System clock f

SYS

Counts up by f

Enables

low frequency

SYS

Clears and starts

warm-up timer

Counts up by fs

fc

fs

Chages f

from fc to fs

End of warm-up timer

Disables

SYS

high frequency

91FY42-18 2006-11-08

Example 2: Setting the clock

Changing from low frequency (fs) to high frequency (fc).

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

LD (SYSCR2),

SET 7, (SYSCR0) ; Enables high-frequency oscillation.

SET 2, (SYSCR0) ; Clears and starts warm-up timer.

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

RES 3, (SYSCR1) ; Changes f

RES 6, (SYSCR0) ; Disables low-frequency oscillation.

X: Don’t care,

−: No change

−X10− − − −B ; Sets warm-up time to 2

TMP91FY42

14

/fc.

Detects stopping of warm-up timer.

from fs to fc.

SYS

<XEN>

X1, X2 pins

<XTEN>

XT1, XT2 pins

Warm-up timer

End of warm-up timer

<SYSCK>

System clock f

SYS

Counts up by f

Enables

high frequency

SYS

Clears and starts

warm-up timer

Counts up by f

End of warm-up

timer

OSCH

Chages f

from fs to fc

fcfs

SYS

Disables

low frequency

91FY42-19 2006-11-08

(2) Clock gear controller

TMP91FY42

When the high-frequency clock fc is selected by setting SYSCR1<SYSCK> = 0, f

FPH

is set according to the contents of the clock gear select register SYSCR1<GEAR2:0> to

either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of f

FPH

reduces power consumption.

Example 3: Changing to a high-frequency gear

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0000B ; Changes f

X: Don’t care

SYS

to fc/2.

(High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2:0> register. It is

necessary the warm-up time until changing after writing the register value.

There is the possibility that the instruction next to the clock gear changing instruction is

executed by the clock gear before changing. To execute the instruction next to the clock gear

switching instruction by the clock gear after changing,input the dummy instruction as follows

(Instruction to execute the write cycle).

(Example)

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0001B ; Changes f

LD (DUMMY), 00H ; Dummy instruction.

Instruction to be executed after clock gear has changed.

SYS

to fc/4.

(3) Internal colck pin output function

P64/SCOUT pin outputs the internal clocks f

FPH

or fs.

The port 6 coutrol register P6CR<P64C> = 1, P6FC<P64F> = 1 specifies the SCOUT

output pin. The selection of output clock is set by SYSCR2<SCOSEL>.

Table 3.3.2 shows pin states in ther respective operation modes which is under

condition that P64/SCOUT pin is specifies as SCOUT output.

Table 3.3.2 SCOUT Pin States in the Operation Modes

Operation Mode

SCOUT

<SCOSEL> = “0” Outputs fs clock

<SCOSEL> = “1” Output f

NORMAL,

SLOW

clock

FPH

IDLE2 IDLE1 STOP

HALT Mode

Fixed to “0” or

“1”

91FY42-20 2006-11-08

3.3.4 Prescaler Clock Controller

For the internal I/O (TMRA01 to TMRA67, TMRB0 to TMRB1, SIO0 to SIO1,SBI) there

is a prescaler which can divide the clock.

The φT clock input to the prescaler is either the clock f

divided by 2. The setting of the SYSCR0<PRCK0:1> register determines which clock signal

is input. When it’s used internal SBI circuit, <PRCK1:0> register must be set to 00.

3.3.5 Noise Reduction Circuits

Noise reduction circuits are built in, allowing implementation of the following features.

(1) Reduced drivability for high-frequency oscillator

(2) Reduced drivability for low-frequency oscillator

(3) Single drive for high-frequency oscillator]

(4) Disables Output for ALE-pin

(4) Runaway provision with SFR protection register

The above functions are performed by making the appropriate settings in the EMCCR0

to EMCCR1 registers.

TMP91FY42

divided by 2 or the clock fc/16

FPH

(1) Reduced drivability for high-frequency oscillator

(Purpose)

Reduces noise and power for oscillator when a resonator is used.

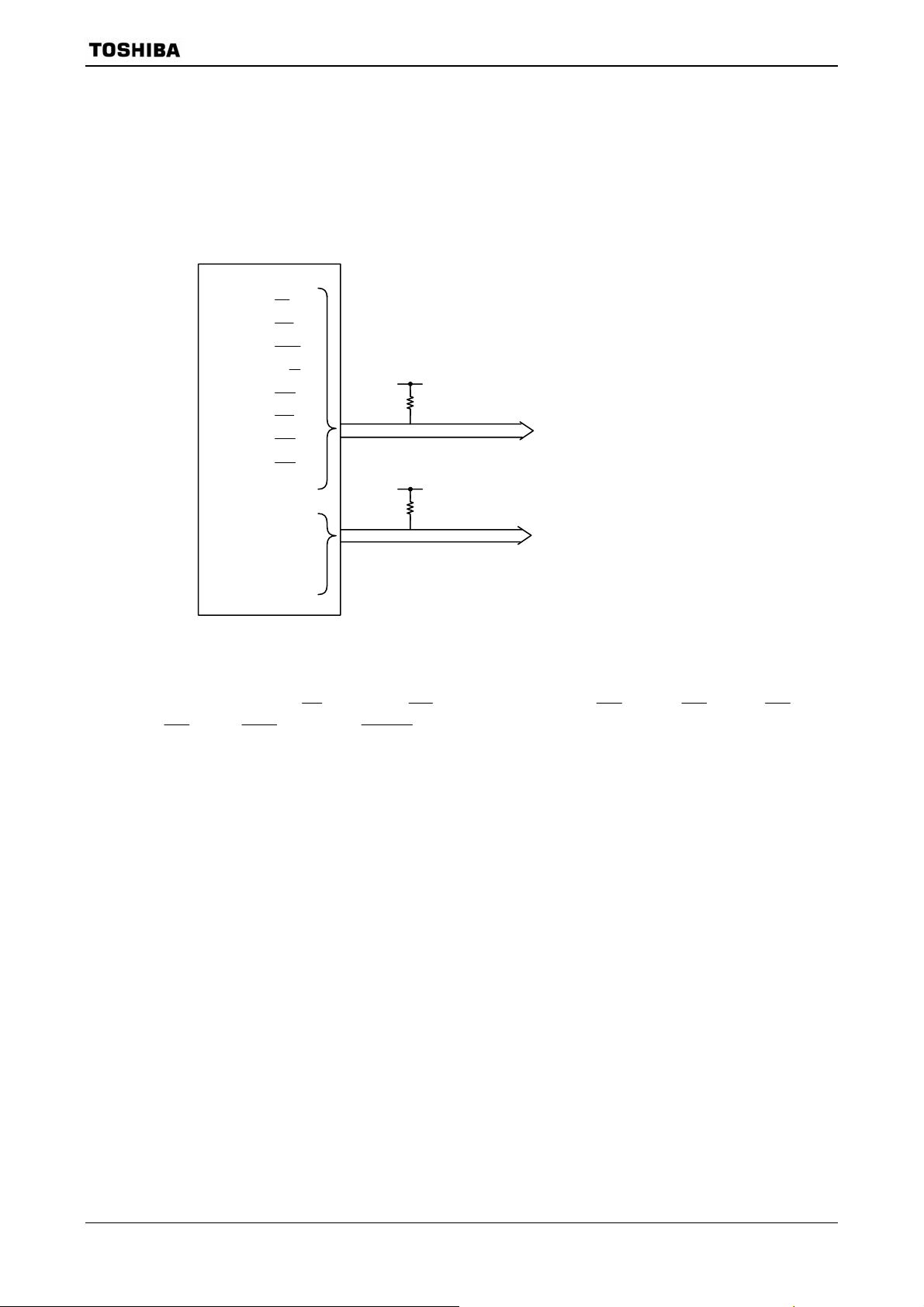

(Block diagram)

f

C1

Resonator

C2

X1 pin

Enable oscillation (STOP + EMCCR0<EXTIN>)

EMCCR0<DRVOSCH>

X2 pin

OSCH

(Setting method)

The drivability of the oscillator is reduced by writing 0 to EMCCR0<DRVOSCH>

register. By reset, <DRVOSCH> is initialized to 1 and the oscillator starts oscillation

by normal drivability when the power supply is on. The case of V

≤ 2.7 V, it is

CC

impossible to use selecting function of drivability of High-frequency oscillator.

Do not write “0” to EMCCR0<DRVOSCH>.

91FY42-21 2006-11-08

TMP91FY42

(2) Reduced drivability for low-frequency oscillator

(Purpose)

Reduces noise and power for oscillator when a resonator is used.

(Block diagram)

C1

Resonator

C2

XT1 pin

Enable oscillation

EMCCR0<DRVOSCL>

fs

XT2 pin

(Setting method)

The drivability of the oscillator is reduced by writing 0 to the EMCCR0<DRVOSCL>

register. By reset, <DRVOSCL> is initialized to 1.

(3) Single drive for high-frequency oscillator

(Purpose)

Not need twin-drive and protect mistake operation by inputted noise to X2 pin when

the external oscillator is used.

(Block diagram)

f

X1 pin

Enable oscillation (STOP + EMCCR0<EXTIN>)

OSCH

EMCCR0<DRVOSCH>

X2 pin

(Setting method)

The oscillator is disabled and starts operation as buffer by writing 1 to

EMCCR0<EXTIN> register. X2 pin is always outputted 1.

By reset, <EXTIN> is initialized to 0.

Note: Do not write EMCCR0<EXTIN> = “1” when using external resonator.

91FY42-22 2006-11-08

A

TMP91FY42

(4) Disables Output for ALE-pin

(Purpose)

Disables output ALE pulse for reducing noise when CPU does not access to external

area.

(Block diagram)

EMCCR0<ALEEN>

Internal ALE

LE pin

(Setting method)

ALE pin is set to high-impedance by writing “0” to EMCCR0<ALEEN> register. By

reset, <ALEEN> is initialized to “0”. Write “1” to <ALEEN> before access when CPU

will access to external area.

(4) Runaway provision with SFR protection registers

(Purpose)

Provision in runaway of program by noise mixing.

Write operation to specified SFR is prohibited so that provision program in runaway

prevents that it is it in the state which is fetch impossibility by stopping of clock,

memory control register (CS/WAIT controller) is changed.

Specified SFR list

1. CS/WAIT controller

B0CS, B1CS, B2CS, B3CS, BEXCS,

MSAR0, MSAR1, MSAR2, MSAR3,

MAMR0, MAMR1, MAMR2, MAMR3

2. Clock gear (Only EMCCR1 is available to write).

SYSCR0, SYSCR1, SYSCR2, EMCCR0

4. (DFM)

DFMCR0

(Block diagram)

To EMCCR1

Write except “1FH

Write ”1FH”

Protect register

EMCCR0<PROTECT>

S Q

R

Write signal to SFR

Write signal to the SFR which is disables

Write signal to the othre SFR

(Setting method)

The protect-status is ON by writing except “1FH” Codes to EMCCR1 register, and

CPU is disabled to write-operation to the specific-SFR.

The protect-status is OFF by writing “1FH” code to EMCCR1.The protect-status is

set to EMCCR0<PROTECT>register.

It is initialized to OFF by resetting.

91FY42-23 2006-11-08

3.3.6 Standby Controller

(1) HALT modes

When the HALT instruction is executed, the operating mode switches to IDLE2,

IDLE1 or STOP mode, depending on the contents of the SYSCR2<HALTM1:0>

register.

The subsequent actions performed in each mode are as follows:

a. IDLE2: Only the CPU halts.

The internal I/O is available to select operation during IDLE2 mode by

setting the following register.

Table 3.3.3 shows the registers of setting operation during IDLE2 mode.

Table 3.3.3 SFR Setting Operation during IDLE2 Mode

TMRA01 TA01RUN<I2TA01>

TMRA23 TA23RUN<I2TA23>

TMRA45 TA45RUN<I2TA45>

TMRA67 TA67RUN<I2TA67>

TMRB0 TB0RUN<I2TB0>

TMRB1 TB1RUN<I2TB1>

SIO0 SC0MOD1<I2S0>

SIO1 SC1MOD1<I2S1>

SBI SBI0BR0<I2SBI0>

AD converter ADMOD1<I2AD>

WDT WDMOD<I2WDT>

TMP91FY42

Internal I/O SFR

b. IDLE1: Only the oscillator and the Special timer for CLOCK continue to

operate.

c. STOP: All internal circuits stop operating.

The operation of each of the different HALT modes is described in

Table 3.3.4.

Table 3.3.4 I/O Operation during HALT Modes

HALT Mode IDLE2 IDLE1 STOP

SYSCR2<HALTM1:0> 11 10 01

CPU Stop

I/O ports Keep the state when the HALT instruction was

TMRA01~TMRA67,

TMRB0~TMRB1

SIO0~SIO1, SBI

Block

AD converter

WDT

Special timer for CLOCK Operational available

Interrupt controller Operate

Available to select

operation block

executed.

See Table 3.3.7,

Table 3.3.8

Stop

91FY42-24 2006-11-08

TMP91FY42

(2) How to release the HALT mode

These halt states can be released by resetting or requesting an interrupt. The halt

release sources are determined by the combination between the states of interrupt

mask register <IFF2:0> and the HALT modes. The details for releasing the halt status

are shown in

Table 3.3.5.

Released by requesting an interrupt

The operating released from the HALT mode depends on the interrupt enabled

status. When the interrupt request level set before executing the halt instruction

exceeds the value of interrupt mask register,the interrupt due to the source is

processed after releasing the HALT mode, and CPU status executing an

instruction that follows the halt instruction. When the interrupt request level set

before executing the halt instruction is less than the value of the interrupt mask

register, releasing the HALT mode is not executed (in non-maskable interrupts,

interrupt processing is processed after releasing the HALT mode regardless of the

value of the mask register). However only for INT0 to INT4 and INTRTC, even if

the interrupt request level set before executing the halt instruction is less than

the value of the interrupt mask register, releasing the the HALT mode is executed.

In this case, interrupt processing, and CPU starts executing the instruction next

to the HALT instruction, but the interrupt request flag is held at 1.

Note: Usually, interrupts can release all halt status. However, the interrupts (

NMI,

INT0 to INT4, INTRTC) which can release the HALT mode may not be able to

do so if they are input during the period CPU is shifting to the HALT mode (for

about 5 clocks of f

) with IDLE1 or STOP mode (IDLE2 is not applicable to

FPH

this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to the HALT mode

completely, halt status can be released without difficulty. The priority of this

interrupt is compared with that of the interrupt kept on hold internally, and the

interrupt with higher priority is handled first followed by the other interrupt.

• Releasing by resetting

Releasing all halt status is executed by resetting.

When the stop mode is released by reset, it is necessry enough resetting time

(See

Table 3.3.6) to set the operation of the oscillator to be stable.

When releasing the HALT mode by resetting, the internal RAM data keeps the

state before the HALT instruction is executed. However the other settings

contents are initialized. (Releasing due to interrupts keeps the state before the

HALT instruction is executed.)

91FY42-25 2006-11-08

TMP91FY42

Table 3.3.5 Source of Halt State Clearance and Halt Clearance Operation

Status of Received Interrupt

Interrupt Enabled

(Interrupt level) ≥ (Interrupt mask)

Interrupt Disabled

(Interrupt level) < (Interrupt mask)

HALT mode IDLE2 IDLE1 STOP IDLE2 IDLE1 STOP

NMI ♦ ♦ ♦*1 − − −

INTWD ♦ × × − − −

INT0∼INT4 (Note 1) ♦ ♦ ♦*1 ○ ○ ○*1

INTRTC ♦ ♦ × ○ ○ ×

INT5∼INT8 ♦ (Note2) × × × × ×

INTTA0∼INTTA7 ♦ × × × × ×

INTTB00, INTTB01, INTTB10,

Interrupt

INTTB11,INTTBOF0, INTTBOF1

INTRX0∼INTRX1,

INTTX0

∼INTTX1

Source of halt state clearance

INTSBI ♦ × × × × ×

INTAD ♦ × × × × ×

RESET Initialize LSI.

♦

♦

× × × × ×

× × × × ×

♦: After clearing the HALT mode, CPU starts interrupt processing.

○: After clearing the HALT mode, CPU resumes executing starting from instruction following the HALT

instruction.

×: It can not be used to release the HALT mode .

−: The priority level (Interrupt request level) of non-maskable interrupts is fixed to 7, the highest priority

level. There is not this combination type.

*1: Releasing the HALT mode is executed after passing the warm-up time.

Note1: When the HALT mode is cleared by an INT0 interrupt of the level mode in the interrupt enabled

status, hold level H until starting interrupt processing. If level L is set before holding level L,

interrupt processing is correctly started.

Note2: When the external interrupts INT5 to INT8 are used during IDLE2 mode, set to 1 for

TB0RUN<I2TB0> and TB1RUN<I2TB1>.

(Example releasing IDLE1 mode)

An INT0 interrupt clears the halt state when the device is in IDLE1 mode.

Address

8200H LD (P6FC), 08H ; Sets P63 to INT0.

8203H LD (IIMC), 00H ; Selects INT0 interrupt rising edge.

8206H LD (INTE0AD), 06H ; Sets INT0 interrupt level to 6.

8209H EI 5 ; Sets interrupt level to 5 for CPU.

820BH LD (SYSCR2), 88H ; Sets HALT mode to IDLE1 mode.

820EH HALT ; Halts CPU.

INT0 INT0 interrupt routine

RETI

820FH LD XX, XX

91FY42-26 2006-11-08

(3) Operation

a. IDLE2 mode

In IDLE2 mode only specific internal I/O operations, as designated by the

IDLE2 setting register, can take place. Instruction execution by the CPU stops.

Figure 3.3.6 illustrates an example of the timing for clearance of the IDLE2

mode halt state by an interrupt.

TMP91FY42

AD0~AD15

Interrupt for

X1

A0~A23

ALE

RD

WR

release

Address

Data Data

Address Address

IDLE2

mode

Figure 3.3.6 Timing Chart for IDLE2 Mode Halt State Cleared by Interrupt

b. IDLE1 mode

In IDLE1 mode, only the internal oscillator and the Special timer for CLOCK

continue to operate. The system clock in the MCU stops.

In the halt state, the interrupt request is sampled asynchronously with the

system clock; however, clearance of the halt state (e.g., restart of operation) is

synchronous with it.

Figure 3.3.7 illustrates the timing for clearance of the IDLE1 mode halt state by

an interrupt.

X1

A0∼A23

ALE

AD0∼AD15

RD

WR

Interrupt for

release

Data Data Address Address

IDLE1 mode

Figure 3.3.7 Timing Chart for IDLE1 Mode Halt State Cleared by Interrupt

91FY42-27 2006-11-08

r

TMP91FY42

c. STOP mode

When STOP mode is selected, all internal circuits stop, including the internal

oscillator pin status in STOP mode depends on the settings in the

SYSCR2<DRVE> register.

Table 3.3.7, Table 3.3.8 summarizes the state of these

pins in STOP mode.

After STOP mode has been cleared system clock output starts when the

warm-up time has elapsed, in order to allow oscillation to stabilize. After STOP

mode has been cleared, either NORMAL mode or SLOW mode can be selected

using the SYSCR0<RSYSCK> register. Therefore, <RSYSCK>, <RXEN> and

<RXTEN> must be set see the sample warm-up times in

Table 3.3.6.

Figure 3.3.8 illustrates the timing for clearance of the STOP mode halt state by

an interrupt.

X1

Warm-up

timer

A0∼A23

ALE

AD0∼AD15

RD

WR

Interrupt fo

release

Data Data Address Address

STOP

mode

Figure 3.3.8 Timing Chart for STOP Mode Halt State Cleared by Interrupt

Table 3.3.6 Sample Warm-up Times after Clearance of STOP Mode

at f

SYSCR0

<RSYSCK>

0 (fc) 9.0 μs 0.607 ms 2.427 ms

1 (fs) 7.8 ms 500 ms 2000 ms

8

) 10 (214) 11 (216)

01 (2

SYSCR2<WUPTM1:0>

= 27 MHz, fs = 32.768 kHz

OSCH

91FY42-28 2006-11-08

TMP91FY42

• (Setting example)

• The STOP mode is entered when the low frequency operates, and high frequency operates

after releasing due to NMI.

Address

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

8FFDH LD (SYSCR1), 08H ; f

9000H LD (SYSCR2), −X1001X1B ; Sets warm-up time to 2

9002H LD (SYSCR0), 011000 − −B ; Operates high-frequency after released.

9005H HALT

9006H LD XX, XX RETI

NMI

SYS

= fs/2.

14

/f

.

OSCH

Clears and starts hit

warm-up timer

(High frequency)

End

NMI interrupts routine

• −: No change

91FY42-29 2006-11-08

TMP91FY42

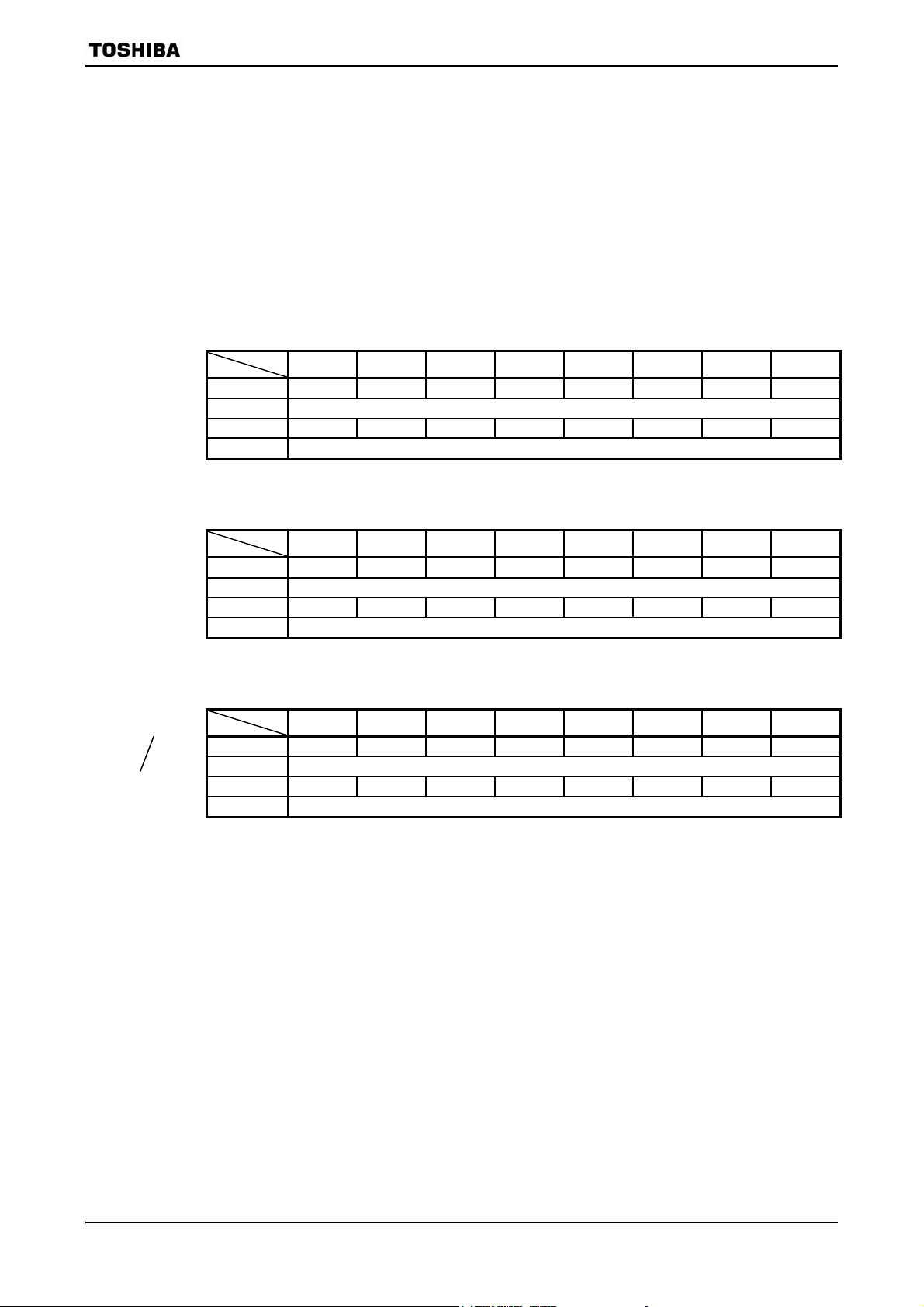

Table 3.3.7 Input buffer state table

Input Buffer State

When the CPU is

operating

When

Used as

function

Pin

ON upon

external

read

– – – –

ON

– – – –

ON ON ON

ON ON ON OFF

ON ON ON OFF

– – – –

ON

– –

ON ON ON ON

–

When

Used as

Input Port

ON

ON upon

port read

OFF

ON

–

,

Input

Function

Name

WAIT

BUSRQ

–

ADTRG

– – – – –

–

For

oscillator

For port OFF OFF

– ON – ON – ON –

During

Reset

OFF

OFF

ON

OFF

ON ON ON

0CTS

1CTS

OFF

ON

OFF

ON ON

Port

Name

P00-07 AD0-AD7

P10-17 AD8-AD15

P20-27 –

P32 –

P33

P34

P35-P37 – *1

P40-43 –

P50-52,

P54-57

P53

P60 SCK

P61 SDA

P62 SCL,SI

P63 INT0

P64-66 – – – – –

P70 TA0IN

P73 TA4IN

P71-72,

P74-75

P80 INT5,TB0IN0

P81 INT6,TB0IN1

P84 INT7,TB1IN0

P85 INT8,TB1IN1

P82-83,

P86-87

P90,P93 –

P91 RXD0

P92 SCLK0,

P94 RXD1

P95 SCLK1,

P96 XT1

P97 –

PA0 INT1

PA1 INT2

PA2 INT3

PA3 INT4

PA4-A7 –

,

NMI

RESET

AM0,AM1

In HALT mode

(IDLE2)

When

Used as

function

Pin

OFF OFF OFF

ON ON

ON

–

When

Used as

Input Port

OFF

ON ON

OFF OFF

OFF OFF

ON

OFF

When

Used as

function

Pin

OFF

OFF

In HALT mode (STOP)

<DRVE>=1 <DRVE>=0

When

Used as

function

Pin

OFF

ON *2

OFF

ON ON

OFF

–

–

When

Used as

Input Port

OFF

OFF

ON

–

–

When

Used as

Input Port

OFF

ON

ON

OFF

*1

*1

*1

*1

*2

X1 –

ON: The buffer is always turned on. A current flow

OFF: The buffer is always turned off. *2: AIN input does not cause a current to flow through the buffer.

–: No applicable

the input buffer if the input pin is not driven.

– – OFF – OFF –

*1: Port having a pull-up/pull-down resistor.

91FY42-30 2006-11-08

TMP91FY42

Table 3.3.8 Output buffer state table

Input Buffer State

Port

Name

P00-07 AD0-AD7

P10-17

P20-27

P30

P31

P32

P33-34,37 – – – – – *1

P35

P36 R/W *1

P40

P41

P42

P43

P60 SCK

P61 SDA,SO

P62 SCL

P63,65-66 – – – – –

P64 SCOUT ON ON ON OFF

P70,73 – – – – –

P71 TA1OUT

P72 TA3OUT

P74 TA5OUT

P75 TA7OUT

P80-81,

P84-85

P82 TB0OUT0

P83 TB0OUT1

P86 TB1OUT0

P87 TB1OUT1

P90 TXD0

P91,94 – – – – –

P92 SCLK0

P93 TXD1

P95 SCLK1

P96 – ON –

P97 XT2

PA0-A7 – –

ALE –

X2 – ON

Output

Function

Name

AD8-AD15

A8-A15

A0-A7

A16-A23

RD

WR

HWR

BUSAK

0CS

1CS

2CS

3CS

– – – – –

For

oscillator

For port ON OFF OFF

During

Reset

OFF

ON

*1

*1

*1

*1

*1

OFF

OFF ON OFF ON OFF OFF

OFF

ON: The buffer is always turned on. When the bus

When the CPU is

operating

When

Used as

function

Pin

ON upon

external

write

ON ON ON

ON ON ON OFF

ON ON ON OFF

ON ON ON OFF

ON ON ON OFF

ON

When

Used as

output

Port

ON

ON

– ON –

In HALT mode

(IDLE2)

When

Used as

function

Pin

OFF OFF

–

–

When

Used as

output

Port

ON

ON

When

Used as

function

Pin

OFF OFF

ON ON

Output “H”

level

*1: Port having a pull-up/pull-down resistor

In HALT mode (STOP)

<DRVE>=1 <DRVE>=0

–

–

When

Used as

output Port

ON

ON

–

When

Used as

function

Output “H”

Pin

OFF

–

–

level

When

Used as

output

Port

OFF

–

is released, however, output buffers for some

pins are turned off.

OFF: The buffer is always turned off.

–

: Not applicable

*1

91FY42-31 2006-11-08

3.4 Interrupts

Interrupts are controlled by the CPU interrupt mask register SR<IFF2:0> and by the built-

in interrupt controller.

The TMP91FY42 has a total of 45 interrupts divided into the following five types:

• Interrupts generated by CPU: 9 sources

(Software interrupts, illegal instruction interrupt)

• Internal interrupts: 26 sources

• Interrupts on external pins (

A (Fixed) individual interrupt vector number is assigned to each interrupt.

One of six (Variable) priority level can be assigned to each maskable interrupt.

The priority level of non-maskable interrupts are fixed at 7 as the highest level.

When an interrupt is generated, the interrupt controller sends the piority of that interrupt

to the CPU. If multiple interrupts are generated simultaneously, the interrupt controller

sends the interrupt with the highest priority to the CPU. (The highest priority is level 7 using

for non-maskable interrupts.)

The CPU compares the priority level of the interrupt with the value of the CPU interrupt

mask register <IFF2:0>. If the priority level of the interrupt is higher than the value of the

interrupt mask register, the CPU accepts the interrupt.

The interrupt mask register <IFF2:0> value can be updated using the value of the EI

instruction (EI num sets <IFF2:0> data to num).

TMP91FY42

NMI

and INT0 to INT8): 10 sources

For example, specifying EI 3 enables the maskable interrupts which priority level set in the

interrupt controller is 3 or higher, and also non-maskable interrupts.

Operationally, the DI instruction (<IFF2:0> = 7) is identical to the EI7 instruction. DI

instruction is used to disable maskable interrupts because of the priority level of maskable

interrupts is 1 to 6. The EI instruction is vaild immediately after execution.

In addition to the above general-purpose interrupt processing mode, TLCS-900/L1 has a

micro DMA interrupt processing mode as well. The CPU can transfer the data (1/2/4 bytes)

automatically in micro DMA mode, therefore this mode is used for speed-up interrupt

processing, such as transferring data to the internal or external peripheral I/O. Moreover,

TMP91FY42 has software start function for micro DMA processing request by the software

not by the hardware interrupt.

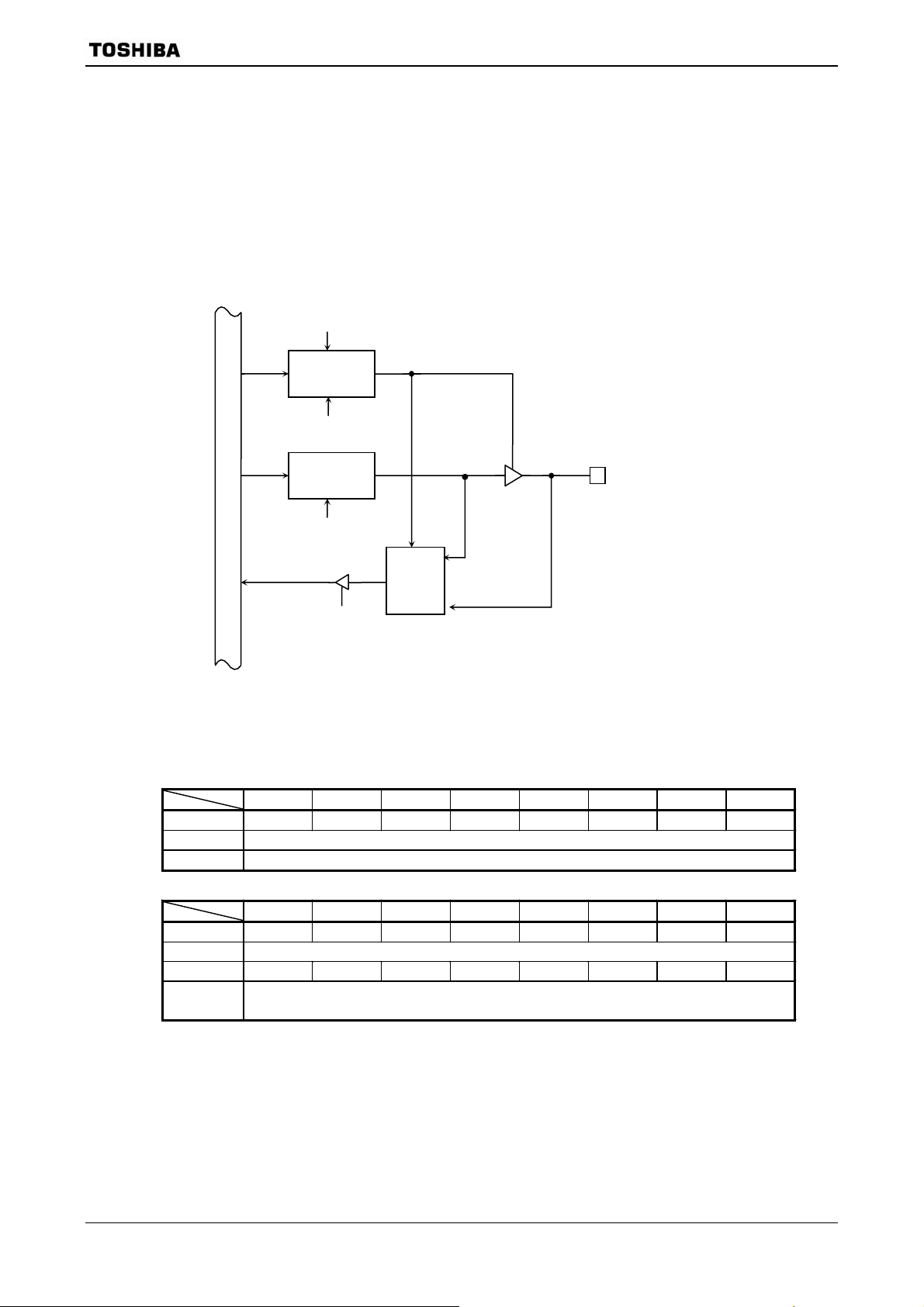

Figure 3.4.1 shows the overall interrupt processing flow.

91FY42-32 2006-11-08

General-purpose

interrupt

processing

Interrupt processing

Interrupt specified

by micro DMA

start vector?

No

Interrupt vector value V

read

Interrupt request F/F clear

PUSH PC

PUSH SR

SR<IFF2:0> ←

Level of

accepted

interrupt + 1

INTNEST ← INTNEST + 1

PC ← (FFFF00H + V)

Interrupt processing

program

RETI instruction

POP SR

POP PC

INTNEST ← INTNEST − 1

End

Yes

Clear interrupt request flag

TMP91FY42

Micro DMA soft start

request

Data transfer by

micro DMA

Count ← Count − 1

Count = 0

No

Micro DMA processing

Yes

Clear vector register

generating micro DMA

transfer and interrupt

(INTTC0 to INTTC3)

Figure 3.4.1 Overall Interrupt Processing Flow

91FY42-33 2006-11-08

3.4.1 General-purpose Interrupt Processing

When the CPU accepts an interrupt, it usually performs the following sequence of

operations. That is also the same as TLCS-900/L and TLCS-900/H.

(1) The CPU reads the interrupt vector from the interrupt controller.

If the same level interrupts occur simultaneously, the interrupt controller generates

an interrupt vector in accordance with the default priority and clears the interrupt

request.

(The default priority is already fixed for each interrupt: The smaller vector value has

the higher priority level.)

(2) The CPU pushes the value of program counter (PC) and status register (SR) onto the

stack area (Indicated by XSP).

(3) The CPU sets the value which is the priority level of the accepted interrupt plus 1

(+1) to the interrupt mask register <IFF2:0>. However, if the priority level of the

accepted interrupt is 7, the register’s value is set to 7.

(4) The CPU increases the interrupt nesting counter INTNEST by 1 (+1).

(5) The CPU jumps to the address indicated by the data at address FFFF00H + interrupt

vector and starts the interrupt processing routine.

(6) The above processing time is 18-states (1.33 μs at 27 MHz) as the best case (16 bits

data bus width and 0 waits).

When the CPU compled the interrupt processing, use the RETI instruction to

return to the main routine. RETI restores the contents of program counter (PC) and

status register (SR) from the stack and decreases the interrupt nesting counter

INTNEST by 1 (−1).

TMP91FY42

Non-maskable interrupts cannot be disabled by a user program. Maskable

interrupts, however, can be enabled or disabled by a user program. A program can set

the priority level for each interrupt source. (A priority level setting of 0 or 7 will

disable an interrupt request.)

If an interrupt request which has a priority level equal to or greater than the value

of the CPU interrupt mask register <IFF2:0> comes out, the CPU accepts its

interrupt. Then, the CPU interrupt mask register <IFF2:0> is set to the value of the

priority level for the accepted interrupt plus 1 (+1).

Therefore, if an interrupt is generated with a higher level than the current

interrupt during its processing, the CPU accepts the later interrupt and goes to the

nesting status of interrupt processing.

Moreover, if the CPU receives another interrupt request while performing the said

(1) to (5) processing steps of the current interrupt, the latest interrupt request is

sampled immediately after execution of the first instruction of the current interrupt

processing routine. Specifying DI as the start instruction disables maskable interrupt

nesting.

A reset initializes the interrupt mask register <IFF2:0> to 111, disabling all

maskable interrupts.

Table 3.4.1 shows the TMP91FY42 interrupt vectors and micro DMA start vectors.

The address FFFF00H to FFFFFFH (256 bytes) is assigned for the interrupt vector

area.

91FY42-34 2006-11-08

TMP91FY42

Table 3.4.1 TMP91FY42 Interrupt Vectors Table

Default

Priority

1 Reset or “SWI 0” instruction 0000H FFFF00H

2 “SWI 1” instruction 0004H FFFF04H

3 INTUNDEF: Illegal instruction or “SWI 2” instruction 0008H FFFF08H

4 “SWI 3” instruction 000CH FFFF0CH

5 “SWI 4” instruction 0010H FFFF10H

6 “SWI 5” instruction 0014H FFFF14H

7 “SWI 6” instruction 0018H FFFF18H

8 “SWI 7” instruction 001CH FFFF1CH

9

10

−

11 INT0 pin 0028H FFFF28H 0AH

12 INT1 pin 002CH FFFF2CH 0BH

13 INT2 pin 0030H FFFF30H 0CH

14 INT3 pin 0034H FFFF34H 0DH

15 INT4 pin 0038H FFFF38H 0EH

16 INT5pin 003CH FFFF3CH 0FH

17 INT6 pin 0040H FFFF40H 10H

18 INT7 pin 0044H FFFF44H 11H

19 INT8 pin 0048H FFFF48H 12H

20 INTTA0: 8-bit timer 0 004CH FFFF4CH 13H

21 INTTA1: 8-bit timer 1 0050H FFFF50H 14H

22 INTTA2: 8-bit timer 2 0054H FFFF54H 15H

23 INTTA3: 8-bit timer 3 0058H FFFF58H 16H

24 INTTA4: 8-bit timer 4 005CH FFFF5CH 17H

25 INTTA5: 8-bit timer 5 0060H FFFF60H 18H

26 INTTA6: 8-bit timer 6 0064H FFFF64H 19H

27 INTTA7: 8-bit timer 7 0068H FFFF68H 1AH

28 INTTB00: 16-bit timer 0 (TB0RG0) 006CH FFFF6CH 1BH

29 INTTB01: 16-bit timer 0 (TB0RG1) 0070H FFFF70H 1CH

30 INTTB10: 16-bit timer 1 (TB0RG0) 0074H FFFF74H 1DH

31 INTTB11: 16-bit timer 1 (TB0RG1) 0078H FFFF78H 1EH

32 INTTBOF0: 16-bit timer 0 (Over-flow) 007CH FFFF7CH 1FH

33 INTTBOF1: 16-bit timer 1 (Over-flow) 0080H FFFF80H 20H

34 INTRX0: Serial reception (Channel 0) 0084H FFFF84H 21H

35 INTTX0: Serial transmission (Channel 0) 0088H FFFF88H 22H

36 INTRX1: Serial reception (Channel 1) 008CH FFFF8CH 23H

37 INTTX1: Serial transmission (Channel 1) 0090H FFFF90H 24H

38 INTSBI: SBI interrupt 0094H FFFF94H 25H

39 INTRTC: Special timer for clock 0098H FFFF98H 26H

40 INTAD: AD conversion end 009CH FFFF9CH 27H

41 INTTC0: Micro DMA end (Channel 0) 00A0H FFFFA0H

42 INTTC1: Micro DMA end (Channel 1) 00A4H FFFFA4H

43 INTTC2: Micro DMA end (Channel 2) 00A8H FFFFA8H

44 INTTC3: Micro DMA end (Channel 3) 00ACH FFFFACH

Type

Non maskable

Maskable

Interrupt Source and Source of Micro DMA

Request

NMI

pin

INTWD: Watchdog timer 0024H FFFF24H

Micro DMA (MDMA)

(Reserved)

:

(Reserved)

Vector

Value (V)

0020H FFFF20H

− − −

00B0H

:

00FCH

Vector

Reference

Address

FFFFB0H

:

FFFFFCH

Micro DMA

Start Vector

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

:

−

91FY42-35 2006-11-08

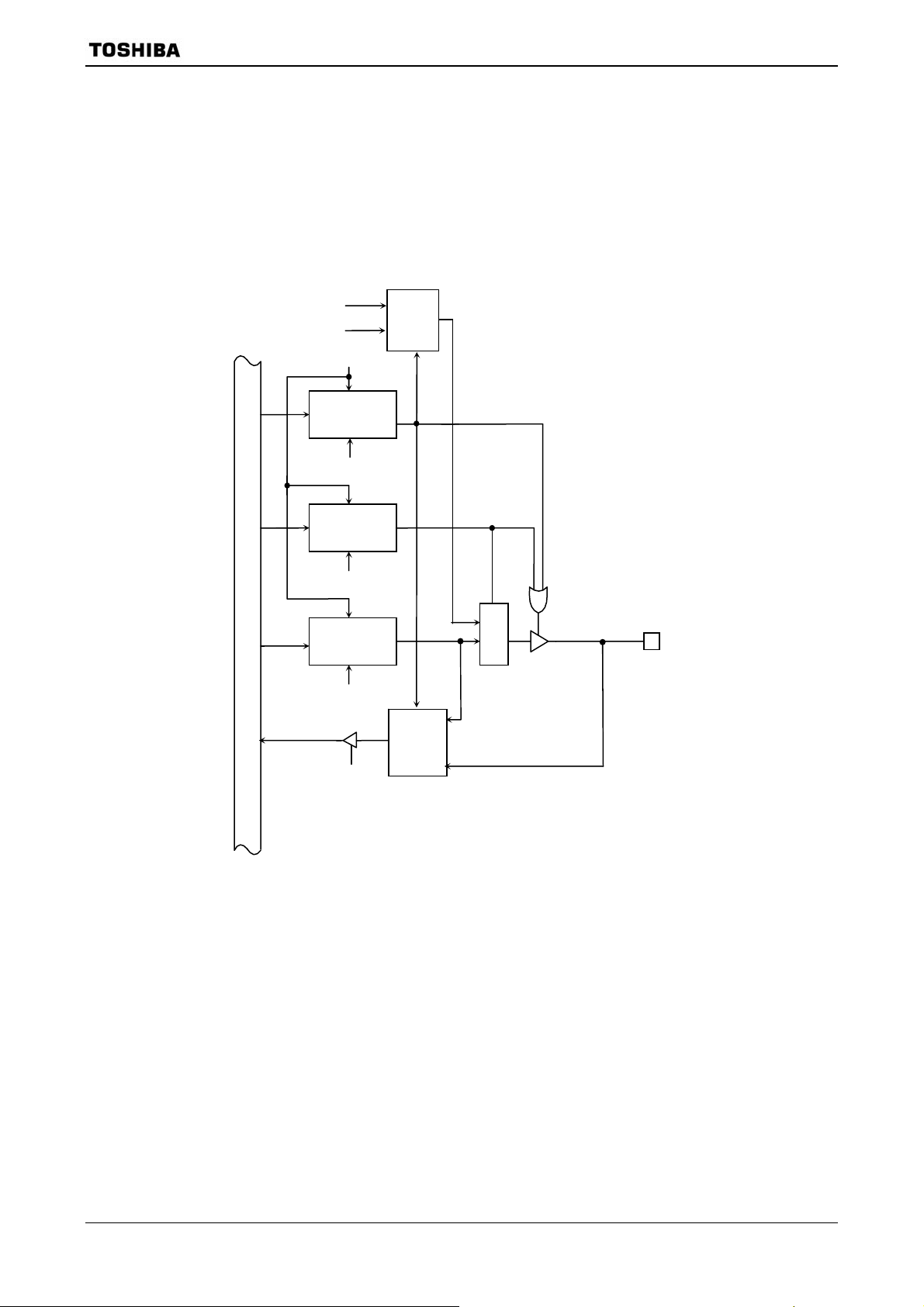

3.4.2 Micro DMA Processing

In addition to general-purpose interrupt processing, the TMP91FY42 supprots a micro

DMA function. Interrupt requests set by micro DMA perform micro DMA processing at

the highest priority level (Level 6) among maskable interrupts, regardless of the priority

level of the particular interrupt source. Micro. The micro DMA has 4 channels and is

possible continuous transmission by specifing the say later burst mode.

Because the micro DMA function has been implemented with the cooperative operation

of CPU, when CPU goes to a standby mode by HALT instruction, the requirement of

micro DMA will be ignored (Pending).

(1) Micro DMA operation

When an interrupt request specified by the micro DMA start vector register is

generated, the micro DMA triggers a micro DMA request to the CPU at interrupt

priority level 6 and starts processing the request in spite of any interrupt source’s

level. The micro DMA is ignored on <IFF2:0> = 7.

The 4 micro DMA channels allow micro DMA processing to be set for up to 4 types

of interrupts at any one time. When micro DMA is accepted, the interrupt request

flip-flop assigned to that channel is cleared.

The data are automatically transferred once (1/2/4 bytes) from the transfer source

address to the transfer destination address set in the control register, and the

transfer counter is decreased by 1 (−1).

If the decreased result is 0, the micro DMA transfer end interrupt (INTTC0 to

INTTC3) passes from the CPU to the interrupt controller. In addition, the micro DMA

start vector register DMAnV is cleared to 0, the next micro DMA is disabled and

micro DMA processing completes. If the decreased result is other than 0, the micro

DMA processing completes if it isn’t specified the say later burst mode. In this case,

the micro DMA transfer end interrupt (INTTC0 to INTTC3) aren’t generated.

If an interrupt request is triggered for the interrupt source in use during the

interval between the clearing of the micro DMA start vector and the next setting,

general-purpose interrupt processing executes at the interrupt level set. Therefore, if

only using the interrupt for starting the micro DMA (Not using the interrupts as a

general-purpose interrupt: Level 1 to 6), first set the interrupt level to 0 (Interrupt

requests disabled).

If using micro DMA and general-purpose interrupts together, first set the level of

the interrupt used to start micro DMA processing lower than all the other interrupt

levels. In this case, the cause of general interrupt is limited to the edge interrupt.

(Note)

TMP91FY42

The priority of the micro DMA transfer end interrupt (INTTC0 to INTTC3) is

defined by the interrupt level and the default priority as the same as the other

maskable interrupt.

Note: If the priority level of micro DMA is set higher than that of other interrupts, CPU operates as follows.

In case INTxxx interrupt is generated first and then INTyyy interrupt is generated between checking

“Interrupt specified by micro DMA start vector” (in the

setting below. The vector shifts to that of INTyyy at the time.

This is because the priority level of INTyyy is higher than that of INTxxx.

In the interrupt routine, CPU reads the vector of INTyyy because cheking of micro DMA has finished.

And INTyyy is generated regardless of transfer counter of micro DMA.

INTxxx: level 1 without micro DMA

INTyyy: level 6 with micro DMA

Figure 3.4.1) and reading interrupt vector with

91FY42-36 2006-11-08

TMP91FY42

If a micro DMA request is set for more than one channel at the same time, the

priority is not based on the interrupt priority level but on the channel number. The

smaller channel number has the higher priority (Channel 0 (High) > Channel 3 (Low)).

While the register for setting the transfer source/transfer destination addresses is a

32-bit control register, this register can only effectively output 24-bit addresses.

Accordingly, micro DMA can access 16 Mbytes (The upper 8 bits of the 32 bits are not

valid).

Three micro DMA transfer modes are supported: 1-byte transfer, 2-byte (One word)

transfer, and 4-byte transfer. After a transfer in any mode, the transfer

source/destination addresses are increased, decreased, or remain unchanged.

This simplifies the transfer of data from I/O to memory, from memory to I/O, and

from I/O to I/O. For details of the transfer modes, see 3.4.2 (4) “Detailed description of

the transfer mode register”. As the transfer counter is a 16-bit counter, micro DMA

processing can be set for up to 65536 times per interrupt source. (The micro DMA

processing count is maximized when the transfer counter initial value is set to

0000H.)

Micro DMA processing can be started by the 30 interrupts shown in the micro DMA

start vectors of

Table 3.4.1 and by the micro DMA soft start, making a total of 31

interrupts.

Figure 3.4.2 shows the word transfer micro DMA cycle in transfer destination

address INC mode (except for counter mode, the same as for other modes).

(The conditions for this cycle are based on an external 16-bit bus, 0 waits, transfer

source/transfer destination addresses both even-numberd values.)

A0 to A23

RD

1 state

DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8

X1

(Note 1) (Note 2)

Transfer source address

Transfer destination

address

WR /HWR

D0 to D15

Output Input

Figure 3.4.2 Timing for Micro DMA Cycle

States 1 to 3: Instruction fetch cycle (gets next address code).

If 3 bytes and more instruction codes are inserted in the instruction queue buffer, this cycle

becomes a dummy cycle.

States 4 to 5: Micro DMA read cycle

State 6: Dummy cycle (The address bus remains un changed from state 5)

States 7 to 8: Micro DMA write cycle

Note 1: If the source address area is an 8-bit bus, it is increased by two states.

If the source address area is a 16-bit bus and the address starts from an odd number, it is increased by

two states.

Note 2: If the destination address area is an 8-bit bus, it is increased by two states.

If the destination address area is a 16-bit bus and the address starts from an odd number, it is increased

by two states.

91FY42-37 2006-11-08

TMP91FY42

(2) Soft start function

In addition to starting the micro DMA function by interrupts, TMP91FY42 includes

a micro DMA software start function that starts micro DMA on the generation of the

write cycle to the DMAR register.

Writing “1” to each bit of DMAR register causes micro DMA once (If write “0” to

each bit, micro DMA doesn’t operate). At the end of transfer, the corresponding bit of

the DMAR register which support the end channel are automatically cleared to “0”.

Only one-channel can be set for DMA request at once. (Do not write “1” to plural

bits.)

When writing again “1” to the DMAR register, check whether the bit is “0” before

writing “1”. If read “1”, micro DMA transfer isn’t started yet.

When a burst is specified by DMAB register, data is continuously transferred until

the value in the micro DMA transfer counter is “0” after start up of the micro DMA. If

execute soft start during micro DMA transfer by interrupt source, micro DMA

transfer counter doesn’t change. Don’t use Read-modify-write instruction to avoid

writing to other bits by mistake.

Symbol Name Address 7 6 5 4 3 2 1 0

DMAR3 DMAR2 DMAR1 DMAR0

R/W

0 0 0 0

DMA request

DMAR

DMA

request

register

89H

(Prohibit

RMW)

(3) Transfer control registers

The transfer source address and the transfer destination address are set in the

following registers in CPU. Data setting for these registers is done by an LDC cr, r

instruction.

Channel 0

DMAS0 DMA source address register 0 : Only use LSB 24 bits

DMAD0 DMA destination address register 0 : Only use LSB 24 bits

DMAC0 DMA counter register 0 : 1 to 65536

DMAM0 DMA mode register 0

Channel 3

DMAS3 DMA source address register 3

DMAD3 DMA destination address register 3

DMAC3 DMA counter register 3

DMAM3 DMA mode register 3

32 bits

8 bits

16 bits

91FY42-38 2006-11-08

DMAM0 to

DMAM3

(4) Detailed description of the transfer mode register

8 bits

0 0 0 Mode

Note: When setting a value in this register, write 0 to the upper 3 bits.

TMP91FY42

000

000 00 Byte transfer 8 states 593 ns

(Fixed)

01 Word transfer 12 states 889 ns

10 4-byte transfer

001 00 Byte transfer 8 states 593 ns

01 Word transfer 12 states 889 ns

10 4-byte transfer

010 00 Byte transfer 8 states 593 ns

01 Word transfer 12 states 889 ns

10 4-byte transfer

011 00 Byte transfer 8 states 593 ns

01 Word transfer 12 states 889 ns

10 4-byte transfer

100 00 Byte transfer 8 states 593 ns

01 Word transfer 12 states 889 ns

10 4-byte transfer

101 00 Counter mode

Number of

Transfer Bytes

Transfer destination address INC mode

............................................. I/O to memory

(DMADn+) ← (DMASn)

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

Transfer destination address DEC mode

............................................. I/O to memory

(DMADn−) ← (DMASn)

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

Transfer source address INC mode

............................................. Memory to I/O

(DMADn) ← (DMASn+)

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

Transfer source address DEC mode

............................................. Memory to I/O

(DMADn) ← (DMASn−)

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

Fixed address mode

...................................................... I/O to I/O

(DMADn) ← (DMASn−)

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

................... for counting number of times interrupt is generated

DMASn ← DMASn + 1

DMACn ← DMACn − 1

If DMACn = 0, then INTTCn is generated.

Mode Description

Number of

Execution States

5 states 370 ns

Minimum

Execution Time

at fc = 27 MHz