Toshiba Perugia 10M Diagram

Perugia 10M

MP Build(A03)

2009.05.05

DATE CHANGE NO.

REV

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE =

FILE NAME :

P/N

XXXXXXXXXXXX

EE

3

XXXX-XXXXXX-XX

DATE

POWER

VER :

DATE

INVENTEC

TITLE

Perugia10M

CODE

SIZE

A3

DOC. NUMBER REV

1310A2250501 x01

CS

SHEET

OF

631

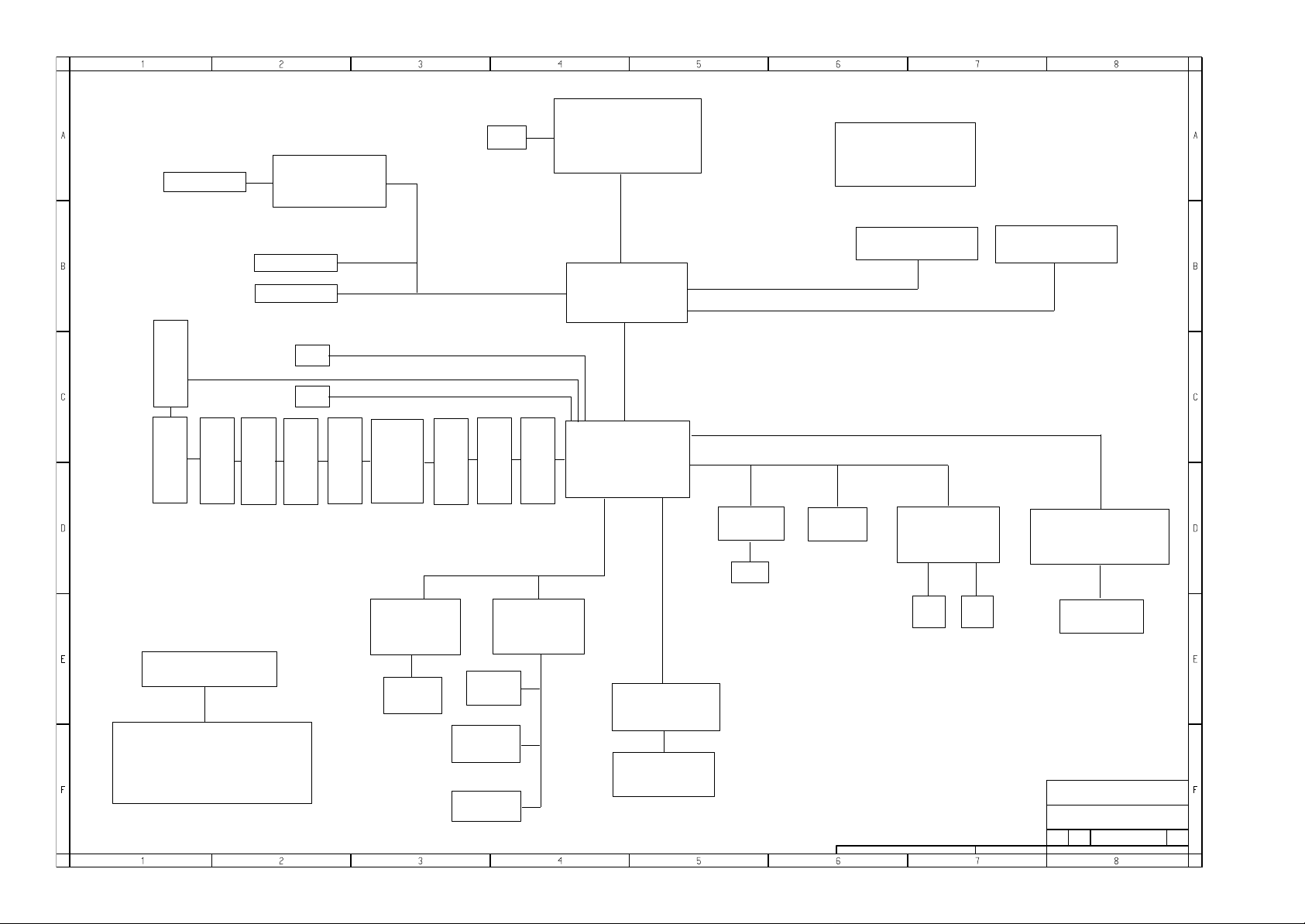

TABLE OF CONTENTS

PAGE

1.COVER PAGE

2.INDEX

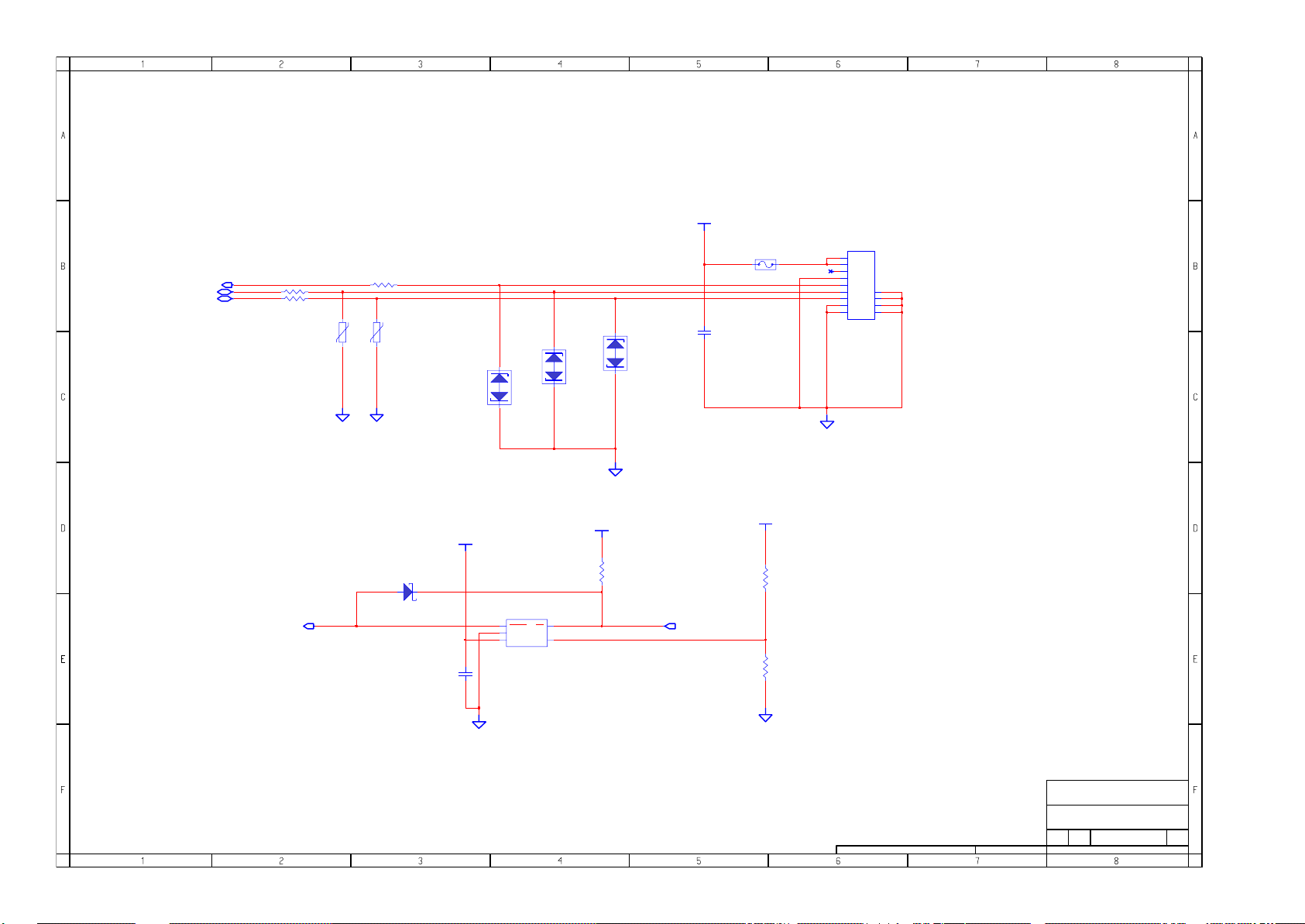

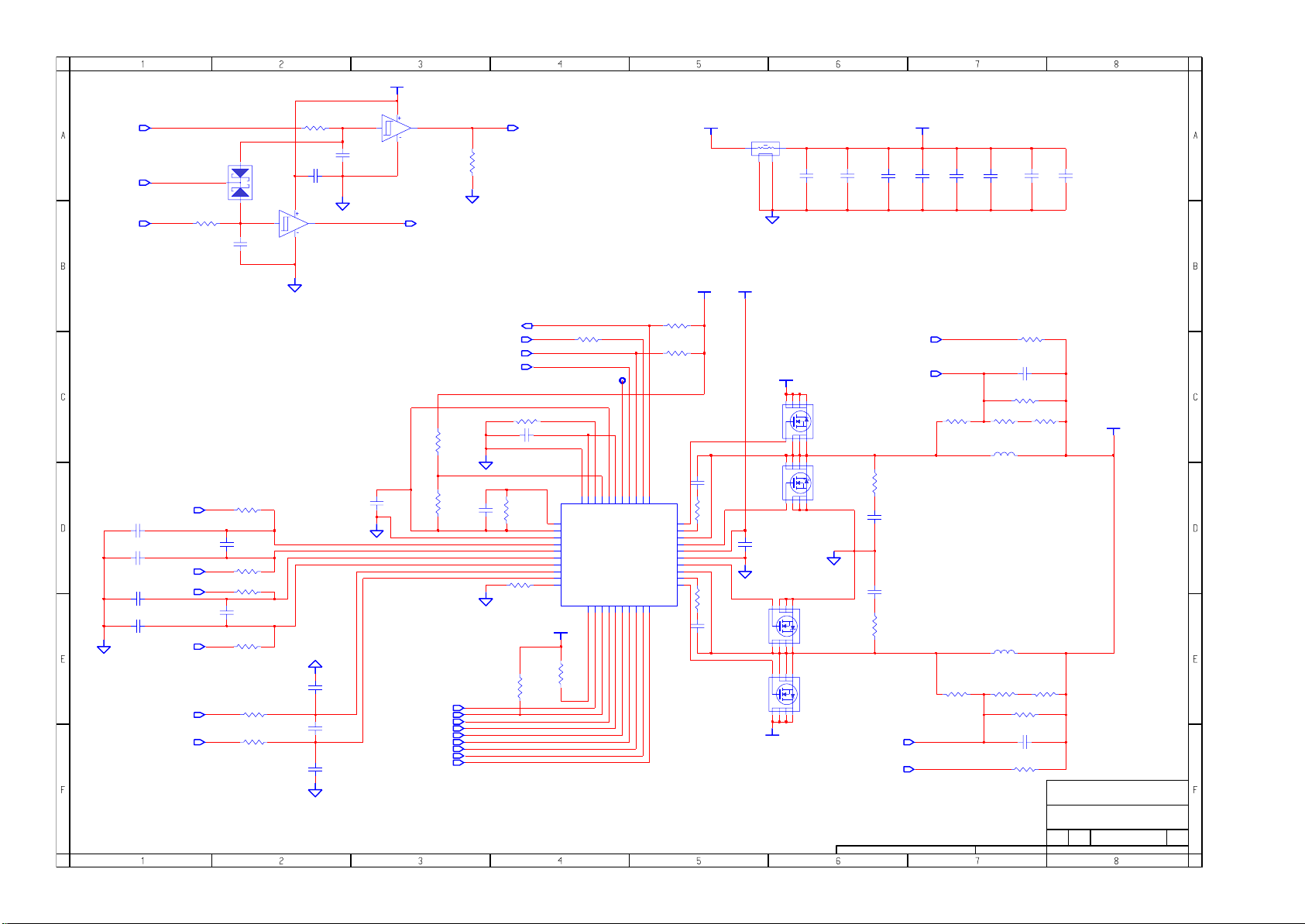

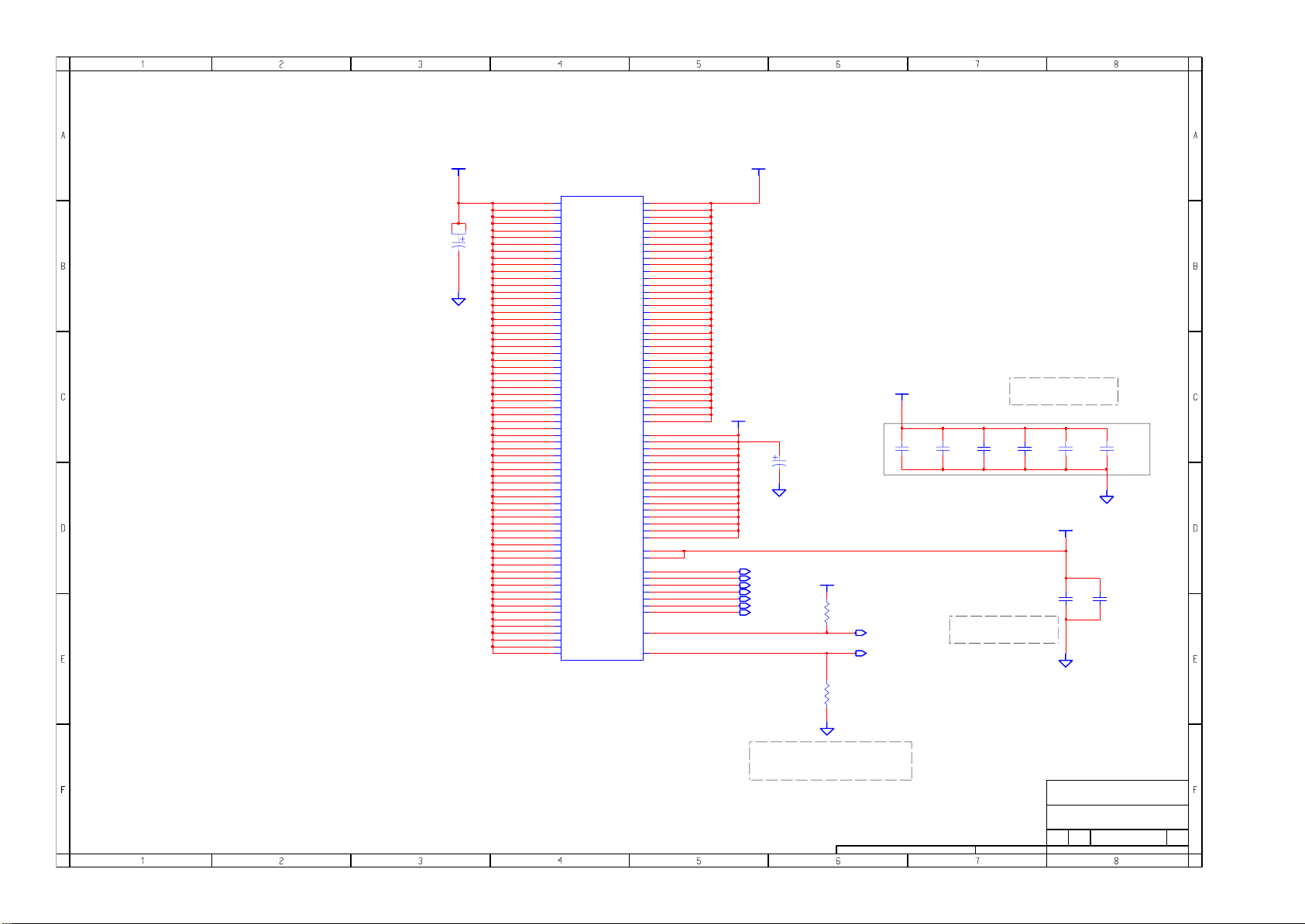

3.BLOCK DIAGRAM

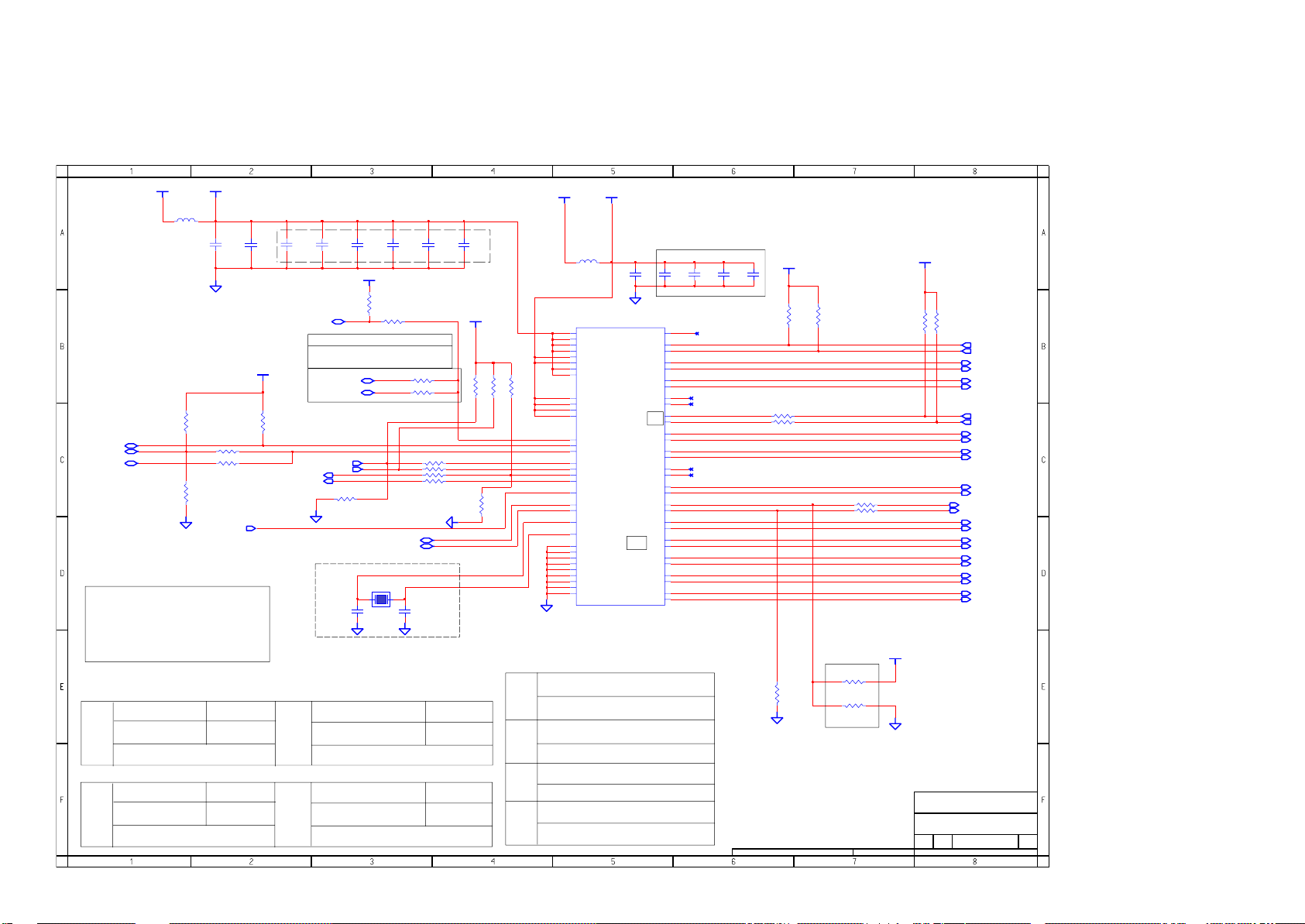

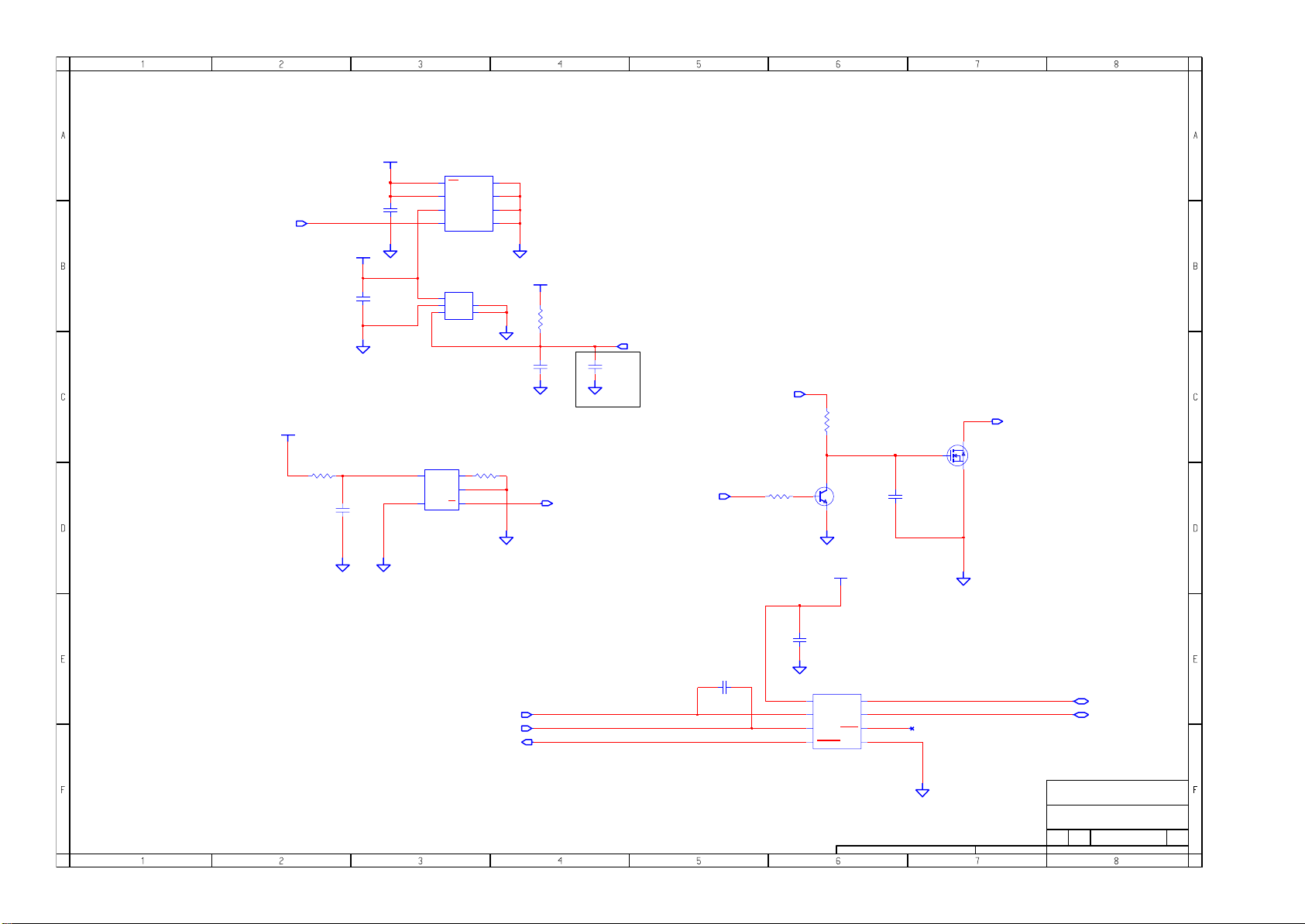

4.POWER SEQUENCE BLOCK

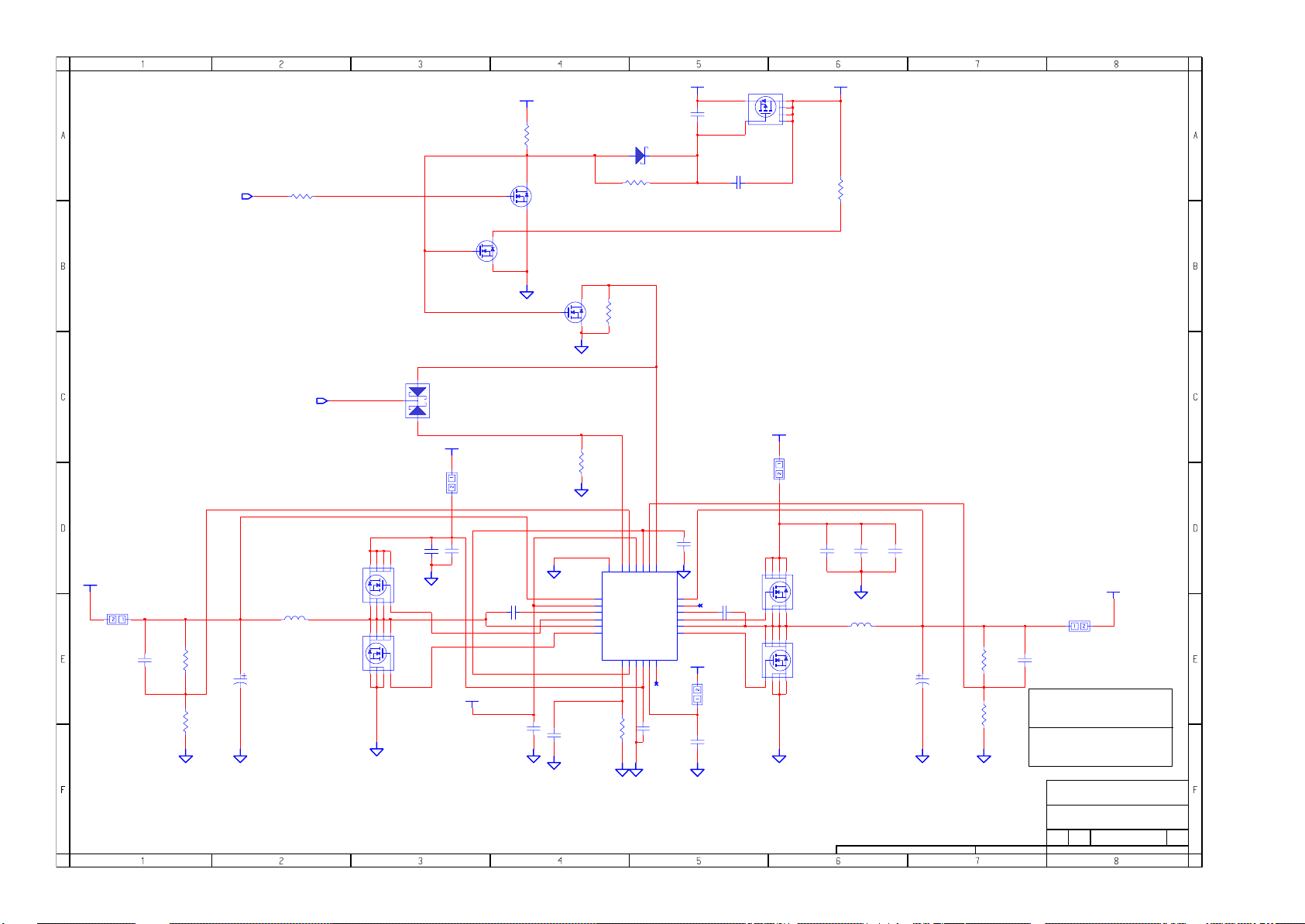

5-12.SYSTEM POWER

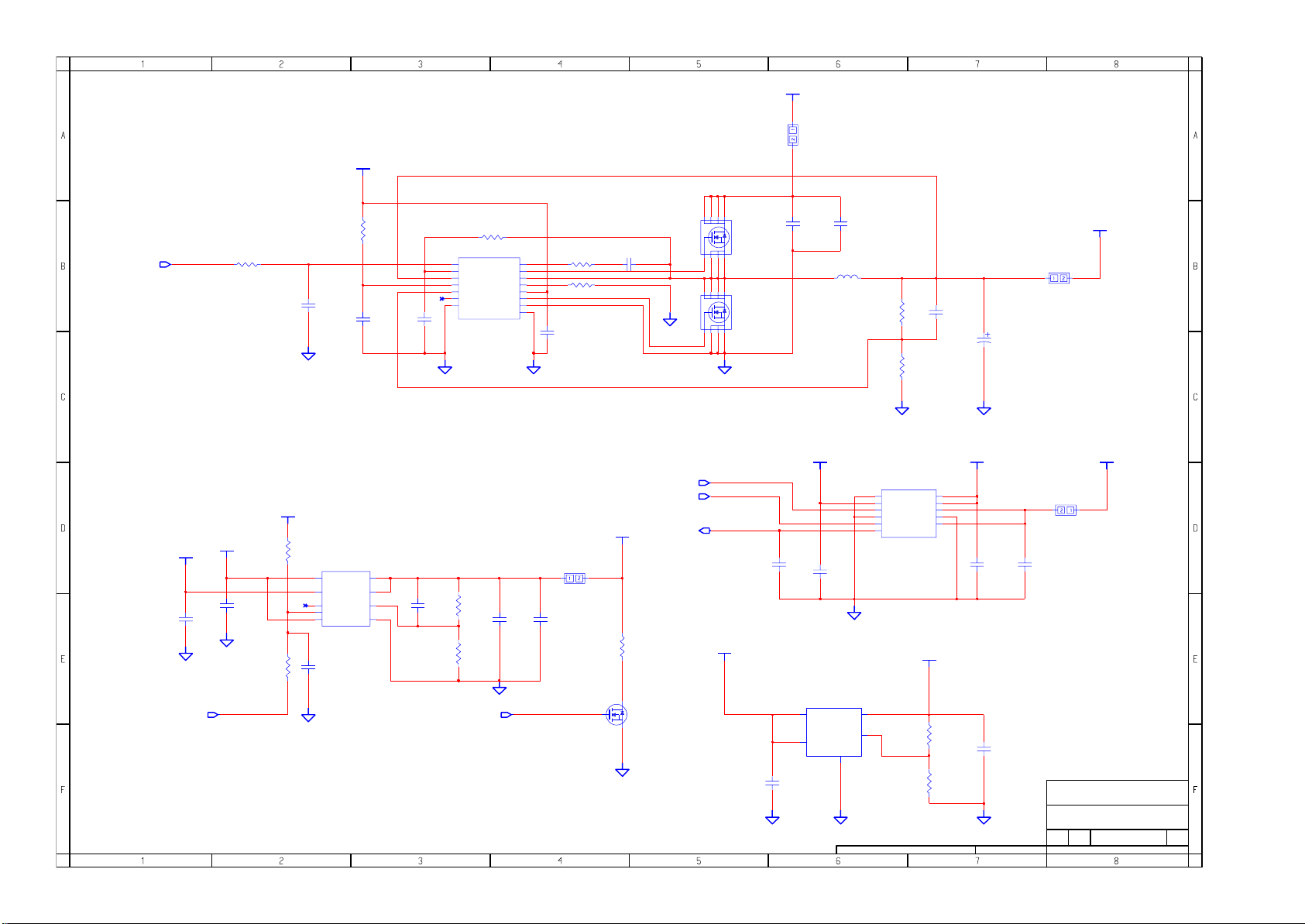

13.CLOCK GENERATOR

14.PENRYN-1

15.PENRYN-2

16.PENRYN-3

17.PENRYN-4

18.FAN & THERMAL CONTROLLER

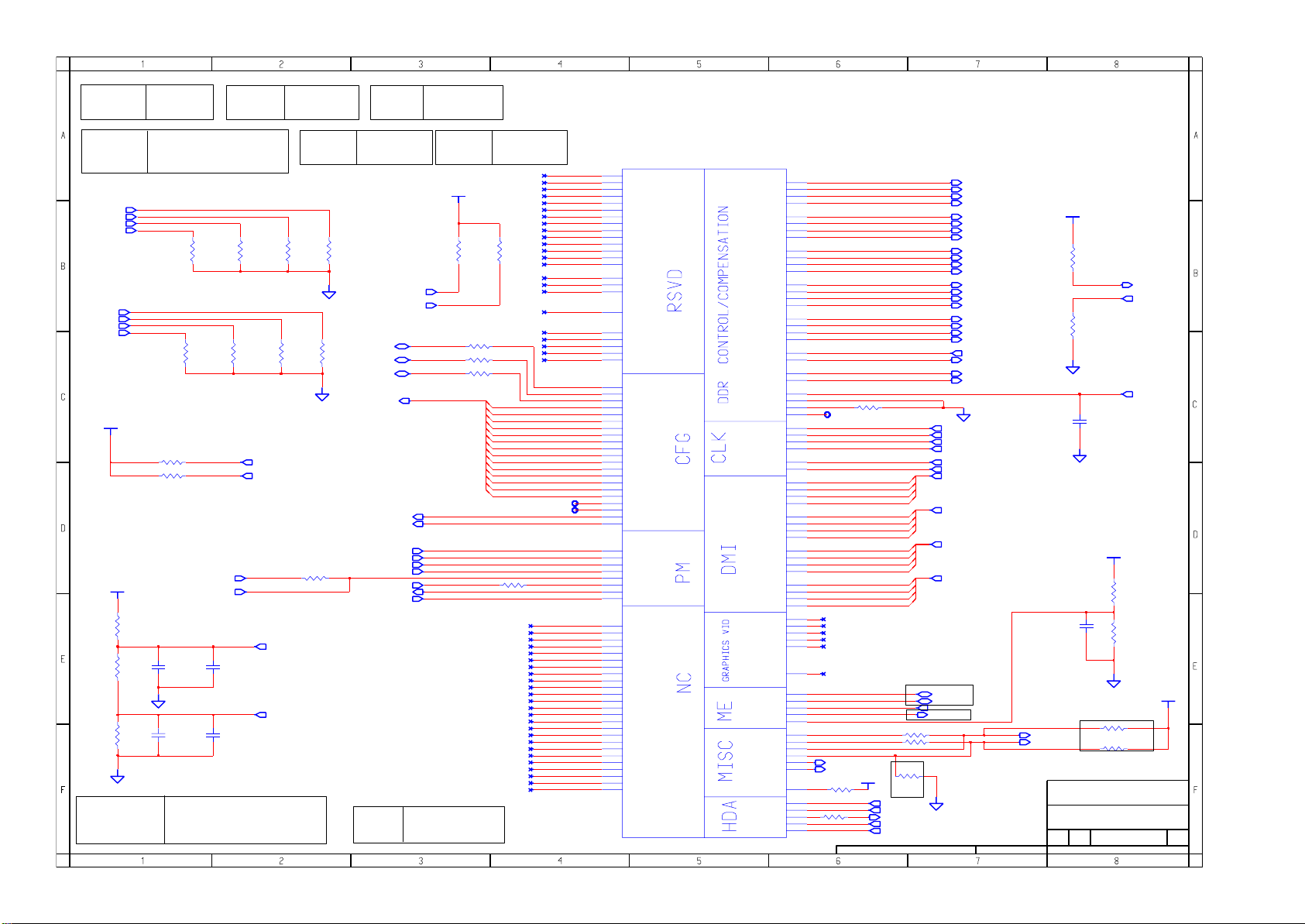

19.CANTIGA-1

20.CANTIGA-2

21.CANTIGA-3

22.CANTIGA-4

23.CANTIGA-5

24.CANTIGA-6

25.CANTIGA-7

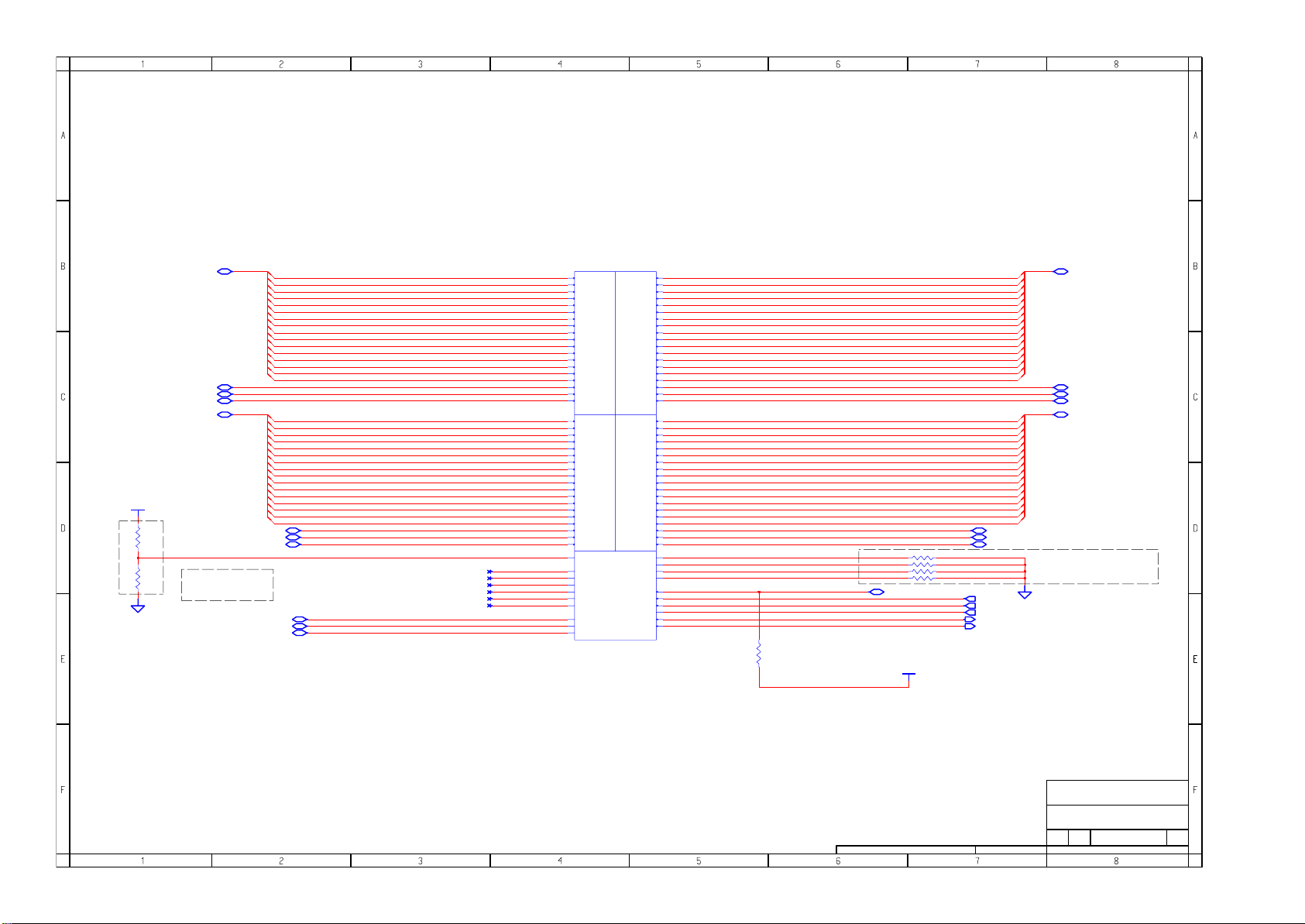

26.DDR2 DIMM0

27.DDR2 DIMM1

28.DDR DAMPING

29.CRT CONN

30.LCM CONN

PAGE

31.ICH9-1

32.ICH9-2

33.ICH9-3

34.ICH9-4

35.ICH9-5

36.SATA HDD CONN

37.ODD CONN

38.USB CONN

39.ESATA CONN

40.Camera

41.BLUE TOOTH CONN

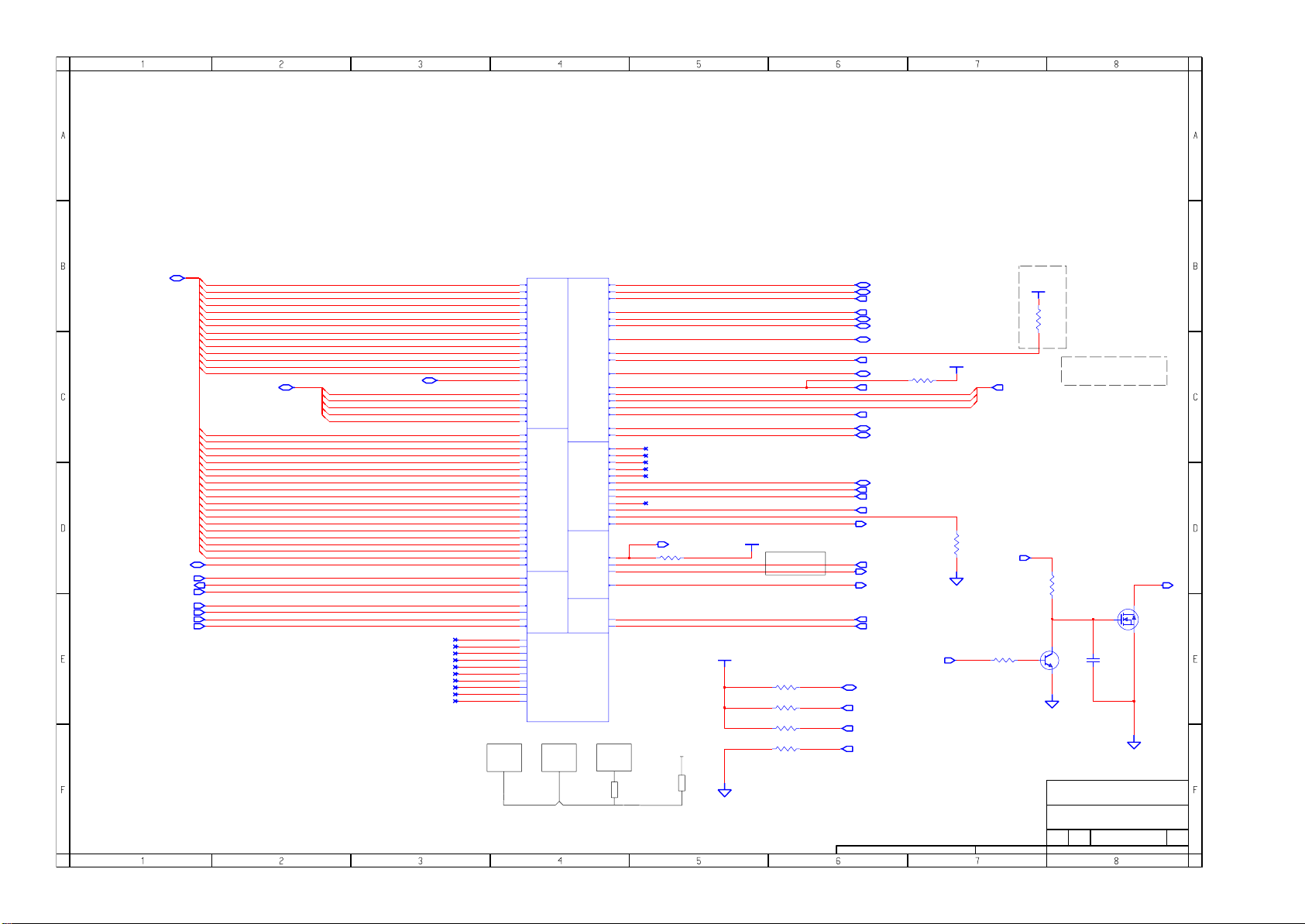

42.KBC

43.K/B & TP/B CONN

44.Audio Codec

45.Audio AMP/MIC/Speaker

46.LAN CONTROLLER

47.RJ45 & TRANSFORMER

48.HDMI & CEC

49.HDMI CONN

50.USB Card Reader

51.Card Bus-1

52.Card Bus-2

53.Express Card

PAGE

54.WLAN /Debug

55.MDC 1.5 CONN

56.LED(M/B) & HOTKEY/B CONN

57.KILL SWITCH& HALL SENSOR

58.Screw

59.EMI

60.3D sensor

61. Hotkey board

62. Touch pad board

63. power board

CHANGE by

Loren

24-Mar-2009

INVENTEC

TITLE

Perugia10M

CODE

SIZE

A3

DOC. NUMBER

1310A2250501 x01

CS

SHEET

REV

OF

632

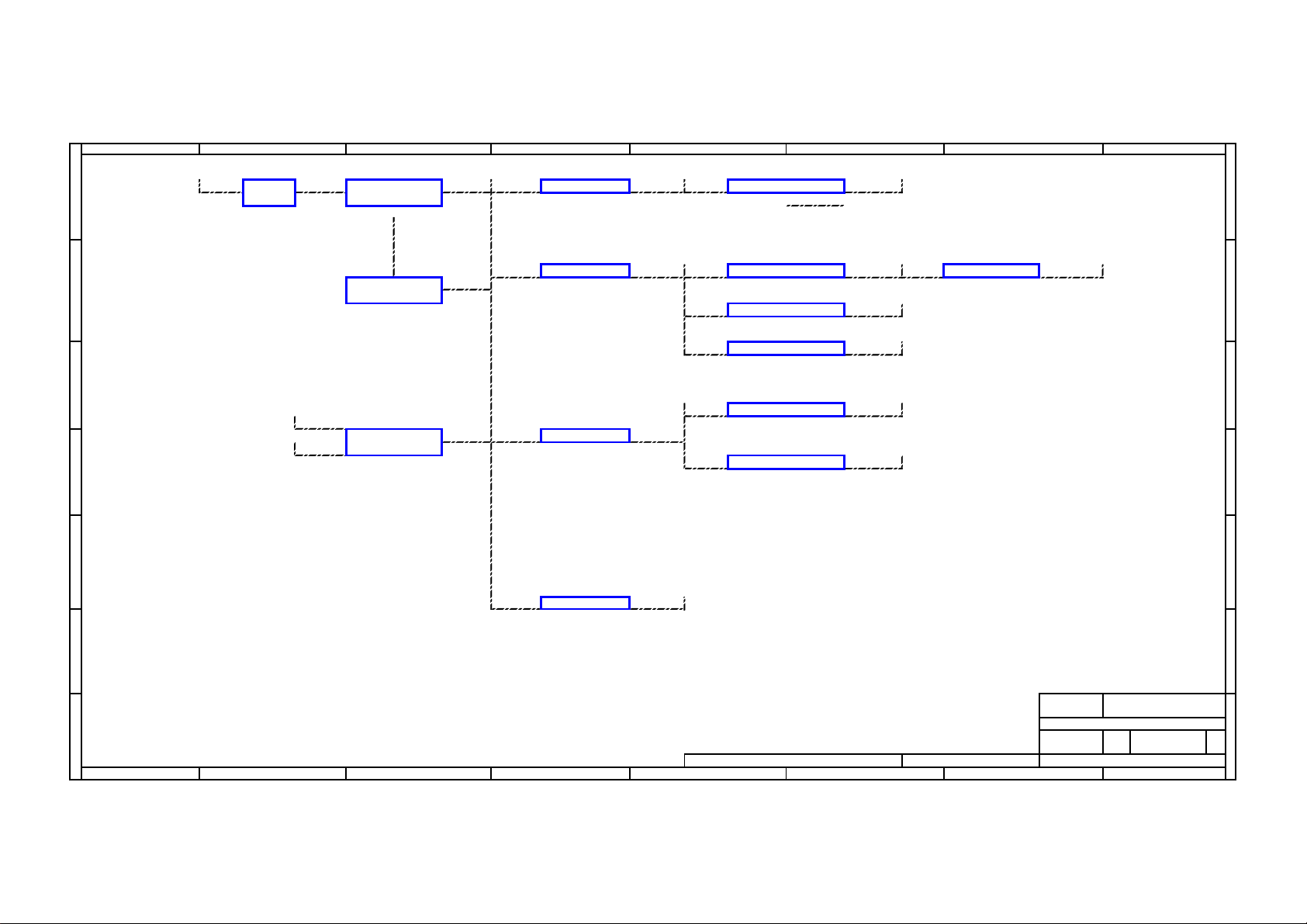

HDMI CONN

PTN3360A

Level shifter

LCM

CRT

XDP

Penryn

(uFCPGA)

Socket P

FSB

677/800/1067

Cantiga

DDR2 Interface

DDR2 Interface

Clock generator

SLG8SP510T

DDR II _SODIMM0

667 MHz/ 800 MHz

DDR II _SODIMM1

667 MHz/ 800 MHz

+ eSATA

CONN

USB1

CONN

USB0

CONN

USB2

CONN

USB3

BATTERY

System Charger &

DC/DC System power

(IMVP-6

VR)

HDD

ODD

USB4

NEW Card

WLAN

USB5

USB6

MDC / Modem

Module 56K

Bluetooth

RJ11

SATA_1

SATA_4

SATA_5

USB7

CAMERA

JACK

SPEAKER

HP JACK

USB8

RESERVE

3.3V, AZALIA

Realtek

ALC 272

MIC

USB9

RESERVE

DMI

ICH9-M

WINBOND

NPCE781LA0DX

SPI EEROM

Realtek

RTL8103E

RJ45

3.3V, LPC_Interface,33MHz

BIOS

3.3V, PCI_Interface,33MHz

EXPRESS

CARD

CHANGE by

MINI CARD

Wireless LAN

ANT

Loren

ANT

15-Apr-2009

CARD BUS

RICOH_R5C804

PCMCIA

INVENTEC

TITLE

Perugia10M

SIZE

A3

DOC. NUMBER

CODE

1310A2250501 x01

CS

SHEET

REV

OF

633

12

3

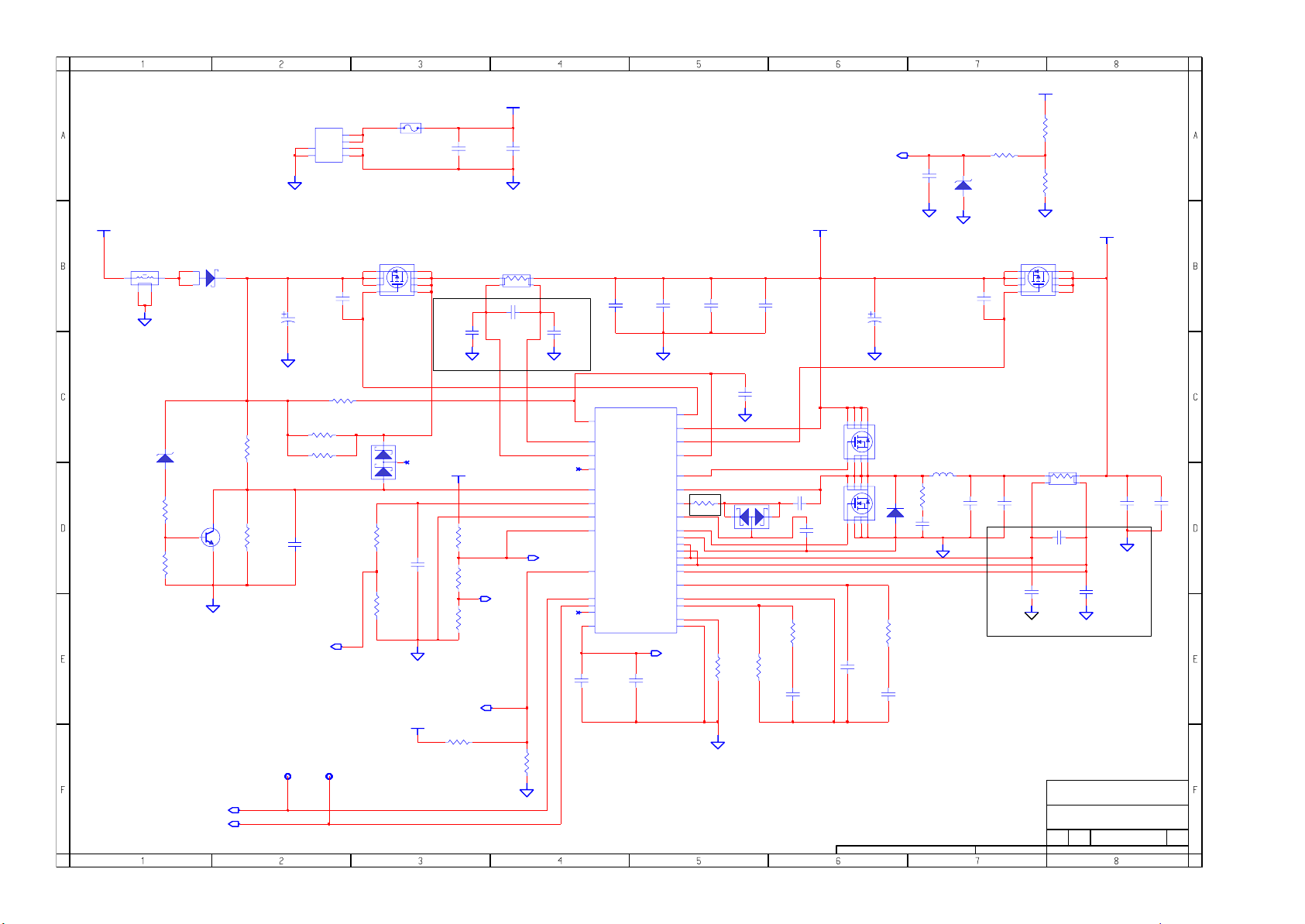

Adaptor +VBAT

A

GM 8A 6036A0003401 Charge current 3A/1.5A/512mA F 300K

PM 12A 6036A0006001 Charge voltage 12.6V OCP 7.42A R=120K

FUSE

P.5 P.5 P.12

EC_SMB2 Peak 6.10A Avg 4.31A

CHG_EN 330uF_25mΩ // 108.5uF_0.8mΩ

BATT_IN

ACPRES P.7 P.8

B

C

+VCORE_+-1.5%

+VCORE1_+-1.5%

D

BQ24721C

Charger

Battery Pack

TI_51620

Power budget 57A F 300K P.9

F 280K OCP 9.53A R=13K

OCP 60.87A R=10K Peak 7.48A Avg7.27A

peak 57A Avg 30.629A 330uF_14mΩ // 542uF_0.8mΩ

900uF_1.5mΩ

P.6 Power budget 11.487A

P.12

4

TPS51125_ 5V

P.7

Power budget 10.164A

TPS51125_ V3.3LA

P.7

F 375K

OCP 7.85A R=130K P.12

Peak 6.89A Avg 1.77A

330uF_25mΩ // 21.9uF_3.1mΩ

TSP51117_ 1.8V

P.9

Power budget 10.688A

56

+V5A_+-5%

+V5S

L/S AM3423

Power budget 3.802A Inrush 1.28A

Peak 2.67A 145.1uF_1.7mΩ

+V3LA_+-5%

V1.8_+-5%

L/S AM3423

Power budget 0.598A Inrush 0.51A Power budget0. 399A Inrush 0.53A

Peak 0.42A 0.7uF_14.9mΩ Peak 0.24A 10.4uF_6.7mΩ

L/S AM3423

Power budget0.35A Inrush 0.336A

Peak 0.25A 131.1uF_2.7mΩ

L/S AM3423

Power budget 10.229A Inrush 1.3A

Peak 7.16A 293.9uF_0.3mΩ

APL5930

Power budget 3.384A

Peak 2.37A 432.9uF_0.5mΩ

+V3A +V3A_LAN

+V3

+V3S

P.12

+V1.5S

P.9

+V0.9

G2997 F6U

Power budget 0.9A

Peak 0.63A 3.4uF_3.1mΩ

7

L/S AM3423

8

A

B

C

D

E

TSP51117_VCC_NB

Power budget 17.324A

Changing Points~~All PWM as same Minneapolis 10 OCP 13.76A R=10K

F

Power budget ~~IC Spec (max current )

Peak current ~~Ratio of Internal prediction

G

Avg current ~~test result(max current)

Inrush ~~L/S turn no

F 300K

Peak 12.13A Avg 8.64A

330uF_14mΩ // 1230.2uF_0.5mΩ

+VCCP_+-5%

P.11

CHANGE by Loren Huang 14-Feb-2009

56 812 3 4

E

F

TITLE

Power Sequence Block

SIAE A3

P

erugia10M

CODECSDOC.NUMBER

1310A2250501

REV

F

A

SHEET 4 OF 70

7

CN6000

1

1

2

2

3

G

G1

3

4

G2

G

4

ACES_91302_0047L_1_4P

FUSE6000

12

8A_125V

C6004

1

10pF_50V

2

+VADPTR

5-

1

2

C6003

0.1uF_50V

HW_V_ADC

C6032

0.1uF_10V

+VBAT

5-,6-,7-,8-,9-,11-,30-,59-

1

R6024

174K_1%

R6005

1

D6005

RLZ3.0B_OPEN2

12

33_5%

For ESD

42-

1

2

2

1

R6026

13.3K_1%

2

+VADPTR

5-

NFM60R30T222

ROHM_RLZ24

L6000

12

34

D600121

1

R6013

1K_5%

2

1

MMBT3904

R6016

10K_5%

2

EC_SMB2_CLK

EC_SMB2_DATA

D6000

1

2

PDS1040S

1

B

Q6004

3

R6009

432K_1%

3

C

E

2

18-,42-

18-,42-

C6002

47uF_35v

1

2

1

R6010

33K_1%

2

0.01uF_50v

1

2

12

4.7K_5%

12

4.7K_5%

C6015

1

2

0402_OPEN

ACPRES

TP27

C6006

1

2

R6015

12

0_5%

R6002

R6008

D6004

BAT54S_30V_0.2A

42-

TP28

Q6001

AM4825P_AP

1

S

2

3

4

G

2

3

1

1

R6021

47K_5%

2

C6018

1uF_10v

1

R6022

100K_5%

2

8

D

7

6

5

1

2

+V5LA

5-,6-,7-,12-,18-,39-,49-

C6013

0.1uF_25V

+V5LA

1

2

1

2

1

2

CHG_EN

R6006

1

100K_5%

C6014

0.1uF_25V

1

2

5-,6-,7-,12-,18-,39-,49-

R6018

8.06K_1%

R6019

39.2K_1%

42-

BATT_IN

R6020

22.6K_1%

42-

2

200K_5%

R6001

12

34

0.01_1%

12

NEAR IC

1

2

6-

THRM1

1

R6007

2

C6012

0.1uF_25V

1

2

C6028

1

4.7uF_25V

2

U803

12

VCC

3

ACN

4

ACP

6

BYPASS#

5

ACDET

11

VREF5

10

AGND

15

TS

1

CHGEN#

14

SCL

13

SDA

25

ALARM#

17

IOUT

TI_BQ24721C_QFN_32P

C6033

1

2

0.1uF_10V

1

2

ACDRV#

BATDRV#

PVCC

HIDRV

BTST

REGN

LODRV

PGND

SYNP

SYNN

ISYNSET

42-

C6035

0.1uF_10V

C6009

0.1uF_25V

2

23

SYS

24

32

30

29

PH

31

28

27

26

22

21

20

SRP

19

SRN

18

BAT

7

EAO

8

EAI

9

FBO

16

33

TML

HW_I_ADC

C6008

1

4.7uF_25V

2

R6004

12

4.7_5%

EMI

1

R6017

56K_5%

2

C6010

1

4.7uF_25V

2

C6025

1

4.7uF_25v

2

C6011

12

12

3

BAT54AWD6003

1

2

1

R6012

200K_5%

2

C6019

1

2

+VBAT

0.1uF_25V

C6020

1

1uF_10v

2

R6014

18K_5%

100pF_50v

5-,6-,7-,8-,9-,11-,30-,59-

765

8

G

1

4

23

8765

G

23

41

C6016

1

56pF_50v

2

CHANGE by

1

C6029

68uF_25V

2

D

Q6003

FDMC8884

S

Q6002

FDMC8884

D

S

D6002

SBR3U40P1

1

2

C6017

1

2

PLC0755P_10uH_3.9A

L6001

12

1

R6003

4.7_5%

2

1

21

C6007

2200pF_50V

2

R6011

10K_5%

0.0015uF_50V

C6005

0.01uF_50v

1

2

4.7uF_25V

C6000

1

2

C6027

1

2

4.7uF_25V

15-Oct-2008Loren

Q6000

1

S

2

3

4

G

AM4825P_AP

1

C6021

0.1uF_25V

C6022

1

2

0.1uF_25V

+VPACK

6-

8

D

7

6

5

R6000

2

3

4

0.01_1%

1

2

4.7uF_25V

12

NEAR IC

C6023

1

0.22uF_25v

2

INVENTEC

TITLE

Perugia10M

CODESIZE DOC. NUMBER

A3

CS

SHEET

563

C6001

OF

C6026

1

2

4.7uF_25V

REV

x011310A2250501

THRM1

EC_SMB1_DATA

EC_SMB1_CLK

542-,6042-,60-

R2502

R2503

12

33_5%

12

33_5%

D2500

EZJZ0V500AA

R804 1K_5%

1

2

12

1

D2501

2

EZJZ0V500AA

D7410

12

PHP_PESD5V0S1BB_SOD523_2P_OPEN

PHP_PESD5V0S1BB_SOD523_2P_OPEN

D7412

D7411

12

12

PHP_PESD5V0S1BB_SOD523_2P_OPEN

+VPACK

5-

12

LITTLEFUSE_R451015_15A_65V

C803

1

2

1000pF_50v

FUSE800

CN800

1

1

2

2

3

3

4

4

5

5

6

G1

6

G

7

G2

7

G

8

G3

8

G

9

G4

9

SYN_200045MR009G151ZR_9P

G

+V5LA

+V5LA

5-,6-,7-,12-,18-,39-,49-

D9068

13

BAT54_30V_0.2A_OPEN

+V5AUXON THRM_SHUTDWN#

7-,42-

C4388

0.1uF_10V

U6960

1

MRRESET

2

GND

3

VSEN

VCC

GMT_G686LT11U_SOT23_5P

1

2

5

4

5-,6-,7-,12-,18-,39-,49-

1

R6960

10K_5%

2

18-

+VBAT

5-,7-,8-,9-,11-,30-,59-

1

R6961

510K_1%

2

1

R6962

100K_1%

2

CHANGE by

Loren

10-Oct-2008

INVENTEC

TITLE

SELECT & BATTERY CONN

CODE

CS

SHEET

DOC. NUMBER

663

SIZE

A3

REV

x011310A2250501

OF

EC_PW_ON

42-

R6103

12

10K_5%

SSM3K7002FU

Q6103

1

G

SSM3K7002FU

D

S

3

2

Q6106

1

G

+V5LA

5-,6-,7-,12-,18-,39-,49-

1

R6101

10K_5%

2

3

D

S

2

BAT54_30V_0.2A

7-,12-,18-,31-,38-,39-,42-,48-,56-,57-

D6100

13

R6100

12

100K_5%

+V3LA

1

2

C8402

0402_OPEN

C6117

0.033uF_16V

Q6101

4

S

D

G

AM3423P

1

2

+V3A

1

2

5

63

8-,31-,32-,33-,34-,39-,42-,46-,53-,54-,56-

1

R6102

200_5%

2

+V3LA

7-,12-,18-,31-,38-,39-,42-,48-,56-,57-

PAD6101

2

1

POWERPAD_2_0610

C6103

0402_OPEN

1

R6109

6.8K_1%

2

1

2

1

R6110

10K_1%

2

MPLC0730_3R3_5.7A

1

C6104

2

330uF_6.3V

+V5AUXON

L6101

12

6-,42-

Q6105

FDMC8884

Q6104

FDS6690AS

8765

D

8

D

S

123

765

G

41S23

G

4

1

3

2

4.7uF_25v

C6109

D6101

BAT54C_30V_0.2A

+VBAT

5-,6-,7-,8-,9-,11-,30-,59-

PAD6013

POWERPAD_2_0610

4.7uF_25V

C6108

1

1

2

2

+V3LDO

Q6107

1

SSM3K7002FU

C6105

12

0.1uF_25V 12

TI_TPS51125_QFN_24P

C6110

1

C6116

1

2

4.7uF_6.3V

1uF_6.3V

2

1

3

D

R6112

G

120K_1%

S

2

2

+VBAT

1

R6111

130K_1%

2

U6100

820K_5%

12

VO2

8

VREG3

9

DRVH2

LL2

R6104

1

C6115

0.22uF_6.3V

2

3

5

25

4

2

1

6

TML

VFB1

VFB2

VREF

TONSEL

ENTRIP1

ENTRIP2

SKIPSEL

EN0

13

1

2

GND

14

15

1

2

VO1

PGOOD

VBST1VBST2

DRVH1

DRVL1DRVL2

VIN

VCLK

VREG5

16

18

17

C6112

2.2uF_25v

LL1

247

23

22

2110

2011

19

+V5LA

1

2

0.1uF_25V

C6106

12

5-,6-,7-,12-,18-,39-,49-

PAD6843

POWERPAD2x2m

C6111

10uF_6.3V

5-,6-,7-,8-,9-,11-,30-,59-

PAD6102

POWERPAD_2_0610

765

8

D

Q6102

G

FDMC8884

S

123

4

8765

D

Q6100

G

FDS6690AS

41S23

C6107

1

2

4.7uF_25V

4.7uF_25V

MPLC0730_3R3_5.7A

1

2

L6100

C6101

1

2

4.7uF_25V

C6100

330uF_6.3V

C6113

+V5A

8-,9-,11-,12-,30-,34-,38-,39-,44-,45-

PAD6100

C6102

1

0402_OPEN

2

SKIPSEL

TONSEL

POWERPAD_2_0610

>>VRE3 OR VRE5=OOA

>>VREF=ASKIP

>>GND=PWM

>>VRE5=365/460

>>VRE3=300/375

>>VREF=245/305

>>GND=200/250

1

R6107

1

15.4K_1%

2

2

1

R6108

10K_1%

2

CHANGE by

INVENTEC

TITLE

SYSTEM POWER(3V/5V/12V)

CODE

CS

SHEET

DOC. NUMBER

763

SIZE

10-Oct-2008Loren

A3

REV

x011310A2250501

OF

SLP_S5#_3R

8-,12-,32-,42-

R6204

1

0_5%

2

C6204

0402_OPEN

1

2

C6207

2.2uF_6.3v

+V5A

1

2

R6207

10_5%

1

2

7-,8-,9-,11-,12-,30-,34-,38-,39-,44-,45-

C6205

0402_OPEN

U6200

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

1

TI_TPS51117_QFN_14P

2

R6203

2

274K_1%

VBST

DRVH

V5DRV

DRVL

PGND

+VBAT

5-,6-,7-,9-,11-,30-,59-

PAD6200

POWERPAD_2_0610

6

7

8

5

Q6201

3

4G1

G

41S23

D

FDMC8884

S

2

8

765

Q6200

D

FDS6690AS

1

2.2_5%

13K_1%

C6201

0.1uF_25V

12

C6202

1

2

2.2uF_6.3v

R6201

12

12

R6202

14

13

12

LL

11

TRIP

10

9

8

15

TML

C6210

1

2

4.7uF_25v

MPLC0730_2R2_7.3A

C6203

1

2

4.7uF_25V

L6200

12

14.3K_1%

10K_1%

R6205

R6206

8-,19-,23-,24-,26-,27-,59-

+V1.8

PAD6201

1

C6206

1

2

0402_OPEN

2

1

2

C6208

1

330uF_2.5V

2

POWERPAD_2_0610

8-,12-,18-,29-,32-,34-,36-,37-,40-,42-,43-,44-,51-,59-,60-

+V5S

8-,12-,18-,29-,32-,34-,36-,37-,40-,42-,43-,44-,51-,59-,60-

1

2

SLP_S3#_3R SLP_S3_5R

C190

2.2uF_6.3v

+V1.8

8-,19-,23-,24-,26-,27-,59-

C162

1

2

22uF_6.3v

0402_OPEN

8-,12-,32-,42-

+V5S

1

R6823

0402_OPEN

2

VIN

VCNTL

6

POK

7

EN

8

VIN

9

ANPEC_APL5930KAI_TRG_SOP_8P

1

C163

1

R163

2

0402_OPEN

2

VTT

2

3

4

5

12-,34-

1

R27

2.1K_1%

2

1

R28

10K_1%

2

+V1.8

1

2

C6840

22uF_6.3v

C69

1

2

4.7uF_6.3V

22-Oct-2008

PAD6840

POWERPAD_2_0610

C6842

1

22uF_6.3v

2

INVENTEC

TITLE

Perugia10M

SYSTEM POWER(+V1.8/+V1.25S)

SIZE

A3

CS

SHEET

+V0.9S

28-,59-8-,19-,23-,24-,26-,27-,59-

DOC. NUMBER

1310A2250501 x01

OFCHANGE by

638

REVCODE

+V5A

7-,8-,9-,11-,12-,30-,34-,38-,39-,44-,45-

C6843

C6841

1

0.1uF_10V

2

1uF_6.3V

U3

1

IN

3

SHDN#

GND

2

GMT_G916T1Uf_SOT23_5_5P

C68

1uF_10V

U6840

11

TML1VDDQSNS

10

VIN VLDOIN

9

S5

8

PGND

GND

7

S3

VTTSNS

6

VTTREF

GMT_G2997F6U_MSOP10_10P

+V1.5A

5

OUT

4

SET

M_VREF

8-,12-,32-,42-

8-,12-,32-,42-

19-,26-,27-

+V3A

7-,31-,32-,33-,34-,39-,42-,46-,53-,54-,56-

1

2

1

2

SLP_S5#_3R

SLP_S3#_3R

+V1.5S

16-,24-,34-,44-,53-,54-,59-

U9

VOUT

45

VOUT

3

FB

GND

1

2

2

1

C189

39pF_50V

1

R168

9.1K_1%

2

1

R169

10K_1%

2

C197

1

2

22uF_6.3v

12-,49-

PAD6

POWERPAD_2_0610

C198

1

2.2uF_6.3V

2

SSM3K7002FU_OPEN

1

Q22

G

1

R167

0603_OPEN

2

3

D

S

2

Loren

7-,8-,11-,12-,30-,34-,38-,39-,44-,45-

+V5A

+VBAT

5-,6-,7-,8-,11-,30-,59-

PAD9

POWERPAD_2_0610

SLP_S3#_5R

11-,12-,60-

R232

12

100K_5%

VCCP_PG

+V3S

11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

1

R186

10K_5%

2

11-

C250

1

0.1uF_10V

2

C275

2.2uF_6.3v

1

R240

10_5%

2

C276

1

2

0402_OPEN

U18

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

1

TI_TPS51117_QFN_14P

2

2

R242

274K_1%

1

VBST

DRVH

V5DRV

DRVL

PGND

8765

D

Q28

G

SI7230DN

2.2_5%

2

13K_1%

C278

0.1uF_25V

12

C277

1

2.2uF_6.3v

2

R233

1

12

R243

14

13

12

LL

11

TRIP

10

9

8

15

TML

23

41

8765

G

41S23

Q31

S

D

FDS8672S

C252

1

2

4.7uF_25V

MPLC0730_1R0_10.6A

C4390

1

2

4.7uF_25V

L18

12

4.12K_1%

10K_1%

R241

R262

1

2

1

2

1

0402_OPEN

C274

2

1

2

330uF_2.5V

C251

PAD7

POWERPAD_2_0610

+VCCP

11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

INVENTEC

TITLE

Perugia10M

GRAPHIC POWER (+VGFX_CORE)

CHANGE by OF

Loren

10-Oct-2008

A3

CODE

CS

SHEET

DOC. NUMBER

963

REVSIZE

x011310A2250501

BLANK

INVENTEC

TITLE

Perugia10M

SYSTEM POWER(+VCCP/+V1.5S)

SIZE

CODE

CS

SHEET

DOC. NUMBER

10 63

CHANGE by OF

Loren

10-Oct-2008

A3

REV

x011310A2250501

9-,12-,60-

SLP_S3#_5R

VR_PWRGD

11-,14-,18-,32-

C4141

C4142

C4143

C4144

1

1

1

1

9-

47pF_50v

2

47pF_50v

2

47pF_50v

2

47pF_50v

2

VSSSENSE

VCCSENSE

12

180K_1%

CSP1

CSN1

CSN2

CSP2

R184

11-

11-

R6968

11-

R6970330_5%

11-

16-

16-

1

3

2

1

2

R6967

12

330_5%

2

47pF_50v

1

C4145

12

330_5%

330_5%R6969

1

2

47pF_50v

1

C4146

1

12

12

D24

BAT54C

C200

1uF_6.3v

R6971

0_5%

R6972

0_5%

2

2

0402_OPEN

5

2

3

C4147

C4149

0402_OPEN

R185

12

180K_1%

12

C192

0.1uF_10V

U12

4

PHP_74LVC1G17_SOT753_5P

1

2

1

C4148

0402_OPEN

2

1

2

C201

1

2

1uF_6.3v

C4150

0.22uF_6.3v

2

1

2

+V3S

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

PHP_74LVC1G17_SOT753_5P

5

U13

4

3

19-,32-

PM_PWROK

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

1

R6973

0402_OPEN

2

1

R6974

470pF_50V

0_5%

2

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

H_DPRSTP#

PSI#

H_VID6

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

11-,42-

1

R6071

10K_5%

2

VR_PWRGD

PM_DPRSLPVR

IMVP_CKEN#

VCORE_EN

2

1

C4151

15-,19-,31-

15-

1616161616-

1616-

VCORE_ENVCCP_PG

R6977

1

C4152

1

R6975

4.75K_1%

2

12

R6976

20K_1%

1

R6978

0402_OPEN

2

11-,14-,18-,32-

R6980

12

19-,32-

499_1%

11-,42-

124K_1%

2

2.2uF_6.3v

12

40

41

PwPd

1

V5FILT

DROOP DRVH1

2

VREF

3

GND

4

CSP1

5

U6961

CSN1

6

TI_TPS51620RHAR_QFN_40P

CSN2

7

CSP2

8

GNDSNS

9

VSNS

10

THERM

VR_TT#

11

+VCCP

1

R6979

56_5%

2

38

39

ISLEW

DPRSTP#

12

13

TP1002

37

TONSEL

OSRSEL

PSI#

VID6

14

36

35

TRIPSEL

VID5

15

34

33

VR_ON

PWRMON

VID316VID4

18

17

32

CLK_EN#

DPRSLPVR

VID119VID2

31

PGOOD

VID0

20

VBST1

DRVL1

PGND

DRVL2

VBST2

DRVH2

R6981

2

10K_5%

R6982

2

10K_5%

LL1

V5IN

LL2

30

29

28

27

26

25

24

23

22

21

+VBAT

NFM60R30T222

+V3S

1

1

2

1

1

0.1uF_25v

R6983

C4153

2.2_5%

2

1

R6984

2.2_5%

2

12

0.1uF_25v

C4154

5-,6-,7-,8-,9-,30-,59-

+V5A

1

2

L3312

1

2

34

C4156

1

2

0.01uF_50v

7-,8-,9-,12-,30-,34-,38-,39-,44-,45-

+VBAT_CPU

11-

8

765

D

G

S

4

123

4

D

G

S

C4155

2.2uF_6.3v

4

123

S

TPCA8A04_H

Q1409

G

D

8

765

4

123

S

TPCA8030_H

G

Q1408

8D765

11-

+VBAT_CPU

8765

Q1406

TPCA8030_H

123

Q1407

TPCA8A04_H

0603_OPEN

C4157

1

2

0.01uF_50v

0603_OPEN

C4159

R6986

CHANGE by

4.7uF_25V

C4160

1

2

1

2

R6985

0603_OPEN

1

2

C4158

0603_OPEN

2

1

2

1

CSP2

CSN2

+VBAT_CPU

11-

C4161

1

2

4.7uF_25V

CSN1

CSP1

11-

11-

4.7uF_25V

11-

11-

2

42.2K_1%

R6988

2

42.2K_1%

C4163

C4162

1

1

2

2

4.7uF_25V

R6987

R6989

1

12

220K_5%

L3313

1

ETQP4LR36WFC_PANASONIC

L3314

1

ETQP4LR36WFC_PANASONIC

R6990

1

1

220K_5%

10-Oct-2008Loren

4.7uF_25V

C4391

1

2

R6994

12

0_5%

C4164

12

0.01uF_16V

R6991

1

2

200K_1%

R6995

12

63.4K_1%

2

2

R6996

12

2

63.4K_1%

R6992

12

200K_1%

C4165

1

2

0.01uF_16V

R6993

12

0_5%

C4392

1

2

4.7uF_25V

+VCC_CORE

16-,59-

INVENTEC

TITLE

Perugia10M

CPU POWER(VCC_CORE)

SIZE

A3

CS

SHEET

11 63

REVDOC. NUMBERCODE

x011310A2250501

OF

U29-A

74ACT14MTC

8-,12-,18-,29-,32-,34-,36-,37-,40-,42-,43-,44-,51-,59-,60-

SLP_S3#_5R

9-,11-,60-

5-,6-,7-,12-,18-,39-,49-

14

12

7

+V5S

1

R202

200_5%

2

BAT54_30V_0.2A 1

D26

+V5LA

3

5-,6-,7-,12-,18-,39-,49-

U29-F

74ACT14MTC

22uF_6.3v

SLP_S5#_5R

+V5LA

14

7

+V3

1

C377

2

R420

200_5%

BAT54_30V_0.2A

D44

5-,6-,7-,12-,18-,39-,49-

12-

1312

Q42

1

D

2

5

6

G

AM3423P

1

2

BAT54_30V_0.2A

1

3

U29-B

74ACT14MTC

5-,6-,7-,12-,18-,39-,49-

S

1

2

3

1

+V5LA

4

3

0402_OPEN

C378

680pF_50v

D42

14

34

7

+V5LA

C366

12

0.1uF_10V

C8403

+V3LA

7-,18-,31-,38-,39-,42-,48-,56-,57-

C8404

1

1

2

2

0402_OPEN

1

R421

220K_5%

2

8-,32-,42-

SLP_S3#_3R

U29-C

74ACT14MTC

+V3S

9-,11-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

Q40

4

1

S

D

2

G

AM3423P

5-,6-,7-,12-,18-,39-,49-

14

56

5

63

1

2

C365

1

2

680pF_50v

R418

+V5LA

220K_5%

14

U29-D

98

7

74ACT14MTC

R419

220K_5%

12-

SLP_S5_5R

8-,32-,42-

C356

47uF_6.3V

2

1

2

1

SLP_S5#_3R

1

2

R417

200_5%

3

2

R376

200_5%

1

3

D

1

G

S

Q38

2

SSM3K7002FU

D43

2

1

BAT54A_30V_0.2A

7

SLP_S5#_5R

SLP_S5_5R

C8406

0402_OPEN

+V1.5A

8-,34-

8

7

6

5

12-

12-

+V5A

7-,8-,9-,11-,30-,34-,38-,39-,44-,45-

4

S

G

AM3423P

4

S

1

2

AM3423P

C213

12

680pF_50v

G

CHANGE by

Q6

1

S

D

2

3

4

G

AO4406

C8

680pF_50v

R1

12

220K_5%

8-,49-

+V5S

8-,12-,18-,29-,32-,34-,36-,37-,40-,42-,43-,44-,51-,59-,60-

Q25

1

D

2

5

63

Q26

1

D

2

5

63

1

2

1

G

SSM3K7002FU

SLP_S3_5R

10-Oct-2008Loren

Q1

+V1.5

55-

1

R6

200_5%

2

3

D

S

2

INVENTEC

TITLE

Perugia10M

POWER(SLEEP)

SIZE

A3

CS

DOC. NUMBER

OFSHEET

12 63

REVCODE

x011310A2250501

FSB FSC

1

1

0

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

15-,1915-,19-

32-

1K_5%

R7124

FSB CLOCK

FREQUENCY

0

0

0

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

CPU_BSEL1

CPU_BSEL2

CLK_R_SB14

FSA

1

0

0

*CLKREQ# pin controls SRC Table.

Byte5: bit6 =0(PWD)

SRC0

CR#_A

Byte5: bit7=0, disable CR#_A; 1,enable CR#_A

Byte5: bit2 =0(PWD)

SRC0

CR#_C

Byte5: bit3=0, disable CR#_C; 1,enable CR#_C

+VCCP_CLKGEN

Layout note: All decoupling 0.1uF disperse closed to pin

L2501

BLM11A121S

1

2

C4028

C4027

1

11

2

2

10uF_10v

10uF_10v

C4030

C4029

1

2

2

0.1uF_10v

0.1uF_10v

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

CPU_BSEL0

Card reader

R967

CLKREQ_R_SATA#

CLKREQ_R_MCH#

CLK_R_KBPCI

CLK_R_CBPCI

CR#_B

R6029

CLK_R_CARD48

CLK_R_SB48

4251-

R7131

C4031

27pF_50V

Please place close to CLKGEN within 500mils

Byte5: bit4 =0(PWD)

SRC1

667

800

1066

1

R7128

0402_OPEN

2

2

1

10K_5%

R7120

CLK_PWRGD

12

12

HOST CLOCK

FREQUENCY

166

200

266

Byte5: bit6 =1

SRC2

R7127

33_5%

+VCCP

1

32-

2

1K_5%

R7107

Byte5: bit5=0, disable CR#_B; 1,enable CR#_B

Byte5: bit2 =1

SRC2

Byte5: bit0 =0(PWD)

SRC1 SRC4

CR#_D

Byte5: bit1=0, disable CR#_D; 1,enable CR#_D

C4032

1

22

0.1uF_10v

1

2

0.1uF_10v10.1uF_10v

C4035

C4034

+VCCP

12

R6031

1K_5%

R6032

12

15-,19-

2.2K_5%

OPEN

Stuff

OPEN

22._1%

22_1%

33_5%

22_1%

2

1

R967

50-

R6029 22_1%

12

32-

475_1%

1

2

R7118

1

0402_OPEN

3219-

2

ICH_3S_SMDATA

14.31818MHZ

12

1

30PPM

2

ICH_3S_SMCLK

X401

1

2

R7109 1

R7119

R7125

C4033

27pF_50V

475_1%

2

12

33_5%

12

33_5%

0402_OPEN

26-,27-,3226-,27-,32-

Byte5: bit4 =1

SRC4

Byte5: bit0 =1

+V3S

+V3S_CLKGEN

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

C4036

1

2

0.1uF_10v

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

+V3S

R7122

R7132

R7108

2

12

1

2

1

10K_5%

10K_5%

10K_5%

CPU_BSEL0_USB48

1

R7126

2

CLK_SB14

CLKREQ_SATA#

CLKREQ_MCH#

CLK_KBPCI

CLK_CBPCI

L2502

BLM11A121S

1

U4001

26

VDD_SRC_IO

45

VDD_SRC_IO

36

VDD_SRC_IO

12

VDD_IO

39

VDD_SRC

61

VDD_REF

20

VDD_PLL3_IO

49

VDD_CPU_IO

9

VDD_48

2

VDD_PCI

55

VDD_CPU

16

VDD_PLL3

10

USB_FS_A

57

FS_B_TEST_MODE

62

REF_FS_C_TEST_SEL

1

PCI_0_CLKREQ_A#

3

PCI_1_CLKREQ_B#

4

PCI_2

5

PCI_3

56

CKPWRGD_PD#

64

SCL

63

SDA

60

XTAL_IN

59

XTAL_OUT

8

VSS_PCI

11

VSS_48

15

VSS_IO

19

VSS_PLL3

23

VSS_SRC

29

VSS_SRC

42

VSS_SRC

58

VSS_REF

52

VSS_CPU

SLG_SLG8SP510T_TSSOP_64P

Layout note: All decoupling 0.1uF disperse closed to pin

2

C4037

1

1

2

2

10uF_10v

NC

PCI_STOP#

CPU_STOP#

CPU_1_MCH

CPU_1_MCH#

CPU_0

CPU_0#

SRC_8_CPU_ITP

SRC_8#_CPU_ITP#

SRC_11_CLKREQ_H#

SRC_11#_CLKREQ_G#

SRC_10

SRC_10#

SRC_9

SRC_9#

SRC_7_CLKREQ_F#

SRC_7#_CLKREQ_E#

SRC_6

SRC_6#

PCI_4_SEL_LCDCLK#

PCIF_5_ITP_EN

SRC_4

SRC_4#

SRC_3_CLKREQ_C#

SRC_3#_CLKREQ_D#

SRC_2

SRC_2#

LCDCLK_27M

LCDCLK#_27M_SS

SRC_0_DOT_96

SRC_0#_DOT_96#

Byte6: bit7=0, disable CR#_E; 1,enable CR#_E

CR#_E

SRC6

Byte6: bit6=0, disable CR#_F; 1,enable CR#_F

CR#_F

SRC8

Byte6: bit5=0, disable CR#_G; 1,enable CR#_G

CR#_G

SRC9

Byte6: bit4=0, disable CR#_H; 1,enable CR#_H

CR#_H

SRC10

C4038

0.1uF_10v

48

38

37

CLK_NBCLK

51

CLK_NBCLK#

50

CLK_CPUBCLK

54

CLK_CPUBCLK#

53

47

46

CLKREQ_NEWCARD#

33

CLKREQ_WLAN#

32

CLK_PCIE_NCARD

34

CLK_PCIE_NCARD#

35

CLK_PCIE_WLAN

30

CLK_PCIE_WLAN#

31

44

43

CLK_PCIE_SB

41

CLK_PCIE_SB#

40

CLK_3S_MINICARD2

6

CLK_3S_ICHPCI

7

CLK_PEG_MCH

27

CLK_PEG_MCH#

28

CLK_PCIE_LAN

24

CLK_PCIE_LAN#

25

CLK_SATA

21

CLK_SATA#

22

CLKSS1_DREF

17

CLKSS1_DREF#

18

CLK_DREF

13

CLK_DREF#

14

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

C4039

C4040

1

2

0.1uF_10v

1

2

0.1uF_10v

1

2

10K_5%_OPEN

475_1%

475_1%

10K_5%

CHANGE by

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

+V3S

C4041

0.1uF_10v

1

1

R7129

R7130

10K_5%_OPEN

2

2

12

R7111

12

R7112

12

33_5%

2

1

33_5%

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

R6045

R6050

1

2

Loren

12

0402_OPEN

1

2

R6044

10K_5%

27_Select=0

LCD_SST 100MHz

27_Select=1

27MHz NON-SPREAD CLOCK

10-Oct-2008

R6042

R6043

+V3S

R7115

10K_5%

+V3S

TITLE

SIZE

A3 CS

1

1

R7116

10K_5%

2

2

32-

PCISTOP#_3

32-

CPUSTOP#_3

21-

CLK_NBCLK

21-

CLK_NBCLK#

14-

CLK_CPUBCLK

14-

CLK_CPUBCLK#

53-

CLKREQ_R_NEWCARD#

54-

CLKREQ_R_WLAN#

53-

CLK_PCIE_NCARD

53-

CLK_PCIE_NCARD#

54-

CLK_PCIE_WLAN

54-

CLK_PCIE_WLAN#

32-

CLK_PCIE_SB

32-

CLK_PCIE_SB#

54-

CLK_R_PCI_DEBUG

33-

CLK_R_ICHPCI

19-

CLK_PEG_MCH

19-

CLK_PEG_MCH#

46-

CLK_PCIE_LAN

46-

CLK_PCIE_LAN#

31-

CLK_SATA

31-

CLK_SATA#

19-

CLKSS1_DREF

19-

CLKSS1_DREF#

19-

CLK_DREF

19-

CLK_DREF#

INVENTEC

Perugia10M

CLOCK_GENERATOR

CODE

DOC. NUMBER

SHEET

OF

13 63

REV

x011310A2250501

H_A#(35:3)

H_ADSTB#1

H_STPCLK#

H_A20M#

H_FERR#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

21-

H_A#(3)

H_A#(4)

H_A#(5)

H_A#(6)

H_A#(7)

H_A#(8)

H_A#(9)

H_A#(10)

H_A#(11)

H_A#(12)

H_A#(13)

H_A#(14)

H_A#(15)

H_A#(16)

H_REQ#(4:0) H_RS#(2:0)

H_A#(17)

H_A#(18)

H_A#(19)

H_A#(20)

H_A#(21)

H_A#(22)

H_A#(23)

H_A#(24)

H_A#(25)

H_A#(26)

H_A#(27)

H_A#(28)

H_A#(29)

H_A#(30)

H_A#(31)

H_A#(32)

H_A#(33)

H_A#(34)

H_A#(35)

21-

313131-

31313131-

21-

H_REQ#(0)

H_REQ#(1)

H_REQ#(2)

H_REQ#(3)

H_REQ#(4)

H_ADSTB#0

21-

CN807-1

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD01

N5

RSVD02

T2

RSVD03

V3

RSVD04

B2

RSVD05

C3

RSVD06

D2

RSVD07

D22

RSVD08

D3

RSVD09

F6

RSVD010

FOX_PZ4782K_274M_41_478P

GMCH

CPU

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

ADDR GROUP 0

INIT#

CONTROL

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDI

ADDR GROUP 1

TDO

TMS

XDP/ITP SIGNALS

TRST#

DBR#

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

ICH

H CLK

BCLK0

BCLK1

RESERVED

ICH9

18-,19-,31-

14-

14-

14-

14-

21-

H_ADS#

21-

H_BNR#

21-

H_BPRI#

21-

H_DEFER#

21-

H_DRDY#

21-

H_DBSY#

21-

H_BREQ#0

31-

H_INIT#

21-

H_LOCK#

21-

H_CPURST#

21-

H_TRDY#

21-

H_HIT#

21-

H_HITM#

14-

H_BPM5_PREQ#

14-

H_TCK

14-

TDI_FLEX

14-

H_TMS

32-

XDP_DBRESET#

18-

H_THERMDA

18-

THERM_MINUS

PM_THRMTRIP#

13-

CLK_CPUBCLK

13-

CLK_CPUBCLK#

H_BPM5_PREQ#

TDI_FLEX

H_TMS

H_TCK

R59

0402_OPEN

PROCHOT#

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

2

H_RS#(0)

H_RS#(1)

H_RS#(2)

14-

1

R128

54.9_1%

2

21-

VR_PWRGD

R7305

12

2.2K_5%

2SC2411K

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

1

R153

56_5%

CLOSED TO CPU

2

51 ohm +/-1% pull-up to +VCCP

(VCCP) if ITP is implemented

11-,18-,32-

1

R7404

2M_5%

Q7206

2

2

3

C

B

E

1

Q7207

1

G

SSM3K7002FU

C7402

1

2

0402_OPEN

ICH_PROCHOT#

33-

3

D

S

2

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

1

14-

PROCHOT#

2

R152

68_5%1

+VCCP

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

10mils/10mils

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

R65

12

54.9_1%

R142

12

54.9_1%

R63

1

2

54.9_1%

R64

12

54.9_1%

PM_THRMTRIP# should be T at CPU

CHANGE by

Loren

10-Oct-2008

INVENTEC

TITLE

Perugia10M

PENRYN-1

SIZE

CODE

DOC. NUMBER

A3

1310A2250501 x01

CS

SHEET

REV

OF

6314

H_D#(63:0)

H_DSTBN#0

H_DSTBP#0

H_DINV#0

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

1

R911

1K_1%

2

1

2

R912

2K_1%

GTLREF

Layout note: Zo=55 ohm,

0.5" max for GTLREF.

15-,21-

212121-

15-,21-

H_DSTBN#1

H_DSTBP#1

H_DINV#1

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

CN807-2

H_D#(0)

H_D#(1)

H_D#(2)

H_D#(3)

H_D#(4)

H_D#(5)

H_D#(6)

H_D#(7)

H_D#(8)

H_D#(9)

H_D#(10)

H_D#(11)

H_D#(12)

H_D#(13)

H_D#(14)

H_D#(15)

H_D#(16)

H_D#(17)

H_D#(18)

H_D#(19)

H_D#(20)

H_D#(21)

H_D#(22)

H_D#(23)

H_D#(24)

H_D#(25)

H_D#(26)

H_D#(27)

H_D#(28)

H_D#(29)

H_D#(30)

H_D#(31)

212121-

13-,1913-,1913-,19-

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

DATA GRP 0

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

DATA GRP 1

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

MISC

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

FOX_PZ4782K_274M_41_478P

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

DATA GRP 2DATA GRP 3

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

1

R60

0402_OPEN

2

11-,19-,31-

H_D#(32)

H_D#(33)

H_D#(34)

H_D#(35)

H_D#(36)

H_D#(37)

H_D#(38)

H_D#(39)

H_D#(40)

H_D#(41)

H_D#(42)

H_D#(43)

H_D#(44)

H_D#(45)

H_D#(46)

H_D#(47)

H_D#(48)

H_D#(49)

H_D#(50)

H_D#(51)

H_D#(52)

H_D#(53)

H_D#(54)

H_D#(55)

H_D#(56)

H_D#(57)

H_D#(58)

H_D#(59)

H_D#(60)

H_D#(61)

H_D#(62)

H_D#(63)

12

R901 27.4_1%

12

R900 54.9_1%

12

27.4_1%R62

12

R61 54.9_1%

H_DPRSTP#

CLOSED TO CPU

3121312111-

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

212121-

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

PSI#

H_DSTBN#3

H_DSTBP#3

H_DINV#3

15-,21-

H_D#(63:0)

21-

H_DSTBN#2

21-

H_DSTBP#2

21-

H_DINV#2

15-,21-

H_D#(63:0)H_D#(63:0)

Note:

COMP1 & COMP3 5-mil wide

COMP0 & COMP2 18-mil wide

CHANGE by

INVENTEC

TITLE

Perugia10M

PENRYN-2

SIZE

CODE

10-Oct-2008Loren

A3

DOC. NUMBER REV

CS

SHEET

15 63

x011310A2250501

OF

+VCC_CORE

11-,16-,59-

12

C142

3

900uF_2.5V

CN807-3

A7

VCC001

A9

VCC002

A10

VCC003

A12

VCC004

A13

VCC005

A15

VCC006

A17

VCC007

A18

VCC008

A20

VCC009

B7

VCC010

B9

VCC011

B10

VCC012

B12

VCC013

B14

VCC014

B15

VCC015

B17

VCC016

B18

VCC017

B20

VCC018

C9

VCC019

C10

VCC020

C12

VCC021

C13

VCC022

C15

VCC023

C17

VCC024

C18

VCC025

D9

VCC026

D10

VCC027

D12

VCC028

D14

VCC029

D15

VCC030

D17

VCC031

D18

VCC032

E7

VCC033

E9

VCC034

E10

VCC035

E12

VCC036

E13

VCC037

E15

VCC038

E17

VCC039

E18

VCC040

E20

VCC041

F7

VCC042

F9

VCC043

F10

VCC044

F12

VCC045

F14

VCC046

F15

VCC047

F17

VCC048

F18

VCC049

F20

VCC050

AA7

VCC051

AA9

VCC052

AA10

VCC053

AA12

VCC054

AA13

VCC055

AA15

VCC056

AA17

VCC057

AA18

VCC058

AA20

VCC059

AB9

VCC060

AC10

VCC061

AB10

VCC062

AB12

VCC063

AB14

VCC064

AB15

VCC065

AB17

VCC066

AB18

VCC067

FOX_PZ4782K_274M_41_478P

VCC068

VCC069

VCC070

VCC071

VCC072

VCC073

VCC074

VCC075

VCC076

VCC077

VCC078

VCC079

VCC080

VCC081

VCC082

VCC083

VCC084

VCC085

VCC086

VCC087

VCC088

VCC089

VCC090

VCC091

VCC092

VCC093

VCC094

VCC095

VCC096

VCC097

VCC098

VCC099

VCC0100

VCCP01

VCCP02

VCCP03

VCCP04

VCCP05

VCCP06

VCCP07

VCCP08

VCCP09

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCA01

VCCA02

VCCSENSE

VSSSENSE

+VCC_CORE

11-,16-,59-

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

VID0

AF5

VID1

AE5

VID2

AF4

VID3

AE3

VID4

AF3

VID5

AE2

VID6

AF7

AE7

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

1

C930

2

220uF_2v_15mR_Panasonic

11-

H_VID0

11-

H_VID1

11-

H_VID2

11-

H_VID3

11-

H_VID4

11-

H_VID5

11-

H_VID6

+VCC_CORE

11-,16-,59-

1

R114

100_1%

2

1

R127

100_1%

2

11-

11-

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

C153

1

1

2

2

0.1uF_10V

VCCSENSE

VSSSENSE

C154

0.1uF_10V

LAYOUT NOTE:

PLACE C2461 NEAR PIN B26

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (NORTH SIDE

SECONDARY)

C120

C155

1

1

2

2

0.1uF_10V

8-,24-,34-,44-,53-,54-,59-

0.1uF_10V

0.01uF_16v

C957

1

2

+V1.5S

C121

0.1uF_10V

1

2

C119

1

2

0.1uF_10V

1

C956

10uF_6.3V

2

LAYOUT NOTE:

ROUTE VCCSENSE AND VSSSENSE TRACE AT

24.7 OHM WITH 50 MIL SPACEING

PLACE PU AND PD WITHIN I INCH OF CPU

CHANGE by

Loren 10-Oct-2008

INVENTEC

TITLE

Perugia10M

PENRYN-3

CODE

SIZE

A3

DOC. NUMBER

1310A2250501 x01

CS

SHEET

REV

OF

6316

CN807-4

A4

VSS001

A8

VSS002

A11

VSS003

A14

VSS004

A16

VSS005

A19

VSS006

A23

VSS007

AF2

VSS008

B6

VSS009

B8

VSS010

B11

VSS011

B13

VSS012

B16

VSS013

B19

VSS014

B21

VSS015

B24

VSS016

C5

VSS017

C8

VSS018

C11

VSS019

C14

VSS020

C16

VSS021

C19

VSS022

C2

VSS023

C22

VSS024

C25

VSS025

D1

VSS026

D4

VSS027

D8

VSS028

D11

VSS029

D13

VSS030

D16

VSS031

D19

VSS032

D23

VSS033

D26

VSS034

E3

VSS035

E6

VSS036

E8

VSS037

E11

VSS038

E14

VSS039

E16

VSS040

E19

VSS041

E21

VSS042

E24

VSS043

F5

VSS044

F8

VSS045

F11

VSS046

F13

VSS047

F16

VSS048

F19

VSS049

F2

VSS050

F22

VSS051

F25

VSS052

G4

VSS053

G1

VSS054

G23

VSS055

G26

VSS056

H3

VSS057

H6

VSS058

H21

VSS059

H24

VSS060

J2

VSS061

J5

VSS062

J22

VSS063

J25

VSS064

K1

VSS065

K4

VSS066

K23

VSS067

K26

VSS068

L3

VSS069

L6

VSS070

L21

VSS071

L24

VSS072

M2

VSS073

M5

VSS074

M22

VSS075

M25

VSS076

N1

VSS077

N4

VSS078

N23

VSS079

N26

VSS080

P3

VSS081

FOX_PZ4782K_274M_41_478P

VSS082

VSS083

VSS084

VSS085

VSS086

VSS087

VSS088

VSS089

VSS090

VSS091

VSS092

VSS093

VSS094

VSS095

VSS096

VSS097

VSS098

VSS099

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

CHANGE by

INVENTEC

TITLE

Perugia10M

PENRYN-4

CS

SHEET

DOC. NUMBERSIZE

17 63

10-Oct-2008Loren

A3

REVCODE

x011310A2250501

OF

+V5S

8-,12-,29-,32-,34-,36-,37-,40-,42-,43-,44-,51-,59-,60-

FAN1_DAC0_3

U1

1

C810

2.2uF_6.3v12

42-

2

3

4

FON

VIN

VO

VSET

8

GND

7

GND

6

GND

5

GND

GMT_G995P1U_SOP8_8P

+V5S_FAN

+V5LA

5-,6-,7-,12-,39-,49-

R66

12

150_5%

C76

0.1uF_10V

9-,11-,12-,13-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

C3

1

2

2.2uF_6.3v

1

2

3

CN802

1

2

3

G

G1

G2

G

ACES_85205_0300N_3P

FAN CN

U4

R36

12

SET15VCC

24.9K_1%

2

GND

4

3

1

2

HYST OT

GMT_G708T1U_SOT23_5P

+V3S

6-,18-

1

R2

10K_5%

2

C1

1

2

220pF_25V

Thermal shoutdown at 86.1C +/-3C from 60C to 100C

RSET=0.0012*T - 0.9308*T+96.147

2

Hysteresis is 30C

H_THERMDA

THERM_MINUS

THRM_SHUTDWN#

14-

14-

6-,18-

C2

1

2

680pF_50V

close to KBC

THRM_SHUTDWN#

42-

FAN_TACH1

PM_THRMTRIP#

C193

100pF_50v

12

14-,19-,31-

VR_PWRGD

11-,14-,32-

Q24

R188

12

2

330_5%

B

2SC2411K

1

C165

2

0.1uF_10V

U14

1

VDD

2

D+

3

D-

4

T_CRIT_A

WINB_W83L771AWG_TSSOP_8P

1

R187

2M_5%

2

3

C

E

1

+V3LA

7-,12-,31-,38-,39-,42-,48-,56-,57-

8

SCL

7

SDA

6

ALERT

5

GND

C202

1

0402_OPEN

2

Q23

G

1

SSM3K7002FU

6-,18-

THRM_SHUTDWN#

3

D

S

2

5-,42-

EC_SMB2_CLK

5-,42-

EC_SMB2_DATA

Thermal Sensor For CPU

LAYOUT NOTES: PUT THE THERMAL SENSOR CLOSE TO CPU

CHANGE by

Loren

10-Oct-2008

INVENTEC

TITLE

Perugia10M

THERMAL&FAN CONTROLLER

DOC. NUMBER

CODE

SIZE

A3

1310A2250501 x01

CS

SHEET

OF

REV

6318

MCH_CFG(5)

MCH_CFG(13:12)

XOR/ALLZ

NOTE: CFG[2:0] STRP : 010b : 800 MT/S

MCH_CFG(5)

MCH_CFG(6)

MCH_CFG(7)

MCH_CFG(9)

MCH_CFG(10)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(16)

LOW=DMIx2

HIGH=DMIx4

00=PARTIAL CLOCK GATING DISABLE

01=XOR MODE ENABLE

10=ALL-Z MODE ENABLE

11=NORMAL OPERATION

011b : 667 MT/S

19191919-

19191919-

1

R889

2.2K_1%

2

1

R888

0402_OPEN

2

MCH_CFG(7)

(CPU Strap)

1

R875

0402_OPEN

2

1

R886

0402_OPEN

2

1

2

1

R887

0402_OPEN

2

+V3S

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

R869 10K_5%

+V1.8

8-,19-,23-,24-,26-,27-,59-

1

R131

1K_1%

2

1

R133

3K_1%

2

1

R132

1K_1%

2

MCH_CFG(20)

DIGITAL DISPLAY

PORT(SDVO/DP/iHDMI)

CONCURRENT WITH PCIE

12

12

VR_PWRGD_CK505

C136

1

2

0.01uF_16v

C135

1

2

0.01uF_16v

LOW=ONLY DIGITAL DISPLAY PORT

(SDVO/DP/iHDMI)OR PCIEIS OPERATIONAL

HIGH= DIGITAL DISPLAY PORT

(SDVO/DP/iHDMI)AND PCIE ARE OPERATING

VIA THE PEG PORT

10K_5%R868

PM_PWROK

1

2

1

2

19-,26-

19-,27-

C138

2.2uF_6.3v

C137

2.2uF_6.3v

PM_EXTTS#0

PM_EXTTS#1

32-

11-,19-,32-

19-

SM_RCOMP_VOH

19-

SM_RCOMP_VOL

LOW=RSVD

HIGH=Mobile CPU

MCH_CFG(16)

(FSB Dynamic

ODT)

1

R874

R877

0402_OPEN

0402_OPEN

2

1

R876

0402_OPEN

2

R842

0_5%_OPEN

2

1

MCH_CFG(9)

PCIE Graphics

Lane

LOW=Dynamic ODT

HIGH=Dynamic ODT

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

MCH_CFG(17:3)

MCH_CFG(19)

MCH_CFG(20)

PM_SYNC#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PLT_RST#

PM_THRMTRIP#

PM_DPRSLPVR

MCH_CFG(19)

(DMI LANE

REVERSAL)

Disable

Enable

MCH_CFG(19)

MCH_CFG(20)

13-,15-

13-,15-

13-,15-

19-

LOW=NORMAL

HIGH=LANES REVERSED

LOW=Reverse Lane

HIGH=Normal operation

MCH_CFG(6)

+V3S

1

R871

0402_OPEN

2

19-

19-

R879

12

R878

12

R880

12

1919-

3211-,15-,3119-,2619-,27-

33-,4214-,18-,3111-,32-

R165

LOW=TPM

HIGH=TPM

1

R870

0402_OPEN

2

1K_5%

1K_5%

1K_5%

MCH_CFG(3)

MCH_CFG(4)

MCH_CFG(5)

MCH_CFG(6)

MCH_CFG(7)

MCH_CFG(8)

MCH_CFG(9)

MCH_CFG(10)

MCH_CFG(11)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(14)

MCH_CFG(15)

MCH_CFG(16)

12

Enable

Disable

NOTE :

USE 4K-OHM RESISTOR WHEN INSTALLING

PULL-UP/PULL-DOWN RESISTOR ON ANY

MCH-CFG CONNECTION/PINS.

U7-2

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

AL34

RSVD10

AK34

RSVD11

AN35

RSVD12

AM35

RSVD13

T24

RSVD14

B31

RSVD15

AJ6

RSVD16

M1

RSVD17

AY21

RSVD20

A47

RSVD21

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

H21

P29

R28

T28

R29

N33

P32

AT40

AT11

T20

R32

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

B7

F1

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

100_5%

PM_EXTTS#0

PM_EXTTS#1

TP3

TP2

ITL_CANTIGA_GM_FCBGA_1329P

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

BB36

SB_CKE_1

BA17

SA_CS#_0

AY16

SA_CS#_1

AV16

SB_CS#_0

AR13

SB_CS#_1

BD17

SA_ODT_0

AY17

SA_ODT_1

BF15

SB_ODT_0

AY13

SB_ODT_1

BG22

SM_RCOMP

BH21

SM_RCOMP#

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

CLKREQ#

ICH_SYNC#

TSATN

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

13-

K36

32-

H36

B12

B28

B30

B29

C29

A28

R885 499_1%12

TP1

DDPC_CTRLCLK

DDPC_CTRLDATA

TMDS_SCLK

TMDS_SDATA

CLKREQ_R_MCH#

MCH_ICH_SYNC#

R7030

2

R7090

1

33_5%

SM_RCOMP_VOH

SM_RCOMP_VOL

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

CHANGE by

56_5%

2

+VCCP

1

3131313131-

DMI_TXN(0)

DMI_TXN(1)

DMI_TXN(2)

DMI_TXN(3)

DMI_TXP(0)

DMI_TXP(1)

DMI_TXP(2)

DMI_TXP(3)

DMI_RXN(0)

DMI_RXN(1)

DMI_RXN(2)

DMI_RXN(3)

DMI_RXP(0)

DMI_RXP(1)

DMI_RXP(2)

DMI_RXP(3)

11-,19-,32-

R7033

R7031

1

0402_OPEN

HDA_BCLK

HDA_RST#

HDA_SDIN3

HDA_SDOUT

HDA_SYNC

26-,2826-,2827-,2827-,28-

26-,2826-,2827-,2827-,28-

26-,2826-,2827-,2827-,28-

13131313-

131332-

32-

32-

32-

4 mils/ 7mils

32-

CL_CLK0

32-

CL_DATA0

PM_PWROK

32-

CL_RST#0

12

0402_OPENR7032

12

0402_OPEN

2

Loren

26-

MA_CLK_DDR1

26-

MA_CLK_DDR2

27-

MB_CLK_DDR1

27-

MB_CLK_DDR2

26-

MA_CLK_DDR1#

26-

MA_CLK_DDR2#

27-

MB_CLK_DDR1#

27-

MB_CLK_DDR2#

MA_CKE0

MA_CKE1

MB_CKE0

MB_CKE1

MA_CS0#

MA_CS1#

MB_CS0#

MB_CS1#

MA_ODT0

MA_ODT1

MB_ODT0

MB_ODT1

19-

SM_RCOMP

19-

SM_RCOMP#

19-

SM_RCOMP_VOH

19-

SM_RCOMP_VOL

CLK_DREF

CLK_DREF#

CLKSS1_DREF

CLKSS1_DREF#

CLK_PEG_MCH

CLK_PEG_MCH#

DMI_TXN(3:0)

DMI_TXP(3:0)

DMI_RXN(3:0)

DMI_RXP(3:0)

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,29-,30-,31-,32-,33-,34-,39-,41-,42-,43-,44-,45-,46-,48-,49-,50-,51-,53-,54-,56-,59-

iHDMI enable : no stuff

iHDMI disnable : stuff

10-Oct-2008

4848-

+V1.8

8-,19-,23-,24-,26-,27-,59-

12

R130

80.6_1%

12

R143

80.6_1%

8-,26-,27-

C889

1

2

0.1uF_10V

1

2

C1020

0.1uF_10V

iHDMI enable : stuff

iHDMI disnable : no stuff

R7036

TMDS_SCLK

TMDS_SDATA

R7037

1

1

INVENTEC

TITLE

Perugia10M

CANTIGA-1

SIZE

CODE

A3

CS

SHEET

19-

SM_RCOMP

19-

SM_RCOMP#

M_VREF

+VCCP

9-,11-,13-,14-,15-,16-,19-,20-,21-,23-,24-,31-,34-,59-

1

R7038

1K_1%

2

12

R7039

499_1%

+V3S

2.2K_5%

2

2.2K_5%

2

DOC. NUMBER

19 63

REV

x011310A2250501

OF

Loading...

Loading...