Page 1

FILE NO.016-9502

TECHNICAL TRAINING MANUAL

COLOUR TELEVISION

N5MM1 Chassis

MM20E45

Page 2

CONTENTS

SECTION I

OUTLINE

SECTION II

CHANNEL SELECTION CIRCUIT

SECTION III

RGB SIGNAL PROCESSING CIRCUIT

SECTION IV

CRT DRIVE CIRCUIT

SECTION V

MODE DISCRIMINATING CIRCUIT AND SYNC SIGNAL PROCESSING CIRCUIT

SECTION VI

SYNC SEPARATION CIRCUIT OF TV MODE

SECTION VII

HORIZONTAL AND VERTICAL OSCILLATION CIRCUIT

SECTION VIII

VERTICAL DEFLECTION CIRCUIT

SECTION IX

HORIZONTAL DEFLECTION CIRCUIT

SECTION X

PROTECTION CIRCUIT

SECTION XI

OSD STABILIZATION CIRCUIT

SECTION XII

PICTURE TUBE

SECTION XIII

POWER SUPPLY CIRCUIT

SECTION XIV

FAILURE DIAGNOSIS PROCEDURES

Page 3

SECTION I OUTLINE

1. OUTLINE OF N5MM1 CHASSIS

(MM20E45)

This model is a 20” color TV with 181 channel tuner and built

in VGA and Mac II capability. The hybrid design of this

model allows it to serve several purposes. Television

reception, a monitor running Multimedia, PC applications,

or for playback of video games. The 20” FST picture tube

features a stripe pitch 0.58mm, providing a favourable

comparisons to conventional designs which generally measure

0.75 to 0.9mm.

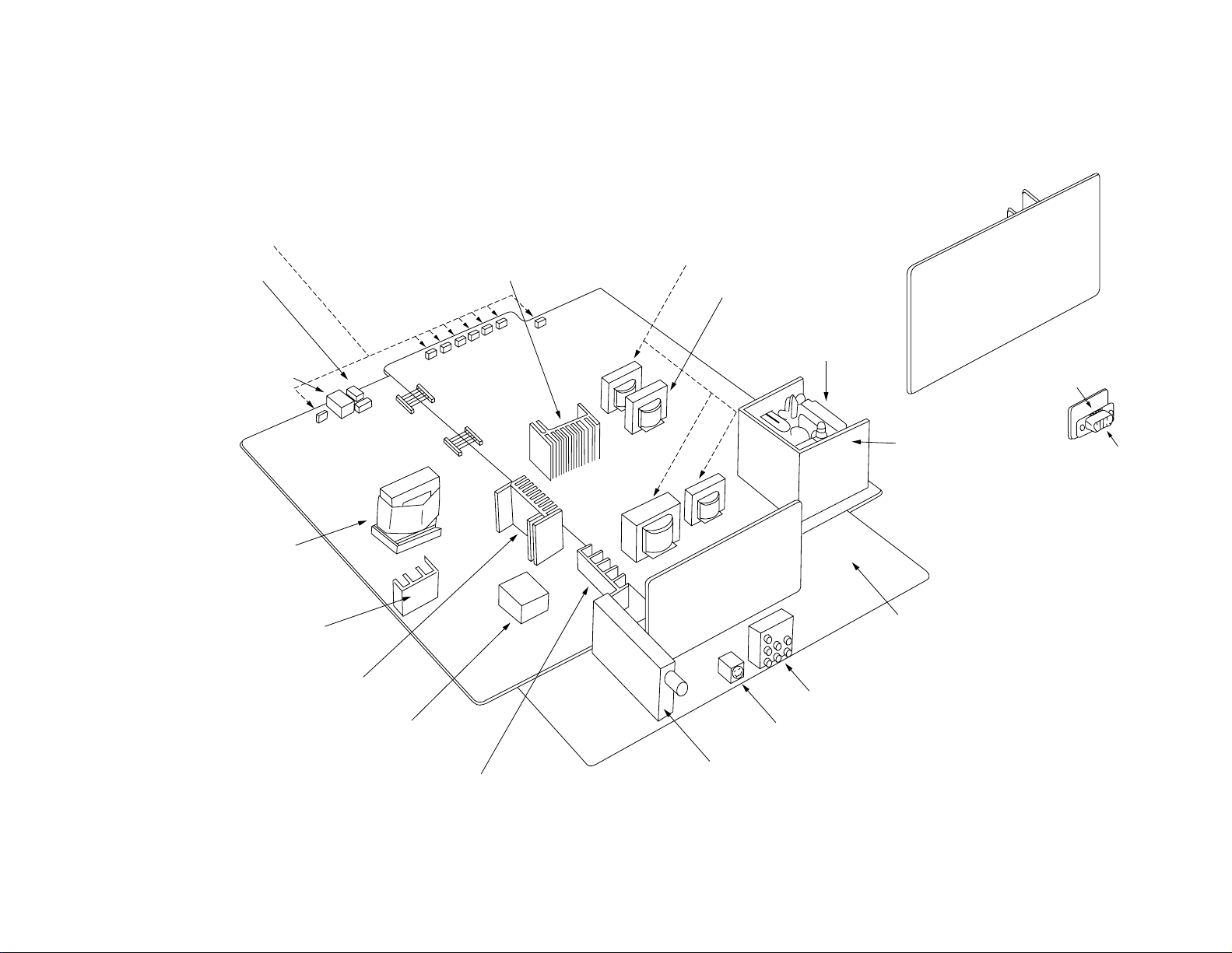

2. PC BOARD CONFIGURATION

(1) Power/V.C.D. PB5226

PB5226-1 Power

PB5226-2 V.C.D.

(2) Deflection PB5227

(3) Signal/Video PB5228

PB5228-1 Signal

PB5228-2 Video

PB5228-3 D-SUB

1-1

Page 4

Converter trans

Front keys

Power LED

Remote control

receiver

3. CONSTRUCTION OF CHASSIS

Choke coils

V out radiator

Choke trnas

Video unit

Flyback trans

D-sub unit

1-2

Power unit

Converter trans

Rectifier

Power radiator

Stand by trans

Sound out radiator

Def unit

V/C/D unit

Tuner

Jack board

S-VIDEO

H out radiator

Signal unit

D-sub connector

Page 5

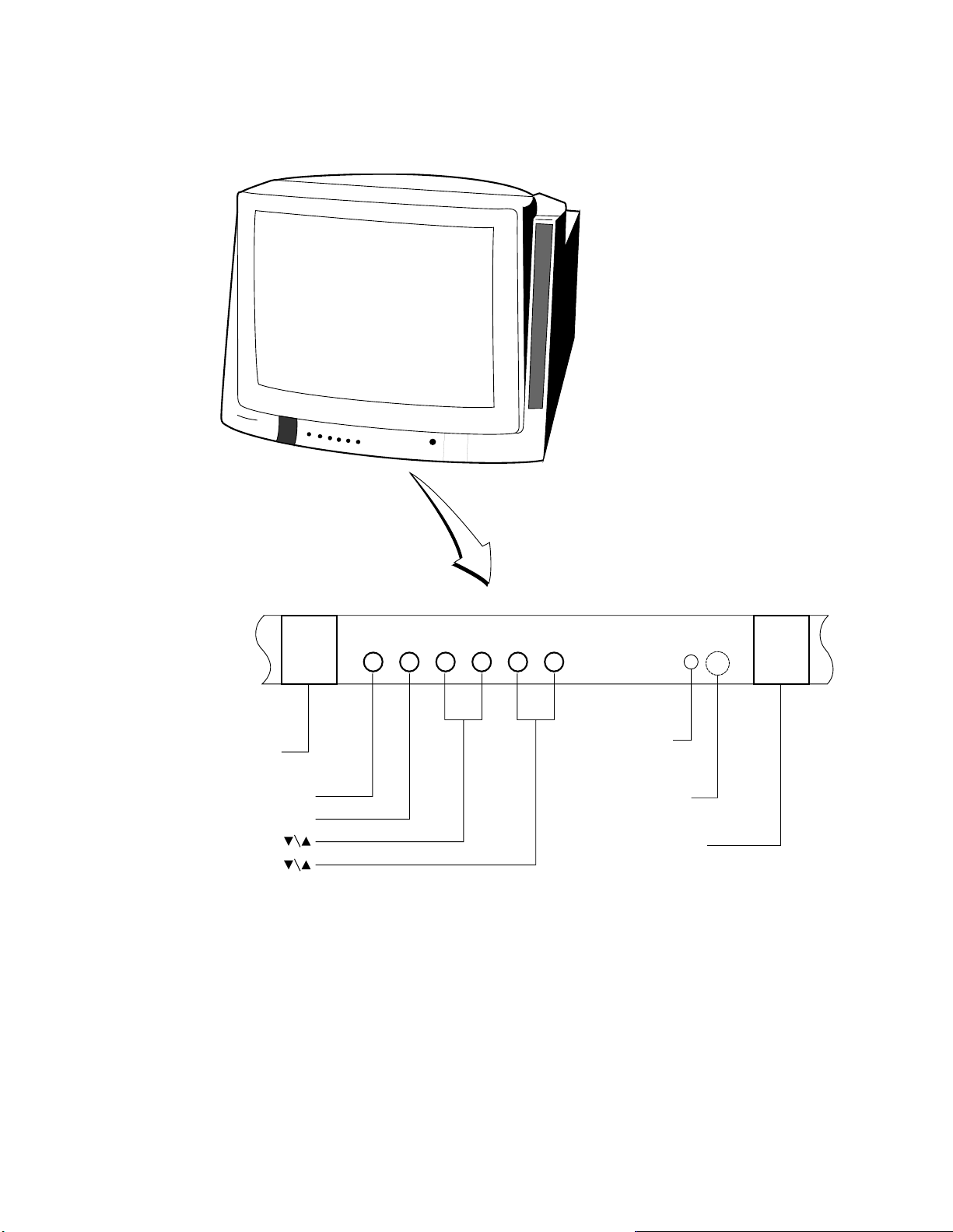

4. LOCATION OF CONTROLS

4-1 TV Set

RGB/

TV/VIDEO

button

MENU button

ADV button

VOLUME

CHANNEL

POWER indicator

REMOTE senser

POWER button

1-3

Page 6

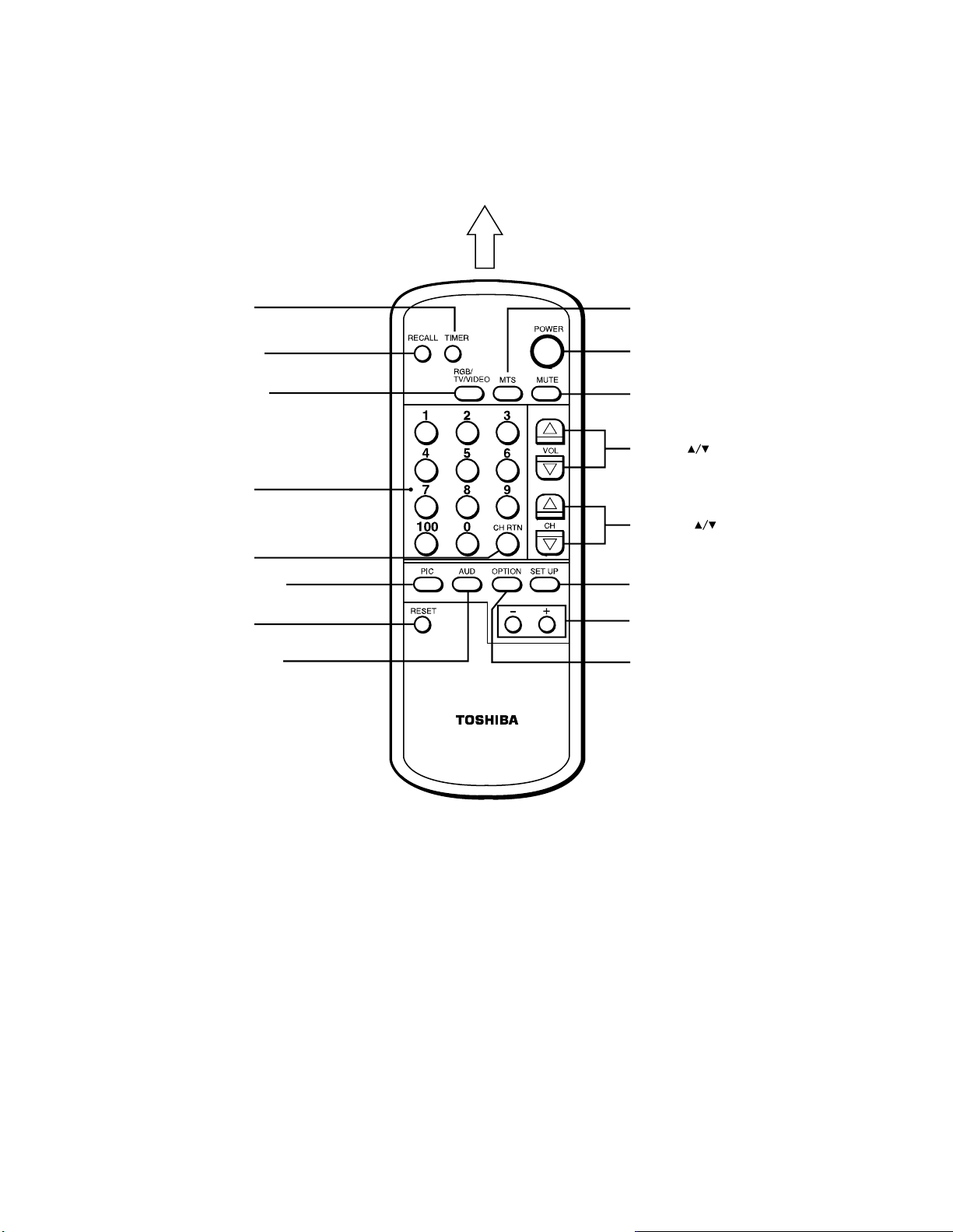

4-2 Remote Control

T

s

This Remote Control allows you to control the functions of your TV set from 16 feet (5m) away. The “*” marked function buttons

do not have duplicate locations on your TV set. They can be controlled only by the Remote Control.

Aim at the TV set

TIMER button*

RECALL button*

V/VIDEO button

Channel Number

buttons*

CH RTN (Channel Return)

button*

PIC (Picture)* button

RESET button*

AUD (Audio) button*

MTS button*

POWER button

MUTE button

VOLUME buttons

CHANNEL button

SET UP button*

-/+ buttons

OPTION button*

1-4

Page 7

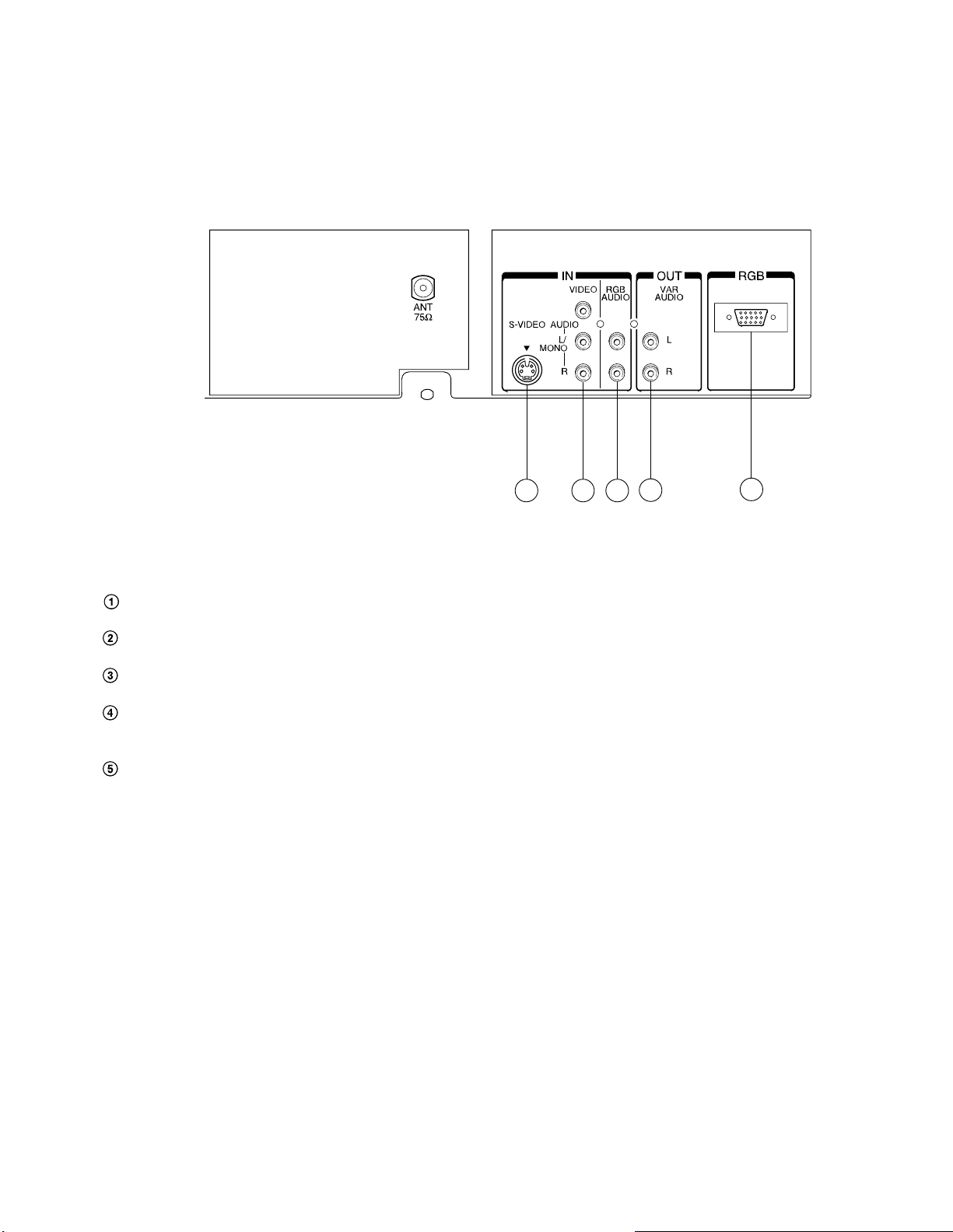

4-3 Monitor Panel

This TV set is equipped with RGB INPUT connector, RGB AUDIO INPUT jacks, S-VIDEO INPUT jack, VIDEO/AUDIO

INPUT jacks and VARIABLE AUDIO OUTPUT jacks of connecting your desired personal computer and video/audio

equipment.

TV Rear

3

4

5

2

1

RGB INPUT Connector – provide for direct connection of a personal computer.

RGB AUDIO INPUT Jacks – provide for direct connection of a personal computer with audio output terminals.

S-VIDEO INPUT Jack – provide for direct S-video connection from an S VHS VCR or a video disc player.

VIDEO/AUDIO INPUT Jacks – provide for direct connection of video devices (VCR, video disc player, camcorder, etc.)

with video/audio outputs.

VARIABLE AUDIO OUTPUT Jacks – feed volume-controlled stereo audio out from whatever displayed on the screen,

allows connection of audio amplifier and lets you adjust sound level with TV’s remote.

1-5

Page 8

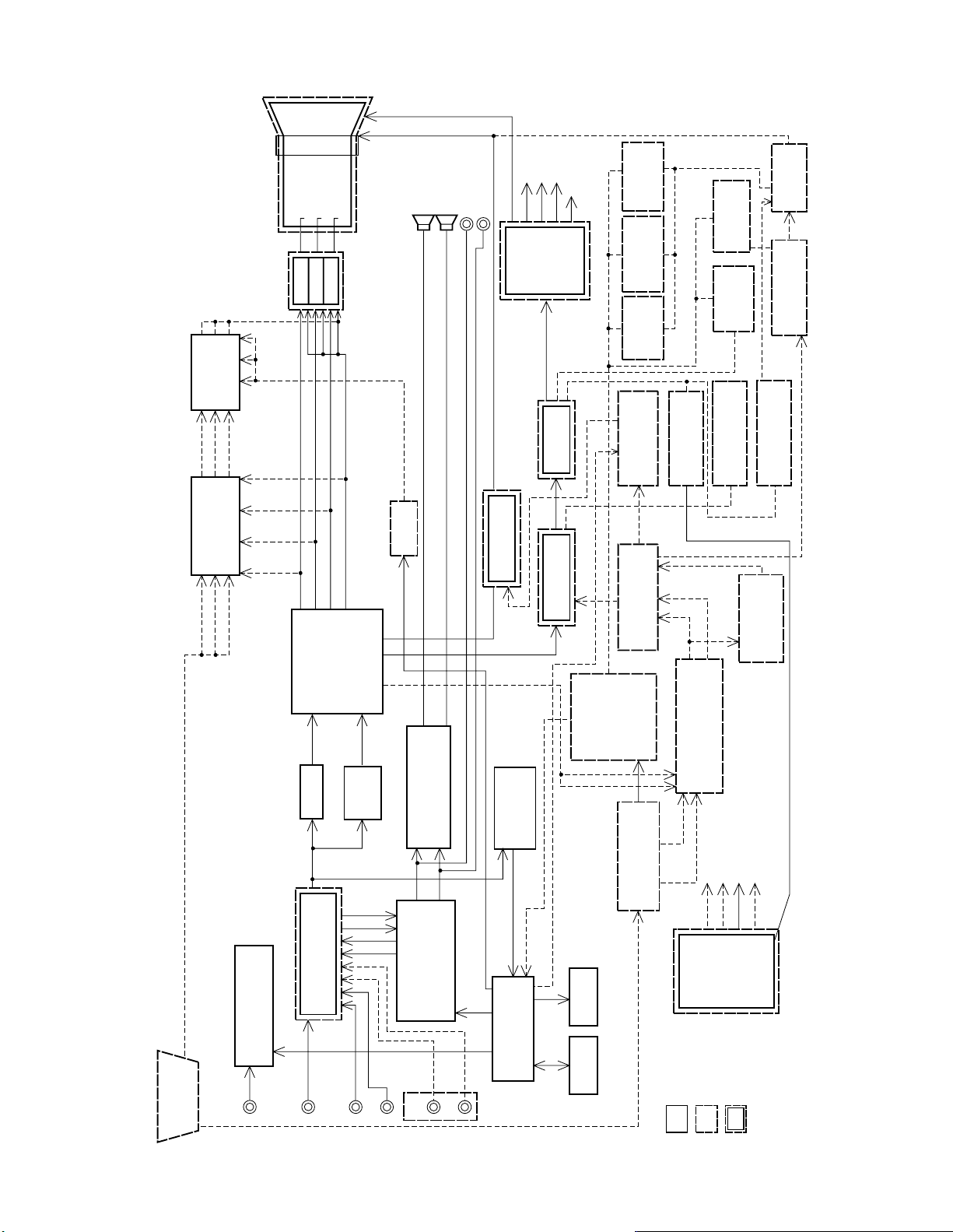

5. MM20E45 BLOCK DIAGRAM

EH

VAR. OUT

VIDEO

(VERT)

(+15V)

(HEATER)

capacitor

switching

Resonance

Drive

switching

output

Horizontal

Signal

switching

AN5862K

RGB

TA7730

Signal switching

RGB

FBT

G-output

B-output

R-output

output

Horizontal

OSD

LA7837

Vertical output

R-Y G-Y B-Y -Y

Horizontal drive

V/C/D

TA8801

Linear coil

switching

S-shape

capacitor

switching

DPC

TA8859AP

High voltage

control chopper

H

Horizontal/vertical

oscillation LA7860

V

capacitor

switching

Resonance

Drive

switching

F/V conversion

Horizontal drive

control chopper

Horizontal amplitude

IR9331

20VMMTV BLOCK DIAGRAM

D.L

TC4053BP

Signal switching

RGB

Tuner/IF module

RF

VIDEO

L

Band

pass

R

TA8200AH

Audio output

L

R

CXA1774S

Audio control

L

R

1-6

C. CAP slicer

Micro-computer

Mode distinction

TA75339AP

TC74HC86AP

TC4514P

TA75902

Synchronizing signal

process M52346SP

H.Sync

DAC

Memory

V.Sync

Syncon G

TC40538P

Synchronizing

signal switching

+15V

HEATER

Power unit

To be added

for MM

TV & MM

AUDIO

VERT.

+100V

Model change

( ) For MM

Page 9

6. SPECIFICATIONS

SPECIFICATIONS

GENERAL

10 Local Keys 8key

11 Front Surround –

SOUND

PICTURE

OTHER

TERM

CABINET

12 Sub Bass System

13 Audio Output 5W x 2

14 Speaker Size & Nbr 80 x 120 x 2

15 Comb Filter (GLS)

16 Black Level Expand –

17 Horizontal Resolution 500

18 Parental-Ch Lock

19 Channel Caption –

20 Off Timer (180min)

21 Channel Search –

22 S-Video In-Term (1)

23 Audio, Video In-Term (1)

24 Variable Audio Out (RCA Jack)

25 RGB Audio (L, R)

26 Mini D-Sub 15pin

27 Rod-Ant/Adapter –/–

MODEL No.

1 Picture Tube D/T Invar

2 Channel Capacity 181ch

3 C. Caption

4 MTS with dbx

5 Bass, Treble, Balance

6 Sub Audio Program

7 Remote hand unit Regu.

8 Nbr of RMT Button 29key

9 LED Indicators (P)

MM20E45

NEW

1-7

Page 10

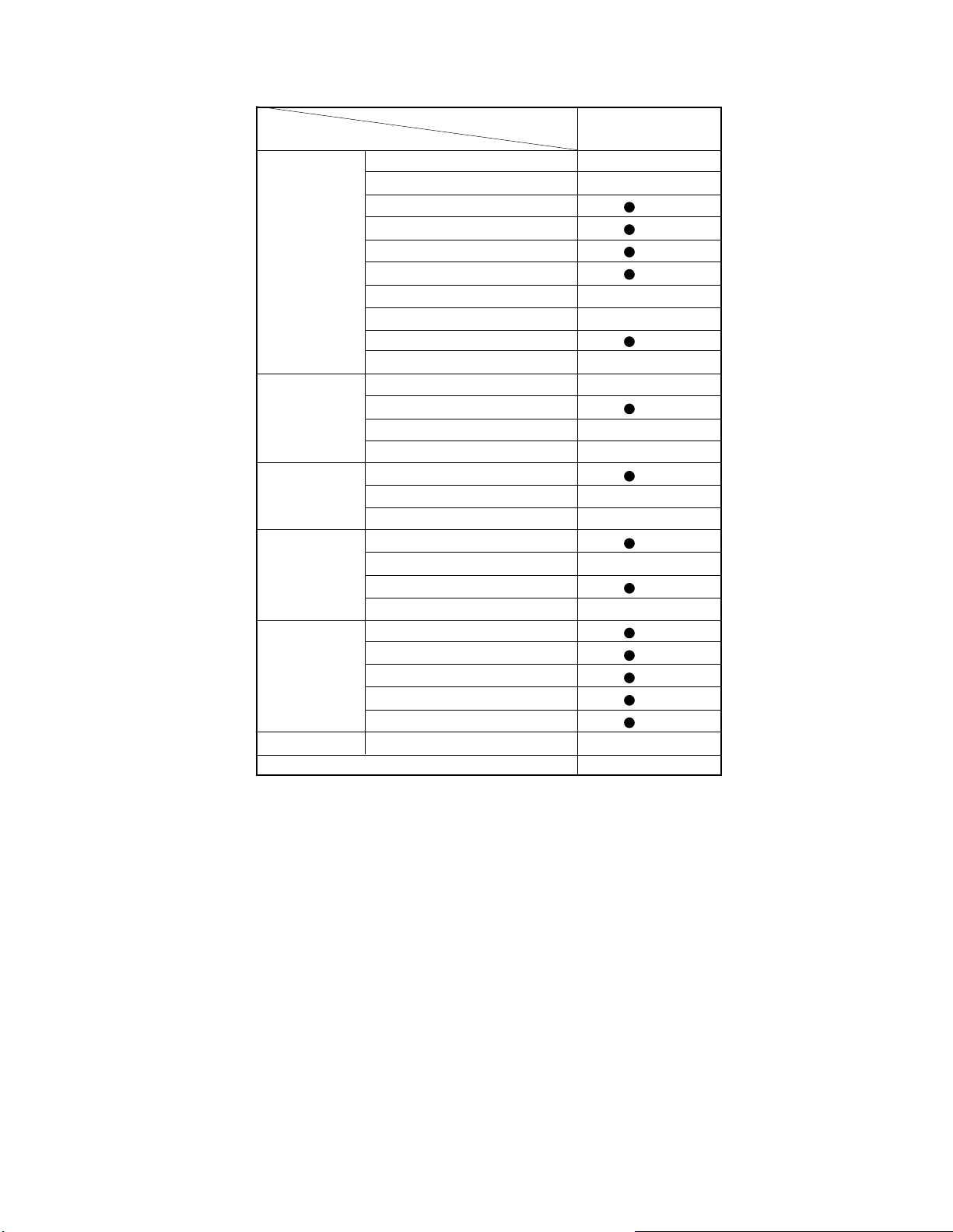

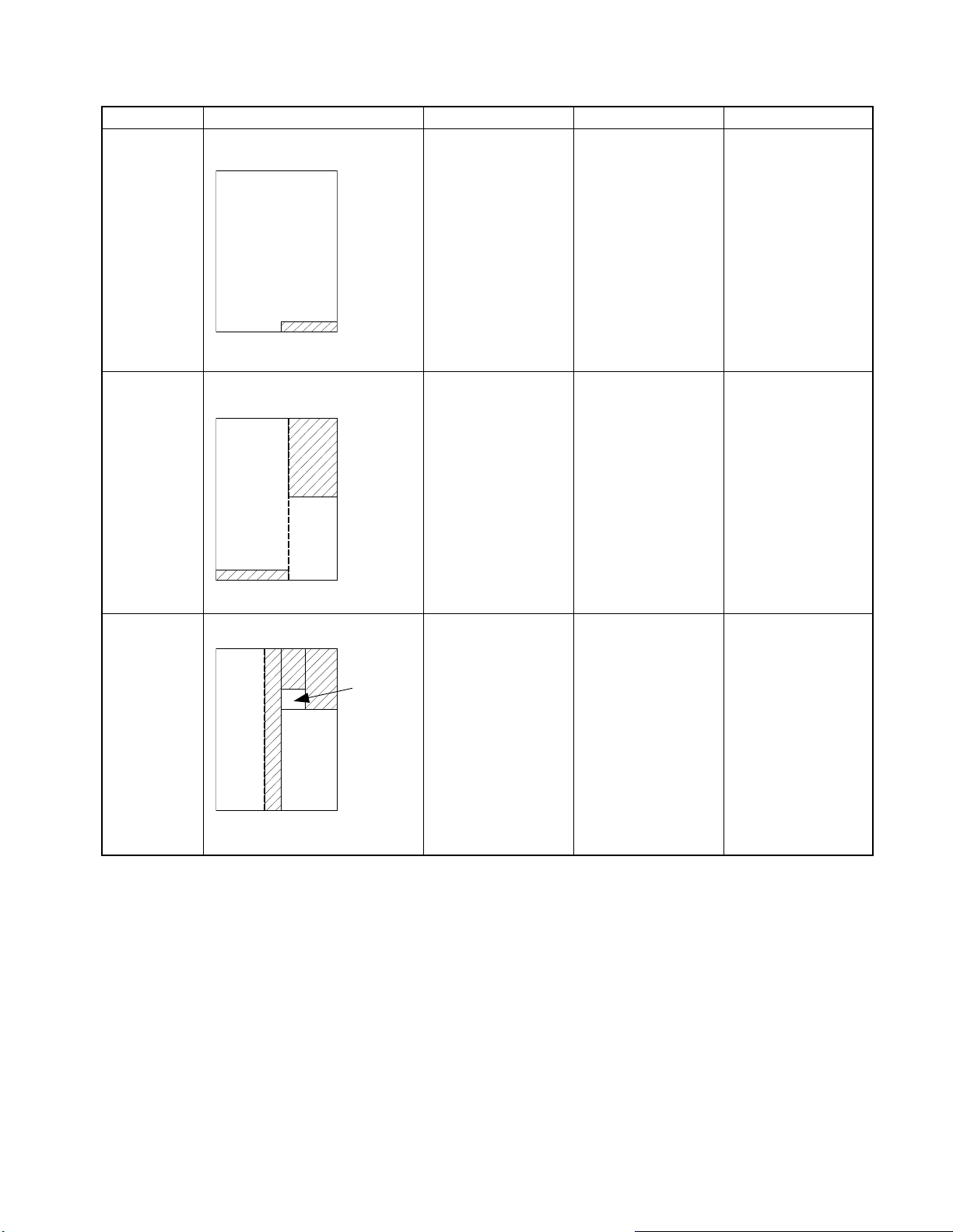

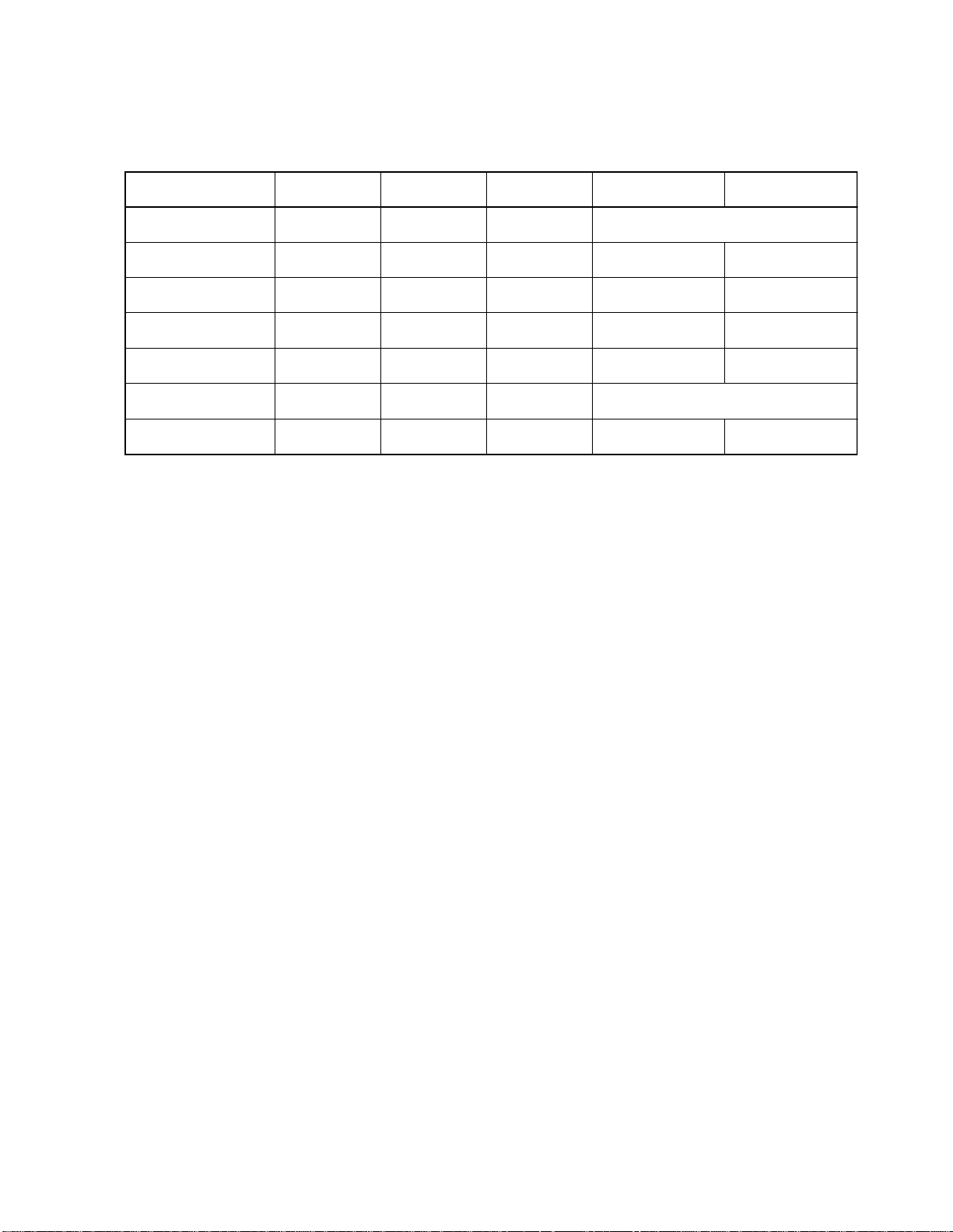

MM20E45 PC BOARD CONSTRUCTION

p

ITEM MM20E45 NEW MODEL CIRCUIT NOTE

DEF

PB5227

POWER/VCD

PB5226

249 x 330

249 x 330

POWER

dro

V/C/D

V-CUT LINE

Hole drawing: New

drop

Hole drawing: New

Hole drawing: New

Hole drawing: New

Def.

PB5227

(249.0 x 330.0)

Power/Audio

PB5226-1

(153.0 x 317.0)

Video/Chroma/Def

PB5226-2

(96.0 x 160.0)

Printed wiring board

part code

P/P-M/P:

23534680B

Printed wiring board

part code

P/P-M/P:

23534679B

SIGNAL/

VIDEO

PB5228

249 x 330

SIGNAL

VIDEO

-

drop

D-SUB

Hole drawing: New

Hole drawing: New

Signal

PB5228-1

(110.0 x 330.0)

Video (CRT/D)

PB5228-2

(119.0 x 210.0)

D-Sub

PB5228-3

(28.5 x 41.5)

Printed wiring board

part code

P/P: 23534681B

M/P: 23534681C

1-8

Page 11

SECTION II CHANNEL SELECTION CIRCUIT

1. OUTLINE OF CHANNEL SELECTION

SYSTEM

The channel selection circuit in the N5MM1 chassis employs

a bus system which performs a central control by connecting

a channel selection microcomputer to a control IC in each

circuit block through control lines called a bus.

In the bus system which controls each IC, the I2C-bus system

(two line bus system) promoted by Philips Co., Ltd. in the

Netherlands has been employed.

The ICs controlled by the I2C-bus control system are: ICG01

for audio system process, ICA02 for non-volatile memory,

H001 for main U/V tuners, IC302 for deflection distortion

corrections.

2. OPERATION OF THE CHANNEL

SELECTION CIRCUIT

2-1 Channel Selection Control Microcomputer

(ICA01 Toshiba TMP87CM34N-3101)

8 bit microcomputer, TLCS-870 series for TV receivers,

TMP87CM34N (42 pins, built-in CCD) developed by Toshiba

is employed. With this microcomputer each IC and circuit

shown below are controlled.

2-1-1 Non-volatile Memory IC

(ICA02 NEC µPD672CX)

(1) Memorizes data for video and audio signal adjustment

values, sound volume, woofer adjustment value, external

input status, etc.

(2) Memorizes adjustment data for white balance (RGB cut

off, GB drive), sub-brightness, sub color, sub-tint, etc.

(3) Memorizes deflection distortion correction value data

adjusted for each unit.

2-1-2 U/V Tuner Unit

(H001 Toshiba EL911L)

(1) A desired station can be received by transferring a

channel selection frequency data (division data) to the

I2C-bus type frequency synthesizer provided in the

tuner and by setting a band switch data which selects the

UHF or VHF band.

2-1-3 Deflection Distortion Correction IC

(IC302 Toshiba TA8859AP)

(1) Sets adjustment memory values for vertical amplitude,

linearity, horizontal amplitude, parabola, corner, pedestal

distortion, etc.

2-1-4 Audio System Process IC

(ICG01, SONY CXA1784S)

2-1

Page 12

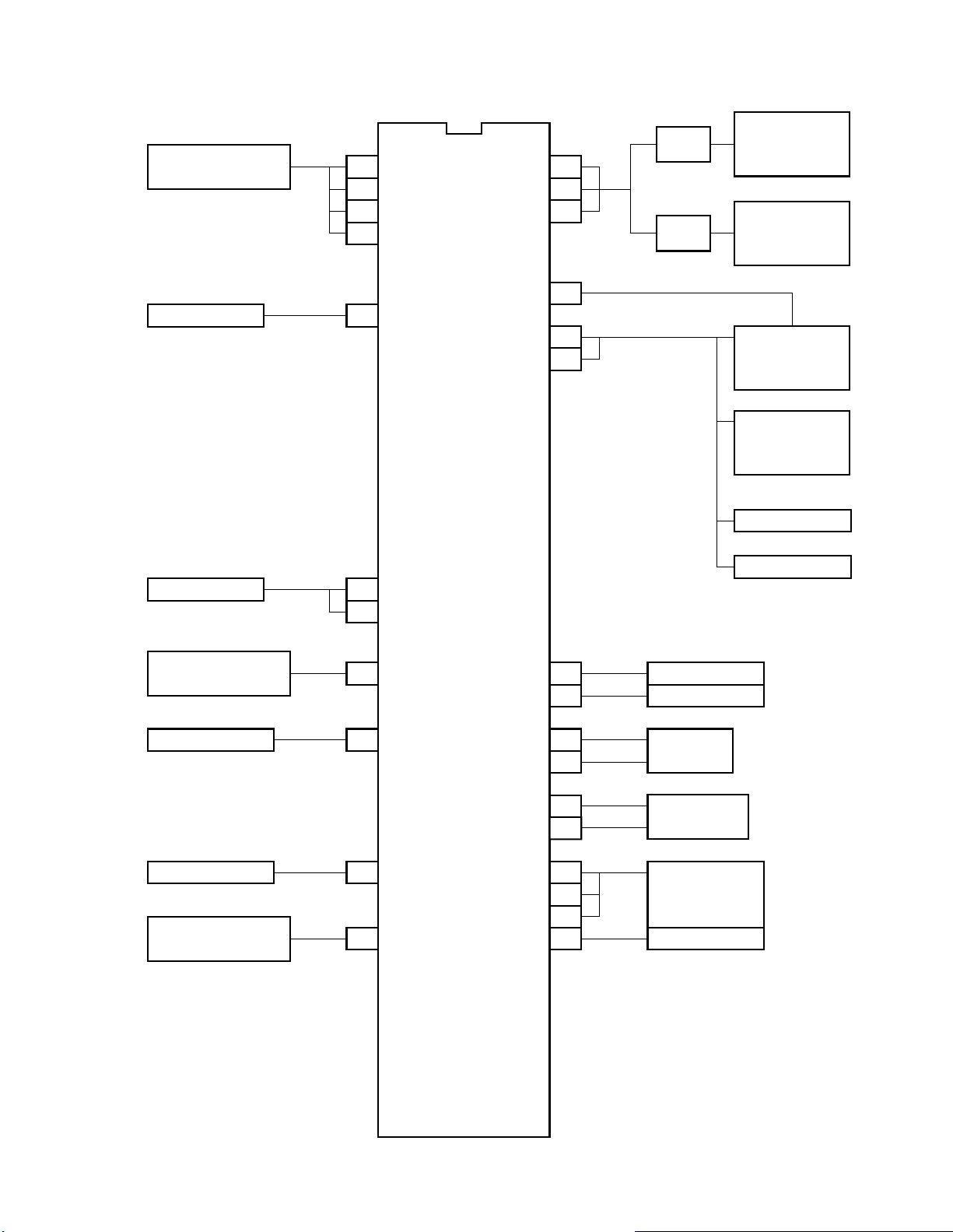

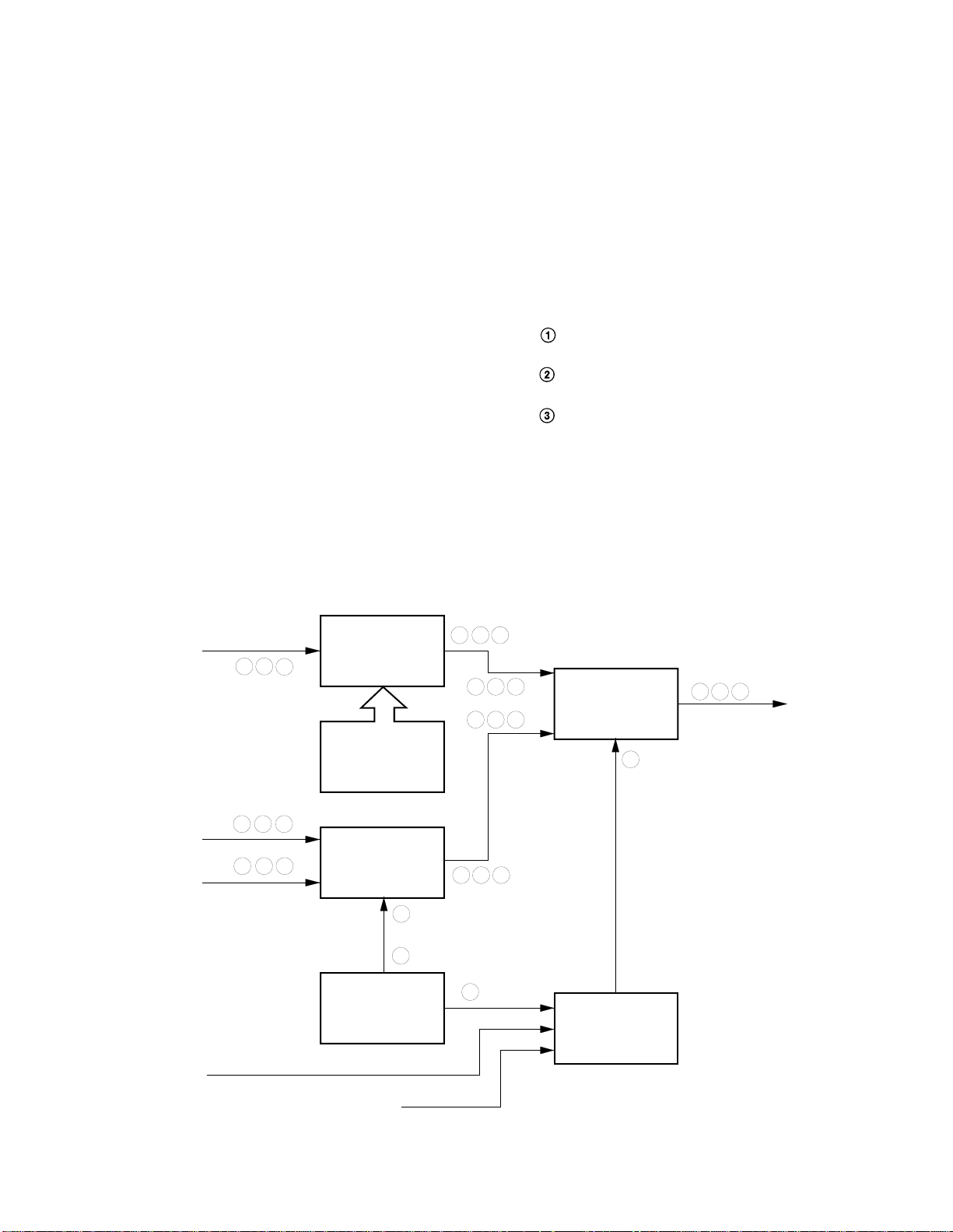

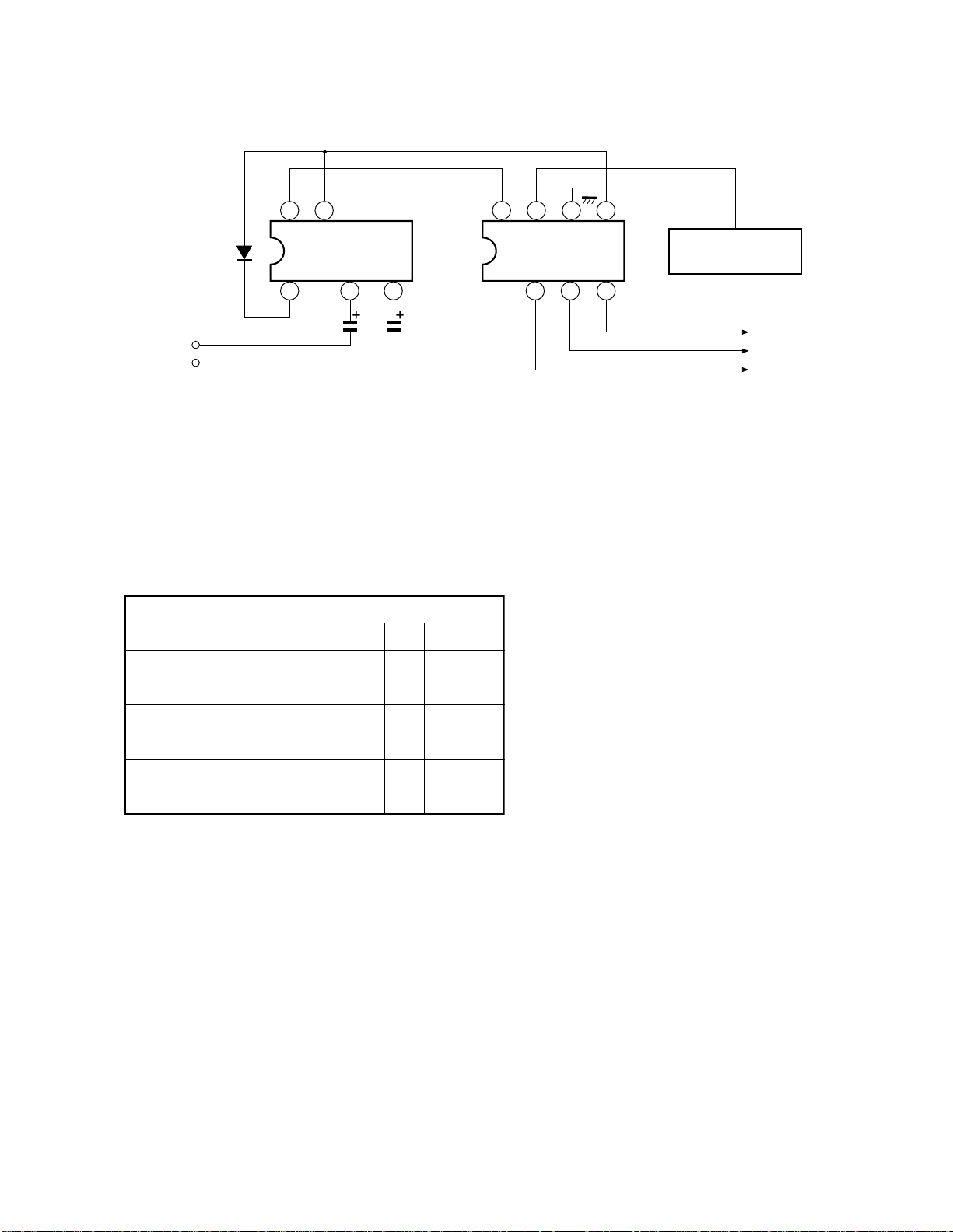

3. SYSTEM BLOCK DIAGRAM

VIDEO SIGNAL

PROCESS CIRCUIT

A/V DSP UNIT

25

24

23

22

10

QA01

TMP87CM34N-3101

Y

B

G

R

EXIT A

STB

CLK

DATA

AFT

SCL

SDA

37

38

DAC1

5

6

7

DAC2

9

PICTURE

CONTROL

AUDIO

CONTROL

TUNER/IF

MEMORY

µPD6272CX

QA02

KEY SWITCH

RGB MODE

DISCRIMINATION

RELAY DRIVE

SYNC SEPA.

REMOTE

CONTROLLER LIGHT

ERCEPTION UNIT

13

KEY A

14

KEY B

15 MODE

1

RELAY

35

SYNC

RMT

36

HD

VD

OSC1

OSC0

X1

X0

RST

HOLD

VDD

VSS

26

28

31

33

27

29

32

34

42

21

DPG

MTS

H. PULSE

V. PULSE

6.13 MHz

TRF1147T

8MHz CLOCK

TCR1056

RESET

CIRCUIT,

5V

GND

2-2

Page 13

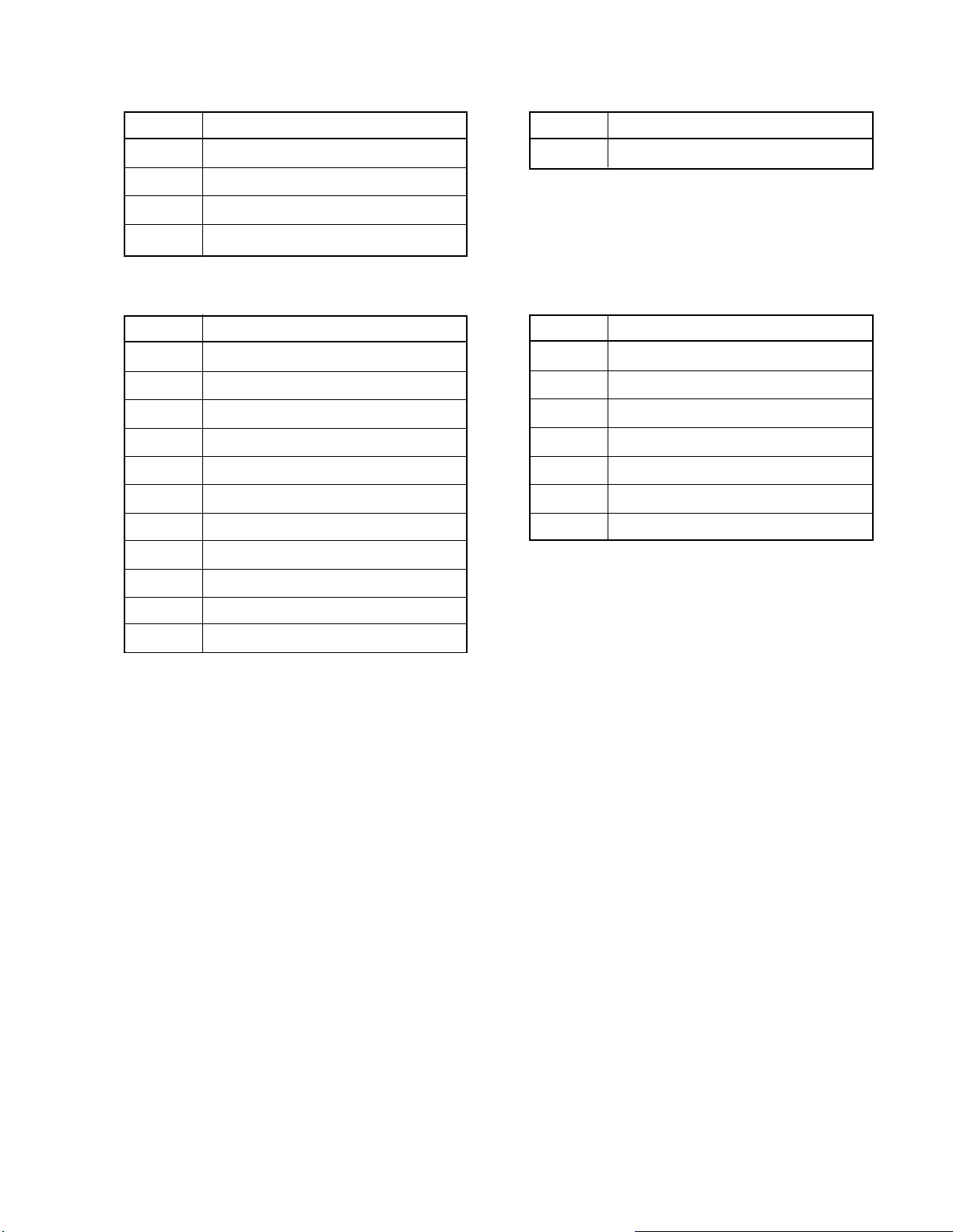

3-1 Microcomputer Terminal Name and Operation Logic

Terminal No. Terminal name I/O control resistor

1 RELAY Positive logic

2 P.B

3

4 MUTE Positive logic

5 STB T BUS PERIOD

6 CLK T BUS CLOCK

7 DATA T BUS DATA

8 I-CSTOP Negative logic

9 AFT

10 EXTA TV: H VIDEO/RGB: L

11 SPKOFF Negative logic

12 LINE21

13 KEY1 Local key input 0~5V

14 KEY2 Local key input 0~5V

15 MODE RGB MODE input 0~5V

16

17 Y IN

18 B IN

19 G IN

20 R IN

21 VSS GND

22 R

23 G

24 B

25 Y

26 HD H sync pulse input

27 VD V sync pulse input

28 OSC1

29 OSC0

30 TEST For microcomputer shipping test. Fixed low level

31 X IN

32 X OUT

33 RESET Negative logic

34 STOP Negative logic

35 RMT Remote controller signal det. Negative logic

36 SYNC Sync pulse signal input

37 SCL I2C BUS CLOCK

38 SDA I2C BUS DATA

39 TC1 GND

40 CSIN

41 VIN

42 VDD Microcomputer power supply

Oscillation connection terminal for OSD circuit

6.13MHz TRF1147T

High frequency oscillation connection terminal

Part for caption

2-3

Page 14

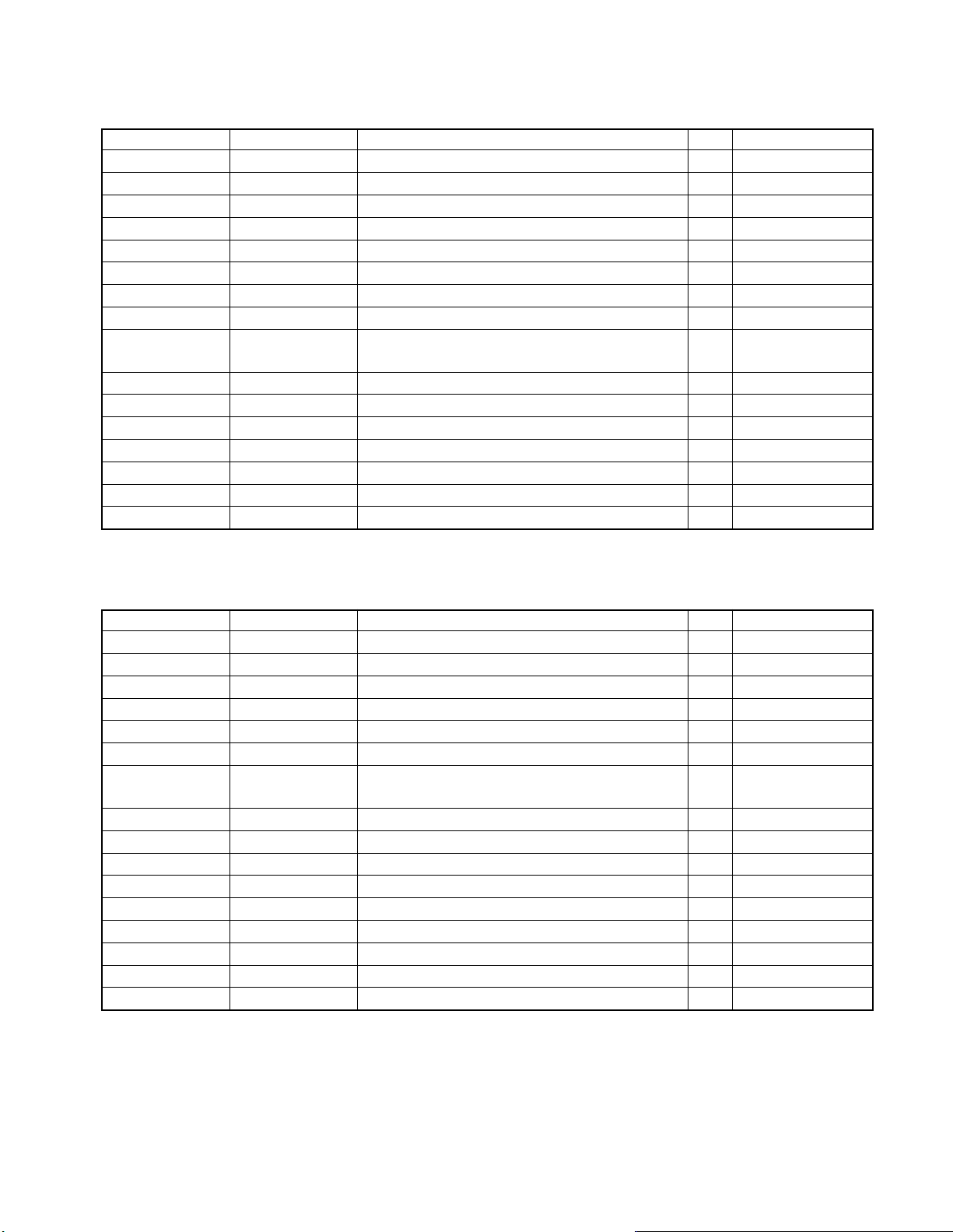

3-2 DAC Terminal Name and Operation Logic

(1) DAC (QX01)

Terminal No. Terminal name Function I/O Logic

1 VDD INTERFACE POWER SUPPLY

2 DAT T-BUS DATA INPUT TERMINAL I

3 CLK T-BUS CLOCK INPUT TERMINAL I

4 PRD T-BUS PERIOD INPUT TERMINAL I

5 RESET

6 SUB-ADDRESS CHANGEOVER TERMINAL O

7 RGB CONT RGB CONTRAST O 0~5V

8 VSS GND

9 SBS SUB BASS SYSTEM O ON: L OFF: H

(H at SPK OFF)

10 RGB BRT RGB BRIGHTNESS O 0~5V

11 TNT TINT O 0~5V

12 COLOR COLOR O 0~5V

13 SHARP SHARPNESS O 0~5V

14 BRT BRIGHTNESS O 0~5V

15 CONT CONTRAST O 0~5V

16 VCC POWER SUPPLY

(2) DAC (QX001)

Terminal No. Terminal name Function I/O Logic

1 VDD INTERFACE POWER SUPPLY

2 DAT T-BUS DATA INPUT TERMINAL I

3 CLK T-BUS CLOCK INPUT TERMINAL I

4 PRD T-BUS PERIOD INPUT TERMINAL I

5 RESET

6 SUB-ADDRESS CHANGEOVER TERMINAL O

7 TV/RGB TV/RGB SWITCH TERMINAL O TV: L RGB: H

(L at RGB NO SIG.)

8

9 MUTE VIDEO MUTE O NEGATIVE LOGIC

10 H-POS H-POSITION O 0~5V

11 H-SIZ H-SIZE O 0~5V

12 V-POS V-POSITION O 0~5V

13 TV/RGB TV/RGB SWITCH TERMINAL O TV: H RGB: L

14 NO SIG NON/YES SIGNAL OUTPUT O YES: H NON: L

15 SUB CONT SUB CONTRAST (TV) O 0~5V

16 VCC POWER SUPPLY

2-4

Page 15

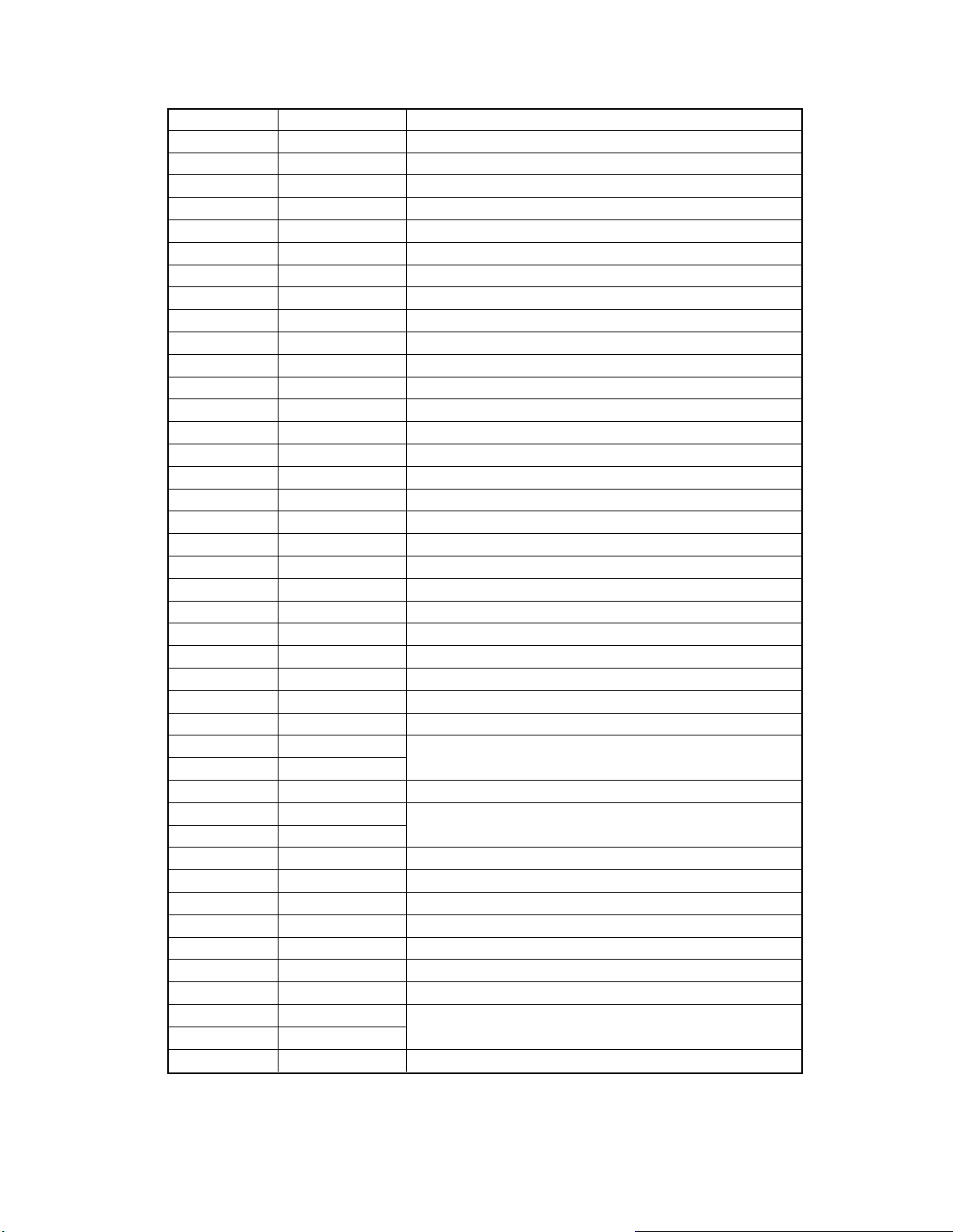

3-3 Remote Control Code Assignment

Custom codes are 40H.

Key

No.

Data

code

Function

K1 00H 0

K2 01H 1

K3 02H 2

K4 03H 3

K5 04H 4

K6 05H 5

K7 06H 6

K8 07H 7

K9 08H 8

K10 09H 9

K11 0AH 100

K12 0BH

K13 0CH RESET

K14 0DH AUDIO

K15 0EH PIC

K16 0FH RGB/TV/VIDEO

K17 10H MUTE

K18 11H

K19 12H POWER

K20 13H MTS

K21 14H OPTION

K22 15H TIMER

K23 16H SET UP

K24 17H CH RTN

K25 18H

K26 19H CONTROL UP

K27 1AH VOL UP

K28 1BH CH UP

K29 1CH RECALL

K30 1DH CONTROL DN

K31 1EH VOL DN

K32 1FH CH DN

K33 40H

K34 41H

K35 42H

K36 43H

K37 44H

K38 45H

K39 46H

K40 47H

K41 48H

K42 49H

K43 4AH

K44 4BH

K45 4CH

K46 4DH

K47 4EH

K48 4FH

Continuity

Key

No.

Data

code

K49 50H

K50 51H

K51 52H

K52 53H

K53 54H

K54 55H

K55 56H

K56 57H

K57 58H EXIT

K58 59H

K59 5AH SET UP

K60 5BH OPTION

K61 5CH

K62 5DH

K63 5EH

K64 5FH

K88 97H

K109 CCH

K110 CDH

K111 CEH

K112 CFH

Function

Continuity

2-5

Page 16

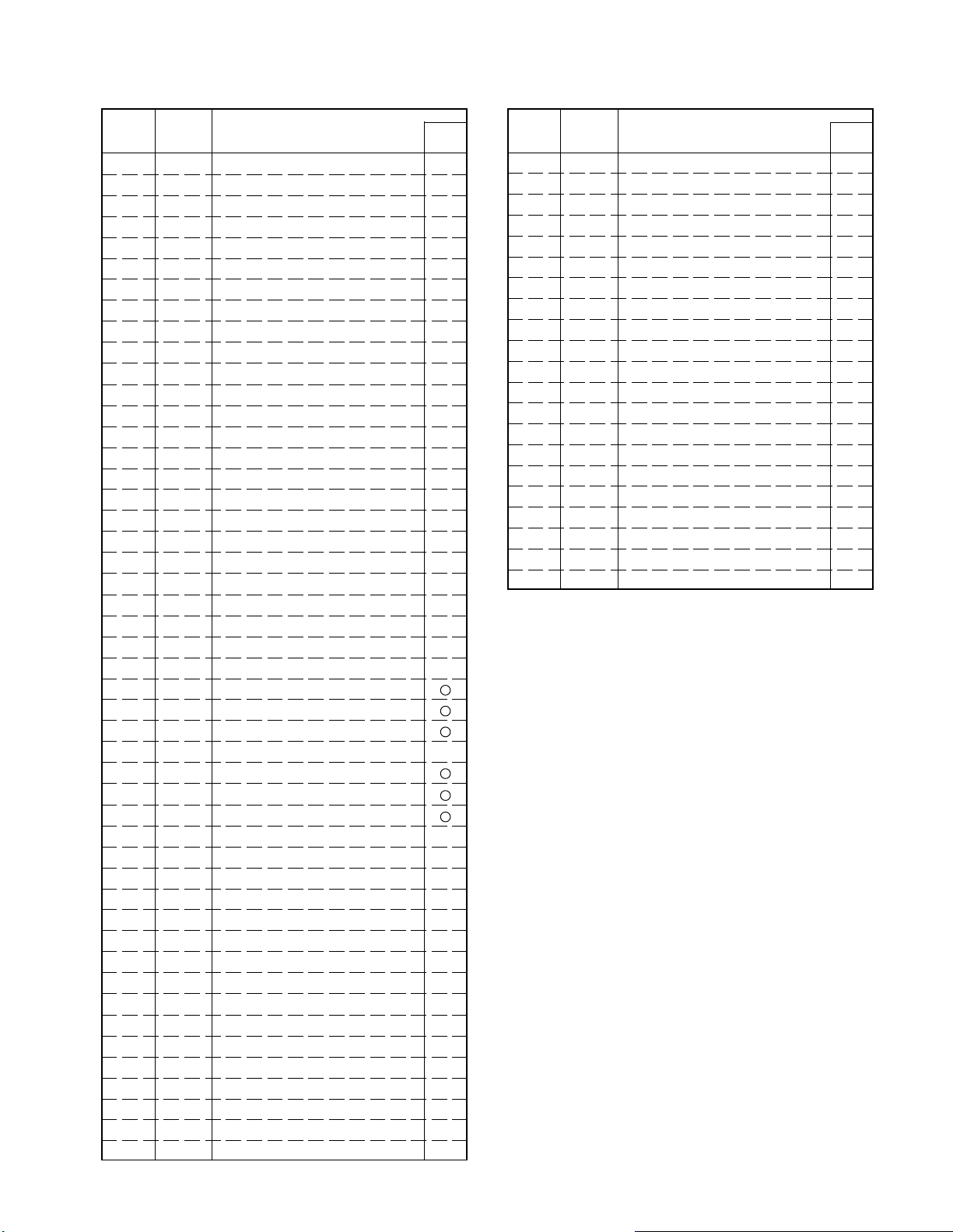

3-4 Local Key Assignment

1. Detection method of Local Key

Detection method of Local Key in N4ES chassis is analogue way to detect what voltage appears at local key input terminals

(pins 13, 14) of Micom when the key is pressed.

By this method, key detections of a maximum of 7 keys can be done, using local key input terminal (pin 13). As seen in the Local

key circuit below, when one of key among S13-1 to S13-7 is pressed, the VIN which corresponds to the switch is applied to input

terminal (pin 13). Judgement of key-input is done by measuring what voltage VIN is at the pin. Voltage measuring and key

judgement are performed by A/D converter in Micom and by the software.

KEY No. Function

S13-1 POWER

S13-2 CH UP

S13-3 CH DN

S13-4 VOL UP

S13-5 VOL DN

S13-6 ADV

S13-7 MENU

S14-1 RGB/TV/VIDEO

LOCAL KEY Assignment table

33K

7.5K

7.5K

11K

16K

30K

68K

KEY1

33K

13 14

S13-1 S14-1

S13-2

S13-3

S13-4

S13-5

S13-6

S13-7

KEY2

2-6

Page 17

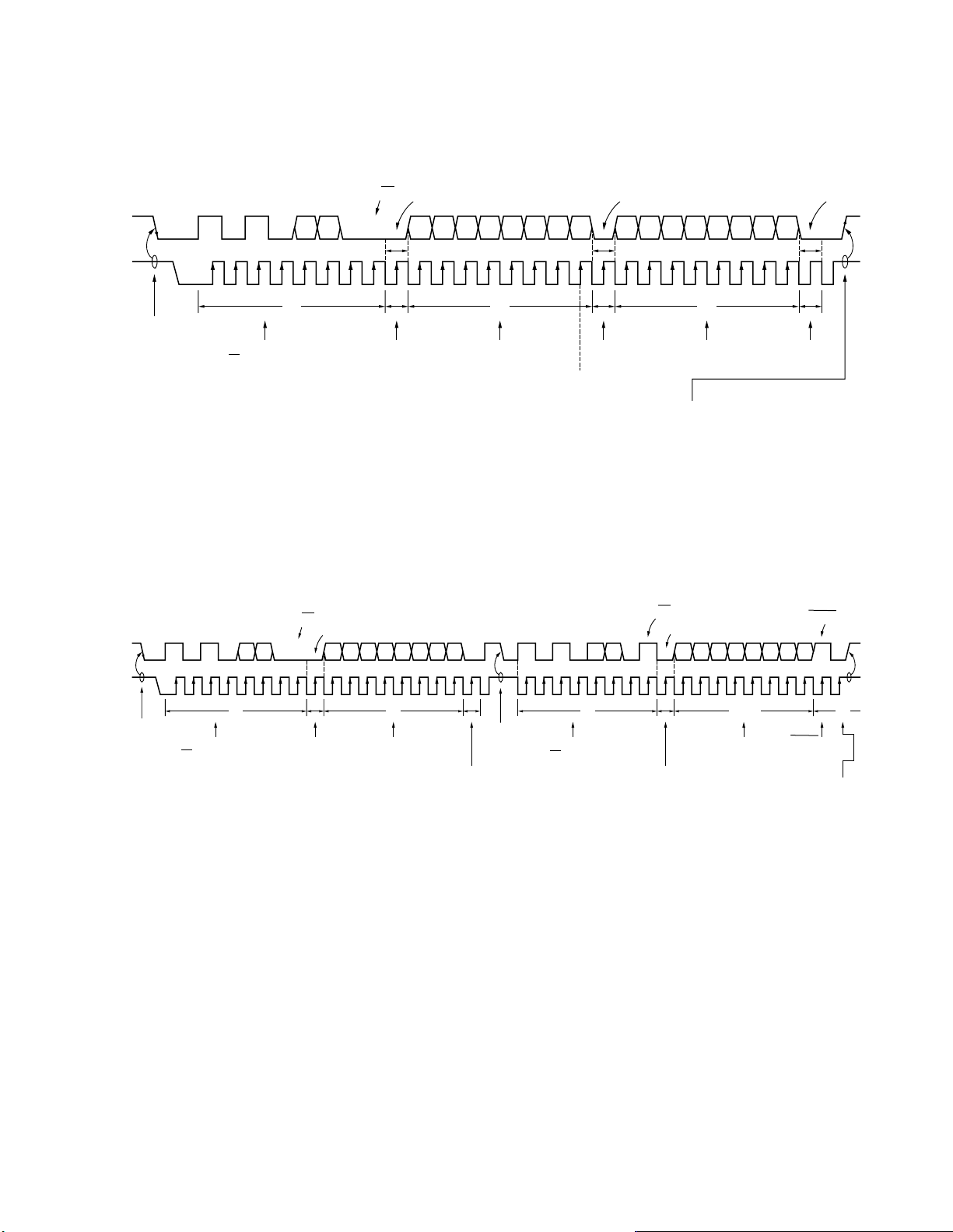

4. I2C BUS INTERFACE OPERATION TIMING

p

As an example of I2C Bus interface operation timings,

control for a memory IC will be shown below.

4-1 Write Mode (1 Byte)

DA

CL

Start bit issue

4-2 Read Mode

SDA

SCL

Start bit issue

1

0

15243

Slave address

R/W command input

Slave address

1

1

0

1

0

Slave address

R/W command input

R/W

2

1

A

0

A

6789

1

ACK signal

output

R/W

A

A

2

1

00

5243

789

6

ACK signal

output

ACK(OUT)

WA7WA6WA5WA4WA3WA2WA1WA

00

Word address

input

ACK(OUT)

WA7WA6WA5WA4WA3WA2WA1WA

Word address

input

Fig. 2-1

0

ININ

Start bit issue

ACK signal

input

ACK(OUT)

D7D6D5D4D3D2D1D

0

ACK signal

output

Word address

update

Stop bit issue

After completion of write operation

word address becomes the write

address +1 and held at that value.

R/W

ACK(OUT)

2

1

A

0

A

6789

1

1

00

15243

IN

Slave address

R/W command input

ACK signal

out

ut

0

INININ

Write data

input

D7D6D5D4D3D2D1D

ACK signal

output

OUT

Read data

output

ACK signal

input

ACK(OUT)

ACK(IN)

0

IN

Stop bit issue

Fig. 2-1

2-7

Page 18

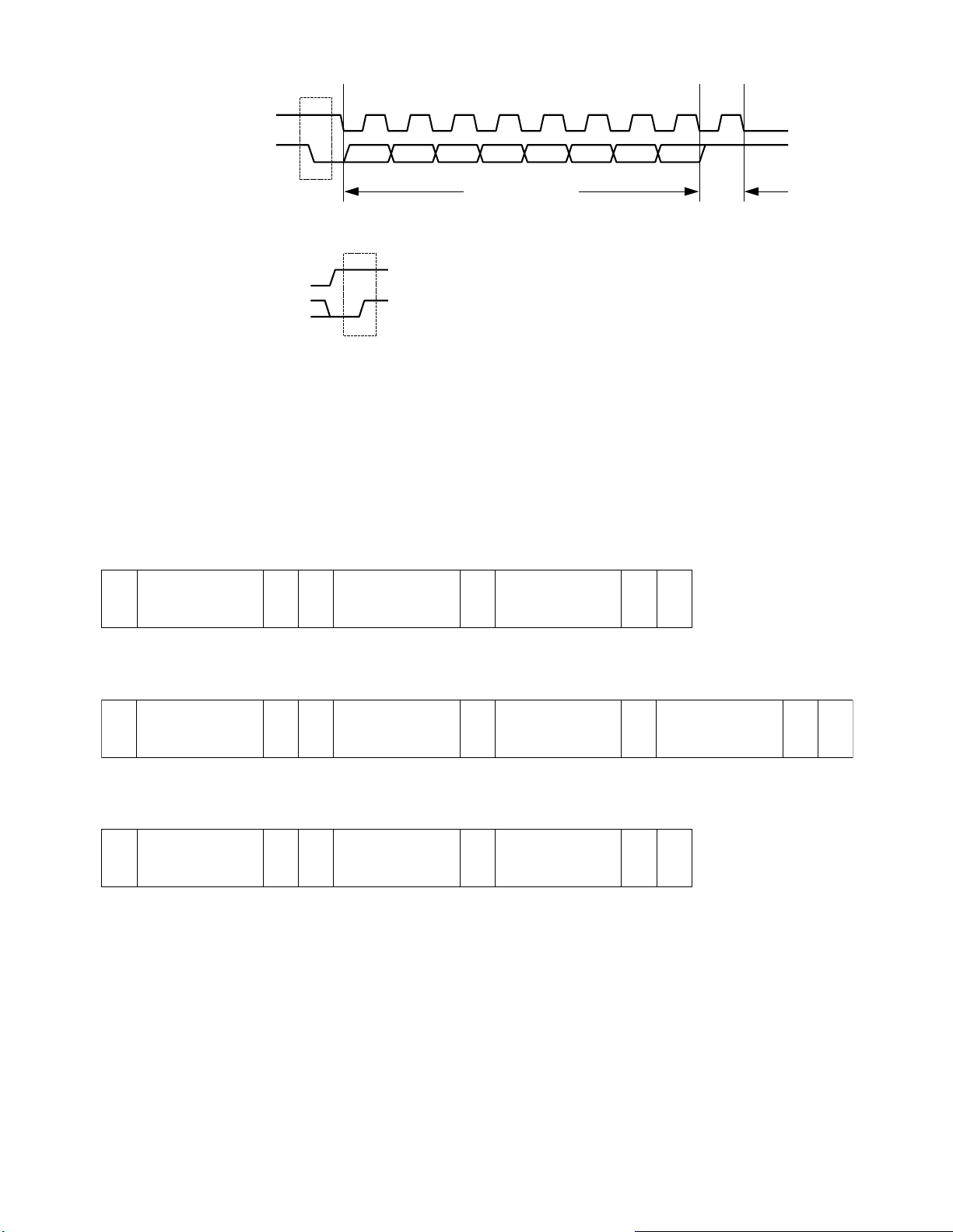

4-2-1 Generation of Start/stop Status

SCL terminal

DA termianl

SCL terminal

SDA termianl

4-3 I2C Bus Data Format

(1) Memory IC

* Write mode

Start

condition

152637489

D7 D6 D5 D4 D3 D2 D1 D0

Data transmission

Acknowledge

signal

Stop

condition

Fig. 2-3

S

Slave address

8 bits

A0H (WRITE)

* Read mode

S

Slave address

8 bits

(2) DPC IC

S

Slave address

8 bits

8CH

RW AC

AC

RW

RW AC

Word address

8 bits

Word address

8 bits

Sub-address

8 bits

AC

AC

AC

Data 8 bits

Slave address

8 bits

Data 8 bits

AC ST

AC

AC ST

Data 8 bits

AC ST

2-8

Page 19

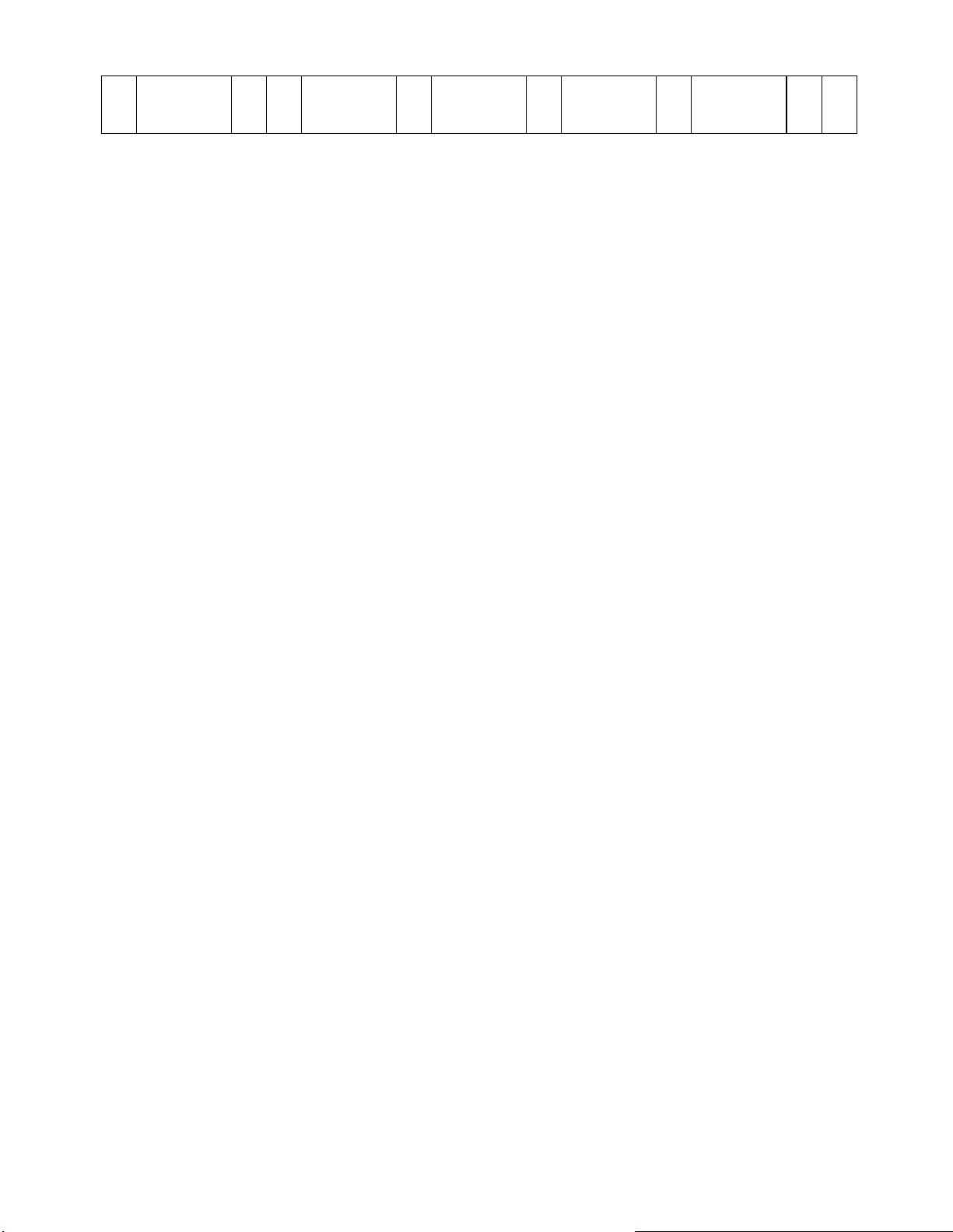

(3) U/V tuner unit

S

Slave address

8 bits

RW AC AC ST

FM

8 bits

AC

Main screen tuner: COH

FM: Variable divider control byte

FL: Variable divider control byte

CO: Charge pump sensitivity switching bit and test mode bit

BA: Band switching bit

FL

8 bits

AC AC

CO

8 bits

BA

8 bits

2-9

Page 20

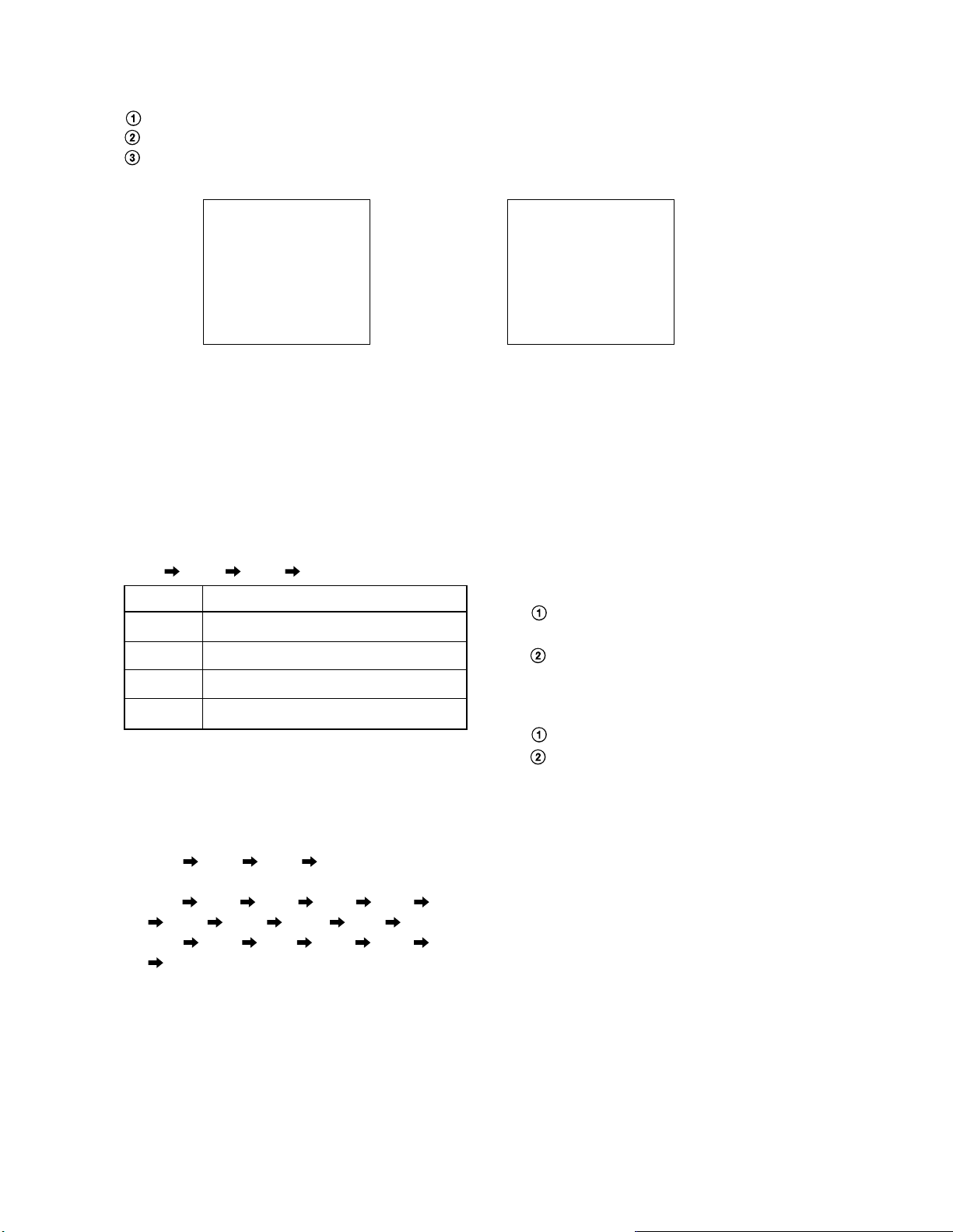

5. SERVICE ADJUSTMENT MODE

1. Entering to Service Adjustment mode

Press MUTE key on the remote control unit once.

Press again the MUTE key, and keep pressing it.

Keep pressing the MUTE key, press MUTE key on TV set.

120H 8DH

Adjusting picture of NTSC mode

2. Switch-over of Service Adjustment mode

Every pressing of MENU key makes main address switch

over.

161H 1E2H 120H 114H

Address

161H Video section sub-adjustment

1E2H OSD horizontal starting position

120H Deflection section sub-adjustment

Adjustment contents

120H 8DH

RGB 350

Adjusting picture of RGB mode

4. Adjusting method of data

Pressing ADJUST UP/DOWN key on remote control

unit changes the data value ranging from 00H to FFH.

5. Cancellation method of Service mode

The operation of key that accompanies display of

other than from 1 to 4 makes the mode cancel.

During servicing in RGB mode, changing of the

mode of RGB causes cancellation.

Address, Data

Mode display of RGB

114H Multi-sound adjustment

3. Switch-over within Service Adjustment mode

Pressing of VOL UP key on remote control unit or on TV

set makes address switch over cyclically, and VOL DN

key switches over in reverse direction.

a) 161H 107H 163H 108H

b) 1E2H

c) 120H 121H 122H 123H 125H 126H

127H 128H 12AH 111H 112H

d) 114H 115H 116H 116H 117H 118H

119H

6. Other service function

MUTE key : Shipping-out preset

RECALL key: Initializing of memory

2-10

Page 21

ADDRESS OF SERVICE MODE

a) Video section sub-adjustment

Address

161H SUB BRIGHT

107H SUB COLOR

163H SUB TINT

108H SUB CONTRAST

c) Deflection section sub-adjustment

Address

120H PICTURE HEIGHT

121H V-LINEARITY

122H V-S CORRECTION

123H V-SHIFT

125H PICTURE WIDTH

126H E-W PARABOLA

127H E-W CORNER

Adjustment contents

Adjustment contents

b) OSD horizontal starting position

Address

1E2H OSD-H.POSI

d) Multi-sound adjustment

Address

114H ATT

115H STEREO VCO

116H SAPVCO (MSB)

116H SAPLPF (LSB)

117H FILTER

118H SPECTRAL

119H WIDEBAND

Adjustment contents

Adjustment contents

128H KEYSTONE

12AH V-CORRECTION

111H HORIZ POSITION

112H VERT POSITION

2-11

Page 22

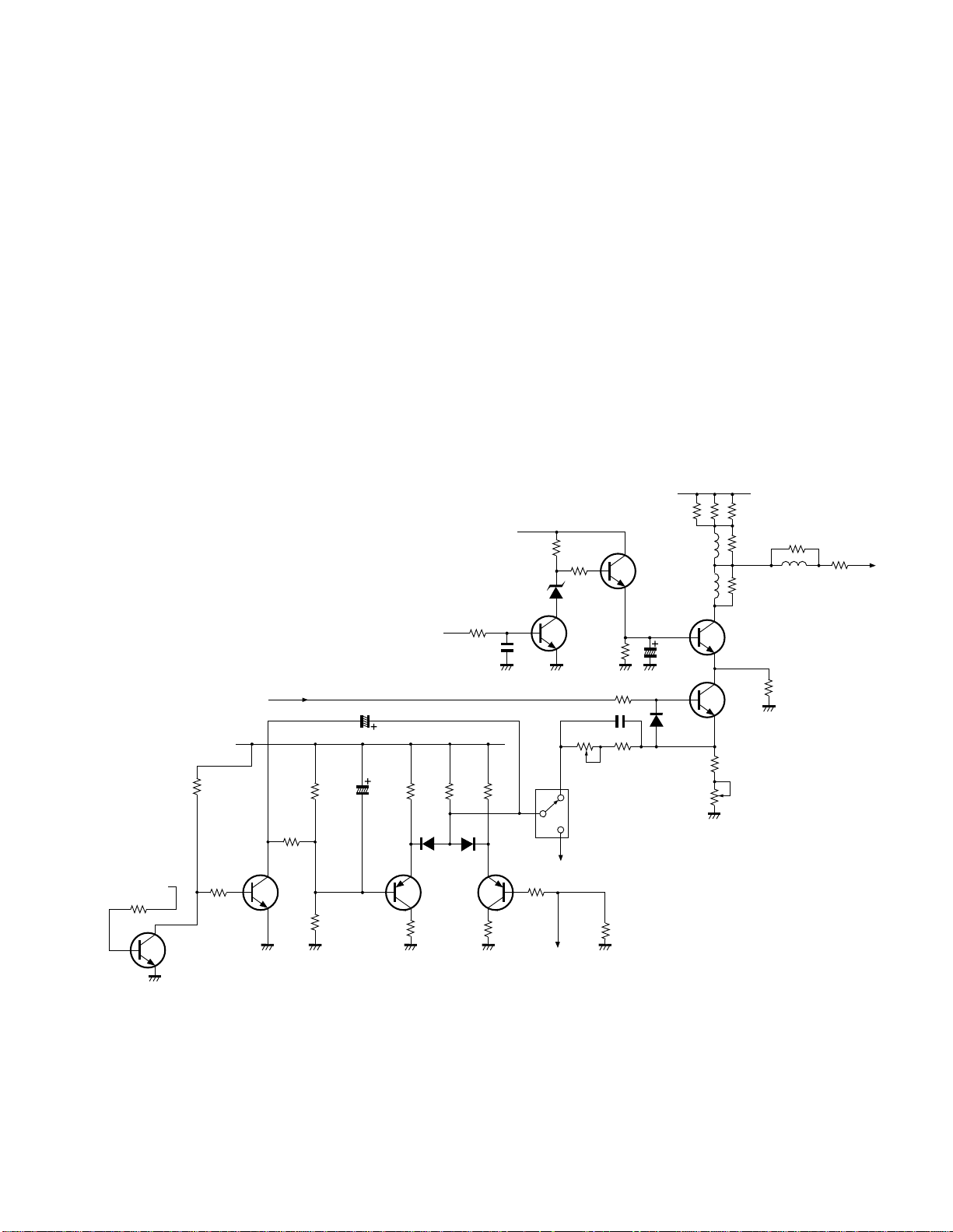

SECTION III RGB SIGNAL PROCESSING CIRCUIT

1. OUTLINE

The signal flow is explained as follows. RGB signal is input

to D-SUB 15P and is processed to be output at CRT Drive

circuit.

2. OPERATION AND FLOW OF RGB

SIGNAL

Fig. 1 shows flow chart of RGB signal.

3. CIRCUIT OPERATION

(1) RGB signal input at D-SUB 15P is supplied to pins 2, 6,

10 of RGB signal processing IC M52327SP respectively.

(2) The signal which is input to RGB signal processing IC,

is processed in four steps ; 1) Amplification, 2) Contrast

control, 3) Brightness control, 4) Black level clamp.

After that, the signal is output at pins 28, 24, 20 and then

is input to pins 1, 2, 3 of Signal switching IC AN5862K.

(3) In TV reception, R-Y, G-Y and B-Y outputs of IC501

TA8801AN are selected by IC216 AN5862K and ICR03

AN5862K, and are output at pins 5, 6, 8 of ICR03

AN5862K.

(4) TV/RGB switching pulse output from ICX001

TB1203AP, OSD switching pulse output from

microcomputer and blanking pulse are input to OR gate

circuit. And output from OR gate is input to pin 4 of

ICR03 AN5862K.

These operations function as following 3 items.

In TV mode, output from ICR03 AN5862K is

turned over to TV.

In RGB mode, OSD signal is made by OSD

switching pulse from OR gate.

In RGB mode, blanking is performed.

A8801AN

R-Y, G-Y, B-Y

utput

MICOM

OSD output

MICOM

Y output

(1)

RGB input

62

10

13 12 11

(3)

ICR02

RGB AMP

M52327SP

1) SIGNAL AMP

2) CONTRAST

3) BRIGHTNESS

4) CLAMP

321

IC216

SIGNAL

SWITCHING

AN5862K

4

3

ICX001

SWITCHING

SIGNAL

GENERATOR

TB1203AP

28 24 20

13 12 11

7

(2)

865

321

ICR03

SIGNAL

SWITCHING

AN5862K

4

(4)

OR

GATE

865

Signal

output

Blanking pulse

Fig. 1

3-1

Page 23

SECTION IV CRT DRIVE CIRCUIT

1. OUTLINE

CRT Drive circuit is designed with its output load resistance

decreased, to obtain wide frequency band, and heat-sink of

output transistor is enlarged in size. Cut-off control and

Drive control of TV signal are adjusted with variable resistors

on CRT drive circuit, otherwise RGB signals are adjusted by

bias control and gain control of RGB AMP ICR03 M52327SP.

2. CIRCUIT OPERATION

For example, Green axis circuit is explained as follows.

(1) G signal which is output at pin 6 of AN5862K, is

supplied to the base of Q904, and is amplified in wide

band by Q903 and Q904. Then it is input to cathode of

CRT.

(2) The level of pin 7 of ICX001 TA1203AP becomes (L)

in RGB and (H) in TV. Utilizing this level change,

emitter bias level of Q904 is changed over RGB mode

and TV mode.

(3) The MUTE signal is generated at pin 9 of ICX001 in

POWER ON/OFF, CH selecting, MODE changing.

This signal turns Q903 to cut-off to prevent disorder of

picture from displayed on screen.

(4) Cut-off and Drive controls can be adjusted with R952

and R954.

+200V

+12V

RR25

DR08

RR26

L905

QR05

L904

R922, R923, R924

R925

R921

L906

R920

R926

KG

ICX001 TA1203AP

TV/RGB

Pin7

R209

Q206

+12V

R207

R941

ICR03

Pin6

R943

R942

Q907

ICX001 TA1203AP

MUTE Pin9

C909

C910

R944

R946

R964

R945

D904

Q908

RR24

CR13

R947

D905

Q904

Fig. 1

R961

DEF Circuit

R948

-Y

QR04

R927

R954

SERVICE

SWITCH

R914

C904

R918

R949

Q903

C907

R915

Q904

D902

R918

R952

4-1

Page 24

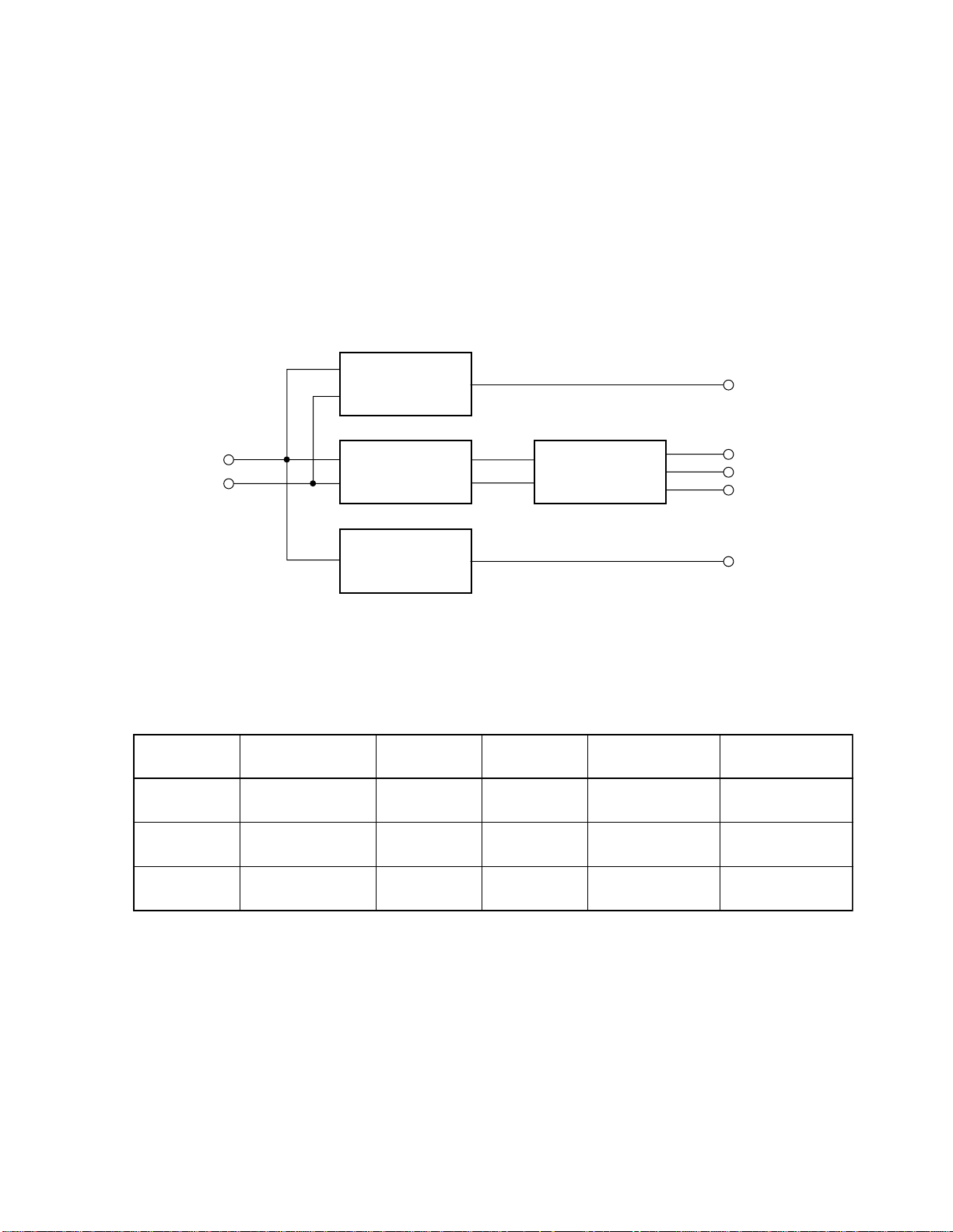

SECTION VMODE DISCRIMINATION CIRCUIT AND SYNC

SIGNAL PROCESSING CIRCUIT

Mode discriminating circuit performs to discriminate the kind of signals ; the signal which is input to D-SUB connector, is VGA,

or is Macintosh signal.

Sync signal processing circuit performs to process sync signals into shape which can be utilized in horizontal and vertical osc

circuits, because the signals which are input to D-SUB connector from a personal computer have various figures.

1.OUTLINE OF MODE DISCRIMINATING CIRCUIT

This model, for the simplification, reduces discriminating functions than CRT monitor for computer. The functions are those:

to identify VGA signal or not; horizontal scanning frequency is higher or lower than 28kHz; the signal is input or not.

NO SIGNAL

DISCRIMINATION

ICH01, QH06

No signal

Hor. sync

Vert. sync

POLARITY

DISCRIMINATION

ICH01

FREQUENCY

DISCRIMINATION

ICH04, ICH05

DECODER

ICH02

VGA480

VGA400

VGA350

Low frequency

Fig. 1

VGA has three modes by number of vertical line. These are made to be able identify by polarity of horizontal and vertical sync

signal. The difference of VGA mode signal is described in Table-1.

Kind No. of Ver. line fH fV Hor. Sync polarity Ver. Sync polarity

VGA480 480 31.5kHz 60Hz Negative Negative

VGA400 400 31.5kHz 70Hz Negative Positive

VGA350 350 31.5kHz 70Hz Positive Negative

Table-1

The above discriminated output is supplied to Ch. selection IC ICA01, and to be used as a sign to switch operations of related

circuit.

5-1

Page 25

2. OUTLINE OF SYNC SIGNAL PROCESSING CIRCUIT

As mentioned above, signal input at D-SUB connector from personal computer, sometimes shows various shape of sync signal.

Representative signals are described in Table-2.

Kind Resolution fH Fv Hor. Sync polarity Ver. Sync polarity

IBM PGC 640 x 480 30.5kHz 60Hz Composite Sync

IBM VGA480 640 x 480 31.5kHz 60Hz Negative Negative

IBM VGA400 640 x 400 31.5kHz 70Hz Negative Positive

IBM VGA350 640 x 350 31.5kHz 70Hz Positive Negative

SVGA 800 x 600 35.2kHz 56Hz Positive Positive

Macintosh 13Ó 640 x 480 35.0kHz 67Hz Sync on Green or Composite Sync

VESA VGA 640 x 480 37.9kHz 72Hz Negative Negative

Table-2

Roughly classified, they are of two shapes; one is, like Macintosh, SYNC ON GREEN which is imposed on video signal, and

the other is the output in TTL level separated from video signal. The TTL level method is classified to Composite Sync which

combines horizontal and vertical sync, and to Separate Sync which separates respectively.

And besides, in Separate Sync method, polarity is different by kind of signal.

Even though these various sync signal are input, always positive polarity of hor and ver sync signal is supplied to horizontal

and vertical sync osc circuit. This is the role of this circuit.

5-2

Page 26

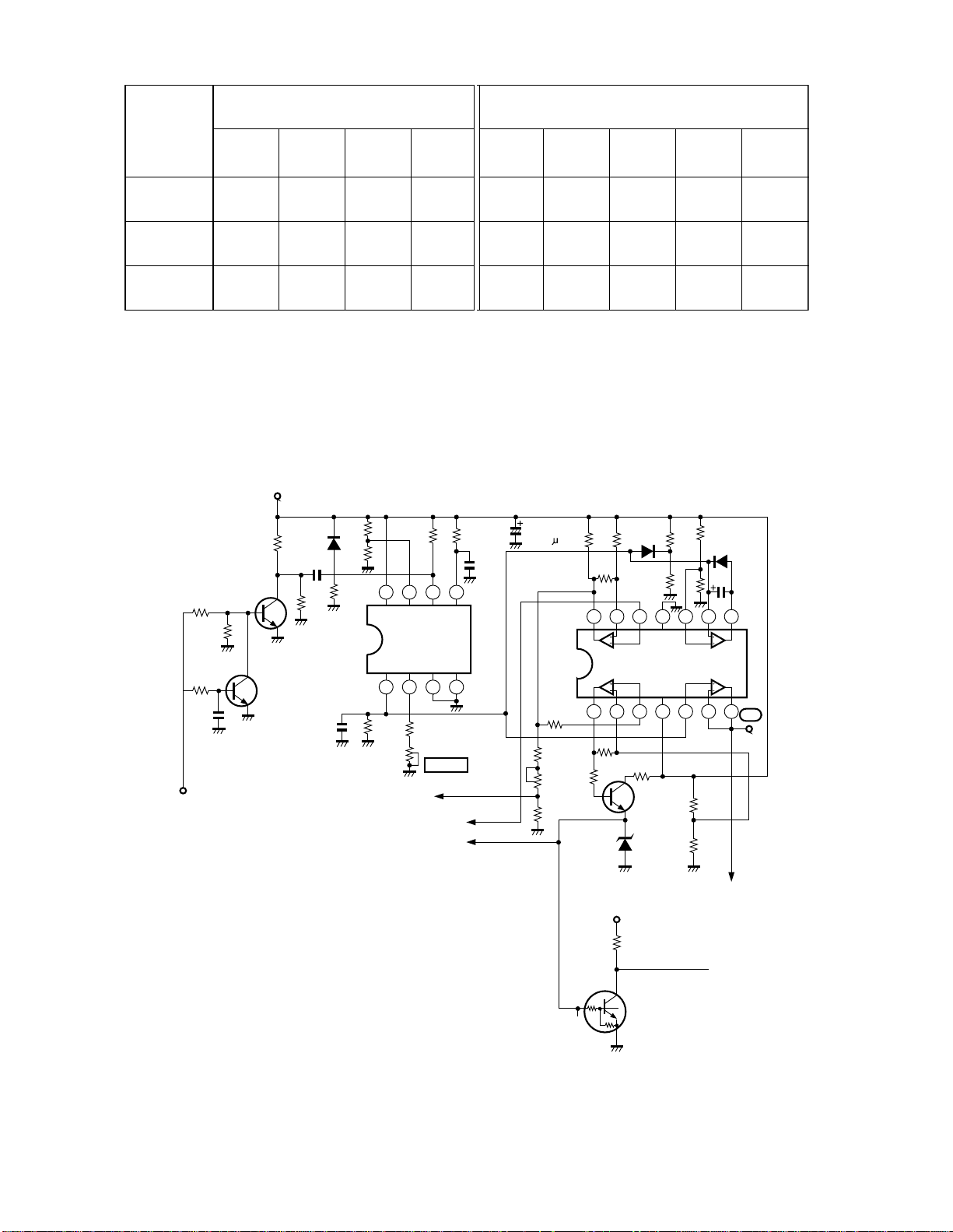

3. MODE DISCRIMINATING CIRCUIT OPERATION

h

The circuit which discriminates three modes of VGA, is as follows.

DH31

19 18

ICH01

M52346SP

13 12 11 10

BCDA

ICH02

TC4028BP

fH > 28KHz/Hig

FREQUENCY

DISCRIMINATION

2

Hor. sync

Vert. sync

6 8 4 6 7

VGA350

VGA400

VGA480

Fig. 2

Mode discrimination of VGA is done by the circuit in Fig. 2. ICH01 M52346SP also performs process of sync signal, and the

logic output is shown in Table-3. ICH02 is Decoder IC TC4028BP, and the truth table is shown in Table-4.

Input at pin 6

H. COMP.

H. COMP. (POS.)

H. COMP. (POS.)

H. COMP. (POS.)

H. COMP. (NEG.)

H. COMP. (NEG.)

H. COMP. (NEG.)

NON

NON

NON

Input at pin 8

V.

NON

V. (POS.)

V. (NEG.)

NON

V. (POS.)

V. (NEG.)

NON

V. (POS.)

V. (NEG.)

Output pin

1 2 18 19

H

L

L

H

H

H

H

H

H

L

L

L

L

H

L

L

H

H

H

H

H

L

L

H

L

H

L

L

L

H

L

L

H

L

L

H

Table-3. Logic output of M52346SP Table-4. Truth table of TC4028BP

When Macintosh signal is input in form of negative composite sync, diode DH31 prevents confusion between Macintosh signal

and VGA400.

5-3

Page 27

The outputs of VGA three modes are tabled as in Table-5.

ICH01 M52346SP ICH02 TC4028BP

Kind

pin 6 pin 8 pin 18 pin 19

pin 11

(D)

pin 12

(C)

pin 13

(B)

pin 10

(A)

output

(High)

VGA480 Nega Nega H H L H H H pin 4

VGA400 Nega Posi H L L H L H pin 6

VGA350 Posi Nega L H L H H L pin 7

Table-5

As shown in table above, since the result of frequency discrimination is input to pin 12 (c) of decoder ICH02, in case that

frequency of input signal is lower than 28kHz, the mode is discriminated as not VGA mode even though polarity of sync signal

is same combination as VGA.

Operation of frequency discriminating circuit is explained as follows, and configuration is shown in Fig. 3.

+12V

RH90

27K

RH64

33K

RH48

22K

CK24

M0.015

Hori. Sync

RH09

QH03

2SC752Y

DH03

1SS176

or

1SS133

12K

CH12

SL100P

RH10

QK11

2SC1815Y

or 2SC17405,Q

or 2SC1685Q

18K

CH14

M2.2

RH12

10K

RH13

10K

RH11

15K

RH14

10K

7

8

ICH04

IR9331

F/V CONVERTER

2

1

RH16

RH18

1/4W4.7KF

1/4W

82KF

3

2

1

F/V ADJ

H. OSC

Def. circuit

6

3

RH17

2KB

5

4

RH15

5.6K

CH13

T1200

CH15

16V47

2

RH19

68K

RH21

1/4W11KF

RH75

8.2K

RH24

1/4W3.3KF

1

RH52

10K

3

RH26

1/4W1.8KF

RH20

1/4W

47KF

13

14

2

1

RH28 580K

+5V

DH04

1SS176

or

1SS133

RH23

1.8KG

11

12

ICH05

TA75902P

or LM2902N

3

4

RH27 680

QH10

2SC1815Y

or 0

DH06

RD5.1ESAB1

or UZ5,1BSA

RH22

560KG

RK59

10

5

RK58

33KG

12KG

98

6

RH29

1/4W

13KF

RH30

1/4W

8.2KF

DK17

1SS176

1SS133

7

H.Size

or

CK17

M680

F/V

LOW FREQ

QH09

RN1202

Fig. 3

ICH04, F/V (Frequency-Voltage) converter, produces the voltage proportional to hor. scan frequency of input signal.

This voltage is amplified in ope. amp ICH05. The comparator which is consisted of ICH05, compares frequency to operate

so that emitter voltage of OH10 becomes HIGH level when the frequency is high.

5-4

Page 28

Block diagram of ICH04 IR9331 is shown in Fig. 4.

t

Vcc

8

Current Output

Reference Voltage

Frequency Output

Current

1

2

Output Circuit

3

SW

1.90V

15

Mirror

Circuit

11

Reference

1.90V

Voltage

Each

Bias

Circuit

4

GND

Fig. 4

Comparator

R-S

Flip Flop

Timer

Comparator

R

7

6

5

2R

Comparator Inpu

Threshold

R-C

Operation of F/V converter circuit using this IC are as

follows.

When horizontal sync signal is input to pin 6 of IC through

QH03, this performs as a trigger, charge of capacitor CH13

which is connected to pin 5 begins. Voltage at pin 5 is

compared with reference voltage(Vcc x 2/3) by the comparater

inside IC, and the voltage finally reaches the reference

voltage to reverse the comparater. This reverse operation

discharges the capacitor rapidly. Next, when hor sync signal

comes, this operation is again repeated.

The period that this capacitor is being charged is constant, in

spite of input signal.

Hor. Sync

pulse

Voltage

of pin6

Voltage

of pin5

Current

of pin1

0

2

Vcc

3

0

0

1.9V

RH16+RH17

5-5

Tc

TH

Fig. 5

Page 29

In this period, current is supplied to capacitor CH14. This

y

current is a constant current which is made in CURRENT

MIRROR circuit, and is set with resistor RH18 connected to

pin 2. The voltage (1.9V) at pin 2, which is divided by

resistance of RH18, produces the current. The current flows

through CH14. Therefore, average voltage at pin 1 is decided

by the formula below.

1.9V

E =

RH16+RH17

RH18

•

TC

1.9V

=

•

TH

RH16+RH17

• 82kW •TC • fH (V)

DH04, RH22 and RH23 perform to limit F/V convert voltage

so that it does not rise extremely, even though the higher

frequency than responsive range of this model, is input. The

circuit using Ope Amp from pin 8 to pin10 of ICH05 limits

F/V convert voltage so that it does not decreases below

specified value when input signal does not come.

The voltage at pin 1 which is limited by the upper and lower

values, is amplified through amplifier of from pins 12 to 14

of ICH05. The amplifying character is set to the suitable one

to control free-running frequency of hor osc circuit.

As understanding from the above formula, at pin 1, the

voltage which is proportional to frequency of hor sync

signal, is obtained.

QK11 performs the function to prevent picture bending on

screen by the increase of F/V convert voltage, because the

period of equalized pulse is seemed as twice of frequency

when composite sync including equalized pulse like NTSC

within hor sync. is input. Countermeasure to this trouble is

to eliminate trigger pulse only for ver sync period.

Operation of no signal det. circuit is as follows.

M52346SP

Output voltage of this amplifier is compared with the reference

voltage by the comparater of pins1 to 3. When hor frequency

is high, the voltage at pin 1 becomes HIGH level. The

reference voltage of this comparater is selected so that the

comparater turns reverse when frequency is approximately

28kHz. The output of the comparater turns reverse to

become mode discriminating output, and besides it is used to

switching of circuit operation at some points in the hor

deflection circuit.

+5V

14

ICH01

86421

No signal

QH07

Green Video

Hor. sync

Vert. s

nc

QH06

Fig. 6

ICH01 is used in this circuit, which is explained in Mode discriminating circuit of VGA. This IC contains inside the function

which discriminates existence of hor-ver sync signal at pins 6 and 8. When the sync signal as shown in Table-3 does not exist,

logic outputs at pins 1 and 2 turn LOW to level. But, in Sync On Green method, discrimination whether sync signal is existed

or not is impossible. Therefore discriminating circuit is added by connecting QH06 to pin 14 at which hor sync signal is input.

The added circuit performs that emiter voltage turns to LOW level only when hor sync signal does not exist.

No signal situation is detected by way that these three output is set up in OR logic by diodes, collector voltage of QH07 is turned

to HIGH level.

5-6

Page 30

4. SYNC SIGNAL PROCESSING CIRCUIT

This circuit also employs ICH01, the same as Mode discriminating circuit.

Posi Non

Posi Non

Posi Non

Posi Non

Posi

Posi

Non

Non

H.Pol.

Neg

Neg

V.Pol.

Neg

Neg

H.State

Neg

Neg

V.State

Neg

Neg

Clamp

Clamp

Timing

20 19 18 17 16 15 14 13 12 11

Logic

Logic

1

Green

Sep

Filter

Clamp

Gen.

Clamp

Out

Sync

Sep.

Green

IN

Green

Edge

SW

Vcc

5432

GND

12V

HD

Out

Comp/H

IN

Comp/H

Hor.

Shape

Comp/H

Out

Det

HD

Hor.

Det

H.Det

VD

Out

Vert

IN

Vert.

Shape

Vert

VDHDHD

Digital

GND

Vert

Det

Vert.

Det

+

Vert

S/S

IN

V.Sync

Sep.

9876

10

Vert

S/S

Adj

Digital Vcc

(5~12V)

GND

Sync signals are input as follows; TTL level hor sync or

composite sync to pin 6, TTL level ver sync to pin 8, and Sync

On Green sync to pin 4. Output signals are as follows;

Positive ver sync at pin 13, Positive hor sync at pin 14 and

Negative hor sync at pin 15.

When plural sync signals are at the same time input, the

priority order is decided as in Table-6.

Fig. 7

Input signal (pin) Output signal (pin)

pin 4 pin 6 pin 8

O

O

O

O

X

X

X

X

X

O

X

O

X

O

X

O

pin 14

pin 15

X

X

O

O

X

X

O

O

pin 13 pin 17

4

6

4

6

X

6

X

6

Table-6. Priority order of output

11

11

11

4

6

6

8

X

4

6

X

6

8

8

X

6

5-7

Page 31

5. INTERFACE OF MODE DISCRIMINATING CIRCUIT AND CH. SELECTION MICOM

The result of mode ident. explained in Section 3 is converted to d.c. and is supplied to pin 15 of Ch. Selection Micom ICA01.

ICA01

RGB MODE

QA05

RN1202

CA27

M0.01

VGA480

RA54

16K

QA06

RN1202

VGA400

CA28

M0.01

RA51

16K

RN1202

VGA350

Micom ICA01 recognizes kind of input signal by the voltage

at pin 15, reads out data which are stored in memory and

controls operation of deflection circuit like width, distortion

and picture position, and send them to circuits.

The memories controlling this deflection circuit are equipped

by 1 set for TV mode, and by 4 sets for RGB mode. In RGB

mode, 3 sets are used for VGA and reminder 1 set is used for

Macintosh and other signal than VGA. And when signal is

not input in RGB mode, micom supplies switching signal so

that deflection circuit only operates in TV mode.

+5V

RA49

33K

QA07

CA29

M0.01

RA52

11K

QA08

RN1202

LOW FREQ

CA30

M0.01

RA53

7.5K

QA09

RN1202

NO SIG

RA50

7.5K

CA31

M0.01

Fig. 8

When frequency of input signal is lower than 28kHz, micom

switches over automatically the size and display position of

OSD character.

The relation of input signal state and voltage at pin 15 of

ICA01 is shown in Table-7.

Input signal AD conversion value (H) Center voltage (V

Mac. and other

than VGA

E0 ~ FF 4.71 A A’

C0 ~ DF 4.08

)

Kind of memory

Sub data User data

VGA480 A0 ~ BF 3.45 B B’

VGA400 80 ~ 9F 2.82 C C’

VGA350 60 ~ 7F 2.20 D D’

LOW FREQ 40 ~ 5F 1.57 A A’

No signal

20 ~ 3F 0.94

00 ~ 1F 0.31

TV mode E

Table-7

5-8

Page 32

SECTION VI SYNC SEPARATION CIRCUIT OF TV MODE

Sync separation of TV mode is done by the circuit contained in V/C/D IC the same as ordinary TV.

This output signal and sync signal from RGB input, are switched in latter stage and are applied to hor and ver osc circuit.

Operation of sync separation of V/C/D IC is as follow, though the switching circuit is explained later.

1. SYNC SEPARATION CIRCUIT

The sync separation circuit separates a sync signal from a

video signal and feeds it to an H and V deflection circuits.

The separation circuit consists of an amplitude separation (H

and V sync separation circuit) and a frequency separation

circuit (V sync separation circuit) which performs the

separation by using a frequency difference between H and V.

Sync

Composite

video

signal

input

61

Q501

H. V SYNC

SEPARATION

CIRCUIT

Fig. 1 Sync separation circuit block diagram

In the N4ES chassis, all these sync separation circuits are

contained in a V/C/D IC (TA8801AN).

Fig. 1 shows a block diagram of the sync separation circuit.

H sync signal

Pin

5

V SYNC

SEPARATION

CIRCUIT

WAVEFORM

SHAPEING

CIRCUIT

V sync signal

(Reset pulse)

Pin

1

6-1

Page 33

2. THEORY OF OPERATION

2-1 H, V Sync Separation Circuits

Fig. 2 shows a basic sync separation circuit and Fig.3 shows

a composite video signal.

When a composite video signal is applied Fig. 2:

(1) The transistor is forward-biased with a voltage charged

into the coupling capacitor turns on, so, a sync signal

shown in Fig. 4 is developed at point .

H.Vcc

A

Charging

Composite

video signal

RS

C

Discharging

Tr

RB

Fig. 2 Basic circuit

(2) The transistor is reverse-biased with a voltage charged

into the coupling capacitor C for a period other than the

sync signal period, and becomes non conductive status.

(3) The charging time constant TC and discharging time

constant TD in the basic circuit are given by following

equations.

TC = C x (RS + RD)

(Note: RD = resistance between B – E)

TD = C x (RS + RB)

(4) If the discharging time constant is set to a considerably

large value compared with the H scanning time, base of

the transistor is set to a negative potential for a long

period. That is, the sync separation transistor is reversebiased and becomes non conductive status for the

video signal period, thus only the sync signal is

extracted. The sync signal obtained in this stage is fed

to the H AFC circuit and V integration circuit.

Fig. 3 Composite video signal

Fig. 4 Sync separation output

2-2 V Sync Separation Circuit

To separate a V sync signal from the composite sync signal

consisting of V and H sync signals mixed, two stages of

integration circuits are provided inside the IC.

The circuit consists of a differential circuit and a Miller

integration circuit, and has following functions.

(1) Removes H sync signal component.

(2) Maintain stable V sync performance for a tape recorded

with a copy guard.

(3) Stabilized V sync performance under special field

conditions (poor field, ghost, sync depressed, adjacent

channel best).

The V sync signal separated in this stage is processed in a

waveform shape circuit and then used as a reset pulse in the

V division circuit as stated later.

6-2

Page 34

SECTION VII HORIZONTAL AND VERTICAL OSCILLATION CIRCUIT

Ordinary TV uses the osc circuit contained inside V/C/D IC, but this model can not use this due to Multi Scan TV covering 15kHz

to 40kHz. Other IC ICH08 (LA7860) for oscillation is added. This IC is for CRT monitor, and the hor osc frequency, the hor

phase and the duty ratio of hor output pulse can be controlled by d.c. voltage. Block diagram is shown below.

12V

VRS

V.BLK

Vvs

V.OUT

2nd delay

To

14pin

12k

0.01µ

VR2

5k

0.01µ

V.BLK

Vhg

1200p

V.D

V.D

4.7µ

3300p

H.LOCK

0.01µ

VR3

5k

AFC

V/I

To

14pin

12k

Vosc

1.8k

100µ

SAW

SW2

2

1µ

100

0.001µ

V.SYNC

0.1µ

330k

1µ

V.Ref

V.OSC

1st delay

123456789101112131415

EN

0.01µ

0.01µ

H.SYNC

0.015µ

RAMP.G

To

14pin

Vh

560p

VR1

5k

12k

18k

5k

22k

To

14pin

1

160p

0.01µ

3.3k

2.2µ

H.LOCK

H.OSC

2.2µ

1200p

22k

470p

0.01µ

FBP

30k

M.M

H.REG

NC12V

9V

60mA

H.D

H.OUT

COMP

1000µ

161718192021222324252627282930

5k

0.01µ

To

14pin

VR4

Vdet

12k

Fig. 1 Circuit for measuring electrical characteristics

7-1

Page 35

1. SECTIONAL EXPLANATION OF IC

4

22K

100

50K

(1) Pin 1 is input terminal of hor sync signal.

Coupling capacitor of 0.01 µF is used to feed hor sync signal

of approx. 2V. For input sync signal, both polarities of

positive and negative can be allowed, and trigger is done on

the front edge.

The pulse width of sync signal which can be input into this

terminal, is 3/20Th (Th: one cycle of hor) or less for both

polarities of positive and negative.

C1

1

180

80K

0.01

H.SYNC

Fig. 2

(3) Pin 3 is control terminal of H. SHIFT.

Range of control voltage is 0 to 2.5V. When control voltage

is 2.5V, phase of FBP become most delayed condition to hor

sync signal.

The hor phase shift controlled by this terminal is decided by

time constant connected to pin 4, and is independent of hor

osc frequency of pin 11.

3

1K

Fig. 4

(2) Pin 2 is ENABLE terminal of hor sync signal.

When this terminal is open, voltage of this terminal turns

LOW condition by inside bias of IC.

At the time, hor osc circuit is locked on hor sync signal which

is input from pin 1.

To turn hor osc circuit to running condition, the voltage of

this terminal is raised to 3V or more.

2

2.5V

100

30K

(4) Pin 4 is time constant circuit to decide hor phase shift

controlled by voltage of pin 3.

H: ENABLE IN

Fig. 3

Fig. 5

7-2

Page 36

(5) Pin 5 is terminal of SHIFT GAIN CONTROL.

Range of control voltage is 0 to 2.5V. When control voltage

is 2.5V, phase of FBP become most delayed condition to hor

sync signal. The hor phase shift controlled by this terminal

is decided by time constant connected to pin 6. And since

phase control by this terminal synchronizes to hor osc

frequency, uses the same value of capacitor as that connected

to pins 6 and 11.

On the assumption that FBP width which is input to pin 18

always constant, when voltage of this terminal is turned to

0V, phase difference does not change with the change of hor

osc frequency.

And when the voltage of this terminal is turned to 2.5V,

phase of FBP is controlled to the delayed tendency comparing

to hor osc frequency input at pin 1: Longer the period of hor

osc frequency is, more delayed the tendency is.

2.5K

5

(6) Time constant of pin 6 decides the phase shift controlled

by pin 5.

100

100

43K

6

Fig. 7

Fig. 6

Ts

Tdelay

H.SYNC [ PIN]

1st DELAY [ PIN]

2nd DELAY [ PIN]

Ts

1/10Th

Tfbp

Tf

1/10Th

Tst

INT.SYNC [ PIN]

FBP [ PIN]

FBP DELAY [ PIN]

SAW [ PIN]

H.OUT [ PIN]

H.OSC [ PIN]

1

4

6

10

18

20

22

15

11

Fig. 8 Timing chart of hor phase control

7-3

Page 37

Ts is decided by the external time constant at pin 4, and is the

first delay value controlled by d.c. voltage of pin 3. This

phase value is not independent of hor period.

Tg is decided by capacitor at pin 6 and resistor at pin 9, and

is the second delay value that is controlled by d.c. voltage of

pin 5. This phase value is the function of hor period.

Tf is delay value of FBP which is decided by time constant

of pin 20.

SAW, which is AFC comparing waveform produced at pin

22, begins discharge at from edge of descent.

In Fig. 8, Tdelay means phase value from the front edge of hor

sync signal input at pin 1, to the center of FBP input to pin 18.

In figure, INT.SYNC is made by comparing triangle wave of

the second delay with a certain voltage. The pulse width of

INT. SYNC is always 1/10Th, independent of control voltage

at pins 3 and 5. Inside IC, the center of INT. SYNC and such

a point that 1/10Th passes from the start time of discharge

of SAW waveform, are controlled to be coincide together by

the AFC circuit.

The control voltage of pin 8 and the hor free-running frequency

fH are represented by the following expression.

(8) Pin 8 is control terminal of hor osc frequency of pin 11.

The range of control voltage is 0 to 2.5V. When this voltage

is 0V, hor osc frequency becomes the lowest frequency, and

when 2.5V, it becomes maximum.

1.8K

8

Fig. 10

(9) Pin 9 gives output of voltage which is added by 1V to the

voltage input at pin 8.

The current decided by external resistor flows through hor

osc circuit, second DELAY, and SAW generator to control

them. Variable resistor RH25 adjusts hor osc frequency.

Fh=(2/3) • 1/(11.5CR) • (V8+1)

Here; V8 : Control voltage of pin 8

C : External capacitor of pin 11

R : External resistor of pin 9

(7) Pin 7 is connected with capacitor which smooths AFC

comparing waveform.

In figure, Vsig is the same signal as the comparing waveform

made at pin 22.

7

100

5K

4.7 F

Vsig

Fig. 9

2K

2K

3K

RH25

RGB

ADJ.

666

9

Fig. 11

(10) Pin 10 is filter terminal of AFC.

The time constant of this filter affects hor jitter. The pull-in

range of AFC is ±4.7%, and does not depend on the constant

of the filter so much.

7.5K

2.2 F

7.5K

25K

10

1K

7-4

Fig. 12

0.027

2.2 F

Page 38

(11) Pin 11 is to be connected with hor osc capacitor.

When shifting control range of frequency to upper or lower,

the value of capacitor is changed as requested.

11

2700pF

Fig. 13

(12) Pin 12 is GND terminal of horizontal block.

(15) Pin 15 is control terminal of H. OUT DUTY.

Controlling the voltage at this terminal from 9V to approx.

7.5V makes possible to regulate the DUTY of H. OUT. The

controlling range is approx. 28% to 66%. DUTY of H. OUT,

when d.c. voltage of pin15 is fixed, is always kept constant

even though hor osc frequency is changed by controlling

voltage at pin8.

15

1.5K

Fig. 15

(16) Pin 16 is hor output terminal.

The output voltage is approx. 5V when the terminal is set in

high impedance. And output current becomes approx. 2mA

when the terminal is connected to ground through 100 ohm.

Internal transistor can accept current of approx. 10mA.

(13) Pin 13 is a low pass filter giving band limit to hor osc

circuit.

1.5K

13

1000pF

Fig. 14

(14) Pin 14 is Vcc terminal of horizontal block.

Since pin 14 has approx. 9V regulator inside IC, current of

approx. 60 mA is applied at this pin.

5.5V

2K

10

50K

16

Fig. 16

(17) Pin 17 is vacant terminal.

(18) Pin 18 is input terminal of FBP

Threshold voltage inside IC is approx. 1.5V. When this

voltage becomes 1.5V or more, Mono-multi which is

connected to pin20, begins operation.

7-5

1.5V

Fig. 17

2K

9V

18

Page 39

(19) Pin 19 is H.LOCK output terminal.

This model does not use this terminal. This terminal gives

output of discriminating result of approx. 5V, when hor sync

signal input from outside of IC and hor output at pin16 are in

synchronization.

(22) Pin 22

Capacitor for producing AFC comparing wave is connected.

The external capacitor is selected so that triangle waveform

at pin22 becomes approx. 2 to 3V. If wave height is small,

the loop-gain of AFC decreases.

920U

MAX

5.7V

1.5K

500

19

Fig. 18

(20) Pin 20

FBP which is input from pin18, is delayed by the time

constant of this pin.

100

100

100

22

30

3300pF

5K

Fig. 20

(23) Pin 23 is GND terminal of Ver block.

(24) Pin 24 is ver output terminal.

The output voltage is approx. 5V when the terminal is set in

high impedance. And output current becomes approx. 2mA

when the terminal is connected to ground through 100 ohm.

Internal transistor can accept current of approx. 10mA.

HIGH period of output is 300 µs, and it is independent of

frequency of ver sync signal which is input at pin 30. By the

control voltage of pin 26; V SHIFT terminal, the rising of this

pin voltage can be delayed by approx. 0 to 470 µs against the

front edge of ver sync signal.

20

150pF

22K

Fig. 19

(21) Pin 21 is a terminal for power source of the ver block.

The rated voltage is 12V.

7-6

0.5V

Fig. 21

2K

50K

10

24

Page 40

(25) Pin 25 is a terminal for ver blanking output.

The output voltage is approx. 5V when the terminal is set in

high impedance.

HIGH period of output is independent of frequency of ver

sync signal which is input at pin 30. This terminal rises at

front edge of ver sync signal, and the rising is delayed by

approx. 100 µs from the rising of pin24.

(27) Pin 27 is a terminal which is connected with capacitor

which produces RAMP wave output at pins 25 and 26.

Recommended value is 0.015 µF, and if this value of capacitor

is increased, respective absolute or maximum values of

Tvshift, Tvd (pin 24 output), and Tvd-vblk (pin 25 output)

can be enlarged, keeping the conditions below.

73U

0.5V

2K

100

68K

25

Fig. 22

(26) Pin 26 is V SHIFT terminal.

The control voltage range is 0 to 2.5V. When this terminal

voltage is 0V, ver output of pin 24 rises at the same time as

ver sync signal. By controlling this terminal voltage up to

2.5V, ver output of pin 24 can be delayed up to 470 µs from

the front porch of ver sync signal.

26

36K

100

27

0.015 F

Fig. 24

Tvshift

Tvd

Tvd-vblk

Tshift : Tvd : Tvd-vblk = 470 : 300 : 100

Fig. 25

V.SYNC

24

PIN VDRIVE

25

PIN VBLK

Fig. 23

7-7

Page 41

(28) Pin 28 is a terminal which produces reference current of

V

ver osc circuit and RAMP wave making circuit.

The recommended value is 330k ohm.

100

28

330K

Fig. 26

(30) Pin 30 is an input terminal of ver sync signal.

Ver sync signal of approx. 2V(p-p) is applied through

coupling capacitor 1µF. For input sync signal, both polarities

of positive and negative can be acceptable, and the sync is

triggered at front edge of sync signal.

50K

300

30

50K

Fig. 28

3.0

(29) Pin 29 is a terminal to connect ver osc capacitor.

Using recommended 0.1µF ±10% allows ver sync signal

ranging from approx. 50Hz to 160Hz to be pulled-in with no

adjustment. To shift the pull-in range upper or lower, the

value of this capacitor is selected to suitable value. Supposing

this capacitor is increased, the pull-in range shifts to lower

in both upper and lower limits of frequencies.

10U

29

100

0.1 F

100

Fig. 27

7-8

Page 42

2. CIRCUMFERENCE CIRCUIT OF IC

2-1 Sync Signal Switching Circuit

The circuit switches the sync signal from V/C/D IC (IC501)

in reception of TV or Video, and the sync signal from sync

processing IC (ICH01) in RGB mode to supply to OSC IC.

As shown in Fig. 29, C2MOS digital IC ICH13 (TC4053BP)

is employed in switching.

Hor.

Vert.

14

13

ICH01

M52346SP

8

6

RGB input

Hor. sync

Vert. sync

The circuit which is consisted of QK13, CK25 and RK50,

operates to eliminate sync pulse only for period of ver sync,

so that in RGB mode top edge of picture does not show AFC

bending affected by ver sync, when composite sync is input.

The sync signals applied to OSC IC ICH08 are both positive.

Hor sync pulse is supplied to F/V convert circuit as well.

+12V

RGB/TV

QH17

14

11

12

13

ICH13

TC4053BP

5

4

3

10

9

30

ICH08

LA7860

1

TV mode

Hor. sync

Vert. sync

To QH03

RK50

QK13

CK25

Fig. 29

7-9

Page 43

2-2 Hor OSC frequency Control Circuit

To synchronizing hor deflection circuit to input signal, the

circuit controls free-running frequency of hor osc circuit

responding with input signal.

In RGB input, by utilizing output voltage of F/V convert

circuit as mentioned above, such control voltage as freerunning frequency automatically follows to input signal

frequency, is applied to pin 8 of ICH08.

But in TV mode, the circuit changes to add the fixed voltage,

not F/V convert voltage.

The reason is to prevent that circuit operation becomes

unstable, because F/V convert voltage varies largely due to

noise in reception of no signal and vacant channel. This fixed

voltage is adjusted with variable resistor RH35, to set freerunning frequency of TV mode.

15

ICH13 the same as above sync signal is used for switching.

The signal to switch the IC is sent though QH17. (See Fig. 29)

When the mode is selected with remote unit or key of TV set,

channel selecting IC sends data which makes voltage at

pin13 of DAC ICX001 5V or 0V, using T-Bus line. This

voltage at pin13 of DAC is supplied to base of QH17 through

buffer amp. QX02. This voltage becomes 5V in RGB mode,

and 0V in TV mode.

+12V

ICH05

12

14

13

ICH04

IR9331

1

6

7

5

ICH05

12

2-3 Hor Phase Shift Circuit

The circuit can adjust hor picture position, by utilizing phase

shift function contained inside ICH08 (LA7860).

This control voltage is supplied from pin10 of DAC IC

ICX001 which receives data from micom ICA01 through TBus line. Therefore, the voltage can be adjusted by remote

unit.

T-Bus

ICH13

+9V

RH35

NTSC

fH ADJ

Fig. 30

Only in RGB mode, the circuit is designed so that user can

adjust to requested condition with remote unit or key of TV

set.

Adjusting data are stored in memory ; Factory adjusting data

are one for TV and four for RGB, User adjusting data are four

for RGB.

8

ICH08

14

ICA01

MICOM

ICX001

DAC

10

ICH08

LA7860

3

ICK09

3

1

2

Fig. 31

7-10

Page 44

H.SYNC

6

RK50

10K

CK25

M0.0056

QK13

2SC1815Y

or 2SC1740S,Q

V.BLK

G

H.V.OSC

RH66

12K

RH67

22K

H

VHP(0~5V)

ICH08

LA7860

VFV

RH57

RK91

12K

15K

Y

LH10

RH56

TEM2009

1K

CH17

50V

1µ

30 29 28 27 26 25 24 23

V.OSC

CH24

M0.01

RH68

33K

RH69 10K

RH70

CH25

16V 10µ

RH82 2R47

CH18

V.Ref

RAMP.0

10K

RH99

330K

M0.1

1st delay

RH71

22K

CH19

M0.015

CH26

CH27

M0.01

RH65

T560

10K

CH76

RH87

M0.01

100

V.OUT

2nd delay

RH72

22K

RH73

10

RH60

6.8K

CH30

50V

10µ

RH61

QH42

RN1202

7654321

RH74

22K

CH22

16V

CH23

330µ

150P

CH21

CH20

M0.1

M0.0033

22 21 20 19 18 17 16

H.LOCK

AFC

89

100

V/I

RH25

SAW

H.OSC

10 11 12 13 14 15

CH33

RK66

1/4W

T2700

3.6KF

RH77

1/4W

RH78

2.7KF

2.2K

CH31

1

M0.039

5KB

2

3

RGB fH ADJ.

Fig. 32

CH32

50V

2.2µ

RH62

22K

CH34

M0.001

CH73

50V

2.2µ

12V

M.M

AFC

CH35

M0.1

RH59

3.9K

H.REG

RH79

1.5K

CH36

16V

330µ

H.OUT

COMP

QK07

2SC752-Yoro

RK38

18K

RH34

1/4W1KF

CH37

50V

10µ

NTSC fH ADJ.

1

RH35 5008

RH80

18K

RH81

39K

2

3

QH15

RN1203

RK36

3.3K

H.D

RH3

1/4W

750F

2-4 Other Circumference Circuit

QH15 changes the duty ratio of hor output pulse (that is; hor

drive pulse) of ICH08 so that the base current of hor output

transistor becomes respectively optimum in both high

frequency mode and low frequency mode (including TV

mode). Since for the signal which drives QH15, the output of

frequency discriminating circuit as mentioned above is used,

duty ratio changes around 28kHz. In passing, when frequency

is low, ratio of period of high level in output pulse at pin 16

is extended.

Driving pulse of control IC IC302 (TA8859AP) in Ver

deflection circuit is supplied by inverted pulse at pin 24 of

ICH08.

The pulse at pin 25 is used as blanking pulse in Video circuit.

7-11

Page 45

SECTION VIII VERTICAL DEFLECTION CIRCUIT

The basic configulation is the same as TV of N4SS chassis. Size and linearity are adjusted by sending data to IC302 (TA8859AP)

through I2C-Bus line.

Unlike ordinary TV, the adjusting data are stored in memory; 4 sets for RGB mode besides for TV. In RGB mode only, user

control can be adjusted, and in addition, 3 sets of user adjusting data are memorized.

Ver centering circuit which is adjustable by remote control, is added as well. And in RGB mode, user can control size and picture

position.

1. OUTLINE

As can be seen from the block diagram, the sync circuit and

the V trigger circuit are contained in ICH08 (LA7860), and

the sawtooth generation circuit and amplifier (V drive circuit)

SYNC

CIRCUIT

ICH08 LA7860

V. TRIGGER

IC302 TA8859AP

Fig. 1 Block diagram of V deflection circuit

1-1 Theory of Operation

The purpose of the V output circuit is to provide a sawtooth

wave signal with good linearity in V period to the deflection

yoke.

When a switch S is opened, an electric charge charged up to

a reference voltage VP discharges in an constant current rate,

contained in IC302 (TA8859AP). The output circuit and

pump-up circuit circuits are included in IC301 (TA8427K).

SAM TOOTH

WAVE GAIN

CIRCUIT

AMP

LOGIC

CIRCUIT

and a reference sawtooth voltage generates at point . This

voltage is applied to (+) input (non-inverted input) of an

differential amplifier, A. As the amplification factor of A is

sufficiently high, a deflection current flows so that the

voltage V2 at point becomes equal to the voltage at point

IC301 TA8427K

PUMP-UP

CIRCUIT

OUTPUT

Microcomputer

CENTERING

CIRCUIT

DEFLECTION

YOKE

.

VP

a

R1 C2

S: Switch

R2

Differential

amplifier

A

L

C2

R3

c

V2

Fig. 2

8-1

Page 46

2. V OUTPUT CIRCUIT

3

2-1 Actual Circuit

R320

R329

C321

15

14

13

C332

IC302

3

6

8

+12V

R308

C314

R317

C319

+29V

D309

6

5

C308

3

2

C311

D301

L301

R307

R306

R304

R303

C305

C313

C309

C306

R305

R336

CENTERING

CIRCUIT

Q308,Q309

L462

R309

D308

7

IC301

4

1

C312

Fig. 3

2-2 Sawtooth Waveform Generation

(1) Circuit Operation

The sawtooth waveform generation circuit consists of as

shown in Fig. 4. When a trigger pulse enters pin 13, it is

differentiated in the waveform shape circuit and only the

falling part is detected by the trigger detection circuit, so the

waveform generation circuit is not susceptible to variations

of input pulse width.

WAVEFORM

SHAPE

DC=0V

TRIGGER

The pulse generation circuit also works to fix the V ramp

voltage at a reference voltage when the trigger pulse enters,

so it can prevent the sawtooth wave start voltage from

variations by horizontal component, thus improving

interlacing characteristics.

DET.

R329

PULSE

GAIN

14

C321 C322

V. LAMP

15

+12V

Fig. 4

AGC

16

C32

8-2

Page 47

2-3 V Output

(1) Circuit Operation

The V output circuit consists of a V driver circuit IC302,

Pump-up circuit and output circuit IC301, and external

circuit components.

Q2 amplifies its input fed from pin 4 of IC301. Q3, Q4

output stage connected in a SEPP amplifies the current

and supplies a sawtooth waveform current and supplied

a sawtooth waveform current to a deflection yoke. Q3 turns

on for first half of the scanning period and allows a positive

current to flow into the deflection yoke (Q3 DY C306

R305 GND), and Q4 turns on for last half of the

scanning period and allows a negative current to flow into

the deflection yoke (R305 C306 DY Q4). These

operations are shown in Fig. 5.

Q301

Q2

4

+27V

D301

6

BIAS

CIRCUIT

1

3

Q3

C308

D308

Q4

Fig. 5 V output circuit

In Fig. 6 (a), the power Vcc is expressed as a fixed level,

and the positive and negative current flowing into the

deflection yoke is a current (d) = current (b) + (c) in Fig.

6, and the emitter voltage of Q3 and Q4 is expressed as

(e).

50V

V 3

D309

R309

7

2

DY

C306

R305

V 7

V 2

Q3 ON

Q4 ON

27V

GND

27V

GND

50V

GND

GND

Q3 collector loss i1 x Vce1 and the value is equal to

multiplication of Fig. 6 (b) and slanted section of Fig. 6

(e), and Q4 collector loss is equal to multiplication of

Fig. 6 (c) and dotted section of Fig. 6 (e).

Q3

Q4

Q2

(a) Basic circuit

Power Vcc

i1

i2

Vce1

Fig. 6 Output stage operation waveform

8-3

GND

(b) Q3 Collector current i1

(c) Q4 Collector current i2

GND

(d) Deflection yoke current i1+i2

GND

Vp

Vcc

1/2 Vcc

GND

(e)

Page 48

To decrease the collector loss of Q3, the power supply

y

D301 C308

D308

D309 R309

Q301

Q3

Q4

D1

2

7

L462

C306

R305

Switch

6

3

D301 C308

D308

D309 R309

Q301

Q3

Q4

D1

2

7

L462

C306

R305

Switch

6

3

Last half

VR

First half

voltage is decreased during scanning period as shown in

Fig. 7, and VCE1 decreases and the collector loss of Q3

also decreases.

Q3 Collector loss decrease

by amount of this area

Power supply for

flyback period (Vp)

Power supply for

scanning period

(Vcc)

Since pin 7 of a transistor switch inside IC301 is

connected to the ground for the scanning period, the

power supply (pin 3) of the output stage shows a voltage

of (VCC – VF), and C308 is charged up to a voltage of

(VCC – VF – VR) for this period.

Last half of flyback period

Current flows into L462 D1 C308 D308

VCC (+27V) GND R305 C306 L462 in

this order, and the voltage across these is:

VP = VCC + VF + (VCC – VF – VR) + VF about 58V is

applied to pin 3. In this case, D301 is cut off.

Scanning period

Fl

back period

Fig. 7 Output stage power supply voltage

In this way, the circuit which switches power supply

circuit during scanning period and flyback period is

called a pump-up circuit. The purpose of the pump-up

circuit is to return the deflection yoke current rapidly

for a short period (within the flyback period) by applying

a high voltage for the flyback period. The basic operation

is shown in Fig. 8.

First half of flyback period

Current flows into VCC switch D309 D308

IC301 (pin 3) Q3 L462 C306 R305 in this

order, and a voltage of

VP = VCC – VCE (sat) – VF + (VCC – VF – VR) – VCE (sat),

about 54V is applied to pin 3.

In this way, a power supply voltage of about 29V is

applied to the output stage for the scanning period and

about 54V for flyback period.

(a) Scanning period

Fig. 8

8-4

(b) Flyback period

Page 49

2-4 V Linearity Characteristic Correction

(1) S-character Correction

(Up-and Down-ward Extension Correction)

A parabola component developed across C306 is integrated

by R306 and C305, and the voltage is applied to pin 6 of

(2) Up- and Down-ward Linearity Balance

A voltage developed at pin 2 of IC301 is divided with

resistors R307 and R303, and the voltage is applied to pin 6

of IC302 to improve the linearity balance characteristic.

IC302 to perform S-character correction.

Moreover, the S-character correction, up- and down-ward

balance correction, and M-character correction are also

performed through the bus control.

3. VER CENTERING CIRCUIT

This circuit is designed so that user can adjust picture to desired position on screen, in spite of various signals which exist as

input signals in RGB mode.

2

I C-Bus

6

L462

C306

R305

Q308

ICA01

MICOM

T-Bus

ICA02

MEMORY

+30V

IC301

V OUT

1

2

ICX001

DAC

12

ICK09

6

7

5

Supplying current to Q309 from deflection yoke L462 causes

picture position to move up, in reverse supplying current to

L462 from Q308 causes position to move down. This control

can be done by remote control unit or key on TV set. Micom

IC sends data to DAC IC ICX001 via T-Bus line, and the

output is sent from pin 12 to pin 5 of Ope. amp ICK09 to

adjust base voltages of Q308 and Q309.

R325

Q309

Q307

C325

Fig. 9

To memorize picture position, control data;1 for TV and 4

for RGB are stored in Memory IC ICA02.

Micom reads out the data which responds the selected mode,

and sends it to DAC. As a result, picture position automatically

fits to the preadjusted position.

8-5

Page 50

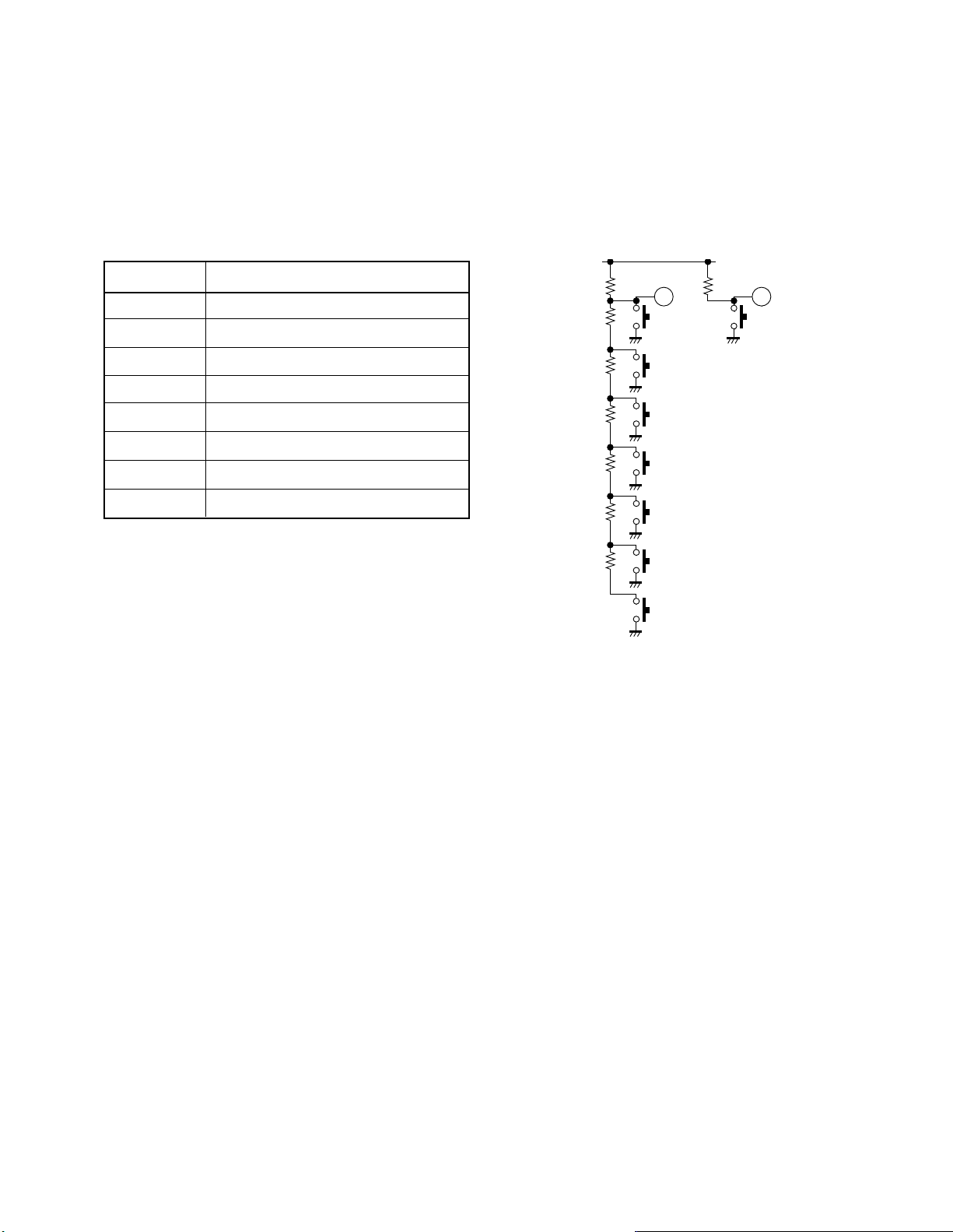

SECTION IX HORIZONTAL DEFLECTION CIRCUIT

This model employs special circuit configulation, since the hor deflection circuit should keep operation with any frequency

ranging from 15kHz to 40kHz unlike ordinary TV set. That is; the circuit which fills the role of supplying current into deflection

yoke, and the circuit which generates the high voltage, are separated.

From now on, the former is called as DEFLECTION CIRCUIT, and the latter is called as HIGH VOLTAGE CIRCUIT.

Therefore, two hor output transistors exist, and also two sets of hor drive circuit exist.

But on both circuits, operation theory of the most basic part is the same as that of ordinary TV. The circuit description is as

follows.

1. DEFLECTION CIRCUIT

1-1 Outline

Fig. 1 is block diagram.

QH30

H.Drive

Trans.

TK01

CHOPPER

REGULATOR

HOR.

OUTPUT

QH25

CH60

CH57

CH58

QH29

L462

11

TH02

3

1

6

5

8

4

AFC pulse

BLK pulse

CH65

TH02 is a transformer corresponding to FBT of ordinary TV

set, and from which AFC pulse and BLK pulse are taken out.

The power source produced from pins 4 to 6 of the transformer,

let the hor centering circuit which moves raster left and right

operate.

In ordinary TV, size and side-pincushion distortion are

adjusted by using diode modulator, but in this model, those

are adjusted by using chopper.

LH04

CH66

QH36

Fig. 1

Unlike TV, the resonating capacitor and the S-character

capacitor are changed by operation frequency.

The changing elements are QH29 and QH39. Then, basic

operation theory common with TV, will be explained in the

next section.

9-1

Page 51

1-2 Theory of Operation

Description of the basic circuit

(1) Operation of Basic Circuit

To perform the horizontal scanning, a sawtooth wave

current must be flown into the horizontal deflection

coil. Theoretically speaking, this operation can be made

with the circuit shown in Fig. 2 and .

As the switching operation of the circuit can be replaced

with switching operation of a transistor and a diode, the

basic circuit of the horizontal output can be expressed

by the circuit shown in Fig. 2 . That is, the transistor

can be turned on or off by applying a pulse across the

base emitter. A forward switching current flows for onperiod, and a reverse switching current flows through